Intersil ISL5740 Datasheet

TM

ISL5740

PRELIMINARY

Data Sheet June 2000 File Number 4821.2

3V Dual 10-Bit, 20/40/60MSPS A/D

Converter with Internal Voltage Reference

The ISL5740 is a monolithic, dual 10-bit analog-to-digital

converter fabricated in an advanced CMOS process. It is

designed for high speed applications where integration,

bandwidth and accuracy are essential. The ISL5740

features a 9-stage pipeline architecture. The fully pipelined

architecture and an innovative input stage enable the

ISL5740 to accept a variety of input configurations, singleended or fully differential. Only one external clock is

necessary to drivebothconverters and an internal band-gap

voltage reference is provided. This allows the system

designer to realize an increased level of system integration

resulting in decreased cost and power dissipation.

The ISL5740 has excellent dynamic performance while

consuming less than 280mW power at 60MSPS. The A/D

only requires a single +3.0V power supply. Data output

latches are provided which present valid data to the output

bus with a latency of 5 clock cycles.

The ISL5740 is offered in 20MSPS, 40MSPS and 60MSPS

sampling rates.

Ordering Information

TEMP.

PART

NUMBER

RANGE

(oC) PACKAGE PKG. NO.

ISL5740/2IN -40 to 85 48 Ld LQFP Q48.7x7 20

ISL5740/3IN -40 to 85 48 Ld LQFP Q48.7x7 30

ISL5740/4IN -40 to 85 48 Ld LQFP Q48.7x7 40

ISL5740/6IN -40 to 85 48 Ld LQFP Q48.7x7 60

ISL5740 EVAL 25 Evaluation Platform

SAMPLIN

G RATE

(MSPS)

Features

• Sampling Rate . . . . . . . . . . . . . . . . . . . . . .20/40/60MSPS

• 9.1 Bits at f

= 10MHz

IN

• Low Power at 60MSPS. . . . . . . . . . . . . . . . . . . . . .280mW

• Power Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 6mW

• Wide Full Power Input Bandwidth. . . . . . . . . . . . . 400MHz

• SFDR at f

= 10MHz. . . . . . . . . . . . . . . . . . . . . . . . .70dB

IN

• Excellent Channel-to-Channel Isolation. . . . . . . . . . .75dB

• On-Chip Sample and Hold Amplifiers

• Internal Bandgap Voltage Reference . . . . . . . . . . . . 1.25V

• Single Supply Voltage Operation . . . . . . . . . .+2.7V - 3.6V

• TTL/CMOS(3V) Digital Inputs CMOS Digital Outputs

• Offset Binary or Two’s Complement Digital Data Output

Format

• Dual 10-Bit A/D Converters on a Monolithic Chip

• Pin Compatible Upgrade to AD9288

Pinout

• Wireless Local Loop

• PSK and QAM I&Q Demodulators

• Medical Imaging and Instrumentation

• Wireless Communications Systems

• Battery Powered Instruments

Pinout

CC

CC

AV

I CLK

DV

GND

ID9

ID8

ID7

ID6

ID5

ID4

ID3

ID2

GND

I

+

IN

-

I

IN

DFS

IV

RIN

V

ROUT

QV

RIN

S1

S2

QINQIN+

GND

3-1

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16

CC

AV

Q CLK

DV

CC

GND

QD9

QD8

QD7

QD6

QD5

QD4

373839404142434445464748

2423222120191817

QD3

36

35

34

33

32

31

30

29

28

27

26

25

QD2

ID1

ID0

GND

DV

GND

AV

AV

GND

DV

GND

QD0

QD1

CC

CC

CC

CC

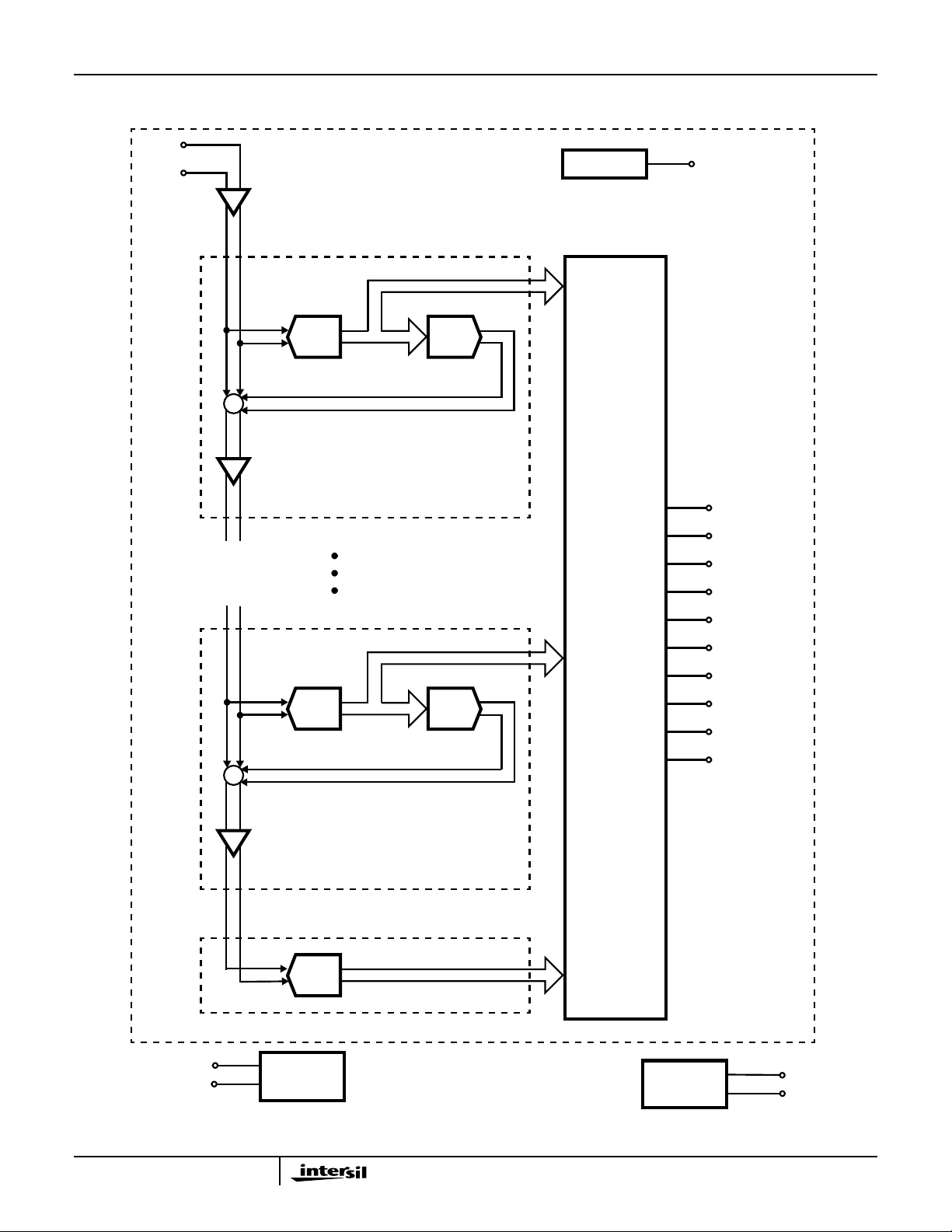

Functional Block Diagram

-

I/Q

IN

I/Q

+

IN

S/H

STAGE 1

ISL5740

CLOCK

I/QCLK

2-BIT

FLASH

+

-

∑

X2

STAGE 8

2-BIT

FLASH

+

∑

-

2-BIT

DAC

2-BIT

DAC

DIGITAL DELAY

AND

DIGITAL ERROR

CORRECTION

I/QD9 (MSB)

I/QD8

I/QD7

I/QD6

I/QD5

I/QD4

I/QD3

I/QD2

I/QD1

I/QD0 (LSB)

V

I/QV

ROUT

RIN

X2

REFERENCE

3-2

2-BIT

FLASH

STAGE 9

AV

CC

AGND DV

CC

DGND

I OR Q CHANNEL

MODE

DATA FORMAT

S1/S2

DFS

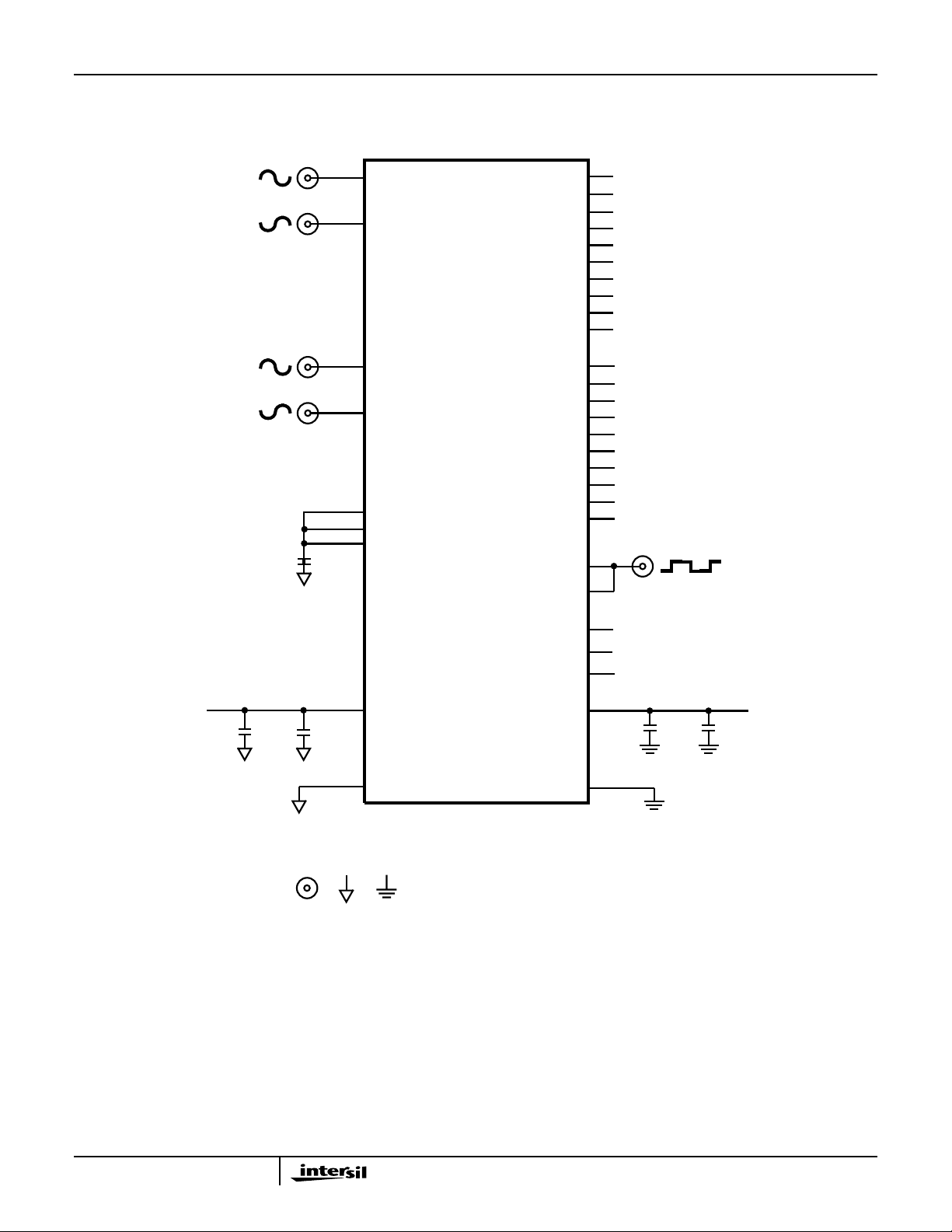

Typical Application Schematic

ISL5740

ISL5740

I

+

IN

- (3) IIN-

I

IN

QIN+

QIN-

0.1µF

(2) I

+

IN

(11) QIN+

(10) QIN-

(5) IV

RIN

(6) QV

RIN

(7) V

ROUT

ID1 (36)

ID2 (37)

ID3 (38)

ID4 (39)

ID5 (40)

ID6 (41)

ID7 (42)

ID8 (43)

(MSB) ID9 (44)

(LSB) QD0 (26)

QD1 (25)

QD2 (24)

QD3 (23)

QD4 (22)

QD5 (21)

QD6 (20)

QD7 (19)

QD8 (18)

(MSB) QD9 (17)

ICLK (47)

QCLK (14)

ID0(LSB) ID0 (35)

ID1

ID2

ID3

ID4

ID5

ID6

ID7

ID8

ID9

QD0

QD1

QD2

QD3

QD4

QD5

QD6

QD7

QD8

QD9

CLOCK

+3V

10µF

S1 (8)

S2 (9)

DFS (4)

AGND

(13,30,31,48) AV

(12,29,32) AGND

DGND

+

0.1µF

BNC

CC

DVCC(15, 28, 33, 46)

DGND (16, 27, 34, 45)

10µF AND 0.1µF CAPS

ARE PLACED AS CLOSE

TO PART AS POSSIBLE

S1

S2

DFS

0.1µF10µF

+

3V

3-3

ISL5740

Pin Descriptions

PIN NO. NAME DESCRIPTION

1A

2I

3I

GND

IN+

IN-

4 DFS Data Format Select (Low for Offset

5IV

6V

ROUT

7QV

8 S1 Mode Select Pin 1 (See Table)

9 S2 Mode Select Pin 2 (See Table)

10 Q

11 Q

12 A

GND

13 AV

14 QCLK Q-Channel Clock Input

15 DV

16 D

GND

17 QD9 Q-Channel, Data Bit 9 Output (MSB)

18 QD8 Q-Channel, Data Bit 8 Output

19 QD7 Q-Channel, Data Bit 7 Output

20 QD6 Q-Channel, Data Bit 6 Output

21 QD5 Q-Channel, Data Bit 5 Output

22 QD4 Q-Channel, Data Bit 4 Output

23 QD3 Q-Channel, Data Bit 3 Output

Analog Ground

I-Channel Positive Analog Input

I-Channel Negative Analog Input

Binary and High for Twos Complement

Output Format)

I-Channel Voltage Reference Input

RIN

+1.25V Reference Voltage Output

(Decouple with 0.1µF Capacitor)

Q-Channel Voltage Reference Input

RIN

Q-Channel Negative Analog Input

IN-

Q-Channel Positive Analog Input

IN+

Analog Ground

Analog Supply

CC

Digital Supply

CC

Digital Ground

Pin Descriptions (Continued)

PIN NO. NAME DESCRIPTION

24 QD2 Q-Channel, Data Bit 2 Output

25 QD1 Q-Channel, Data Bit 1 Output

26 QD0 Q-Channel, Data Bit 0 Output (LSB)

27 D

GND

28 DV

29 A

GND

30 AV

31 AV

32 A

GND

33 DV

34 D

GND

35 ID0 I-Channel, Data Bit 0 Output (LSB)

36 ID1 I-Channel, Data Bit 1 Output

37 ID2 I-Channel, Data Bit 2 Output

38 ID3 I-Channel, Data Bit 3 Output

39 ID4 I-Channel, Data Bit 4 Output

40 ID5 I-Channel, Data Bit 5 Output

41 ID6 I-Channel, Data Bit 6 Output

42 ID7 I-Channel, Data Bit 7 Output

43 ID8 I-Channel, Data Bit 8 Output

44 ID9 I-Channel, Data Bit 9 Output (MSB)

45 D

GND

46 DV

47 ICLK I-Channel Clock Input

48 AV

CC

CC

CC

CC

CC

CC

Digital Ground

Digital Supply

Analog Ground

Analog Supply

Analog Supply

Analog Ground

Digital Supply

Digital Ground

Digital Ground

Digital Supply

Analog Supply

3-4

Loading...

Loading...