Intersil Corporation ICL7137, ICL7136 Datasheet

December 1997

ICL7136, ICL7137

31/2 Digit LCD/LED, Low Power Display,

A/D Converters with Overrange Recovery

Features

• First Reading Overrange Recovery in One Conversion

Period

• Guaranteed Zero Reading for 0V Input on All Scales

• True Polarity at Zero for Precise Null Detection

• 1pA Typical Input Current

• True Differential Input and Reference, Direct Displa y Drive

- LCD ICL7136

- LED lCL7137

• Low Noise - Less Than 15µV

P-P

• On Chip Clock and Reference

• No Additional Active Circuits Required

• Low Power - Less Than 1mW

• Surface Mount Package Available

• Drop-In Replacement for ICL7126, No Changes Needed

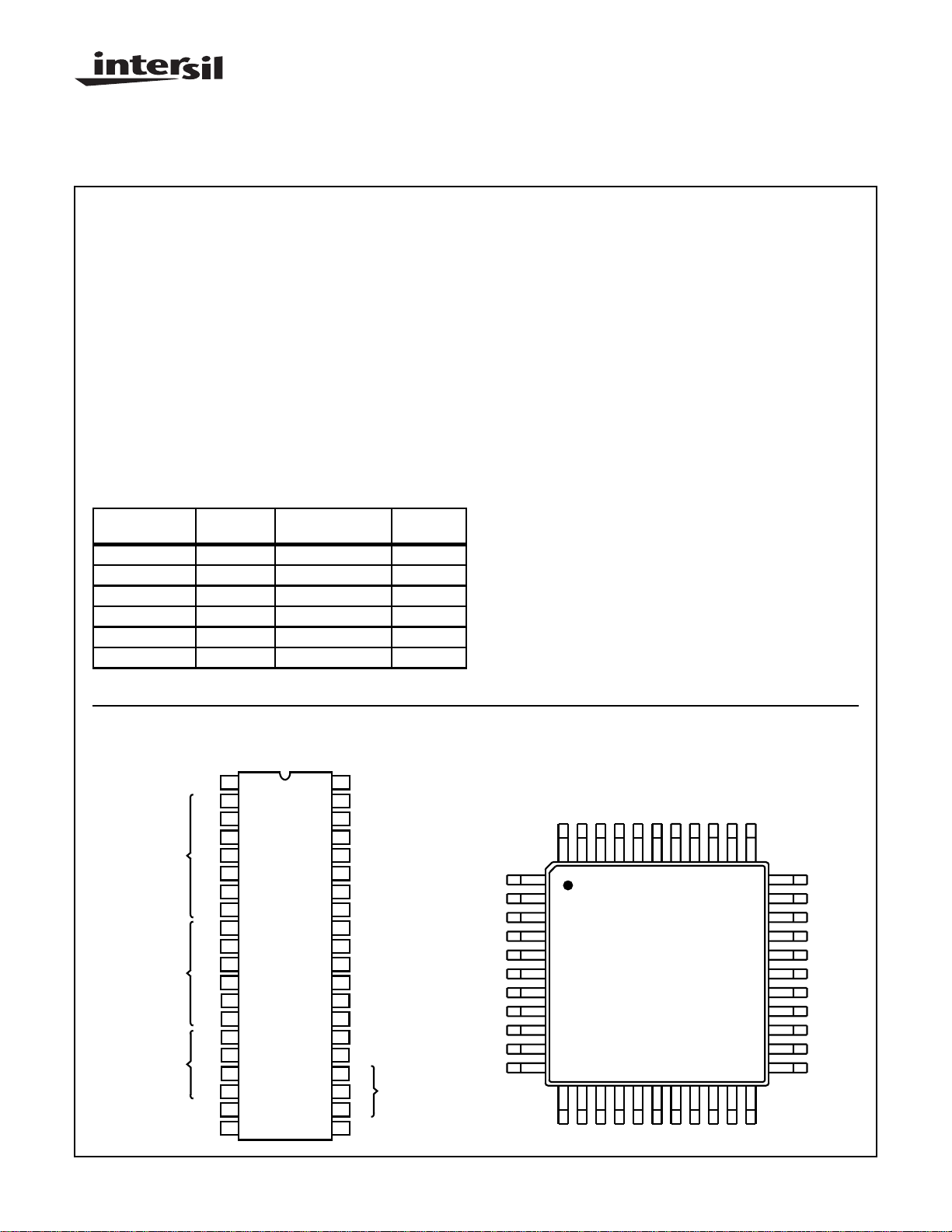

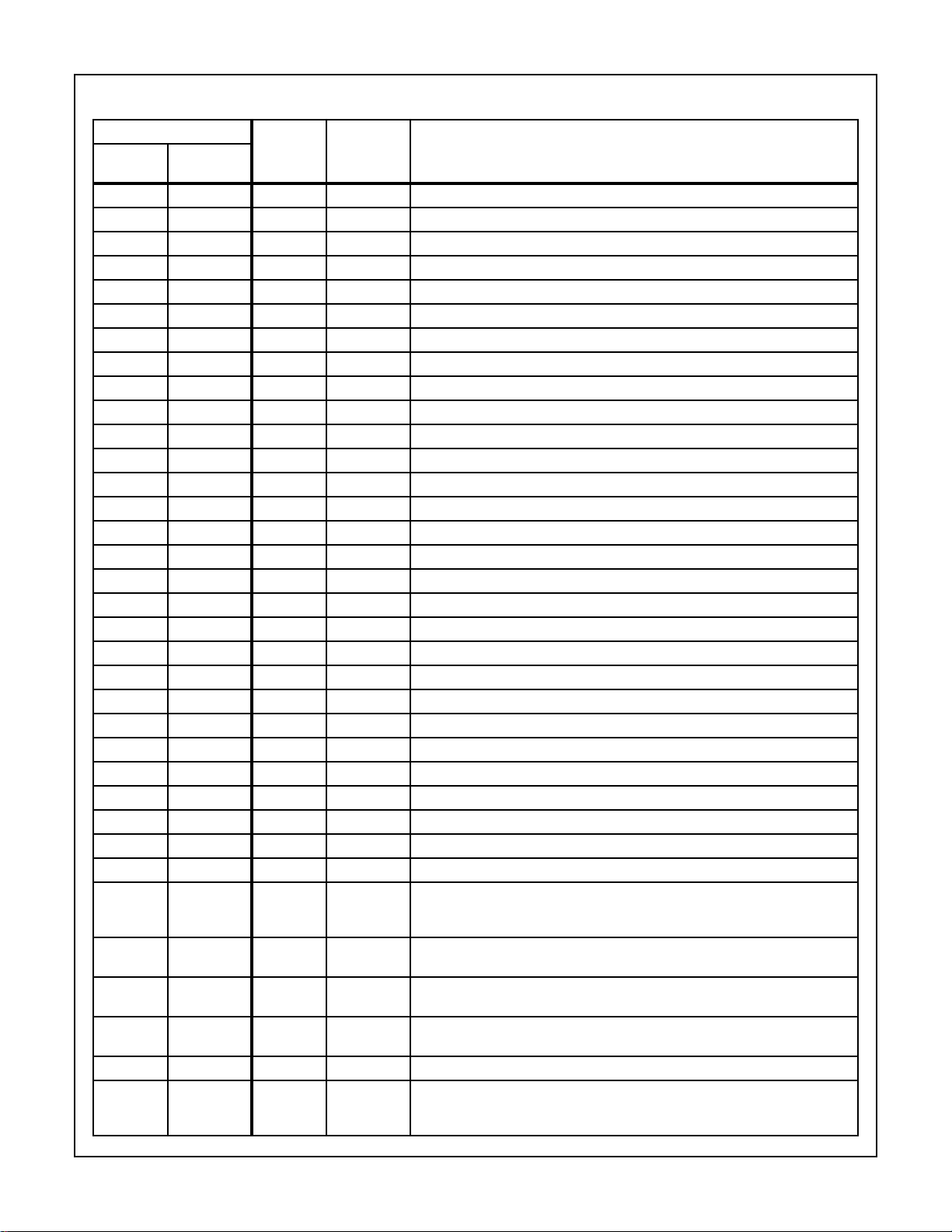

Ordering Information

TEMP.

PART NUMBER

ICL7136CPL 0 to 70 40 Ld PDIP E40.6

ICL7136RCPL 0 to 70 40 Ld PDIP (Note) E40.6

ICL7136CM44 0 to 70 44 Ld MQFP Q44.10x10

ICL7137CPL 0 to 70 40 Ld PDIP E40.6

ICL7137RCPL 0 to 70 40 Ld PDIP (Note) E40.6

ICL7137CM44 0 to 70 44 Ld MQFP Q44.10x10

NOTE: “R” indicates device with reversed leads.

RANGE (oC) PACKAGE PKG. NO.

Description

The Intersil ICL7136 and ICL7137 are high performance, low

power 31/2 digit, A/D converters. Included are seven segment decoders, display drivers, a reference, and a clock.

The ICL7136 is designed to interface with a liquid crystal display (LCD) and includes a multiplexed backplane drive; the

ICL7137 will directly drive an instrument size, light emitting

diode (LED) display.

The ICL7136 and ICL7137 bring together a combination of

high accuracy, versatility, and true economy. It features autozero to less than 10µV, zero drift of less than 1µV/

bias current of 10pA (Max), and rollover error of less than

one count. True differential inputs and reference are useful in

all systems, but give the designer an uncommon advantage

when measuring load cells, strain gauges and other bridge

type transducers. Finally, the true economy of single power

supply operation (ICL7136), enables a high performance

panel meter to be built with the addition of only 10 passive

components and a display.

The ICL7136 and ICL7137 are improved versions of the

ICL7126, eliminating the overrange hangover and hysteresis

effects, and should be used in its place in all applications. It

can also be used as a plug-in replacement for the ICL7106

in a wide variety of applications, changing only the passive

components.

o

C, input

Pinouts

(PDIP)

TOP VIEW

1

V+

2

D1

3

C1

4

B1

(1’s)

(10’s)

(100’s)

(1000) AB4

(MINUS)

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

A1

F1

G1

E1

D2

C2

B2

A2

F2

E2

D3

B3

F3

E3

POL

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

| Copyright © Intersil Corporation 1999

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

OSC 1

OSC 2

OSC 3

TEST

REF HI

REF LO

+

C

REF

C

-

REF

COMMON

IN HI

IN LO

A-Z

BUFF

INT

VG2 (10’s)

C3

(100’s)

A3

G3

BP/GND

NC

NC

TEST

OSC 3

NC

OSC 2

OSC 1

V+

D1

C1

B1

1

44 43 42 41 40

1

2

3

4

5

6

7

8

9

10

11

12 13 14 15 16 17

A1 F1 G1 E1 D2 C2

REF HI

REF LO

+

REF

C

-

C

(MQFP)

TOP VIEW

REF

COMMON

IN HI

IN LO

39 38 37 36 35 34

B2 A2 F2 E2 D3

A-Z

BUFF

INT

V-

33

32

31

30

29

28

27

26

25

24

23

2221201918

File Number 3086.2

NC

G2

C3

A3

G3

BP/GND

POL

AB4

E3

F3

B3

ICL7136, ICL7137

Absolute Maximum Ratings Thermal Information

Supply Voltage

ICL7136, V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15V

ICL7137, V+ to GND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6V

ICL7137, V- to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-9V

Analog Input Voltage (Either Input) (Note 1). . . . . . . . . . . . . V+ to V-

Reference Input Voltage (Either Input) . . . . . . . . . . . . . . . . . V+ to V-

Clock Input

ICL7136 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TEST to V+

ICL7137 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .GND to V+

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . .0oC to 70oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Input voltages may exceed the supply voltages provided the input current is limited to ±100µA.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

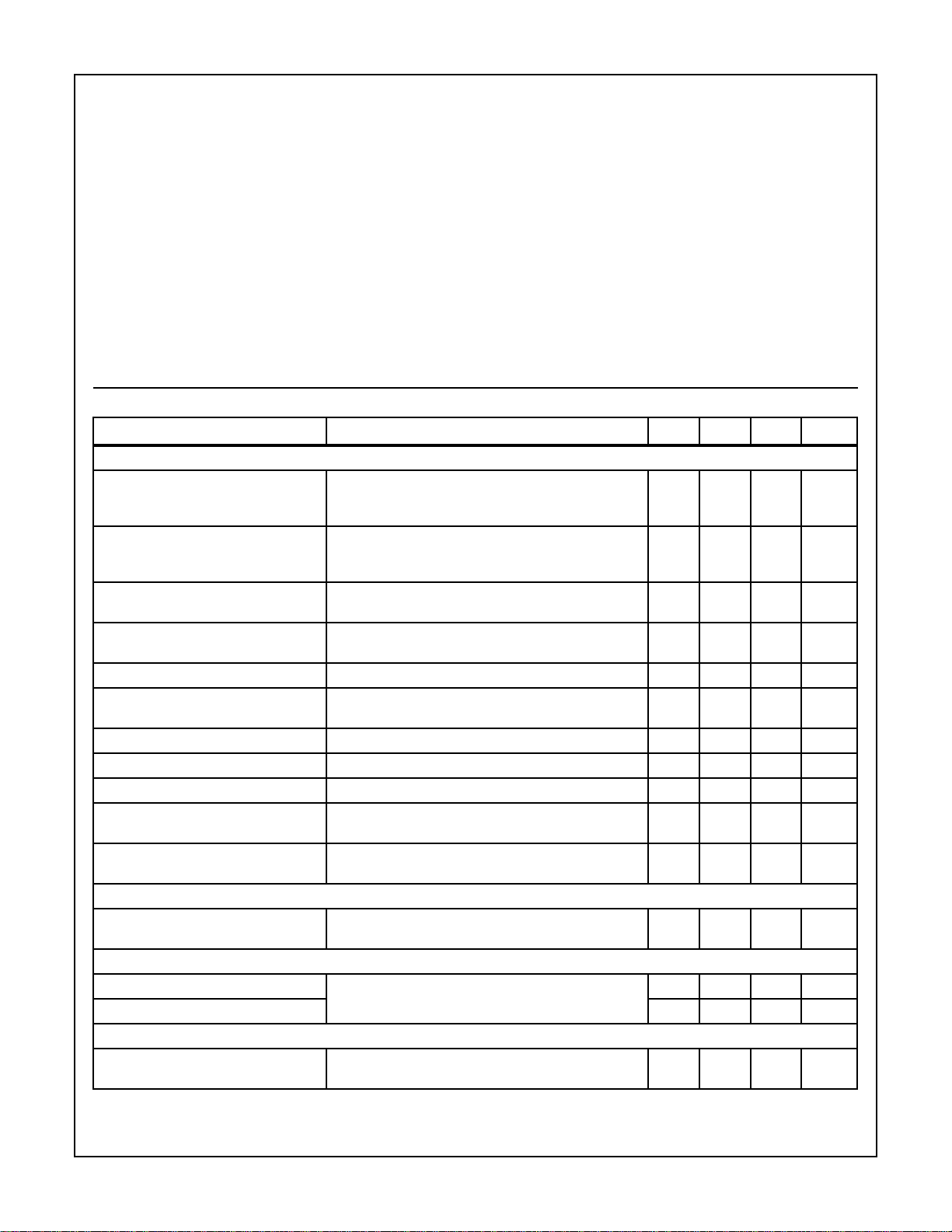

Electrical Specifications (Note 3)

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

SYSTEM PERFORMANCE

Zero Input Reading VIN = 0V, Full Scale = 200mV -000.0 ±000.0 +000.0 Digital

Ratiometric Reading VlN = V

Rollover Error -VIN = +VlN≅ 200mV Difference in Reading for Equal

Positive and Negative Inputs Near Full Scale

Linearity Full Scale = 200mV or Full Scale = 2V Maximum

Deviation from Best Straight Line Fit (Note 5)

Common Mode Rejection Ratio VCM = ±1V, VIN = 0V, Full Scale = 200mV (Note 5) - 50 - µV/V

Noise VIN = 0V, Full Scale = 200mV (Peak-To-Peak Value Not

Exceeded 95% of Time) (Note 5)

Leakage Current Input VlN = 0V (Note 5) - 1 10 pA

Zero Reading Drift VlN = 0V, 0oC To 70oC (Note 5) - 0.2 1 µV/oC

Scale Factor Temperature Coefficient VIN = 199mV, 0oC To 70oC, (Ext. Ref. 0ppm/oC) (Note 5) - 1 5 ppm/oC

COMMON Pin Analog Common Voltage 25kΩ Between Common and Positive Supply (With

Respect to + Supply)

Temperature Coefficient of Analog

Common

SUPPLY CURRENT ICL7136

V+ Supply Current VIN = 0 (Does Not Include Common Current) 16kHz

SUPPLY CURRENT ICL7137

V+ Supply Current VIN = 0 (Does Not Include Common Current) 16kHz

V- Supply Current -40-µA

DISPLAY DRIVER ICL7136 ONLY

Peak-To-Peak Segment Drive Voltage

Peak-To-Peak Backplane Drive Voltage

25kΩ Between Common and Positive Supply (With

Respect to + Supply) (Note 5)

Oscillator (Note 6)

Oscillator (Note 6)

V+ = to V- = 9V (Note 4) 4 5.5 6 V

REF

, V

= 100mV 999 999/

REF

Thermal Resistance (Typical, Note 2) θJA (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

MQFP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .300oC

(MQFP - Lead Tips Only)

Read-

ing

1000 Digital

1000

- ±0.2 ±1 Counts

- ±0.2 ±1 Counts

-15-µV

2.4 3.0 3.2 V

- 150 - ppm/oC

- 70 100 µA

- 70 200 µA

Read-

ing

2

ICL7136, ICL7137

Electrical Specifications (Note 3) (Continued)

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

DISPLAY DRIVER ICL7137 ONLY

Segment Sinking Current V+ = 5V, Segment Voltage = 3V

(Except Pins 19 and 20) 58-mA

Pin 19 Only 10 16 - mA

Pin 20 Only 47-mA

NOTES:

3. Unless otherwise noted, specifications apply to both the ICL7136 and ICL7137 at TA = 25oC, f

circuit of Figure 1. ICL7137 is tested in the circuit of Figure 2.

4. Back plane drive is in phase with segment drive for ‘off’ segment, 180 degrees out of phase for ‘on’ segment. Frequency is 20 times

conversion rate. Average DC component is less than 50mV.

5. Not tested, guaranteed by design.

6. 48kHz oscillator increases current by 20µA (Typ).

= 48kHz. ICL7136 is tested in the

CLOCK

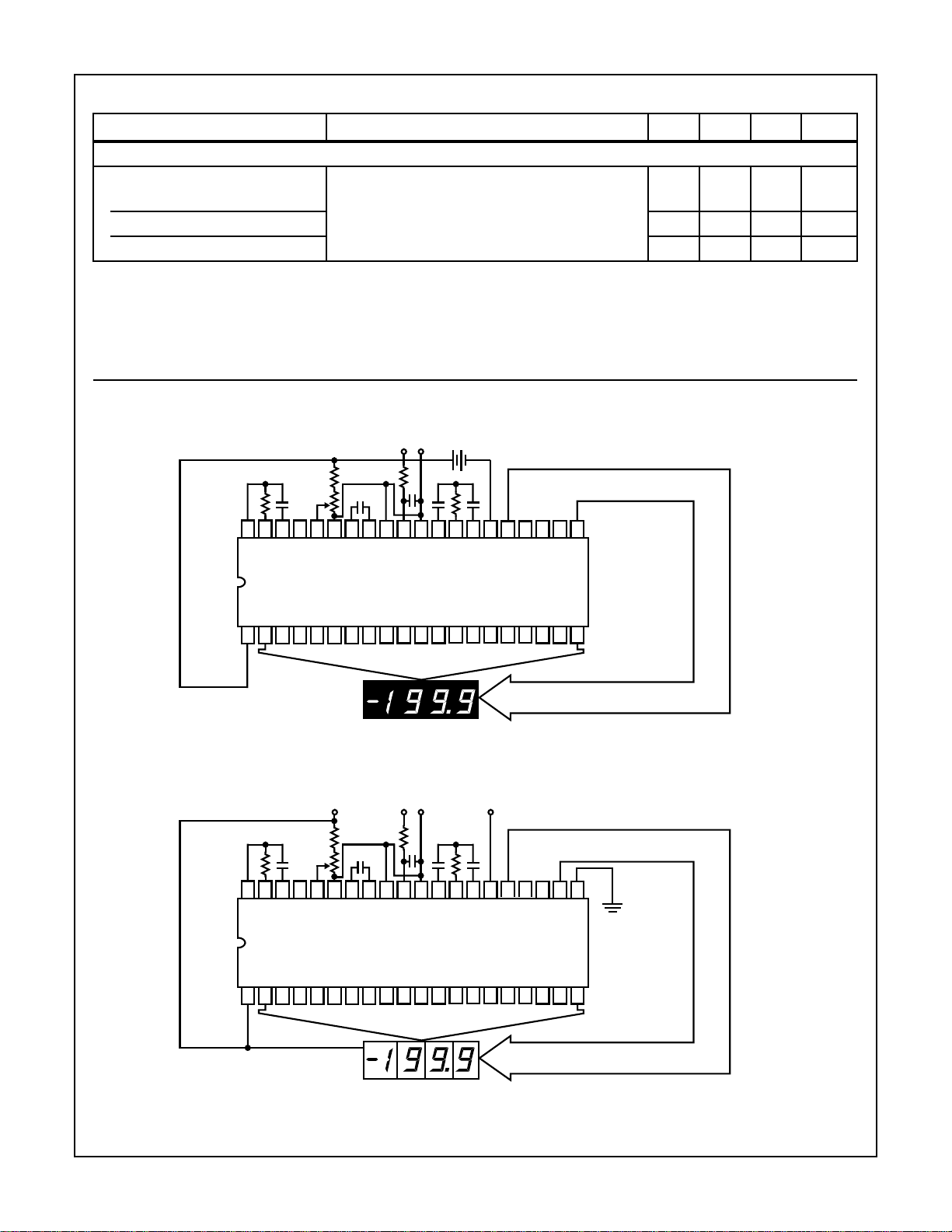

Typical Applications and Test Circuits

IN

C

5

C

2

IN HI

IN LO

101112

9V

+

-

R

2

C

3

28

29

27262524232221

V-

INT

A-Z

BUFF

F2

E2

A2

D3

13

14151617181920

DISPLAY

G2

B3

C1= 0.1µF

C2= 0.47µF

C3= 0.047µF

C3

A3

G3

BP

C4= 50pF

C5= 0.01µF

R1= 240kΩ

R2= 180kΩ

F3

E3

AB4

POL

R3= 180kΩ

R4= 10kΩ

R5= 1MΩ

+ -

R

C

+

REF

C

5

1

-

REF

COM

C

R

1

R

C

4

OSC 3

TEST

4

REF HI

REF LO

R

3

4039383736353433323130

OSC 1

OSC 2

ICL7136

V+

D1C1B1

123456789

F1

G1

E1

D2C2B2

DISPLAY

A1

FIGURE 1. ICL7136 TEST CIRCUIT AND TYPICAL APPLICA TION WITH LCD DISPLAY COMPONENTS SELECTED FOR 200mV FULL SCALE

+5V -5V

R

1

R

R

3

4

C

4

+ -

IN

R

5

C

5

R

C

1

2

C

C

2

3

DISPLAY

C1= 0.1µF

C2= 0.47µF

IN LO

28

29

27262524232221

V-

INT

A-Z

BUFF

F2

E2

A2

D3

13

14151617181920

G2

B3

C3= 0.047µF

C3

A3

G3

GND

C4= 50pF

C5= 0.01µF

R1= 240kΩ

R2= 180kΩ

F3

E3

AB4

POL

R3= 180kΩ

R4= 10kΩ

R5= 1MΩ

4039383736353433323130

OSC 2

OSC 3

TEST

REF HI

OSC 1

+

REF

C

REF LO

-

REF

C

COM

IN HI

ICL7137

V+

D1C1B1

123456789

F1

G1

E1

D2C2B2

101112

DISPLAY

A1

FIGURE 2. ICL7137 TEST CIRCUIT AND TYPICAL APPLICA TION WITH LED DISPLAY COMPONENTS SELECTED FOR 200mV FULL SCALE

3

Design Information Summary Sheet

• OSCILLATOR FREQUENCY

= 0.45/RC

f

OSC

C

> 50pF; R

OSC

f

(Typ) = 48kHz

OSC

• OSCILLATOR PERIOD

= RC/0.45

t

OSC

• INTEGRATION CLOCK FREQUENCY

CLOCK

= f

OSC

f

• INTEGRATION PERIOD

= 1000 x (4/f

t

INT

• 60/50Hz REJECTION CRITERION

t

INT/t60Hz

or t

• OPTIMUM INTEGRATION CURRENT

= 1µA

I

INT

• FULL SCALE ANALOG INPUT VOLTAGE

(Typ) = 200mV or 2V

V

lNFS

• INTEGRATE RESISTOR

V

R

INT

---------------- -=

INFS

I

INT

• INTEGRATE CAPACITOR

t

()I

()

C

INT

INT

--------------------------------=

V

INT

• INTEGRATOR OUTPUT VOLTAGE SWING

t

()I

()

V

•V

INT

INT

INT

--------------------------------=

C

INT

MAXIMUM SWING:

(V- + 0.5V) < V

> 50kΩ

OSC

/4

)

OSC

lNT/t50Hz

INT

INT

INT

= Integer

< (V+ - 0.5V), V

(Typ) = 2V

INT

ICL7136, ICL7137

• DISPLAY COUNT

COUNT 1000

• CONVERSION CYCLE

= t

t

CYC

t

= t

CYC

when f

OSC

• COMMON MODE INPUT VOLTAGE

(V- + 1V) < V

• AUTO-ZERO CAPACITOR

0.01µF < C

• REFERENCE CAPACITOR

0.1µF < C

•V

COM

Biased between V+ and V-.

•V

• ICL7136 POWER SUPPLY: SINGLE 9V

• ICL7136 DISPLAY: LCD

• ICL7137 POWER SUPPLY: DUAL ±5.0V

• ICL7137 DISPLAY: LED

≅ V+ - 2.8V

COM

Regulation lost when V+ to V- < ≅6.8V.

If V

COM

the V

COM

V+ - V- = 9V

Digital supply is generated internally

V

TEST

Type: Direct drive with digital logic supply amplitude.

V+ = +5V to GND

V- = -5V to GND

Digital Logic and LED driver supply V+ to GND

Type: Non-Multiplexed Common Anode

V

IN

---------------

×=

V

REF

x 4000

CL0CK

x 16,000

OSC

= 48kHz; t

< (V+ - 0.5V)

lN

< 1µF

AZ

< 1µF

REF

CYC

= 333ms

is externally pulled down to (V + to V -)/2,

circuit will turn off.

≅ V+ - 4.5V

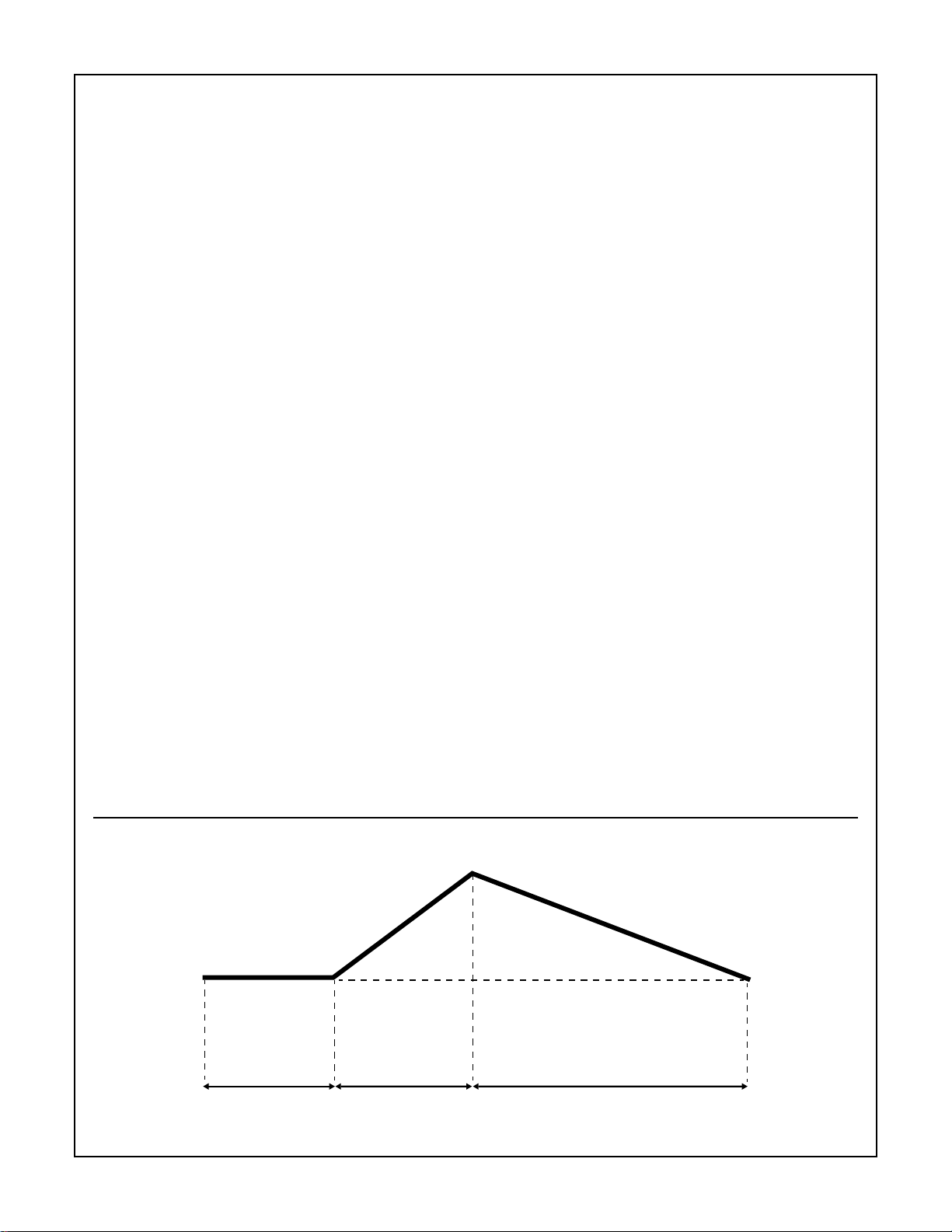

Typical Integrator Amplifier Output Waveform (INT Pin)

AUTO ZERO PHASE

(COUNTS)

2999 - 1000

SIGNAL INTEGRATE

PHASE FIXED

1000 COUNTS

TOTAL CONVERSION TIME = 4000 x t

4

DE-INTEGRATE PHASE

= 16,000 x t

CLOCK

0 - 1999 COUNTS

OSC

ICL7136, ICL7137

Pin Descriptions

PIN NUMBER

44 PIN

FLATPACK

1 8 V+ Supply Power Supply.

2 9 D1 Output Driver Pin for Segment “D” of the display units digit.

3 10 C1 Output Driver Pin for Segment “C” of the display units digit.

4 11 B1 Output Driver Pin for Segment “B” of the display units digit.

5 12 A1 Output Driver Pin for Segment “A” of the display units digit.

6 13 F1 Output Driver Pin for Segment “F” of the display units digit.

7 14 G1 Output Driver Pin for Segment “G” of the display units digit.

8 15 E1 Output Driver Pin for Segment “E” of the display units digit.

9 16 D2 Output Driver Pin for Segment “D” of the display tens digit.

10 17 C2 Output Driver Pin for Segment “C” of the display tens digit.

11 18 B2 Output Driver Pin for Segment “B” of the display tens digit.

12 19 A2 Output Driver Pin for Segment “A” of the display tens digit.

13 20 F2 Output Driver Pin for Segment “F” of the display tens digit.

14 21 E2 Output Driver Pin for Segment “E” of the display tens digit.

15 22 D3 Output Driver pin for segment “D” of the display hundreds digit.

16 23 B3 Output Driver pin for segment “B” of the display hundreds digit.

17 24 F3 Output Driver pin for segment “F” of the display hundreds digit.

18 25 E3 Output Driver pin for segment “E” of the display hundreds digit.

19 26 AB4 Output Driver pin for both “A” and “B” segments of the display thousands digit.

20 27 POL Output Driver pin for the negative sign of the display.

21 28 BP/GND Output Driver pin for the LCD backplane/Power Supply Ground.

22 29 G3 Output Driver pin for segment “G” of the display hundreds digit.

23 30 A3 Output Driver pin for segment “A” of the display hundreds digit.

24 31 C3 Output Driver pin for segment “C” of the display hundreds digit.

25 32 G2 Output Driver pin for segment “G” of the display tens digit.

26 34 V

27 35 INT Output Integrator amplifier output. To be connected to integrating capacitor.

28 36 BUFF Output Input buffer amplifier output. To be connected to integrating resistor.

29 37 A-Z Input Integrator amplifier input.To be connected to auto-zero capacitor.

30

31

32 40 COMMON Supply/

33

34

35

36

37 3 TEST Input Display test. Turns on all segments when tied to V+.

38

39

40

38

39

41

42

43

44

4

6

7

NAME FUNCTION DESCRIPTION40 PIN DIP

-

IN LO

IN HI

C

REF

C

REF

REF LO

REF HI

OSC3

OSC2

OSC1

Supply Negative power supply.

Input Differential inputs. To be connected to input voltage to be measured. LO and HI

designators are for reference and do not imply that LO should be connected to

lower potential, e.g., for negative inputs IN LO has a higher potential than IN HI.

Internal voltage reference output.

Output

-

+

Input Input pins for reference voltage to the device. REF HI should be positive

Output

Output

Input

Connection pins for reference capacitor.

reference to REF LO.

Device clock generator circuit connection pins.

5

ICL7136, ICL7137

Detailed Description

Analog Section

Figure 3 shows the Analog Section for the ICL7136 and

ICL7137. Each measurement cycle is divided into four

phases. They are (1) auto-zero (A-Z), (2) signal integrate

(INT) and (3) de-integrate (DE), (4) zero integrate (ZI).

Auto-Zero Phase

During auto-zero three things happen. First, input high and low

are disconnected from the pins and internally shorted to analog

COMMON. Second, the reference capacitor is charged to the

reference voltage. Third, a feedback loop is closed around the

system to charge the auto-zero capacitor C

for offset voltages in the buff er amplifier , integr ator , and comparator. Since the comparator is included in the loop , the A-Z accuracy is limited only by the noise of the system. In any case, the

offset referred to the input is less than 10µV.

Signal Integrate Phase

During signal integrate, the auto-zero loop is opened, the

internal short is removed, and the internal input high and low

are connected to the external pins. The converter then

integrates the differential voltage between IN HI and IN LO

for a fixed time. This differential voltage can be within a wide

common mode range: up to 1V from either supply. If, on the

other hand, the input signal has no return with respect to the

converter power supply, IN LO can be tied to analog

COMMON to establish the correct common mode voltage. At

the end of this phase, the polarity of the integrated signal is

determined.

De-Integrate Phase

The final phase is de-integrate, or reference integrate. Input

low is internally connected to analog COMMON and input

to compensate

AZ

high is connected across the previously charged reference

capacitor. Circuitry within the chip ensures that the capacitor

will be connected with the correct polarity to cause the

integrator output to return to zero. The time required for the

output to return to zero is proportional to the input signal.

Specifically the digital reading displayed is:

V

IN

DISPLAY READING = 1000

---------------

V

.

REF

Zero Integrator Phase

The final phase is zero integrator. First, input low is shorted to

analog COMMON. Second, the reference capacitor is charged

to the reference voltage. Finally, a feedback loop is closed

around the system to IN HI to cause the integrator output to

return to zero. Under normal conditions, this phase lasts for

between 11 to 140 clock pulses, but after a “heavy” overrange

conversion, it is e xtended to 740 clock pulses .

Differential Input

The input can accept differential voltages anywhere within the

common mode range of the input amplifier, or specifically from

0.5V below the positive supply to 1V abov e thenegative supply.

In this range, the system has a CMRR of 86dB typical. However, care must be exercised to assure the integrator output

does not saturate. A worst case condition would be a large positive common mode voltage with a near full scale negative differential input voltage. The negative input signal drives the

integrator positive when most of its swing has been used up by

the positive common mode voltage. For these critical applications the integrator output swing can be reduced to less than

the recommended 2V full scale swing with little loss of accuracy. The integrator output can swing to within 0.3V of either

supply without loss of linearity .

IN HI

COMMON

IN LO

STRAY STRAY

+

REF

A-Z

REF HI

34

C

V+

10µA

31

INT

32

INT

30

C

REF

REF LO

36

A-Z, A-Z,

ZI ZI

DE- DE+

A-Z AND DE(±)

AND ZI

FIGURE 3. ANALOG SECTION OF ICL7136 AND ICL7137

35

DE-DE+

33

R

INT

-

C

REF

-

+

INPUT

HIGH

N

26

V-

BUFFER

28 29 27

-

+

V+

1

2.8V

C

AZ

A-Z INT

INTEGRATOR

6.2V

INPUT

LOW

A-Z

ZI

-

+

COMPARATOR

C

INT

-

+

TO

DIGITAL

SECTION

6

Loading...

Loading...