Intersil Corporation ICL7135CPI Datasheet

TM

ICL7135

Data Sheet December 2000

41/2 Digit, BCD Output, A/D Converter

The Intersil ICL7135 precision A/D converter, with its

multiplexed BCD output and digit drivers, combines dualslope conversion reliability with ±1in 20,000 count accuracy

and is ideally suited for the visual display DVM/DPM market.

The 2.0000V full scale capability, auto-zero, and autopolarity are combined with true ratiometric operation, almost

ideal differential linearity and true differential input. All

necessary active devices are contained on a single CMOS

lC, with the exception of display drivers, reference, and a

clock.

The ICL7135 brings together an unprecedented combination

of high accuracy, versatility, and true economy. It features

auto-zero to less than 10µV, zero drift of less than 1µV/

input bias current of 10pA (Max), and rollover error of less

than one count. The versatility of multiplexed BCD outputs is

increased by the addition of several pins which allow it to

operate in more sophisticated systems. These include

STROBE, OVERRANGE, UNDERRANGE, RUN/HOLD and

BUSY lines, making it possible to interface the circuit to a

microprocessor or UART.

o

C,

File Number 3093.2

Features

• Accuracy Guaranteed to ±1 Count Over Entire ±20000

Counts (2.0000V Full Scale)

• Guaranteed Zero Reading for 0V Input

• 1pA Typical Input Leakage Current

• True Differential Input

• True Polarity at Zero Count for Precise Null Detection

• Single Reference Voltage Required

• Overrange and Underrange Signals Available for AutoRange Capability

• All Outputs TTL Compatible

• Blinking Outputs Gives Visual Indication of Overrange

• Six Auxiliary Inputs/Outputs are Available for Interfacing to

UARTs , Microprocessors , or Other Circuitry

• Multiplexed BCD Outputs

Ordering Information

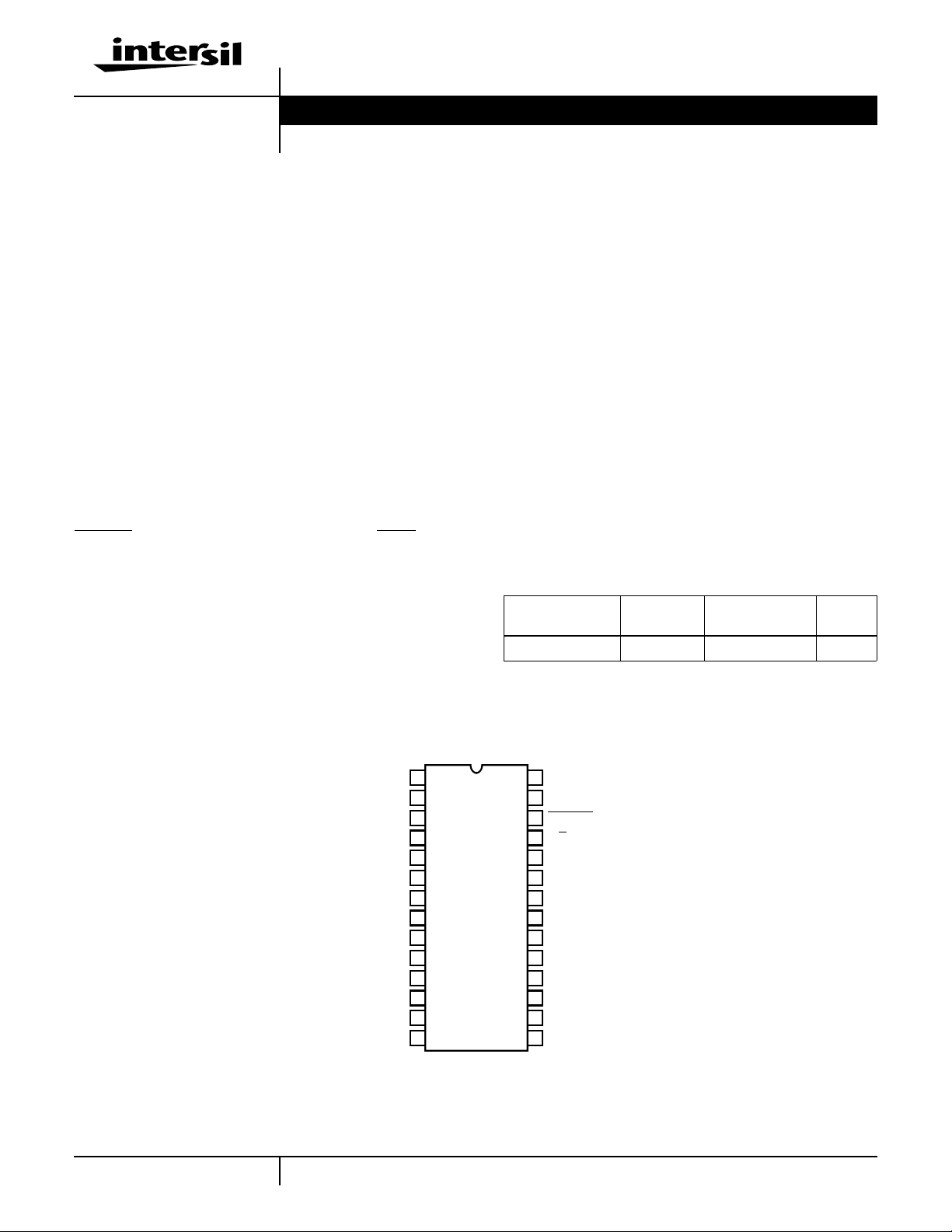

Pinout

REFERENCE

ANALOG COMMON

INT OUT

AZ IN

BUFF OUT

REF CAP -

REF CAP +

IN LO

IN HI

V+

(MSD) D5

(LSB) B1

B2

TEMP.

PART NUMBER

ICL7135CPI 0 to 70 28 Ld PDIP E28.6

ICL7135

(PDIP)

TOP VIEW

28

V-

1

2

3

4

5

6

7

8

9

10

11

12

13

14

UNDERRANGE

27

OVERRANGE

STROBE

26

H

25

R/

24

DIGITAL GND

23

POL

CLOCK IN

22

21

BUSY

20

(LSD) D1

D2

19

18

D3

17

D4

16

(MSB) B8

15

B4

RANGE (oC) PACKAGE

PKG.

NO.

1

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

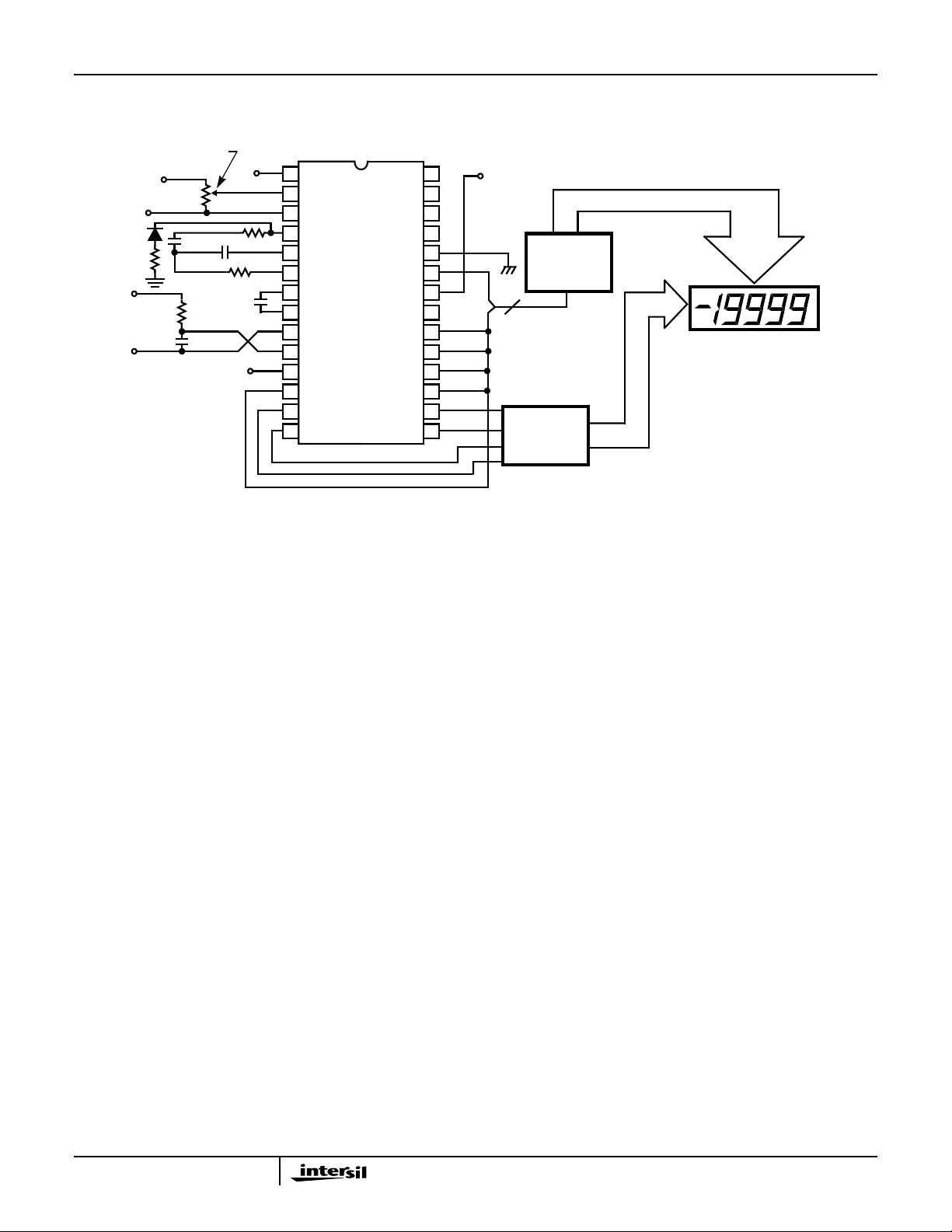

Typical Application Schematic

ICL7135

V

REF

ANALOG

GND

100kΩ

SIGNAL

INPUT

SET V

IN

REF

100kΩ

= 1.000V

0.47µF

1µF

100K

0.1µF

-5V

27Ω

100kΩ

1µF

+5V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

ICL7135

28

27

26

25

24

23

22

21

20

19

18

17

16

15

CLOCK IN

120kHz

0V

TRANSISTORS

6

SEVEN

DECODE

SEG.

ANODE

DRIVER

DISPLAY

2

ICL7135

Absolute Maximum Ratings Thermal Information

Supply Voltage V+ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +6V

V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -9V

Analog Input Voltage (Either Input) (Note 1) . . . . . . . . . . . . V+ to V-

Reference Input Voltage (Either Input). . . . . . . . . . . . . . . . . V+ to V-

Clock Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND to V+

Operating Conditions

Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 70oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Input voltages may exceed the supply voltages provided the input current is limited to +100µA.

2. θJA is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

Thermal Resistance (Typical, Note 2) . . . . . . . . . . . . . θJA (oC/W)

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

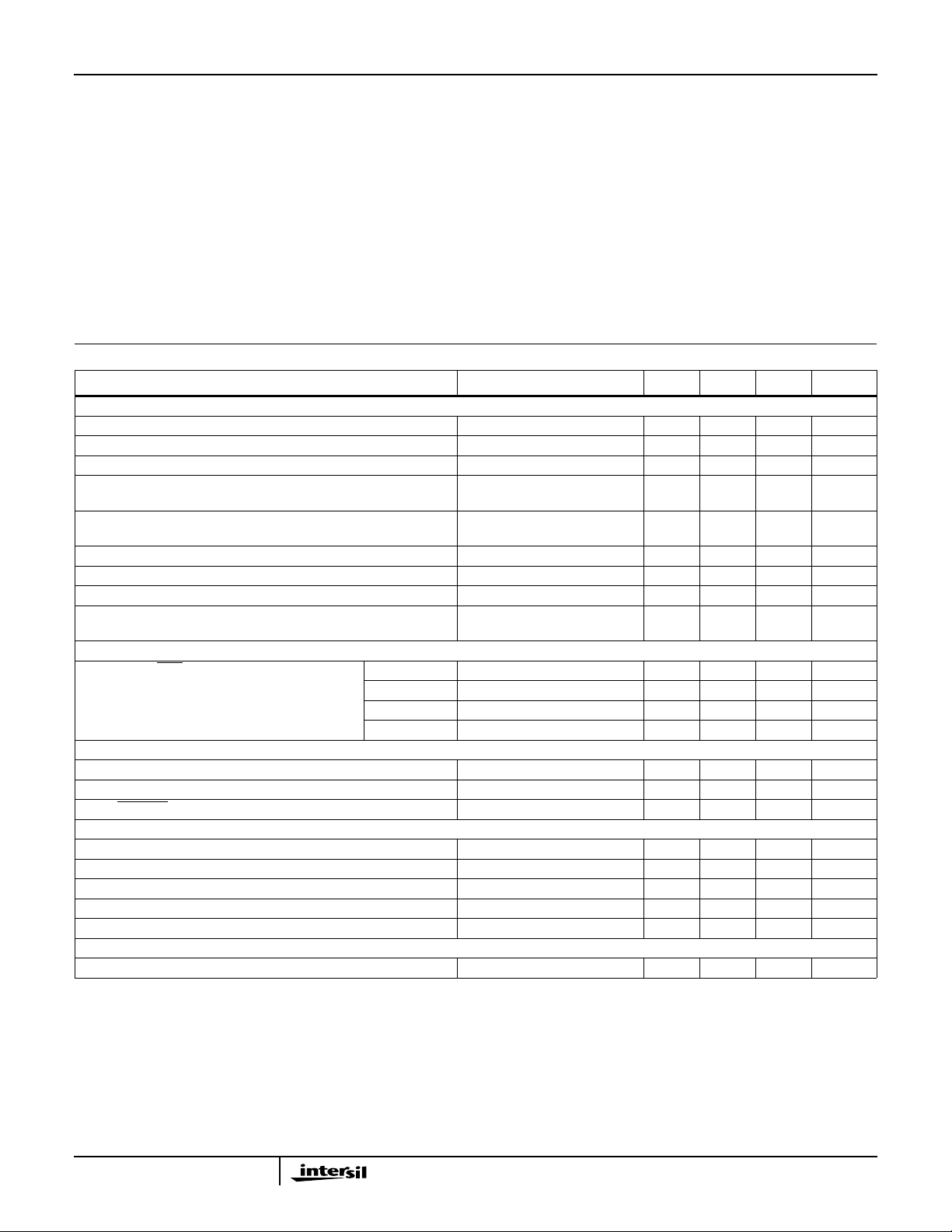

Electrical Specifications V+ = +5V, V- = -5V, T

PARAMETER TEST CONDITIONS

= 25oC, f

A

Set for 3 Readings/s, Unless Otherwise Specified

CLK

MIN TYP MAX UNITS

ANALOG (Notes 3, 4)

Zero Input Reading V

Ratiometric Error (Note 4) V

= 0V, V

lN

= V

lN

Linearity Over ± Full Scale (Error of Reading from Best Straight Line) -2V ≤ V

Differential Linearity (Difference Between Worse Case Step of

-2V ≤ V

= 1.000V -00000 +00000 +00000 Counts

REF

= 1.000V -3 0 +3 Counts

REF

≤ +2V - 0.5 1 LSB

IN

≤ +2V - 0.01 - LSB

IN

Adjacent Counts and Ideal Step)

Rollover Error (Difference in Reading for Equal Positive and

≡ +VlN≈ 2V - 0.5 1 LSB

-V

lN

Negative Voltage Near Full Scale)

Noise (Peak-to-Peak Value Not Exceeded 95% of Time), e

Input Leakage Current, I

ILK

N

Zero Reading Drift (Note 7) V

Scale Factor Temperature Coefficient, T

(Notes 5 and 7) VlN = +2V, 0oC to 70oC

C

VlN = 0V, Full scale = 2.000V - 15 - µV

VlN = 0V - 1 10 pA

= 0V, 0oC to 70oC - 0.5 2 µV/oC

lN

- 2 5 ppm/oC

Ext. Ref. 0ppm/oC

DIGITAL INPUTS

Clock In, Run/

Hold (See Figure 2) V

V

I

I

INH

INL

INL

INH

VIN = 0V - 0.02 0.1 mA

VIN = +5V - 0.1 10 µA

2.8 2.2 - V

- 1.6 0.8 V

DIGITAL OUTPUTS

All Outputs, V

B1, B2, B4, B8, D1, D2, D3, D4, D5, V

BUSY,

OL

OH

STROBE, OVERRANGE, UNDERRANGE, POLARITY, V

IOL = 1.6mA - 0.25 0.40 V

IOH = -1mA 2.4 4.2 - V

OHIOH

= -10µA 4.9 4.99 - V

SUPPLY

+5V Supply Range, V+ +4 +5 +6 V

-5V Supply Range, V- -3 -5 -8 V

+5V Supply Current, I+ fC = 0 - 1.1 3.0 mA

-5V Supply Current, I- f

Power Dissipation Capacitance, C

PD

= 0 - 0.8 3.0 mA

C

vs Clock Frequency - 40 - pF

CLOCK

Clock Frequency (Note 6) DC 2000 1200 kHz

NOTES:

1

3. Tested in 4

4. Tested with a low dielectric absorption integrating capacitor, the 27Ω INT OUT resistor shorted, and R

/2 digit (20.000 count) circuit shown in Figure 3. (Clock frequency 120kHz.)

= 0. See Component Value Selection

lNT

Discussion.

5. The temperature range can be extended to 70oC and beyond as long as the auto-zero and reference capacitors are increased to absorb the

higher leakage of the ICL7135.

6. This specification relates to the clock frequency range over which the lCL7135 will correctly perform its various functions See “Max Clock

Frequency” section for limitations on the clock frequency range in a system.

7. Parameter guaranteed by design or characterization. Not production tested.

3

ICL7135

V

REF

100kΩ

ANALOG

GND

SIGNAL

INPUT

IN

100kΩ

REF

0.47µF

1µF

0.1µF

= 1.000V

-5V

27Ω

100kΩ

1µF

+5V

V-

1

REF

2

3

ANALOG GND

INT OUT

4

A-Z IN

5

BUF OUT

6

REF CAP 1

7

REF CAP 2

8

IN LO-

9

IN HI+

10

V+

11

MSD D5

12

LSB B1

13

B2

14

ICL7135

UNDERRANGE

OVERRANGE

STROBE

RUN/

HOLD

DIGITAL GND

POLARITY

CLOCK IN

BUSY

LSD DI

MSB B8

D2

D3

D4

B4

28

27

26

25

24

0V

23

CLOCK

22

IN

120kHz

21

20

19

18

17

16

15

PAD

SET V

100K

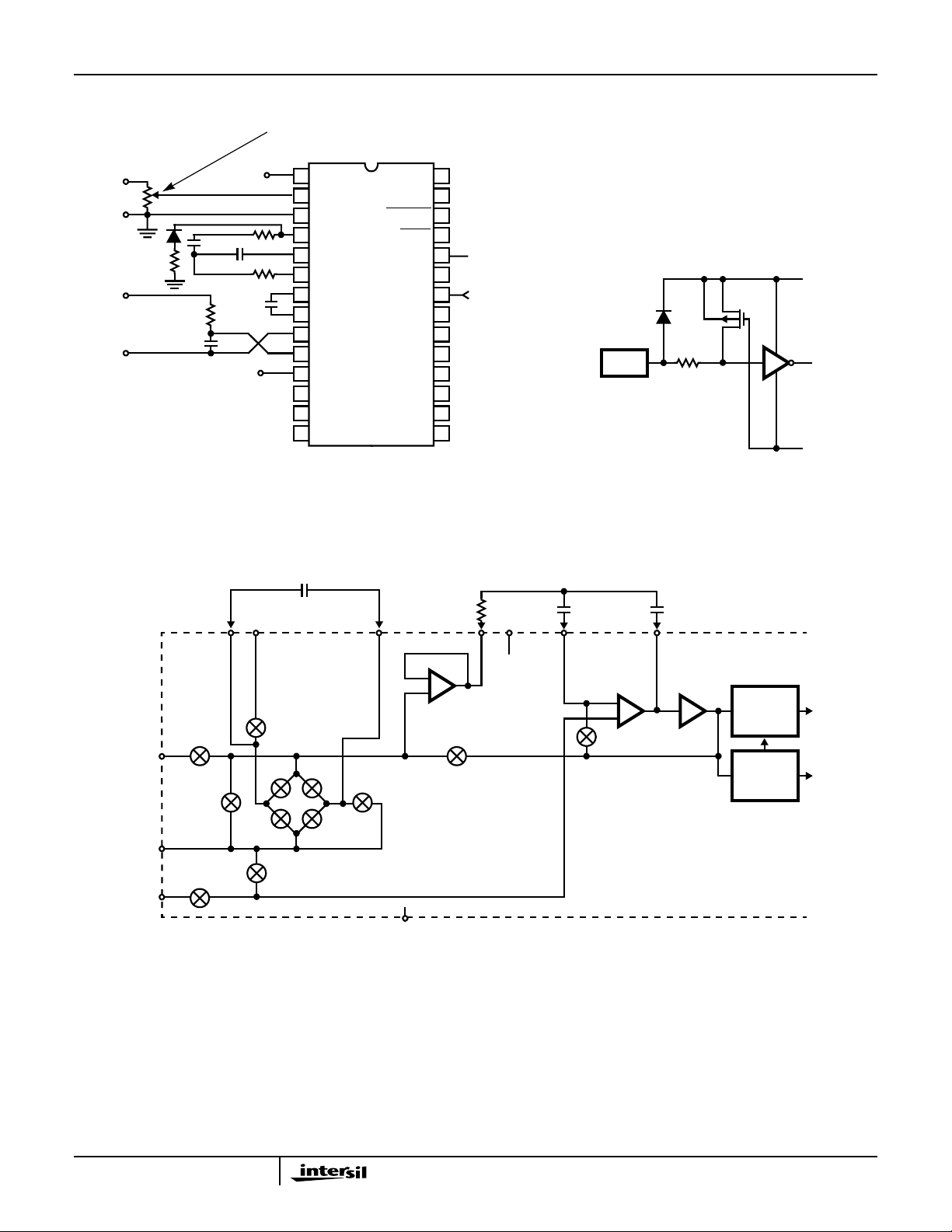

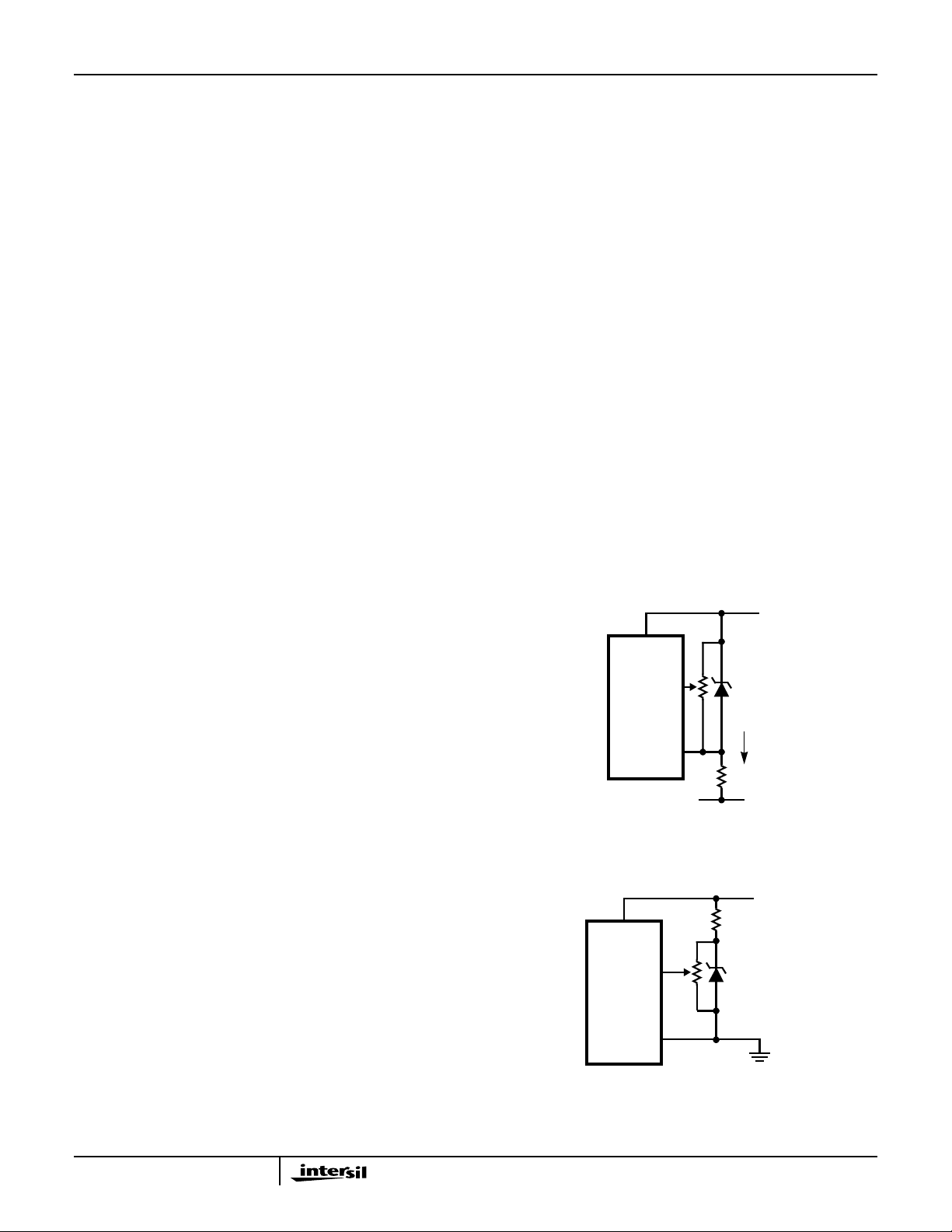

FIGURE 1. ICL7135 TEST CIRCUIT FIGURE 2. ICL7135 DIGITAL LOGIC INPUT

+

V

DIG GND

IN HI

ANALOG

COMMON

IN LO

C

REF

C

REF+

10

INT

AZ

3

INT

9

REF HI

2

87

AZ

DE(-) DE(+)

DE(+) DE(-)

A/Z, DE(±), ZI

A/Z

C

REF

-

V

INPUT

HIGH

1

R

INT

BUFFER

-

+

ZI

C

AZ

+

V

AUTO

ZERO

INTEGRAT OR

AZ

COMP ARATOR

INPUT

LOW

C

INT

INT

45611

-

+

+

ZEROCROSSING

DETECTOR

POLARITY

F/F

FIGURE 3. ANALOG SECTION OF ICL7135

4

ICL7135

Detailed Description

Analog Section

Figure 3 shows the Block Diagram of the Analog Section for

the ICL7135. Each measurement cycle is divided into four

phases. They are (1) auto-zero (AZ), (2) signal-integrate

(INT), (3) de-integrate (DE) and (4) zero-integrator (Zl).

Auto-Zero Phase

During auto-zero, three things happen. First, inputhigh and low

are disconnected from thepins and internally shorted to analog

COMMON. Second, the reference capacitor is charged to the

reference voltage. Third, a feedback loop is closed around the

system to charge the auto-zero capacitor C

for offset voltages in the b uff er amplifier, integrator , and

comparator. Since the comparator is included in the loop, the

AZ accuracy is limited only by the noise of the system. In any

case, the offset referred to the input is less than 10µV.

Signal Integrate Phase

During signal integrate, the auto-zero loop is opened, the

internal short is removed, and the internal input high and low

are connected to the external pins. The converter then

integratesthe differential voltage between IN HIand IN LO fora

fixed time. This diff erential v oltage can be within a wide

common mode range; within one volt of either supply .If, on the

other hand, the input signal has no return with respect to the

converter power supply,IN LO can be tied to analog COMMON

to establish the correct common-mode voltage. At the end of

this phase, the polarity of the integrated signal is latched into

the polarity F/F.

De-Integrate Phase

The third phase is de-integrate or reference integrate. Input

low is internally connected to analog COMMON and input

high is connected across the previously charged reference

capacitor. Circuitry within the chip ensures that the capacitor

will be connected with the correct polarity to cause the integrator output to return to zero. The time required for the output to return to zero is proportional to the input signal.

Specifically the digital reading displayed is:

V

IN

---------------

OUTPUT COUNT 10,000

=

V

.

REF

Zero Integrator Phase

The final phase is zero integrator. First, input low is shorted

to analog COMMON. Second, a feedback loop is closed

around the system to input high to cause the integrator

output to return to zero. Under normal condition, this phase

lasts from 100 to 200 clock pulses, but after an overrange

conversion, it is extended to 6200 clock pulses.

to compensate

AZ

Howev er, since the integrator also swings with the common

mode voltage, care must be exercisedto assure theintegrator

output does not saturate. A worst case condition would be a

large positive common-mode voltage with a near full scale

negative differential input v oltage. The negative input signal

drives the integrator positive when most of its swing has been

used up by the positive common mode voltage. For these

critical applications the integrator swing can be reduced to

less than the recommended 4V full scale swing with some

loss of accuracy. The integrator output can swing within 0.3V

of either supply without loss of linearity.

Analog COMMON

Analog COMMON is used as the input low return during autozero and de-integrate. If IN LO is diff erent from analog

COMMON, a common mode voltage exists in the system and

is taken care of by the excellent CMRR of the converter.

Howev er, in most applications IN LO will be set at a fixed

known voltage (power supply common for instance). In this

application, analog COMMON should be tied to the same

point, thus removing the common mode voltage from the

converter. The reference voltage is referenced to analog

COMMON.

Reference

The reference input must be generated as a positive voltage

with respect to COMMON, as shown in Figure 4.

V+

6.8V

ZENER

V-

V+

6.8kΩ

ICL8069

1.2V

REFERENCE

I

Z

ICL7135

COMMON

V+

REF HI

ICL7135

REF HI

FIGURE 4A.

20kΩ

Differential Input

The input can accept differentialvoltages anywhere within the

common mode range of the input amplifier; or specifically

from 0.5V below the positive supply to 1V abov e the negative

supply. In this range the system has a CMRR of 86dB typical.

5

COMMON

FIGURE 4B.

FIGURE 4. USING AN EXTERNAL REFERENCE

Loading...

Loading...