HI5960

Data Sheet November 1999

14-Bit, 125+MSPS, CommLinkTMHigh

Speed D/A Converter

The HI5960 is a 14-bit, 125+MSPS (Mega Samples Per

Second), high speed, low power, D/A converter which is

implemented in an advanced CMOS process. Operating

from a single +3V to +5V supply, the converter provides

20mA of full scale output current and includes edgetriggered CMOS input data latches. Low glitch energy and

excellentfrequency domain performance are achieved using

a segmented current source architecture.

This devicecomplements the CommLink HI5x60 and HI5x28

family of high speed converters, which includes 8, 10, 12,

and 14-bit devices.

Ordering Information

TEMP.

PART

NUMBER

HI5960IB -40 to 85 28 Ld SOIC M28.3 125MHz

HI5960IA † -40 to 85 28 Ld TSSOP M28.173A 125MHz

HI5960SOICEVAL1 25 Evaluation Platform 125MHz

RANGE

(oC) PACKAGE PKG. NO.

CLOCK

SPEED

† TSSOP Samples Available November 1999.

Pinout

HI5960

TOP VIEW

File Number 4655.3

Features

• Throughput Rate . . . . . . . . . . . . . . . . . . . . . . .125+MSPS

• Low Power . . . 175mW at 5V, 32mW at 3V (at 100MSPS)

• Adjustable Full Scale Output Current. . . . . 2mA to 20mA

• Internal 1.2V Bandgap Voltage Reference

• Single Power Supply from +5V to +3V

• Power Down Mode

• CMOS Compatible Inputs

• Excellent Spurious Free Dynamic Range

(77dBc, f

= 50MSPS, f

S

= 2.51MHz)

OUT

• Excellent Multitone Intermodulation Distortion

Applications

• Cellular Basestations

• WLL, Basestation and Subscriber Units

• Medical/Test Instrumentation

• Wireless Communications Systems

• Direct Digital Frequency Synthesis

• High Resolution Imaging Systems

• Arbitrary Waveform Generators

D13 (MSB)

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0 (LSB)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1

CLK

28

27

DV

DD

26

DCOM

25

ACOM

24

AV

DD

23

COMP2

22

IOUTA

21

IOUTB

20

ACOM

19

COMP1

18

FSADJ

17

REFIO

16

REFLO

15

SLEEP

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

CommLink™ is a trademark of Intersil Corporation.

| Copyright © Intersil Corporation 1999

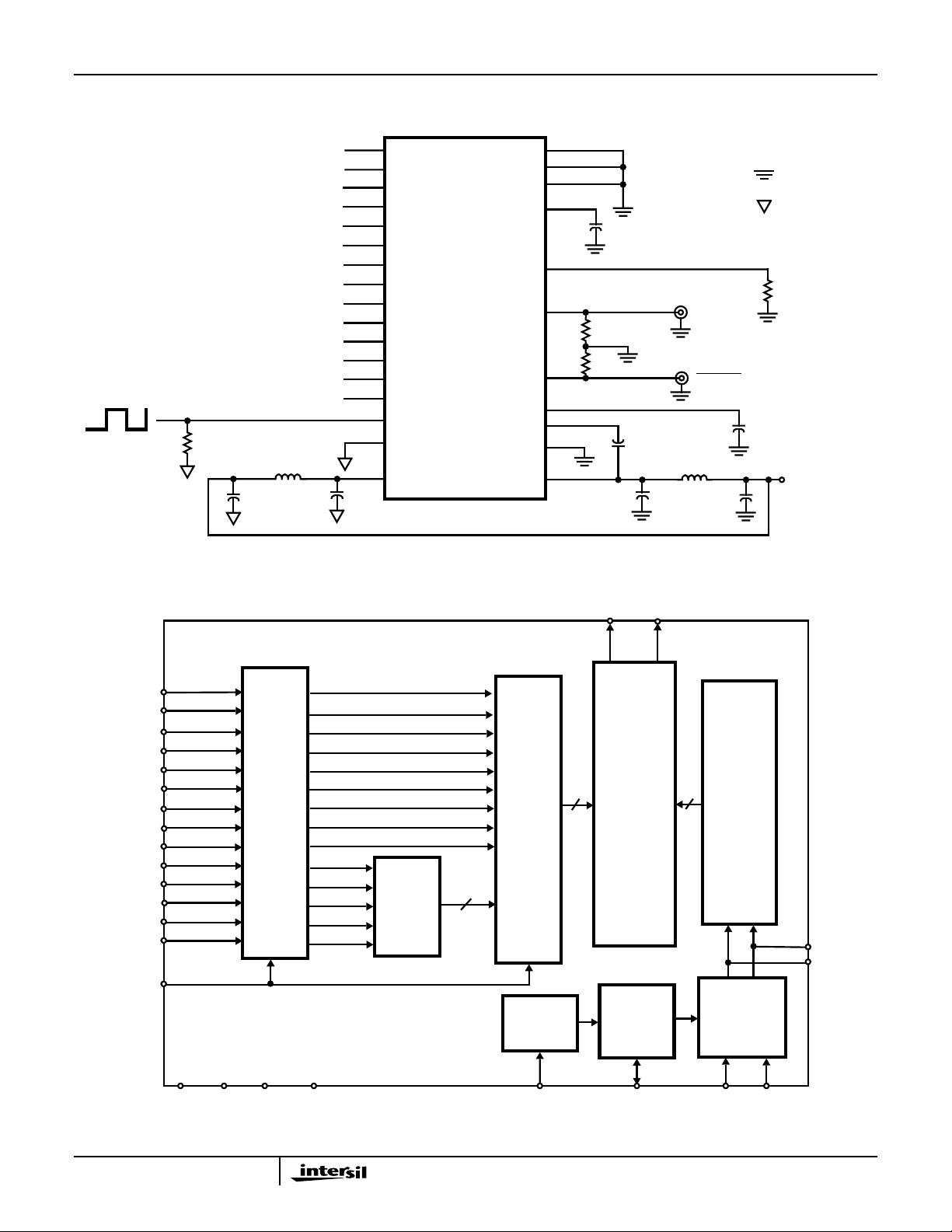

Typical Applications Circuit

50Ω

BEAD

+

10µF

10µH

0.1µF

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

D13 (1)

D12 (2)

D11 (3)

D10 (4)

D9 (5)

D8 (6)

D7 (7)

D6 (8)

D5 (9)

D4 (10)

D3 (11)

D2 (12)

D1 (13)

D0 (LSB) (14)

CLK (28)

DCOM (26)

(27)

DV

DD

HI5960

HI5960

(25) ACOM

(15) SLEEP

(16) REFLO

(17) REFIO

(18) FSADJ

(22) IOUTA

(21) IOUTB

(23) COMP2

(19) COMP1

(20) ACOM

(24) AV

DD

0.1µF

50Ω

50Ω

0.1µF

0.1µF

D/A OUT

D/A OUT

0.1µF

FERRITE

BEAD

10µH

10µF

R

SET

+

ACOM

DCOM

1.91kΩ

+5V OR +3V (VDD)

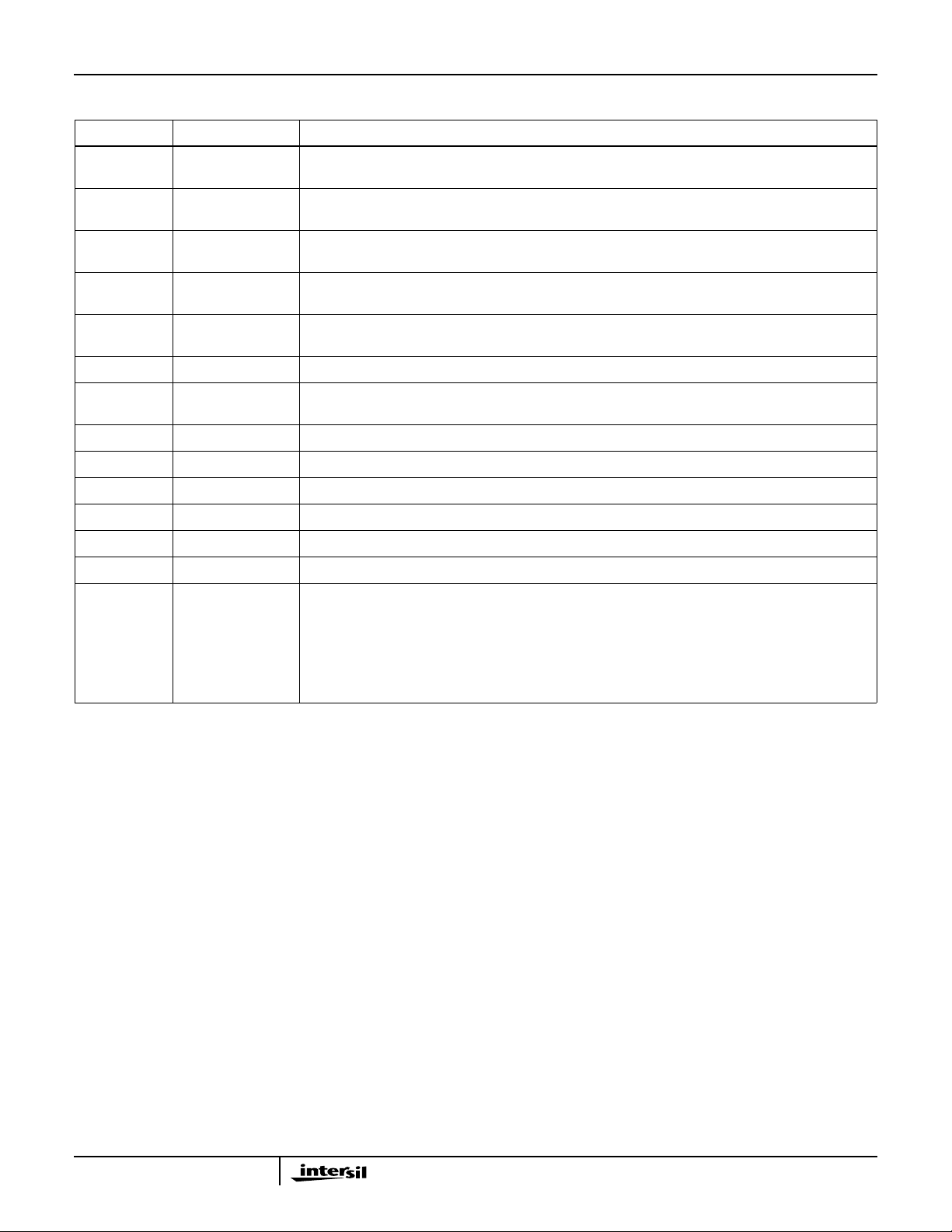

Functional Block Diagram

(LSB) D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

(MSB) D13

CLK

LATCH

UPPER

5-BIT

DECODER

31

LATCH

INT/EXT

REFERENCE

SELECT

IOUTA IOUTB

SWITCH

40

MATRIX

INT/EXT

VOLTAGE

REFERENCE

CASCODE

CURRENT

SOURCE

40

SEGMENTS

GENERATION

9 LSBs

31 MSB

BIAS

+

COMP2

COMP1

AVDDACOM DVDDDCOM

2

REFLO

REFIO

FSADJ

SLEEP

HI5960

Pin Descriptions

PIN NO. PIN NAME DESCRIPTION

1-14 D13 (MSB) Through

D0 (LSB)

15 SLEEP ControlPinfor Power-Down mode.SleepMode isactivehigh; Connect togroundfor Normal Mode.Sleep

16 REFLO Connect to analog ground to enable internal 1.2V reference or connect to AVDD to disable internal

17 REFIO Reference voltage input if internal reference is disabled. Ref erence v oltage output if internal ref erence is

18 FSADJ Full Scale Current Adjust. Use a resistor to ground to adjust full scale output current. Full Scale Output

19 COMP1 For use in reducing bandwidth/noise. Recommended: connect 0.1µF to AVDD.

21 IOUTB The complimentary current output of the device. Full scale output current is achieved when all input bits

22 IOUTA Current output of the device. Full scale output current is achieved when all input bits are set to binary 1.

23 COMP2 Connect 0.1µF capacitor to ACOM.

24 AV

20, 25 ACOM Connect to Analog Ground.

26 DCOM Connect to Digital Ground.

27 DV

28 CLK Clock Input. Input data to the DAC passes through the “master” latches when the clock is low and is

DD

DD

Digital Data Bit 13, (Most Significant Bit) through Digital Data Bit 0, (Least Significant Bit).

pin has internal 20µA active pulldown current.

reference.

enabled. Use 0.1µF cap to ground when internal reference is enabled.

Current = 32 x V

are set to binary 0.

Analog Supply (+3V to +5V).

Digital Supply (+3V to +5V).

latched into the “master” latches when the clock is high. Data presented to the “slave” latch passes

through when the clock is logic high and is latched into the “slave” latches when the clock is logic low.

Adequate setup timemustbeallowedfortheMSBs to pass through the thermometer decoder before the

clock goes high. This master-slave arrangement comprises an edge-triggered flip-flop, with the DAC

beingupdatedonthe rising clockedge.Itis recommended thattheclockedge be skewedsuchthatsetup

time is larger than the hold time.

FSADJ/RSET

.

3

HI5960

Absolute Maximum Ratings Thermal Information

Digital Supply Voltage DVDD to DCOM . . . . . . . . . . . . . . . . . . +5.5V

Analog Supply Voltage AVDD to ACOM. . . . . . . . . . . . . . . . . . +5.5V

Grounds, ACOM TO DCOM. . . . . . . . . . . . . . . . . . . . -0.3V to +0.3V

Digital Input Voltages (D9-D0, CLK, SLEEP). . . . . . . . DVDD+ 0.3V

Reference Input Voltage Range. . . . . . . . . . . . . . . . . . AVDD+ 0.3V

Analog Output Current (I

) . . . . . . . . . . . . . . . . . . . . . . . . . 24mA

OUT

Operating Conditions

Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA(oC/W)

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

TSSOP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC - Lead Tips Only)

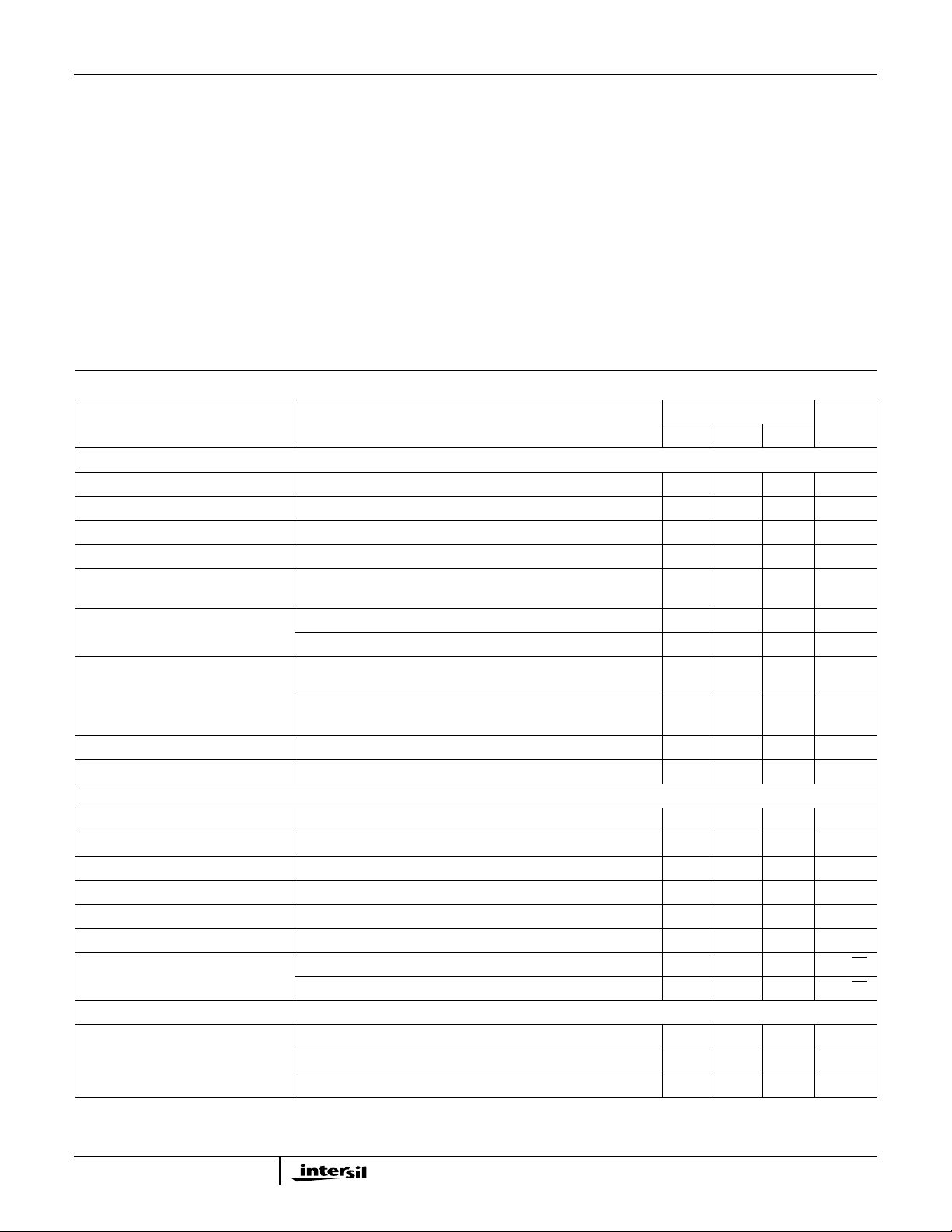

Electrical Specifications AV

PARAMETER TEST CONDITIONS

= DVDD = +5V, V

DD

= Internal 1.2V, IOUTFS = 20mA, TA = 25oC for All Typical Values

REF

T

= -40oC TO 85oC

A

UNITSMIN TYP MAX

SYSTEM PERFORMANCE

Resolution 14 - - Bits

Integral Linearity Error, INL “Best Fit” Straight Line (Note 8) -5 ±2.5 +5 LSB

Differential Linearity Error, DNL (Note 8) -3 ±1.5 +3 LSB

Offset Error, I

OS

(Note 8) -0.025 +0.025 % FSR

Offset Drift Coefficient (Note 8) - 0.1 - ppm

FSR/oC

Full Scale Gain Error, FSE With External Reference (Notes 2, 8) -10 ±2 +10 % FSR

With Internal Reference (Notes 2, 8) -10 ±1 +10 % FSR

Full Scale Gain Drift With External Reference (Note 8) - ±50 - ppm

FSR/oC

With Internal Reference (Note 8) - ±100 - ppm

FSR/oC

Full Scale Output Current, I

FS

2 - 20 mA

Output Voltage Compliance Range (Note 3, 8) -0.3 - 1.25 V

DYNAMIC CHARACTERISTICS

Maximum Clock Rate, f

Output Settling Time, (t

CLK

) ±0.05% (±8 LSB) (Note 8) - 35 - ns

SETT

(Note 3) 125 - - MHz

Singlet Glitch Area (Peak Glitch) RL = 25Ω (Note 8) - 5 - pV•s

Output Rise Time Full Scale Step - 2.5 - ns

Output Fall Time Full Scale Step - 2.5 - ns

Output Capacitance -10- pF

Output Noise IOUTFS = 20mA - 50 - pA/√Hz

IOUTFS = 2mA - 30 - pA/√Hz

AC CHARACTERISTICS

+5V Power Supply

Spurious Free Dynamic Range,

SFDR Within a Window

f

= 100MSPS, f

CLK

f

= 100MSPS, f

CLK

f

= 50MSPS, f

CLK

= 20.2MHz, 30MHz Span (Notes 4, 8) - 77 - dBc

OUT

= 5.04MHz, 8MHz Span (Notes 4, 8) - 97 - dBc

OUT

= 5.02MHz, 8MHz Span (Notes 4, 8) - 97 - dBc

OUT

4

Loading...

Loading...