Intersil Corporation HI5800 Datasheet

HI5800

Data Sheet June 1999

12-Bit, 3MSPS, Sampling A/D Converter

The HI5800 is a monolithic, 12-bit, sampling Analog-toDigital Converter fabricated in the HBC10 BiCMOS process.

It is a complete subsystem containing a sample and hold

amplifier, voltage reference, two-step subranging A/D, error

correction, control logic,andtiming generator. The HI5800 is

designed forhigh speed applications where wide bandwidth,

accuracy and low distortion are essential.

Ordering Information

TEMP.

PART

NUMBER LINEARITY

HI5800BID ±1 LSB -40 to 85 40 Ld SBDIP D40.6

HI5800JCD

HI5800KCD

±2 LSB

±1 LSB

HI5800-EV 25 Evaluation Board

RANGE

(oC) PACKAGE

PKG.

NO.

0 to 70 40 Ld SBDIP D40.6

File Number 2938.10

Features

• Throughput Rate . . . . . . . . . . . . . . . . . . . . . . . . . .3MSPS

• 12-Bit, No Missing Codes Over Temperature

• Integral Linearity Error . . . . . . . . . . . . . . . . . . . . . 1.0 LSB

• Buffered Sample and Hold Amplifier

• Precision Voltage Reference

• Input Signal Range. . . . . . . . . . . . . . . . . . . . . . . . . . ±2.5V

• 20MHz Input BW Allows Sampling Beyond Nyquist

• Zero Latency/No Pipeline Delay

Applications

• High Speed Data Acquisition Systems

• Medical Imaging

• Radar Signal Analysis

• Document and Film Scanners

• Vibration/Waveform Spectrum Analysis

• Digital Servo Control

Pinout

HI5800

(SBDIP)

TOP VIEW

REF

RO

RG

REF

ADJ

ADJ

AV

CC

OUT

V

AGND

ADJ+

ADJ-

AV

EE

AV

CC

AGND

AV

EE

A0

CS

OE

CONV

DV

EE

DGND

DV

CC

1

IN

2

3

4

5

6

IN

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

IRQ

OVF

AV

CC

D11 (MSB)

D10

D9

D8

DV

CC

DGND

AGND

AV

EE

D7

D6

D5

D4

D3

D2

D1

D0 (LSB)

AV

CC

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Copyright © Intersil Corporation 1999

Functional Block Diagram

REF

OUT

REF

IN

REFERENCE

HI5800

LATCH

7-BIT

D0 (LSB)

D1

D2

DIGITAL

OUTPUTS

ADJ+

ADJ-

V

IN

AV

S AND H

CCAVEEDVCCDVEE

Typical Application Schematic

+10µF

C23

0.1µF

C22

0.01µF

C1

V

IN

CONV

OE

A0

CS

7-BIT

FLASH

X32

AGND DGND

HI5800

(1)

REF_IN

REF_OUT

AGND

AGND

AGND

DGND

DGND

V

CONV

OE

A0

CS

(5)

(7)

(12)

(31)

(19)

(32)

(6)

IN

(37)

(17)

(16)

(14)

(15)

(22)

(MSB)D11

(18)

(33)

(20)

(LSB)

(23)

(24)

(25)

(26)

(27)

(28)

(29)

(34)

(35)

(36)

(40)

(39)

DV

DV

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

IRQ

OVF

EE

CC

7-BIT

LATCH

7-BIT

DAC

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

IRQ

OVF

ADJ

10µF

OUTPUT LATCHES

CONTROL

LOGIC

AND

TIMING

0.1µF

+

10µF

ERROR CORRECTION

RG

10µF, 0.1µF, AND 0.01µF CAPS ARE PLACED

AS CLOSE TO PART AS POSSIBLE

0.1µF

ADJ

BNC

GND

RO

+

D10

D11 (MSB)

OVF

IRQ

CS

CONV

OE

AO

AV

AV

CC

R9

10K

EE

R11

10K

R10

10K

2

RO_ADJ

RG_ADJ

(8)

ADJ+

(9)

ADJ-

(2)

(3)

(4)

AV

(11)

AV

(21)

(38)

(10)

AV

(13) (30)

CC

CC

EE

0.1µF

10µF

+

0.1µF 10µF

+

HI5800

Absolute Maximum Ratings Thermal Information

Supply Voltages

AVCC or DVCC to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5.5V

AVEE or DVEE to GND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . -5.5V

DGND to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.3V

Analog Input Pins

Reference Input REFIN . . . . . . . . . . . . . . . . . . . . . . . . . . . +2.75V

Signal Input VIN . . . . . . . . . . . . . . . . . . . . . . . . . . ±(REFIN +0.2V)

RO

, RG

ADJ

Digital I/O Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .GND to V

, ADJ+, ADJ-. . . . . . . . . . . . . . . . . . . . . VEE to V

ADJ

CC

CC

Operating Conditions

Temperature Range

HI5800JCD/KCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 70oC

HI5800BID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

SBDIP Package . . . . . . . . . . . . . . . . . . 40 15

Maximum Junction Temperature

SBDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering, 10s). . . . . . . . . . . . .300oC

Electrical Specifications AV

PARAMETER TEST CONDITIONS

SYSTEM PERFORMANCE

Resolution 12 - - 12 - - Bits

Integral Linearity Error, INL fS = 3MHz, fIN = 45Hz Ramp - 0.7 ±2-±0.5 ±1 LSB

Differential Linearity Error, DNL

(Guaranteed No Missing Codes)

Offset Error, V

(Adjustable to Zero)

Full Scale Error, FSE

(Adjustable to Zero)

DYNAMIC CHARACTERISTICS (Input Signal Level 0.5dB Below Full Scale)

Throughput Rate No Missing Codes 3.0 - - 3.0 - - MSPS

Signal to Noise Ratio (SNR) fS = 3MHz, fIN = 20kHz 66 69 - 68 71 - dB

RMS Signal

=

------------------------------RMS Noise

Signal to Noise Ratio (SINAD) f

--------------------------------------------------------------

=

RMS Noise + Distortion

Total Harmonic Distortion, THD f

Spurious Free Dynamic Range,

SFDR

Intermodulation Distortion, IMD fS = 3MHz, f1 = 49kHz,

Differential Gain fS = 1MHz - 0.9 - - 0.9 - %

Differential Phase fS = 1MHz - 0.05 - - 0.05 - Degrees

Aperture Delay, t

OS

RMS Signal

AD

= +5V, DVCC = +5V, AVEE = -5V, DVEE = -5V; Internal Reference Used,

CC

Unless Otherwise Specified

HI5800JCD HI5800KCD, HI5800BID

0oC TO 70oC

0oC TO 70oC

MIN TYP MAX MIN TYP MAX

fS = 3MHz, fIN = 45Hz Ramp - ±0.5 ±1-±0.3 ±1 LSB

(Note 8) JCD, KCD - ±2 ±15 - ±2 ±15 LSB

BID - - - - ±3 ±15 LSB

(Note 8) JCD, KCD - ±2 ±15 - ±2 ±10 LSB

BID - - - - ±3 ±15 LSB

fS = 3MHz, fIN = 1MHz 65 67 - 67 69 - dB

= 3MHz, fIN = 20kHz 66 68 - 68 71 - dB

S

fS = 3MHz, fIN = 1MHz 65 67 - 67 68 - dB

= 3MHz, fIN = 20kHz - -74 -70 - -85 -74 dBc

S

fS = 3MHz, fIN = 1MHz - -70 -68 - -77 -70 dBc

fS = 3MHz, fIN = 20kHz 71 76 - 76 86 - dBc

fS = 3MHz, fIN = 1MHz 68 72 - 71 77 - dBc

- -74 -66 - -79 -70 dBc

f2 = 50kHz (Note 3)

(Note 3) - 12 20 - 12 20 ns

-40oC TO 85oC

UNITS

3

HI5800

Electrical Specifications AV

= +5V, DVCC = +5V, AVEE = -5V, DVEE = -5V; Internal Reference Used,

CC

Unless Otherwise Specified (Continued)

HI5800JCD HI5800KCD, HI5800BID

0oC TO 70oC

PARAMETER TEST CONDITIONS

Aperture Jitter, t

AJ

0oC TO 70oC

MIN TYP MAX MIN TYP MAX

(Note 3) - 10 20 - 10 20 ps

-40oC TO 85oC

UNITS

ANALOG INPUT

Input Voltage Range - ±2.5 ±2.7 - ±2.5 ±2.7 V

Input Resistance 1 3 - 1 3 - MΩ

Input Capacitance - 5 - - 5 - pF

Input Current - ±1 ±10 - ±1 ±10 µA

Input Bandwidth - 20 - - 20 - MHz

INTERNAL VOLTAGE REFERENCE

Reference Output Voltage,

REF

OUT

(Loaded)

2.450 2.500 2.550 2.470 2.500 2.530 V

Reference Output Current (Note 5) 2 - - 2 - - mA

Reference Temperature

-20- -13-ppm/

Coefficient

REFERENCE INPUT

Reference Input Range - 2.5 2.6 - 2.5 2.6 V

Reference Input Resistance - 200 - - 200 - Ω

DIGITAL INPUTS

Input Logic High Voltage, V

Input Logic Low Voltage, V

Input Logic Current, I

IL

Digital Input Capacitance, C

IH

IL

IN

(Note 6) 2.0 - - 2.0 - - V

- - 0.8 - - 0.8 V

VIN = 0V, 5V - ±1 ±10 - ±1 ±10 µA

VIN = 0V - 5 - - 5 - pF

DIGITAL OUTPUTS

Output Logic High Voltage, V

Output Logic Low Voltage, V

Output Logic High Current, I

Output Logic Low Current, I

Output Three-State Leakage

Current, I

OZ

Digital Output Capacitance, C

OH

OL

OH

OL

OUT

I

= -160µA 2.4 4.3 - 2.4 4.3 - V

OUT

I

= 3.2mA - 0.22 0.4 - 0.22 0.4 V

OUT

-0.160 -6 - -0.160 -6 - mA

3.2 6 - 3.2 6 - mA

V

= 0V, 5V - ±1 ±10 - ±1 ±10 µA

OUT

-10- -10-pF

TIMING CHARACTERISTICS

Minimum CONV Pulse, t

CS to CONV Setup Time, t

CONV to CS Setup Time, t

Minimum OE Pulse, t

CS to OE Setup Time, t

OE to CS Setup Time, t

1

2

3

4

5

6

IRQ Delay from Start Convert, t

IRQ Pulse Width, t

8

(Notes 3, 4) 10 - - 10 - - ns

(Note 3) 10 - - 10 - - ns

(Note 3) 0 - - 0 - - ns

(Notes 3, 5) 15 - - 15 - - ns

(Note 3) 0 - - 0 - - ns

(Note 3) 0 - - 0 - - ns

(Note 3) 10 20 25 10 20 25 ns

7

JCD, KCD 190 200 230 190 200 230 ns

BID - - - 180 195 230 ns

Minimum Cycle Time for

Conversion, t

9

IRQ to Data Valid Delay, t

Minimum A0 Pulse, t

11

10

(Note 3) -5 0 +5 -5 0 +5 ns

(Notes 3, 5) 10 - - 10 - - ns

- 325 333 - 325 333 ns

o

C

4

HI5800

Electrical Specifications AV

= +5V, DVCC = +5V, AVEE = -5V, DVEE = -5V; Internal Reference Used,

CC

Unless Otherwise Specified (Continued)

HI5800JCD HI5800KCD, HI5800BID

0oC TO 70oC

PARAMETER TEST CONDITIONS

Data Access from OE Low, t

12

0oC TO 70oC

MIN TYP MAX MIN TYP MAX

(Note 3) 10 18 25 10 18 25 ns

-40oC TO 85oC

UNITS

LSB, Nibble Delay from A0 High, t13(Note 3) - 10 20 - 10 20 ns

MSB Delay from A0 Low, t

CS to Float Delay, t

Minimum CS Pulse, t

15

16

CS to Data Valid Delay, t

Output Fall 2 Time, t

Output Rise Time, t

f

r

14

17

(Note 3) - 14 20 - 14 20 ns

(Note 3) 10 18 25 10 18 25 ns

(Notes 3, 5) 15 - - 15 - - ns

(Note 3) 10 18 25 10 18 25 ns

(Note 3) - 5 20 - 5 20 ns

(Note 3) - 5 20 - 5 20 ns

POWER SUPPLY CHARACTERISTICS

IV

IV

IDV

IDV

CC

EE

CC

EE

- 170 220 - 170 220 mA

- 150 190 - 150 190 mA

- 24 40 - 24 40 mA

-25-25mA

Power Dissipation - 1.7 2.2 - 1.7 2.2 W

PSRR VCC, VEE±5% - 0.01 - - 0.01 - %/%

NOTES:

2. Dissipation rating assumes device is mounted with all leads soldered to printed circuit board.

3. Parameter guaranteed by design or characterization and not production tested.

4. Recommended pulse width for CONV is 60ns.

5. Recommended minimum pulse width is 25ns.

6. This is the additional current available from the REF

pin with the REF

OUT

pin driving the REFIN pin.

OUT

7. The A0 pin VIH at -40oC may exceed 2.0V by up to 0.4V at initial power up.

8. Excludes error due to internal reference temperature drift.

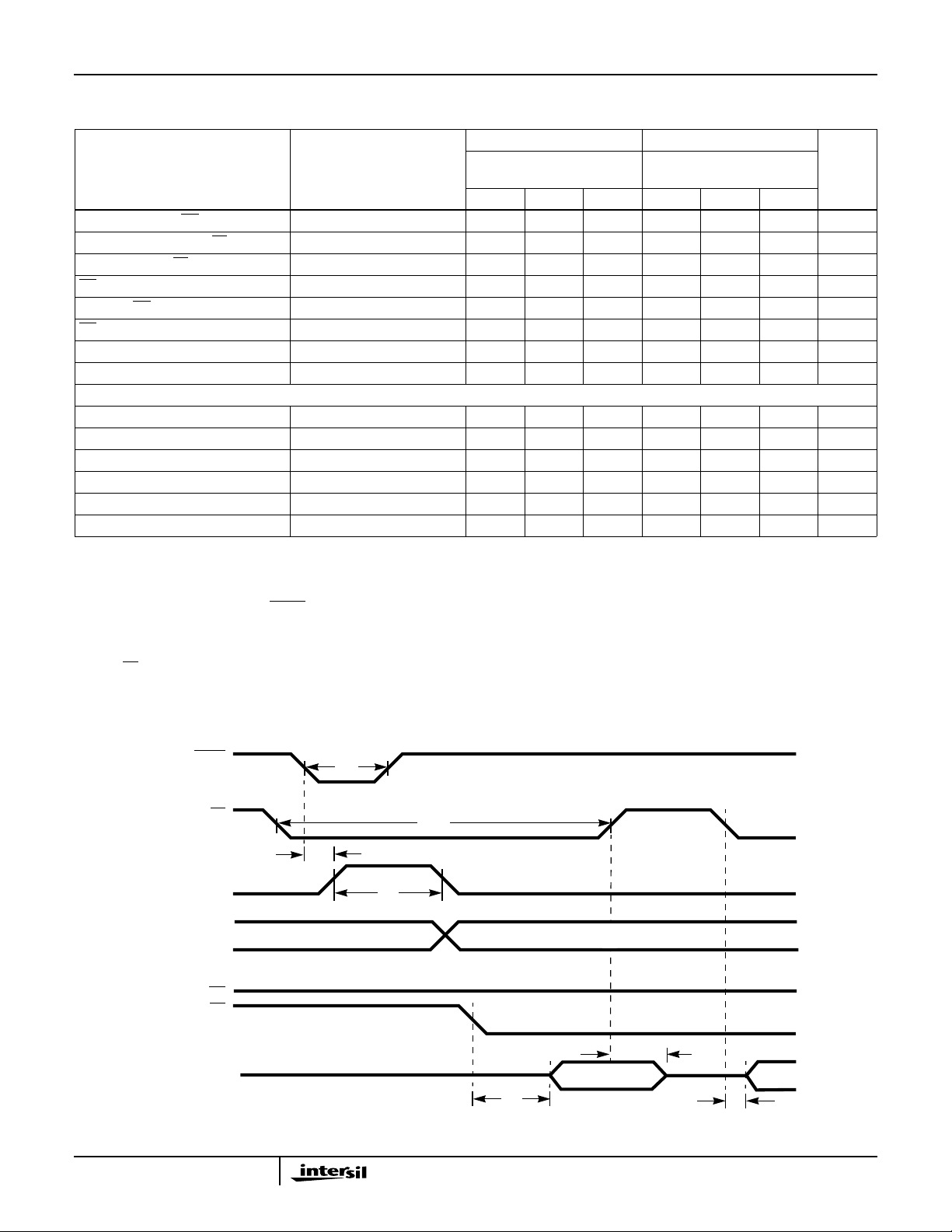

Timing Diagrams

CONV

CS

IRQ

DATA VALID

AO

OE

D0 - D11, OVF

ACQUIRE N

5

t

1

t

7

N CONVERSION

N - 1 DATA

t

16

t

8

t

12

FIGURE 1. SINGLE SHOT TIMING

N DATA

t

15

N DATA

t

17

Loading...

Loading...