TM

HI3300

Data Sheet March 2000 File Number 4822.1

3V 10-Bit, 20MSPS A/D Converter with

Internal Voltage Reference

The HI3300 is a monolithic, 10-bit analog-to-digital converter

fabricated in an advanced CMOS process. It is designed for

high speed applications where integration, bandwidth and

accuracy are essential. The HI3300 features a 2-step

parallel architecture to allow the system designer to realize

an increased level of system integration resulting in

decreased cost and power dissipation.

The HI3300 has excellent dynamic performance while

consuming less than40mWpowerat 20MSPS. The A/D only

requires a single +3.0V power supply.

Ordering Information

TEMP.

PART

NUMBER

RANGE

(oC) PACKAGE PKG. NO.

HI3300IN -40 to 85 48 Ld LQFP Q48.7x7-S 20

SAMPLING

RATE

(MSPS)

Features

• Sampling Rate . . . . . . . . . . . . . . . . . . . . . . . . . . .20MSPS

• Low Power at 20MSPS. . . . . . . . . . . . . . . . . . . . . . .40mW

• Power Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 3mW

• Wide Full Power Input Bandwidth. . . . . . . . . . . . . 100MHz

• On-Chip Sample and Hold Amplifiers

• Single Supply Voltage Operation . . . . . . . . . .+2.7V - 3.3V

Applications

• Wireless Local Loop

• PSK and QAM I&Q Demodulators

• Medical Imaging

• Wireless Communications Systems

• Battery Powered Instruments

Pinout

HI3300

48 LEAD LQFP

TOP VIEW

DD

SS

DV

DV

AV

SS

AV

DD

DD

Av

AT

CAL

AV

SS

AV

DD

TS

VIN

TSTR

DV

DV

DO

D1

D2

D3

D4

SS

DD

D5

D6

D7

D8

D9

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16

TO

TIN

SS

AV

RESET

Av

DD

TEST

LINV

MINV

Av

DD

CLK

OE

373839404142434445464748

36

35

34

33

32

31

30

29

28

27

26

25

2423222120191817

CE

BE

AV

DD

AV

SS

VRBS

VRB

VRBC

VRMC

VRTC

VRT

VRTS

AV

DD

AV

SS

1

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

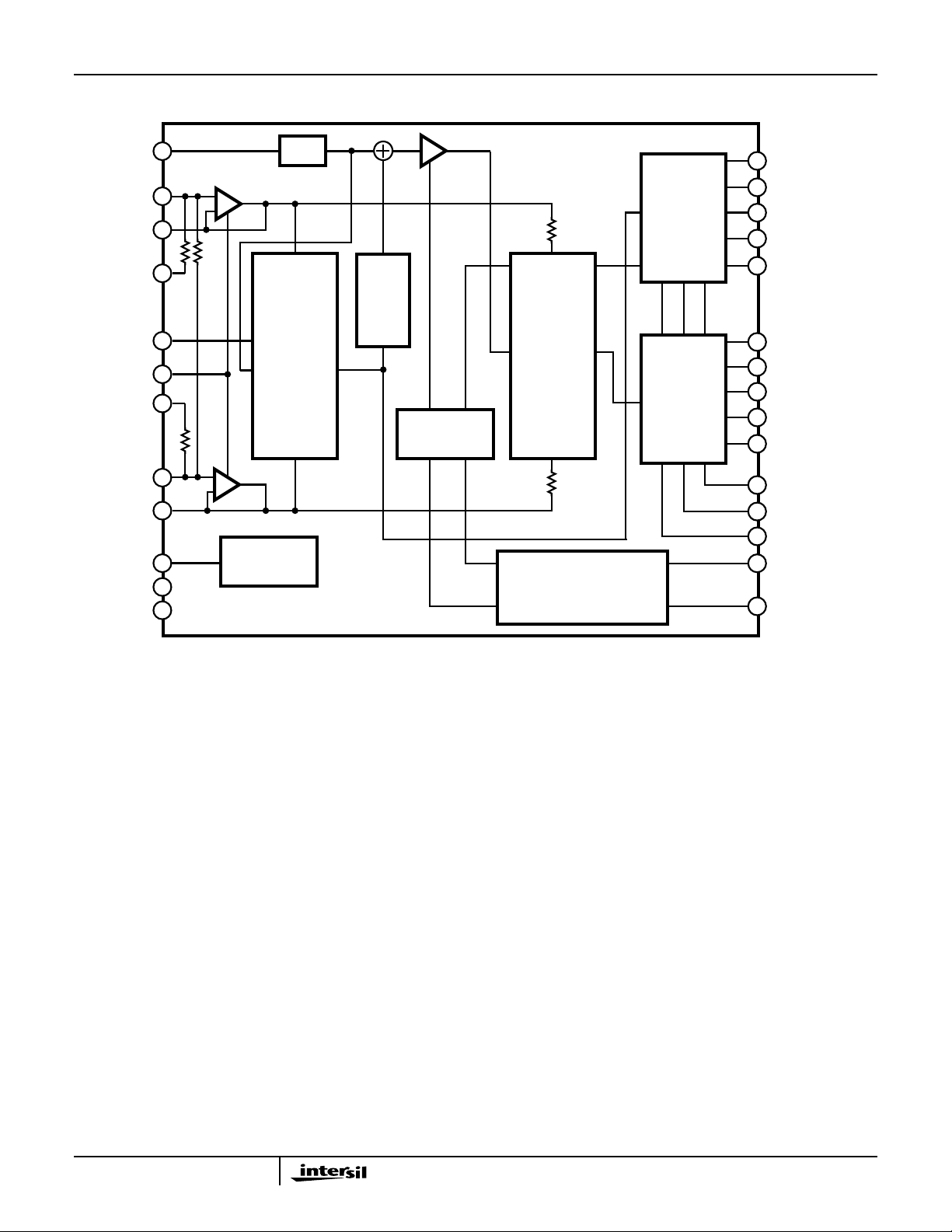

Block Diagram

38

VIN

28

VRT

29

VRTC

27

VRTS

HI3300

x 8

DAC

+

D9

-

COARSE

CORRECTION

AND

LATCH

12

11

D8

D7

10

9

D6

8

D5

S/H

AMP

+

-

VRMC

BE

VRBS

VRB

VRBC

CLK

OE

CE

30

36

33

32

31

22

23

24

+

-

COARSE

COMPARATE

AND

ENCODE

CALIBRATION

UNIT

TIMING

GEN

FIN3

FINE

COMPARATE

COMPARATE

AND

AND

ENCODE

ENCODE

AUTO

CALIBRATION PULSE

GENERATOR

FIND

LATCH

5

D4

4

D3

D2

3

D1

2

D0 (LSB)

1

MINV

20

LINV

19

TEST MODE

18

CAL

42

RESET

15

2

HI3300

Absolute Maximum Ratings Thermal Information

Supply Voltage (AVDD) . . . . . . . . . . . . . . . . . . . AVSS -0.5V to 4.5V

(DVDD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DVSS -0.5V to 4.5V

Reference Voltage (VRT, VRB). . . . . . . . AVDD +0.5V to AVSS -0.5V

Input Voltage (Analog) (VIN) . . . . . . . . . . . . . . AVDD +0.5V to -0.5V

Input Voltage (Digital) (VIH, VIL) . . . . . . AVDD +0.5V to AVSS -0.5V

Output Voltage (Digital) (VOH, VOL). . . . DVDD +0.5V to DVSS -0.5V

Operating Conditions

Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

Supply Voltage Range (AVDD, AVSS) . . . . . . . . . . . . 3.0V to ±0.3V

(DVDD, DVSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3.0V to ±0.3V

DVSS - AVSS . . . . . . . . . . . . . . . . . . . . . . . . . .0mV to 100mV

Reference Input Voltage (VRB). . . . . . . . . 0.3 AVDD to 0.5 AVDDV

(VRT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.6 AVDD to 0.8 AVDDV

Analog Input (VIN) . . . . . . . . . . . . . . . . . . . . . . . 0.9 Vp-p or More

Clock Pulse Width (t

Operating Ambient Temperature (T

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

PW1

), (t

) . . . . . . . . . . . . . . . . 25ns (Min)

PW0

) . . . . . . . . -40oC to 85oC

OPR

Thermal Resistance (Typical, Note 1) θJA (oC/W)

48 Ld LQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(Lead Tips Only)

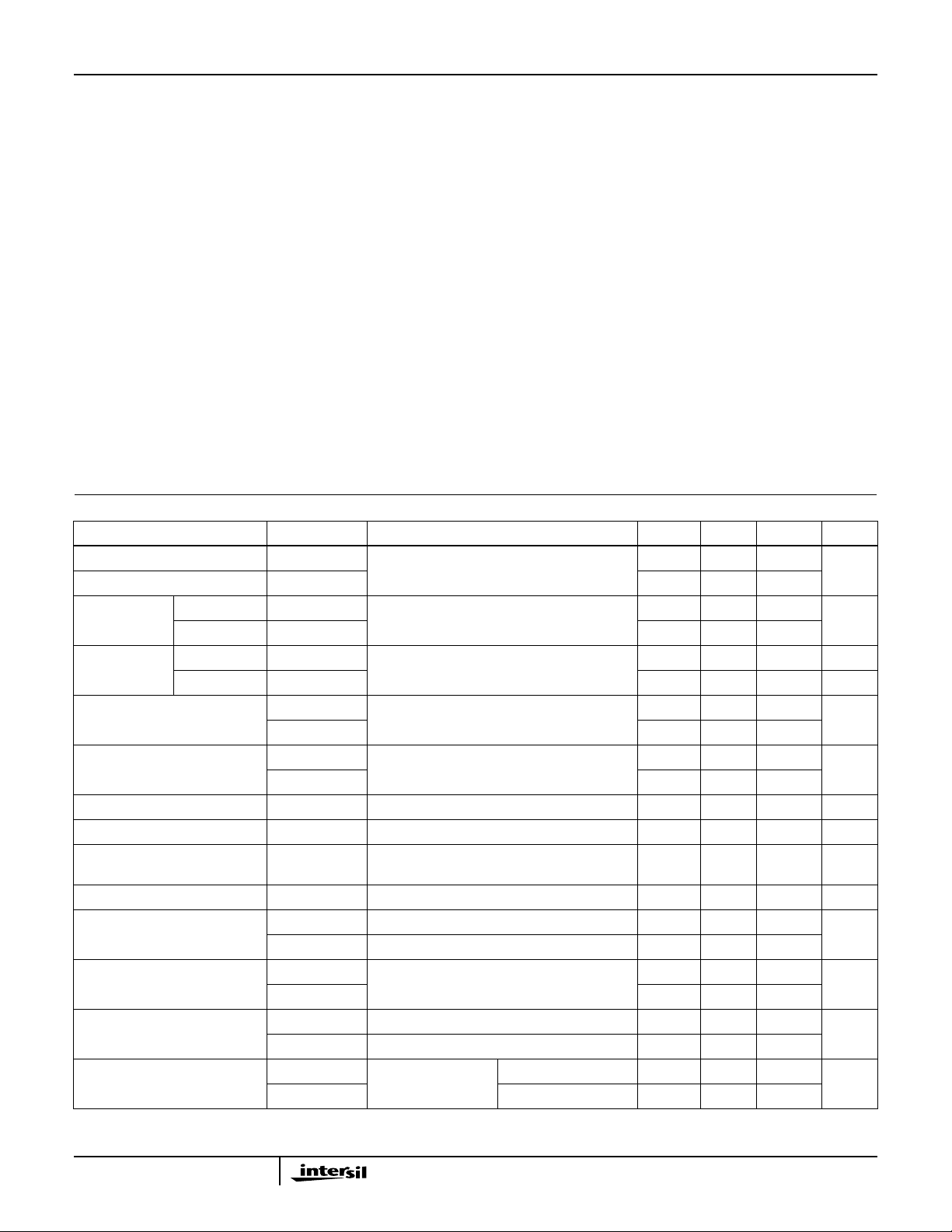

Electrical Specifications f

= 20MSPS, AVDD = 3V, DVDD = 3V, VRB = 1V, VRT = 2V, TA = 25oC

C

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT

Maximum Conversion Rate fC max f

= 1.0kHz Triangular Wave Input 20 - - MSPS

IN

Minimum Conversion Rate fC min - - 0.5

Supply Voltage Analog IA

Digital ID

Standby Current Analog IA

Digital ID

Reference Pin Current 1 I

Reference Pin Current 2 I

RT1

I

RB1

RT2

I

RB2

DD

DD

ST

ST

fIN = 1.0kHz Triangular Wave Input - 12 - mA

BE = High - 1.0 CE = AV

DD

VRTS, VRBS: Open Between VRT and V

BE = AVDD Between V

RTC

and V

RBC

RB

- 1.0 - mA

- 1.0 - µA

- 100 - µA

- -100 -

-2-mA

--2Analog Input Band BW -1dB - TBD - MHz

Analog Input Capacitance C

Reference Resistance Value 1 R

Reference Resistance Value 2 R

IN

REF1

REF2

Between V

and V

RBS

Between V

and VRT, VRT and VRB, V

RTS

and V

RTC

RBC

RB

-10-pF

- 10k - Ω

- 500 - Ω

Offset Voltage EOT EOT = Theoretical Value - Measured Value - TBD - mV

EOB EOB = Measured Value - Theoretical Value - TBD -

Digital Input Voltage V

Analog Input Current A

Digital Input Current I

IH

V

IL

IH

A

IL

IH

I

IL

A

= 2.7 to 3.3V 0.7 - - V

VDD

- - 0.2

VIN= 2V - 20 - µA

VIN = 1V - -20 AVDD = 3.3V VIH - AV

VIL = AV

DD

SS

--5µA

--5

3

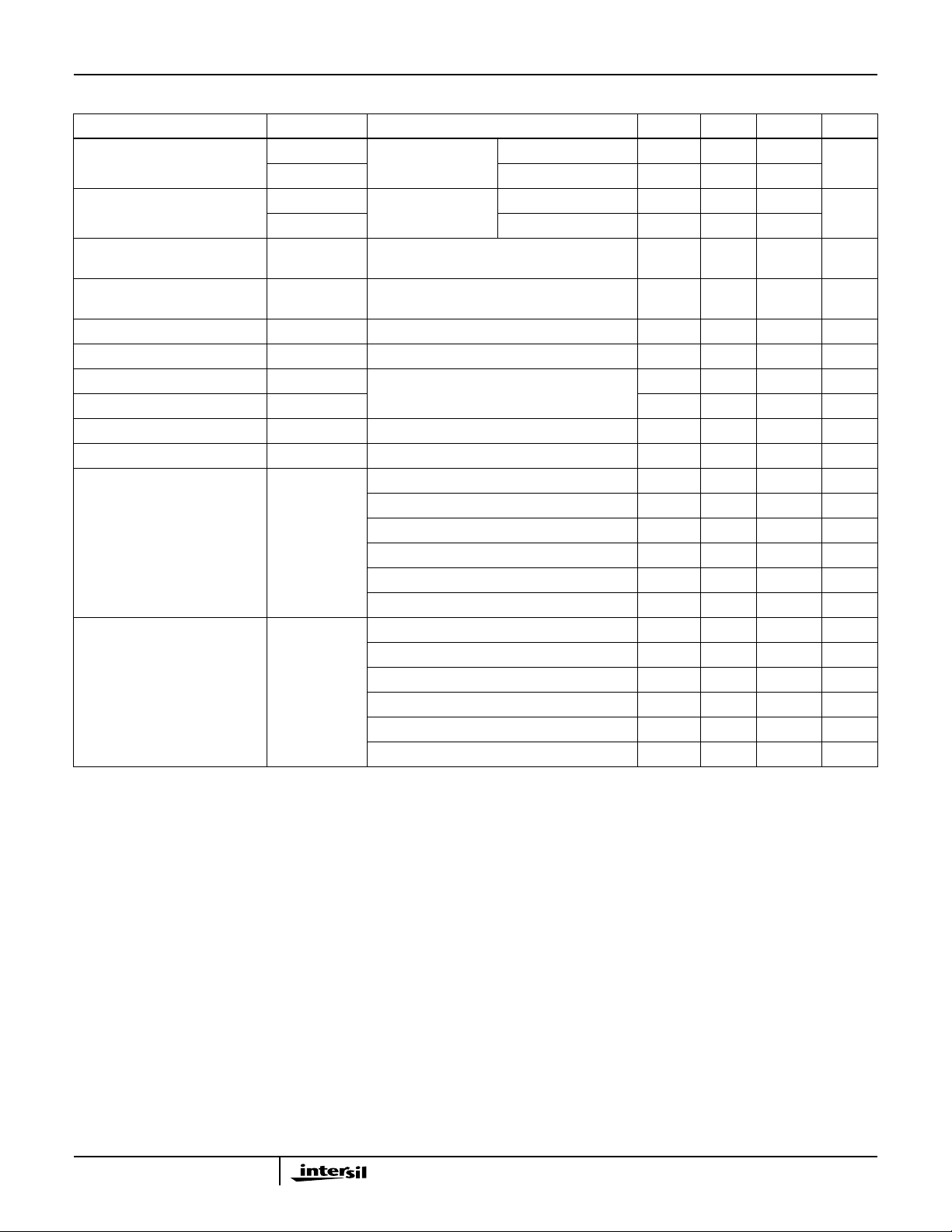

HI3300

Electrical Specifications f

= 20MSPS, AVDD = 3V, DVDD = 3V, VRB = 1V, VRT = 2V, TA = 25oC (Continued)

C

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT

Digital Output Current I

Digital Output Current I

Three-State Output Disable time t

OH

I

OL

OZH

I

OZL

PEZ

OE = AV

SS

DVDD = 2.7V

OE = AV

DD

DVDD = 3.3V

VOH = DVDD -0.4V 1.0 - - mA

VOL = 0.4V 1.0 - VOH = DV

DD

VOL = 0V - - 1.0

Clock not Synchronized for Active → High

- - 1.0 µA

-2-ns

Impedance

Three-State Output Enable Time t

PEZ

Clock not Synchronized For High Impedance →

-2-ns

Active

Integral Nonlinearity Error E

Differential Nonlinearity Error E

L

D

- ±1.0 - LSB

- ±0.5 - LSB

Differential Gain Error DG NTSC 40 IRE Mod Ramp, fC = 14.3MSPS - TBD - %

Differential Phase Error DP - TBD - Deg

Output Data Delay t

Sampling Delay t

DL

SD

CL = 20pF - 3 - ns

-2-ns

SNR SNR fIN = 100kHz - TBD - dB

fIN = 500kHz - TBD - dB

fIN = 1MHz - TBD - dB

fIN = 3MHz - TBD - dB

fIN = 7MHz - TBD - dB

fIN = 10MHz - TBD - dB

SFDR SFDR fIN = 100kHz - TBD - dB

fIN = 500kHz - TBD - dB

fIN = 1MHz - TBD - dB

fIN = 3MHz - TBD - dB

fIN = 7MHz - TBD - dB

fIN = 10MHz - TBD - dB

4

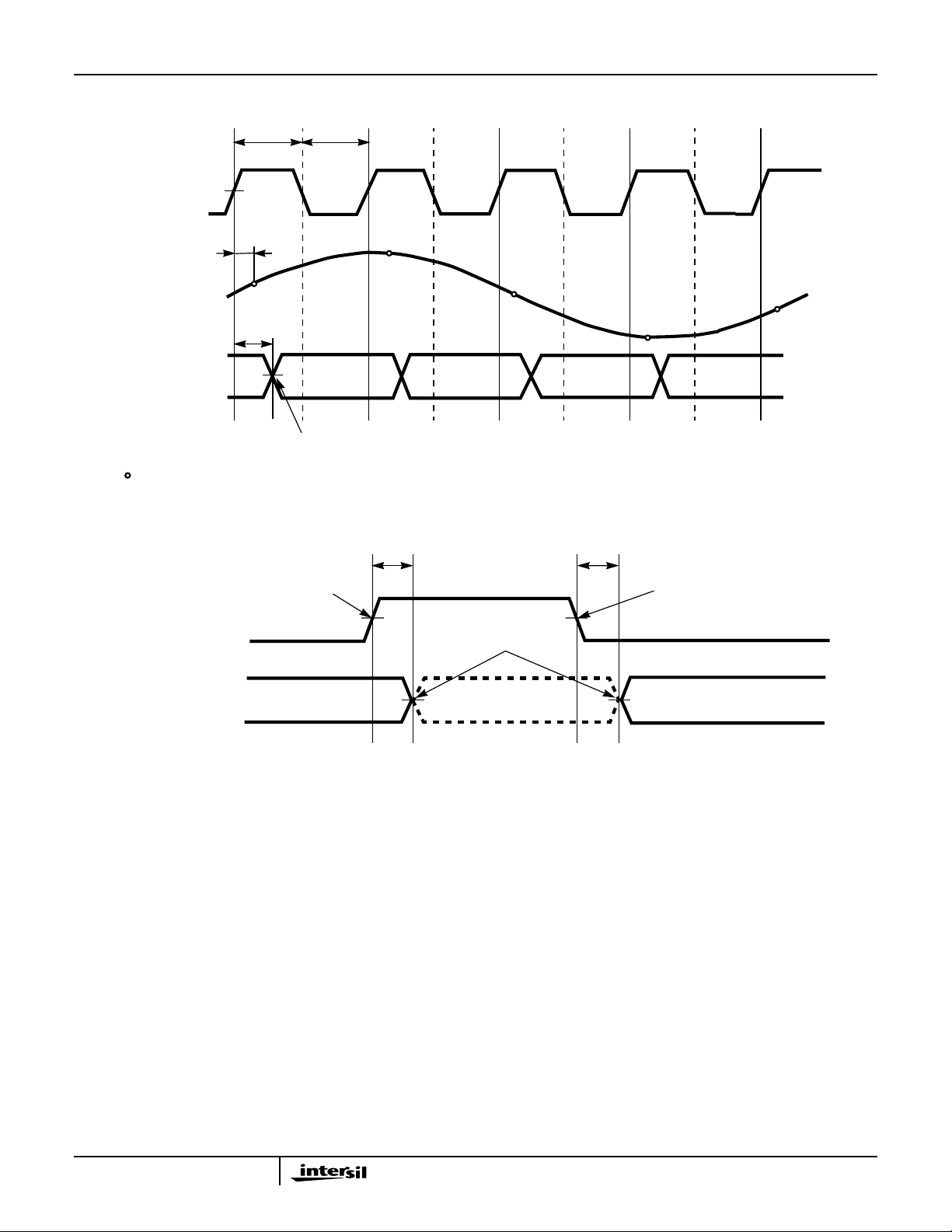

Timing Diagrams

HI3300

t

PW1

CLOCK

ANALOG INPUT

DATA OUTPUT

NOTE: Indicates point at which analog data is sampled.

:

1.5V

t

SD

N

t

DL

t

PW0

N +1

N -3 N -2

1.5V

FIGURE 1. TIMING CHART 1

t

PEZ

N +2

N -1

t

PZE

N +3

N +4

N

OUTPUT ENABLE (OE)

DATA OUTPUT

1.5V

1.5V

ACTIVE HIGH IMPEDANCE

FIGURE 2. TIMING CHART 2

1.5V

ACTIVE

5