®

CA3420

Data Sheet October 4, 2005

0.5MHz, Low Supply Voltage, Low Input

Current BiMOS Operational Amplifier

The CA3420 is an integrated circuit operational amplifier that

combines PMOS transistors and bipolar transistors on a

single monolithic chip. The CA3420 BiMOS operational

amplifier features gate protected PMOS transistors in the

input circuit to provide very high input impedance, very low

input currents (less than 1pA). The internal bootstrapping

network features a unique guardbanding technique for

reducing the doubling of leakage current for every 10°C

increase in temperature. The CA3420 operates at total

supply voltages from 2V to 20V either single or dual supply.

This operational amplifier is internally phase compensated to

achieve stable operation in the unity gain follower

configuration. Additionally, it has access terminals for a

supplementary external capacitor if additional frequency rolloff is desired. Terminals are also provided for use in

applications requiring input offset voltage nulling. The use of

PMOS in the input stage results in common mode input

voltage capability down to 0.45V below the negative supply

terminal, an important attribute for single supply application.

The output stage uses a feedback OTA type amplifier that

can swing essentially from rail-to-rail. The output driving

current of 1.5mA (Min) is provided by using nonlinear current

mirrors.

FN1320.9

Features

• 2V Supply at 300µA Supply Current

• 1pA Input Current (Typ) (Essentially Constant to 85°C)

• Rail-to-Rail Output Swing (Drive ±2mA into 1kΩ Load)

• Pin Compatible with 741 Operational Amplifiers

• Pb-Free Plus Anneal Available (RoHS Compliant)

Applications

• pH Probe Amplifiers

• Picoammeters

• Electrometer (High Z) Instruments

• Portable Equipment

• Inaccessible Field Equipment

• Battery-Dependent Equipment (Medical and Military)

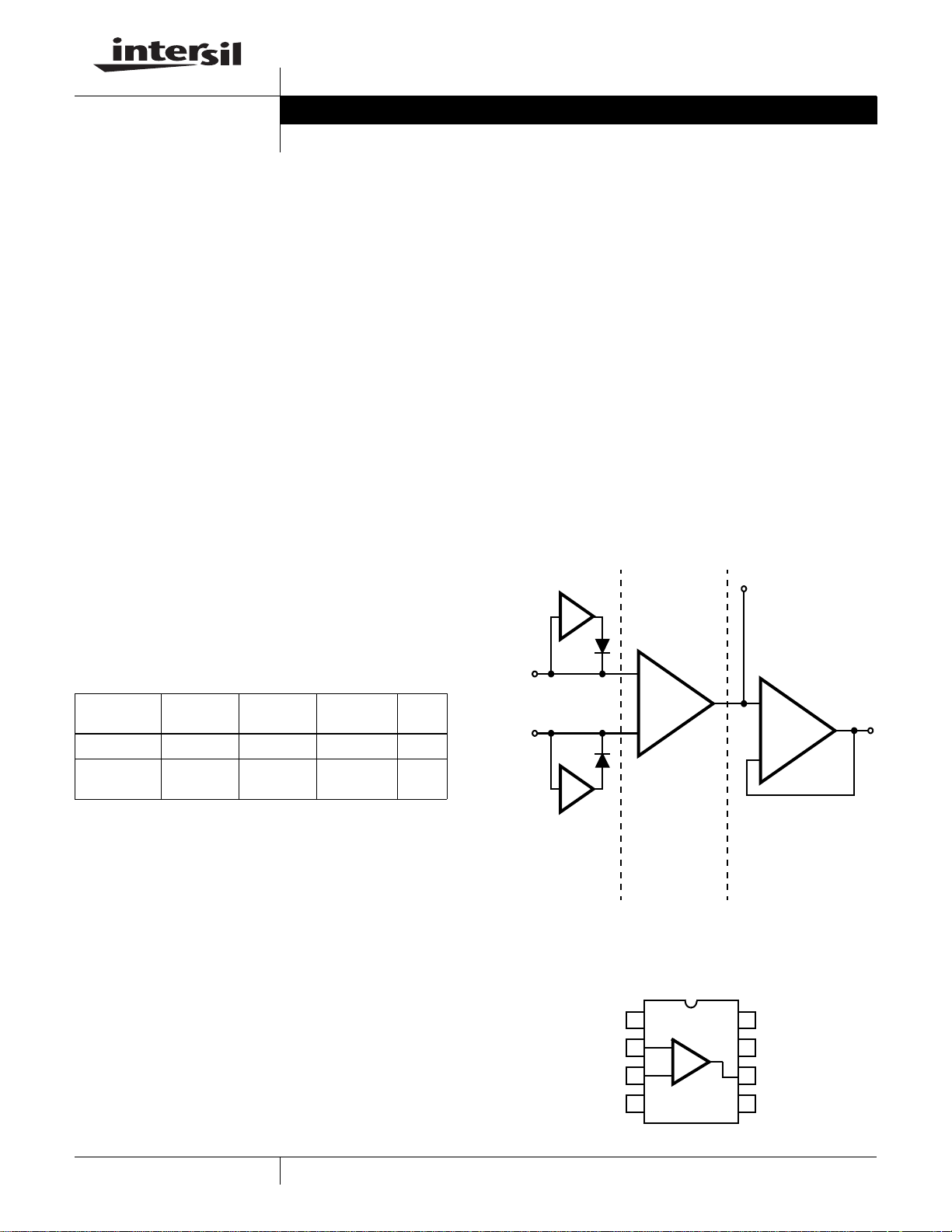

Functional Diagram

X1

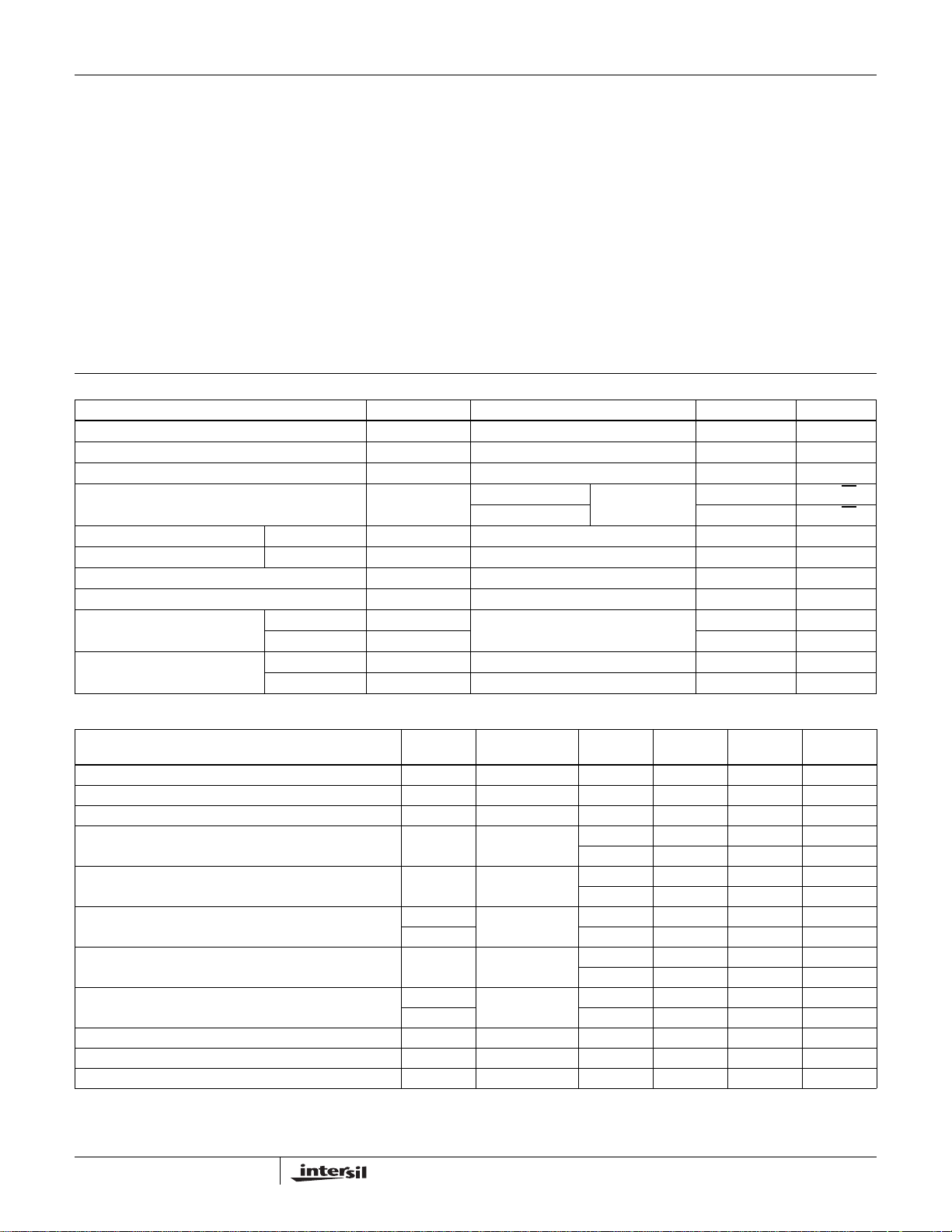

Ordering Information

PART

NUMBER

CA3420E CA3420E -55 to 125 8 Ld PDIP E8.3

CA3420EZ

(Note)

*Pb-free PDIPs can be used for through hole wave solder

processing only. They are not intended for use in Reflow solder

processing applications.

NOTE: Intersil Pb-free plus anneal products employ special

Pb-free material sets; molding compounds/die attach materials and

100% matte tin plate termination finish, which are RoHS compliant

and compatible with both SnPb and Pb-free soldering operations.

Intersil Pb-free products are MSL classified at Pb-free peak reflow

temperatures that meet or exceed the Pb-free requirements of

IPC/JEDEC J STD-020.

PAR T

MARKING

CA3420EZ -55 to 125 8 Ld PDIP*

TEMP.

RANGE (°C) PACKAGE

(Pb-free)

PKG.

DWG. #

E8.3

X1

BUFFER AMPS;

BOOTSTRAPPED

INPUT PROTECTION

NETWORK

Pinout

OFFSET NULL

INPUT

NON-INV.

INPUT

INV.

V-

-

BIPOLAR

+

1

2

3

4

MOS

HIGH GAIN

(50K)

CA3420 (PDIP)

TOP VIEW

-

+

MOS

BIPOLAR

OTA BUFFER

8

STROBE

7

V+

6

OUTPUT

5

OFFSET NULL

(X2)

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2002, 2005. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

CA3420

Absolute Maximum Ratings Thermal Information

Supply Voltage (V+ to V-). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15V

DC Input Voltage . . . . . . . . . . . . . . . . . . . . . . (V+ + 8V) to (V- -0.5V)

Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1mA

Output Short Circuit Duration (Note 1). . . . . . . . . . . . . . . . Indefinite

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . -55°C to 125°C

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Thermal Resistance (Typical, Note 2) θ

PDIP Package* . . . . . . . . . . . . . . . . . . 105 N/A

Maximum Junction Temperature (Plastic Package) . . . . . . . 150°C

Maximum Storage Temperature Range . . . . . . . . . . -65°C to 150°C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300°C

*Pb-free PDIPs can be used for through hole wave solder processing

only. They are not intended for use in Reflow solder processing

applications.

NOTES:

1. Short circuit may be applied to ground or to either supply.

is measured with the component mounted on an evaluation PC board in free air.

2. θ

JA

(°C/W) θJC (°C/W)

JA

Electrical Specifications Typical Values Intended Only for Design Guidance, V

= ±10V, TA = 25°C

SUPPLY

PARAMETER SYMBOL TEST CONDITIONS TYP UNITS

Input Resistance R

Input Capacitance C

Output Resistance R

Equivalent Input Noise Voltage e

I

I

O

N

f = 1kHz RS = 100Ω 62 nV/√Hz

150 TΩ

4.9 pF

300 Ω

f = 10kHz 38 nV/√Hz

Short-Circuit Current Source IOM+2.6mA

To Opposite Supply Sink I

Gain Bandwidth Product f

-2.4mA

OM

T

0.5 MHz

Slew Rate SR 0.5 V/µs

Transient Response Rise Time t

R

RL = 2kΩ, CL = 100pF 0.7 µs

Overshoot OS 15 %

Current from Terminal 8 To V- I

To V + I

Electrical Specifications For Equipment Design, At V

+20µA

8

-2mA

8

= ±1V, TA = 25°C, Unless Otherwise Specified

SUPPLY

TEST

PARAMETER SYMBOL

Input Offset Voltage |V

Input Offset Current (Note 3) |I

Input Current (Note 3) |I

Large Signal Voltage Gain A

IO

IO

I

OL

CONDITIONS MIN TYP MAX UNITS

| - 5 10 mV

| - 0.01 4 pA

|-15pA

RL = 10kΩ 10 100 - kV/V

80 100 - dB

Common Mode Rejection Ratio CMRR - 560 1800 µV/V

55 65 - dB

Common Mode Input Voltage Range V

Power Supply Rejection Ratio PSRR ∆V

+0.20.5- V

lCR

---1.3- V

V

lCR

/∆V - 100 1000 µV/V

IO

60 80 - dB

+R

Max Output Voltage V

OM

- -0.85 -0.91 - V

V

OM

= ∞ 0.90 0.95 - V

L

Supply Current I+ - 350 650 µA

Device Dissipation P

Input Offset Voltage Temperature Drift ∆V

D

/∆T- 4-µV/°C

lO

-0.71.1 mW

NOTE:

3. The maximum limit represents the levels obtainable on high speed automatic test equipment. Typical values are obtained under laboratory conditions.

2

FN1320.9

October 4, 2005

Electrical Specifications For Equipment Design, at V

PARAMETER SYMBOL

Input Offset Voltage |V

Input Offset Current (Note 4) |I

Input Current (Note 4) |I

Large Signal Voltage Gain A

Common Mode Rejection Ratio CMRR - 100 320 µV/V

Common Mode Input Voltage Range V

lCR

V

= ±10V, TA = 25°C, Unless Otherwise Specified

SUPPLY

TEST

CONDITIONS MIN TYP MAX UNITS

| - 5 10 mV

IO

| - 0.03 4 pA

IO

| - 0.05 5 pA

I

RL = 10kΩ 10 100 - kV/V

OL

80 100 - dB

70 80 - dB

+8.59.3- V

- -10 -10.3 - V

lCR

Typical Applications

Picoammeter Circuit

The exceptionally low input current (typically 0.2pA) makes

the CA3420 highly suited for use in a picoammeter circuit.

With only a single 10GΩ resistor, this circuit covers the range

from ±1.5pA. Higher current ranges are possible with suitable

switching techniques and current scaling resistors. Input

transient protection is provided by the 1MΩ resistor in series

with the input. Higher current ranges require that this resistor

be reduced. The 10MΩ resistor connected to pin 2 of the

CA3420 decouples the potentially high input capacitance

often associated with lower current circuits and reduces the

tendency for the circuit to oscillate under these conditions.

High Input Resistance Voltmeter

Advantage is taken of the high input impedance of the CA3420

in a high input resistance DC voltmeter. Only two 1.5V “AA”

type penlite batteries power this exceedingly high-input

resistance (>1,000,000MΩ) DC voltmeter. Full-scale deflection

is ±500mV, ±150mV, and ±15mV. Higher voltage ranges are

easily added with external input voltage attenuator networks.

The meter is placed in series with the gain network, thus

eliminating the meter temperature coefficient error term.

Supply current in the standby position with the meter

undeflected is 300µA. At full-scale deflection this current

rises to 800µA. Carbon-zinc battery life should be in excess

of 1,000 hours.

3

FN1320.9

October 4, 2005

Typical Performance Curves

1.0

= 25°C

T

A

0.8

RL = 100kΩ

0.6

0.4

0.2

0

-0.2

-0.4

-0.6

-0.8

-1.0

POSITIVE AND NEGATIVE SUPPLY VOLTAGE (V)

INPUT & OUTPUT VOLTAGE EXCURSIONS FROM THE

510

SUPPLY VOLTAGE (V)

FIGURE 3. OUTPUT VOLTAGE SWING AND COMMON MODE

INPUT VOLTAGE RANGE vs SUPPLY VOLTAGE

VO-

V

+

O

V

-

ICR

V

+

ICR

10

CA3420

15

10

T

= 25°C

A

V- = 0V

V+ = 2V

V+ = 5V

(mV)

19

V+ = 10V

V+ = 20V

100

VOLTAGE, Q

OUTPUT STAGE TRANSISTOR SATURATION

1000

1010.10.01

LOAD (SOURCING) CURRENT (mA)

FIGURE 4. OUTPUT VOLTAGE vs LOAD SOURCING CURRENT

1000

(mV)

17

100

= 25°C

T

A

V+ = 0V

V- = -20V

V- = -10V

V- = -5V

1000

100

VS = ±10V

= ±5V

V

S

= ±1V

V

S

TA = 25°C

V- = -2V

VO LTA G E, Q

OUTPUT STAGE TRANSISTOR SATURATION

10

1010.10.01

LOAD (SINKING) CURRENT (mA)

10

EQUIVALENT INPUT NOISE VOLTAGE (nV/√Hz)

1

1

10

2

10

3

10

4

10

5

10

FREQUENCY (Hz)

FIGURE 5. OUTPUT VOLTAGE vs LOAD SINKING CURRENT FIGURE 6. INPUT NOISE VOLTAGE vs FREQUENCY

= 25°C

T

A

V

= ±5V

S

= 10kΩ

100

80

60

40

20

OPEN LOOP VOLTAGE GAIN (dB)

0

1

10

2

1

10

3

10

FREQUENCY (Hz)

R

L

C

= 0pF

L

0

-45

-90

-135

-180

OPEN LOOP PHASE (DEGREES)

6

5

4

10

10

10

6

10

FIGURE 7. OPEN LOOP GAIN AND PHASE SHIFT RESPONSE

4

FN1320.9

October 4, 2005

5

Loading...

Loading...