International Rectifier IRU1030CD, IRU1030CT, IRU1030CM Datasheet

Data Sheet No. PD94124

IRU1030

3A LOW DROPOUT POSITIVE

ADJUSTABLE REGULATOR

FEATURES

Guaranteed < 1.3V Dropout at Full Load Current

Fast Transient Response

1% Voltage Reference Initial Accuracy

Output Current Limiting

Built-In Thermal Shutdown

APPLICATIONS

Low Voltage Processor Applications such as:

P54C, P55C, Cyrix M2,

POWER PC, AMD

GTL+ Termination

PENTIUM PRO, KLAMATH

Low Voltage Memory Termination Applications

Standard 3.3V Chip Set and Logic Applications

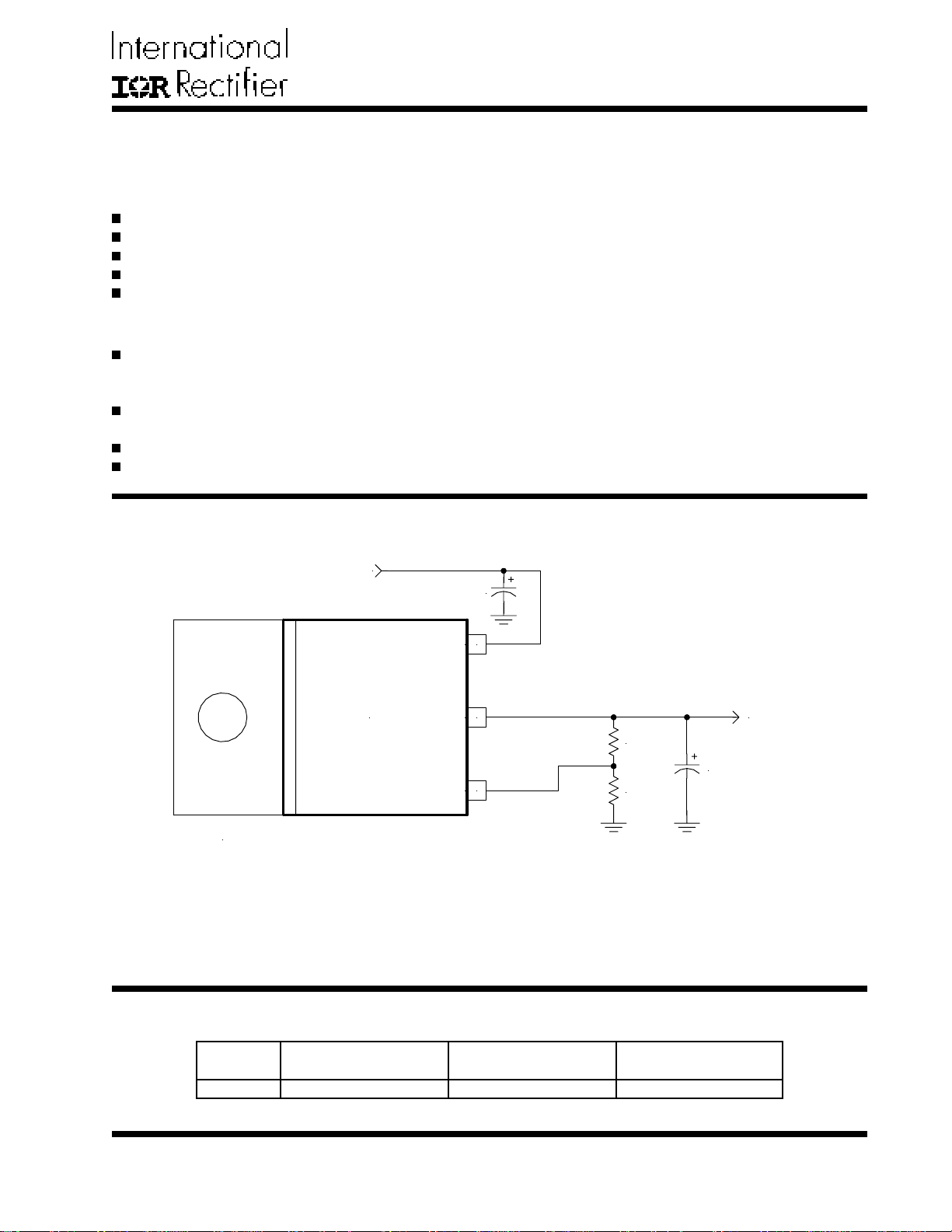

TYPICAL APPLICATION

5V

C1

1500uF

Vin

3

DESCRIPTION

The IRU1030 is a low dropout three-terminal adjustable

regulator with minimum of 3A output current capability.

This product is specifically designed to provide well regulated supply for low voltage IC applications such as

Pentium P54C, P55C as well as GTL+ termination for Pentium Pro and Klamath processor appli-

cations. The IRU1030 is also well suited for other pro-

cessors such as Cyrix, AMD and Power PC appli-

cations. The IRU1030 is guaranteed to have <1.3V dropout at full load current making it ideal to provide well

regulated outputs of 2.5V to 3.3V with 4.75V to 7V input

supply.

Vou t

Adj

2

R1

121

1

R2

200

IRU1030

1030app1-1.1

Figure 1 - Typical Application of IRU1030 in a 5V to 3.3V regulator

Notes: Pentium P54C, P55C, Klamath, Pentium Pro, VRE are trademarks of Intel Corp.Cyrix M2 is trademark of Cyrix Corp.

Power PC is trademark of IBM Corp.

3.3V / 3A

C2

1500uF

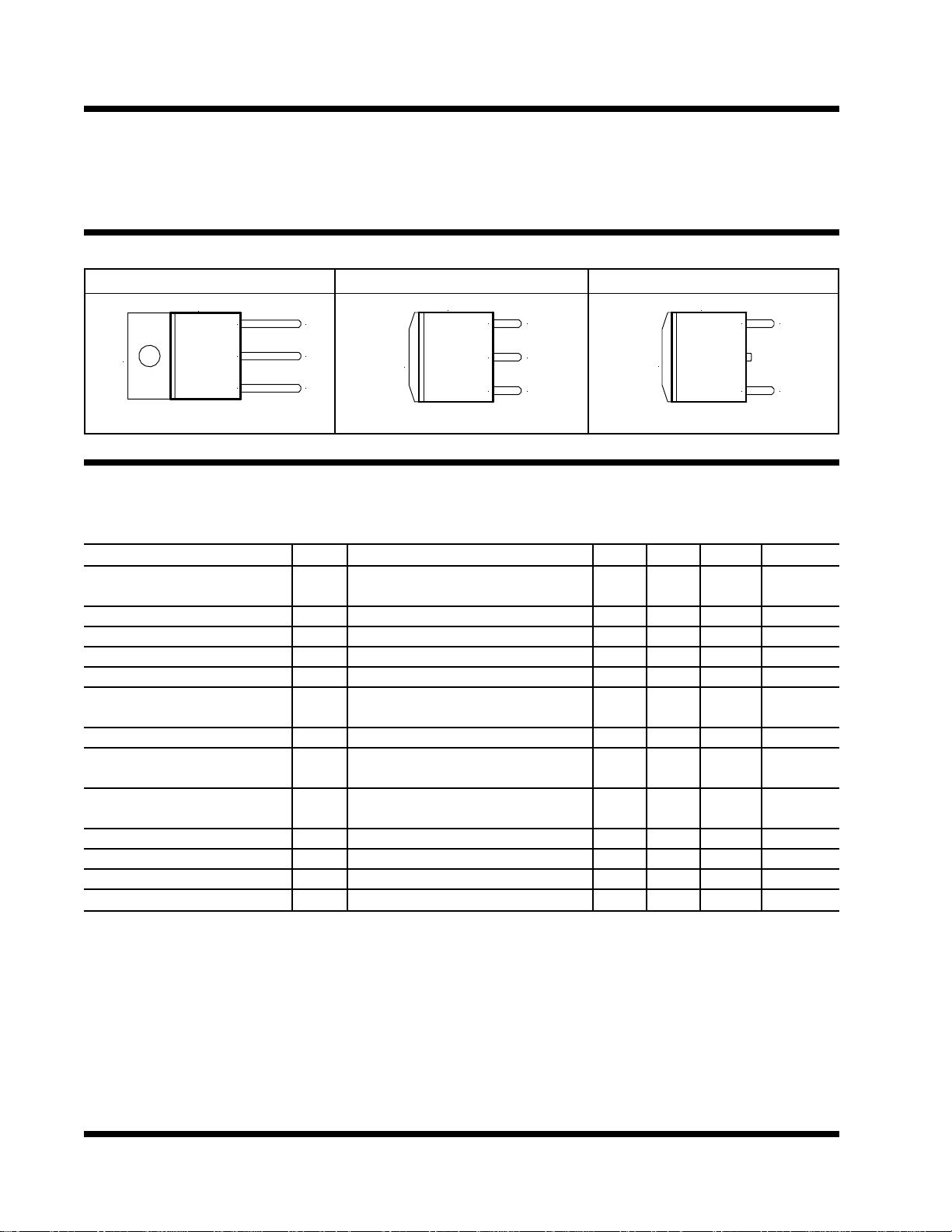

PACKAGE ORDER INFORMATION

Tj (°C) 3-PIN PLASTIC 3-PIN PLASTIC 2-PIN PLASTIC

TO-220 (T) TO-263 (M) TO-252 (D-Pak)

0 To 150 IRU1030CT IRU1030CM IRU1030CD

Rev. 1.1

06/29/01

1

IRU1030

ABSOLUTE MAXIMUM RATINGS

Input Voltage (Vin) .................................................... 7V

Power Dissipation ..................................................... Internally Limited

Storage Temperature Range ...................................... -65°C To 150°C

Operating Junction Temperature Range ..................... 0°C To 150°C

PACKAGE INFORMATION

3-PIN PLASTIC TO-220 (T) 3-PIN PLASTIC TO-263 (M) 2-PIN PLASTIC TO-252 (D-Pak)

Vou t

FRONT VIEW

3

Vin

2

Vou t

1

Adj

Tab is

Vou t

FRONT VIEW

3

2

1

Vin

Vou t

Adj

Tab i s

θJT=2.7°C/W θJA=60°C/W θJA=35°C/W for 1" Square pad θJA=70°C/W for 0.5" Square pad

ELECTRICAL SPECIFICATIONS

Unless otherwise specified, these specifications apply over Cin=1µF, Cout=10µF, and Tj=0 to 150!C.

Typical values refer to Tj=25!C.

PARAMETER SYM TEST CONDITION MIN TYP MAX UNITS

Reference Voltage Vref Io=10mA, Tj=25!C, (Vin-Vo)=1.5V 1.238 1.250 1.262 V

Io=10mA, (Vin-Vo)=1.5V 1.225 1.250 1.275

Line Regulation Io=10mA, 1.3V<(Vin-Vo)<7V 0.2 %

Load Regulation (Note 1) Vin=3.3V, Vadj=0, 10mA<Io<3A 0.4 %

Dropout Voltage (Note 2) ∆Vo Note 2, Io=3A 1.1 1.3 V

Current Limit Vin=3.3V, dVo=100mV 3.1 A

Minimum Load Current Vin=3.3V, Vadj=0V 5 10 mA

(Note 3)

Thermal Regulation 30ms Pulse, Vin-Vo=3V, Io=3A 0.01 0.02 %/W

Ripple Rejection f=120Hz, Co=25µF Tantalum,

Io=1.5A, Vin-Vo=3V 60 70 dB

Adjust Pin Current Iadj Io=10mA, Vin-Vo=1.5V, Tj=25!C,

Io=10mA, Vin-Vo=1.5V 55 120 µA

Adjust Pin Current Change Io=10mA, Vin-Vo=1.5V, Tj=25!C 0.2 5 µA

Temperature Stability Vin=3.3V, Vadj=0V, Io=10mA 0.5 %

Long Term Stability Tj=125!C, 1000Hrs 0.3 1 %

RMS Output Noise Tj=25!C, 10Hz<f<10KHz 0.003 %Vo

Tab i s

Vout

FRONT VIEW

3

Vin

1

Adj

Note 1: Low duty cycle pulse testing with Kelvin connections is required in order to maintain accurate data.

Note 2: Dropout voltage is defined as the minimum differential voltage between Vin and Vout required to maintain regulation at Vout. It is measured when the output

voltage drops 1% below its nominal value.

2

Note 3: Minimum load current is defined as the mini-

mum current required at the output in order for the output voltage to maintain regulation. Typically the resistor

dividers are selected such that this current is automatically maintained.

Rev. 1.1

06/29/01

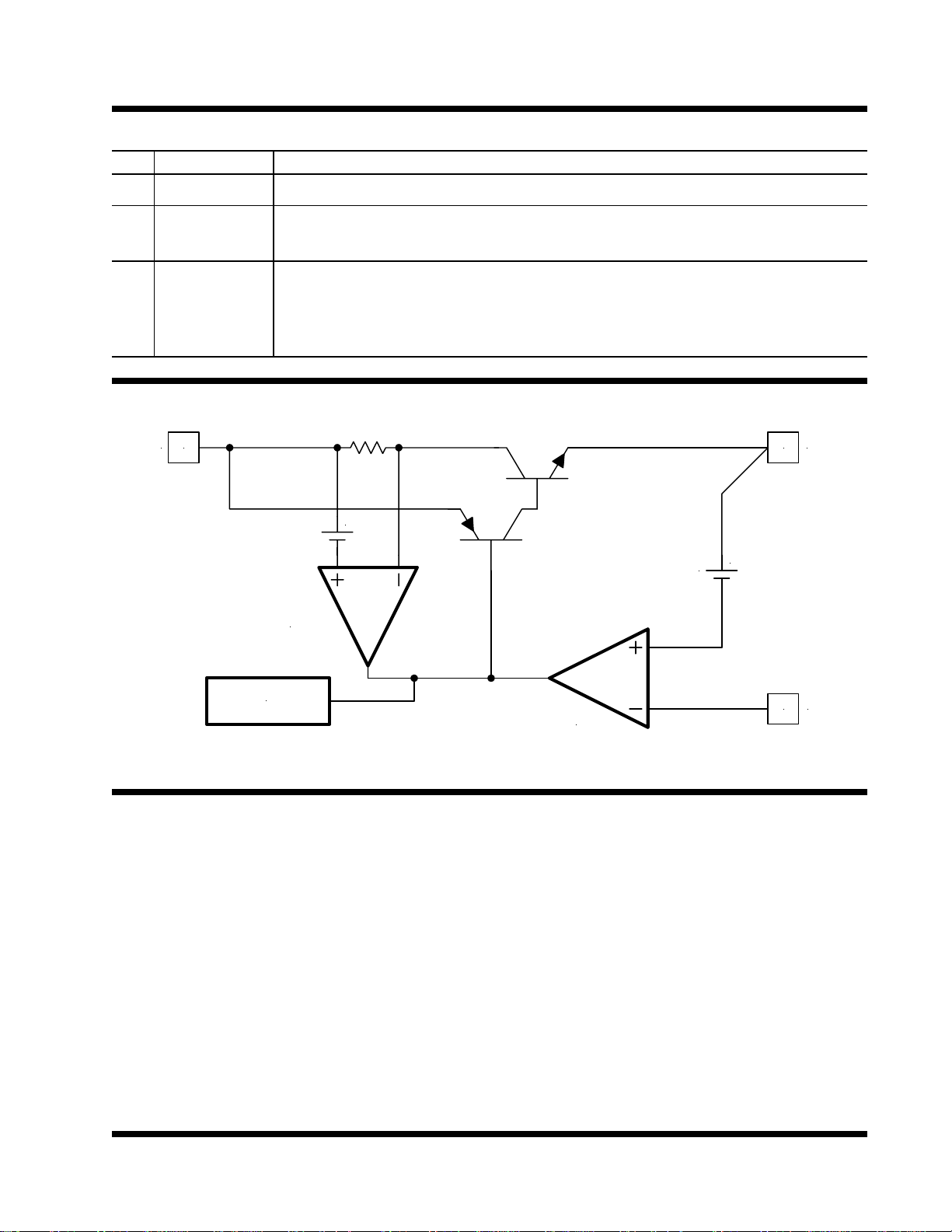

PIN DESCRIPTIONS

PIN # PIN SYMBOL PIN DESCRIPTION

1

Adj

A resistor divider from Vout to Adj pin to ground sets the output voltage.

IRU1030

2

3

Vout

Vin

The output of the regulator. A minimum of 10µF capacitor must be connected from this pin

to ground to insure stability.

The input pin of the regulator. Typically a large storage capacitor is connected from this

pin to ground to insure that the input voltage does not sag below the minimum drop out

voltage during the load transient response. This pin must always be 1.3V higher than Vout

in order for the device to regulate properly.

BLOCK DIAGRAM

Vin 3

CURRENT

LIMIT

2 Vout

+

1.25V

+

THERMAL

SHUTDOWN

Figure 2 - Simplified block diagram of the IRU1030

APPLICATION INFORMATION

Introduction

The IRU1030 adjustable Low Dropout (LDO) regulator is

a three-terminal device which can easily be programmed

with the addition of two external resistors to any voltages within the range of 1.25 to 5.5V. This regulator unlike the first generation of the three-terminal regulators

such as LM117 that required 3V differential between the

input and the regulated output, only needs 1.3V differential to maintain output regulation. This is a key requirement for today’s microprocessors that need typically

3.3V supply and are often generated from the 5V supply. Another major requirement of these microproces-

sors such as the Intel P54C is the need to switch the

load current from zero to several amps in tens of nano-

1030blk1-1.0

seconds at the processor pins, which translates to an

approximately 300 to 500ns current step at the regulator. In addition, the output voltage tolerances are also

extremely tight and they include the transient response

as part of the specification. For example Intel VRE

specification calls for a total of ±100mV including initial

tolerance, load regulation and 0 to 4.6A load step.

The IRU1030 is specifically designed to meet the fast

current transient needs as well as providing an accurate

initial voltage, reducing the overall system cost with the

need for fewer output capacitors.

1 Adj

Rev. 1.1

06/29/01

3

Loading...

Loading...