International Rectifier IR3622MTRPBF, IR3622MPBF Datasheet

IR3622MPbF

www.irf.com

HIGH FREQUENCY 2-PHASE, SINGLE OR DUAL OUTPUT SYNCHRONOUS STEP

DOWN CONTROLLER WITH OUTPUT TRACKING AND SEQUENCING

Description

The IR3622 IC integrates a dual synchronous

Buck controller, providing a high performance and

flexible solution. The IR3622 can be configured

as 2-independent outputs or as current shared

single output. The current share configuration is

ideal for high current applications.

The IR3622 enables output tracking and

sequencing of multiple rails in either ratiometric or

simultaneous fashion. The IR3622 features 180

o

out of phase operation which reduces the

required input/output capacitance and results in

lower number of capacitors. The switching

frequency is programmable from 200kHz to

600kHz per phase using one external resistor. In

addition, IR3622 also allows the switching

frequency to be synchronized to an external clock

signal.

Other key features offered by this device include

two independent programmable soft starts, two

independent power good outputs, precision

enable input, and under voltage lockout function.

The current limit is provided by sensing the lower

MOSFET's on-resistance for optimum cost and

performance. The output voltages are monitored

through dedicated pins to protect against open

circuit, and enhance faster response to an

overvoltage event.

Features

• Dual Synchronous Controller with 180

o

Out of Phase Operation

• Configurable to 2-Independent Outputs or Current

Shared Single Output

• Output Voltage Tracking

• Power up / down Sequencing

• Current Sharing Using Inductor’s DCR

• +/-1% Accurate Reference Voltage

• Programmable Switching Frequency up 600kHz

• Programmable Over Current Protection

• Hiccup Current Limit Using MOSFET R

ds(on)

sensing

• Latched Overvoltage Protection

• Dual Programmable Soft-Starts

• Programmable Enable Input

• Pre-Bias Start-up

• Dual Power Good Outputs

• On Board Regulator

• External Frequency Synchronization

• Thermal Protection

• 32-Lead MLPQ Package

Applications

• Embedded Telecom Systems

• Distributed Point of Load Power Architectures

• Computing Peripheral Voltage Regulators

• Graphics Cards

• General DC/DC Converters

Data Sheet No.PD94722 revA

ORDERING INFORMATION

PKG PACKAGE PIN PARTS PARTS T&R

DESIG DESCRIPTION COUNT PER TUBE PER REEL ORIANTAION

M IR3622MPbF 32 73 ------M IR3622MTRPbF 32 -------- 3000

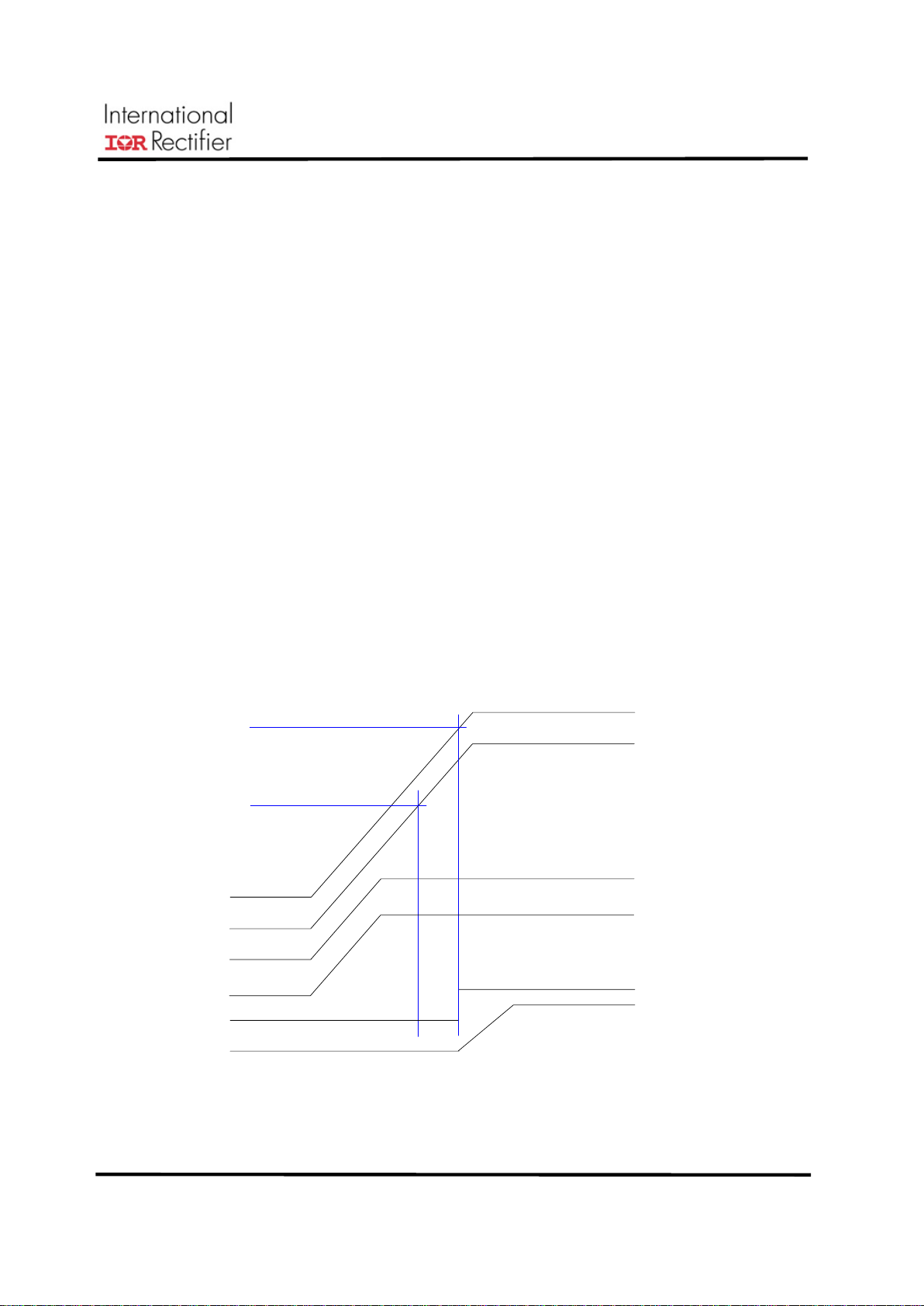

Fig A

Simultaneous Powerup

Vo1

Vo2

Simultaneous Powerdown

Vo1

Vo2

Vo1

Vo2

Ratiometric Powerup

Vo1

Vo2

Ratiometric Powerdown

Vin

Vout1

PGnd1

LDrv1

HDrv1

LDrv2

HDrv2

Gnd

Comp2

Comp1

SS1 / SD

IR3622

Rt

SS2 / SD

PGnd2

OCSet2

OCSet1

Vin

Vout2

Vout1

Track

Seq

03/15/07

IR3622MPbF

www.irf.com

Package Information

2

ΘJA= 36

o

C/W*

ΘJC= 1o C/W

*Exposed pad on underside is connected to a copper

pad through vias for 4-layer PCB board design

ABSOLUTE MAXIMUM RATINGS

(Voltages referenced to GND)

Vcc, VcL Supply Voltage .....................................… -0.5V to 16V

VcH1,VcH2 ……………………….………….……… -0.5V to 30V

PGood1, PGood2 ………. .…………………………. -0.5V to 16V

HDrv1, HDrv2 ………………………………………… -0.5V to 30V (-2V for 100ns)

LDrv1, LDrv2 ………………………………………… -0.5V to 16V (-2V for 100ns)

Gnd to PGnd ……………………………………….. +/- 0.3V

Storage Temperature Range .................................. -65°C To 150°C

Operating Junction Temperature Range ................ -40°C To 125°C

ESD Classification ………………………………..… JEDEC, JESD22-A114 (1KV)

Moisture Sensitivity Level ………………………….. JEDEC, Level 3 @ 260

o

C

Caution: Stresses above those listed in “Absolute Maximum Rating” may cause permanent damage to the

device. These are stress ratings only and function of the device at these or any other conditions beyond those

indicated in the operational sections of the specifications is not implied. Expos ure to “Absolute Maximum Rating”

conditions for extended periods may affect device reliab ility.

E

n

a

b

l

e

13

Fb1

Comp1

SS1/SD1

OCSet1

VcH1

P

G

n

d

2

L

D

r

v

2

V

c

L

L

D

r

v

1

Comp2

SS2/SD2/Mode

OCSet2

VcH2

HDrv2

V

OU

T

3

V

c

c

P

G

o

o

d

1

G

n

d

4

5

6

7

8

9

10

11

12

17

18

19

20

21

28

29

30

3132

Pad

14

15

16

PGood2

Sync

V

SEN1

22

23

24

V

SEN2

Fb2

1

2

3

V

R

E

F

V

P

2

25

26

27

P

G

n

d

1

S

e

q

H

D

r

v

1

Rt

T

r

a

c

k

V

P

1

IR3622MPbF

www.irf.com

Recommended Operating Conditions

3

Electrical Specifications

Unless otherwise specified, these specification apply over Vcc=VcL=VcH1=VcH2=12V, 0oC<Tj<105oC

Symbol Definition Min Max Units

Vcc, VcL Supply Voltage 7.5 14.5 V

VcH1, VcH2 Supply Voltage Converter Voltage + 5V 28 V

Fs Operating frequency 200 600 kHz

Tj Junction temperature -40 125 oC

Parameter

SYM

Test Condition

Min

TYP MAX

Units

Output Voltage Accuracy

FB1,2 Voltage VFB Vp1=Vp2=Vref=0.8V 0.8 V

0oC <Tj< 125oC -1 +1 % Accuracy

-40

o

C <Tj< 125oC; Note2

-1.5

+1.5

%

Supply Current

VCC Supply Current

(Static)

I

CC

(Static) SS=0V, No Switching 13 18 mA

VCC Supply Current

(Dynamic)

ICC (Dynamic) Fs=300kHz, C

LOAD

= 3.3nF 20 30 mA

VCL Supply Current

(Static)

ICL (Static) SS=0V, No Switching 8 10 mA

VCL Supply Current

(Dynamic)

ICL (Dynamic) Fs=300kHz, C

LOAD

= 3.3nF 30 42 mA

V

CH1,2

Supply Current

(Static)

ICH (Static) SS=0V, No Switching 9 11 mA

V

CH1,2

Supply Current

(Dynamic)

ICH (Dynamic Fs=300kHz, C

LOAD

= 3.3nF 30 42 mA

Under Voltage Lockout, Enable

VCC-Start Threshold VCC_UVLO(R) Supply ramping up 6.85 7.1 7.5 V

VCC-Stop Threshold VCC_UVLO(F) Supply ramping down 6.1 6.4 6.7 V

VCC-Hysteresis Supply ramping up and down 0.5 0.8 1.0 V

V

CH1,2

-Start Threshold VCH_UVLO(R) Supply ramping up 4.6 4.95 5.3 V

V

CH1,2

-Stop Threshold VCH_UVLO(F) Supply ramping down 4.1 4.4 4.7 V

V

CH1,2

-Hysteresis Supply ramping up and down 0.32 0.6 0.8 V

Enable-Threshold En_UVLO Supply ramping up 1.14 1.24 1.34 V

Enable-Hysteresis Supply ramping up and down 0.15 0.2 0.33 V

Oscillator

Frequency Range

FS

200

600 kHz

Accuracy

Fs=300kHz -12

+12 %

Ramp Amplitude Vramp

Note1

1.25 V

Min Duty Cycle Dmin Fb=1V 0 %

Min Pulse Width Ton(min)

F

S

=300kHz, Note1

150 ns

Max duty Cycle Dmax FS=300kHz, Fb=0.6V 84 %

Sync Frequency Range Sync(F) 20% above free running Freq 1200 kHz

Sync Pulse Duration Sync(Pulse)

200 300 ns

Sync High Level Threshold Sync(H)

2 V

Sync Low Level Threshold Sync(L)

0.6 V

IR3622MPbF

www.irf.com

Electrical Specifications

4

Parameter SYM Test Condition Min TYP MAX Units

Error Amplifier 1, 2

Fb Voltage Input

Bias Current

IFB SS=3V -0.1 -0.5

µA

E/A Source/Sink

Current

I(source/Sink) 120 200 280

µA

Transconductance gm1,2 3000 4500

µmho

Input offset

Voltage

Voffset Fb to Vref -4 0 +4 mV

VP Voltage Range VP

Note1

0.4 Vcc-2 V

Internal Regulator

Output Accuracy Vout3 6.7 7.2 7.7 V

Dropout Vdrop Vcc(min)=9V, Isource=100mA 2 V

Current Limit Ishort 110 mA

Soft Start/SD

Soft Start Current ISS Source/Sink 18 23 28

µA

Shutdown

Threshold

SD 0.25 V

Over Current Protection

OCSET Current I

OCSET

16 20 24

µA

Hiccup Duty Cycle Hiccup(duty)

Ihiccup / Iocset, Note1

5 %

Over Voltage Protection

OVP Trip Threshold OVP(trip) 1.1Vref 1.15Vref 1.2Vref V

OVP Fault Prop

Delay

OVP(delay) Output Forced to 1.25Vref 5

µ

s

Thermal Shutdown

Thermal shutdown

Note1

140 oC

Thermal shutdown

Hysteresis

Note1

20

o

C

Power Good

Vsen Lower Trip

point

Vsen(trip) Vsen Ramping Down 0.8Vref 0.9Vref 0.95Vref V

PGood Output Low

Voltage

PG(voltage) I

PGood

=2mA 0.1 0.5 V

Output Drivers

LO, Drive Rise Time Tr(Lo) C

LOAD

=3.3nF, Fs=300KHz,

2V to 9V

25 50 ns

LO Drive Fall Time Tf(Lo) C

LOAD

=3.3nF, Fs=300KHz,

9V to 2V

25 50 ns

HI Drive Rise Time Tr(Hi) C

LOAD

=3.3nF, Fs=300KHz,

2V to 9V

25 50 ns

HI Drive Fall Time Tf(Hi) C

LOAD

=3.3nF, Fs=300KHz,

9V to 2V

25 50 ns

Dead Band Tim e Tdead See Figure1 20 60 100 ns

Seq Input

On 2.0 Seq Threshold Seq

Off 0.3

V

Tracking

Track voltage range TK

Note1

0 Vcc V

IR3622MPbF

www.irf.com

5

Note1: Guaranteed by design but not tested in production.

Note2: Cold temperature performance is guaranteed via correlation using statistical quality

control. Not tested in production.

9V

2V

9V

2V

High Side Driver

(HDrv)

Low Side Driver

(LDrv)

Tr

Tf

Deadband

H_to_L

Deadband

L_to_H

Tr

Tf

Fig. 1: Rise / Fall and deadband time for driver section

IR3622MPbF

www.irf.com

6

Pin# Pin Name Description

1 Rt Connecting a resistor from this pin to ground sets the switching frequency

(see figure 16 on page 17 for selecting resistor value)

2 V

SEN2

Sense pin for OVP2 and Power Good2, Channel 2

3 Fb2 Inverting input to the error amplifier2

4 Comp2 Compensation pin for the error amplifier2

5 SS2/SD2/Mode Soft start for channel 2, can be used as SD pin. Float this pin for current

share single output application

6 OCSet2 Current limit set point for channel2

7, 17 VcH2, VcH1 Supply voltage for the high side output drivers. These are connected to

voltage that must be typically 6V higher than their bus voltages. A 0.1uF

high frequency capacitor must be connected from these pins to PGND to

provide peak drive current capability

8,16 HDrv2, HDrv1 Output drivers for the high side power MOSFETs

9 Enable Enable pin, recycling this pin will reset OV, SS and Prebias latch

10, 14 PGnd2, PGnd1 These pins serve as the separate grounds for MOSFET drivers and should

be connected to the system’s ground plane

11, 13 LDrv2 , LDrv1 Output drivers for the synchronous power MOSFETs

12 VcL Supply voltage for the low side output drivers

15 Seq Enable pin for tracking and sequencing. If this pin is not used

connect it to V

out3

18 OCSet1 Current limit set point for Channel 1

19 SS1/SD1 Soft start for Channel 1, can be used as SD pin

20 Comp1 Compensation pin for the error amplifier1

21 Fb1 Inverting input to the error amplifier1

22 V

SEN1

Sense pin for OVP1 and Power Good1, Channel 1

23 Sync External synchronization pin

24 PGood2 Power Good pin output for channel 2, open collector. This pin needs to be

externally pulled high

25 VP1 Non inverting input of error amplifier1

26 VP2 Non inverting input of error amplifier2

27 V

REF

Reference Voltage

28 Gnd IC’s Ground

29 PGood1 Power Good pin output for Channel 1, open collector. This pin needs to be

externally pulled high

30 Vcc Supply voltage for the internal blocks of the IC. A 0.1uF high frequency

capacitor must be connected from this pin to Gnd.

31 V

out3

Output of the internal regulator. A 0.1uF high frequency capacitor must be

connected from this pin to PGnd.

32 Track Sets the type of power up / down sequencing (ratiometric or

simultaneous). If this pin is not used connect it to V

out3

IR3622MPbF

www.irf.com

Block Diagram

Fig. 2: Simplified block diagram of the IR3622

7

PBias2

Bias

Generator

LDrv2

Two Phase

Oscillator

0.8V

3V

Ramp1

Sync

Gnd

HDrv2

VcH2

SS1 / SD

Comp2

Error Amp2

PWM Comp2

POR

PGood2

23uA

Reset Dom

LDrv1

V

CL

HDrv1

VcH1

Fb1

Comp1

Error Amp1

PWM Comp1

Reset Dom

Set1

Set2

Ramp2

64uA

UVLO

VcH2

VcH1

Fb2

PGnd2

Vcc

Rt

SS2 / SD

V

P2

V

REF

PGood1

R

S

Q

Q

S

R

V

SEN1

OCSet2

OVP1

Thermal

Shutdown

PGnd1

OCSet1

23uA

64uA

Hiccup

Control

SS1

SS2

Mode

Regulator

Mode

20uA

20uA

POR

0.8V

PBias1

0.3V

SS1

PBias1

SS1

SS2

3uA

3uA

POR

0.3V

SS2

POR

V

P1

Tracking

Seq

Track

SS1 / SD

V

OUT3

Enable

HDrv1 OFF / LDrv1 ON

OVP1

OVP2

1.15Vref

0.90Vref

V

SEN2

OVP2

HDrv2 OFF / LDrv2 ON

Q

R

S

POR

1.15Vref

0.90Vref

Vcc

Q

R

S

POR

Q

R

S

R

S

Q

Seq

23uA

IR3622MPbF

www.irf.com

8

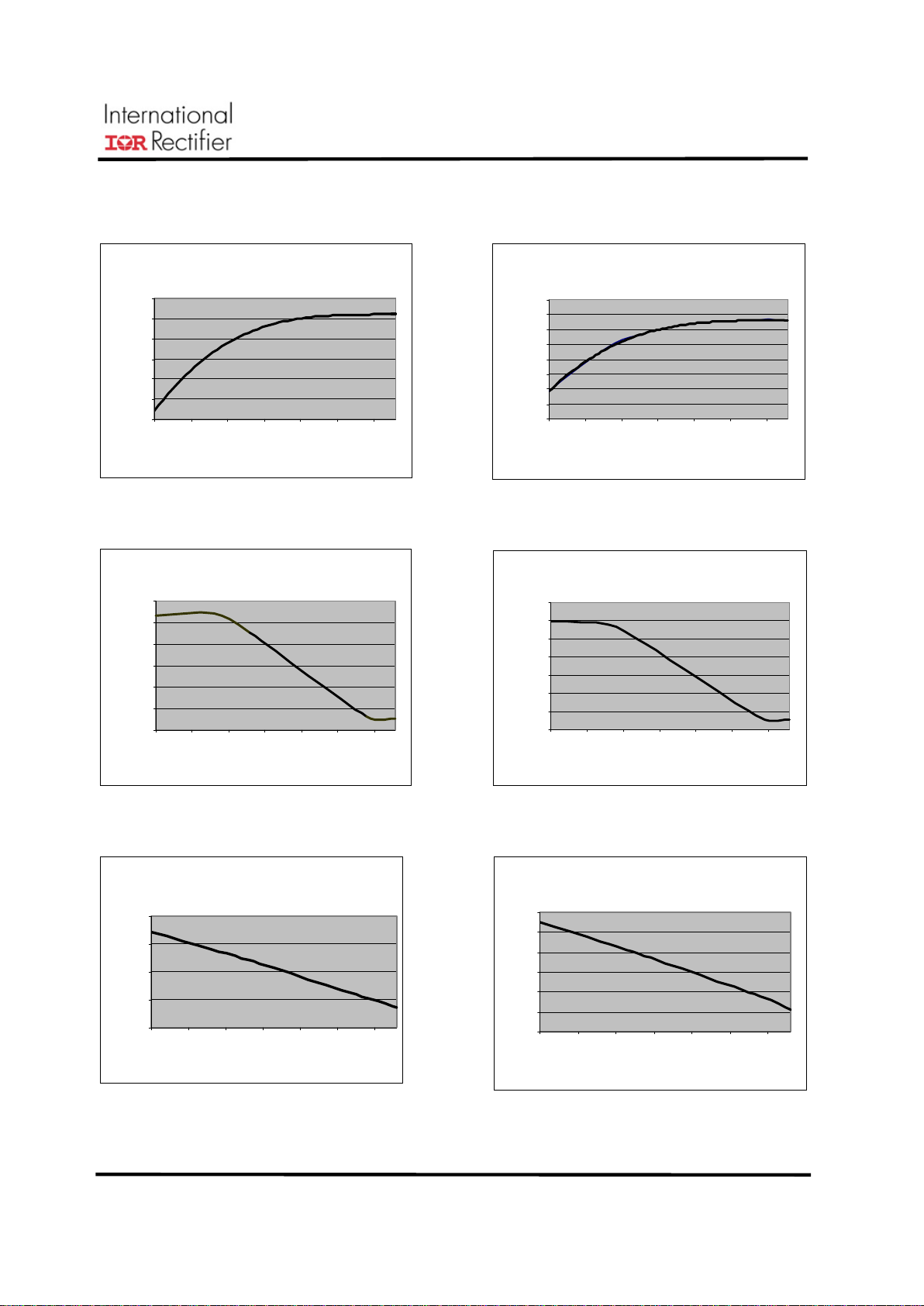

VFb1 vs Temperat ure

0.7975

0.798

0.7985

0.799

0.7995

0.8

0.8005

0.801

0.8015

0.802

-40-20 020406080100120

Temperature (C)

VFb1 (V)

VFb2 vs Temperature

0.7975

0.798

0.7985

0.799

0.7995

0.8

0.8005

0.801

0.8015

0.802

-40 -15 10 35 60 85 110

Temperature (C)

VFb2 (V)

SS1 Current vs Temperature

-25

-24

-23

-22

-21

-20

-19

-40 -15 10 35 60 85 110

Temperature (C)

SS1 Current (uA)

SS2 Cu rrent vs Temperature

-25

-24

-23

-22

-21

-20

-19

-40 -15 10 35 60 85 110

Temperature (C)

SS2 Cu rrent (uA)

Vcc_UVLO vs Temperature

7.1

7.12

7.14

7.16

7.18

7.2

7.22

7.24

7.26

7.28

7.3

-40 -15 10 35 60 85 110

Temperature (C)

Vcc_UVLO (V)

Vo ut3 vs Temperature

7.05

7.07

7.09

7.11

7.13

7.15

7.17

7.19

7.21

7.23

7.25

-40 - 15 10 35 60 85 110

Temperature (C)

VO ut3 (V)

TYPICAL OPERATING CHARACTERISTICS (-40oC-125oC)

IR3622MPbF

www.irf.com

9

I OCSET1 vs Temperature

19

19.5

20

20.5

21

21.5

22

-40 -1 5 10 35 60 85 110

Temperature (C)

IOC SET1 (u A)

IOCSET2 v s Temp erat ure

18

18.5

19

19.5

20

20.5

21

21.5

22

-40 - 15 10 35 60 85 110

Temperature (C)

IOCSET2 (uA )

GM 1 vs Temperatu re

3400

3500

3600

3700

3800

3900

4000

-40 -15 10 35 60 85 110

Temperature (C)

GM1 (umho)

GM2 vs Temp erat u re

3400

3500

3600

3700

3800

3900

4000

4100

-40 -15 10 35 60 85 110

Temperature (C)

GM2 (umho)

Freq 300KHz vs Temperatu re

280

290

300

310

320

-40 -15 10 35 60 85 110

Temperature (C)

Freq (KHz)

Max D uty Cycle vs Temperature

84

86

88

90

92

94

96

-40 -15 10 35 60 85 110

Temperature

Max D uty C y cle (%)

TYPICAL OPERATING CHARACTERISTICS (-40oC-125oC)

IR3622MPbF

www.irf.com

Circuit Description

10

THEORY OF OPERATION

Introduction

The IR3622 is a versatile device for high

performance buck converters. It consists of two

synchronous buck controllers which can be

operated either in two independent outputs mode

or in current share single output mode for high

current applications.

The timing of the IC is provided by an internal

oscillator circuit which generates two 180

o

-out-ofphase clock signals that can be externally

programmed up to 600kHz per phase.

Under-Voltage Lockout

The under-voltage lockout circuit monitors four

signals (Vcc, VcH1, VcH2 and Enable). This

ensures the correct operation of the converter

during power up and power down sequence. The

driver outputs remain in the off state whenever

one of these signals drop below set thresholds.

Normal operation resumes once these signals

rise above the set values. Figure 3 shows a

typical start up sequence.

Programmable Enable Input

The enable features another level of flexibility for

start up. The Enable has precise threshold which

is internally monitored by under-voltage lockout

circuit.

It’s threshold can be externally programmed to

desired level by using two external resistors, so

the converter doesn’t start up until the input

voltage is sufficiently high (see figure 3).

Vcc

7.2V

Vout3

Enable

Vbus

7.2V

11V

12V

12V

SS

3V

Enable OK (IC's POR)

Seq

Fig. 3: Normal Start up, Enable threshold is externally set to 11V

Seq pin is pulled to Vout3 prior to start up

Loading...

Loading...