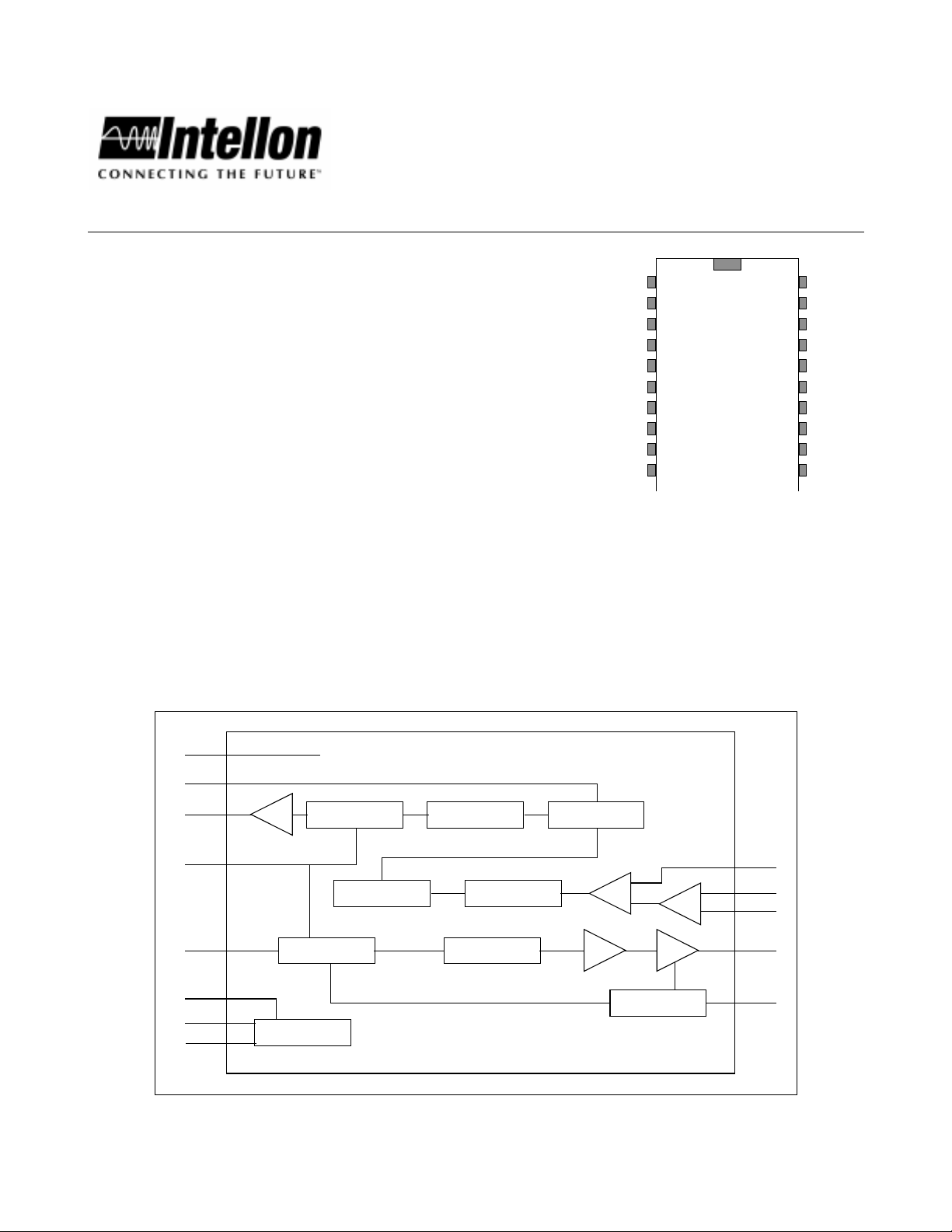

INTELLON SSCP485PL, SSCP485 Datasheet

Technical Data Sheet SSC P485 PL Transceiver IC

Features

VSS

201

18

17

16

15

14

13

12

11

TP0

VDD

SI

C1

C2 VDD

SO

VSS

RST*

TS*

D

A

A

•

Enables low-cost networking products

•

Spread Spectrum Carrier communication technology

•

9600 baud data rate

•

Simple interface

•

Single +5 Volt power supply requirement

•

20 pin SOIC package

4MHZ

NC

VSS

XIN

XOUT

ILD

DI

RO

WL

219

3

D

4

5

SSC

6

D

P485

7

8

9

10

Introduction

The Intellon SSC P485 PL Transceiver IC is a highly integrated spread spectrum comm unication transceiver for

implementing low-cost networking products. The SSC P485 contains a Spread Spectrum Carrier (SSC)

transceiver, signal conditioning circuitry, and a simple host interf ace. A m inimum of exter nal circuitry is required

to connect the SSC P485 to the DC power line, twisted pair cable, or other communication medium.

The inherent reliability of SSC signaling technology provides substantial improvement in network and

communication performance over other low-cost communication methods. The SSC P485 is the ideal basic

communications element for a wide variety of low-cost networking applications.

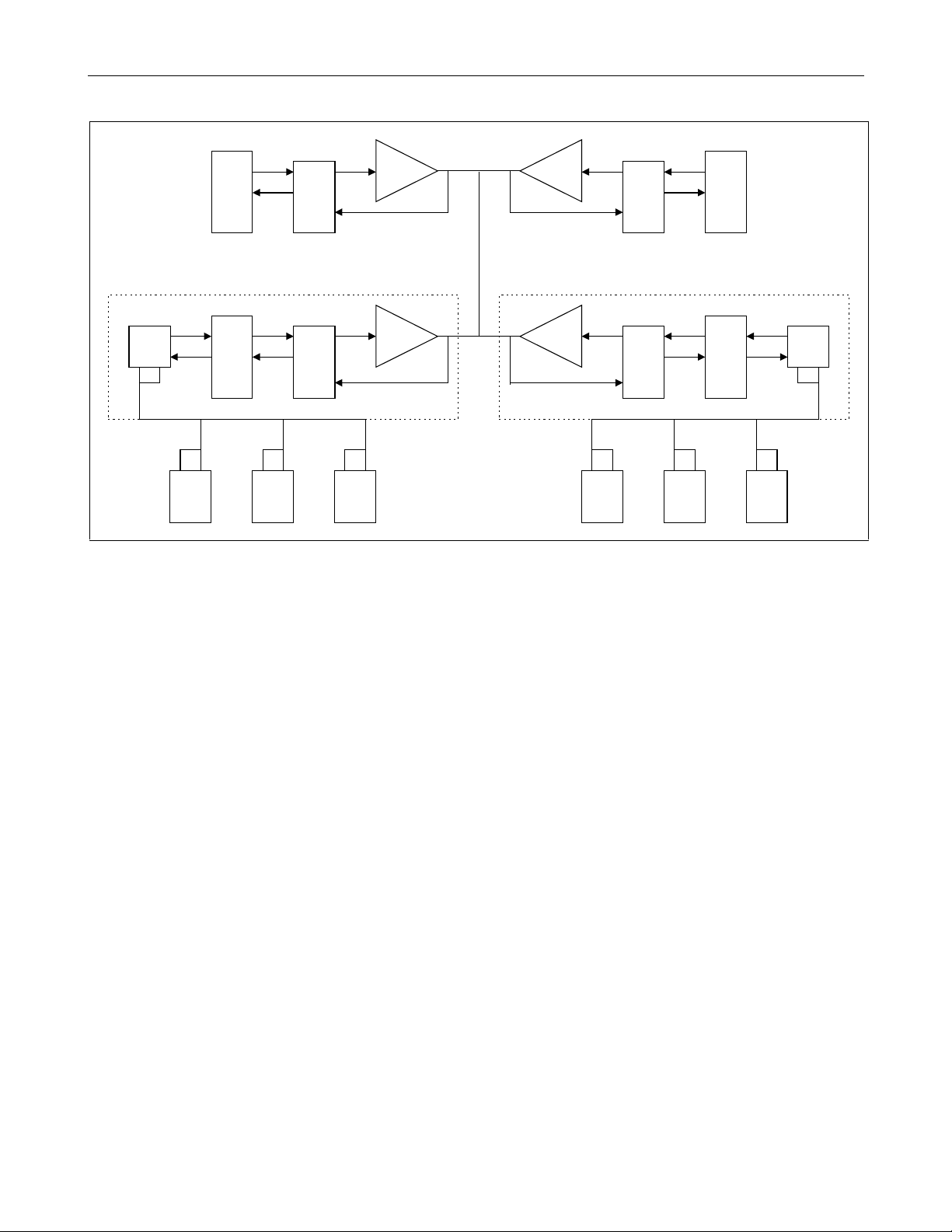

SSC P485 Block Diagram

RST*

ILD

RO

WL

4 MHz

XIN

XOUT

RX Interface Logic

Summation

Encoder

DI

TX Interface Logic

Clock Circui t

Data Decode

Logic

Binary Shift

Register

Waveform

Generator

Tracking & Data

Extraction Logic

Comp

DAC Buf

TS Control

Amp

C2

C1

SI

SO

TS*

July 1998 Revision 5

24000828

ADVANCE INFORMATION

SSC P485 PL Transceiver IC

Absolute Maximum Ratings (1)

Symbol Parameter Value Unit

V

DDMAX

T

V

STG

T

IN

L

DC Supply Voltage -0.3 to 7.0 V

Input Voltage at any Pin VSS-0.3 to VDD+0.3 V

Storage Temperature -65 to +150

Lead Temperature (Soldering, 10 sec onds) 300

Notes:

1. Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Recommended Operating Conditions

Symbol Parameter Min Typical Max Unit

V

DD

F

OSC

T

A

DC Supply Voltage 4.5 5.0 5.5 V

Oscillator Frequency

Operating Temperature -40 +25 +85

Humidity (non-condensing) 95 %

12 ± 0.05%

Electrical Characteristics

Conditions: VDD = 4.5 to 5.5 V T= -40 to +85°C

°C

°C

MHz

°C

Symbol Parameter Min Typical Max Units

V

OH

V

OL

V

IH

V

IL

I

IL

v

SO

I

DD

Minimum High-level Output Voltage 2.4 V

Maximum Low-level Output Voltage (1) 0.4 V

Minimum High-level Input Voltage 2.0 V

Maximum Low-level Input Voltage 0.8 V

Maximum Input Leakage Current

SSC Signal Output Voltage (2) 4 V

Total Power Supply Current 15 mA

±10 µA

Notes:

1. TS* pin I

2. Z

= 2K Ω || 10 pF

L

= 4 mA, all other outputs IOL = 2 mA

OL

P-P

July 1998 2 Revision 5

24000828

ADVANCE INFORMATION

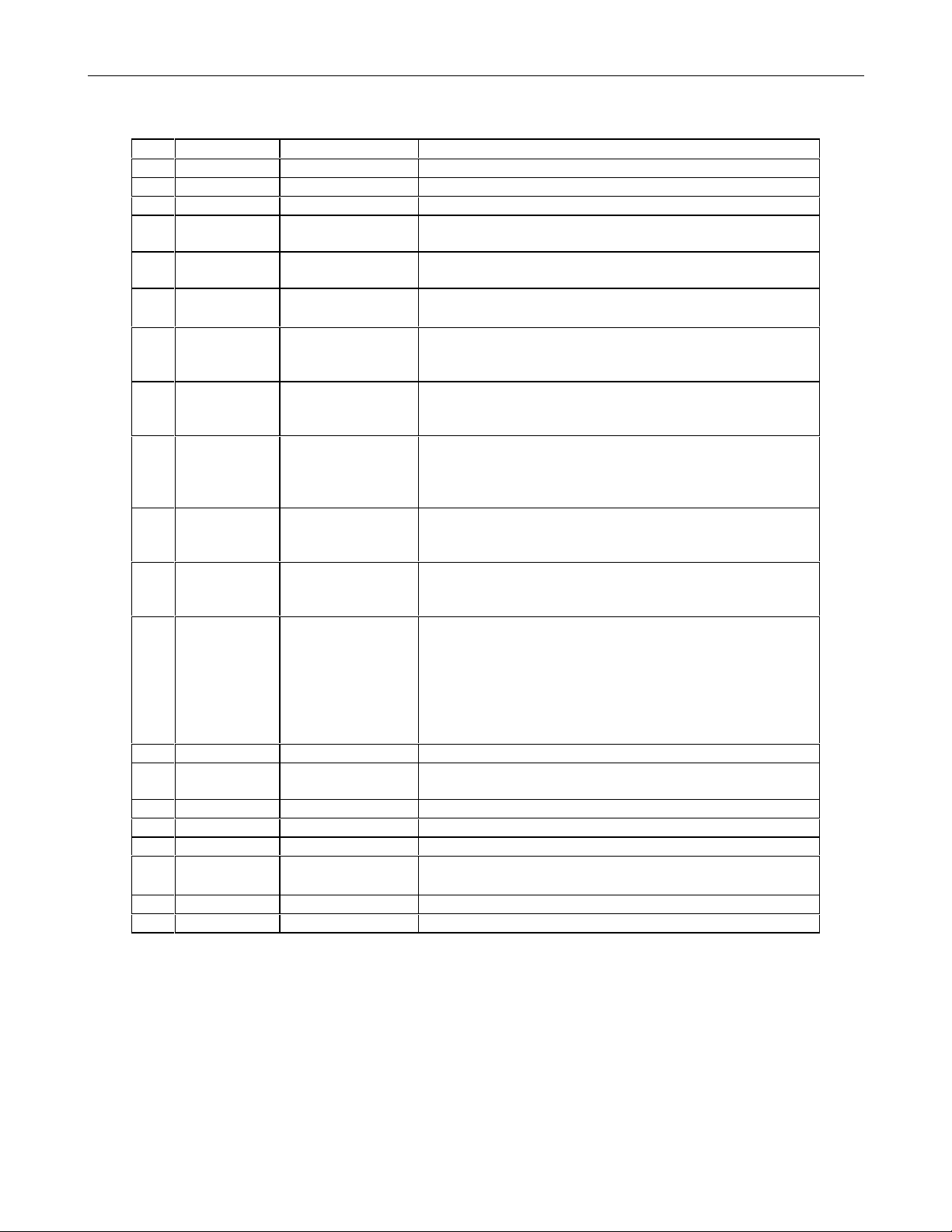

SSC P485 Pin Assignments

Pin Mnemonic Name Description

1 4MHZ 4 MHz Clock Out 4 MHz clock output available for host microcontroller.

2 NC No Connect

3 VSS

D

4 XIN Crystal Input Connected to external crystal to excite the IC’s internal

5 XOUT Crystal Output Connected to external crystal to excite the IC’s internal

6VDD

D

7 ILD Idle Line Detect Digital output, active high. Logic 1 state indicates 10 bit

8 DI Driver Input Digital input. After the preamble, a low on DI (SPACE)

9 RO Receiver Output Digital output. After the preamble and assuming

10 WL Word Length Digital input. Logic 1 (default, internal pullup) selects

11 TS* Tristate Active low digital output. Enables the external output

12 RST* Reset Active low digital input. RST* asynchronously forces

13 VSS

A

14 SO Signal Output Analog signal output. Tri-state enabled with internal

15 C2 Capacitor 2 Connection for 680pF capacitor to ground.

16 C1 Capacitor 1 Connection for 680pF capacitor to ground.

17 SI Signal Input Analog signal input.

18 VDD

A

19 TP0 Test Point 0 Reserved pin for testing.

20 VSS

D

Digital Ground Digital ground reference.

Digital Supply

Analog Ground Analog ground reference.

Analog Supply

Digital Ground Digital ground reference.

SSC P485 PL Transceiver IC

oscillator and digital clock.

oscillator and digital clock.

5.0 VDC ± 10% digital supply voltage with respect to

VSS

.

D

times of idle line, logic 0 indicates detection of carrier or

non-idle line.

transmits a superior2 state on SO, a high on DI (MARK)

transmits a superior1 state on SO.

standard polarity: if superior1 state is detected on SI,

RO will be high (MARK), if superior2 state is detected

on SI, RO will be low (SPACE).

10-bit frame (START, eight data bits, STOP), logic 0

selects 11-bit frame (START, nine data bits, STOP).

amplifier when driven high. Tri-states the external

output amplifier when driven low.

RO and ILD outputs to a high state and TS* to a low

state. RST* can be asserted anytime during normal

operation to force the reset state. RST* must be active

(low) for 1 µsec after VDD

crystal oscillator stabilizes to guarantee the internal

reset state. See Figure 10.

signal.

5.0 VDC ± 10% analog supply voltage with respect to

VSS

.

A

and VDDA stabilize and the

D

July 1998 3 Revision 5

24000828

ADVANCE INFORMATION

SSC P485 PL Transceiver IC

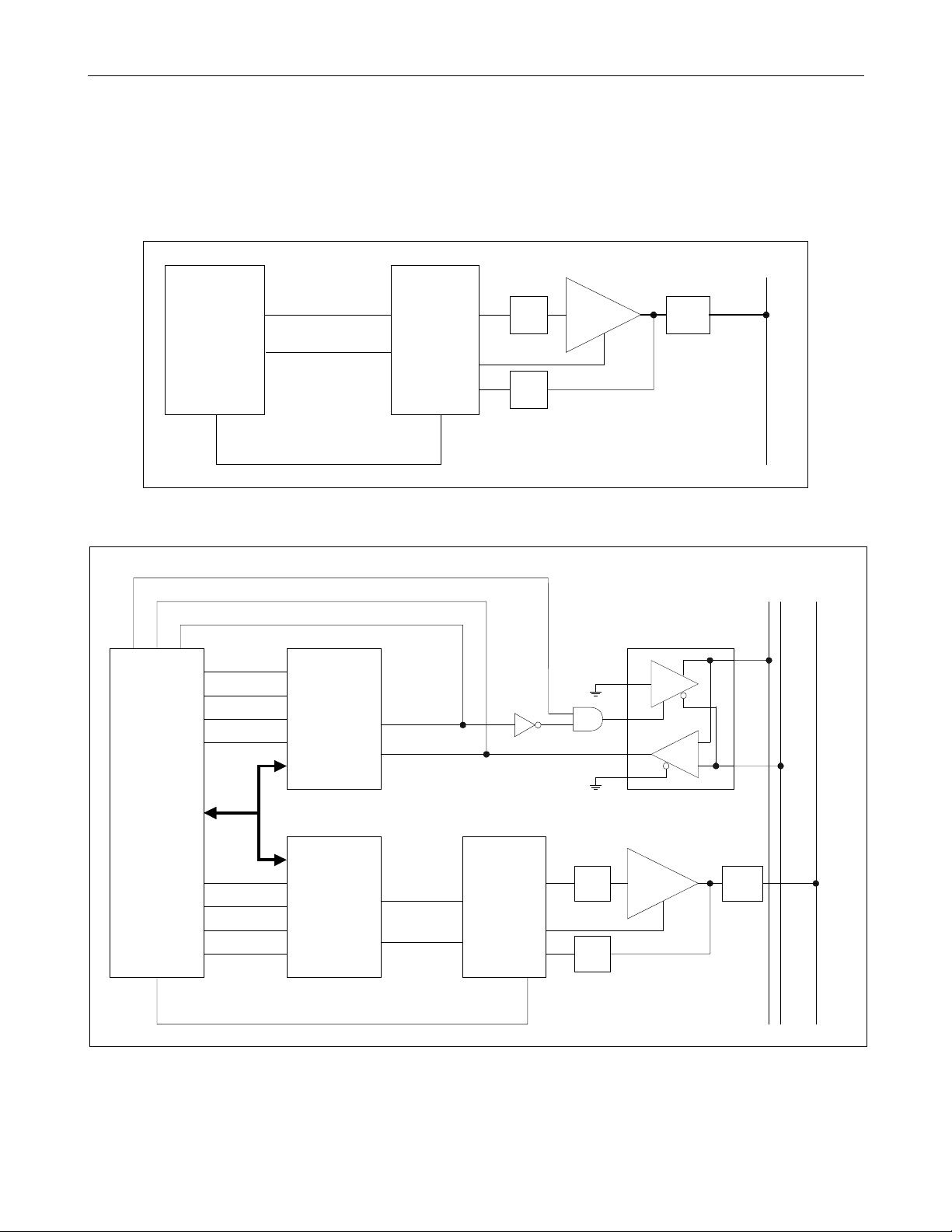

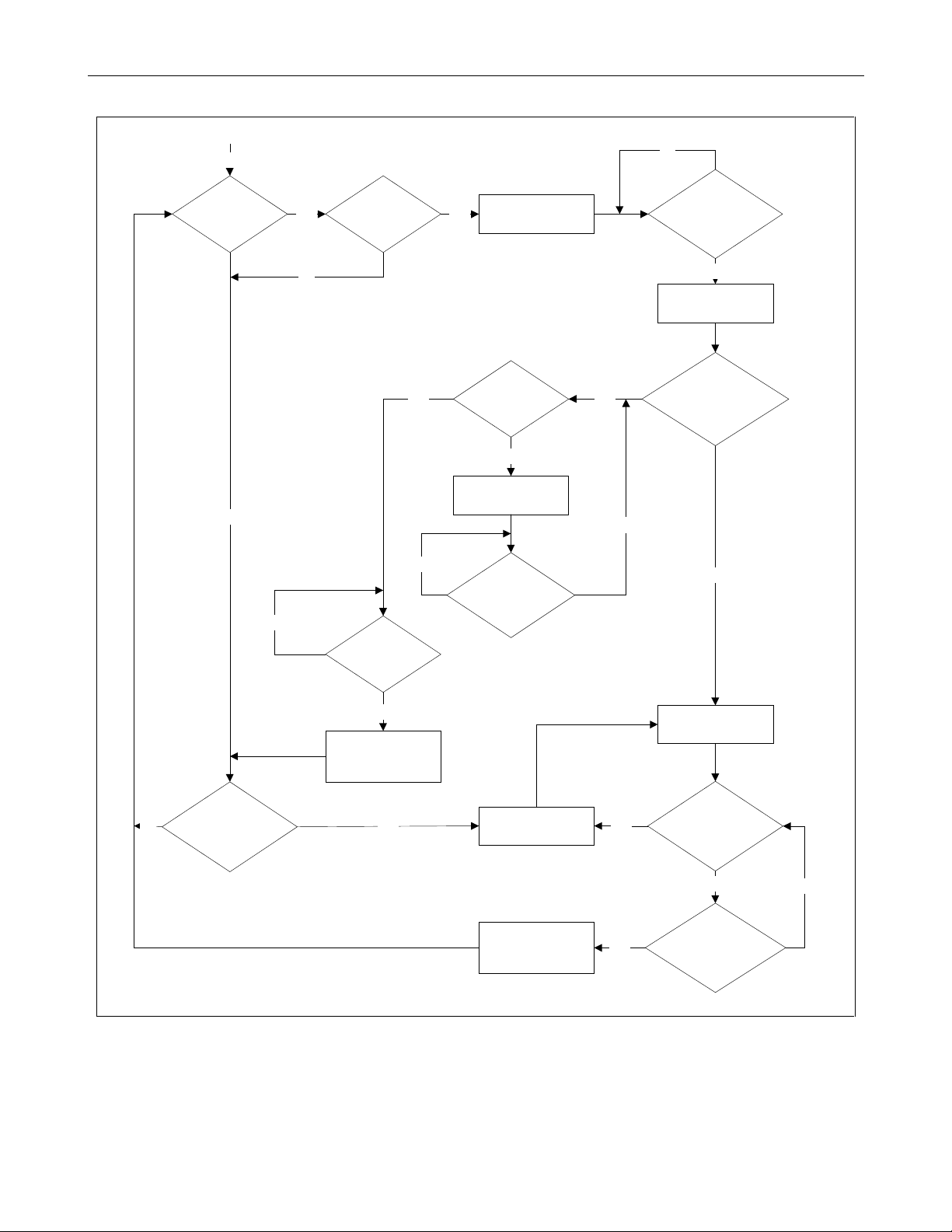

SSC P485 Application Examples

The SSC P485 may be used in a wide variety of applications. A typical node connecting to the medium is shown

in Figure 1. A gateway between an RS485 twisted pair network and a DC power line network is s hown in Figure

2. A multi-point network application with gateways using the SSC P485 is illustrated in Figure 3. Figure 4

presents a host interface f low diagram showing the major steps necessary to transmit and rec eive messages

using the P485 IC.

Single

Wire

Microp rocessor

based Control

Logic

Transmit Enable #1

RXD #1

TXD #1

TXRDY #1

RXRDY #1

RD #1

WR #1

WR

RD

ILD

DI

SSC P485 PL

RO

Transceiver

SO

output

filter

SI

input

filter

Figure 1. SSC P485 Typical Node

UART

TXD #1

RXD #1

SSC P111

Power Line Media

Interface

TS*

medium

coupler

RS-485 Tra n sce iver

D

DE

R

RE*

+

-

Twisted

A

B

Pair

Single

Wire

Microprocessor

based Control

DATA 0-7

Logic

RD #2

WR #2

TXRDY #2

RXRDY #2

ILD

UART

TXD #2

RXD #2

SO

output

DI

SSC P485 PL

Transceiver

RO

SI

ILD

filter

input

filter

SSC P111

Power Line Media

Interface

TS*

medium

coupler

Figure 2. SSC P485 Gateway

July 1998 4 Revision 5

24000828

ADVANCE INFORMATION

SSC P485 PL Transceiver IC

RS485

IC

RS485

device

P111

RS485

device

IC

P111

IC

host

micro

gate

way

micro

P485

IC

gateway gateway

P485

IC

RS485

device

DC power line

P111

P111

IC

P485

IC

IC

P485

IC

RS485

device

Figure 3. SSC P485 Multi-point Network Application

RS485

device

host

micro

gate

way

micro

RS485

IC

RS485

device

July 1998 5 Revision 5

24000828

ADVANCE INFORMATION

SSC P485 PL Transceiver IC

Entry

message to

transmit?

No

No

No

ILD

==logic 1?Yes Yes

Yes

No

write 1st character to

UART

transmitted last

character?

No

write next character to

UART

UART indicate s

transmit buffer

available?

Yes

No

UART indicates

receive character

available?

Yes

read character from

UART

character

transmitted==character

received?

Yes

No

No

UART indicates

receive character

available?

ILD

==logic 1?

Yes

message h as been

transmitted

Yes

read character from

UART

process messag e Yes

Yes

Figure 4. Host Interface Flow Diagram

store character in

message

UART indicates

receive character

available?

No

1-1/2 char times

of quiet since last

character?

No

July 1998 6 Revision 5

24000828

ADVANCE INFORMATION

Loading...

Loading...