INTELLON SSCP300PL, SSCP300 Datasheet

January 1998 Version 1.1

Technical Data Sheet SSC P300 PL Network Interface Controller

Features

• Enables Low-cost CEBus compatible products

• EIA-600 (CEBus) Data Link Layer services

• EIA-600 Physical Layer transceiver

• Spread Spectrum Carrier Power Line technology

• SPI Host Processor interface

• Data Link, Controller, and Monitor modes

• Single +5 Volt power supply requirement

• 20 pin SOIC package

Introduction

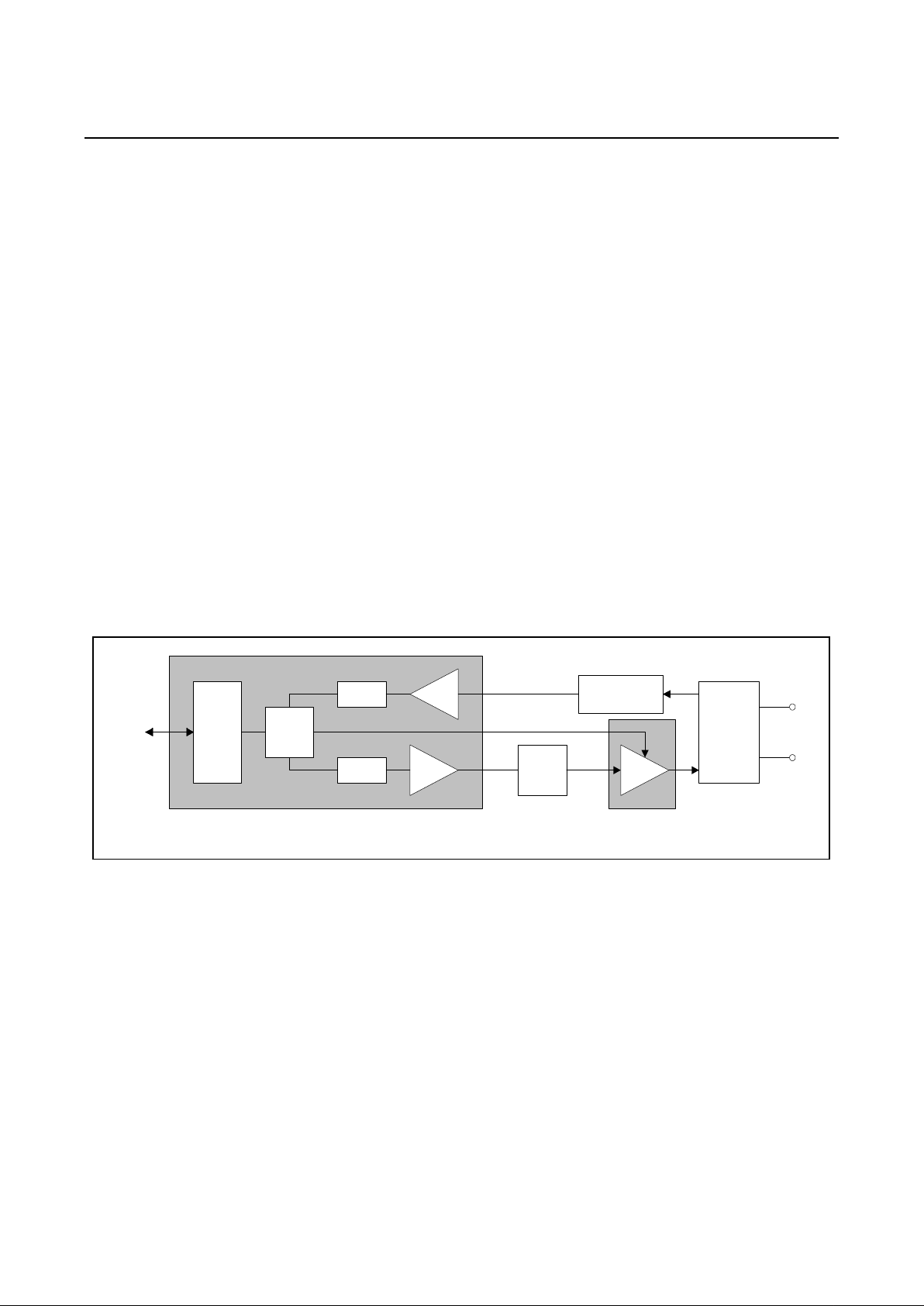

The Intellon SSC P300 PL Network Interface Controller is a highly integrated power line transceiver and

channel access interface for implementing CEBus compatible products. The SSC P300 provides the Data

Link Layer (DLL) control logic for EIA-600 channel access and communication services, a Spread

Spectrum Carrier (SSC) power line transceiver, signal conditioning circuitry, and a serial peripheral

interface (SPI) compatible host interface. A minimum of external circuitry is required to connect the SSC

P300 to the power line. Superior performance is achieved using the SSC P300 in conjunction with the SSC

P111 Media Interface IC. The SSC P300 is used with a host microcontroller to construct CEBus compatible

products, and serves as the basic communications element in a variety of low-cost power line networking

applications.

The inherent reliability of SSC signaling technology and incorporation of basic Data Link functionality

combine to provide substantial improvement in network and communication performance over other power

line communication methods. The SSC P300 also makes an excellent low cost network interface for twisted

pair and DC power systems. A typical CEBus power line node using the SSC P300 is illustrated below.

SSC P300 Node Block Diagram

Host

Micro

Application

I/O

DLL

Micro

Clk

Gen

Xcvr Amp

Buf

ADC

DAC

Osc

4 MHz

RST*

SDI

SDO

SCLK

CS*

INT*

3 MHz

12 MHz

AMP

Output

Filter /

TriState

Switch

Input

Filter

Line

Coupling

AC

Line

TS

SO

SI

Host

System

SSC P300 PL Network Interface Controller

Power Line Analog

Functions

SSC

P300

1

2

3

4

5

6

7

8

9

10

VSSD

TP0

VDDA

SI

C1

C2

SO

VSSA

RST*

TS

20

19

18

17

16

15

14

13

12

11

4 MHz

CS*

VSSD

XIN

XOUT

VDDD

INT*

SCLK

SDO

SDI

SSC PL P300 Network Interface Controller

January 1998 2 Version 1.1

Absolute Maximum Ratings

Symbol Parameter Value Unit

V

DD

DC Supply Voltage -0.3 to 7.0 V

V

IN

Input Voltage at any Pin VSS-0.3 to VDD+0.3 V

T

STG

Storage Temperature -65 to +150

°C

T

L

Lead Temperature (Soldering, 10 seconds) 300

°C

Note:

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. This device

contains protection circuitry to guard against damage due to high static voltages or electric fields. However,

precautions must be taken to avoid applications of any voltage higher than maximum rated voltages.

Recommended Operating Conditions

Symbol Parameter Min Typical Max Unit

V

DD

DC Supply Voltage 4.5 5.0 5.5 V

F

OSC

Oscillator Frequency 12 +/- 0.01% MHz

T

A

Operating Temperature -40 +25 +85

°C

Humidity non-condensing

Electrical Characteristics

Conditions: VDD = 4.5 to 5.5 V T= -40 to +85°C

Symbol Parameter Min Typical Max Units

V

OH

Minimum High-level Output Voltage 2.4 V

V

OL

Maximum Low-level Output Voltage (1) 0.4 V

V

IH

Minimum High-level Input Voltage 2.0 V

V

IL

Maximum Low-level Input Voltage 0.8 V

Hys Minimum Input hysteresis 350 mV

I

IL

Maximum Input Leakage Current +/-10

µA

v

SO

SSC Signal Output Voltage (2) 4 V

P-P

I

DD

Total Power Supply Current 25 mA

Latchup (3) 150 mA

Notes:

1. IOL = 2 mA

2. ZL = 2K Ω || 10 pF

3. JEDEC JC -40.2

SSC PL P300 Network Interface Controller

January 1998 3 Version 1.1

SSC P300 Pin Assignments

Pin Mnemonic Name Description

1 4MHZ 4 MHz clock out 4 MHz clock output available for host microcontroller.

2 CS* Chip select Digital input, active low. Enables serial peripheral interface.

3 VSS

D

Digital ground Digital ground reference.

4 XIN Crystal input Connected to external crystal to excite the IC’s internal

oscillator and digital clock.

5 XOUT Crystal output Connected to external crystal to excite the IC’s internal

oscillator and digital clock.

6 VDD

D

Digital supply 5.0 VDC +/- 10% digital supply voltage with respect to VSSD.

7 INT* Interrupt Digital output, active low. Attention request to host

microcontroller.

8 SCLK SPI data clock Serial peripheral interface clock input from host

microcontroller.

9 SDO SPI data out Data output to host microcontroller serial peripheral interface.

SDO is` tristate when CS* is false.

10 SDI SPI data in Data input from host microcontroller serial peripheral

interface.

11 TS Tristate Active low digital output signal driven from the same internal

signal that enables the output amplifier.

12 RST* Reset Active low digital input.

13 VSS

A

Analog ground Analog ground reference.

14 SO Signal output Analog signal output. Tristate enabled with internal TS signal.

15 C2 Capacitor 2 Connection for 680pF capacitor to ground.

16 C1 Capacitor 1 Connection for 680pF capacitor to ground.

17 SI Signal input Analog signal input.

18 VDD

A

Analog supply 5.0 VDC +/- 10% analog supply voltage with respect to

VSSA.

19 TP0 Test point 0 Reserved pin for testing.

20 VSS

D

Digital ground Digital ground reference.

SSC PL P300 Network Interface Controller

January 1998 4 Version 1.1

SSC P300 Node Overview

The SSC P300 is designed to meet the needs of products requiring EIA-600 compatibility. As the SSC P300

uses fewer interface signals than the SSC P400 does, a lower cost host (microcontroller) may be used.

Coupling the lower cost host with the low cost of the SSC P300, an EIA-600 compliance node can be added to

cost sensitive products. The SSC P300 can transmit and receive all four Data Link services defined in the EIA600 standard, which allows the designer to select the best Data Link service for the job.

As seen in the block diagram on page 1, a typical node consists of three sections: The first section is the host

microprocessor or microcontroller, which is responsible for communicating with the SSC P300 and performing

application specific tasks. The second section is the SSC P300 itself. It is responsible for resource intensive

Data Link functions and Physical layer services of the protocol. Specific DLL services include transmission and

reception of packets, byte-to-symbol conversion for transmitted packets, symbol-to-byte conversion for

received packets, transmit channel access (based on packet priority and EIA-600 access rules), and CRC

generation and checking. The last section is the power line analog functions. These functions include: coupling

the signal frequencies onto the medium, amplification of the transmitted signal to drive the impedance of the

medium, and input filtering of the incoming signal.

The host communicates with the SSC P300 by issuing commands. These commands provide for the

initialization and verification of the node’s operating mode and addresses, for the transmission and reception of

packets, and for the return of status information. In general, the host must provide the following functions in

order to utilize the SSC P300:

1. Initialization routine.

2. Routine to write commands out to the chip.

3. Routine to read data from the chip.

4. Interrupt service routine.

The SSC P300 can be placed into one of three operating modes: Data Link Layer (DLL) mode, Controller

(CON) mode, and Monitor (MON) mode. In the DLL mode, the P300 will manage all address matching, and

timer resources. In the CON mode, the P300 converts the incoming signal into bytes. It becomes the

responsibility of the host to manage address matching and timer resources. The MON mode monitors the

medium. Any packet detected on the medium is passed up to the host regardless of the packet’s address or

type.

DLL Mode

The DLL mode supports the standard CEBus Data Link Layer functionality at the Logical Link Sublayer.

(See Table 1). Most DLL mode functions directly map to the primitives specified in the CEBus Logical Link

Sublayer specification. Detailed control and status information is also provided. The P300 supports all four

Data Link services: Unacknowledged, Acknowledged, Addressed Unacknowledged, and Addressed

Acknowledged services. The DLL mode is selected by writing a value of 00 to the Service_Level field of

Mode_Control byte in the Layer_Config_Info structure. See the section “P300 Data Structures” later in this

document.

Table 1. EIA-600 Device Functionality

EIA-600 Data Link Layer Function Description P300 Implementation

Transmit and receive all of the Data Link layer packet types:

ACK_DATA, UNACK_DATA, ADRACK_DATA and

ADRUNACK_DATA.

One receive and one transmit address sequence number

association is maintained.

Maintain and supply system and node addresses and layer system

management parameters as requested from a higher layer.

Address and layer management parameters are volatile.

Restoration following power loss is the responsibility of the

attached host processor.

Recognize own system and node addresses and the broadcast

address (destination system and node addresses = 0x0000, or

destination system address = own system address and destination

node address = 0x0000).

Fully implemented.

Recognize group addresses. One group address is supported.

SSC P300 PL Network Interface Controller

January 1998 5 Version 1.1

Receive Packet Procedure in DLL Mode

The following assumes a valid correctly addressed packet has been received. The various packet

receive conditions are given below. References to Rc_Dest_Address and Rc_Source_Address refer to

the respective four bytes comprising the Rc_Dest_Device_Code and Rc_Dest_House_Code, and the

Rc_Source_Device_Code and Rc_Source_House_Code as found in the Receive_Header data

structure.

Host Interaction for Packet Reception in DLL Mode

Packet acceptance is posted for the host processor by using the Rc_Attn and Rc_Except flags in the

Interface_Flags byte. The host uses the Interface_Flags to determine what action to take to service the

SSC P300. When Rc_Attn flag is TRUE, the SSC P300 generates a host processor interface attention

signal to asynchronously alert the host that service is required for a received packet. Rc_Attn is set to

TRUE for all received packets accepted and not discarded due to refusal, overrun or duplicate receipt.

The Rc_Except flag is also set if an ACK_DATA or ADRACK_DATA packet was refused, an

UNACK_DATA or ADRUNACK_DATA packet overrun occurred, or if the current receive packet has a

different source and/or destination address than the previous receive packet. DLL_Rc_Link_Status data

structure may be accessed to determine the cause of the Rc_Except flag assertion.

A packet that is accepted and not discarded as a duplicate will cause the buffered

Receive_Header_Info structure (Control field, Destination address and Source address) to be updated

from the corresponding fields of the current Receive_Header_Info structure. If no packet is pending,

that is the host has read all packets, then the Receive_NPDU_Field structure is updated to complete

the reception of the packet.

Whether or not discarded as a duplicate, an accepted ADRACK_DATA/ACK_DATA packet results in

the SSC P300 sending an ADRIACK/IACK acknowledgment.

Packet Acceptance or Refusal

The following describes the conditions under which a valid correctly addressed packet is accepted or

refused/rejected.

Packet Refusal and Overrun

The following describes the conditions under which a valid correctly addressed packet is

refused. If the previously received packet has not yet been serviced by the host, any incoming

ACK_DATA or ADRACK_DATA packet will be refused and Rc_Refused will be posted in

DLL_Rc_Link_Status structure. Any incoming UNACK_DATA or ADRUNACK_DATA packet

will cause an Rc_Overrun to be posted in DLL_Rc_Link_Status structure. A packet which

produces a refuse or overrun condition does not affect the current receive sequence timer. An

ADRACK_DATA/ACK_DATA packet that is refused results in an ADRIACK/FAILURE (busy)

packet being returned to the source. The source then knows that delivery was unsuccessful

and, if able, can retry the transmission.

Receive Sequence Timer Expired

If the receive sequence timer has expired, the packet will be accepted. If the received packet

was ACK_DATA or UNACK_DATA, the receive sequence timer is left clear (zero). If the

received packet was ADRACK_DATA or ADRUNACK_DATA, the receive sequence timer is

reset to approximately 937 ms (1.25 times the Maximum Receive Time-out value of 750 ms).

Receiver Sequence Timer Not Expired

Same Source and Destination Address - If the receive sequence timer is not expired, but the

received packet is ADRACK_DATA or ADRUNACK_DATA with a source and destination

address that matches the previously received packet, the packet is accepted. The packet is

then checked for a duplicate by using the received packet’s sequence number. If the received

packet sequence number matches the previously received sequence number, the received

packet is a

SSC P300 PL Network Interface Controller

January 1998 6 Version 1.1

duplicate and is discarded. If discarded, the receive sequence timer is not modified. If the

packet is not a duplicate and is accepted, the receive sequence timer is reset to 937 ms.

Different Source or Destination Address - If the received packet was ACK_DATA or

UNACK_DATA, and the receive sequence timer is expired, the packet will be refused

(ACK_DATA) or overrun will occur (UNACK_DATA). The appropriate flag (Rc_Refused or

Rc_Overrun) will be posted. If the received packet is ADRACK_DATA or ADRUNACK_DATA

and, if the received source address and/or the destination address does not match the

respective previously received packet addresses, the packet will also be refused

(ADRACK_DATA) or overrun will occur (ADRUNACK_DATA). The appropriate flag

(Rc_Refused or Rc_Overrun) will be posted.

Transmit Packet Procedure in DLL Mode

The host processor is responsible for determining that no outstanding transmission is in progress before

requesting a new packet transfer and transmission (see section, Posting Packet Transmission Status

below). The SSC P300 supports only a single buffered transmit packet so that the previous

transmission must be complete before a new packet can be transferred from the host.

Packet transmission can be accomplished by writing a complete packet with the PT command, or by

using a combination of the WTH and WTI commands that transfer the Transmit_Header_Info structure

(LPDU header) and Transmit_NPDU_Field structure (NPDU packet body) respectively.

The P300 uses a transmit destination association sequence timer to insure that new packets are not

sent to a device whose receive time-out may not yet have expired from a previous transfer from this

node. Thus packets sent to a new or different address may be delayed by the DLL waiting for the

expiration of the transmit sequence timer. Successive packets to the same destination address,

however, will be sent without incurring possible transmit sequence time-out delays. The P300

determines implicitly from the particular transmit commands used by the host processor if a packet with

a (potentially) new destination address is to be transmitted. A command that writes the packet header

containing the destination address (i.e., WTH or PT) is assumed to contain a change in the packet

destination address. If, however, only the packet body (NPDU) is written by a command (i.e., WTI),

then the packet must necessarily be to the same destination address using the same packet header as

the last packet transmitted.

The use of WTI commands following an initial WTH or PT commands are recommended, especially for

ADRACK_DATA or ADRUNACK_DATA type packets. This will allow the maximum transfer rate when

sending multiple packets to the same device by using multiple WTI commands following the initial

WTH or PT command. ACK_DATA or UNACK_DATA type packets do not set the transmit sequence

timers, but the previous transmit sequence timer value must be zero before the P300 initiates the

ACK_DATA or UNACK_DATA transmission.

The SSC P300 can process two packets: one that is currently transmitting and one in the buffer. A third

packet cannot be sent to the SSC P300 until the transmit association timer for the first packet has

expired.

SSC P300 PL Network Interface Controller

January 1998 7 Version 1.1

Writing a Transmit Header

The host, using the WTH command, writes packet Transmit_Header_Info. Both the system and device

source address values transferred in the Transmit_Header_Info should normally be 0xFFFF, resulting

in the P300 substituting its current system and device address as the header packet source address.

The P300 assumes that writing a header with the WTH command changes the destination address,

therefore, actions are taken to preserve transmit time-outs. When the WTH command is executed, the

following steps occur:

1. If the transmit sequence timer is not expired, and the transmit service is addressed-type, the failure

REMOTE_BUSY_XMIT_LIST status is returned, and the WTH command is ignored.

2. If the transmit sequence timer is expired, or the transmit service is non-addressed-type, the data is

transferred to the P300; source addresses are substituted as required and control is returned to the

host.

3. The host may now transfer the Transmit_NPDU_Field and initiate packet transmission via the WTI

command (see Transmitting a Packet with an Existing Header below).

Transmitting a Packet with an Existing Header

To transmit a packet with a valid header previously transferred by a WTH or PT command, the

Transmit_NPDU_Field is written by the host with the WTI command. The existing

Transmit_Header_Info contents are used for the header of the packet to be transmitted. Subsequent

packets addressed to the same device (i.e., using the same Transmit_Header_Info) only require a WTI

command to send the new packet body (NPDU) portion of the subsequent packet. When the WTI

command is executed the following steps occur:

1. If the transmit sequence timer is not expired, and the transmit service is ADR-type, the failure

REMOTE_BUSY_XMIT_LIST status is returned, and the WTI command is ignored. If the transmit

sequence timer is expired, or if the transmit service is non-ADR-type, the packet body data are

transferred to the P300 and control is returned to the host. If the packet is ADRACK_DATA or

ADRUNACK_DATA, the Tr_Seq_# is incremented, and inserted in the transmit header. The Tr_Seq_#

is a Data Link parameter and completely maintained by the P300. If the P300 automatically generates

duplicate packets based on CH_ACCESS_NUM (for ADRUNACK_DATA packets), the same Tr_Seq_#

value will be used for all subsequent copies of the same packet. Thus, if more than one packet is

received at the destination, the duplicates can be eliminated.

2. The Tr_Except flag is set to indicate transmission in process.

3. When the packet transmission starts (i.e. the channel access protocol has been satisfied) and if the

packet is an ADRACK_DATA or ADRUNACK_DATA type, the transmit sequence timer is loaded with

1125 ms. On any subsequent retransmission of an ADR-type packet, due to ADRIACK (remote busy) or

the CH_ACCESS_NUM parameter, the transmit sequence timer is reloaded with 1125 ms.

4. Upon transmission completion, Tr_Attn is asserted. Tr_Except will reflect the success or failure of

the transmit process.

SSC P300 PL Network Interface Controller

January 1998 8 Version 1.1

Transmit Complete Packet

To transmit a complete packet with a single command, the Transmit_Header_Info and

Transmit_NPDU_Field are written consecutively by the host with the PT command.1 When the PT

command is executed the following steps occur:

1. The transmit header and packet body data is transferred to the P300, source address substitution is

made as required and control is returned to the host. If the packet is an ADRACK_DATA or

ADRUNACK_DATA, the Tr_Seq_# is incremented, and inserted in the transmit header. The

Tr_Seq_# is a Data Link parameter and completely maintained by the P300. If the P300

automatically generates duplicate packets based on CH_ACCESS_NUM (for ADRUNACK_DATA

packets), the same Tr_Seq_# value will be used for all subsequent copies of the same packet.

Thus if more than one packet is received at the destination, the duplicates can be eliminated.

2. The Tr_Except flag is set to indicate transmission in process.

3. The P300 then waits for the transmit sequence timer to reach zero (the transmit sequence timer

may have a residual value due to the previous transmission of an ADRACK_DATA or

ADRUNACK_DATA packet), if it has not already done so. When the transmit sequence timer has

expired, the transmission process begins.

4. When the packet transmission starts (i.e. the channel access protocol has been satisfied) and if the

packet is an ADRACK_DATA or ADRUNACK_DATA type, the transmit sequence timer is loaded

with 1125 ms. (1.5 times the Maximum Receive Time-out value of 750 ms.)

5. Upon transmission completion, Tr_Attn is asserted. Tr_Except will reflect the success or failure of

the transmit process.

ACK_DATA or UNACK_DATA Packet Transmission

Use of UNACK_DATA or ACK_DATA packet transmission is generally discouraged. The principal use

of such packet types can be for broadcast messages in which sequencing is unimportant, e.g. “hailing”.

UNACK_DATA and ACK_DATA packet transmissions do not set the transmit association timer, but

transmission of these types still require the expiration of any outstanding transmit association timer

value.

Posting Packet Transmission Status

In-progress, completion and success of a transmission are posted in the Interface_Flags, using the

Tr_Attn and Tr_Except flags. The host can interrogate these flags to determine what action is

necessary. The Tr_Attn flag is set TRUE when the transmit sequence timer becomes zero after a WTH

command is executed, or when a packet transmission, including multiple accesses, if specified, has

completed after a PT or WTI command. The Tr_Except flag is always TRUE when a packet

transmission is in progress following a PT or WTI command, or the transmit sequence timer has not

expired subsequent to a WTH command. Tr_Except is also set whenever Tr_Attn is set TRUE and a

transmit exception condition has occurred.

When the Tr_Attn flag indicates a packet transmission is complete, a new packet can immediately be

sent to the same destination address by using a WTI command. However, transmitting a packet to a

different (new) address may cause the P300 to wait until the current transmit sequence timer has

expired. The P300 assumes that executing a WTH command changes the destination address.

Consequently, execution of a WTH will set Tr_Except to TRUE and Tr_Attn to FALSE if the transmit

sequence timer has not expired. When the transmit sequence timer expires, Tr_Attn will then be posted

as TRUE. If the transmit sequence timer has already expired, Tr_Attn will be set TRUE immediately.

Thus a WTI command should not be executed to send the new packet after a WTH command until

Tr_Attn is set to TRUE.

1

A null length packet transfer with a PT or WTI command will retransmit the previous packet if transmission is not in process. Note that this is

equivalent to transmitting a completely new packet (i.e., Data Link sequence numbers are incremented), and consequently should not be used for

higher level CEBus (e.g. application) transmissions, as the new packet application level sequence information (i.e., Invoke ID number) is not

changed.

SSC P300 PL Network Interface Controller

January 1998 9 Version 1.1

If a packet write command (PT, WTI or WTH) is issued while the P300 has an outstanding transmission

in progress (Tr_Attn is FALSE and Tr_Except is TRUE), the command shall be ignored and an

Interface_Error flag will be posted in the Interface_Flags byte.

Host Processor Busy Processing

Host Processor Busy – The host Indicates that it does not have resources available to service a new

packet by setting the Host_Busy flag. If the Host_Busy flag is set TRUE by the host, the P300 will not

generate an attention sequence in response to a Rc_Attn or Tr_Attn condition. All ongoing Data Link

operations continue as normal, including any packet refusals or overrun conditions that may occur

during the period in which the host is busy. When the host leaves the busy condition and notifies the

P300 by setting the Host_Busy flag to FALSE, any pending receive or transmit conditions (Rc_Attn or

Tr_Attn) will cause an immediate attention sequence to be generated.

Upper Layer Busy - Indicates the host cannot process receive packets at this time. No attention

requests for received packets are generated (the first received packet is stored—subsequent received

packets are refused/ignored). Other attention requests (including transmit complete) are generated

normally. If an attention request is generated due to a non-"received packet" reason, but a packet has

been received, it is the responsibility of the host to either process the received packet immediately or

store the fact and process the received packet later. See the description in the Data Structures section

for information on the Interface_Flags. See the Attention Sequence section, which pertains to

processing all set flags.

Receive Association Limitation

One receive source association variable is provided by the P300. This limits the attached host to receiving

packets from only one source address and one destination address2 within any given receive time-out

period. ADRACK_DATA and ACK_DATA packets received from a different source address or going to a

different destination address are given a ADRIACK/FAILURE (busy) if the receive sequence timer has not

expired. ADRACK_DATA packets can subsequently (automatically) be retransmitted by the source, and so

are not lost. However, the source will not know to retransmit the ADRUNACK_DATA and UNACK_DATA

packets when the receive sequence timer or other busy condition is over. Consequently,

ADRUNACK_DATA and UNACK_DATA packets may be lost. An occurrence of a potentially “lost” packet is

noted by the P300 posting the Rc_Overrun flag in DLL_Rc_Link_Status structure and by setting the

Rc_Except flag in Interface_Flags to TRUE.

DLL Timing Constraints

In high traffic situations, the real time communication constraints of servicing the SSC P300 must be

considered. A worst case condition occurs when a second packet, addressed to the node, is being received

before the host has read the previous packet. In order to prevent packet overrun, the SSC P300 must be

serviced as soon and as quickly as possible. A typical calculation for the service turn-around time uses the

minimum quiet time between packets, a “typical” preamble, an IEOF, and null address fields. Adding up

these values yields a service turn-around time of approximately 4ms. This time should be adequate for

CEBus compliance cases.

Controller (CON) Mode

In this mode, a host may support communications to multiple devices simultaneously using the ADR-type

transmit services. This simultaneous device support requires the maintenance of separate transmit/receive

address associations for each device in the host process.

The CON Mode is selected by the value 11 in the Service_Level field of the Mode_Control byte in the

Layer_Config_Info structure.

Packet Receive in CON Mode

2

Four different destination addresses exist : 1) system address/node address, 2) system address/group address, 3) system address/broadcast

node address, and 4) broadcast system address/broadcast node address.

SSC P300 PL Network Interface Controller

January 1998 10 Version 1.1

Received packets are transferred to the host in a manner allowing the host to determine the addressing

status of the packet and manage the sequence number and association timers for source and

destination addresses. The notification of a received header is via Rc_Except in Interface_Flags. After

receiving the header via the RRH command and processing the Received_Header_Info structure, and

prior to the receipt of the CRC, the host makes a determination whether the packet can be accepted,

rejected, failed busy or ignored. This determination is based on the state of the received service,

sequence number, and receive association timer. The host must notify the P300 controller via

Rcv_Disposition in Node_Control structure as to the suitable disposition of the packet such that

appropriate action at the end of the packet can be performed, including sending an IACK packet. If a

Rcv_Disposition response is not received in time, the packet will be ignored. If the packet has been

accepted, the Rc_Attn is posted to notify the host of the receipt of the completed CRC (end of packet).

This information can be used by the host to manage the receive association timer. The received NPDU

is conveyed via the RRI (preferred) or PR command. The host is responsible for logging the received

NPDU event for association timer purposes.

Packet Transmit in CON Mode

The host sets up the address information for transmission, including the state of the sequence number,

and manages the transmit association timers. Information regarding actual channel access (beginning

of packet) will be passed to the host to assist in transmit association timer management via Tx_Except.

Re-transmission (immediate and multiple ADR-type accesses) are handled by the P300 controller,

based on the transmitting packet’s source address fields. Transmission completion is handled as

described for the DLL mode.

WTH and WTI are not recommended commands for transmitting in this mode, because WTI will

retransmit without changing the sequence number.

CON Timing Constraints

When a data packet is received, the host is responsible for determining the acceptance or rejection of

the packet before the NPDU is completely received. The worst case occurs when the ID packet is

received. In this case, the NPDU contains only one byte. This yields 1.2 ms for the host to acknowledge

the received packet after the attention sequence.

Monitor Mode

The MON Mode is selected by writing a value 10 in the Service_Level field of Mode_Control byte in the

Layer_Config_Info structure.

Packet Receive in MON Mode

In this mode, the SSC P300 will receive and forward to the host all packets on the channel. A packet

must have a legitimate start (IEOF), valid header, valid end (EOP) and valid CRC. No address or type

checking is done and packets addressed to this device will not be acknowledged or sequence number

checked. Further, all packets have the end of packet time (the time of the last UST of the CRC) logged,

which is readable by the host. This time is posted in internal clock cycles (1.5625 µs per count) and is in

a free-running 32-bit format.

Packet Transmit in MON Mode

Any packets transmitted in the MON mode will not be checked for type and will be transmitted as if they

were UNACK_DATA packets. The time of the last UST of the transmitted packet is also logged so that

all channel packet traffic timing is available to the host. If a packet type is transmitted that generates an

acknowledge from the receiver, the acknowledgment will be logged and forwarded to the host just like

any other packet received in the MON Mode. NOTE: Transmitting in MON mode is not recommended.

SSC P300 PL Network Interface Controller

January 1998 11 Version 1.1

MON Timing Constraints

The host must service the received monitor packets before the next packet on the channel is received

in order to avoid an overrun. In the worst case scenario, this means that in the monitor mode, the host

must respond to an attention sequence within about 1 ms and must be able to support the packet

transfer protocol at or near the maximum rate (see the section Signal Timing). If the response time

requirements cannot be met or the maximum transfer rate cannot be supported, received packets may

be lost and/or overwritten.

SSC P300 Power Line Interface

Analog data is transferred between the AC power line and the SSC P300 over the Signal In (SI) and Signal Out

(SO) pins. When transmitting, SSC “chirps” from the SSC P300 SO pin are routed to the output amplifier, which

is enabled by the SSC P300 Tristate (TS) signal. Once amplified, the output signal passes through a low-pass

output filter, which removes harmonic energy (distortion) from the transmit signal. The signal then passes to the

Tristate switch. This switch is enabled by the SSC P300 TS signal and serves to isolate the amplifier and filter

from the power line coupling circuit during receive operation. When the Tristate switch is enabled, the power

line communication signal is routed to the 60 Hz power line through the power line coupling circuit.

When receiving, the power line analog signal passes through the external power-line-coupling network to the

input filter. This bandpass filter passes the chirp frequency band (100 to 400 kHz) to the SSC P300 SI input.

The output amplifier provides the power necessary to drive the impedance of the power line. The output

amplifier is easily implemented using Intellon’s P111 PL Media Interface IC, as illustrated in Figure 1. The P111

provides greater signal output power than previous discrete designs and replaces as many as 30 discrete

components. This increases reliability and requires smaller board size than commonly used discrete

implementations.

DLL

Micro

Xcvr

A/D

D/A

Amp

Buf

Pre-

Filter

Amp

Host

SO

TS

SI

Discrete

Input Filter

TS

TXI

Line

Coupling

AC

Line

SSC P300 PL Network Interface Controller

SSC P111 PL

Media Interface

Figure 1. SSC P300 with P111 PL Media Interface IC

SSC P300 Host Interface

Host Signal Description

SSC P300 interface to the Host system is supported through a Serial Peripheral Interface (SPI) using five

I/O lines. A hardware, active-low, reset signal is also supplied by the host system. These signals are INT*,

CS*, SCLK, SDI, SDO, and RST*. Their description is given below:

INT* - The P300 pulls this line low whenever service from the host is required. The three most common

conditions that generate an interrupt are packet reception, packet transmission, and ready for next SPI byte

transfer.

CS* - The host pulls the chip select line low to start communication with the P300. This line remains low

during the read or write command operation, which is called a transaction. The host sets this line high when

the transaction is completed.

SSC P300 PL Network Interface Controller

January 1998 12 Version 1.1

SCLK - The host generates a clock signal to synchronize the data transfer. When the host is writing data,

the P300 reads the data on the rising edge of the clock. When the host is reading data, the P300 places

data on serial data output (SDO) pin on the falling edge of the clock and the host reads the data on the

rising edge of the clock. See section 6.0, Transaction Timing.

SDI - The data generated by the host is placed on this line and clocked into the P300. The data must be

valid on the rising edge of the clock.

SDO - The data generated by the P300 is placed on this line on the falling edge of the serial clock and is

valid on the rising edge of the clock. The setup and hold times for the P300 must be met if the data is to be

valid on the rising edge of the clock.

RST* - This signal line is pulled low to provide a hardware reset.

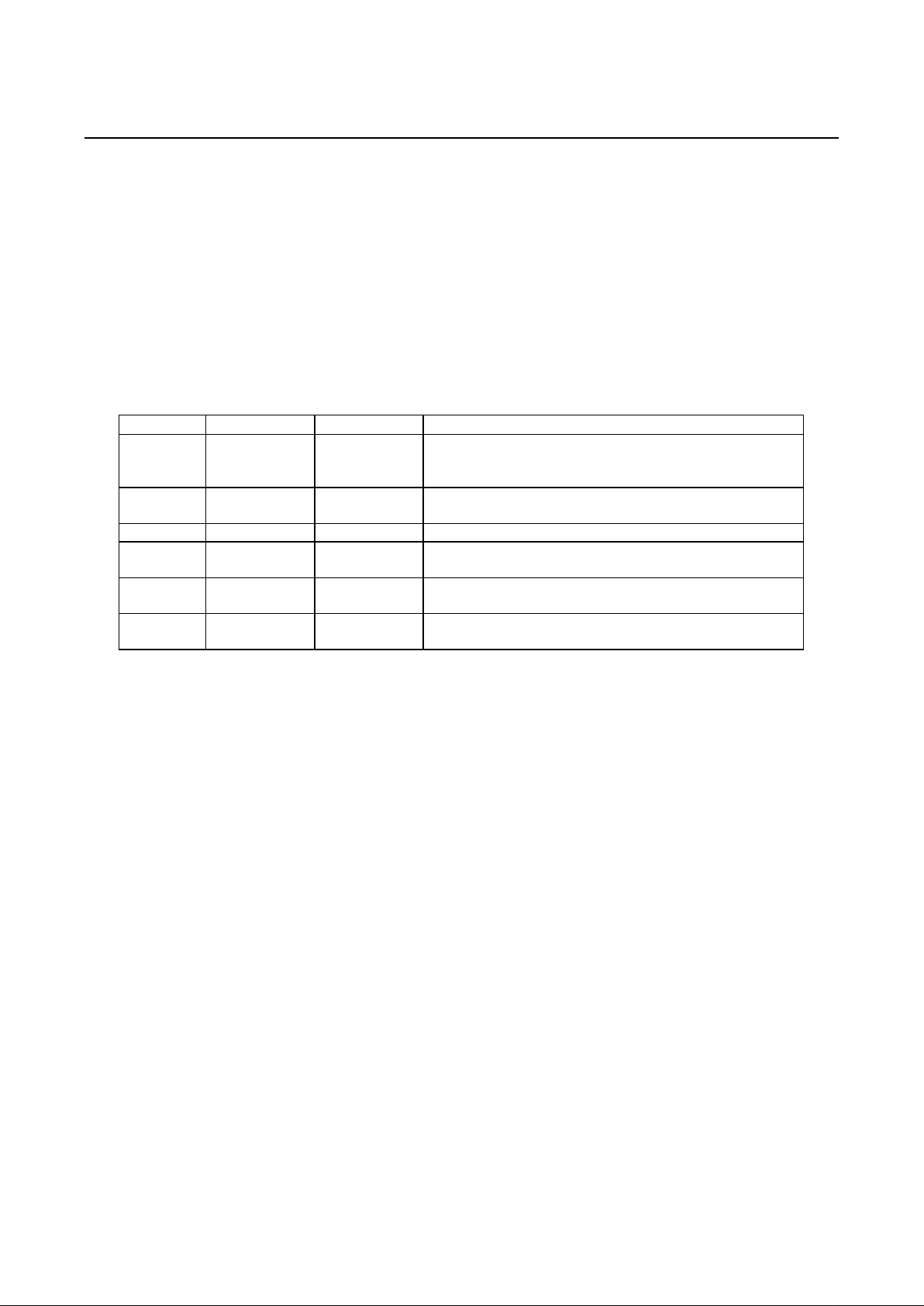

Table 2. Summary of SPI Pin Descriptions

Mnemonic Name Direction Use

INT* Interrupt Output Active low. Used to indicate an attention request

(packet received or transmit packet completed) or

"ready for SPI byte transfer."

CS* Chip Select Input Active low. Must be asserted during a read or write

command operation ("transaction").

SCLK Shift Clock Input Used to synchronize data transfer.

SDI Serial Data In Input Serial data input (normally connected to host's SDO

signal). Data is shifted MSB first.

SDO Serial Data

Out

Output Serial data output (normally connected to host's SDI

signal). Data is shifted MSB first.

RST* Reset Input Reset signal line. The host may assert this signal low

(open collector drive) to provide a hardware reset.

A simple protocol is used to transfer commands and data between the host and SSC P300. These

commands and data include packets to be transmitted, received packets, status and configuration

information.

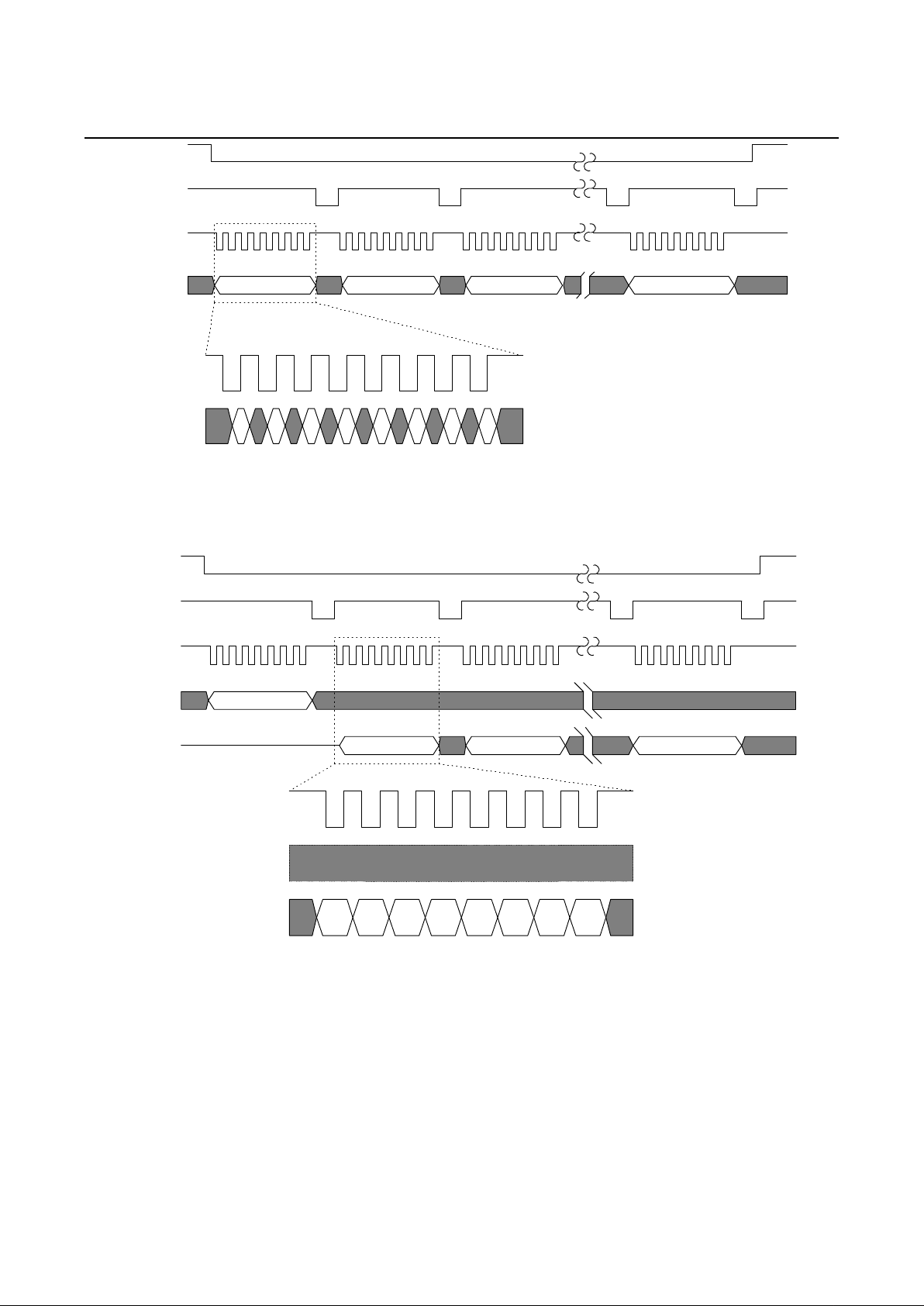

Command Format

The host processor and the P300 have a master/slave relationship. That is, the P300 cannot send data to

the host until commanded to do so. The P300 can only request service from the host, via the interrupt

signal. The host responds to the interrupt with a command that allows the SSC P300 to return its data.

Commands from the host allow the host to read or write the internal registers of the P300. These registers

are grouped together into data structures, which are used for configuring the chip, setting parameters of the

Data Link, returning status information, receiving packet information, and transmitting packets. See the

Commands section for more detailed information about the commands and their use. The command

formats are classified as either a write transaction or a read transaction. A write transaction is composed of

a command byte, a length byte, and the data bytes to be written into the data structure. A read transaction

causes the P300 to transfer data to the host from a data structure. When reading, the command byte is

sent from the host to the SSC P300. The SSC P300 will return a length byte followed by the data bytes

from the data structure. All SSC P300 system information is loaded by the host processor following the

procedure illustrated in Figure 2. All downloaded information is volatile and must be reloaded in case of a

power failure. Data is transferred from the SSC P300 using the read command format shown in Figure 3.

For timing information, see the section on Transaction Timing.

SSC P300 PL Network Interface Controller

January 1998 13 Version 1.1

Command byte Length byte = N Data byte # NData byte # 1

CS*

INT*

SCLK

SDI

b7b6b5b4b3b2b1b

0

Figure 2. Write Command Format

Command byte

CS*

INT*

SCLK

SDI

SDO

Length byte = N Data byte # NData byte # 1

b7 b6 b5 b4 b3 b2 b1 b0

Figure 3. Read Command Format

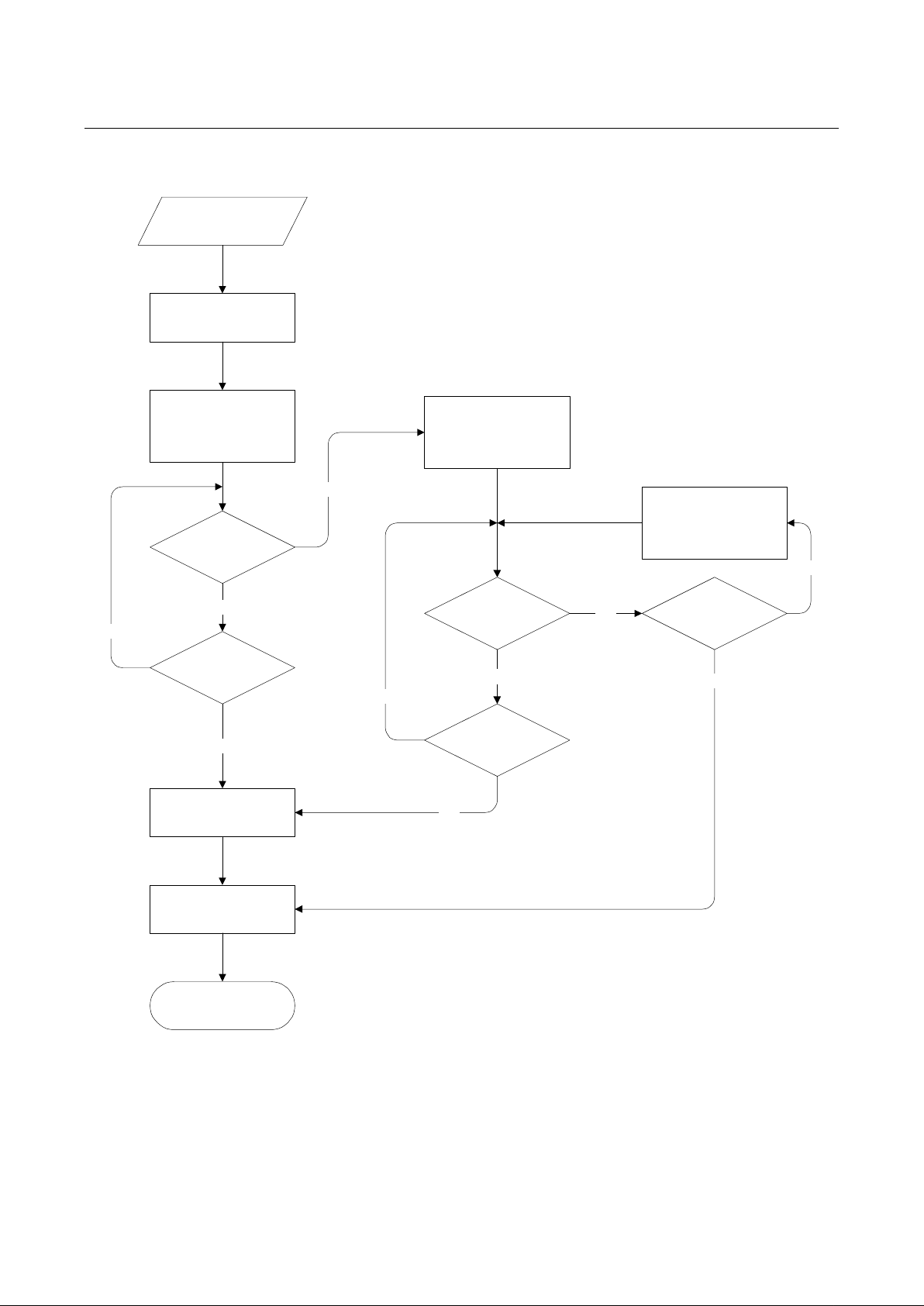

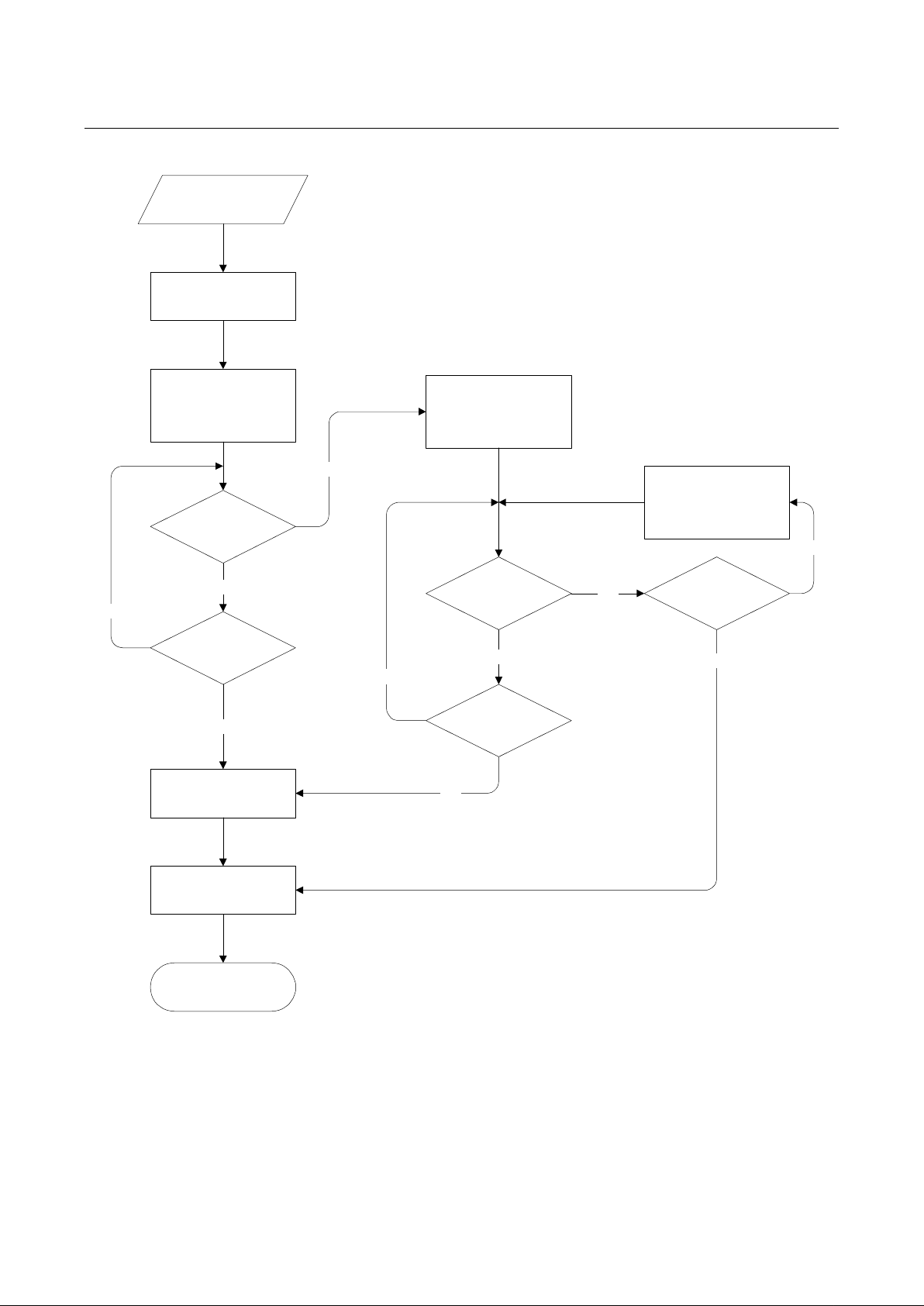

Flowcharts for write and read transactions are given in Figures 4 and 5.

SSC PL P300 Network Interface Controller

January 1998 14 Version 1.1

Figure 4. Write Transaction Flow Chart

Start of Write

Transaction

Clock command byte

out to Network

interface chip

Assert CS* signal

INT* signal low?

Transfer timer

expired?

Set error condition

De-assert CS*

Return to caller

Send next byte to

Network interface chip

More data to

transfer?

No

Yes

No

Send length byte to

Network interface chip

INT* signal low?

Transfer timer

expired?

No

No

Yes

Yes

Yes

Yes

No

.

SSC PL P300 Network Interface Controller

January 1998 15 Version 1.1

Figure 5. Read Transaction Flow Chart

Start of Read

Transaction

Clock command byte

out to Network

interface chip

Assert CS* signal

INT* signal low?

Transfer timer

expired?

Set error condition

De-assert CS*

Return to caller

Get next byte from

Network interface chip

More data to

transfer?

No

Yes

No

Get length byte from

Network interface chip

INT* signal low?

Transfer timer

expired?

No

No

Yes

Yes

Yes

Yes

No

.

SSC PL P300 Network Interface Controller

January 1998 16 Version 1.1

SSC P300 Commands

Command Overview

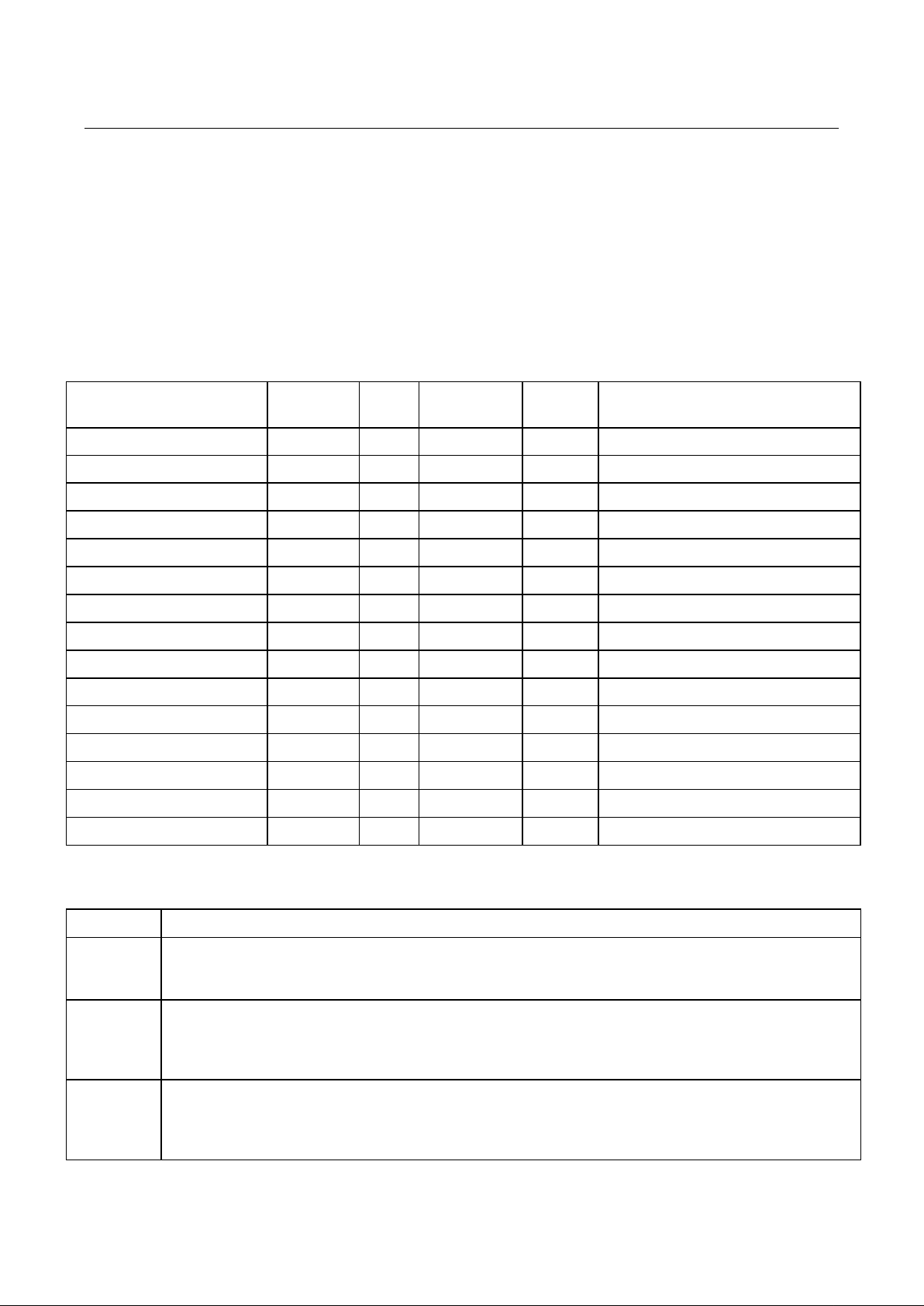

A summary of information needed to use each command is given in Tables 3A and 3B. The information in

these tables defines the command’s name, mnemonic and hex value. The command is then further

classified as belonging to a write transaction or a read transaction. The length defines how many bytes of

information are transferred. The affected data structure column relates the command to the data structure

affected by that command.

Table 3A. Summary of Commands

Name Mnemonic Hex

Value

Transaction

Type

Length Affected Data Structure

Force_Interface_Error FIE 0x00 Read 0 None

Reset RST 0x01 Write 0 None

Layer_Management_Read LR 0x02 Read 7 Layer_Config_Info

Layer_Management_Write LW 0x03 Write 7 Layer_Config_Info

Interface_Read IR 0x04 Read 1 Interface_Flags

Control_Write CW 0x05 Write 2 Node_Control

Status_Read SR 0x06 Read 6 Status_Info

Packet_Receive PR 0x08 Read Variable Receive_Header & Receive_NPDU

Packet_Transmit PT 0x09 Write Variable Transmit_Header & Transmit_NPDU

Read_Receive_Information RRI 0x0A Read Variable Receive_NPDU

Write_Transmit_Invoke WTI 0x0B Write Variable Transmit_NPDU

Read_Receive_Header RRH 0x0C Read 9 Unbuffered Receive_Header

Write_Transmit_Header WTH 0x0D Write 9 Transmit_Header

Write_Register_46 WRS-46 0x46 Write 1 DLL_Access_Control

Read_Register_4 RRS-4 0x84 Read 1 DLL_Rc_Link_Status

Table 3B. Command Description

Mnemonic Description

FIE This command sets the interface error flag in the Interface_Flags data structure. This command is

typically used for testing and debugging. The host performs a read transaction with the command

byte set to 0x00. The SSC P300 returns a length byte of zero.

RST This command disables all functions and I/O except the host interface. The host performs a write

transaction with the command byte set to 0x01 and the length byte set to zero. This command can be

used after an error condition to reset the chip to its initial state. After this command is issued, the chip

must be re-initialized as described in the Initialization section.

LR This command returns the information stored in the Layer_Config_Info data structure. The host

performs a read transaction with the command byte set to 0x02. The P300 will return a length byte

set to 7 followed by the 7 data bytes of the Layer_Config_Info data structure. This command is

typically used to verify the node configuration parameters. See section on Initialization.

Loading...

Loading...