Page 1

Intel® Ethernet Controller X550

Datasheet

Ethernet Networking Division (ND)

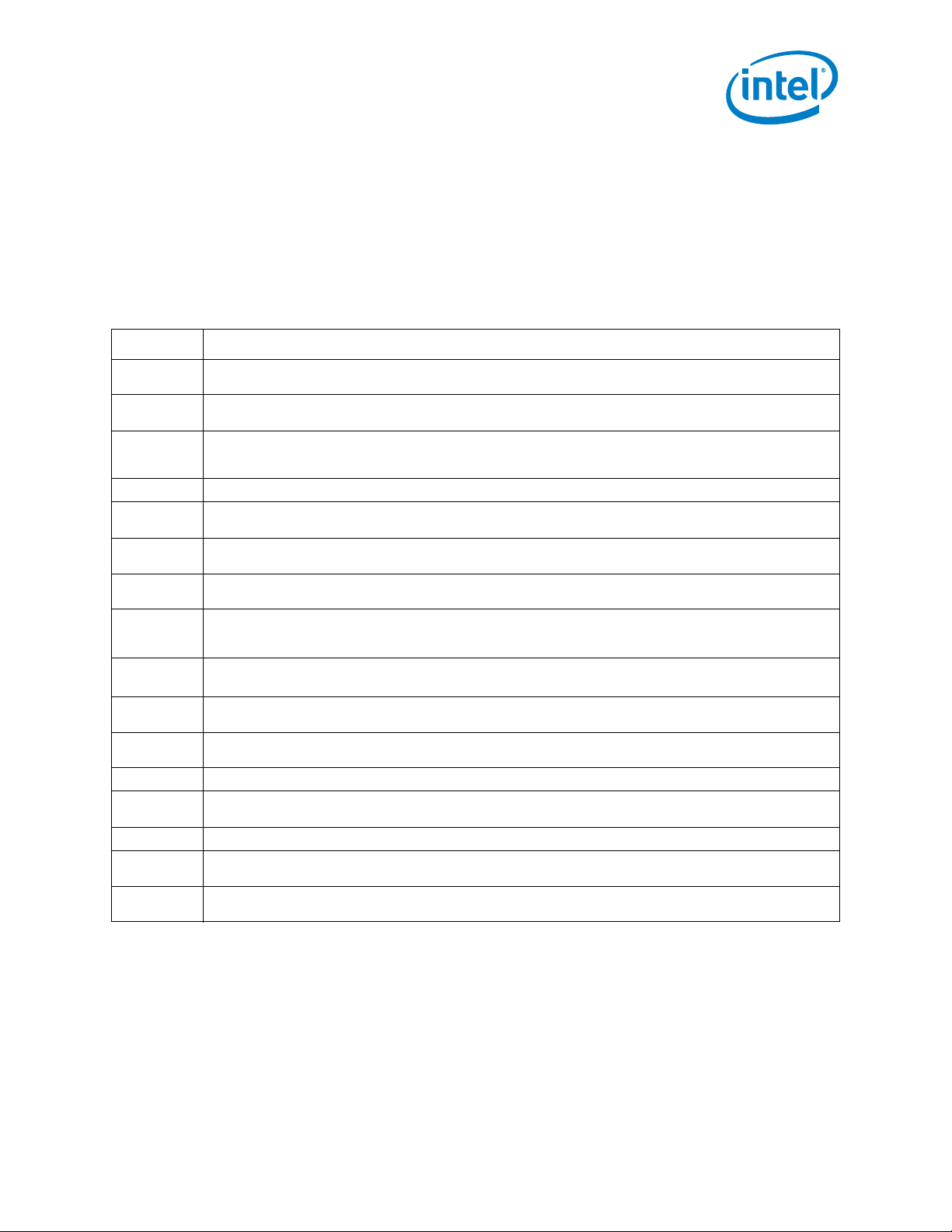

PRODUCT FEATURES

General

Serial Flash interface

Configurable LED operation for software or customizing OEM

LED displays

Device disable capability

Package size - 25 mm x 25 mm (X550-BT2)

Package size - 17 mm x 17 mm (X550-AT2)

Networking

10 GbE/1 GbE/100 Mb/s copper PHYs integrated on-chip

Support for jumbo frames of up to 15.5 KB

Flow control support: send/receive pause frames and receive

FIFO thresholds

Statistics for management and RMON

802.1q VLAN support

TCP segmentation offload: up to 256 KB

IPv6 support for IP/TCP and IP/UDP receive checksum

offload

Fragmented UDP checksum offload for packet reassembly

Message Signaled Interrupts (MSI)

Message Signaled Interrupts (MSI-X)

Interrupt throttling control to limit maximum interrupt rate

and improve CPU usage

Flow Director (16 x 8 and 32 x 4)

128 transmit queues

Receive packet split header

Receive header replication

Dynamic interrupt moderation

TCP timer interrupts

Relaxed ordering

Support for 64 virtual machines per port (64 VMs x 2

queues)

Support for Data Center Bridging (DCB);(802.1Qaz,

802.1Qbb, 802.1p)

Host Interface

PCIe 3.0 Base Specification

Bus width — x1, x4, x8

64-bit address support for systems using more than 4 GB of

physical memory

MAC F

UNCTIONS

Descriptor ring management hardware for transmit and

receive

ACPI register set and power down functionality supporting

D0 and D3 states

A mechanism for delaying/reducing transmit interrupts

Software-controlled global reset bit (resets everything

except the configuration registers)

Four Software-Definable Pins (SDP) per port

Wake up

IPv6 wake-up filters

Configurable flexible filter (through NVM)

LAN function disable capability

Programmable memory transmit buffers (160 KB/port)

Default configuration by NVM for all LEDs for pre-driver

functionality

Manageability

SR-IOV support

Eight VLAN L2 filters

16 Flex L3 port filters

Four Flexible TCO filters

Four L3 address filters (IPv4)

Advanced pass through-compatible management packet

transmit/receive support

SMBus interface to an external Manageability Controller (MC)

NC-SI interface to an external MC

Four L3 address filters (IPv6)

Four L2 address filters

Revision 2.2

July 2017

333369-004

Page 2

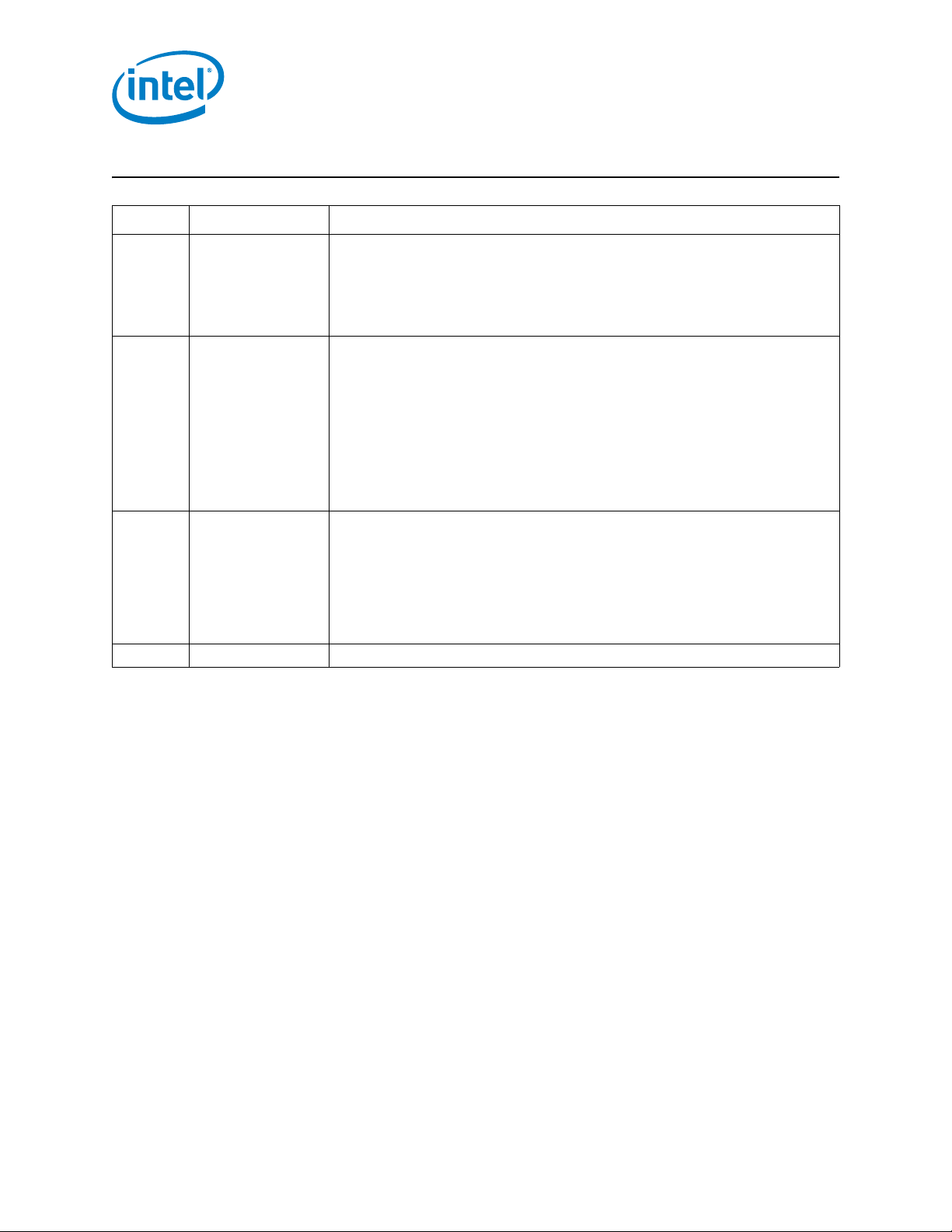

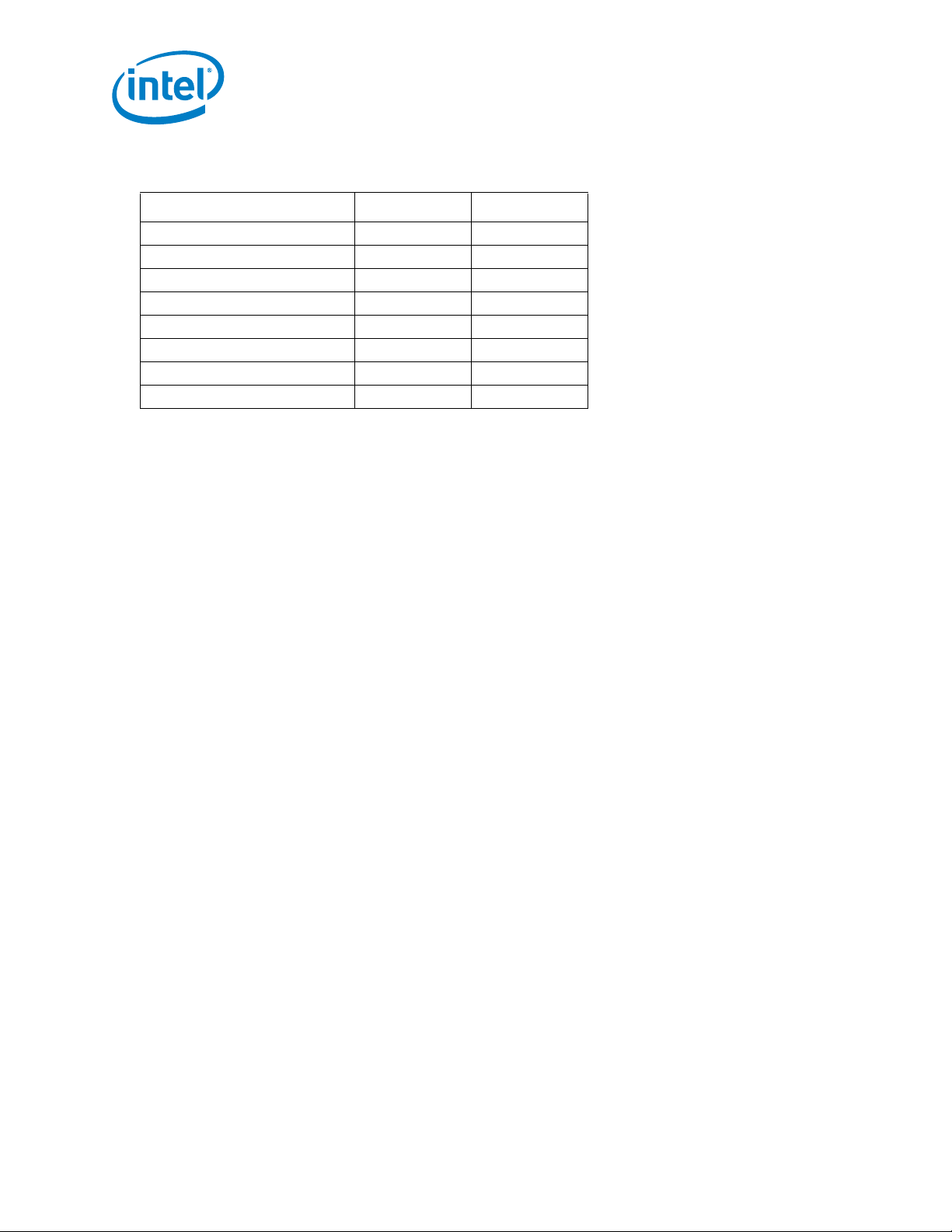

Intel® Ethernet Controller X550 Datasheet—Revision History

Revision History

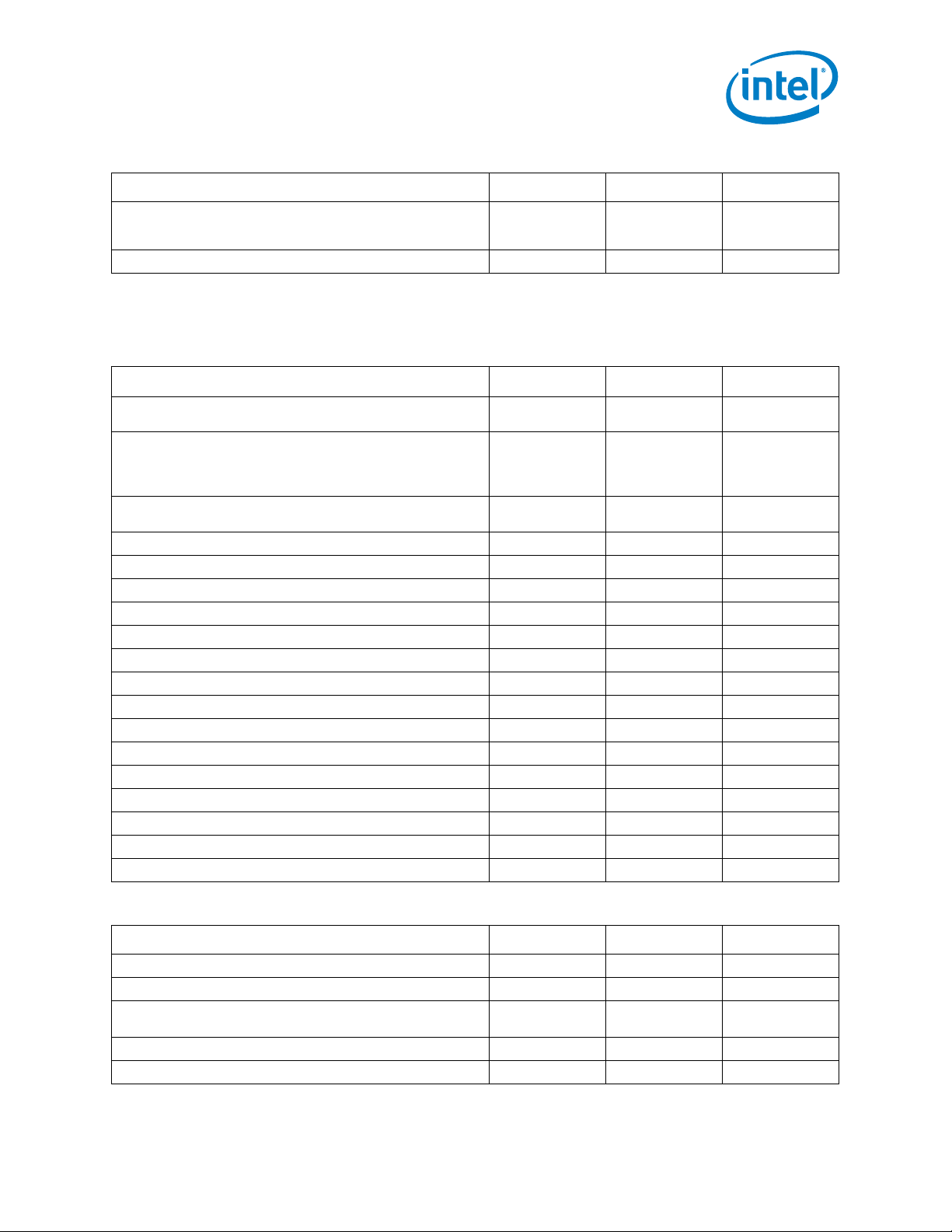

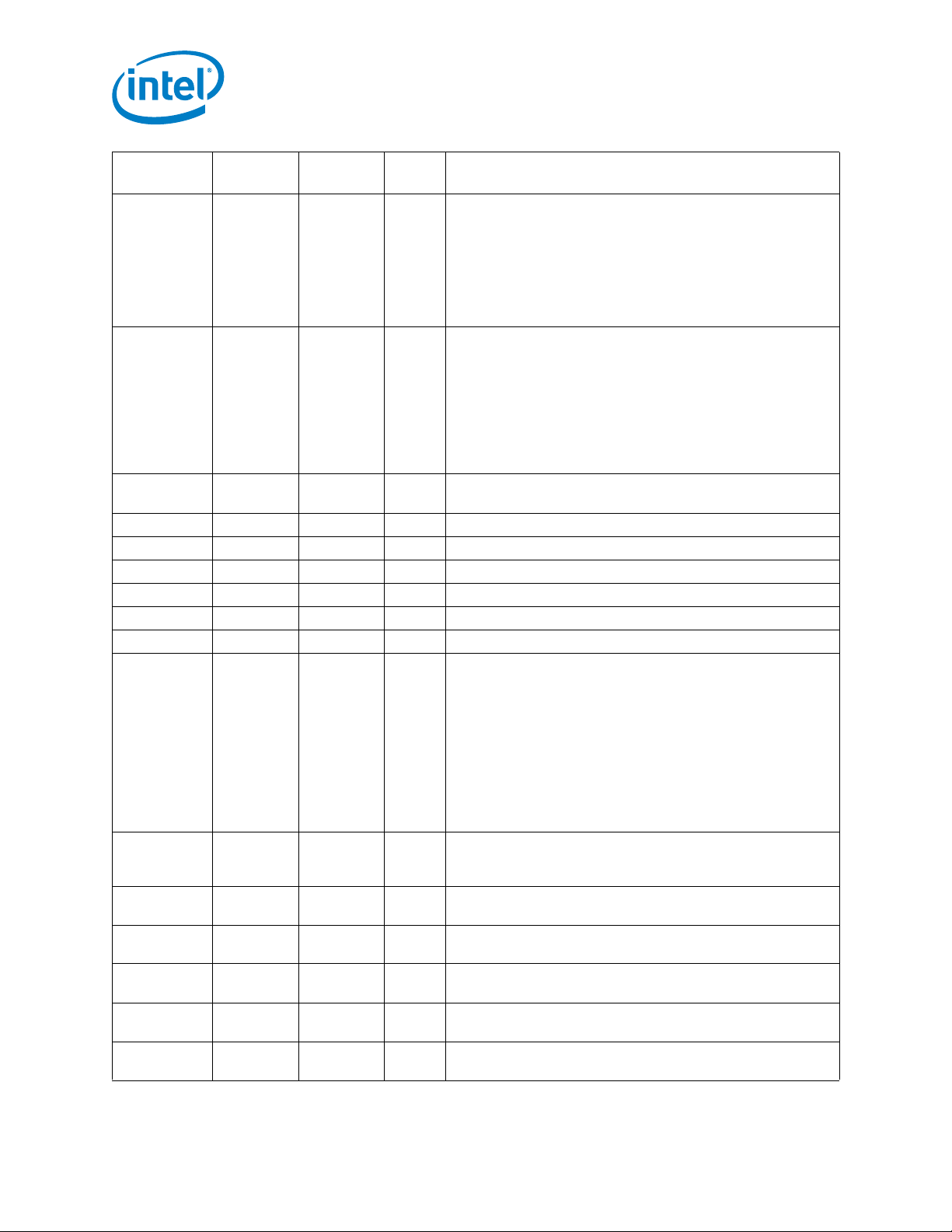

Revision Date Notes

2.2 July 21, 2017 Updates include the following:

•Added Section 2.2.8.1, “Pin Differences in the X550-AT Single Port Device”.

• Section 11.7.6.1.3 — Added reference to list of support message types.

• Section 11.7.6.1.3 — Modified verbiage in “Value” column for Bytes 3:5 in Table 11-44.

• Section 12.3.9 — Added new table for X550-AT power consumption.

• Section 12.3.10.1 — Updated values in associate table.

2.1 May 10, 2016 Updates include the following:

• Removed EEC.FLUPD bit. No longer used for triggering Shadow RAM dump.

• Removed FLUPDATE register (0x00015F54).

• Tab le 3-2 5 — Updated description for SDP1.

• Section 9.2.3.6.7, “Link Capabilities Register (0xAC; RO)” — Changed default value for

ASPM support (bits 11:10) to 10b.

• Section 11.8.3.1, “Driver Info Host Command” — Updated Table 11-49.

• Table 12-3 and Table 12-4 — Changed Device Total Power units from mW to W.

• Table 12-20 — Updated thermal diode typical ESR value to 2.77 .

• Table 15-2 — Updated ID Code values.

• Other miscellaneous updates.

2.0 January 8, 2016 Updates include the following:

1.9

1

October 27, 2015 Initial release (Intel public)

• Updated PHY Registers section.

• Changed Max temperature in NVM mode to 102 (Tjunction max changed 107).

• Added NBASE-T information.

• Removed 10BASE-T information.

• Removed x2 lane width.

• Updated power numbers.

• Updated heat sink and other thermal information.

1. There were no previous versions of this document released.

2 333369-004

Page 3

Contents—Intel

®

Ethernet Controller X550 Datasheet

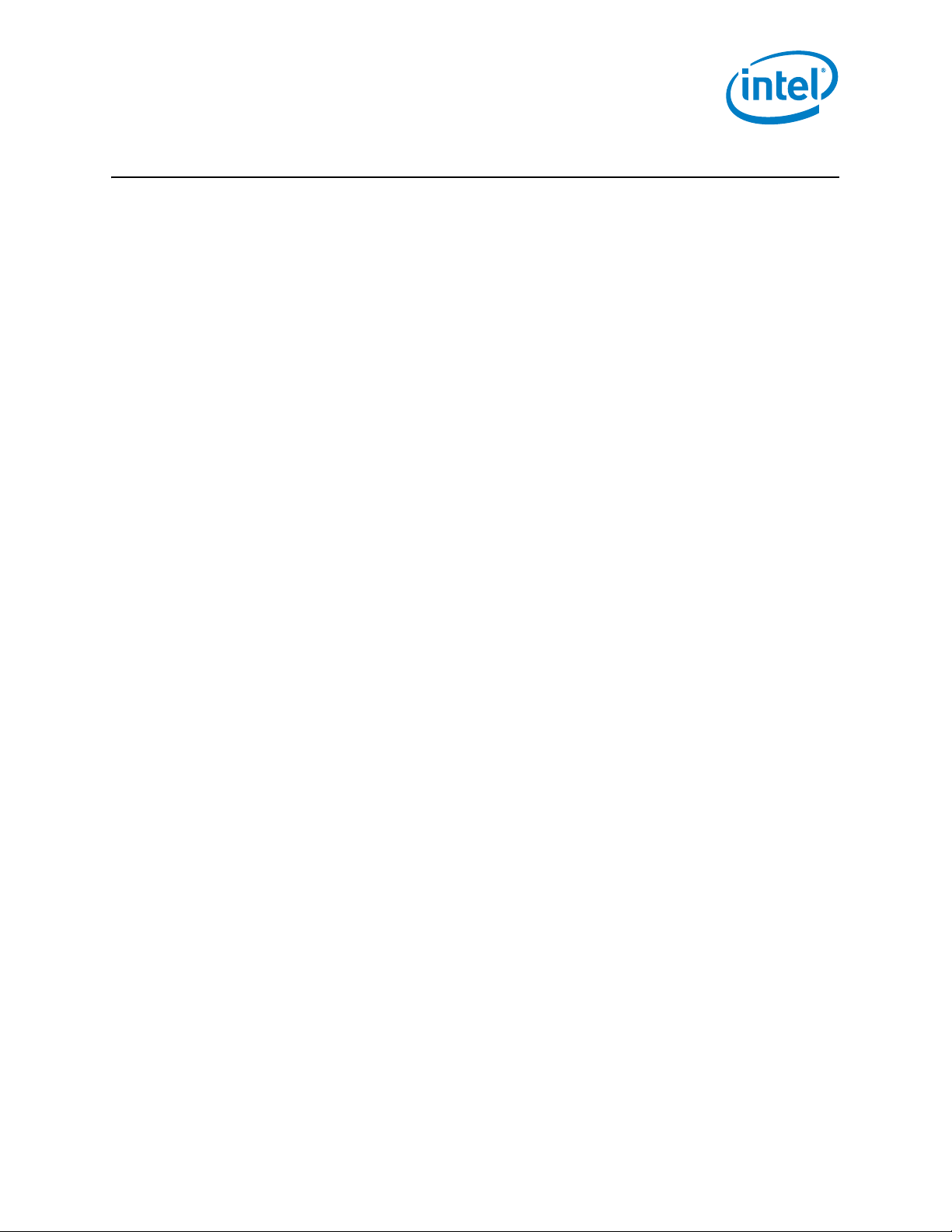

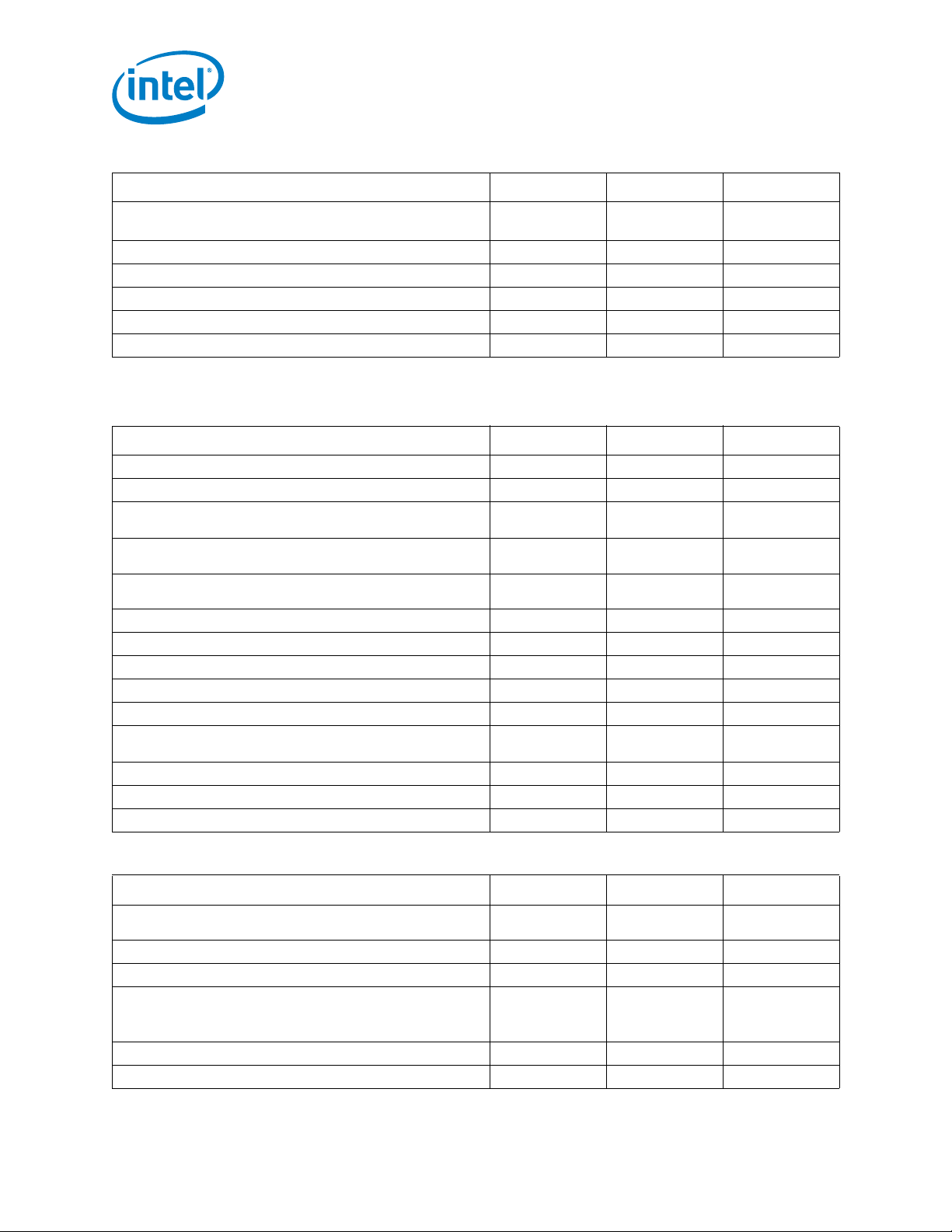

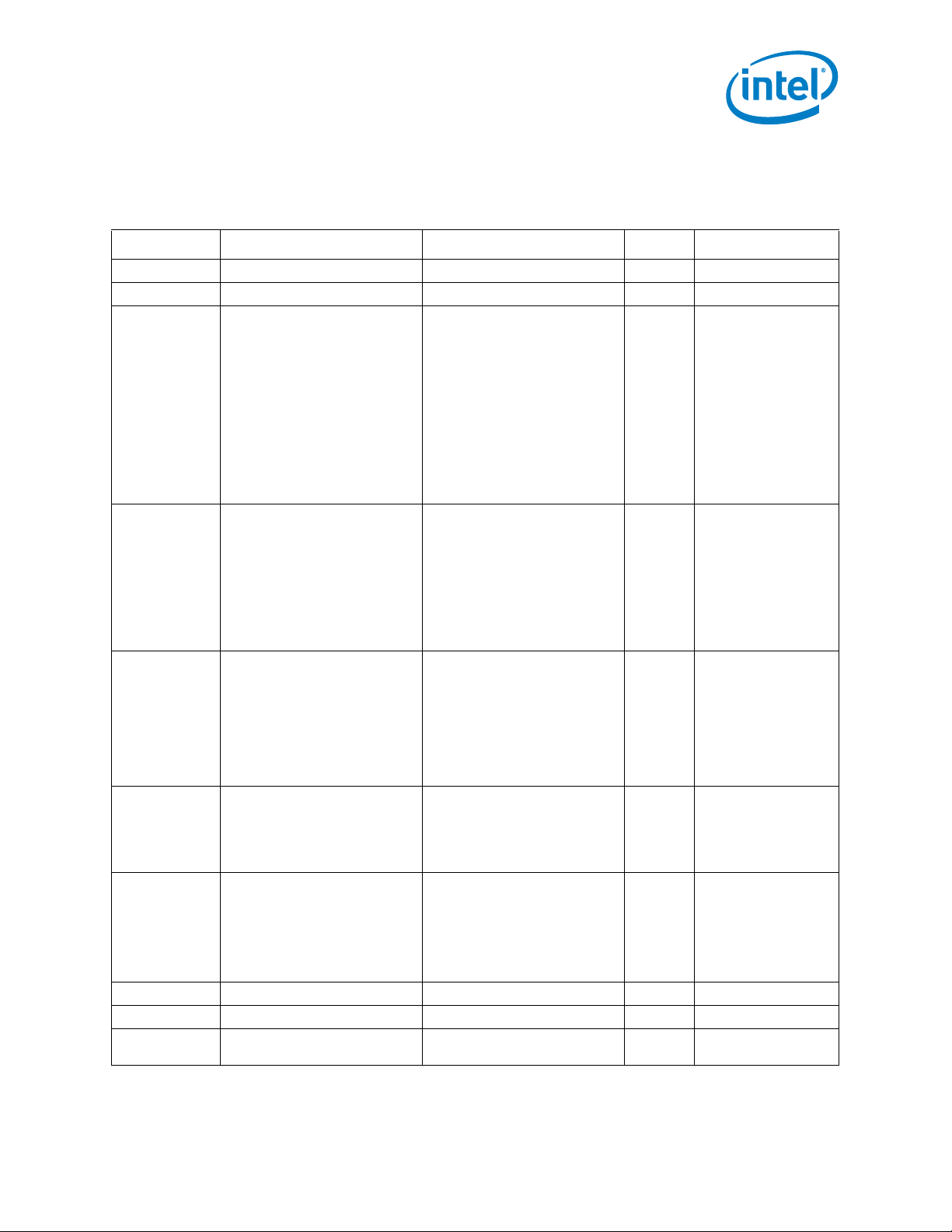

Contents

1.0 Introduction ......................................................................................................... 19

1.1 Scope .................................................................................................................................. 19

1.2 Product Overview .................................................................................................................. 19

1.2.1 System Configurations..................................................................................................... 19

1.3 External Interfaces ................................................................................................................ 20

1.3.1 PCIe Interface ................................................................................................................ 21

1.3.2 Network Interfaces.......................................................................................................... 21

1.3.3 Serial Flash Interface....................................................................................................... 21

1.3.4 SMBus Interface ............................................................................................................. 21

1.3.5 NC-SI Interface .............................................................................................................. 21

1.3.6 Software-Definable Pins (SDP) Interface (General-Purpose I/O)............................................. 22

1.3.7 LED Interface ................................................................................................................. 22

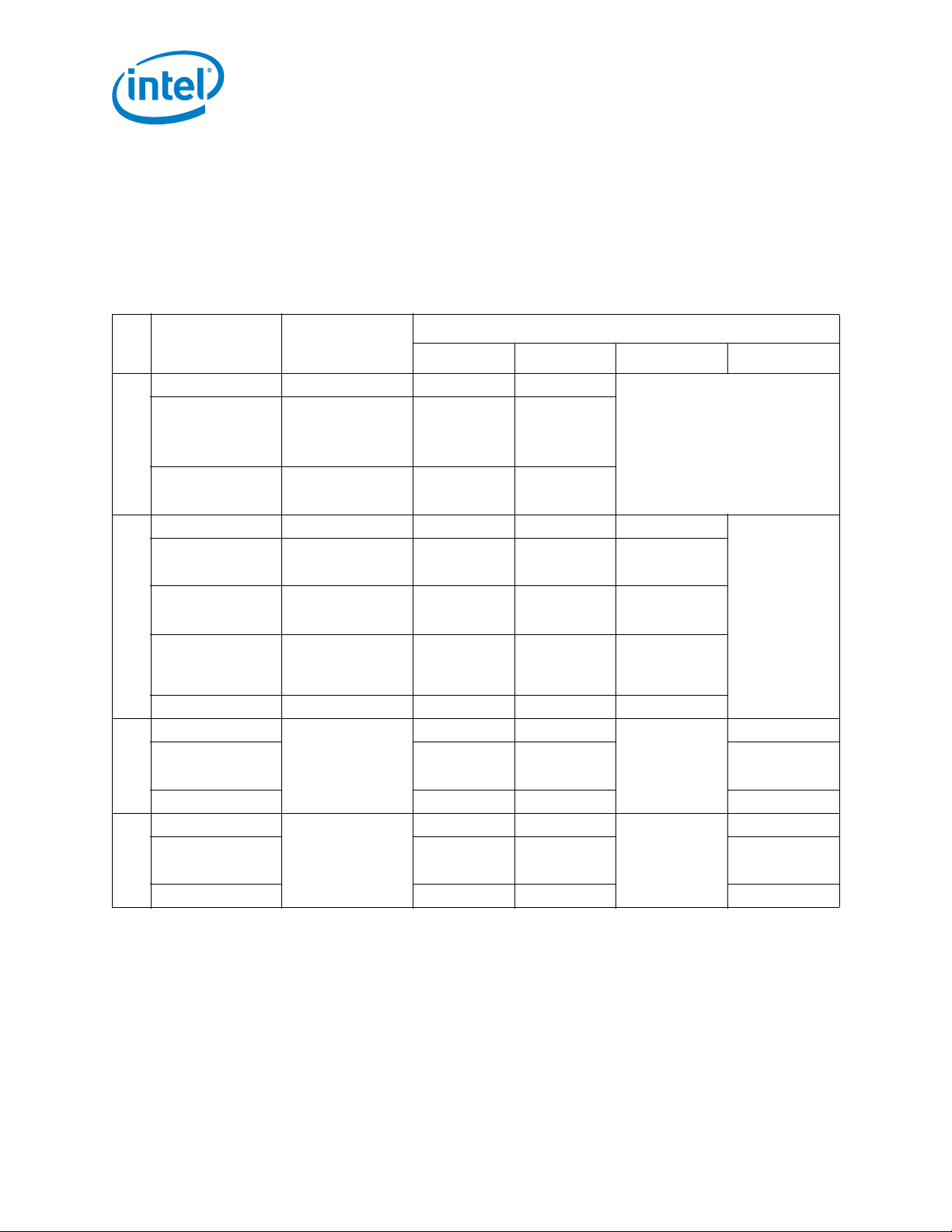

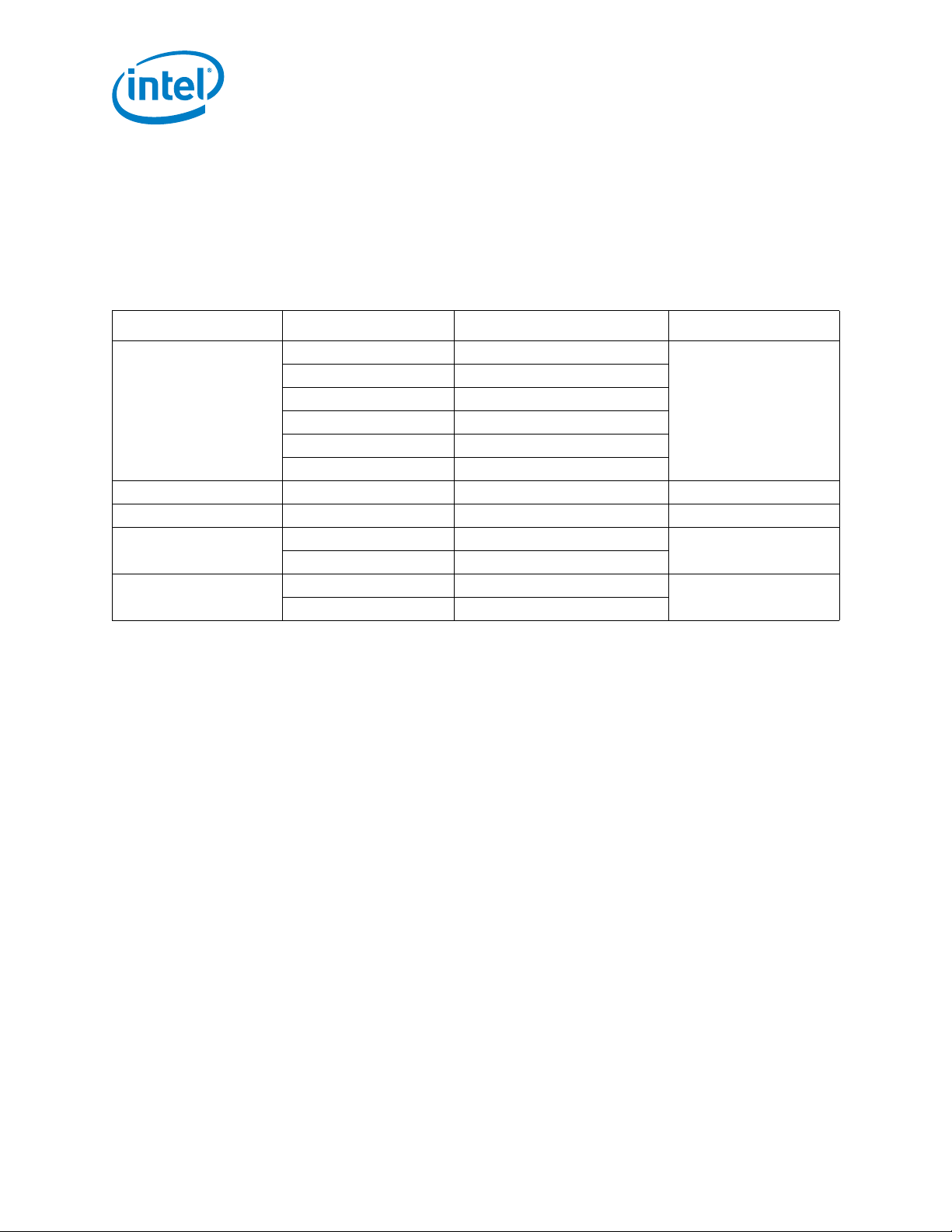

1.4 Feature Summary ................................................................................................................. 22

1.5 Overview: New Capabilities Beyond the X540 ............................................................................ 27

1.5.1 NBASE-T Support............................................................................................................ 27

1.5.2 Filtering Capabilities ........................................................................................................ 27

1.5.3 IEEE 1588 Improvements................................................................................................. 27

1.5.4 Manageability ................................................................................................................. 28

1.6 Conventions ......................................................................................................................... 28

1.6.1 Terminology and Acronyms .............................................................................................. 28

1.6.2 Byte Ordering................................................................................................................. 28

1.7 References ........................................................................................................................... 29

1.8 Architecture and Basic Operation ............................................................................................. 31

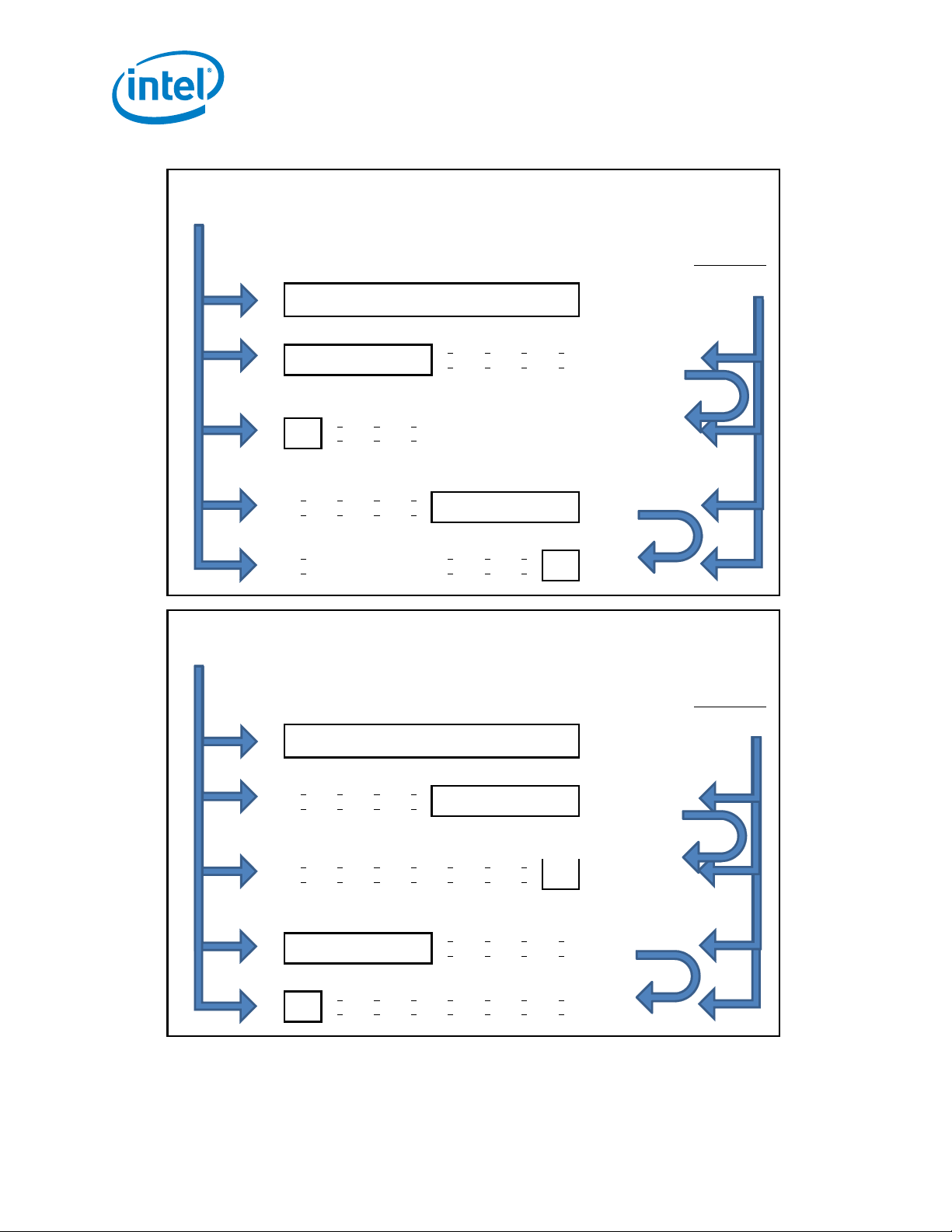

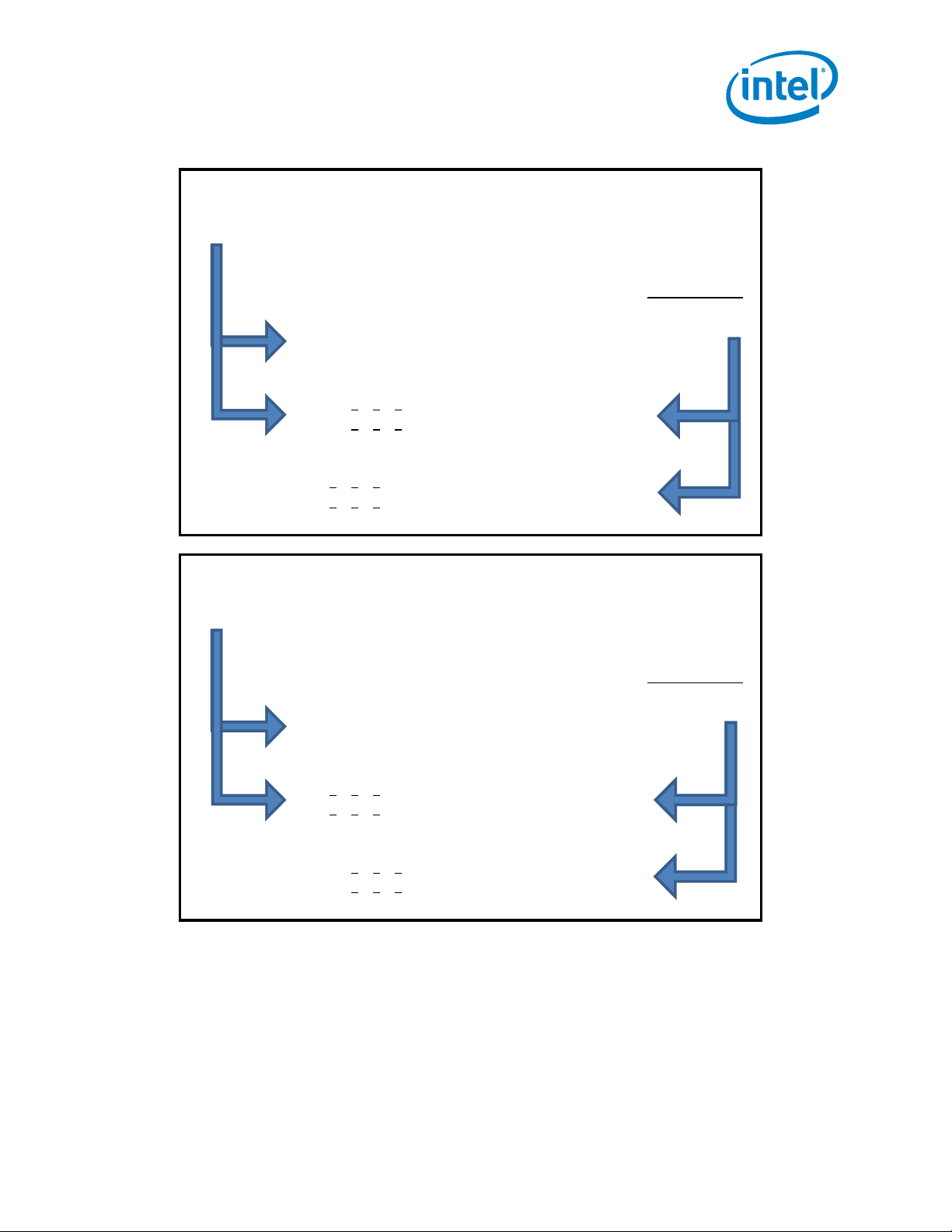

1.8.1 Transmit (Tx) Data Flow................................................................................................... 31

1.8.2 Receive (Rx) Data Flow.................................................................................................... 32

2.0 Pin Interface ......................................................................................................... 33

2.1 Signal Type Definition ............................................................................................................ 33

2.2 Pin Assignments ................................................................................................................... 34

2.2.1 PCIe.............................................................................................................................. 34

2.2.2 MDI............................................................................................................................... 35

2.2.3 Serial Flash .................................................................................................................... 36

2.2.4 SMBus........................................................................................................................... 37

2.2.5 NC-SI............................................................................................................................ 37

2.2.6 Software Defined Pins (SDPs) ........................................................................................... 38

2.2.7 LEDs ............................................................................................................................. 38

2.2.8 RSVD and No-Connect Pins............................................................................................... 39

2.2.9 Miscellaneous ................................................................................................................. 41

2.2.10 JTAG ............................................................................................................................. 42

2.2.11 Power Supplies ............................................................................................................... 43

2.3 Pull-Up/Pull-Down Information ................................................................................................ 45

2.3.1 External Pull-Ups............................................................................................................. 45

2.4 Strapping Options ................................................................................................................. 45

2.5 Ball Out — Top View Through Package ..................................................................................... 46

3.0 Interconnects ....................................................................................................... 49

3.1 PCI Express (PCIe) ................................................................................................................ 49

3.1.1 General Overview............................................................................................................ 49

3.1.2 Transaction Layer............................................................................................................ 50

333369-004 3

Page 4

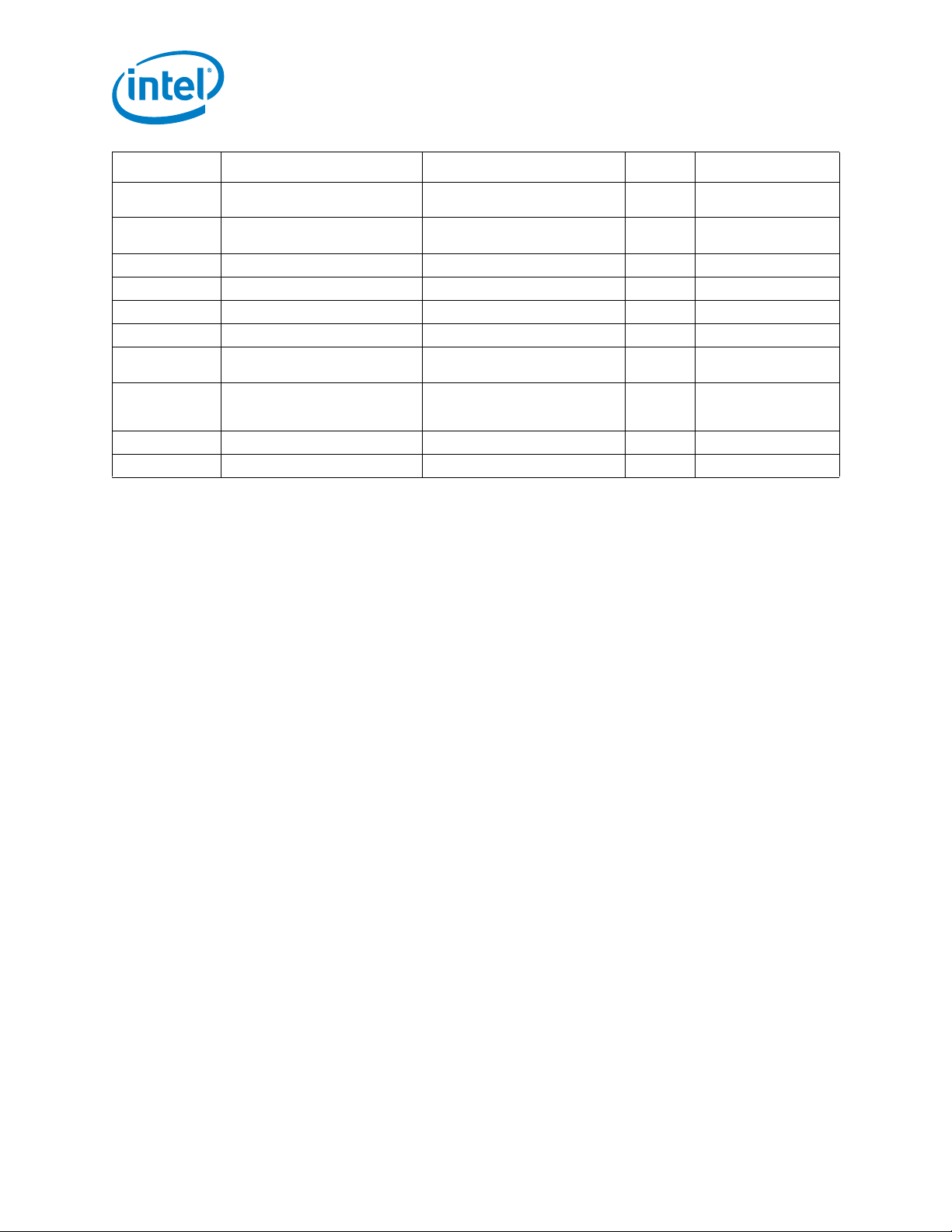

Intel® Ethernet Controller X550 Datasheet—Contents

3.1.3 Link Layer...................................................................................................................... 58

3.1.4 Physical Layer................................................................................................................. 60

3.1.5 Error Events and Error Reporting....................................................................................... 64

3.1.6 Performance and Statistics Counters.................................................................................. 70

3.2 Management Interfaces ......................................................................................................... 78

3.2.1 SMBus........................................................................................................................... 78

3.3 Network Controller — Sideband Interface (NC-SI) ..................................................................... 78

3.3.1 Electrical Characteristics .................................................................................................. 78

3.3.2 NC-SI Transactions ......................................................................................................... 78

3.3.3 MCTP (Over PCIe or SMBus) ............................................................................................. 79

3.4 Non-Volatile Memory (NVM) ................................................................................................... 79

3.4.1 General Overview............................................................................................................ 79

3.4.2 Shadow RAM .................................................................................................................. 80

3.4.3 NVM Clients and Interfaces............................................................................................... 81

3.4.4 Flash Access Contention................................................................................................... 83

3.4.5 Signature Field ............................................................................................................... 84

3.4.6 VPD Support................................................................................................................... 84

3.4.7 NVM Read, Write, and Erase Sequences ............................................................................. 86

3.4.8 Extended NVM Flows ....................................................................................................... 89

3.4.9 NVM Authentication Procedure .......................................................................................... 91

3.5 Configurable I/O Pins — Software-Definable Pins (SDPs) ............................................................ 93

2

3.5.1 I

C Over SDP ................................................................................................................. 95

3.6 LEDs ................................................................................................................................... 97

3.7 Network Interface ................................................................................................................. 98

3.7.1 Overview ....................................................................................................................... 98

3.7.2 Internal MDIO Interface ................................................................................................... 99

3.7.3 Integrated Copper PHY Functionality................................................................................ 100

3.7.4 Ethernet Flow Control (FC) ............................................................................................. 108

3.7.5 Inter Packet Gap (IPG) Control and Pacing........................................................................ 119

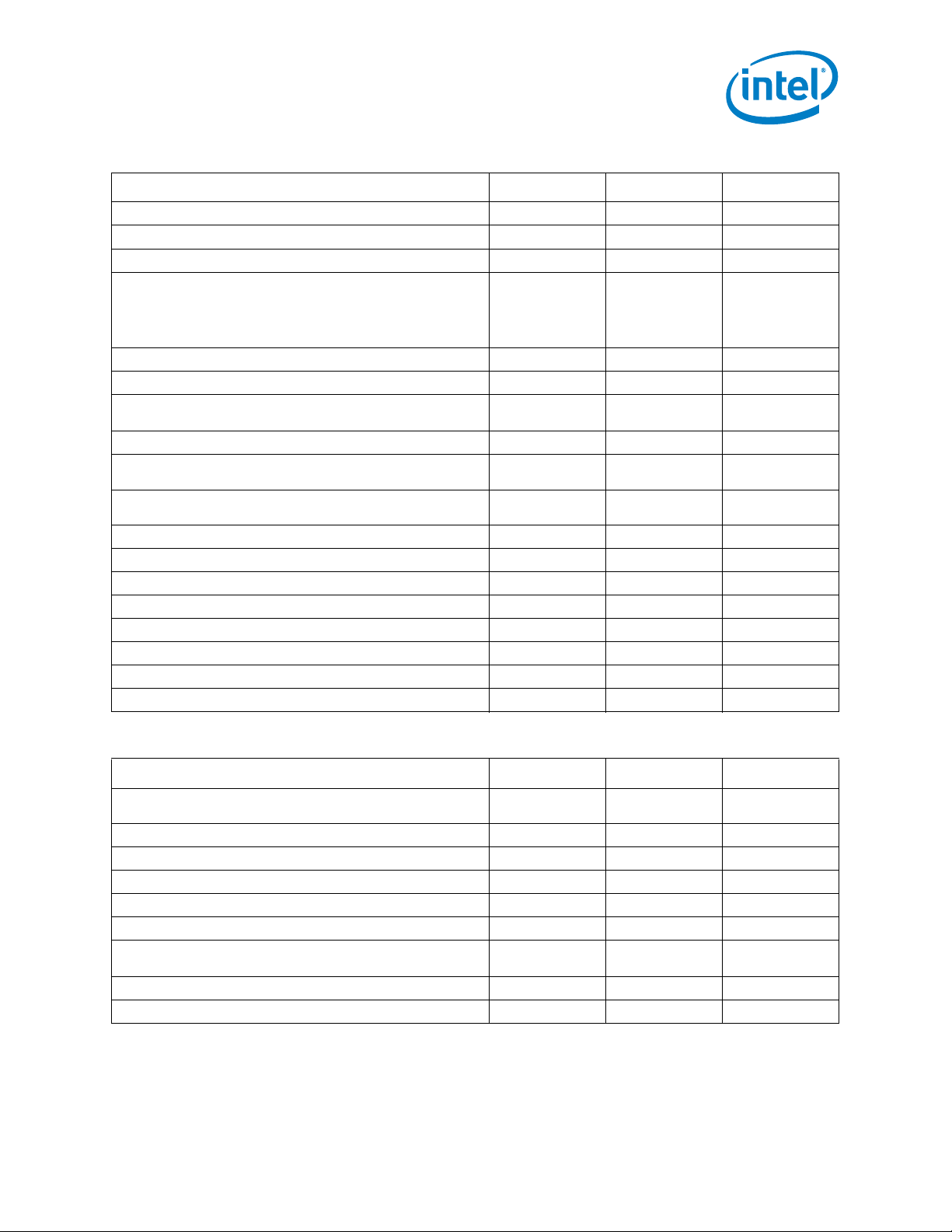

4.0 Initialization ....................................................................................................... 121

4.1 Power Up ........................................................................................................................... 121

4.1.1 Power-Up Sequence ...................................................................................................... 121

4.1.2 Power-Up Timing Diagram.............................................................................................. 122

4.1.3 Main-Power/Aux-Power Operation ................................................................................... 125

4.2 Reset Operation .................................................................................................................. 126

4.2.1 Reset Sources............................................................................................................... 126

4.2.2 Reset in PCI-IOV Environment ........................................................................................ 131

4.2.3 Reset Effects ................................................................................................................ 132

4.3 Queue Disable .................................................................................................................... 135

4.4 Function Disable ................................................................................................................. 136

4.4.1 General ....................................................................................................................... 136

4.4.2 Overview ..................................................................................................................... 136

4.4.3 Control Options............................................................................................................. 137

4.4.4 Event Flow for Enable/Disable Functions........................................................................... 138

4.5 Device Disable .................................................................................................................... 139

4.5.1 Overview ..................................................................................................................... 139

4.5.2 BIOS Disable of the Device at Boot Time by Using the Strapping Option ............................... 140

4.6 Software Initialization and Diagnostics ................................................................................... 140

4.6.1 Introduction ................................................................................................................. 140

4.6.2 Power-Up State ............................................................................................................ 140

4 333369-004

Page 5

Contents—Intel

®

Ethernet Controller X550 Datasheet

4.6.3 Initialization Sequence................................................................................................... 141

4.6.4 100 Mb/s, 1 GbE, and 10 GbE Link Initialization ................................................................ 142

4.6.5 Initialization of Statistics................................................................................................ 142

4.6.6 Interrupt Initialization.................................................................................................... 143

4.6.7 Receive Initialization...................................................................................................... 143

4.6.8 Transmit Initialization.................................................................................................... 146

4.6.9 FCoE Initialization Flow .................................................................................................. 148

4.6.10 Virtualization Initialization Flow....................................................................................... 148

4.6.11 DCB Configuration......................................................................................................... 151

4.6.12 Security Initialization..................................................................................................... 161

4.6.13 Alternate MAC Address Support....................................................................................... 162

4.7 Access to Shared Resources ................................................................................................. 163

5.0 Power Management and Delivery ........................................................................ 165

5.1 Power Targets and Power Delivery ......................................................................................... 165

5.2 Power Management ............................................................................................................. 165

5.2.1 Introduction to X550 Power States .................................................................................. 165

5.2.2 Auxiliary Power Usage ................................................................................................... 166

5.2.3 PCIe Link Power Management......................................................................................... 166

5.2.4 Power States ................................................................................................................ 167

5.2.5 Timing of Power-State Transitions ................................................................................... 172

5.3 Network Interfaces Power Management .................................................................................. 176

5.3.1 PHY Power-Down State .................................................................................................. 176

5.3.2 PHY Power-Down via the PHY Register ............................................................................. 177

5.3.3 Smart Power-Down (SPD) .............................................................................................. 177

5.3.4 Disable 10GBASE-T and/or 1000BASE-T Speeds................................................................ 179

5.3.5 Low Power Link Up (LPLU).............................................................................................. 179

5.3.6 Energy Efficient Ethernet (EEE) ....................................................................................... 184

5.4 Wake-Up ........................................................................................................................... 187

5.4.1 Advanced Power Management Wake-Up ........................................................................... 187

5.4.2 ACPI Power Management Wake-Up.................................................................................. 187

5.4.3 Wake-Up Packets .......................................................................................................... 188

5.4.4 Wake-Up and Virtualization ............................................................................................ 192

5.5 DMA Coalescing .................................................................................................................. 193

5.5.1 DMA Coalescing Activation.............................................................................................. 193

5.5.2 DMA Coalescing Operating Mode ..................................................................................... 194

5.5.3 DMA Coalescing Recommended Settings........................................................................... 195

5.6 LTR ................................................................................................................................... 196

5.6.1 LTR Algorithm............................................................................................................... 196

5.6.2 LTR Initialization Flow.................................................................................................... 197

5.7 Thermal Management .......................................................................................................... 197

5.7.1 General ....................................................................................................................... 197

5.7.2 MC-Based Mode ............................................................................................................ 198

5.7.3 NVM-Based Mode .......................................................................................................... 198

5.7.4 Thermal Sensor Control ................................................................................................. 199

5.7.5 Thermal Sensor Characteristics ....................................................................................... 199

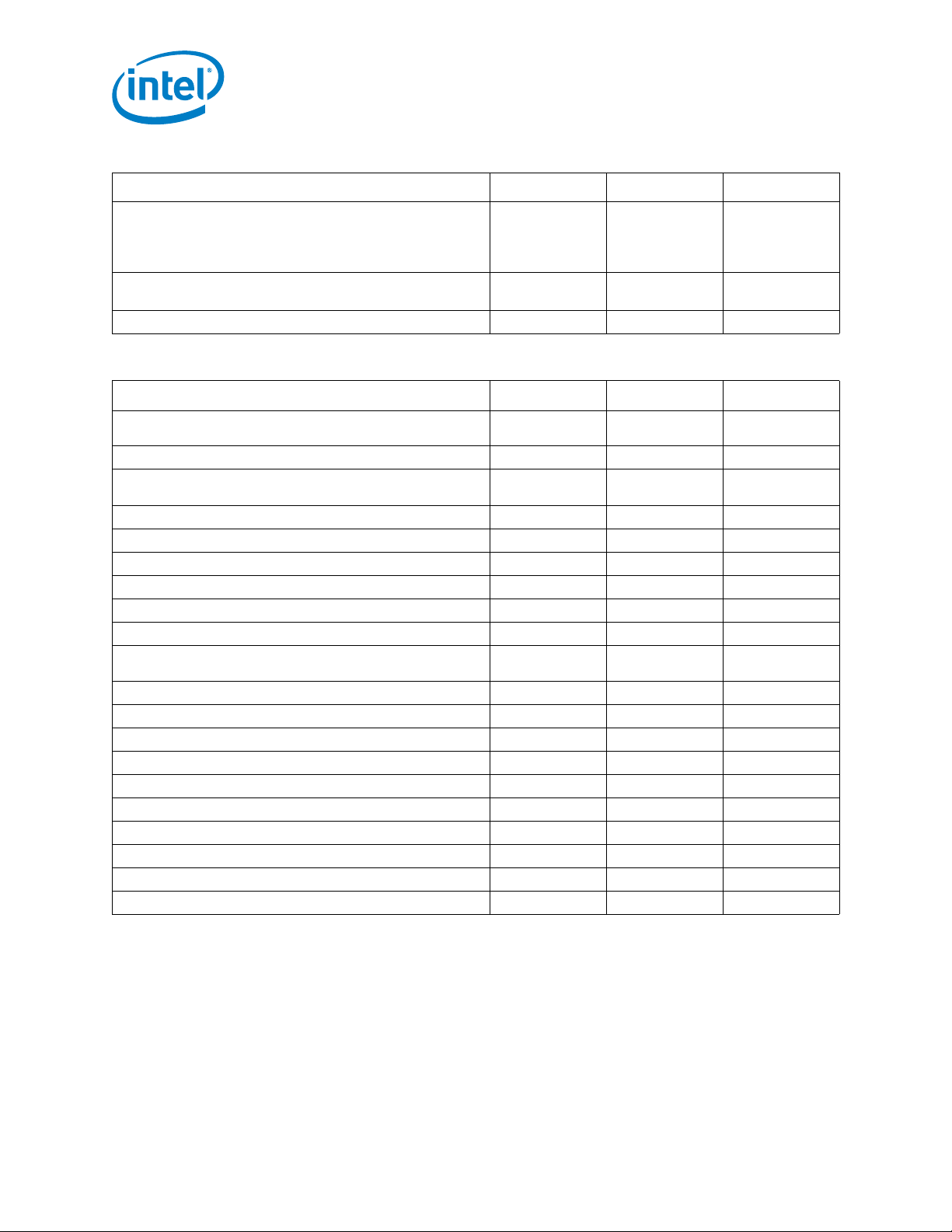

6.0 Non-Volatile Memory Map ................................................................................... 201

6.1 NVM Organization ............................................................................................................... 201

6.1.1 Protected Areas ............................................................................................................ 204

6.2 NVM Header ....................................................................................................................... 205

6.3 Software Sections ............................................................................................................... 207

333369-004 5

Page 6

Intel® Ethernet Controller X550 Datasheet—Contents

6.3.1 Software Compatibility Module — Word Address 0x10-0x14 ................................................ 207

6.3.2 PBA Number Module — Word Address 0x15-0x16 .............................................................. 208

6.3.3 Boot Configuration Block — Word Address 0x17 ................................................................ 209

6.3.4 Software Reserved — Words 0x18-0x2E........................................................................... 211

6.3.5 VPD Module Pointer — Word Address 0x2F ....................................................................... 214

6.3.6 PXE Configuration Words — Word Address 0x30-0x36........................................................ 215

6.3.7 Alternate Ethernet MAC Address Pointer — Word Address 0x37 ........................................... 218

6.3.8 FCoE Scratch Pad Pointer — Word Address 0x39................................................................ 219

6.4 Hardware Sections .............................................................................................................. 220

6.4.1 Hardware Section — Auto-Load Sequence ........................................................................ 220

6.4.2 NVM Init Module ........................................................................................................... 220

6.4.3 PCIe Analog Configuration Module................................................................................... 223

6.4.4 PCIe Link Configuration Module....................................................................................... 223

6.4.5 PCIe General Configuration Module .................................................................................. 224

6.4.6 PCIe Configuration Space 0/1 Modules ............................................................................. 225

6.4.7 LAN Core 0/1 Modules ................................................................................................... 226

6.4.8 CSR 0/1 Auto Configuration Modules................................................................................ 229

6.4.9 PHY Auto Configuration Module ....................................................................................... 230

6.5 Firmware Sections ............................................................................................................... 233

6.5.1 Firmware Module Header................................................................................................ 233

6.5.2 Common Firmware Parameters Module — Global MNG Offset 0x2 ........................................ 234

6.5.3 Pass-Through LAN 0/1 Configuration Modules — Global MNG Offsets 0x03 and 0x06 .............. 235

6.5.4 Sideband Configuration Module — Global MNG Offset 0x04 ................................................. 242

6.5.5 Flexible TCO Filter Configuration Module — Global MNG Offset 0x05..................................... 248

6.5.6 Mini Loader Module ....................................................................................................... 249

6.5.7 Firmware Image Module................................................................................................. 249

6.6 PCIe Expansion/Option ROM ................................................................................................. 252

6.7 PHY Module ........................................................................................................................ 253

6.7.1 Register Provisional Table............................................................................................... 255

7.0 Inline Functions .................................................................................................. 257

7.1 Receive Functionality ........................................................................................................... 257

7.1.1 MAC Layer - Receive...................................................................................................... 257

7.1.2 Packet Filtering............................................................................................................. 258

7.1.3 Rx Queues Assignment .................................................................................................. 263

7.1.4 Receive Data Storage in System Memory ......................................................................... 289

7.1.5 Receive Descriptors....................................................................................................... 289

7.1.6 Receive Offloads ........................................................................................................... 304

7.1.7 Receive Statistics.......................................................................................................... 309

7.2 Transmit Functionality ......................................................................................................... 311

7.2.1 Packet Transmission...................................................................................................... 311

7.2.2 Transmit Contexts......................................................................................................... 320

7.2.3 Transmit Descriptors ..................................................................................................... 320

7.2.4 TCP and UDP Segmentation............................................................................................ 335

7.2.5 Transmit Checksum Offloading in Non-Segmentation Mode ................................................. 342

7.2.6 Transmit Statistics ........................................................................................................ 345

7.3 Interrupts .......................................................................................................................... 347

7.3.1 Interrupt Registers........................................................................................................ 347

7.3.2 Interrupt Moderation ..................................................................................................... 350

7.3.3 TCP Timer Interrupt....................................................................................................... 352

7.3.4 Mapping of Interrupt Causes........................................................................................... 352

6 333369-004

Page 7

Contents—Intel

®

Ethernet Controller X550 Datasheet

7.4 802.1q VLAN Support .......................................................................................................... 359

7.4.1 802.1q VLAN Packet Format ........................................................................................... 359

7.4.2 802.1q Tagged Frames .................................................................................................. 359

7.4.3 Transmitting and Receiving 802.1q Packets ...................................................................... 360

7.4.4 802.1q VLAN Packet Filtering.......................................................................................... 360

7.4.5 Double VLAN and Single VLAN Support ............................................................................ 361

7.4.6 E-tag and VLAN ............................................................................................................ 363

7.5 TLP Processing Hints (TPH) ................................................................................................... 365

7.5.1 Steering Tag and Processing Hint Programming................................................................. 365

7.6 Data Center Bridging (DCB) .................................................................................................. 366

7.6.1 Overview ..................................................................................................................... 366

7.6.2 Transmit-Side Capabilities .............................................................................................. 368

7.6.3 Receive-Side Capabilities................................................................................................ 380

7.7 Time SYNC (IEEE1588 and 802.1AS) ..................................................................................... 384

7.7.1 Overview ..................................................................................................................... 384

7.7.2 Flow and Hardware/Software Responsibilities .................................................................... 384

7.7.3 Hardware Time Sync Elements ........................................................................................ 386

7.7.4 Hardware Time Sync Elements ........................................................................................ 388

7.7.5 Time Sync Interrupts..................................................................................................... 391

7.7.6 PTP Packet Structure ..................................................................................................... 391

7.8 Virtualization ...................................................................................................................... 395

7.8.1 Overview ..................................................................................................................... 395

7.8.2 PCI-SIG SR-IOV Support................................................................................................ 399

7.8.3 Packet Switching........................................................................................................... 409

7.8.4 Security Features.......................................................................................................... 419

7.8.5 Virtualization of Hardware .............................................................................................. 424

7.9 Tunneling Support ............................................................................................................... 424

7.10 Receive Side Coalescing (RSC) .............................................................................................. 425

7.10.1 Packet Candidacy for RSC .............................................................................................. 427

7.10.2 Flow Identification and RSC Context Matching ................................................................... 429

7.10.3 Processing New RSC...................................................................................................... 430

7.10.4 Processing Active RSC ................................................................................................... 430

7.10.5 Packet DMA and Descriptor Write Back............................................................................. 432

7.10.6 RSC Completion and Aging ............................................................................................. 434

7.11 Fibre Channel over Ethernet (FCoE) ....................................................................................... 436

7.11.1 Introduction ................................................................................................................. 436

7.11.2 FCoE Transmit Operation................................................................................................ 437

7.11.3 FCoE Receive Operation ................................................................................................. 443

7.12 Reliability ........................................................................................................................... 458

7.12.1 Memory Integrity Protection ........................................................................................... 458

7.12.2 PCIe Error Handling....................................................................................................... 458

7.13 IPsec Support ..................................................................................................................... 459

7.13.1 Overview ..................................................................................................................... 459

7.13.2 Hardware Features List .................................................................................................. 459

7.13.3 Software/Hardware Demarcation ..................................................................................... 462

7.13.4 IPsec Formats Exchanged Between Hardware and Software ................................................ 463

7.13.5 Tx SA Table.................................................................................................................. 467

7.13.6 Tx Hardware Flow ......................................................................................................... 468

7.13.7 AES-128 Operation in Tx................................................................................................ 470

7.13.8 Rx Descriptors .............................................................................................................. 471

333369-004 7

Page 8

Intel® Ethernet Controller X550 Datasheet—Contents

7.13.9 Rx SA Tables ................................................................................................................ 471

7.13.10 Rx Hardware Flow without TCP/UDP Checksum Offload....................................................... 473

7.13.11 Rx Hardware Flow with TCP/UDP Checksum Offload ........................................................... 474

7.13.12 AES-128 Operation in Rx................................................................................................ 475

8.0 Programming Interface ....................................................................................... 477

8.1 General ............................................................................................................................. 477

8.1.1 Memory-Mapped Access................................................................................................. 477

8.1.2 I/O-Mapped Access ....................................................................................................... 478

8.1.3 Configuration Access to Internal Registers and Memories.................................................... 479

8.1.4 Register Terminology..................................................................................................... 481

8.1.5 VF Registers Allocated per Queue .................................................................................... 481

8.1.6 Non-Queue VF Registers ................................................................................................ 482

8.2 Device Registers - PF ........................................................................................................... 483

8.2.1 BAR0 Registers Summary............................................................................................... 483

8.2.2 Detailed Register Description - PF BAR0 ........................................................................... 498

8.2.2.2 NVM Registers ....................................................................................................... 511

8.2.2.3 Flow Control Registers ............................................................................................ 517

8.2.2.4 PCIe Registers ....................................................................................................... 520

8.2.2.5 PCIe Configuration Space Setting Registers................................................................ 527

8.2.2.6 Interrupt Registers ................................................................................................. 534

8.2.2.7 MSI-X Table Registers............................................................................................. 542

8.2.2.8 Receive Registers ................................................................................................... 543

8.2.2.9 Receive DMA Registers............................................................................................ 556

8.2.2.10 Transmit Registers ................................................................................................. 561

8.2.2.11 DCB Registers........................................................................................................ 567

8.2.2.12 TPH Registers ........................................................................................................ 574

8.2.2.13 Timers Registers .................................................................................................... 576

8.2.2.14 FCoE Registers....................................................................................................... 577

8.2.2.15 Flow Director Registers ........................................................................................... 582

8.2.2.16 MAC Registers ....................................................................................................... 592

8.2.2.17 Statistic Registers .................................................................................................. 597

8.2.2.18 Wake-Up and Proxy Control Registers ....................................................................... 620

8.2.2.19 Management Filters Registers .................................................................................. 627

8.2.2.20 Manageability (ARC Subsystem) HOST Interface Registers ........................................... 634

8.2.2.21 Time Sync (IEEE 1588) Registers ............................................................................. 638

8.2.2.22 Virtualization PF Registers ....................................................................................... 647

8.2.2.23 Power Management Registers .................................................................................. 658

8.2.2.24 Security Registers .................................................................................................. 664

8.2.2.25 IPsec Registers ...................................................................................................... 667

8.2.2.26 VF Registers Mapping in the PF Space ....................................................................... 671

8.2.3 BAR3 Registers Summary............................................................................................... 674

8.2.4 Detailed Register Description - PF BAR3 ........................................................................... 674

8.3 Device Registers - VF .......................................................................................................... 676

8.3.1 BAR0 Registers Summary............................................................................................... 676

8.3.2 Detailed Register Description - VF BAR0 ........................................................................... 678

8.3.3 BAR3 Registers Summary............................................................................................... 687

8.3.4 Detailed Register Description - VF BAR3 ........................................................................... 687

9.0 PCIe Programming Interface .............................................................................. 689

9.1 Overview ........................................................................................................................... 689

9.1.1 Register Attributes ........................................................................................................ 690

8 333369-004

Page 9

Contents—Intel

®

Ethernet Controller X550 Datasheet

9.2 PCIe Register Map ............................................................................................................... 691

9.2.1 PCIe Configuration Space Summary................................................................................. 691

9.2.2 Mandatory PCI Configuration Registers............................................................................. 693

9.2.3 PCI Capabilities............................................................................................................. 700

9.2.4 PCIe Extended Configuration Space ................................................................................. 724

9.2.5 Driver Forward Compatibility Register (0x94; RO).............................................................. 745

9.2.6 CSR Access Via Configuration Address Space .................................................................... 745

9.3 Virtual Functions Configuration Space .................................................................................... 746

9.3.1 Mandatory Configuration Space....................................................................................... 748

9.3.2 PCI Capabilities............................................................................................................. 749

9.3.3 PCIe Extended Capabilities ............................................................................................. 751

10.0 PHY Registers ..................................................................................................... 753

10.1 Introduction ....................................................................................................................... 753

10.1.1 PHY Register Structure................................................................................................... 753

10.1.2 Format and Nomenclature .............................................................................................. 754

10.1.3 Structure ..................................................................................................................... 755

10.1.4 PHY Registers and Documentation ................................................................................... 756

10.2 PMA Registers .................................................................................................................... 757

10.2.1 PMA Standard Control 1: Address 1.0 .............................................................................. 757

10.2.2 PMA Standard Status 1: Address 1.1................................................................................ 757

10.2.3 PMA Standard Device Identifier 1: Address 1.2.................................................................. 758

10.2.4 PMA Standard Device Identifier 2: Address 1.3.................................................................. 758

10.2.5 PMA Standard Speed Ability: Address 1.4 ......................................................................... 758

10.2.6 PMA Standard Devices in Package 1: Address 1.5.............................................................. 759

10.2.7 PMA Standard Devices in Package 2: Address 1.6.............................................................. 760

10.2.8 PMA Standard Control 2: Address 1.7 .............................................................................. 760

10.2.9 PMA Standard Status 2: Address 1.8................................................................................ 760

10.2.10 PMD Standard Transmit Disable Control: Address 1.9......................................................... 762

10.2.11 PMD Standard Signal Detect: Address 1.A ........................................................................ 762

10.2.12 PMD Standard 10G Extended Ability Register: Address 1.B ................................................. 763

10.2.13 PMA Standard Package Identifier 1: Address 1.E ............................................................... 763

10.2.14 PMA Standard Package Identifier 2: Address 1.F................................................................ 763

10.2.15 PMA 10GBASE-T Status: Address 1.81 ............................................................................. 763

10.2.16 PMA 10GBASE-T Pair Swap and Polarity Status: Address 1.82 ............................................. 764

10.2.17 PMA 10GBASE-T Tx Power Backoff Setting: Address 1.83 ................................................... 764

10.2.18 PMA 10GBASE-T Test Modes: Address 1.84 ...................................................................... 765

10.2.19 PMA 10GBASE-T SNR Operating Margin Channel A: Address 1.85 ........................................ 765

10.2.20 PMA 10GBASE-T SNR Operating Margin Channel B: Address 1.86 ........................................ 765

10.2.21 PMA 10GBASE-T SNR Operating Margin Channel C: Address 1.87 ........................................ 766

10.2.22 PMA 10GBASE-T SNR Operating Margin Channel D: Address 1.88 ........................................ 766

10.2.23 PMA 10GBASE-T SNR Minimum Operating Margin Channel A: Address 1.89........................... 766

10.2.24 PMA 10GBASE-T SNR Minimum Operating Margin Channel B: Address 1.8A........................... 766

10.2.25 PMA 10GBASE-T SNR Minimum Operating Margin Channel C: Address 1.8B........................... 767

10.2.26 PMA 10GBASE-T SNR Minimum Operating Margin Channel D: Address 1.8C .......................... 767

10.2.27 PMA 10GBASE-T Receive Signal Power Channel A: Address 1.8D ......................................... 767

10.2.28 PMA 10GBASE-T Receive Signal Power Channel B: Address 1.8E.......................................... 767

10.2.29 PMA 10GBASE-T Receive Signal Power Channel C: Address 1.8F.......................................... 768

10.2.30 PMA 10GBASE-T Receive Signal Power Channel D: Address 1.90 ......................................... 768

10.2.31 PMA 10GBASE-T Skew Delay 1: Address 1.91 ................................................................... 768

10.2.32 PMA 10GBASE-T Skew Delay 2: Address 1.92 ................................................................... 768

333369-004 9

Page 10

Intel® Ethernet Controller X550 Datasheet—Contents

10.2.33 PMA 10GBASE-T Fast Retrain Status and Control: Address 1.93........................................... 769

10.2.34 PMA TimeSync Capability: Address 1.1800 ....................................................................... 769

10.2.35 PMA TimeSync Transmit Path Data Delay 1: Address 1.1801............................................... 770

10.2.36 PMA TimeSync Transmit Path Data Delay 2: Address 1.1802............................................... 770

10.2.37 PMA TimeSync Transmit Path Data Delay 3: Address 1.1803............................................... 770

10.2.38 PMA TimeSync Transmit Path Data Delay 4: Address 1.1804............................................... 770

10.2.39 PMA TimeSync Receive Path Data Delay 1: Address 1.1805 ................................................ 770

10.2.40 PMA TimeSync Receive Path Data Delay 2: Address 1.1806 ................................................ 771

10.2.41 PMA TimeSync Receive Path Data Delay 3: Address 1.1807 ................................................ 771

10.2.42 PMA TimeSync Receive Path Data Delay 4: Address 1.1808 ................................................ 771

10.2.43 PMA Transmit Standard Interrupt Mask 1: Address 1.D000 ................................................. 771

10.2.44 PMA Transmit Standard Interrupt Mask 2: Address 1.D001 ................................................. 772

10.2.45 PMA Receive Reserved Vendor Provisioning 1: Address 1.E400 ............................................ 772

10.2.46 PMA Receive Vendor State 1: Address 1.E800 ................................................................... 773

10.2.47 PMA Receive Vendor State 2: Address 1.E811 ................................................................... 773

10.2.48 PMA Vendor Global Interrupt Flags 1: Address 1.FC00........................................................ 773

10.3 PCS Registers ..................................................................................................................... 774

10.3.1 PCS Standard Control 1: Address 3.0 ............................................................................... 774

10.3.2 PCS Standard Status 1: Address 3.1................................................................................ 774

10.3.3 PCS Standard Device Identifier 1: Address 3.2 .................................................................. 775

10.3.4 PCS Standard Device Identifier 2: Address 3.3 .................................................................. 775

10.3.5 PCS Standard Speed Ability: Address 3.4 ......................................................................... 776

10.3.6 PCS Standard Devices in Package 1: Address 3.5 .............................................................. 776

10.3.7 PCS Standard Devices in Package 2: Address 3.6 .............................................................. 777

10.3.8 PCS Standard Control 2: Address 3.7 ............................................................................... 777

10.3.9 PCS Standard Status 2: Address 3.8................................................................................ 777

10.3.10 PCS Standard Package Identifier 1: Address 3.E................................................................ 778

10.3.11 PCS Standard Package Identifier 2: Address 3.F ................................................................ 778

10.3.12 PCS 10GBASE-T Status 1: Address 3.20........................................................................... 778

10.3.13 PCS 10GBASE-T Status 2: Address 3.21........................................................................... 779

10.3.14 PCS TimeSync Capability: Address 3.1800 ........................................................................ 779

10.3.15 PCS TimeSync Transmit Path Data Delay 1: Address 3.1801 ............................................... 780

10.3.16 PCS TimeSync Transmit Path Data Delay 2: Address 3.1802 ............................................... 780

10.3.17 PCS TimeSync Transmit Path Data Delay 3: Address 3.1803 ............................................... 780

10.3.18 PCS TimeSync Transmit Path Data Delay 4: Address 3.1804 ............................................... 780

10.3.19 PCS TimeSync Receive Path Data Delay 1: Address 3.1805................................................. 780

10.3.20 PCS TimeSync Receive Path Data Delay 2: Address 3.1806................................................. 781

10.3.21 PCS TimeSync Receive Path Data Delay 3: Address 3.1807................................................. 781

10.3.22 PCS TimeSync Receive Path Data Delay 4: Address 3.1808................................................. 781

10.3.23 PCS Transmit Vendor Provisioning 1: Address 3.C400 ........................................................ 781

10.3.24 PCS Transmit Reserved Vendor Provisioning 1: Address 3.C410........................................... 781

10.3.25 PCS Standard Interrupt Mask 1: Address 3.D000............................................................... 782

10.3.26 PCS Standard Interrupt Mask 2: Address 3.D001............................................................... 782

10.3.27 PCS Standard Interrupt Mask 3: Address 3.D002............................................................... 782

10.3.28 PCS Receive Vendor State 1: Address 3.E800 ................................................................... 783

10.3.29 PCS Receive Vendor Alarms 1: Address 3.EC00 ................................................................. 783

10.3.30 PCS Receive Vendor Alarms 10: Address 3.EC09 ............................................................... 784

10.3.31 PCS Vendor Global Interrupt Flags 1: Address 3.FC00 ........................................................ 785

10.3.32 PCS Vendor Global Interrupt Flags 3: Address 3.FC02 ........................................................ 785

10.4 Auto-Negotiation Registers ................................................................................................... 786

10 333369-004

Page 11

Contents—Intel

®

Ethernet Controller X550 Datasheet

10.4.1 Auto-Negotiation Standard Control 1: Address 7.0............................................................. 786

10.4.2 Auto-Negotiation Standard Status 1: Address 7.1.............................................................. 786

10.4.3 Auto-Negotiation Standard Device Identifier 1: Address 7.2 ................................................ 787

10.4.4 Auto-Negotiation Standard Device Identifier 2: Address 7.3 ................................................ 787

10.4.5 Auto-Negotiation Standard Devices in Package 1: Address 7.5 ............................................ 788

10.4.6 Auto-Negotiation Standard Devices in Package 2: Address 7.6 ............................................ 788

10.4.7 Auto-Negotiation Standard Status 2: Address 7.8.............................................................. 789

10.4.8 Auto-Negotiation Standard Package Identifier 1: Address 7.E.............................................. 789

10.4.9 Auto-Negotiation Standard Package Identifier 2: Address 7.F .............................................. 789

10.4.10 Auto-Negotiation Advertisement Register: Address 7.10 ..................................................... 790

10.4.11 Auto-Negotiation Link Partner Base Page Ability Register: Address 7.13................................ 791

10.4.12 Auto-Negotiation Extended Next Page Transmit Register: Address 7.16 ................................ 792

10.4.13 Auto-Negotiation Extended Next Page Unformatted Code Register 1: Address 7.17 ................ 792

10.4.14 Auto-Negotiation Extended Next Page Unformatted Code Register 2: Address 7.18 ................ 793

10.4.15 Auto-Negotiation Link Partner Extended Next Page Ability Register: Address 7.19.................. 793

10.4.16 Auto-Negotiation Link Partner Extended Next Page Unformatted Code Register 1: Address 7.1A 794

10.4.17 Auto-Negotiation Link Partner Extended Next Page Unformatted Code Register 2: Address 7.1B 794

10.4.18 Auto-Negotiation 10GBASE-T Control Register: Address 7.20 .............................................. 794

10.4.19 Auto-Negotiation 10GBASE-T Status Register: Address 7.21 ............................................... 795

10.4.20 Auto-Negotiation Vendor Provisioning 1: Address 7.C400.................................................... 795

10.4.21 Auto-Negotiation Reserved Vendor Provisioning 1: Address 7.C410...................................... 796

10.4.22 Auto-Negotiation Reserved Vendor Provisioning 2: Address 7.C411...................................... 797

10.4.23 Auto-Negotiation Vendor Status 1: Address 7.C800 ........................................................... 798

10.4.24 Auto-Negotiation Reserved Vendor Status 1: Address 7.C810.............................................. 798

10.4.25 Auto-Negotiation Reserved Vendor Status 2: Address 7.C811.............................................. 799

10.4.26 Auto-Negotiation Reserved Vendor Status 3: Address 7.C812.............................................. 800

10.4.27 Auto-Negotiation Reserved Vendor Status 4: Address 7.C813.............................................. 800

10.4.28 Auto-Negotiation Reserved Vendor Status 5: Address 7.C814.............................................. 800

10.4.29 Auto-Negotiation Transmit Vendor Alarms 1: Address 7.CC00 ............................................. 800

10.4.30 Auto-Negotiation Transmit Vendor Alarms 2: Address 7.CC01 ............................................. 801

10.4.31 Auto-Negotiation Standard Interrupt Mask 1: Address 7.D000............................................. 801

10.4.32 Auto-Negotiation Standard Interrupt Mask 2: Address 7.D001............................................. 802

10.4.33 Auto-Negotiation Transmit Vendor Interrupt Mask 1: Address 7.D400 .................................. 802

10.4.34 Auto-Negotiation Transmit Vendor Interrupt Mask 2: Address 7.D401 .................................. 802

10.4.35 Auto-Negotiation Transmit Vendor Interrupt Mask 3: Address 7.D402 .................................. 803

10.4.36 Auto-Negotiation Receive Link Partner Status 1: Address 7.E820......................................... 803

10.4.37 Auto-Negotiation Receive Link Partner Status 4: Address 7.E823......................................... 803

10.4.38 Auto-Negotiation Receive Vendor Alarms 1: Address 7.EC00 ............................................... 804

10.4.39 Auto-Negotiation Receive Vendor Alarms 2: Address 7.EC01 ............................................... 804

10.4.40 Auto-Negotiation Receive Vendor Alarms 3: Address 7.EC02 ............................................... 804

10.4.41 Auto-Negotiation Receive Vendor Alarms 4: Address 7.EC03 ............................................... 804

10.4.42 Auto-Negotiation Receive Vendor Interrupt Mask 1: Address 7.F400..................................... 805

10.4.43 Auto-Negotiation Receive Vendor Interrupt Mask 2: Address 7.F401..................................... 805

10.4.44 Auto-Negotiation Receive Vendor Interrupt Mask 3: Address 7.F402..................................... 805

10.4.45 Auto-Negotiation Receive Vendor Interrupt Mask 4: Address 7.F403..................................... 805

10.4.46 Auto-Negotiation Vendor Global Interrupt Flags 1: Address 7.FC00 ...................................... 806

10.5 100BASE-TX and 1000BASE-T Registers ................................................................................. 807

10.5.1 GbE Standard Device Identifier 1: Address 1D.2................................................................ 807

10.5.2 GbE Standard Device Identifier 2: Address 1D.3................................................................ 807

10.5.3 GbE Standard Devices in Package 1: Address 1D.5 ............................................................ 807

333369-004 11

Page 12

Intel® Ethernet Controller X550 Datasheet—Contents

10.5.4 GbE Standard Vendor Devices in Package 2: Address 1D.6 ................................................. 808

10.5.5 GbE Standard Status 2: Address 1D.8.............................................................................. 808

10.5.6 GbE Standard Package Identifier 1: Address 1D.E.............................................................. 808

10.5.7 GbE Standard Package Identifier 2: Address 1D.F.............................................................. 809

10.5.8 GbE Reserved Provisioning 2: Address 1D.C501 ................................................................ 809

10.6 Global Registers .................................................................................................................. 810

10.6.1 Global Standard Control 1: Address 1E.0 .......................................................................... 810

10.6.2 Global Standard Device Identifier 1: Address 1E.2............................................................. 810

10.6.3 Global Standard Device Identifier 2: Address 1E.3............................................................. 810

10.6.4 Global Standard Devices in Package 1: Address 1E.5 ......................................................... 810

10.6.5 Global Standard Vendor Devices in Package 2: Address 1E.6............................................... 811

10.6.6 Global Standard Status 2: Address 1E.8........................................................................... 812

10.6.7 Global Standard Package Identifier 1: Address 1E.E........................................................... 812

10.6.8 Global Standard Package Identifier 2: Address 1E.F........................................................... 812

10.6.9 Global Firmware ID: Address 1E.20 ................................................................................. 812

10.6.10 Global Diagnostic Provisioning: Address 1E.C400............................................................... 812

10.6.11 Global Thermal Provisioning 2: Address 1E.C421 ............................................................... 813

10.6.12 Global Thermal Provisioning 3: Address 1E.C422 ............................................................... 813

10.6.13 Global Thermal Provisioning 4: Address 1E.C423 ............................................................... 813

10.6.14 Global Thermal Provisioning 5: Address 1E.C424 ............................................................... 813

10.6.15 Global Reserved Provisioning 1: Address 1E.C470.............................................................. 814

10.6.16 Global Reserved Provisioning 3: Address 1E.C472.............................................................. 814

10.6.17 Global Reserved Provisioning 5: Address 1E.C474.............................................................. 815

10.6.18 Global Reserved Provisioning 6: Address 1E.C475.............................................................. 815

10.6.19 Global SMBus 0 Provisioning 6: Address 1E.C485 .............................................................. 816

10.6.20 Global SMBus 1 Provisioning 6: Address 1E.C495 .............................................................. 816

10.6.21 Global Cable Diagnostic Status 1: Address 1E.C800 ........................................................... 816

10.6.22 Global Cable Diagnostic Status 2: Address 1E.C801 ........................................................... 817

10.6.23 Global Cable Diagnostic Status 3: Address 1E.C802 ........................................................... 817

10.6.24 Global Cable Diagnostic Status 4: Address 1E.C803 ........................................................... 818

10.6.25 Global Cable Diagnostic Status 5: Address 1E.C804 ........................................................... 818

10.6.26 Global Cable Diagnostic Status 6: Address 1E.C805 ........................................................... 818

10.6.27 Global Cable Diagnostic Status 7: Address 1E.C806 ........................................................... 818

10.6.28 Global Cable Diagnostic Status 8: Address 1E.C807 ........................................................... 819

10.6.29 Global Thermal Status 1: Address 1E.C820....................................................................... 819

10.6.30 Global Thermal Status 2: Address 1E.C821....................................................................... 819

10.6.31 Global General Status 1: Address 1E.C830 ....................................................................... 819

10.6.32 Global Fault Message: Address 1E.C850 ........................................................................... 820

10.6.33 Global Primary Status: Address 1E.C851 .......................................................................... 820

10.6.34 Global Cable Diagnostic Impedance 1: Address 1E.C880..................................................... 821

10.6.35 Global Cable Diagnostic Impedance 2: Address 1E.C881..................................................... 822

10.6.36 Global Cable Diagnostic Impedance 3: Address 1E.C882..................................................... 823

10.6.37 Global Cable Diagnostic Impedance 4: Address 1E.C883..................................................... 824

10.6.38 Global Status: Address 1E.C884...................................................................................... 824

10.6.39 Global Reserved Status 1: Address 1E.C885 ..................................................................... 825

10.6.40 Global Reserved Status 2: Address 1E.C886 ..................................................................... 825

10.6.41 Global Reserved Status 3: Address 1E.C887 ..................................................................... 825

10.6.42 Global Reserved Status 4: Address 1E.C888 ..................................................................... 826

10.6.43 Global Alarms 1: Address 1E.CC00 .................................................................................. 827

10.6.44 Global Alarms 2: Address 1E.CC01 .................................................................................. 828

12 333369-004

Page 13

Contents—Intel

®

Ethernet Controller X550 Datasheet

10.6.45 Global Alarms 3: Address 1E.CC02 .................................................................................. 829

10.6.46 Global Interrupt Mask 1: Address 1E.D400 ....................................................................... 830

10.6.47 Global Interrupt Mask 2: Address 1E.D401 ....................................................................... 831

10.6.48 Global Interrupt Mask 3: Address 1E.D402 ....................................................................... 832

10.6.49 Global Chip-Wide Standard Interrupt Flags: Address 1E.FC00.............................................. 833

10.6.50 Global Chip-Wide Vendor Interrupt Flags: Address 1E.FC01 ................................................ 834

10.6.51 Global Interrupt Chip-Wide Standard Mask: Address 1E.FF00 .............................................. 835

10.6.52 Global Interrupt Chip-Wide Vendor Mask: Address 1E.FF01................................................. 836

11.0 System Manageability ......................................................................................... 837

11.1 Pass-Through (PT) Functionality ............................................................................................ 837

11.1.1 Supported Topologies .................................................................................................... 838

11.1.2 Pass-Through Packet Routing.......................................................................................... 838

11.2 Components of the Sideband Interface ................................................................................... 839

11.2.1 Physical Layer............................................................................................................... 839

11.2.2 Logical Layer ................................................................................................................ 840

11.3 Packet Filtering ................................................................................................................... 842

11.3.1 Manageability Receive Filtering ....................................................................................... 842

11.3.2 L2 Filters...................................................................................................................... 843

11.3.3 L3/L4 Filtering .............................................................................................................. 844

11.3.4 Flexible 128 Byte Filter .................................................................................................. 846

11.3.5 Configuring Manageability Filters ..................................................................................... 847

11.3.6 Filtering Programming Interfaces..................................................................................... 850

11.3.7 Possible Configurations .................................................................................................. 851

11.3.8 Determining Manageability MAC Address .......................................................................... 852

11.4 OS-to-BMC Traffic ............................................................................................................... 853

11.4.1 Overview ..................................................................................................................... 853

11.4.2 Filtering ....................................................................................................................... 854

11.4.3 Blocking of Network to BMC Flow..................................................................................... 855

11.4.4 OS2BMC and Flow Control .............................................................................................. 855

11.4.5 Statistics...................................................................................................................... 856

11.4.6 OS-to-BMC Enablement ................................................................................................. 856

11.5 SMBus Pass-Through Interface .............................................................................................. 857

11.5.1 General ....................................................................................................................... 857

11.5.2 Pass-Through Capabilities............................................................................................... 857

11.5.3 Port to SMBus Mapping .................................................................................................. 857

11.5.4 Automatic Ethernet ARP Operation .................................................................................. 858

11.5.5 SMBus Transactions....................................................................................................... 858

11.5.6 SMBus Notification Methods............................................................................................ 863

11.5.7 Receive Pass-Through Flow ............................................................................................ 866

11.5.8 Transmit Pass-Through Flow........................................................................................... 866

11.5.9 SMBus Link State Control............................................................................................... 868

11.5.10 SMBus ARP Transactions................................................................................................ 868

11.5.11 SMBus Pass-Through Transactions................................................................................... 871

11.5.12 Example Configuration Steps .......................................................................................... 893

11.5.13 SMBus Troubleshooting.................................................................................................. 902

11.6 NC-SI Pass-Through Interface ............................................................................................... 905

11.6.1 Overview ..................................................................................................................... 905

11.6.2 NC-SI Standard Support ................................................................................................ 909

11.6.3 NC-SI Mode — Intel Specific Commands........................................................................... 911

11.6.4 Asynchronous Event Notifications .................................................................................... 964

333369-004 13

Page 14

Intel® Ethernet Controller X550 Datasheet—Contents

11.6.5 Querying Active Parameters............................................................................................ 964

11.6.6 Resets ......................................................................................................................... 965

11.6.7 Advanced Workflows...................................................................................................... 965

11.6.8 External Link Control via NC-SI ....................................................................................... 968

11.7 MCTP ................................................................................................................................ 970

11.7.1 MCTP Overview............................................................................................................. 970

11.7.2 NC-SI to MCTP Mapping ................................................................................................. 971

11.7.3 MCTP Over PCIe............................................................................................................ 976

11.7.4 MCTP Over SMBus......................................................................................................... 978

11.7.5 NC-SI Over MCTP.......................................................................................................... 979

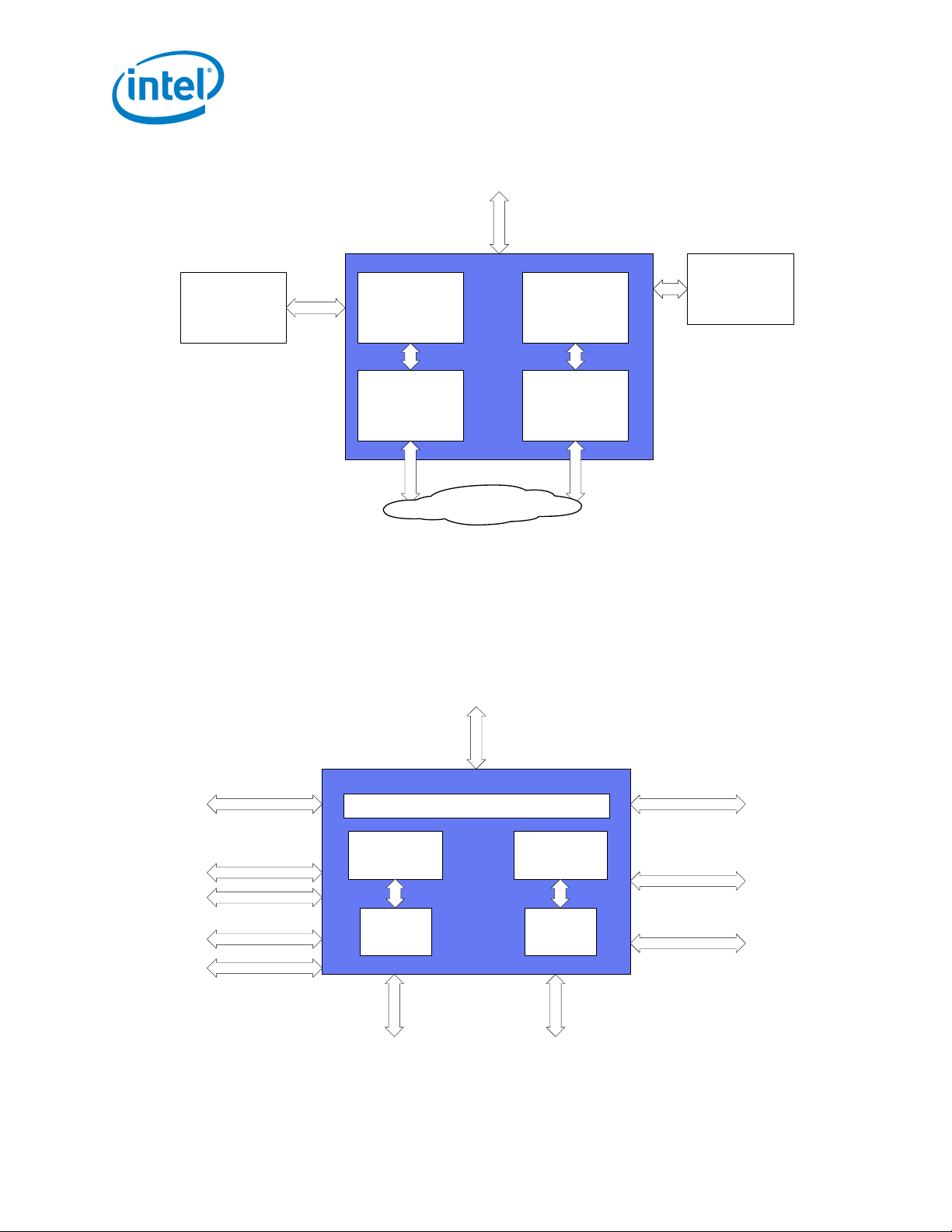

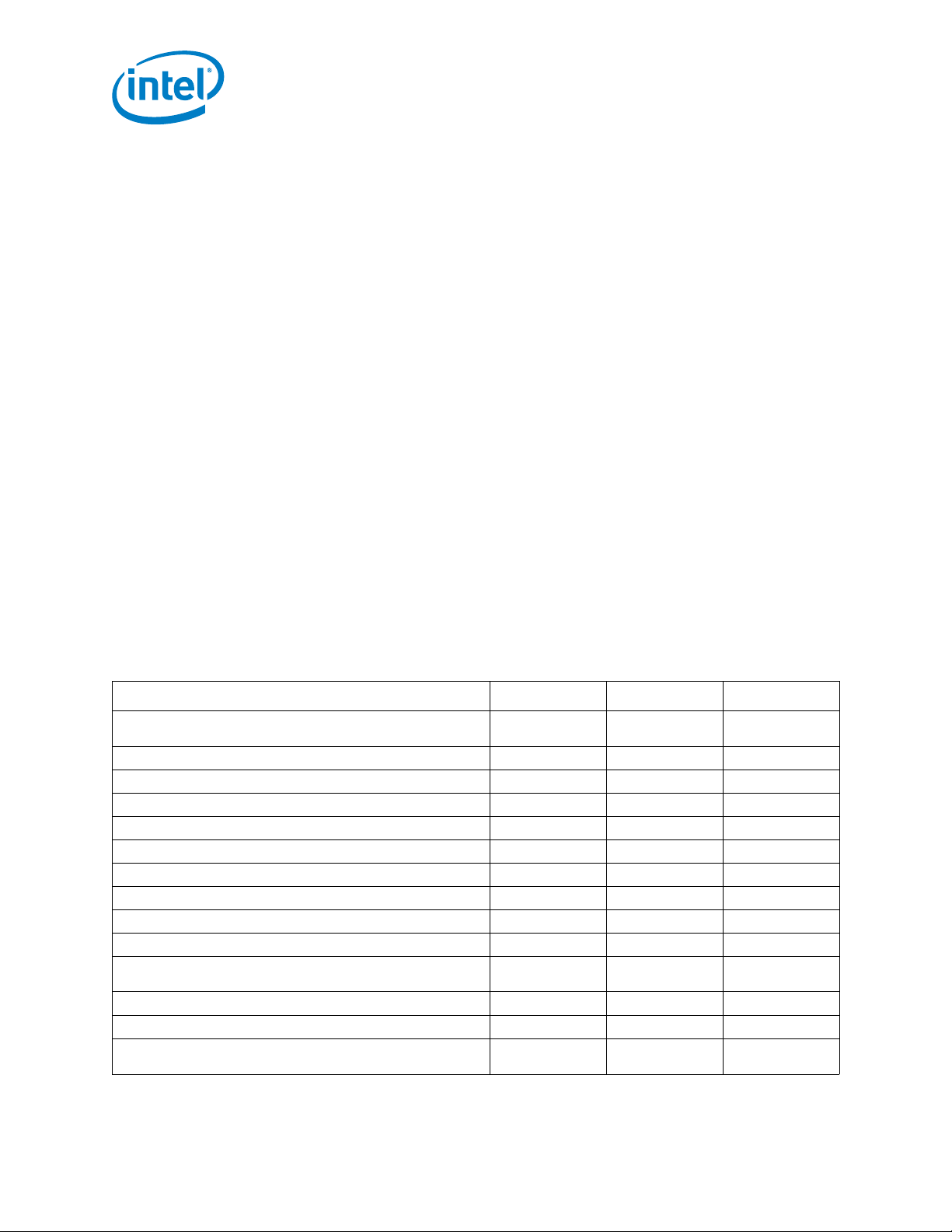

11.7.6 MCTP Programming ....................................................................................................... 981