Page 1

Intel® X38 Express Chipset

Memory Technology and

Configuration Guide

White Paper

January 2008

Document Number: 318469-002

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL

IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT

AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY

WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL

PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY,

OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended

for use in medical, life saving , or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel

reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from

future changes to them.

The Intel

product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product o rder.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other coun tries.

*Other names and brands may be claimed as the property of others.

Copyright © 2007 - 2008, Intel Corporation

®

X38 Express Chipset MCH component may contain design defects or errors known as errata which may cause the

®

PRODUCTS. NO LICENSE, EXPRESS OR

2 White Paper

Page 3

Contents

1 Introduction.....................................................................................................5

2 Technology Enhancements of Intel® Fast Memory Access (Intel® FMA) .....................6

2.1 Just in Time Command Scheduling............................................................6

2.2 Command Overlap..................................................................................6

2.3 Out of Order Scheduling..........................................................................7

2.4 Opportunistic Writes ...............................................................................7

3 Supported Memory Technologies and Configurations..............................................8

3.1 Memory Technology Supported.................................................................8

3.2 DRAM Device Timing Support.................................................................10

3.3 ECC Support........................................................................................10

3.4 Valid Front Side Bus and Memory Speeds.................................................11

3.5 System Memory DIMM Configuration Support...........................................11

4 Memory Organization and Operating Modes ........................................................12

4.1 Single-Channel Mode............................................................................12

4.2 Dual Channel Modes ............................................................................. 12

4.2.1 Dual Channel Symmetric Mode..................................................12

4.2.2 Dual Channel Asymmetric Modes...............................................13

Tables

Table 3-1. Memory Technology Support Details.....................................................9

Table 3-2. DDR2 and DDR3 DRAM Device Timing Support.....................................10

Table 3-3. Intel® X38 Valid FSB/Memory Speed Configurations..............................11

Table 4-1. Sample Dual Channel Symmetric Organization Mode.............................13

Table 4-2. Sample Dual Channel Stacked Asymmetric Organization Mode................13

Table 4-3. Sample Dual Channel L-Shaped Asymmetric Organization Mode..............14

White Paper 3

Page 4

Revision History

Revision

Number

Description Revision

Date

-001

-002

Initial release

Corrected DDR3 DIMM Module Support

Added Configuration details

October 2007

January 2008

§

4 White Paper

Page 5

Introduction

1 Introduction

This document details the Intel® X38 Express Chipset system memory technology

enhancements, supported memory configurations, and memory organizations. It is

intended for a technical audience interested in learning about the performance

enhancements and simplified population rules offered by Intel

and Intel

Chipset.

®

Flex Memory Technology in the platforms based on the Intel X38 Express

®

Fast Memory Access

White Paper 5

Page 6

Technology Enhancements of Intel® Fast Memory Access (Intel® FMA)

2 Technology Enhancements of

®

Intel

(Intel

Fast Memory Access

®

FMA)

This chapter details Intel® X38 Express Chipset technology enhancements of its

memory controller known as Intel

controller is located on the chipset’s 82X38 Memory Controller Hub (MCH) component.

With the growing reliance on faster and less latent memory technologies for today’s

high performance platforms, it has become necessary to not only increase system

memory transfer rate speeds, but to also streamline usage of the memory controller

protocol in novel and intelligent ways to decrease latency and optimize memory

bandwidth. To do this, several Intel technologies, known collectively as Intel

have been included in this generation of Intel’s chipsets.

The following sections outline and explain the technology enhancements: Just In Time

Scheduling, Command Overlap, Out of Order Scheduling, and Opportunistic Writes.

®

Fast Memory Access (Intel® FMA). The memory

2.1 Just in Time Command Scheduling

The Intel X38 Express Chipset has an advanced command scheduler where all pending

requests are examined simultaneously to determine the most efficient request to be

issued next. The most efficient request is picked from all pending requests and issued

to system memory Just In Time to make optimal use of Command Overlapping. Thus,

instead of having all memory access requests go individually through an arbitration

mechanism forcing requests to be executed one at a time, they can be started without

interfering with the current request allowing for concurrent issuing of requests. This

allows for the optimization of bandwidth and reducing of latency while retaining

system memory protocol.

®

FMA,

2.2 Command Overlap

Command Overlap allows for the insertion of the DRAM commands between the

Activate, Precharge, and Read/Write commands normally used, as long as the inserted

commands do not affect the currently executing command. This allows for situations

where multiple commands can be issued in an overlapping manner, increasing the

efficiency of system memory protocol.

6 White Paper

Page 7

Technology Enhancements of Intel® Fast Memory Access (Intel® FMA)

2.3 Out of Order Scheduling

Leveraging Just In Time Scheduling and Command Overlap, the Intel X38 Express

Chipset continuously monitors pending requests to system memory for the best use of

bandwidth and reduction of latency. If there are multiple requests to the same open

page, these requests would be launched in a back to back manner to make optimum

use of the open memory page. This ability to reorder requests on the fly allows the

Intel X38 Express Chipset to further reduce latency and increase bandwidth efficiency.

This is especially important for helping overcome the in-order manner of the Front

Side Bus between the Intel X38 Express Chipset and the processor to minimize

processor starvation.

2.4 Opportunistic Writes

Processor requests for memory reads usually are weighted more heavily than writes to

memory to avoid cases of starving the processor of data to process while the writes

are issued to system memory. Instead of having writes issued to a pending queue to

be flushed to memory when certain watermarks are reached, which could starve the

processor of data while it waits for the write flush to finish, the Intel X38 Express

Chipset monitors system memory requests and issues pending write requests to

memory at times when they will not impact memory read requests. This allows for an

almost continuous flow of data to the processor for processing.

White Paper 7

Page 8

Supported Memory Technologies and Configurations

3 Supported Memory

Technologies and

Configurations

3.1 Memory Technology Supported

The X38 Express Chipset supports the following DDR2 and DDR3 Data Transfer Rates,

DIMM Modules, and DRAM Device Technologies:

• DDR2 Data Transfer Rates:

⎯ 667 (PC2-5300) and 800 (PC2-6400)

• DDR3 Data Transfer Rates:

⎯ 800 (PC3-6400), 1067 (PC3-8500), and 1333 (PC3-10600)

• DDR2 DIMM Modules:

⎯ Raw Card C - Single Sided x16 un-buffered non-ECC

⎯ Raw Card D - Single Sided x8 un-buffered non-ECC

⎯ Raw Card E - Double Sided x8 un-buffered non-ECC

⎯ Raw Card F - Single Sided x8 un-buffered ECC

⎯ Raw Card G - Double Sided x8 un-buffered ECC

• DDR3 DIMM Modules:

⎯ Raw Card A - Single Sided x8 un-buffered non-ECC

⎯ Raw Card B - Double Sided x8 un-buffered non-ECC

⎯ Raw Card C - Single Sided x16 un-buffered non-ECC

• DDR2 and DDR3 DRAM Device Technology:

⎯ 512 Mb and 1 Gb

8 White Paper

Page 9

Supported Memory Technologies and Configurations

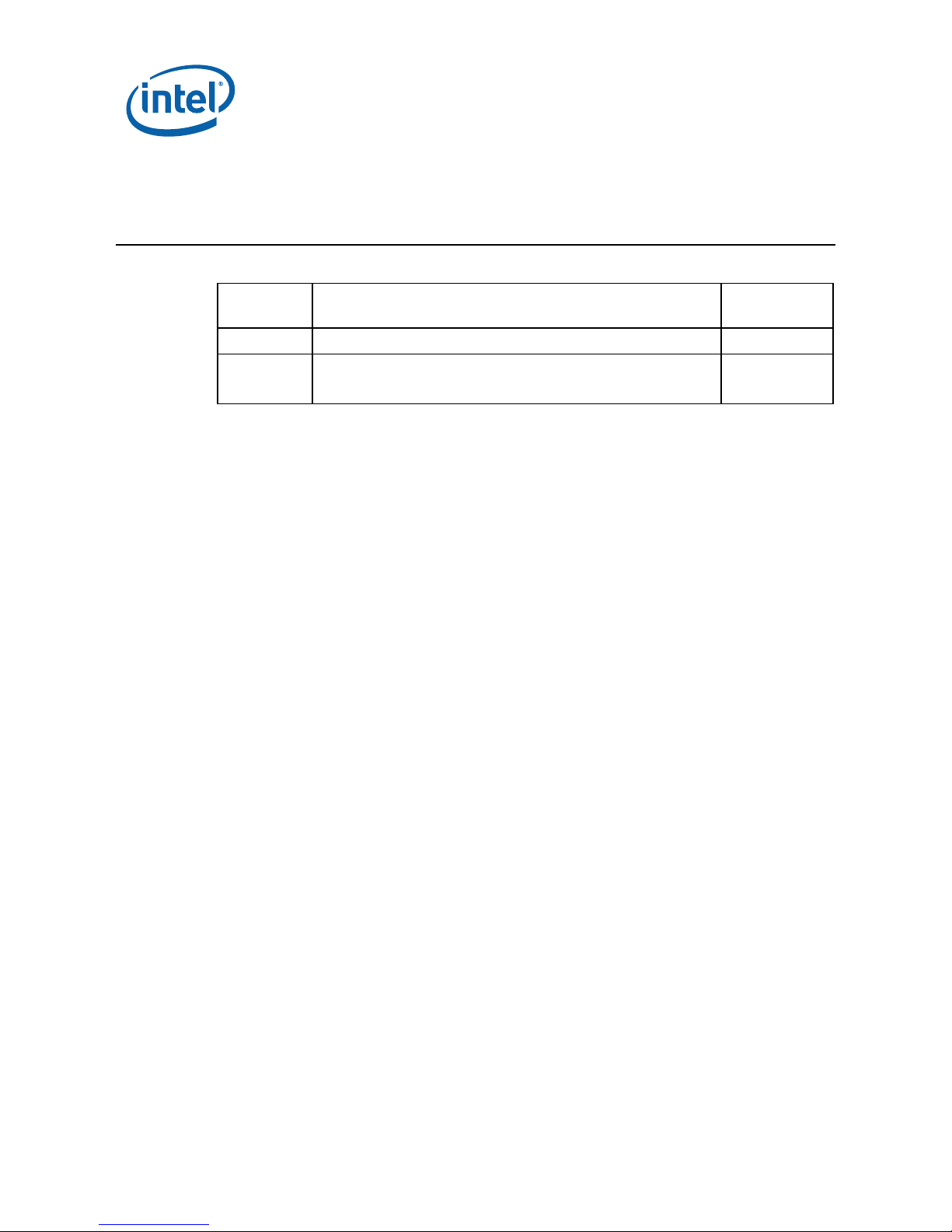

Table 3-1. Memory Technology Support Details

Mem.

Type

DDR2

667

and

800

DDR3

800,

1067,

and

1333

Raw

Card

Ver.

C

D

E

F

G

A

B

C

DIMM

Cap.

256 MB 512 MB 32M X 16 4 1 13/10 4 8K

512 MB 1 GB 64M X 16 4 1 13/10 8 8K

512 MB 512 MB 64M X 8 8 1 14/10 4 8K

1 GB 1 GB 128M X 8 8 1 14/10 8 8K

1 GB 512 MB 64M X 8 16 2 14/10 4 8K

2 GB 1 GB 128M X 8 16 2 14/10 8 8K

512 MB 512Mb 64M X 8 9 1 14/10 4 8K

1 GB 1Gb 128M X 8 9 1 14/10 8 8K

1 GB 512Mb 64M X 8 18 2 14/10 4 8K

2 GB 1Gb 128M X 8 18 2 14/10 8 8K

512 MB 512 MB 64M X 8 8 1 13/10 8 8K

1 GB 1 GB 128M X 8 8 1 14/10 8 8K

1 GB 512 MB 64M X 8 16 2 13/10 8 8K

2 GB 1 GB 128M X 8 16 2 14/10 8 8K

256 MB 512 MB 32M X 16 4 1 12/10 8 8K

512 MB 1 GB 64M X 16 4 1 13/10 8 8K

DRAM

Device

Tech.

DRAM

Org.

# of

DRAM

Devices

# of

Physical

Device

Ranks

# of

Row /Col

Address

Bits

# of

Banks

Inside

DRAM

Page

Size

White Paper 9

Page 10

Supported Memory Technologies and Configurations

3.2 DRAM Device Timing Support

The X38 Express Chipset supports the following DDR2 and DDR3 DRAM Device Speed

Bin and Write Latency (WL) Timings on the main memory interface.

Table 3-2. DDR2 and DDR3 DRAM Device Timing Support

Memory

Type

DDR2

DDR3

DRAM Data

667 MT/s 5 5 5 4 tCK

800 MT/s 5 5 5 4 tCK

800 MT/s 6 6 6 5 tCK

800 MT/s 5 5 5 5 tCK

800 MT/s 6 6 6 5 tCK

1067 MT/s 7 7 7 6 tCK

1067 MT/s 8 8 8 6 tCK

1333 MT/s 8 8 8 7 tCK

1333 MT/s 9 9 9 7 tCK

1333 MT/s 10 10 10 7 tCK

3.3 ECC Support

For DDR3 the X38 Express Chipset does NOT support ECC, does not support ECC unbuffered DIMMs, and it does not support any memory configuration that mixes nonECC with ECC un-buffered DIMMs.

For DDR2 the X38 Express Chipset does support ECC and ECC un-buffered DIMMs but

it does NOT support any memory configuration that mixes non-ECC with ECC unbuffered DIMMs.

Rate

tCL t

t

RCD

WL Units

RP

See Section

10 White Paper

3.1 for un-buffered DIMM support details.

Page 11

Supported Memory Technologies and Configurations

3.4 Valid Front Side Bus and Memory Speeds

The X38 Express Chipset supports the following Front Side Bus (FSB) and system

memory speed configurations.

®

Table 3-3. Intel

X38 Valid FSB/Memory Speed Configurations

Memory

Type

DDR2

DDR3

FSB

1333

MHz

1333

MHz

1067

MHz

1067

MHz

800 MHz 800 MT/s 6.4 GB/s 12.8 GB/s

800 MHz 667 MT/s 5.3 GB/s 10.6 GB/s

1333

MHz

1333

MHz

1333

MHz

1067

MHz

1067

MHz

800 MHz 800 MT/s 6.4 GB/s 12.8 GB/s

DRAM Data

Rate

800 MT/s 6.4 GB/s 12.8 GB/s

667 MT/s 5.3 GB/s 10.6 GB/s

800 MT/s 6.4 GB/s 12.8 GB/s

667 MT/s 5.3 GB/s 10.6 GB/s

1333 MT/s 10.5 GB/s 21.0 GB/s

1067 MT/s 8.5 GB/s 17.0 GB/s

800 MT/s 6.4 GB/s 12.8 GB/s

1067 MT/s 8.5 GB/s 17.0 GB/s

800 MT/s 6.4 GB/s 12.8 GB/s

Single

Channel Peak

Bandwidth

Dual Channel

Peak

Bandwidth

Note: The X38 Express Chipset does not support system memory frequencies that exceed

the frequency of the Front Side Bus. If memory with higher frequency capabilities than

that of the FSB is populated, the memory will be under-clocked to align with the FSB.

3.5 System Memory DIMM Configuration Support

The X38 Express Chipset directly supports one or two channels of DDR2 or DDR3

memory with the following DIMM configurations:

⎯ Supports one or two DDR2 or DDR3 DIMM modules per channel.

White Paper 11

§

Page 12

Memory Organization and Operating Modes

4 Memory Organization and

Operating Modes

The Intel X38 Express Chipset memory interface is designed with Intel® Flex Memory

Technology so that it can be can be configured to support single-channel or dualchannel DDR2 or DDR3 memory configurations. Depending upon how the DIMMs are

populated in each memory channel, a number of different configurations can exist for

DDR2 or DDR3.

The following sections explain and show the different memory configurations that are

supported by the X38 Express Chipset.

4.1 Single-Channel Mode

In this mode, all memory cycles are directed to a single channel.

Single channel mode is used when either Channel-0 or Channel-1 DIMMs are

populated in any order, but not both.

4.2 Dual Channel Modes

4.2.1 Dual Channel Symmetric Mode

This mode provides maximum performance on real applications. Addresses are pingponged between the channels after each cache line (64 byte boundary). If there are

two requests, and the second request is to an address on the opposite channel from

the first, that request can be sent before data from the first request has returned. If

two consecutive cache lines are requested, both may be retrieved simultaneously,

since they are ensured to be on opposite channels.

Dual channel symmetric mode is used when both Channel-0 and Channel-1 DIMMs are

populated in any order with the total amount of memory in each channel being the

same, but the DRAM device technology and width may vary from one channel to the

other.

Table 4-1 is a sample dual channel symmetric memory configuration showing the rank

organization.

12 White Paper

Page 13

Memory Organization and Operating Modes

Table 4-1. Sample Dual Channel Symmetric Organization Mode

Rank

Rank 3 0 MB 2560 MB 0 MB 2560 MB

Rank 2 256 MB 2560 MB 256 MB 2560 MB

Rank 1 512 MB 2048 MB 512 MB 2048 MB

Rank 0 512 MB 1024 MB 512 MB 1024 MB

Channel 0

Population

Cumulative Top

Address in Channel 0

Channel 1

Population

4.2.2 Dual Channel Asymmetric Modes

4.2.2.1 Stacked Asymmetric Mode

In this addressing mode addresses start in channel-0 and stay there until the end of

the highest rank in channel-0, and then addresses continue from the bottom of

channel-1 to the top.

This mode is used when both Channel-0 and Channel-1 DIMMs are populated in any

order with the total amount of memory in each channel being different.

Table 4-2 is a sample dual channel stacked asymmetric memory configuration

showing the rank organization.

Table 4-2. Sample Dual Channel Stacked Asymmetric Organization Mode

Cumulative

Top Address

in Channel 1

Rank

Rank 3 0 MB 1280 MB 0 MB 2304 MB

Rank 2 256 MB 1280 MB 0 MB 2304 MB

Rank 1 512 MB 1024 MB 512 MB 2304 MB

Rank 0 512 MB 512 MB 512 MB 1792 MB

White Paper 13

Channel 0

Population

Cumulative

Top Address in

Channel 0

Channel 1

Population

Cumulative

Top Address

in Channel 1

Page 14

Memory Organization and Operating Modes

4.2.2.2 L-shaped Asymmetric Mode

In this addressing mode the lowest DRAM memory is mapped to dual channel

operation and the top most DRAM memory is mapped to single channel operation. In

this mode the system can run at one zone of dual channel mode and one zone of

single channel mode simultaneously across the whole memory array.

This mode is used when both Channel-0 and Channel-1 DIMMs are populated in any

order with the total amount of memory in each channel being different.

Table 4-3 is a sample dual channel L-shaped asymmetric memory configuration

showing the rank organization.

Table 4-3. Sample Dual Channel L-Shaped Asymmetric Organization Mode

Rank

Rank 3 0 MB 2048 MB 0 MB 2304 MB

Rank 2 0 MB 2048 MB 256 MB 2304 MB

Rank 1 512 MB 2048 MB 512 MB 2048 MB

Rank 0 512 MB 1024 MB 512 MB 1024 MB

Channel 0

Population

Cumulative

Top Address in

Channel 0

Channel 1

Population

Cumulative

Top Address

in Channel 1

§

14 White Paper

Loading...

Loading...