Intel X3350 - Xeon 2.66 Ghz 12M L2 Cache 1333MHz FSB LGA775 Quad-Core Processor, X3350 2.66 L2 1333MHz LGA775 Design Manual

Page 1

Intel® Xeon® Processor

C5500/C3500 Series and LGA1366

Socket

Thermal/Mechanical Design Guide

August 2010

Order Number: 323107-002US

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED,

BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS

PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER,

AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING T O SALE AND/OR USE OF INTEL PRODUCT S INCLUDING

LIABILITY OR WARRANTIES RELA TING T O FITNES S FOR A PARTICULAR PURPOSE, MERCHANT ABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life savin g, or

life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel

reserves these for future definition and shall have no responsibility whatsoev er for conflicts or incompatibilities arising from future

changes to them.

The Intel

may cause the product to deviate from published specifications. Current characterized errata are available on request.

®

Xeon® Processor C5500/C3500 Series and LGA1366 socket may contain design defects or errors known as errata which

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

The code name “Picket Post" presented in this document are only for use by Intel to iden tify pr odu cts, technolo gie s, or serv ice s in

development, that have not been made commercially available to the public, i.e., announced, launched or shipped. They are not

commercial names for products or services and are not intended to function as trademarks.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S and other countries.

* Other brands and names may be claimed as the property of others.

Copyright © 2010, Intel Corporation.

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Thermal/Mechanical Design Guide August 2010

2 Order Number: 323107-002US

Page 3

Contents

1Introduction..............................................................................................................8

1.1 Reference Documents......................... ......................... .. .......................... .. ..........9

1.2 Definition of Terms..............................................................................................9

2 Package Mechanical Specifications ..........................................................................11

2.1 Package Mechanical Specifications.......................................................................11

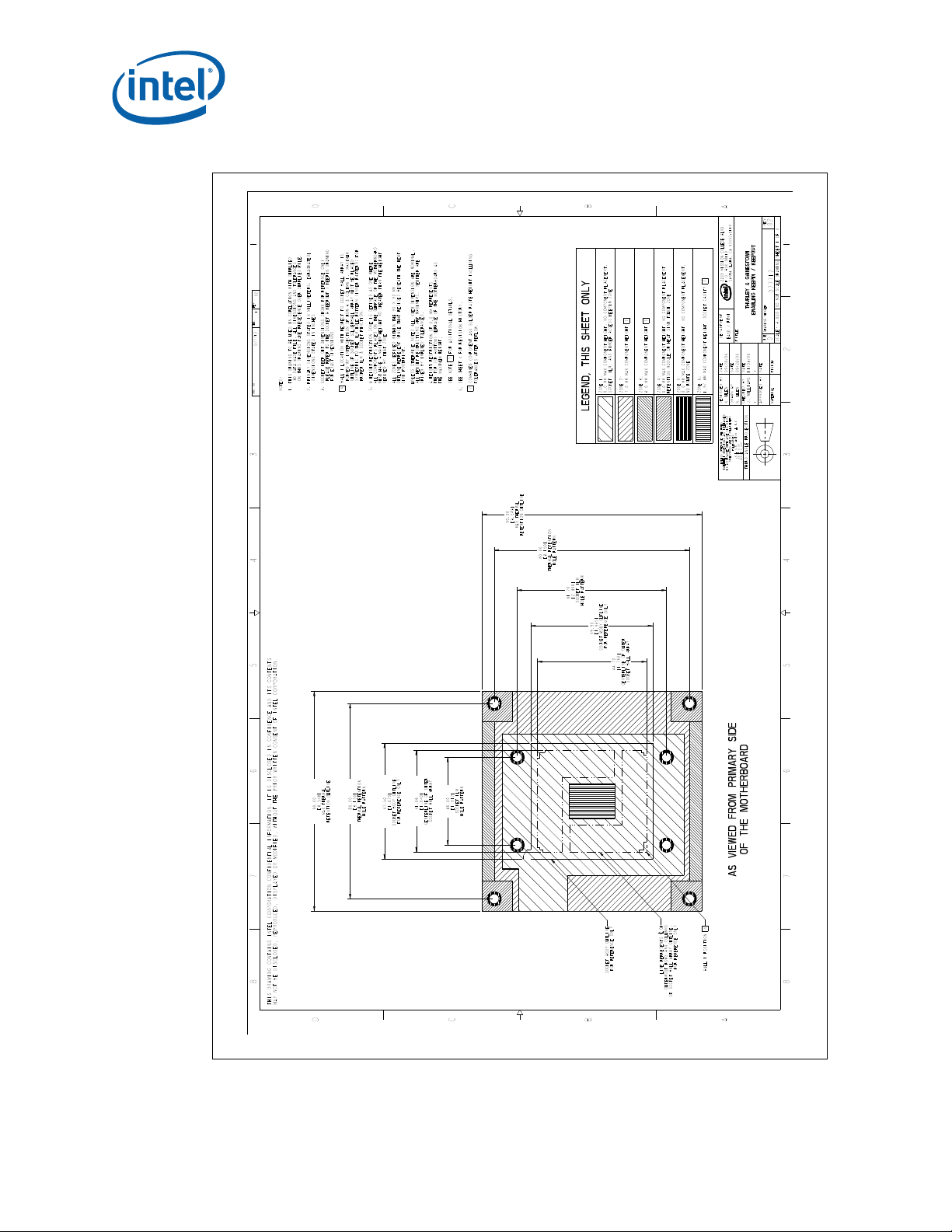

2.1.1 Package Mechanical Drawing.................. .. ........................... .....................12

2.1.2 Processor Component Keep-Out Zones..................................... ... .. .. ..........15

2.1.3 Package Loading Specifications ......................................... .. .. ...................15

2.1.4 Package Handling Guidelines.............................. .. ... .. ........................... .. ..15

2.1.5 Package Insertion Specifications...............................................................15

2.1.6 Processor Mass Specification....................................................................16

2.1.7 Processor Materials.................................................................................16

2.1.8 Processor Markings.................................................................................16

2.1.9 Processor Land Coordinates.....................................................................17

3 LGA1366 Socket ......................................................................................................18

3.1 Board Layout....................................................................................................20

3.2 Attachment to Motherboard................................................................................21

3.3 Socket Components...........................................................................................21

3.3.1 Socket Body Housing..............................................................................21

3.3.2 Solder Balls...........................................................................................21

3.3.3 Contacts ...............................................................................................22

3.3.4 Pick and Place Cover...............................................................................22

3.4 Package Installation / Removal ...........................................................................23

3.4.1 Socket Standoffs and Package Seating Plane..............................................23

3.5 Durability.........................................................................................................24

3.6 Markings..........................................................................................................24

3.7 Component Insertion Forces ...............................................................................24

3.8 Socket Size ......................................................................................................24

3.9 LGA1366 Socket NCTF Solder Joints.....................................................................24

4 Independent Loading Mechanism (ILM)...................................................................26

4.1 Design Concept.................................................................................................26

4.1.1 ILM Cover Assembly Design Overview.......................................................26

4.1.2 ILM Back Plate Design Overview...............................................................27

4.2 Assembly of ILM to a Motherboard.......................................................................28

5 LGA1366 Socket and ILM Electrical, Mechanical and Environmental Specifications .. 31

5.1 Component Mass...............................................................................................31

5.2 Package/Socket Stackup Height ..........................................................................31

5.3 Socket Maximum Temperature............................................................................31

5.4 Loading Specifications.................................... .. .. ................................................33

5.4.1 Board Deflection Guidance.......................................................................33

5.5 Electrical Requirements......................................................................................34

5.6 Environmental Requirements ............................................................................ ..35

6 Thermal Specifications ............................................................................................36

6.1 Package Thermal Specifications...................................................... .. ...................36

6.1.1 Thermal Specifications ............................................................................36

6.1.2 Thermal Metrology .................................................................................47

6.2 Processor Thermal Features................................................................................48

6.2.1 Processor Temperature ...........................................................................48

6.2.2 Adaptive Thermal Monitor........................................................................48

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 3

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 4

6.2.3 THERMTRIP# Signal...................................... ..........................................51

6.3 Platform Environment Control Interface (PECI)......................................................51

6.3.1 Introduction...........................................................................................51

6.3.2 PECI Specifications .................................................................................53

7Thermal Solutions....................................................................................................54

7.1 Performance Targets....................................................................... .. .. ...............54

7.2 Heat Pipe Considerations ....................................................................................56

7.3 Assembly..........................................................................................................57

7.3.1 Thermal Interface Material (TIM) ........................................... .. .. ... ............58

7.4 Structural Considerations....................................................................................58

7.5 Thermal Design........................................................... .. .. .......................... .. .. ....59

7.5.1 Thermal Characterization Parameter..........................................................59

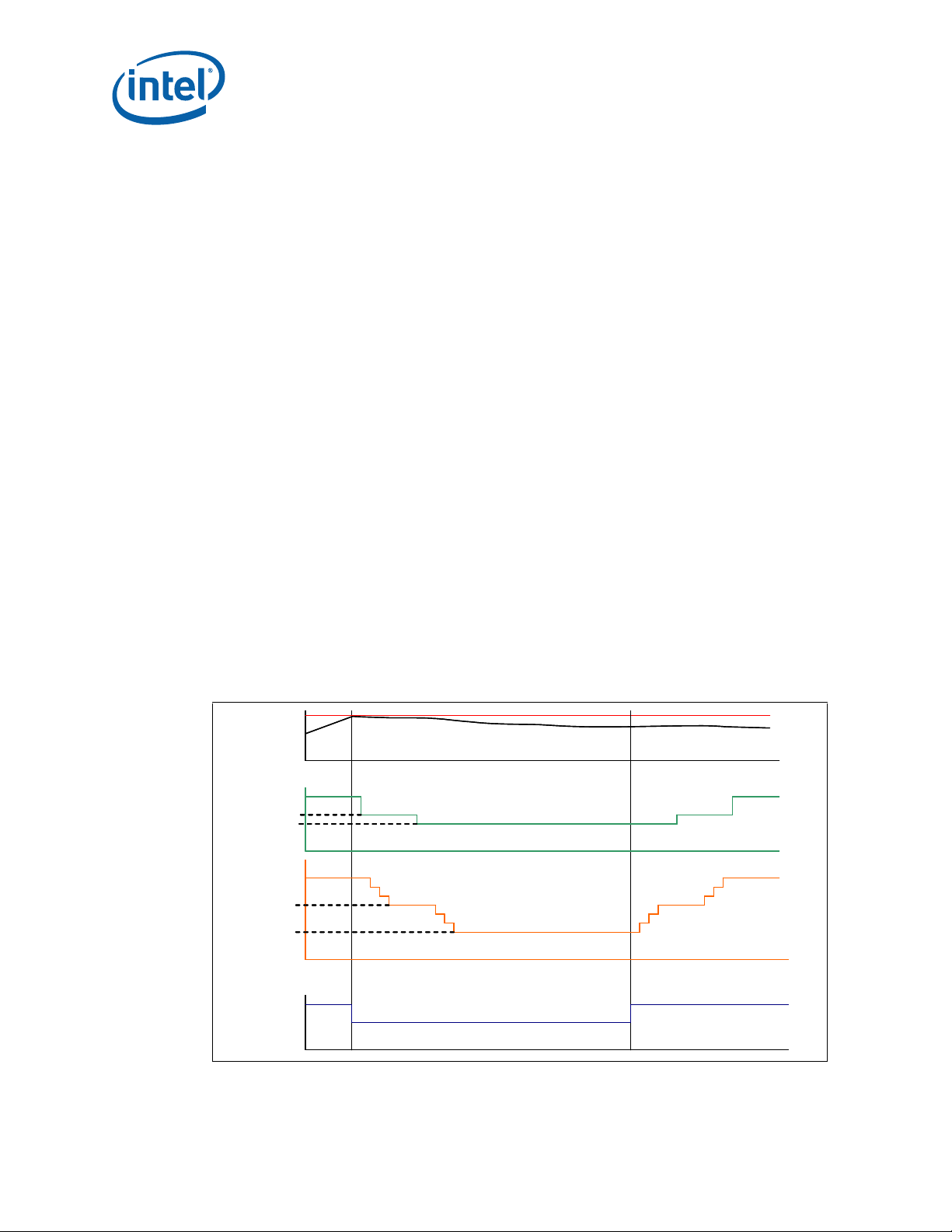

7.5.2 NEBS Thermal Profile ..............................................................................60

7.5.3 Power Thermal Utility ..............................................................................61

7.6 Thermal Features..................... .......................... .. .. ......................... .. .. ...............61

7.6.1 Fan Speed Control ................................................ ... ......................... .. ....61

7.6.2 PECI Averaging and Catastrophic Thermal Management...............................62

7.6.3 Intel® Turbo Boost Technology............................................ .....................62

7.6.4 Absolute Processor Temperature...............................................................63

7.6.5 Custom Heat Sinks For UP ATCA...............................................................63

8 Quality and Reliability Requirements .......................................................................66

8.1 Use Conditions ..................................................................................................66

8.2 Intel Reference Component Validation ..................................................................67

8.2.1 Board Functional Test Sequence ...............................................................67

8.2.2 Post-Test Pass Criteria.............................................................................68

8.2.3 Recommended BIOS/Processor/Memory Test Procedures .............................68

8.3 Material and Recycling Requirements....................................................................68

A Component Suppliers...............................................................................................70

B Mechanical Drawings ...............................................................................................72

C Socket Mechanical Drawings....................................................................................89

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Thermal/Mechanical Design Guide August 2010

4 Order Number: 323107-002US

Page 5

Figures

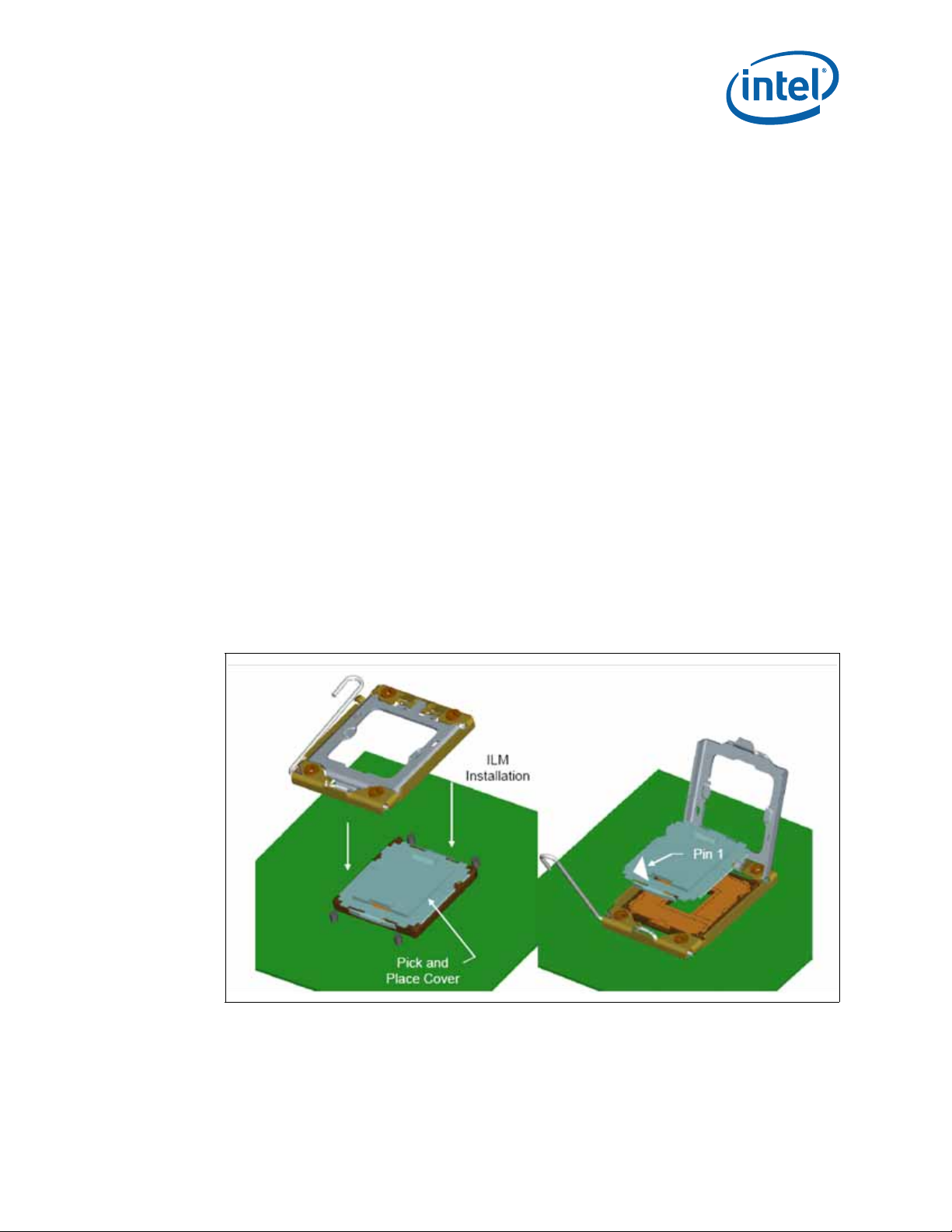

1-1 Intel® Xeon® Processor C5500/C3500 Series Socket Stack-up .......................................8

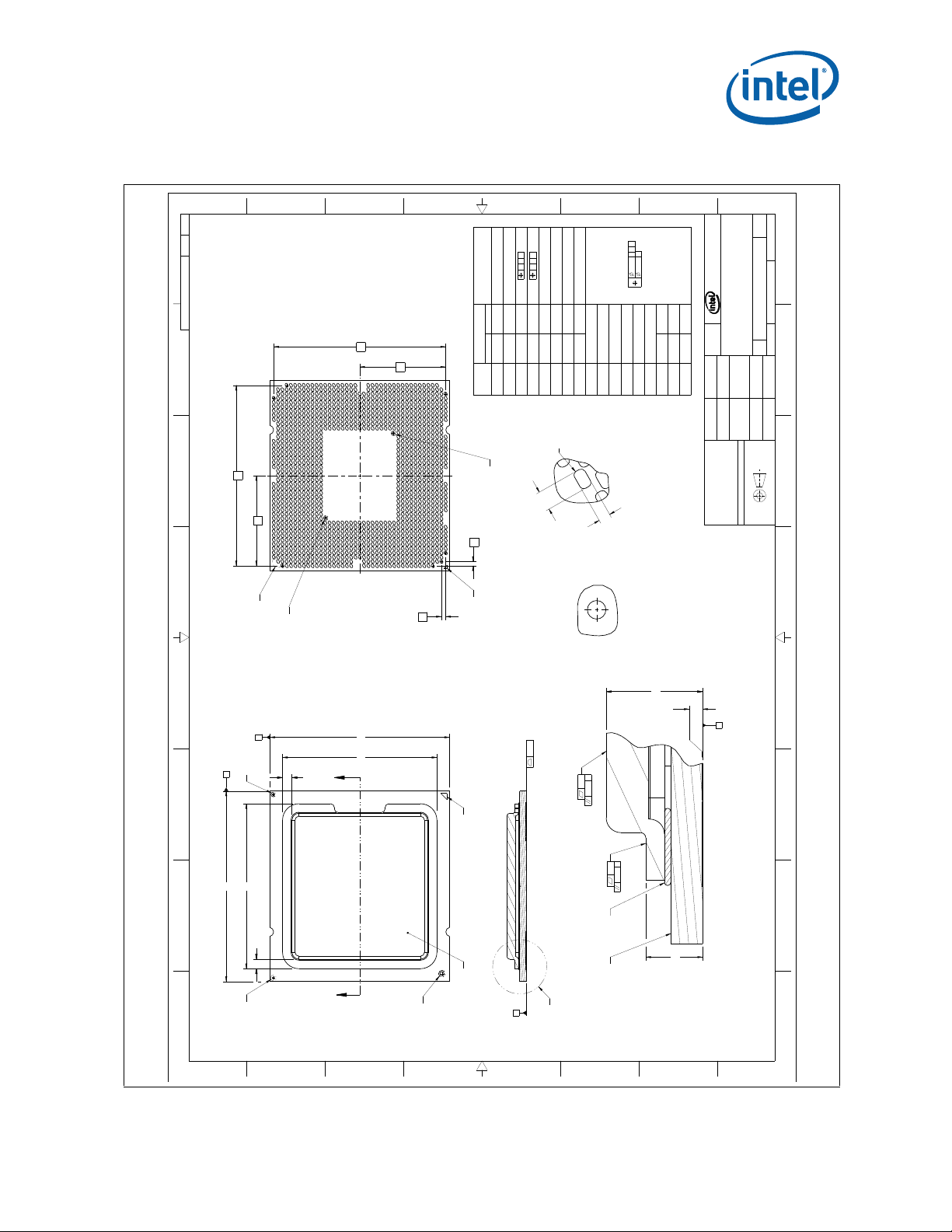

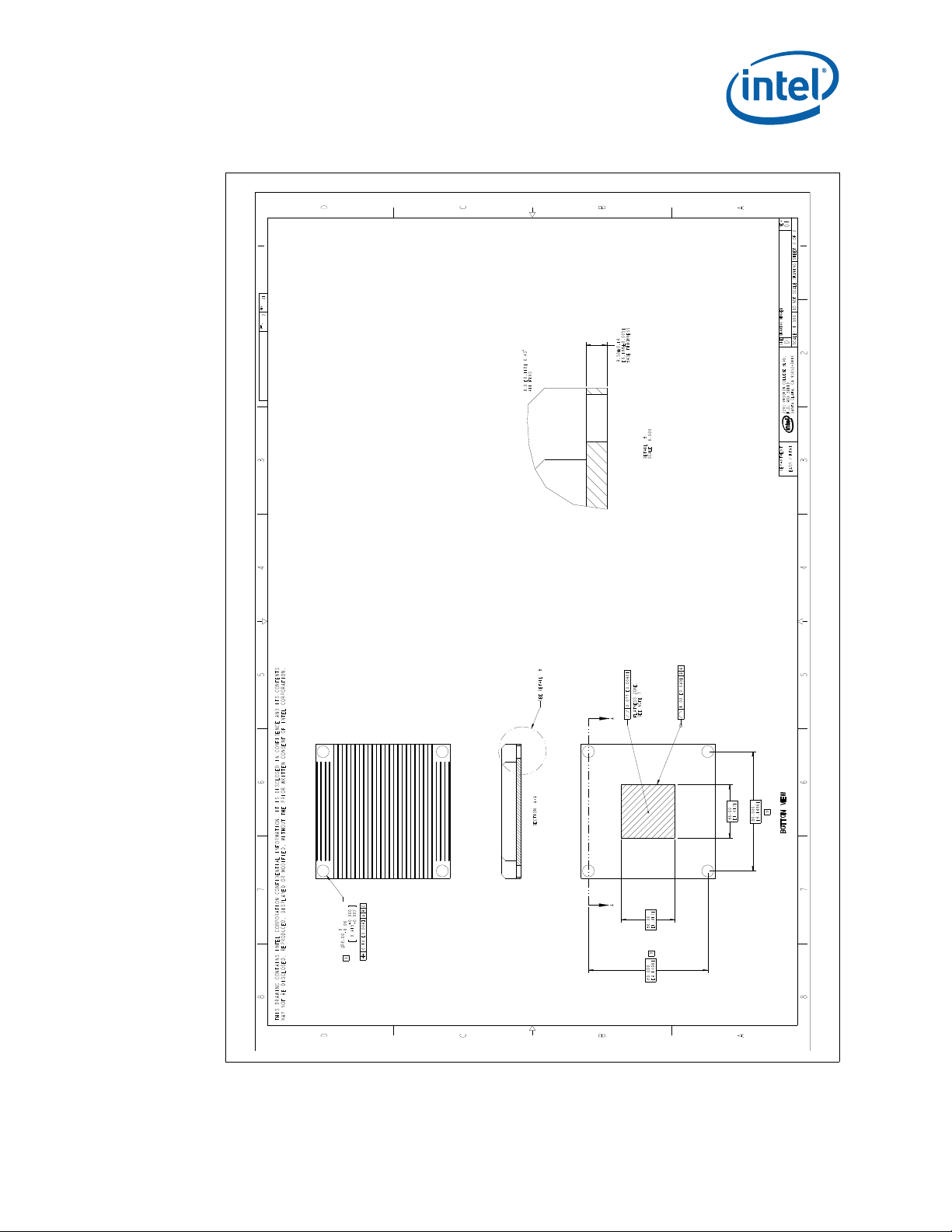

2-1 Processor Package Assembly Sketch.........................................................................11

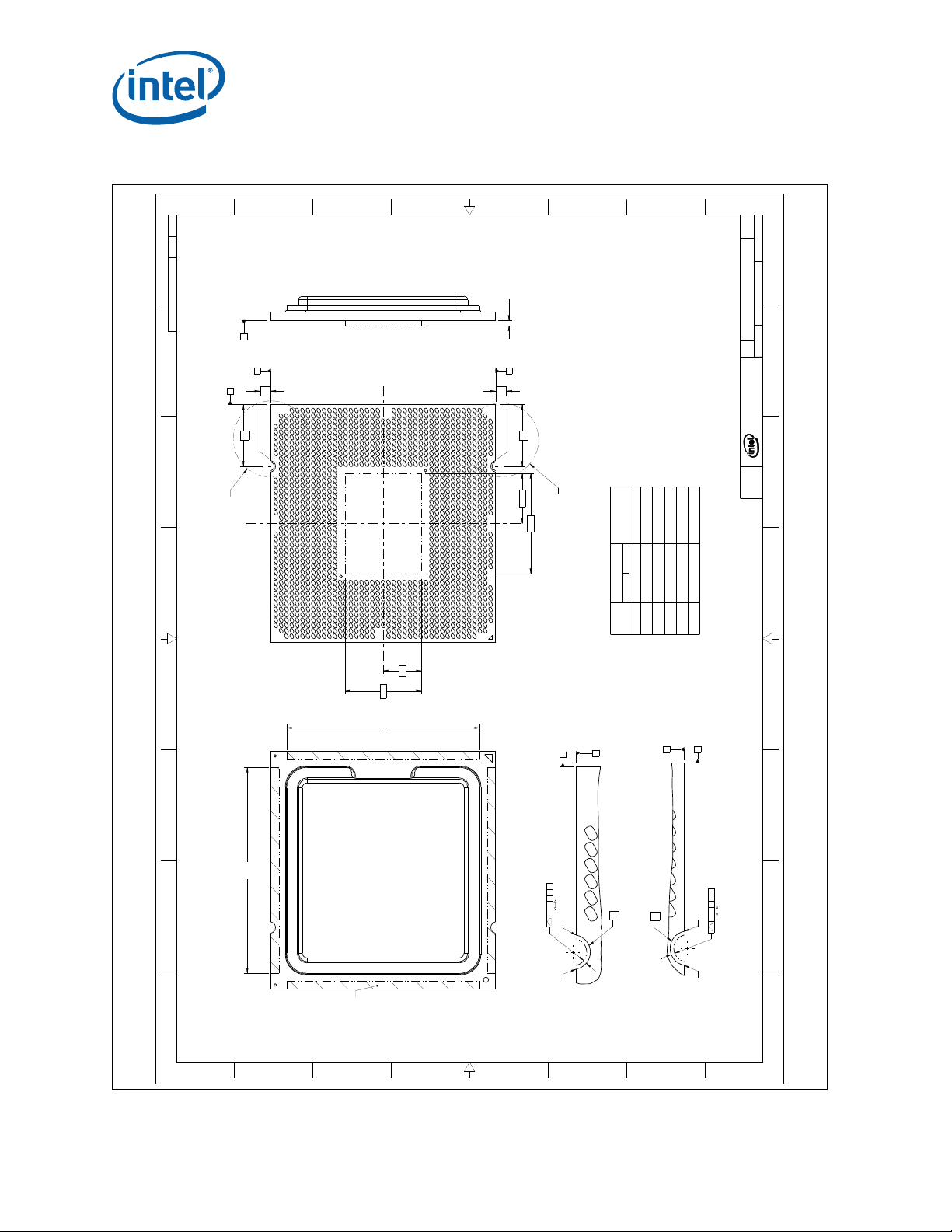

2-2 Processor Package Drawing (Sheet 1 of 2)............................................ .. .. ... ..............13

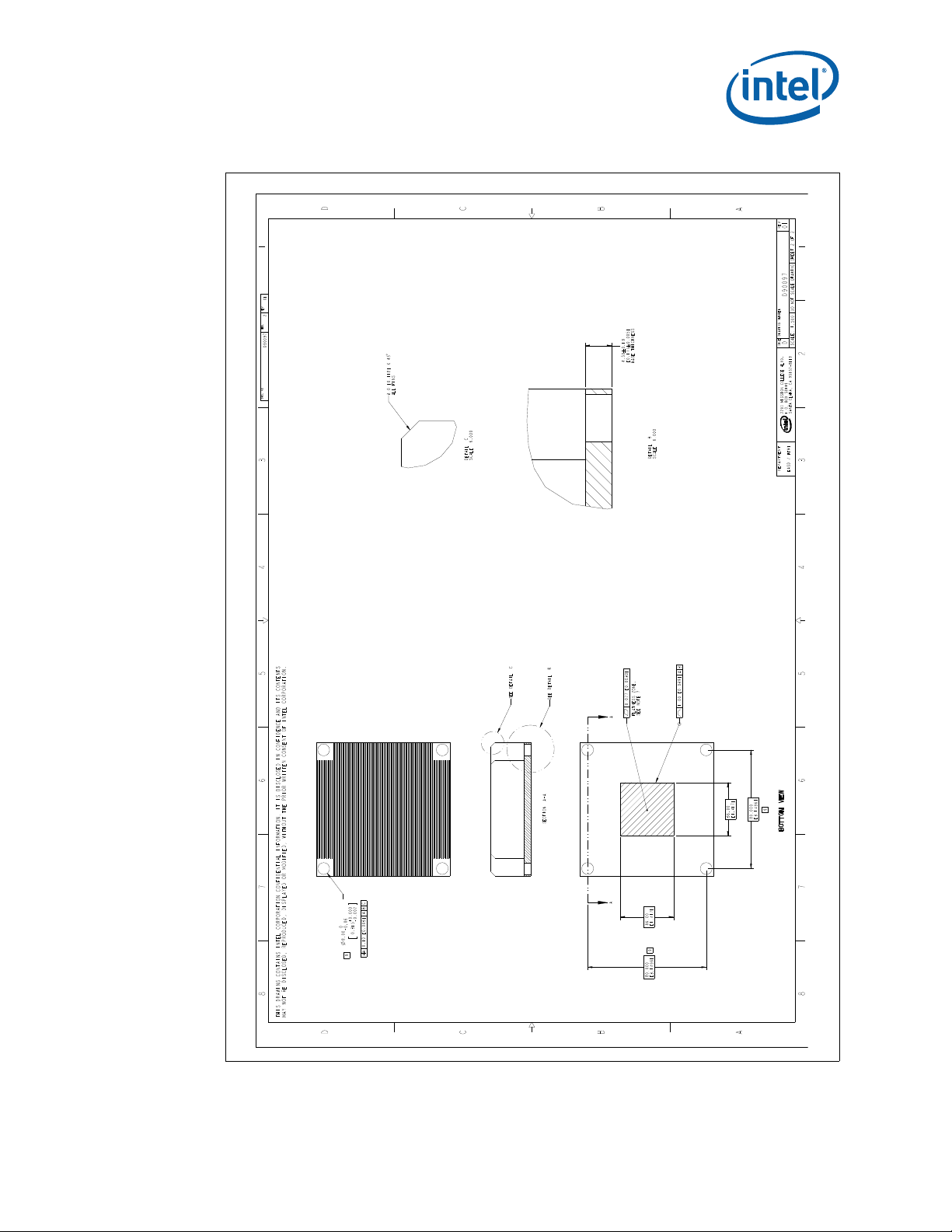

2-3 Processor Package Drawing (Sheet 2 of 2)............................................ .. .. ... ..............14

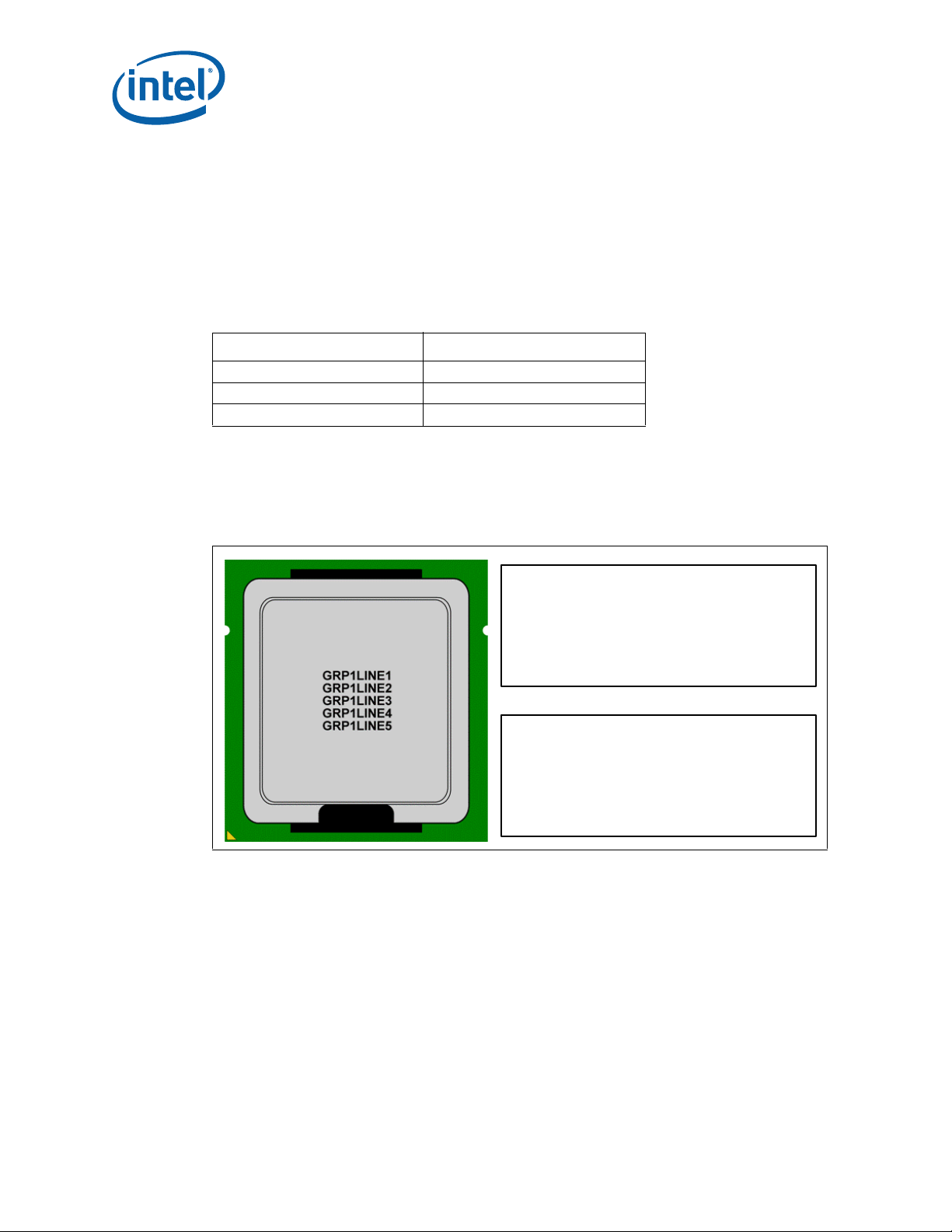

2-4 Processor Top-Side Markings ...................... .. ..................................................... ......16

2-5 Processor Land Coordinates and Quadrants, Bottom View................................ .. .. .. .. .. ..17

3-1 LGA1366 Socket with Pick and Place Cover Removed ..................................................18

3-2 LGA1366 Socket Contact Numbering (Top View of Socket)...........................................19

3-3 LGA1366 Socket Land Pattern (Top View of Board) .....................................................20

3-4 Attachment to Motherboard.....................................................................................21

3-5 Pick and Place Cover...............................................................................................22

3-6 Package Installation / Removal Features ...................................................................23

3-7 LGA1366 NCTF Solder Joints....................................................................................25

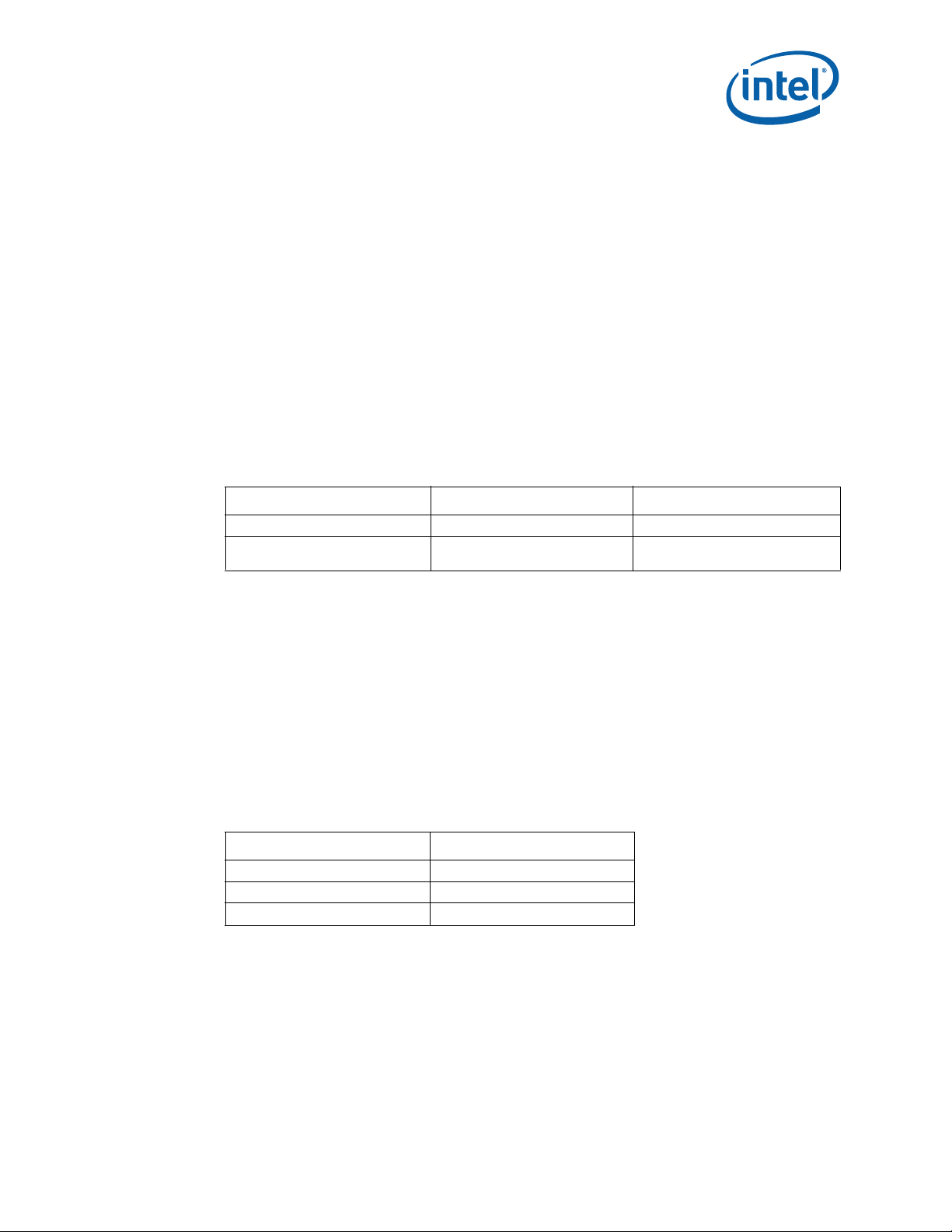

4-1 ILM Cover Assembly...............................................................................................27

4-2 Back Plate...................................... ......................... .. .. ......................... ... .. ............28

4-3 ILM Assembly........................................................................................................29

4-4 Pin1 and ILM Lever................................ .. .. ......................... ... ......................... ........30

5-1 Socket Temperature Measurement Location...............................................................32

5-2 Flow Chart of Knowledge-Based Reliability Evaluation Methodology...............................35

6-1 Intel

6-2 Intel® Xeon® Processor EC3539 and EC5539 Thermal Profile ...................................... 39

6-3 Intel

6-4 Intel® Xeon® Processor LC5518 Thermal Profile................................. .... .. .................. 42

6-5 Intel® Celeron® Processor P1053 Thermal Profile.......................................................43

6-6 Intel

6-7 Intel® Xeon® Processor LC3518 Thermal Profile................................. .... .. .................. 46

6-8 TTV Case Temperature (TCASE) Measurement Location...............................................47

6-9 Frequency and Voltage Ordering ..............................................................................49

7-1 1U Heatsink Performance Curves..............................................................................55

7-2 ATCA Heatsink Performance Curves..........................................................................56

7-3 TTV Die Size and Orientation ...................................................................................57

7-4 1U Reference Heatsink Assembly................................ .. .. .. ............................ .. .. .. ......57

7-5 Processor Thermal Characterization Parameter Relationships........................................59

7-6 NEBS Thermal Profile..............................................................................................60

7-7 UP ATCA Thermal Solution............................................... .. .......................... .. ..........64

7-8 UP ATCA System Layout....................... .. .. ......................... .. .......................... .. ........64

7-9 UP ATCA Heat Sink Drawing ....................................................................................65

B-1 Board Keepin / Keepout Zones (Sheet 1 of 4) ............................................................73

B-2 Board Keepin / Keepout Zones (Sheet 2 of 4) ............................................................74

B-3 Board Keepin / Keepout Zones (Sheet 3 of 4) ............................................................75

B-4 Board Keepin / Keepout Zones (Sheet 4 of 4) ............................................................76

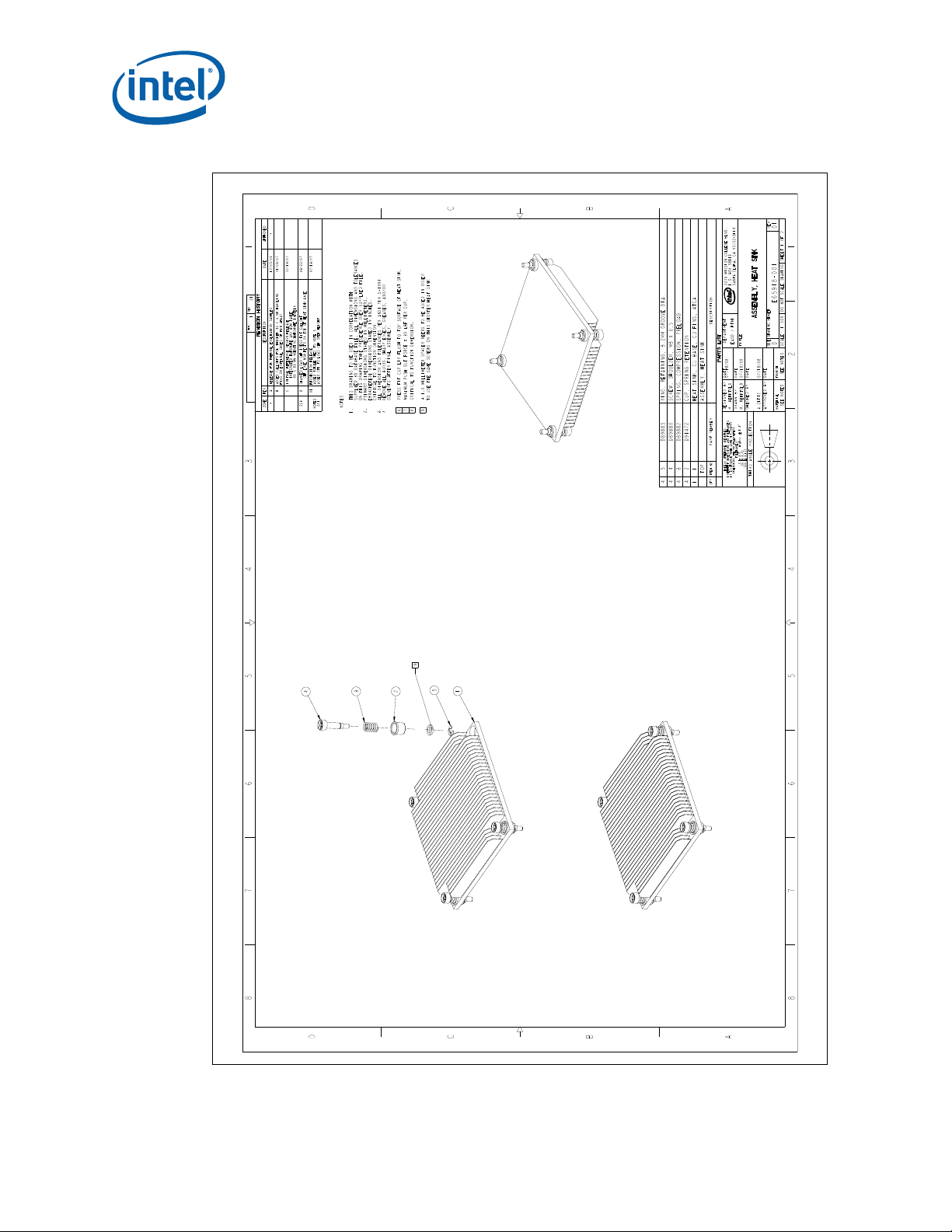

B-5 1U Reference Heatsink Asse mb ly (She et 1 of 2).........................................................77

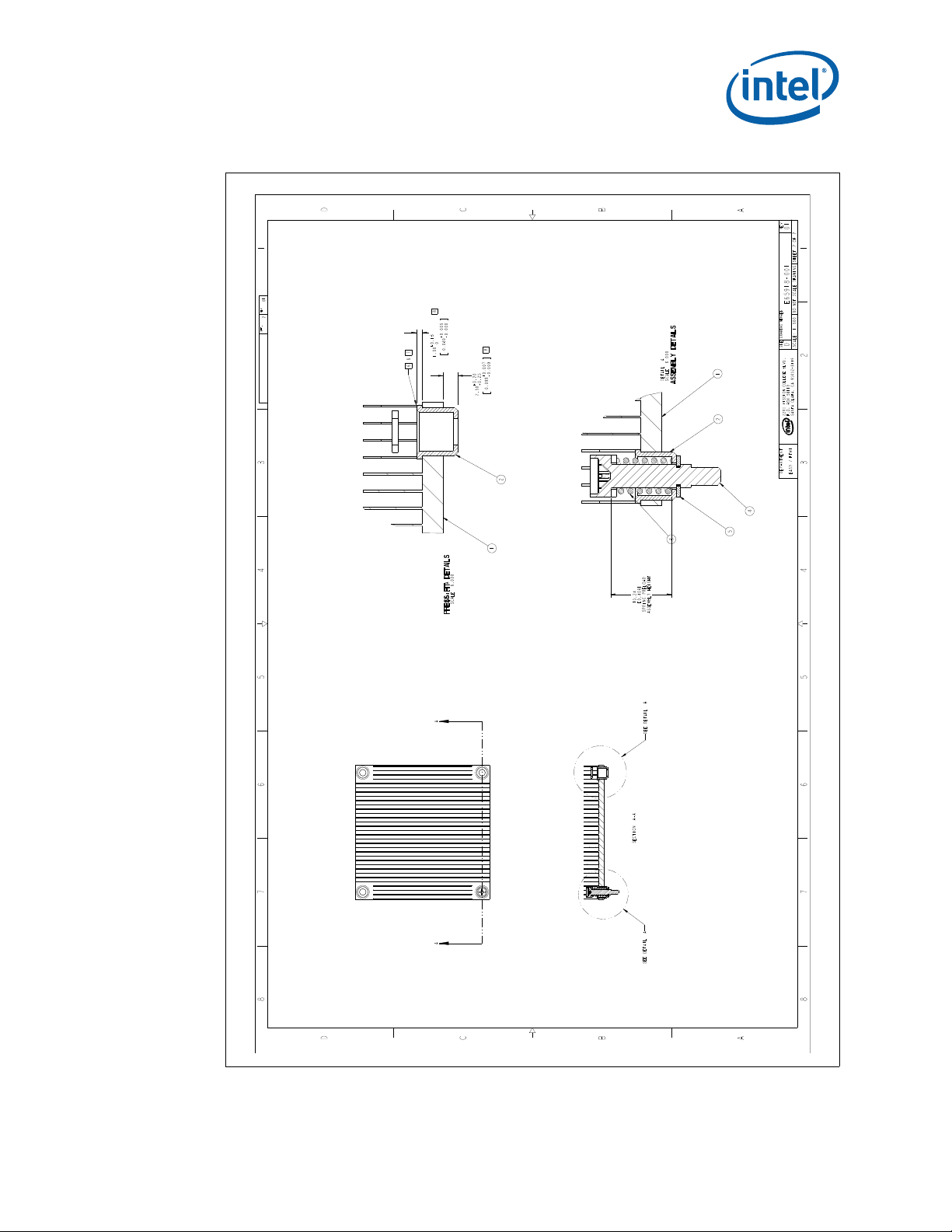

B-6 1U Reference Heatsink Asse mb ly (She et 2 of 2).........................................................78

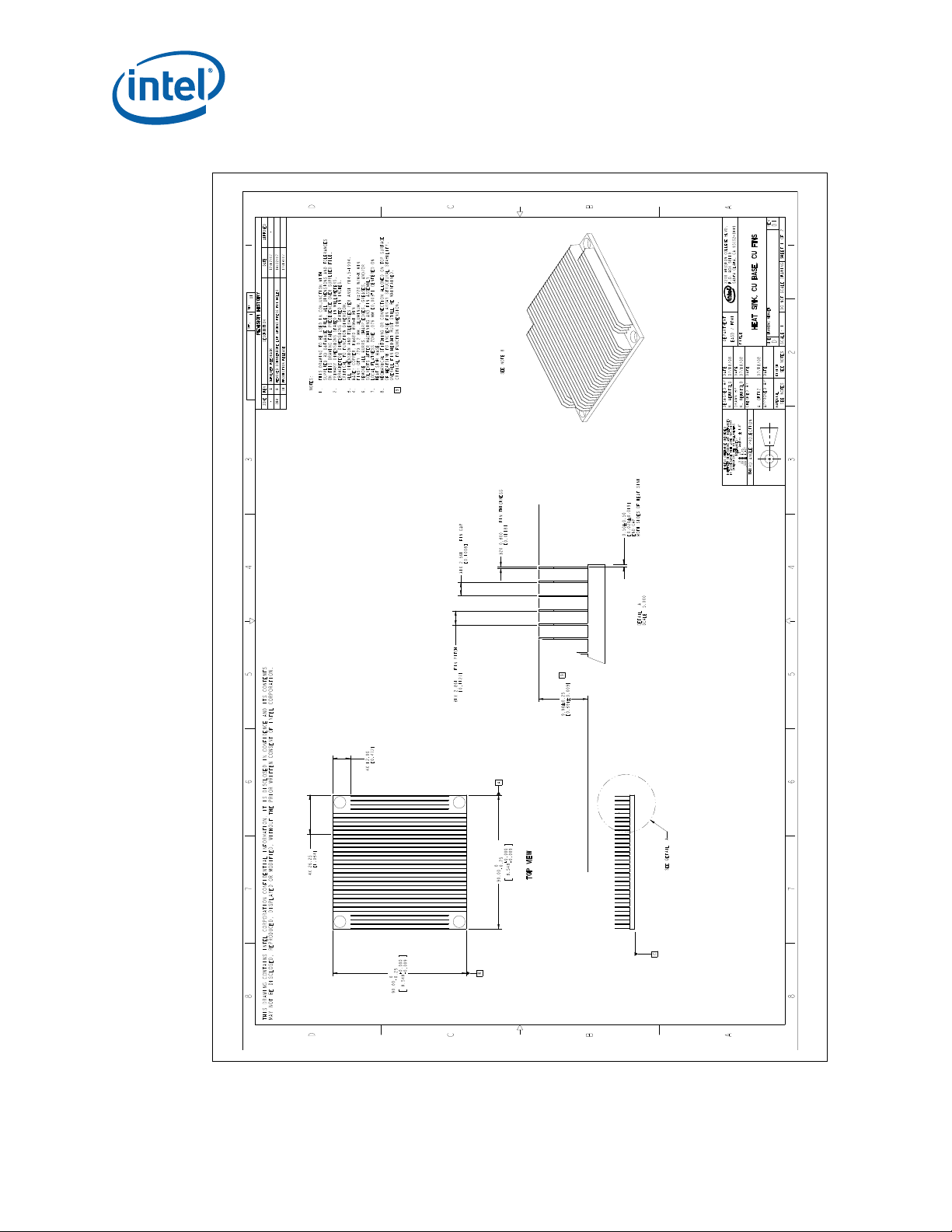

B-7 1U Reference Heatsink Fin and Base (Sheet 1 of 2).....................................................79

B-8 1U Reference Heatsink Fin and Base (Sheet 2 of 2).....................................................80

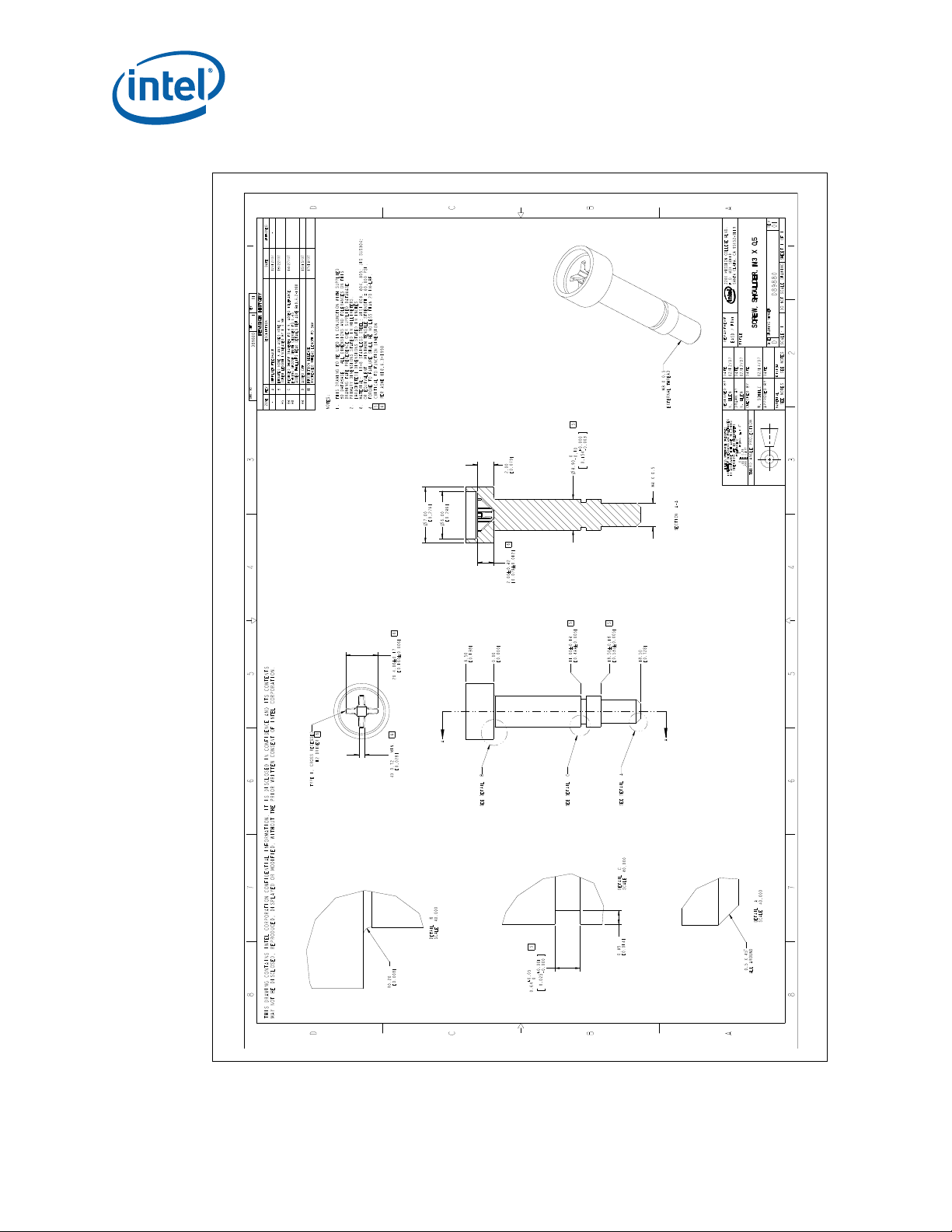

B-9 Heatsink Shoulder Screw (1U, 2U, and Tower)...........................................................81

B-10 Heatsink Compression Spring (1U, 2U, and Tower) .....................................................82

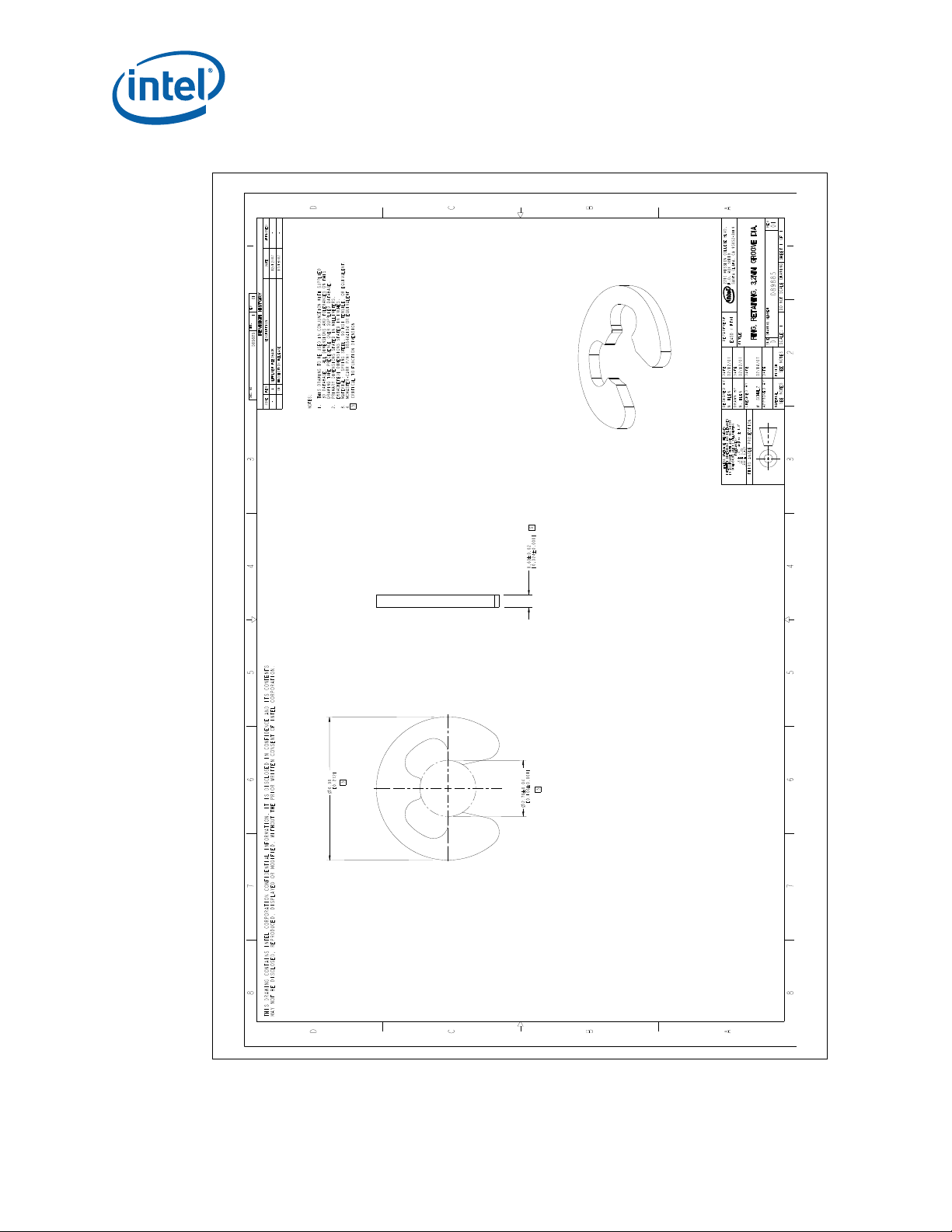

B-11 Heatsink Retaining Ring (1U, 2U, and Tower).............................................................83

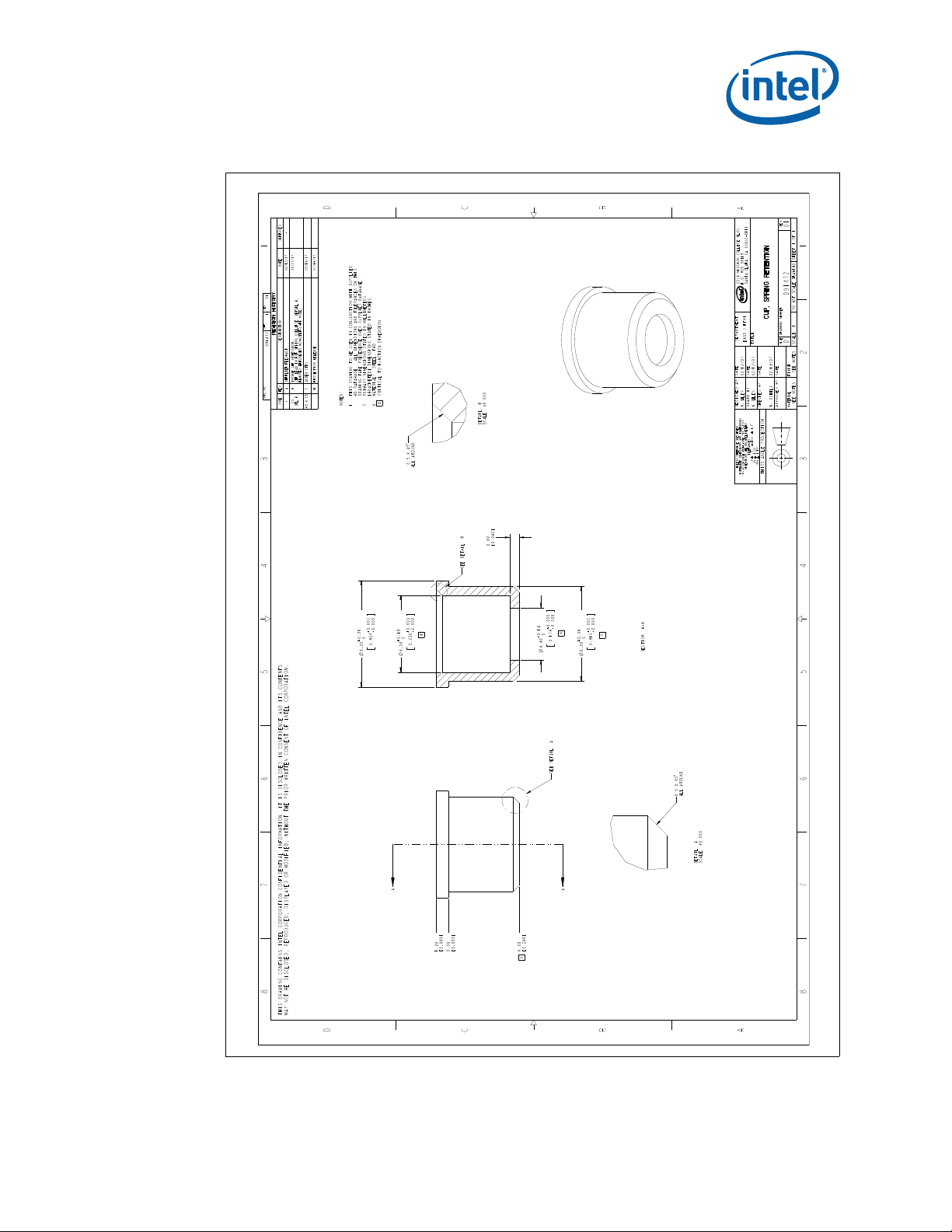

B-12 Heatsink Load Cup (1U, 2U, and Tower)....................................................................84

B-13 ATCA Reference Heatsink Assembly (Sheet 1 of 2)......................................................85

B-14 ATCA Reference Heatsink Assembly (Sheet 2 of 2)......................................................86

B-15 ATCA Reference Heatsink Fin and Base (Sheet 1 of 2).................................................87

B-16 ATCA Reference Heatsink Fin and Base (Sheet 2 of 2).................................................88

®

Xeon® Processor EC5549 and EC5509 Thermal Profile ....................................... 37

®

Xeon® Processor LC5528 Thermal Profile................................. .... .. .................. 40

®

Xeon® Processor LC3528 Thermal Profile................................. .... .. .................. 44

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 5

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 6

C-1 Socket Mechanical Drawing - (Sheet 1 of 4)...............................................................90

C-2 Socket Mechanical Drawing - (Sheet 2 of 4)...............................................................91

C-3 Socket Mechanical Drawing - (Sheet 3 of 4)...............................................................92

C-4 Socket Mechanical Drawing - (Sheet 4 of 4)...............................................................93

Tables

1-1 Reference Documents ....................................................... .. .......................... .. .. ....... 9

1-2 Terms and Descriptions............................................................................................ 9

2-1 Processor Loading Specifications...............................................................................15

2-2 Package Handling Guidelines.................................... ................................................15

2-3 Processor Materials.................................................................................................16

5-1 Socket Component Mass..........................................................................................31

5-2 1366-land Package and LGA1366 Socket Stackup Height .............................................31

5-3 Socket and ILM Mechanical Specifications ..................................................................33

5-4 Electrical Requirements for LGA1366 Socket.................... .. .. .. .. .. ................................. 34

6-1 Intel

6-2 Intel

6-3 Intel® Xeon® Processor EC3539 and EC5539 Thermal Specifications ............................38

6-4 Intel® Xeon® Processor EC3539 and EC5539 Thermal Profile.......................................39

6-5 Intel

6-6 Intel® Xeon® Processor LC5528 Thermal Profile .........................................................41

6-7 Intel® Xeon® Processor LC5518 Thermal Specifications...............................................41

6-8 Intel

6-9 Intel® Celeron® Processor P1053 Thermal Specifications ................................ .............43

6-10 Intel® Celeron® Processor P1053 Thermal Profile................... .....................................43

6-11 Intel

6-12 Intel® Xeon® Processor LC3528 Thermal Profile .........................................................45

6-13 Intel® Xeon® Processor LC3518 Thermal Specifications...............................................45

6-14 Intel

6-15 GetTemp0() Error Codes..........................................................................................53

7-1 Boundary Conditions and Performance Targets ...........................................................54

7-2 Fan Speed Control, TCONTROL and DTS Relationship...................................................61

7-3 TCONTROL Guidance...............................................................................................62

8-1 Server Use Conditions Environment (System Level).....................................................66

8-2 Server Use Conditions Environment (System Level).....................................................67

A-1 Heatsinks and Thermal Interface Material ..................................................................70

A-2 LGA1366 Socket and ILM Components.......................................................................71

B-1 Mechanical Drawing List ..........................................................................................72

C-1 Mechanical Drawing List ..........................................................................................89

®

Xeon® Processor EC5549 and EC5509 Thermal Specifications .............................37

®

Xeon® Processor EC5549 and EC5509 Thermal Profile........................................38

®

Xeon® Processor LC5528 Thermal Specifications...............................................40

®

Xeon® Processor LC5518 Thermal Profile .........................................................42

®

Xeon® Processor LC3528 Thermal Specifications...............................................44

®

Xeon® Processor LC3518 Thermal Profile .........................................................46

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Thermal/Mechanical Design Guide August 2010

6 Order Number: 323107-002US

Page 7

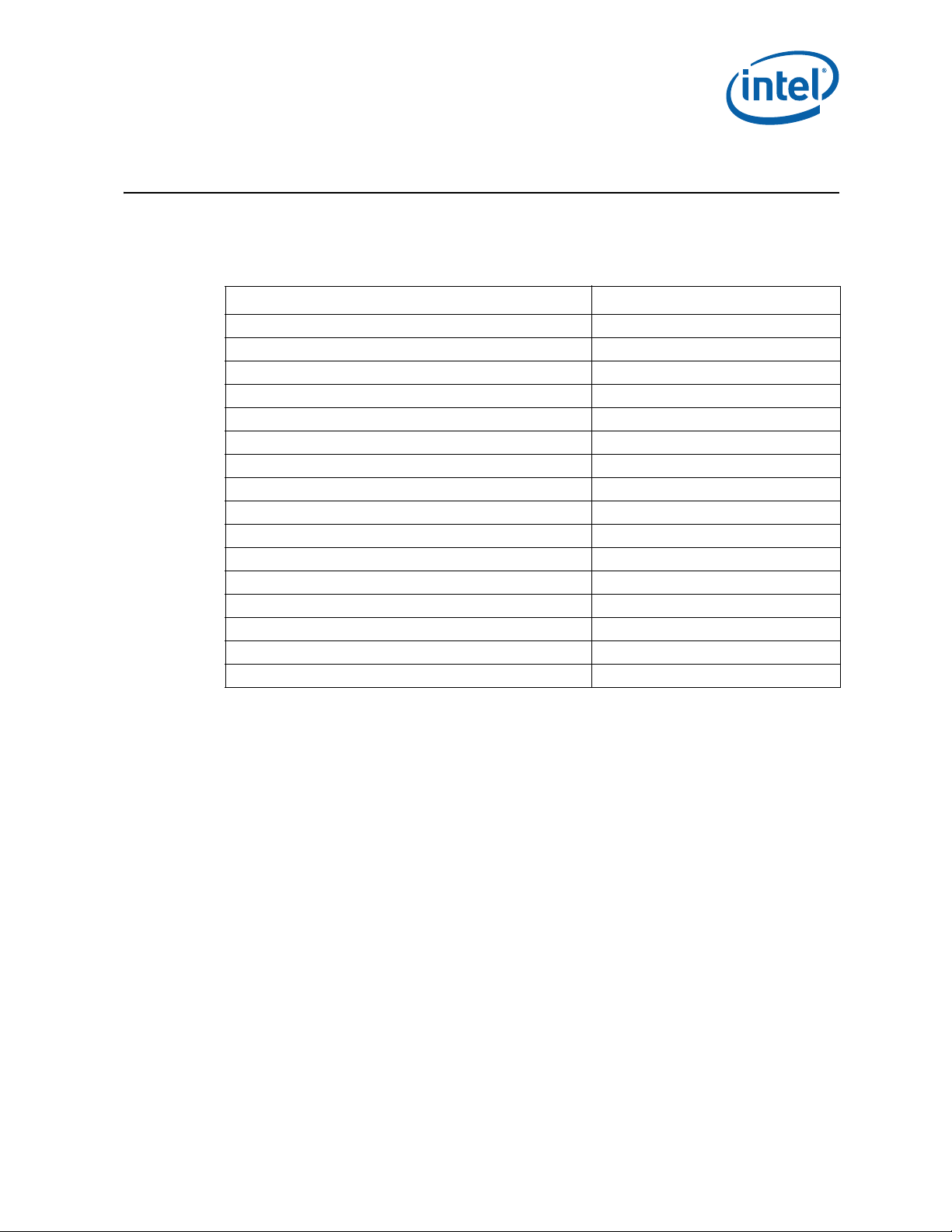

Revision History

Revision Number Description Revision Date

002

001 First release February 2010

Modified Table 5-3, Socket and ILM Mechanical Specifications

Modified Section 7.6.1, Fan Speed Control

§ §

August 2010

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 7

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 8

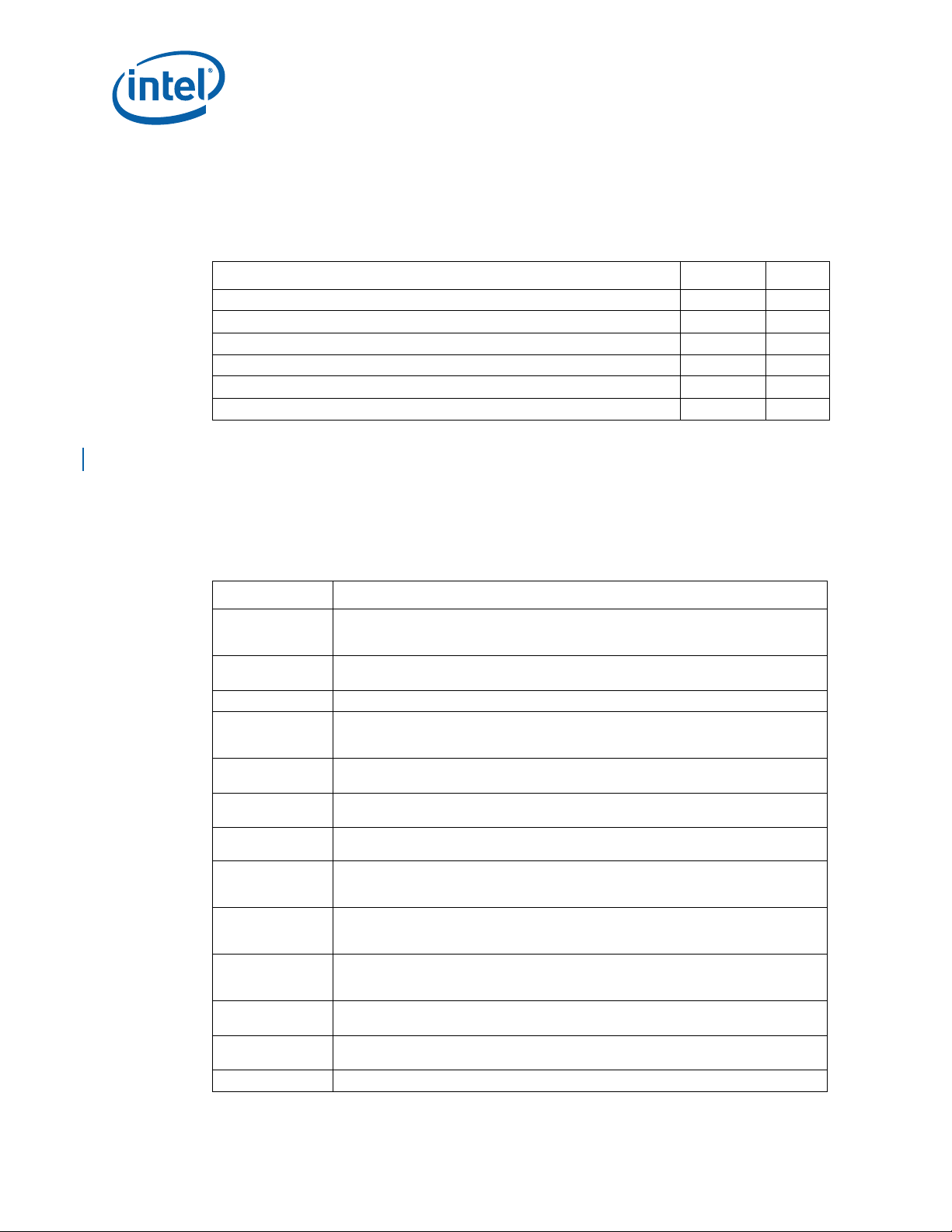

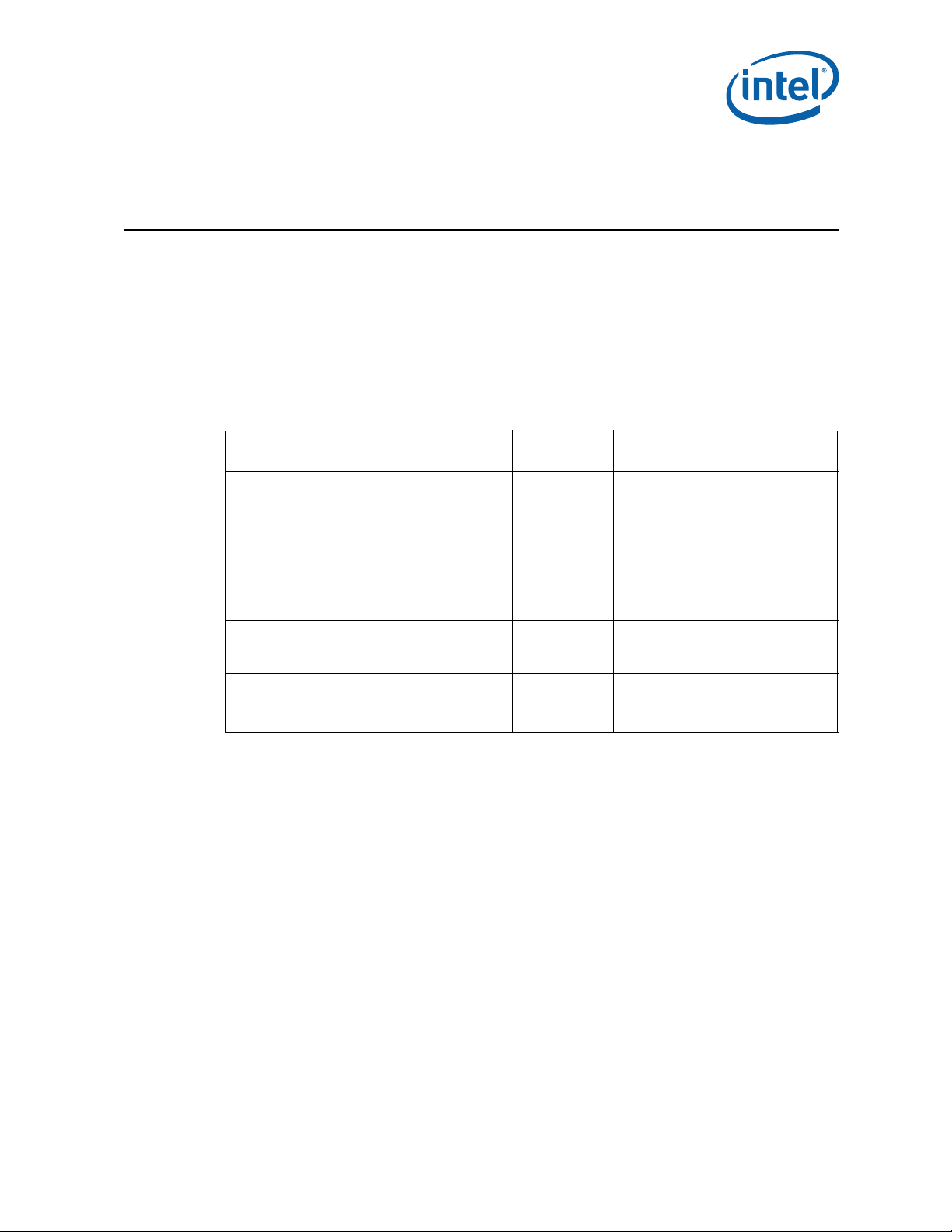

Heatsink

Socket and ILM

Back Plate

Introduction

1 Introduction

This document provides guidelines for the design of thermal and mechanical solutions

for processors in the Picket Post platform. The components described in this document

include:

• The processor thermal solution (heatsink) and associated retention hardware.

• The LGA1366 socket and the Independent Loading Mechanism (ILM) and back

plate.

®

Figure 1-1. Intel

Xeon® Processor C5500/C3500 Series Socket Stack-up

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 8

The goals of this document are:

• To assist board and system thermal mechanical designers.

• To assist designers and suppliers of processor heatsinks.

Other processor specifications are provided in the Intel® Xeon® Processor C5500/

C3500 Series Datasheet.

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 9

1.1 Reference Documents

Material and concepts in the following documents may be beneficial when reading this

document.

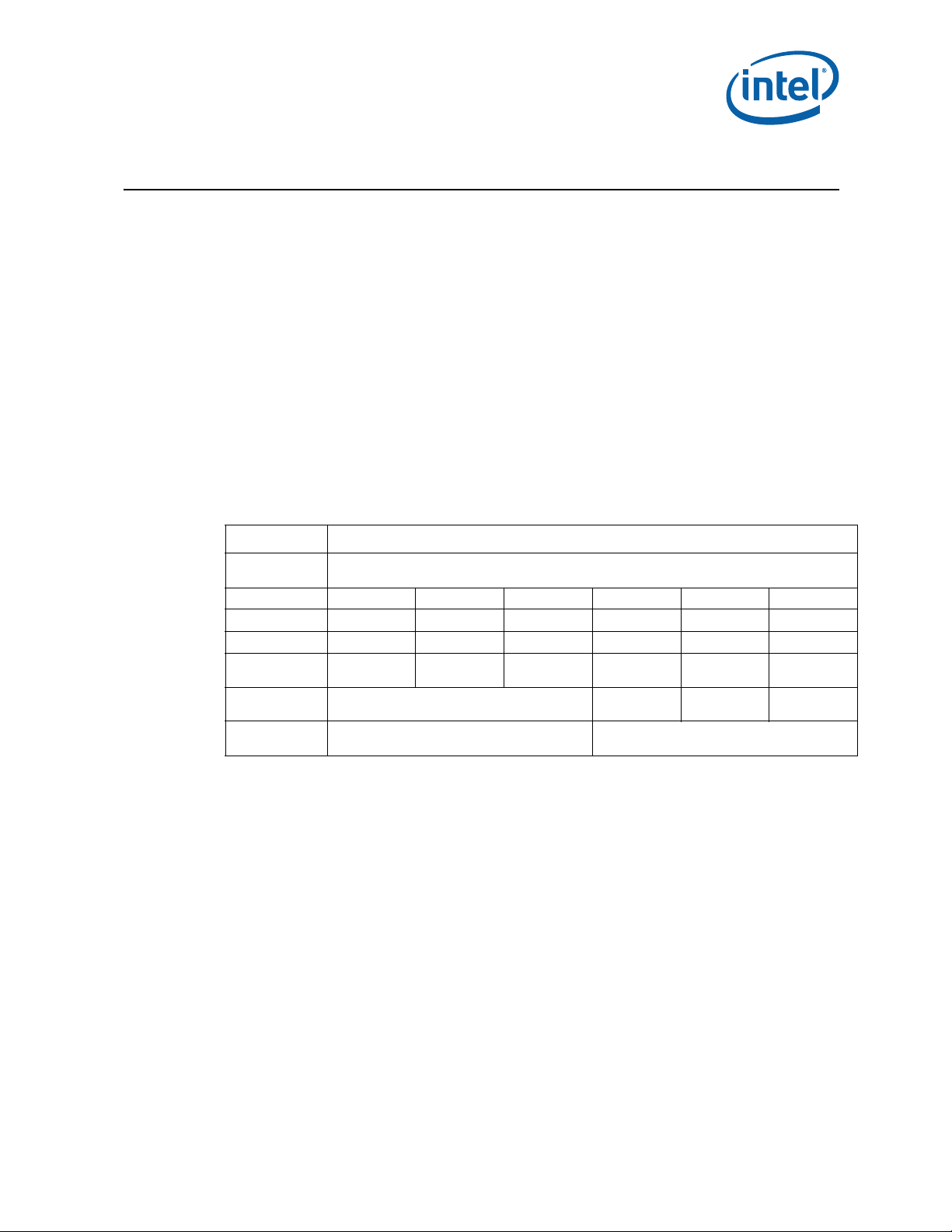

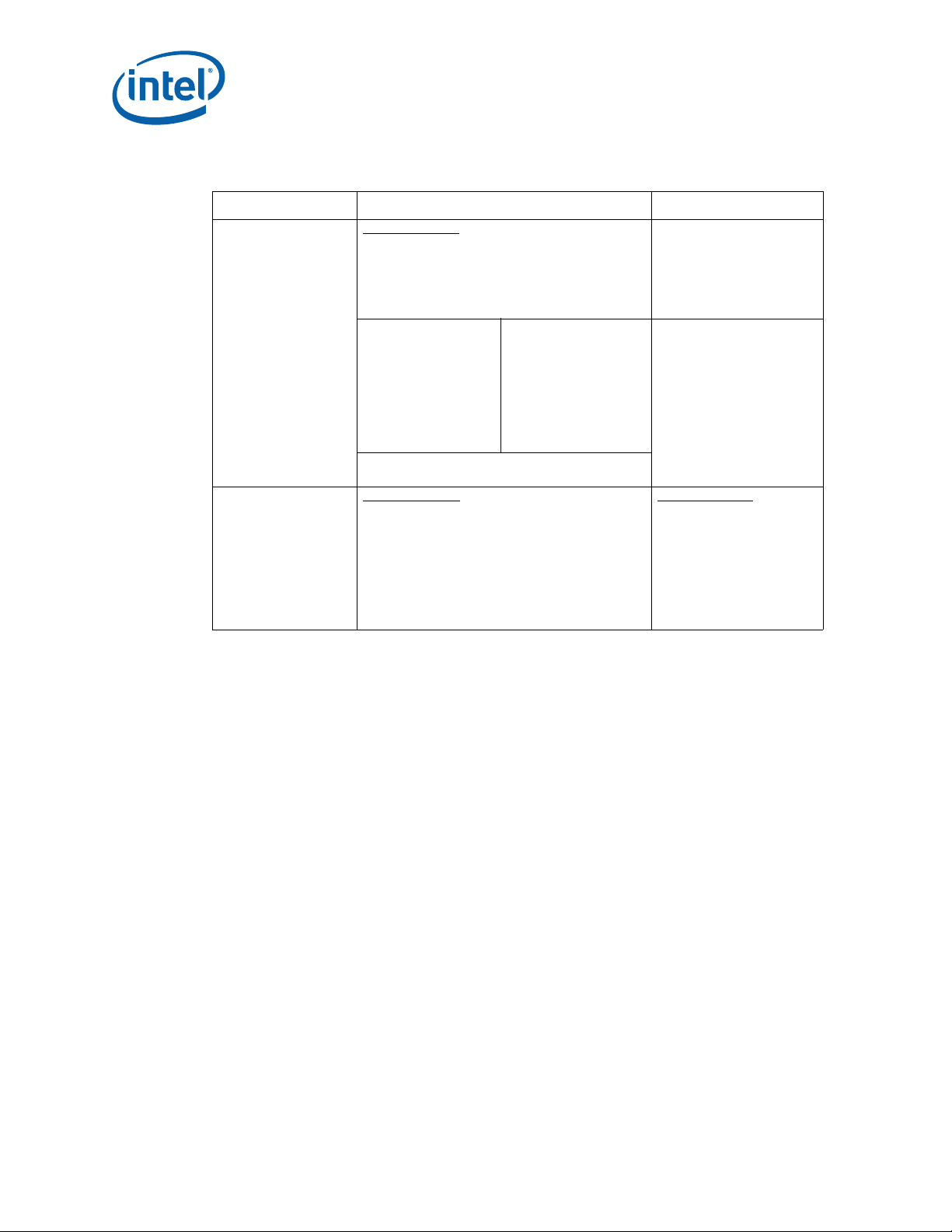

Table 1-1. Reference Documents

Document Document# Notes

European Blue Angel Recycling Standards 3

®

Intel

Xeon® Processor C5500/C3500 Series Datasheet, Volume 1 323103 1

®

Intel

Xeon® Processor C5500/C3500 Series Datasheet, Volume 2 323317 1

®

Intel

Xeon® Processor 5500 Series Mechanical Model 321326 2

®

Intel

Xeon® Processor 5500 Series Thermal Model 321327 2

Entry-level Electronics Bay Specification 4

Notes:

1. See http://developer.intel.com/design/intarch/xeon5000/documentation.htm

2. See http://www.intel.com/p/en_US/products/server/processor/xeon5000/tools

3. Available at http://www.blauer-engel.de

4. Available at http://ssiforum.oaktree.com/

Introduction

1.2 Definition of Terms

Table 1-2. Terms and Descriptions (Sheet 1 of 2)

Term Description

Bypass Bypass is the area between a passive heatsink and any object that can act to form a

DTS Digital Thermal Sensor reports a relative die temperature as an offset from TCC

FSC Fan Speed Control

IHS Integrated Heat Spreader: a component of the processor package used to enhance the

ILM Independent Loading Mechanism provides the force needed to seat the 1366-LGA land

IMON The current monitor input to the CPU. The VRM tells the CPU how much current it is

LGA1366 socket The processor mates with the system board through this surface mount, 1366-land

PECI The Platform Environment Control Interface (PECI) is a one- wire interfac e that p rovid es

Ψ

CA

Ψ

CS

Ψ

SA

T

CASE

T

CASE_MAX

duct. For this example, it can be expressed as a dimension away from the outside

dimension of the fins to the nearest surface.

activation temperature.

thermal performance of the package. Component thermal solutions interface with the

processor at the IHS surface.

package onto the socket contacts.

drawing.

socket.

a communication channel between Intel processor and chipset components to external

monitoring devices.

Case-to-ambient thermal characterization parameter (psi). A measure of thermal

solution performance using t otal package power. Defined as (T

Package Power. Heat source should always be specified for Ψ measurements.

Case-to-sink thermal characterization parameter. A measure of thermal interface

material performance using total package po wer. D efined as (T

Package Power.

Sink-to-ambient thermal characterization parameter. A measure of heatsink thermal

performance using total package power. Defined as (T

The case temperature of the processor , measured at the geometric center of the topside

of the IHS.

The maximum case temperature as specified in a component specification.

– TLA) / Total

CASE

– TS) / Total

CASE

– TLA) / Total Package Power.

S

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

9 Order Number: 323107-002US

Page 10

Introduction

Table 1-2. Terms and Descriptions (Sheet 2 of 2)

Term Description

TCC Thermal Control Circuit: Thermal monitor uses the TCC to reduce the die temperature

T

CONTROL

TDP Thermal Design Power: Thermal solution must be designed to dissipate this target

Thermal Monitor A power reduction feature designed to decrease temperature after the processor has

Thermal Profile Line that defines case temperature specification of a processor at a given power level.

TIM Thermal Interface Material: The thermally conductive compound between the heatsink

T

LA

T

SA

U A unit of measure used to define server rack spacing height. 1U is equal to 1.75 in, 2U

by using clock modulation and/or operating frequency and input voltage adjustment

when the die temperature is very near its operating limits.

T

is a static value below TCC activation used as a trigger point for fan speed

control

control.

power level. TDP is not the maximum power that the processor can dissipate.

reached its maximum operating temperature.

and the processor case. This material fills the air gaps and voids, and enhances the

transfer of the heat from the processor case to the heatsink.

The measured ambient temperature locally surrounding the proc essor. The ambient

temperature should be measured just upstream of a p assive heatsink o r at the fan inlet

for an active heatsink.

The system ambient air temperature external to a system chassis. This temperature is

usually measured at the chassis air inlets.

equals 3.50 in, etc.

§

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 10

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 11

IHS

Substrate

LGA1366 Socket

System Board

Capacitors

TIM

IHS

Substrate

LGA

System Board

Capacitors

Die

TIM

Package Mechanical Specifications

2 Package Mechanical

Specifications

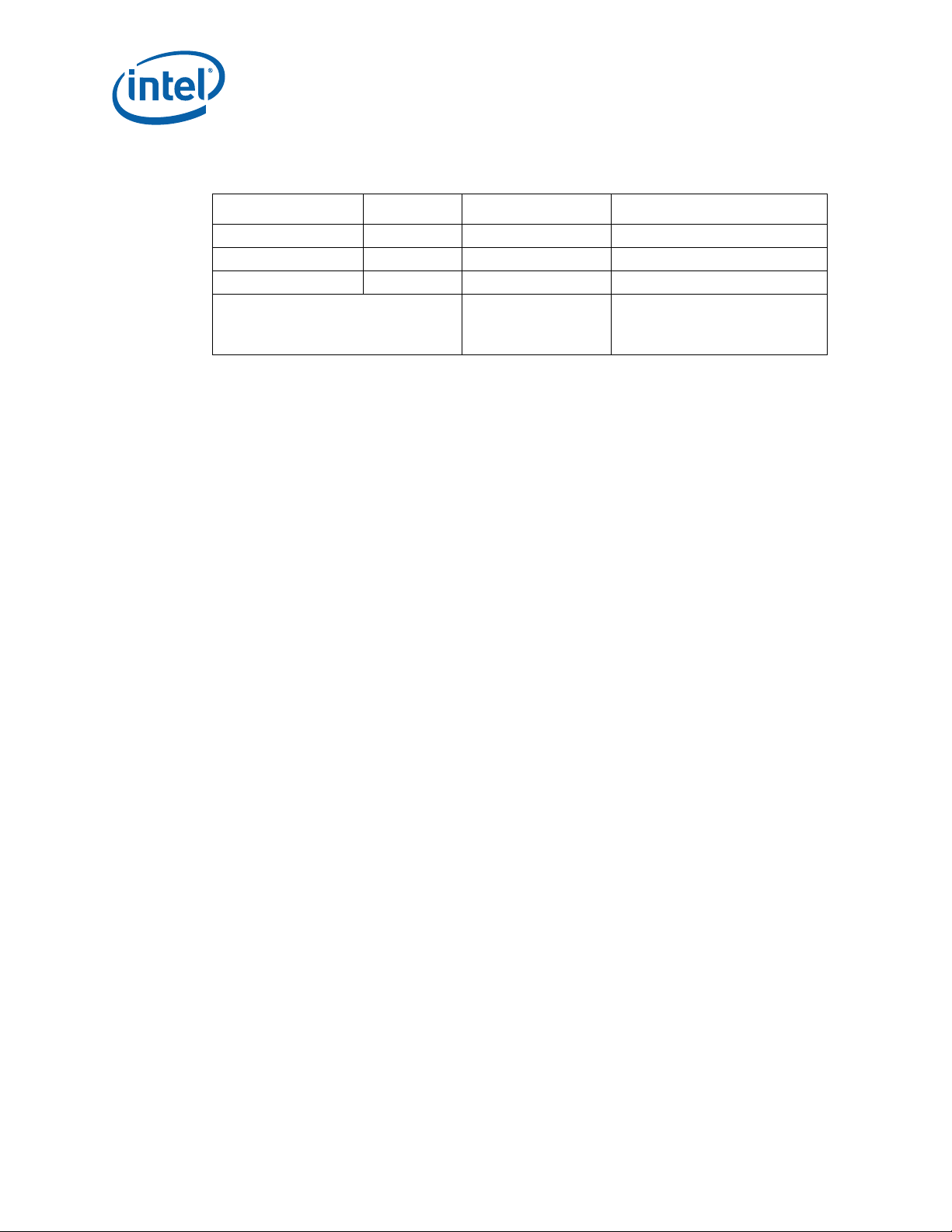

2.1 Package Mechanical Specifications

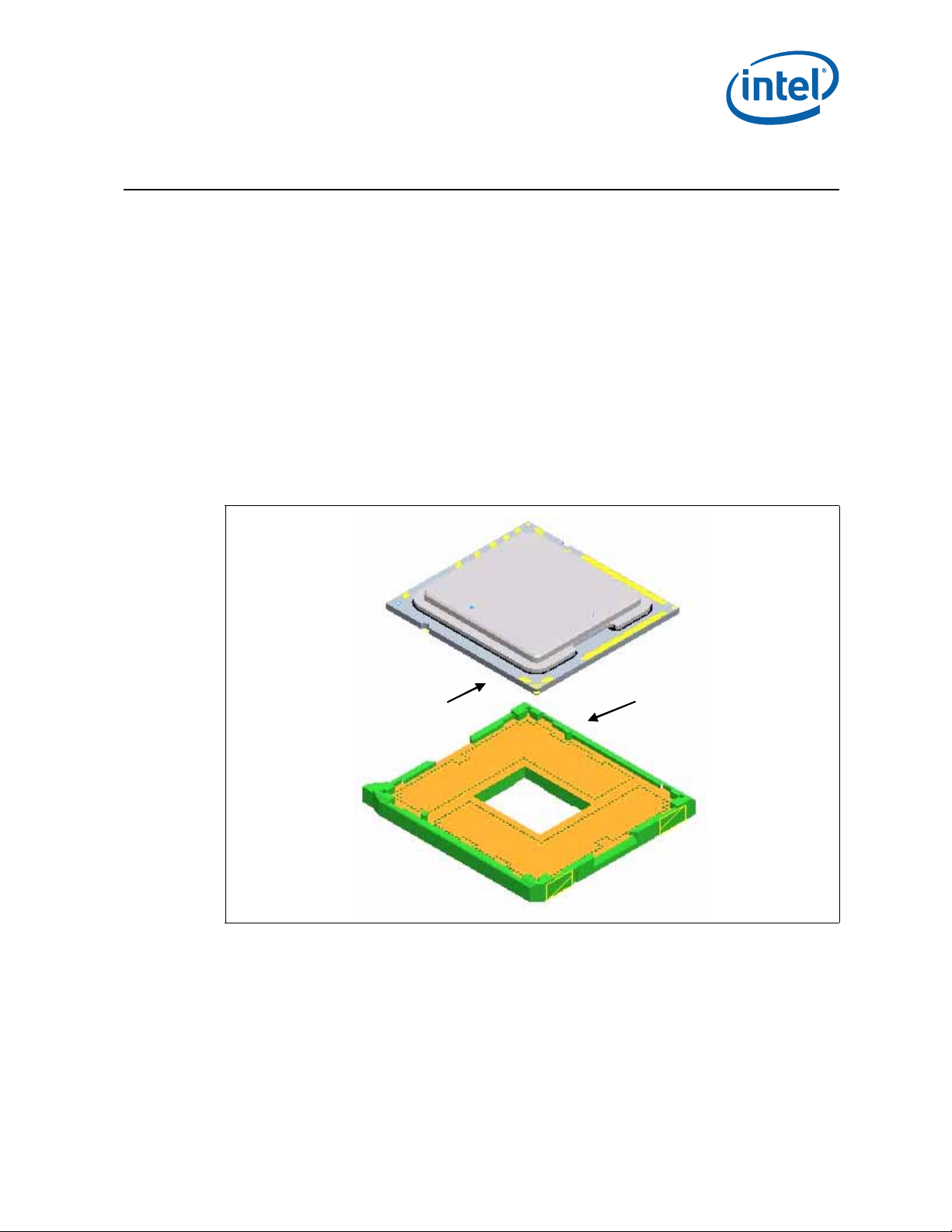

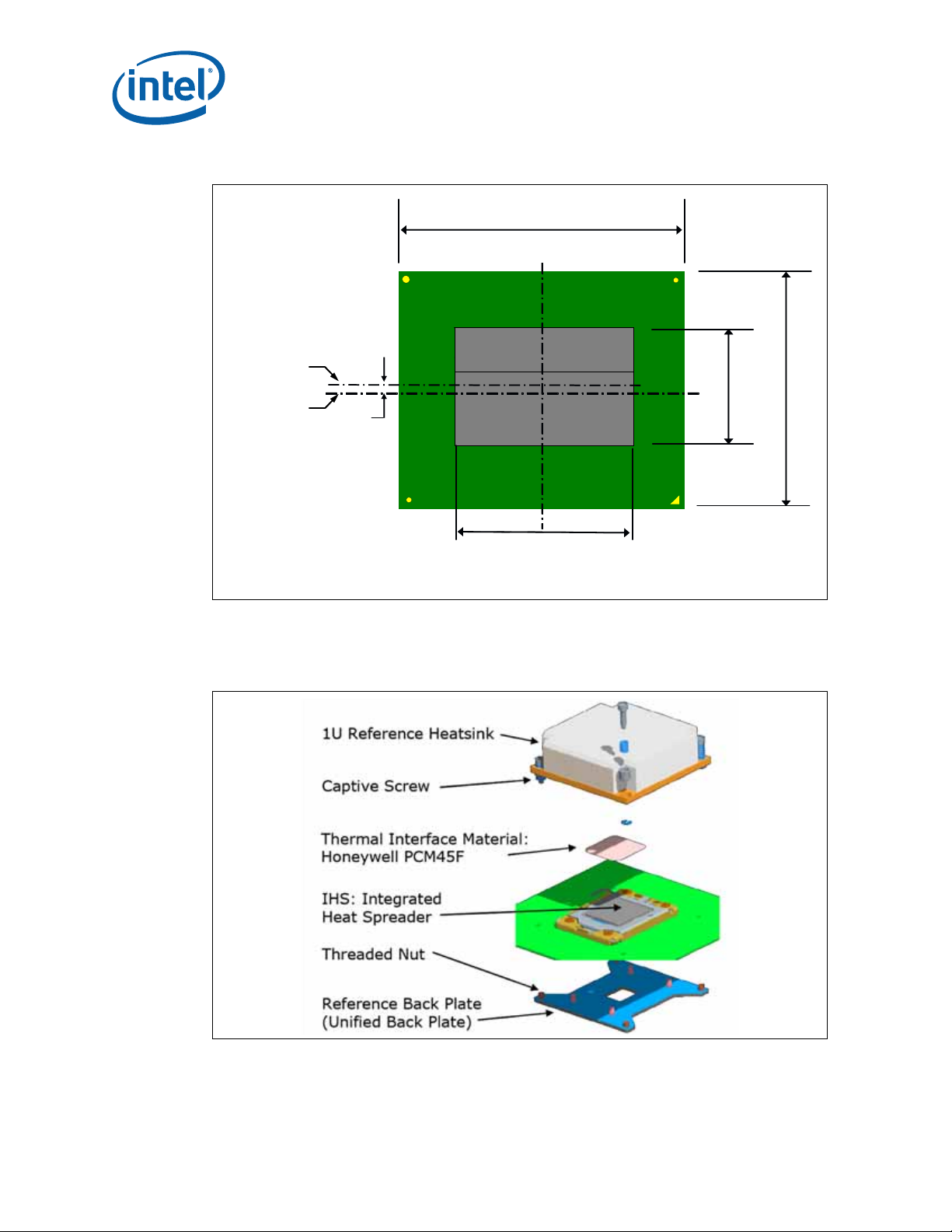

The processor is packaged in a Flip-Chip Land Grid Array (FC-LGA6) package that

interfaces with the motherboard via an LGA1366 socket. The package consists of a

processor mounted on a substrate land-carrier. An integrated heat spreader (IHS) is

attached to the package substrate and core and serves as the mating surface for

processor component thermal solutions, such as a heatsink. Figure 2-1 shows a sketch

of the processor package components and how they are assembled together. See

Section 3 and Section 4.

The package components shown in Figure 2-1 include the following:

• Integrated Heat Spreader (IHS)

• Thermal Interface Material (TIM)

• Processor core (die)

• Package substrate

• Capacitors

Figure 2-1. Processor Package Assembly Sketch

Note:

1. Socket and motherboard are included for reference and are not part of processor package.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 11

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 12

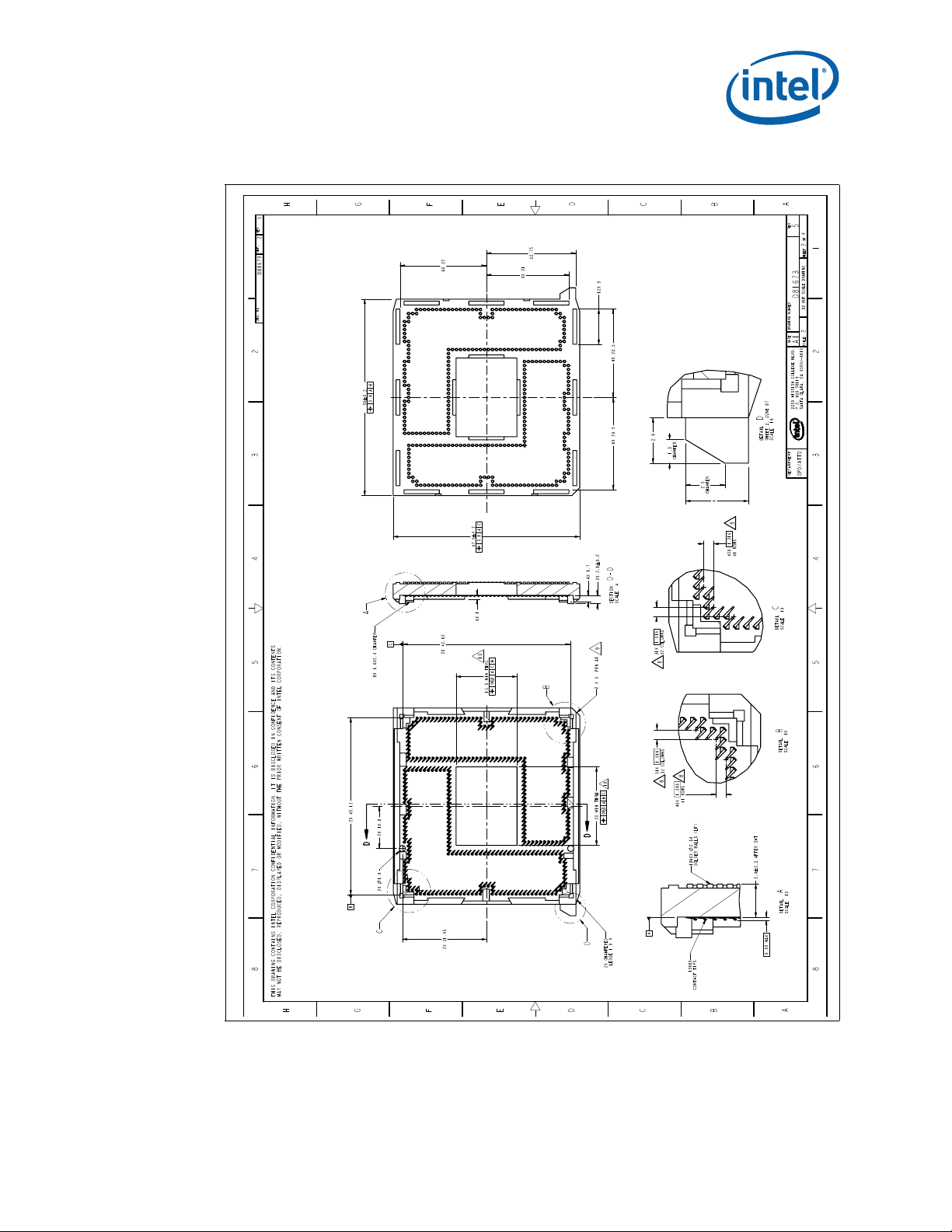

2.1.1 Package Mechanical Drawing

The package mechanical drawings are shown in Figure 2-2 and Figure 2-3. The

drawings include dimensions necessary to design a thermal solution for the processor.

These dimensions include:

1. Package reference with tolerances (total height, length, width, etc.)

2. IHS parallelism and tilt

3. Land dimensions

4. Top-side and back-side component keep-out dimensions

5. Reference datums

6. All drawing dimensions are in mm

Package Mechanical Specifications

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

12 Order Number: 323107-002US

Page 13

8 7 6 5 4 3 2

H

G

F

E

D

C

B

A

8 7 6 5 4 3 2 1

H

G

F

E

D

C

B

A

A

A

R

D

E

C

C

4X RM

1

M

2

M

3

F

4

F

2

B1C

1

C

3

B

2

C

2

C

4

G

2

G

1

H

1

H

2

J

1

J

2

0.02

THIS DRAWING CONTAINS INTEL CORPORATION CONFIDENTIAL INFORMATION. IT IS DISCLOSED IN CONFIDENCE AND ITS CONTENTS

MAY NOT BE DISCLOSED, REPRODUCED, DISPLAYED OR MODIFIED, WITHOUT THE PRIOR WRITTEN CONSENT OF INTEL CORPORATION.

D76126 1 7

DWG. NO SHT. REV

THIS DRAWING CONTAINS INTEL CORPORATION CONFIDENTIAL INFORMATION. IT IS DISCLOSED IN CONFIDENCE AND ITS CONTENTS

MAY NOT BE DISCLOSED, REPRODUCED, DISPLAYED OR MODIFIED, WITHOUT THE PRIOR WRITTEN CONSENT OF INTEL CORPORATION.

D76126 1 7

DWG. NO SHT. REV

DEPARTMENT

2200 MISSION COLLEGE BLVD.

P.O. BOX 58119

SANTA CLARA, CA 95052-8119

TITLE

EMTS DRAWING

SIZE DRAWING NUMBER REV

A1 D76126 7

SCALE: 2:1

DO NOT SCALE DRAWING

SHEET 1 OF 2

FINISHMATERIAL

DATEAPPROVED BY

DATECHECKED BY

DATEDRAWN BY

DATEDESIGNED BY

UNLESS OTHERWISE SPECIFIED

INTERPRET DIMENSIONS AND TOLERANCES

IN ACCORDANCE WITH ASME Y14.5M-1994

DIMENSIONS ARE IN MILLIMETERS

ALL UNTOLERANCED LINEAR

DIMENSIONS ±0

ANGLES ±0.5

THIRD ANGLE PROJECTION

SEE DETAIL B

SEE DETAIL B

SEE DETAIL B

SEE DETAIL B

IHS LID

SEE DETAIL B

PIN 1

SEE DETAIL C

PIN 1

BAAY AWAV AU

AT

ARAP ANAM ALAK AJAH AGAF AEAD ACAB AAY WV UT RP NM LK JH GF ED CB A

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42

SEE DETAIL A

SECTION A-A

DETAIL A

SCALE 20:1

PACKAGE SUBSTRATE IHS SEALANT

IHS LID

DETAIL

C

SCALE 20:1

DETAIL B

SUBSTRATE ALIGNMENT FIDUCIAL

X5

SCALE 35:1

SYMBOL

MILLIMETERS

COMMENTS

MIN MAX

B

1

44.93 45.07

B

2

42.43 42.57

C

1

38.9 39.1

1CE

C

2

36.4 36.6

1CD

C

3

2.2 2.3

C

4

2.2 2.3

F

2

4.377 4.757

F

4

2.498 2.896

G

1

42.672 BASIC

G

2

40.64 BASIC

H

1

21.336 BASIC

H

2

20.32 BASIC

J

1

1.016 BASIC

J

2

1.016 BASIC

M

1

0.19 0.23

M

2

0.88 0.96

M

3

0.53 0.61

0.203

0.08

0.203 C

0.203 C D E

0.071 C

0.05

0.203 C

Package Mechanical Specifications

Figure 2-2. Processor Package Drawing (Sheet 1 of 2)

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 13

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 14

Figure 2-3. Processor Package Drawing (Sheet 2 of 2)

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

8 7 6 5 4 3 2

8 7 6 5 4 3 2 1

R

H

H

H

C

9.455

7.2

1.06 MAX

COMPONENT HEIGHT

T

1

T

2

V

1

V

2

2X 36.5

2X 39

14.4

18.91

E

G

E

G

THIS DRAWING CONTAINS INTEL CORPORATION CONFIDENTIAL INFORMATION. IT IS DISCLOSED IN CONFIDENCE AND ITS CONTENTS

MAY NOT BE DISCLOSED, REPRODUCED, DISPLAYED OR MODIFIED, WITHOUT THE PRIOR WRITTEN CONSENT OF INTEL CORPORATION.

THIS DRAWING CONTAINS INTEL CORPORATION CONFIDENTIAL INFORMATION. IT IS DISCLOSED IN CONFIDENCE AND ITS CONTENTS

MAY NOT BE DISCLOSED, REPRODUCED, DISPLAYED OR MODIFIED, WITHOUT THE PRIOR WRITTEN CONSENT OF INTEL CORPORATION.

D76126 2 7

DWG. NO SHT. REV

DEPARTMENT

2200 MISSION COLLEGE BLVD.

P.O. BOX 58119

SANTA CLARA, CA 95052-8119

SIZE DRAWING NUMBER REV

A1 D76126 7

SCALE: 2:1

DO NOT SCALE DRAWING

SHEET 2 OF 2

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42

SEE DETAIL D

SEE DETAIL E

BAAY AWAV AU

AT

ARAP ANAM ALAK AJAH AGAF AEAD ACAB AAY WV UT RP NM LK JH GF ED CB A

DETAIL D

SCALE 15:1

0.23 C H E

M N

NM

R

2

DETAIL

E

SCALE 15:1

0.23 C H G

J K

KJ

R

1

4X

SURFACE

TEST PAD AREA

SYMBOL

MILLIMETERS

COMMENTS

MIN MAX

R

1

R1.09 --

R

2

R1.09 --

T

1

0.2 --

T

2

11.7 --

V

1

0.2 --

V

2

11.7 --

Package Mechanical Specifications

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

14 Order Number: 323107-002US

Page 15

Package Mechanical Specifications

2.1.2 Processor Component Keep-Out Zones

The processor may contain components on the substrate that define component

keep-out zone requirements. A thermal and mechanical solution design must not

intrude into the required keep-out zones. Do not contact the Test Pad Area with

conductive material. Decoupling capacitors are typically mounted to either the topside

or land-side of the package substrate. See Figure 2-2 and Figure 2-3 for keep-out

zones. The location and quantity of package capacitors may change due to

manufacturing efficiencies but will remain within the component keep-in.

2.1.3 Package Loading Specifications

Table 2-1 provides load specifications for the processor package. These maximum

limits should not be exceeded during heatsink assembly, shipping conditions, or

standard use condition. Exceeding these limits during test may result in component

failure. The processor substrate should not be used as a mechanical reference or load-

.

Table 2-1. Processor Loading Specifications

bearing surface for thermal solutions.

Parameter Maximum Notes

Static Compressive Load 890 N [200 lbf] 1, 2, 3

Dynamic Compressive Load 1779 N [400 lbf] [max static

compressive + dynamic load]

1, 3, 4

Notes:

1. These specifications apply to uniform compressive loading in a direction normal to the processor IHS.

2. This is the maximum static force that can be applied by the heatsink and Independent Loading Mechanism

(ILM).

3. These specifications are based on limited testing for design characterization. Loading limits are for the

package constrained by the limits of the processor socket.

4. Dynamic loading is defined as an 11 ms duration average load superimposed on the static load

requirement.

2.1.4 Package Handling Guidelines

Table 2-2 includes a list of guidelines on package handling in terms of recommended

maximum loading on the processor IHS relative to a fixed substrate. These package

handling loads may be experienced during heatsink removal.

Table 2-2. Package Handling Guidelines

Parameter Maximum Recommended

Shear 70 lbs

Tensile 25 lbs

Torque 35 in.lbs

2.1.5 Package Insertion Specifications

The processor can be inserted into and removed from a LGA1366 socket 15 times. The

socket should meet the LGA1366 requirements detailed in Section 5.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 15

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 16

2.1.6 Processor Mass Specification

GRP1LINE1

GRP1LINE2

G2L1

G2L2

G3L1

G3L2

Legend: Mark Text (Engineering Mark):

GRP1LINE1: INTEL{M}{C}’YY

GRP1LINE2: INTEL CONFIDENTIAL

GRP1LINE3: QDF ES XXXXX

GRP1LINE4: FORECAST-NAME

GRP1LINE5: {FPO} {e4}

Legend: Mark Text (Production Mark):

GRP1LINE1: INTEL{M}{C}’YY PROC#

GRP1LINE2: SUB-BRAND

GRP1LINE3: SSPEC XXXXX

GRP1LINE4: SPEED/CACHE/INTC

GRP1LINE5: {FPO} {e4}

The typical mass of the processor is 35 grams. This mass [weight] includes all the

components that are included in the package.

2.1.7 Processor Materials

Package Mechanical Specifications

Table 2-3 lists some of the package components and associated materials.

Table 2-3. Processor Materials

Component Material

Integrated Heat Spreader (IHS) Nickel Plated Copper

Substrate Fiber Reinforced Resin

Substrate Lands Gold Plated Copper

2.1.8 Processor Markings

Figure 2-4 shows the topside markings on the processor. This diagram is to aid in the

identification of the processor.

Figure 2-4. Processor Top-Side Markings

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

16 Order Number: 323107-002US

Page 17

Package Mechanical Specifications

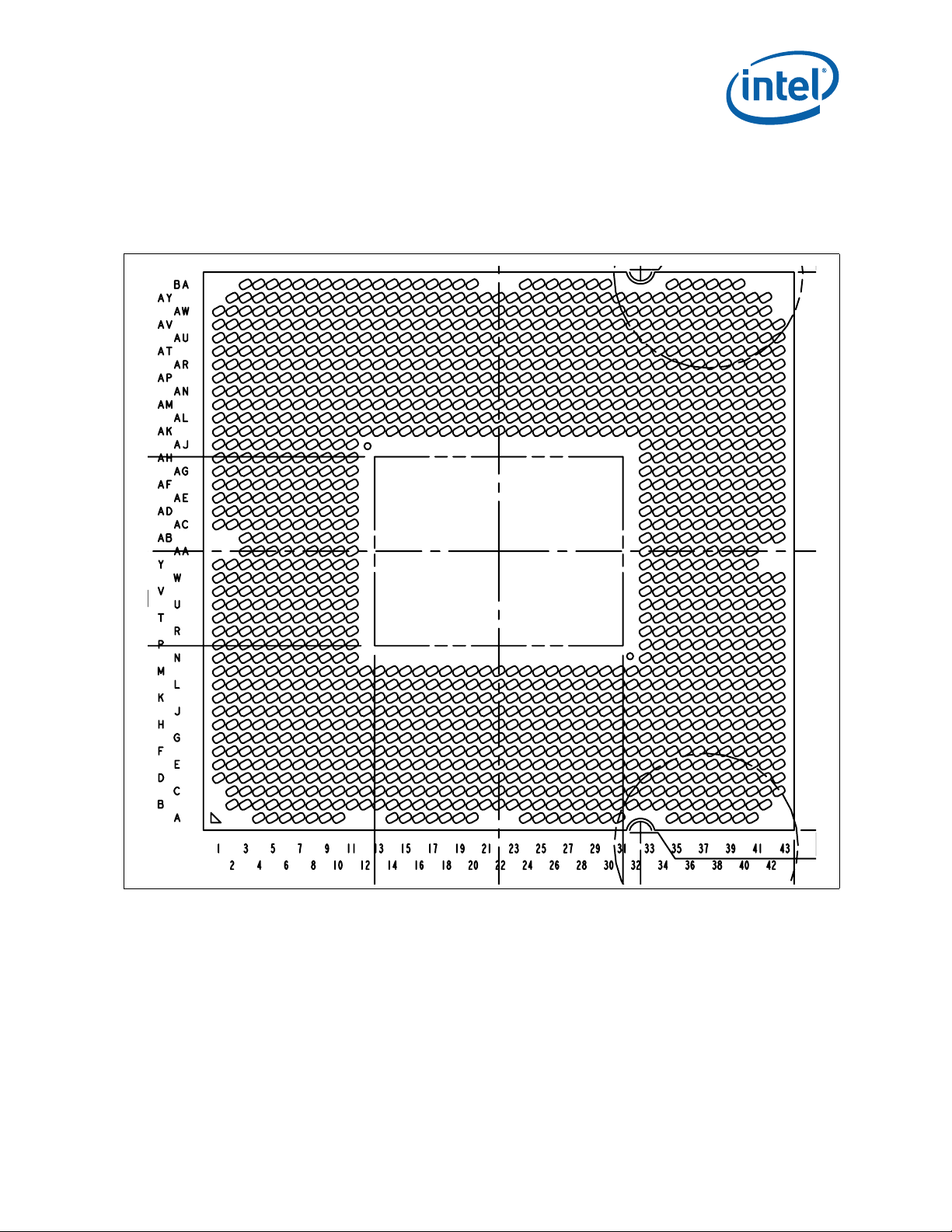

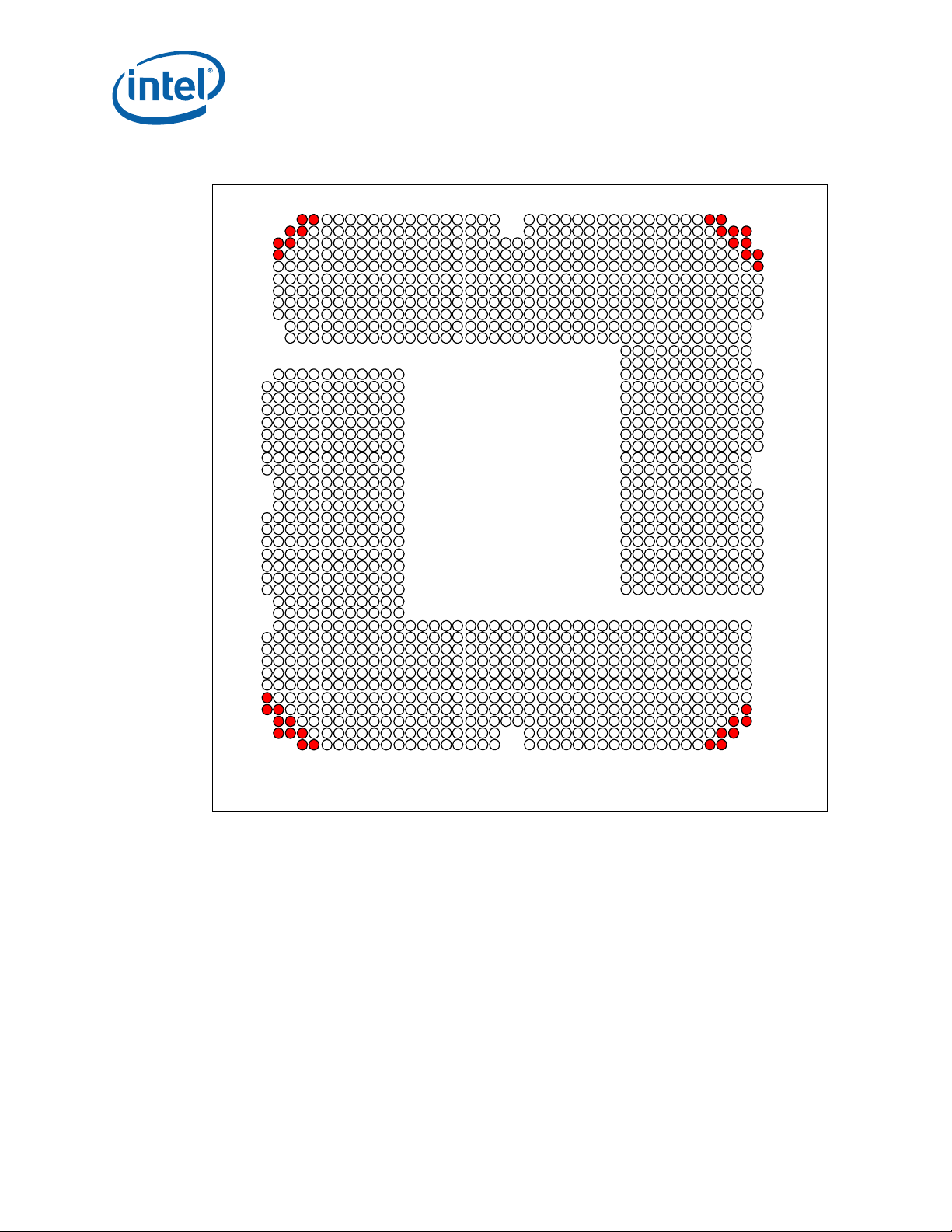

2.1.9 Processor Land Coordinates

Figure 2-5 shows the bottom view of the processor land coordinates. The coordinates

.

Figure 2-5. Processor Land Coordinates and Quadrants, Bottom View

are referred to throughout the document to identify processor lands.

§

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 17

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 18

socket

cavity

package socket

cavity

package

LGA1366 Socket

3 LGA1366 Socket

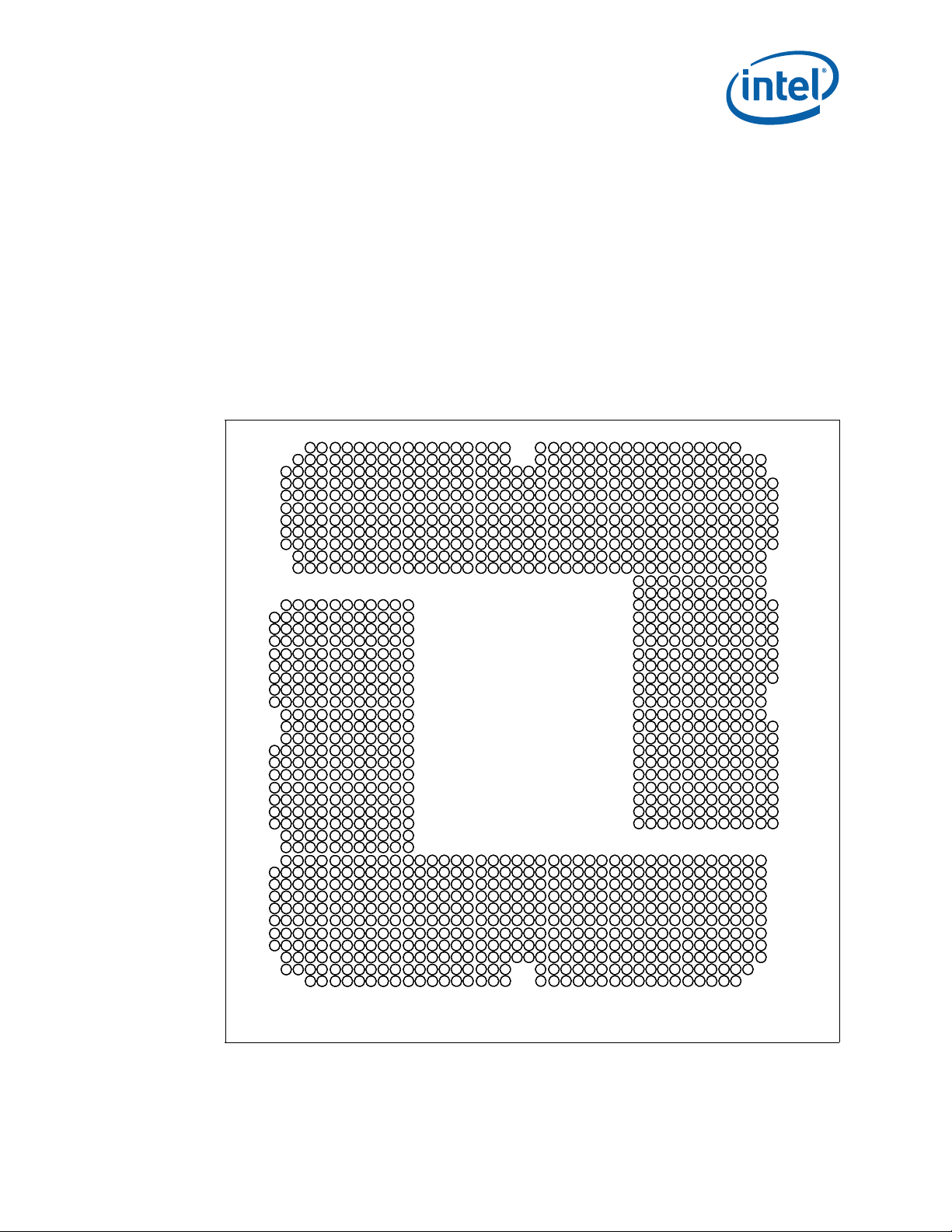

This section describes a surface mount, LGA (Land Grid Array) socket intended for the

Intel® Xeon® processor C5500/C3500 series in the Picket Post platform. The socket

provides I/O, power and ground contacts. The socket contains 1366 contacts arrayed

about a cavity in the center of the socket with lead-free solder balls for surface

mounting on the motherboard.

The socket has 1366 contacts with 1.016 mm X 1.016 mm pitch (X by Y) in a 43 x 41

grid array with 21 x 17 grid depopulation in the center of the array and selective

depopulation elsewhere.

The socket must be compatible with the package (processor) and the Independent

Loading Mechanism (ILM). The design includes a back plate which is integral to having

a uniform load on the socket solder joints. Socket loading specifications are listed in

Section 5.

Figure 3-1. LGA1366 Socket with Pick and Place Cover Removed

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 18

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 19

Figure 3-2. LGA1366 Socket Contact Numbering (Top View of Socket)

LGA1366 Socket

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

19 Order Number: 323107-002US

Page 20

A C E G J L N R U W AA AC AE AG AJ AL AN AR AU AW BA

B D F H K M P T V Y AB AD AF AH AK AM AP AT AV AY BB

1

3

7

5

9

11

15

13

17

19

23

21

25

27

31

29

1

3

7

5

9

11

15

13

17

19

23

21

25

27

31

29

2

8

4

6

10

16

12

14

18

24

20

22

26

32

28

30

2

8

4

6

10

16

12

14

18

24

20

22

26

32

28

30

16

12

15

13

14

17

18

24

20

19

23

21

22

25

26

32

28

27

31

29

30

33

34

40

36

35

39

37

38

41

42

43

LGA1366 Socket

3.1 Board Layout

The land pattern for the LGA1366 socket is 40 mils X 40 mils (X by Y), and the pad size

is 18 mils. There is no round-off (conversion) error between socket pitch (1.016 mm)

and board pitch (40 mil) because these values are equivalent.

In general, metal defined (MD) pads perform better than solder mask defined (SMD)

pads under thermal cycling, and SMD pads perform better than MD pads under

dynamic stress. Recommendations for pad definition on a per pad basis do not exist for

the LGA1366 socket.

The 40 mil spacing results in a reduced drill keepout as compared to previous

platforms. Drill keepout is explained in section 3.2.1 of the Intel

Design Guide (PDG). Select PCB suppliers are capable of producing 40 mil spacing.

Figure 3-3. LGA1366 Socket Land Pattern (Top View of Board)

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 20

®

Xeon® 5500 Platform

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 21

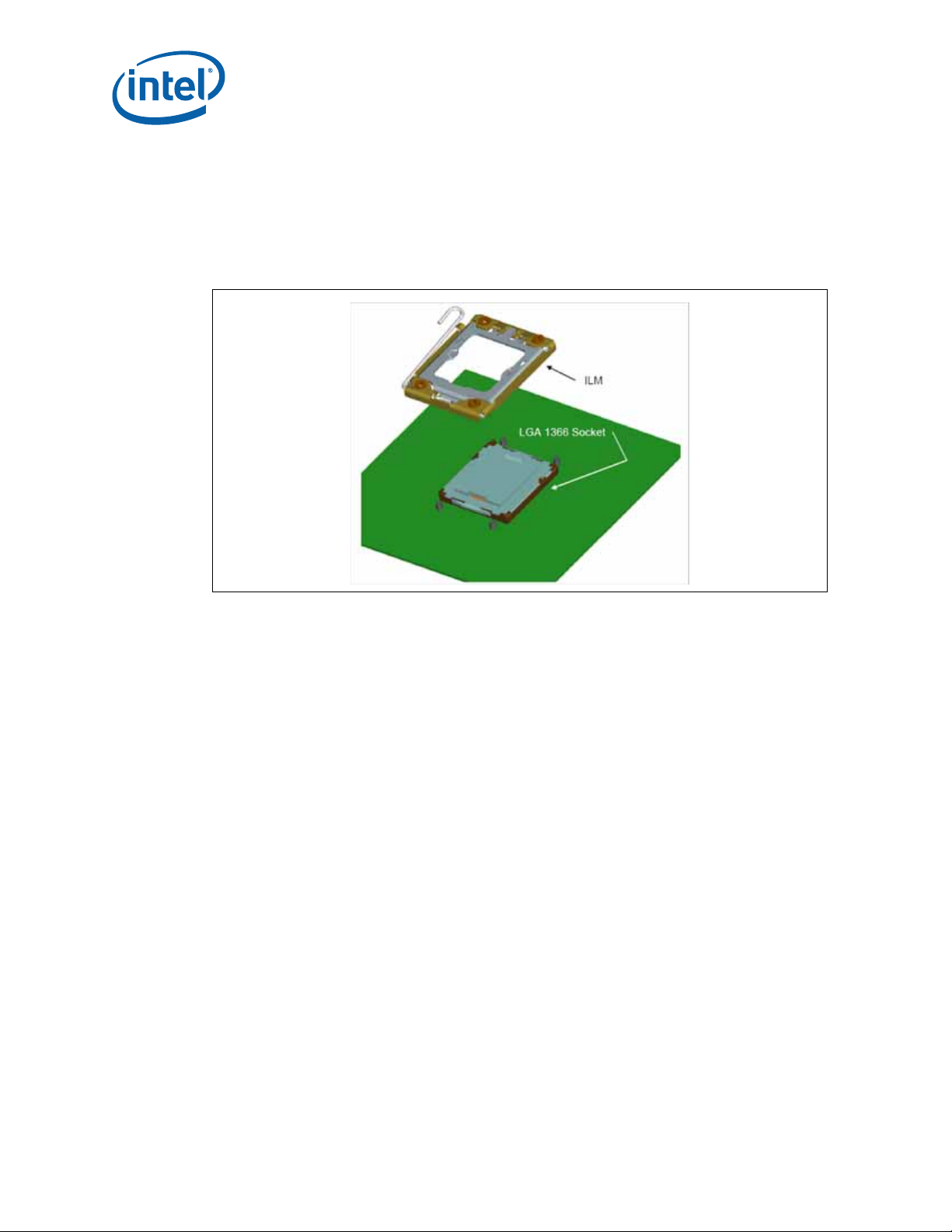

3.2 Attachment to Motherboard

The socket is attached to the motherboard by 1366 solder balls. There are no additional

external methods (i.e. screw, extra solder, adhesive, etc.) to attach the socket. As

indicated in Figure 3-4, the Independent Loading Mechanism (ILM) is not present

during the attach (reflow) process.

Figure 3-4. Attachment to Motherboard

LGA1366 Socket

3.3 Socket Components

The socket has two main components, the socket body and Pick and Place (PnP) cover,

and is delivered as a single integral assembly. See Appendix C for detailed drawings.

3.3.1 Socket Body Housing

The housing material is thermoplastic or equivalent with UL 94 V -0 flame rating capable

of withstanding 260°C for 40 seconds (typical reflow/rework). The socket coefficient of

thermal expansion (in the XY plane), and creep properties, must be such that the

integrity of the socket is maintained for the conditions listed in Section 8.

The color of the housing will be dark as compared to the solder balls. This provides the

contrast needed for pick and place vision systems.

3.3.2 Solder Balls

A total of 1366 solder balls corresponding to the contacts are on the bottom of the

socket for surface mounting with the motherboard.

The socket has the following solder ball material:

• Lead free SAC (SnAgCu) solder alloy with a silver (Ag) content between 3% and

4% and a melting temperature of approximately 217°C. The alloy must be

compatible with immersion silver (ImAg) motherboard surface finish and a SAC

alloy solder paste.

The co-planarity (profile) and true position requirements are defined in Appendix C.

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

21 Order Number: 323107-002US

Page 22

LGA1366 Socket

3.3.3 Contacts

Base material for the contacts is high strength copper alloy.

For the area on socket contacts where processor lands will mate, there is a 0.381 μm

[15 μinches] minimum gold plating over 1.27 μm [50 μinches] minimum nickel

underplate.

No contamination by solder in the contact area is allowed during solder reflow.

3.3.4 Pick and Place Cover

The cover provides a planar surface for vacuum pick up used to place components in

the Surface Mount Technology (SMT) manufacturing line. The cover remains on the

socket during reflow to help prevent contamination during reflow. The cover can

withstand 260° C for 40 seconds (typical reflow/rework profile) and the conditions

listed in Section 6 without degrading.

As indicated in Figure 3-5, the cover remains on the socket during ILM installation, and

should remain on whenever possible to help prevent damage to the socket contacts.

Cover retention must be sufficient to support the socket weight during lifting,

translation, and placement (board manufacturing), and during board and system

shipping and handling.

The covers are designed to be interchangeable between socket suppliers. As indicated

in Figure 3-5, a Pin1 indicator on the cover provides a visual reference for proper

orientation with the socket.

Figure 3-5. Pick and Place Cover

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 22

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 23

3.4 Package Installation / Removal

alignment

walls

orientation

notch

orientation

post

access

Pin1 triangle

Pin1 chamfer

alignment

walls

orientation

notch

orientation

post

access

Pin1 triangle

Pin1 chamfer

As indicated in Figure 3-6, access is provided to facilitate manual installation and

removal of the package.

To assist in package orientation and alignment with the socket:

• The package Pin1 triangle and the socket Pin1 chamfer provide visual reference for

proper orientation.

• The package substrate has orientation notches along two opposing edges of the

package, offset from the centerline. The socket has two corresponding orientation

posts to physically prevent mis-orientation of the package. These orientation

features also provide initial rough alignment of package to socket.

• The socket has alignment walls at the four corners to provide final alignment of the

.

Figure 3-6. Package Installation / Removal Features

package.

LGA1366 Socket

3.4.1 Socket Standoffs and Package Seating Plane

Intel

Thermal/Mechanical Design Guide August 2010

23 Order Number: 323107-002US

Standoffs on the bottom of the socket base establish the minimum socket height after

solder reflow and are specified in Appendix C.

Similarly, a seating plane on the topside of the socket establishes the minimum

package height. See Section 5.2 for the calculated IHS height above the motherboard.

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 24

LGA1366 Socket

3.5 Durability

The socket must withstand 30 cycles of processor insertion and removal. The max

chain contact resistance from Table 5-4 must be met when mated in the 1st and 30th

cycles.

The socket Pick and Place cover must withstand 15 cycles of insertion and removal.

3.6 Markings

There are three markings on the socket:

• LGA1366: Font type is Helvetica Bold - minimum 6 point (2.125 mm).

• Manufacturer's insignia (font size at supplier's discretion).

• Lot identification code (allows traceability of manufacturing date and location).

All markings must withstand 260° C for 40 seconds (typical reflow/rework profile)

without degrading, and must be visible after the socket is mounted on the

motherboard.

LGA1366 and the manufacturer's insignia are molded or laser marked on the side wall.

3.7 Component Insertion Forces

Any actuation must meet or exceed SEMI S8-95 Safety Guidelines for Ergonomics/

Human Factors Engineering of Semiconductor Manufacturing Equipment, example T able

R2-7 (Maximum Grip Forces). The socket must be designed so that it requires no force

to insert the package into the socket.

3.8 Socket Size

Socket information needed for motherboard design is given in Appendix C.

This information should be used in conjunction with the reference motherboard keep-

out drawings provided in Appendix B to ensure compatibility with the reference thermal

mechanical components.

3.9 LGA1366 Socket NCTF Solder Joints

Intel has defined selected solder joints of the socket as non-critical to function (NCTF)

when evaluating package solder joints post environmental testing. The processor

signals at NCTF locations are typically redundant ground or non-critical reserved, so the

loss of the solder joint continuity at end of life conditions will not affect the overall

product functionality. Figure 3-7 identifies the NCTF solder joints.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 24

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 25

.

A C E G J L N R U W AA AC AE AG AJ AL AN AR AU AW BA

B D F H K M P T V Y AB AD AF AH AK AM AP AT AV AY BB

1

3

7

5

9

11

15

13

17

19

23

21

25

27

31

29

1

3

7

5

9

11

15

13

17

19

23

21

25

27

31

29

2

8

4

6

10

16

12

14

18

24

20

22

26

32

28

30

2

8

4

6

10

16

12

14

18

24

20

22

26

32

28

30

16

12

15

13

14

17

18

24

20

19

23

21

22

25

26

32

28

27

31

29

30

33

34

40

36

35

39

37

38

41

42

43

Figure 3-7. LGA1366 NCTF Solder Joints

LGA1366 Socket

Note: For platforms supporting the DP processor land C3 is CTF.

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

25 Order Number: 323107-002US

§

Page 26

Independent Loading Mechanism (ILM)

4 Independent Loading

Mechanism (ILM)

The Independent Loading Mechanism (ILM) provides the force needed to seat the

1366-LGA land package onto the socket contacts. The ILM is physically separate from

the socket body. The assembly of the ILM is expected to occur after wave solder. The

exact assembly location is dependent on manufacturing preference and test flow. See

the Manufacturing Advantage Service collateral for this platform for additional

guidance.

Note: The ILM has two critical functions: deliver the force to seat the processor onto the

socket contacts and distribute the resulting load evenly through the socket solder

joints.

Note: The mechanical design of the ILM is integral to the overall functionality of the LGA1366

socket. Intel performs detailed studies on integration of processor package, socket and

ILM as a system. These studies directly impact the design of the ILM. The Intel

reference ILM will be “build to print” from Intel controlled drawings. Intel recommends

using the Intel Reference ILM. Custom non-Intel ILM designs do not benefit from Intel's

detailed studies and may not incorporate critical design parameters.

4.1 Design Concept

The ILM consists of two assemblies that will be procured as a set from the enabled

vendors. These two components are ILM cover assembly and back plate.

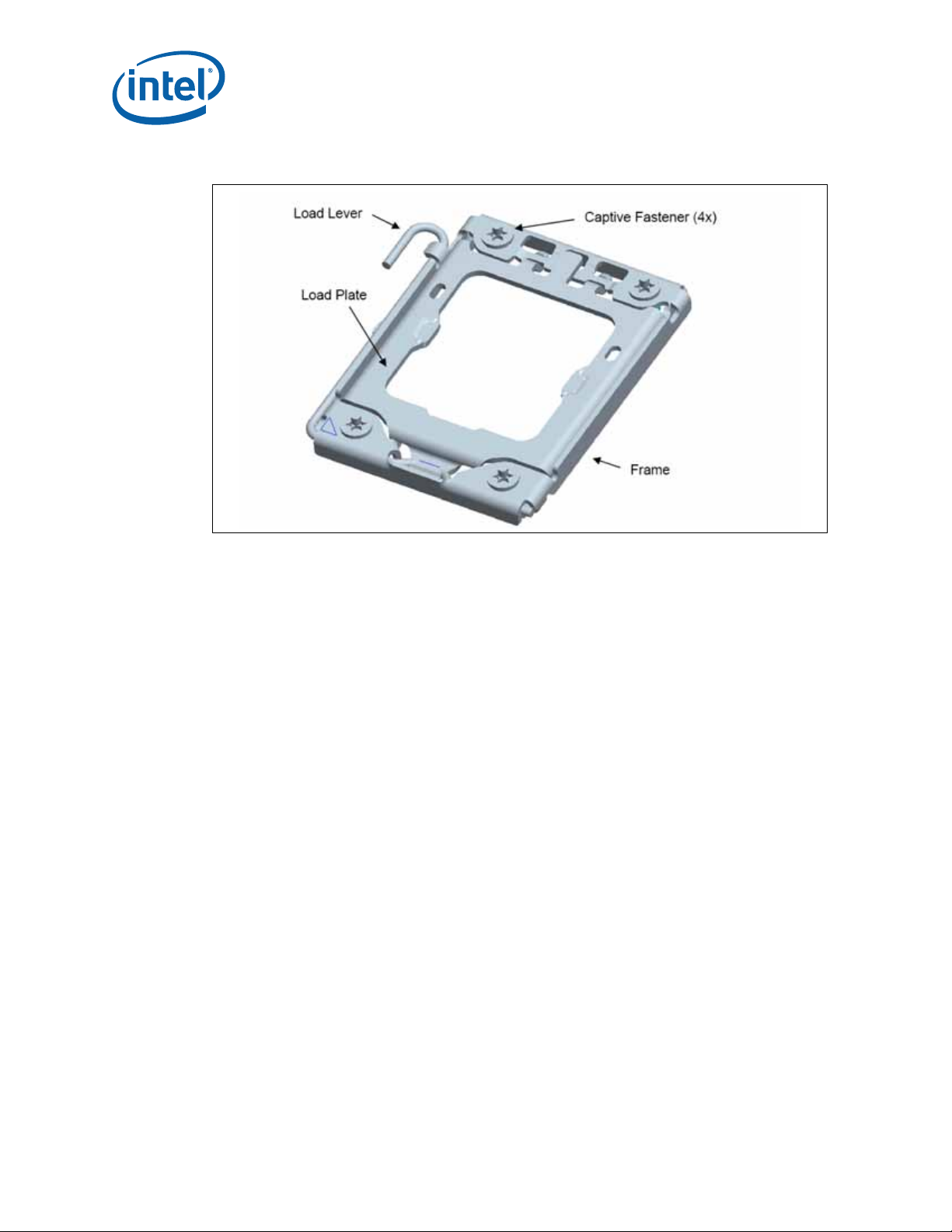

4.1.1 ILM Cover Assembly Design Overview

The ILM cover assembly consists of four major pieces: load lever, load plate, frame and

the captive fasteners.

The load lever and load plate are stainless steel. The frame and fasteners are high

carbon steel with appropriate plating. The fasteners are fabricated from a high carbon

steel. The frame provides the hinge locations for the load lever and load plate.

The cover assembly design ensures that once assembled to the back plate and the load

lever is closed, the only features touching the board are the captive fasteners. The

nominal gap of the frame to the board is ~1 mm when the load plate is closed on the

empty socket or when closed on the processor package.

When closed the load plate applies two point loads onto the IHS at the “dimpled”

features shown in Figure 4-1. The reaction force from closing the load plate is

transmitted to the frame and through the captive fasteners to the back plate. Some of

the load is passed through the socket body to the board inducing a slight compression

on the solder joints.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 26

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 27

Figure 4-1. ILM Cover Assembly

Independent Loading Mechanism (ILM)

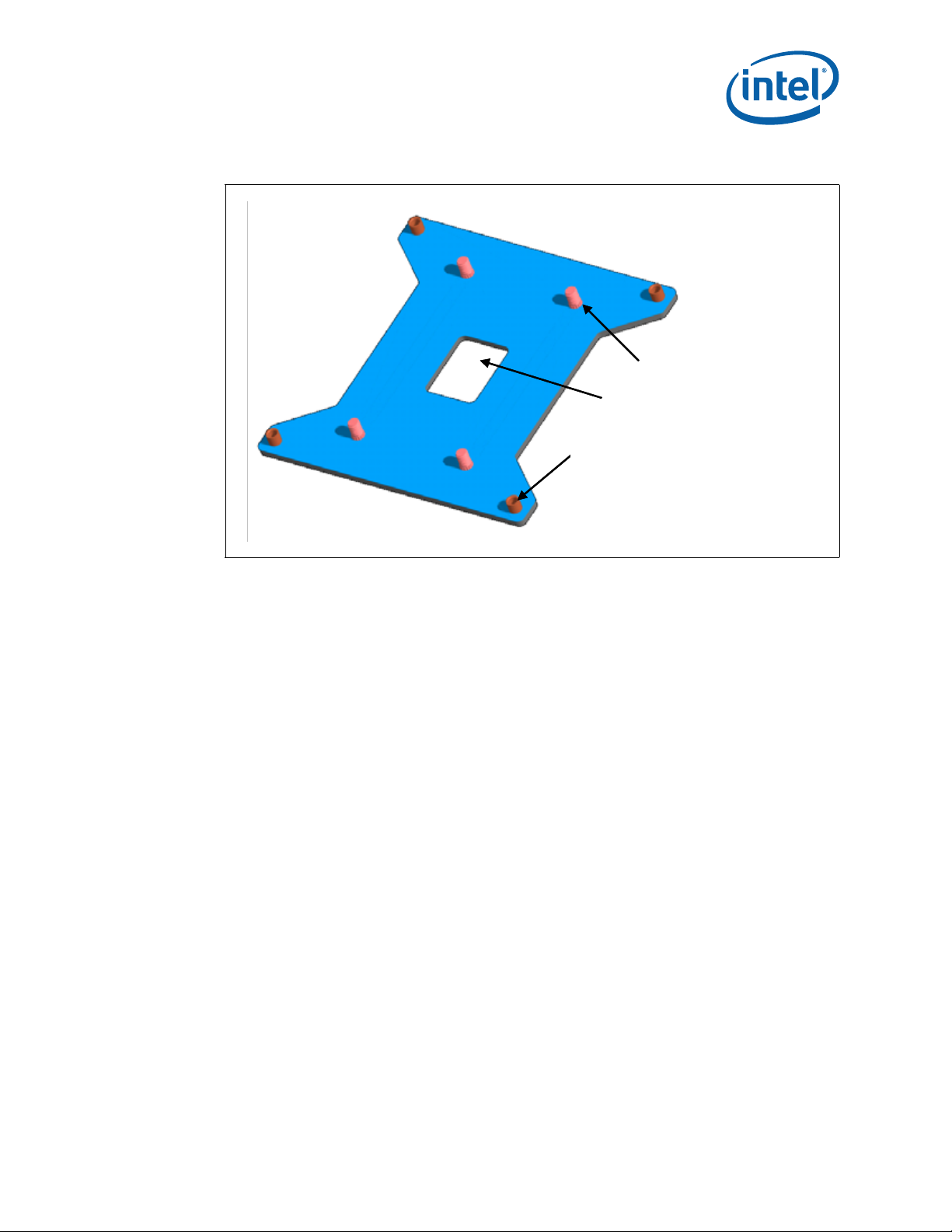

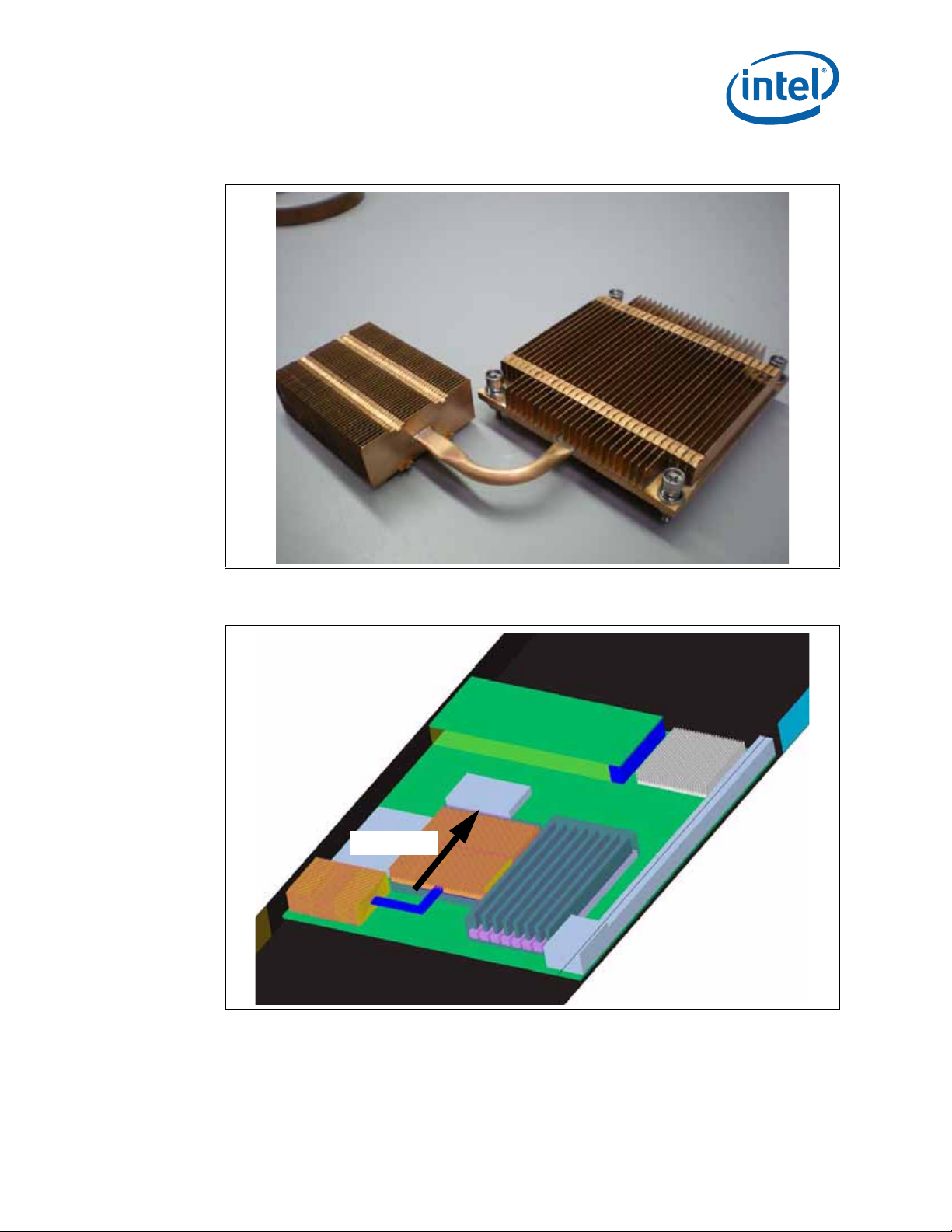

4.1.2 ILM Back Plate Design Overview

The unified back plate for 2-socket server and 2-socket Workstation products consists

of a flat steel back plate with threaded studs for ILM attach, and internally threaded

nuts for heatsink attach. The threaded studs have a smooth surface feature that

provides alignment for the back plate to the motherboard for proper assembly of the

ILM around the socket. A clearance hole is located at the center of the plate to allow

access to test points and backside capacitors. An additional cut-out on two sides

provides clearance for backside voltage regulator components. An insulator is preapplied.

Back plates for processors in 1-socket workstation platforms are covered in the Intel

®

Processor 3500 Series Thermal/Mechanical Design Guide.

Xeon

®

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

27 Order Number: 323107-002US

Page 28

Threaded studs

Threaded nuts

Clearance hole

C

u

t

-

o

u

t

Threaded studs

Threaded nuts

Clearance hole

C

u

t

-

o

u

t

C

u

t

-

o

u

t

Threaded studs

Clearance hole

Threaded nuts

Independent Loading Mechanism (ILM)

Figure 4-2. Back Plate

4.2 Assembly of ILM to a Motherboard

The ILM design allows a bottoms up assembly of the components to the board. In

step 1 (see Figure 4-3), the back plate is placed in a fixture. Holes in the motherboard

provide alignment to the threaded studs. In step 2, the ILM cover assembly is placed

over the socket and threaded studs. Using a T20 Torx* driver fasten the ILM cover

assembly to the back plate with the four captive fasteners. Torque to 8 inch-pounds.

The length of the threaded studs accommodate board thicknesses from 0.062” -

0.100”.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 28

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 29

.

Figure 4-3. ILM Assembly

Independent Loading Mechanism (ILM)

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

29 Order Number: 323107-002US

Page 30

Independent Loading Mechanism (ILM)

As indicated in Figure 4-4, socket protrusion and ILM key features prevent 180-degree

rotation of ILM cover assembly with respect to socket. The result is a specific Pin 1

orientation with respect to ILM lever.

See the Manufacturing Advantage Service for additional details on fixtures and

assembly guidance.

Figure 4-4. Pin1 and ILM Lever

§

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 30

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 31

LGA1366 Socket and ILM Electrical, Mechanical and Environmental Specifications

5 LGA1366 Socket and ILM

Electrical, Mechanical and

Environmental Specifications

This chapter describes the electrical, mechanical and environmental specifications for

the LGA1366 socket and the Independent Loading Mechanism.

5.1 Component Mass

Table 5-1. Socket Component Mass

Component Mass

Socket body, contacts, and PnP cover 15 gm

ILM cover 43 gm

ILM back plate for dual processor server products 100 gm

Notes:

1. Preliminary guidance.

5.2 Package/Socket Stackup Height

Table 5-2 provides the stackup height of a processor in the 1366-land LGA package and

LGA1366 socket with the ILM closed and the processor fully seated in the socket.

Table 5-2. 1366-land Package and LGA1366 Socket Stackup Height

Integrated stackup height (mm)

From top of board to top of IHS

Notes:

1. This data is provided for information only, and should b e deriv ed from: (a) th e height of th e sock et se ating

plane above the motherboard after reflow, given in Appendix C, (b) the height of the package, from the

package seating plane to the top of the IHS, and accounting for its nominal variation and tolerances that

are given in the corresponding processor Datasheet.

2. This value is a RSS calculation.

7.729 ± 0.282 mm

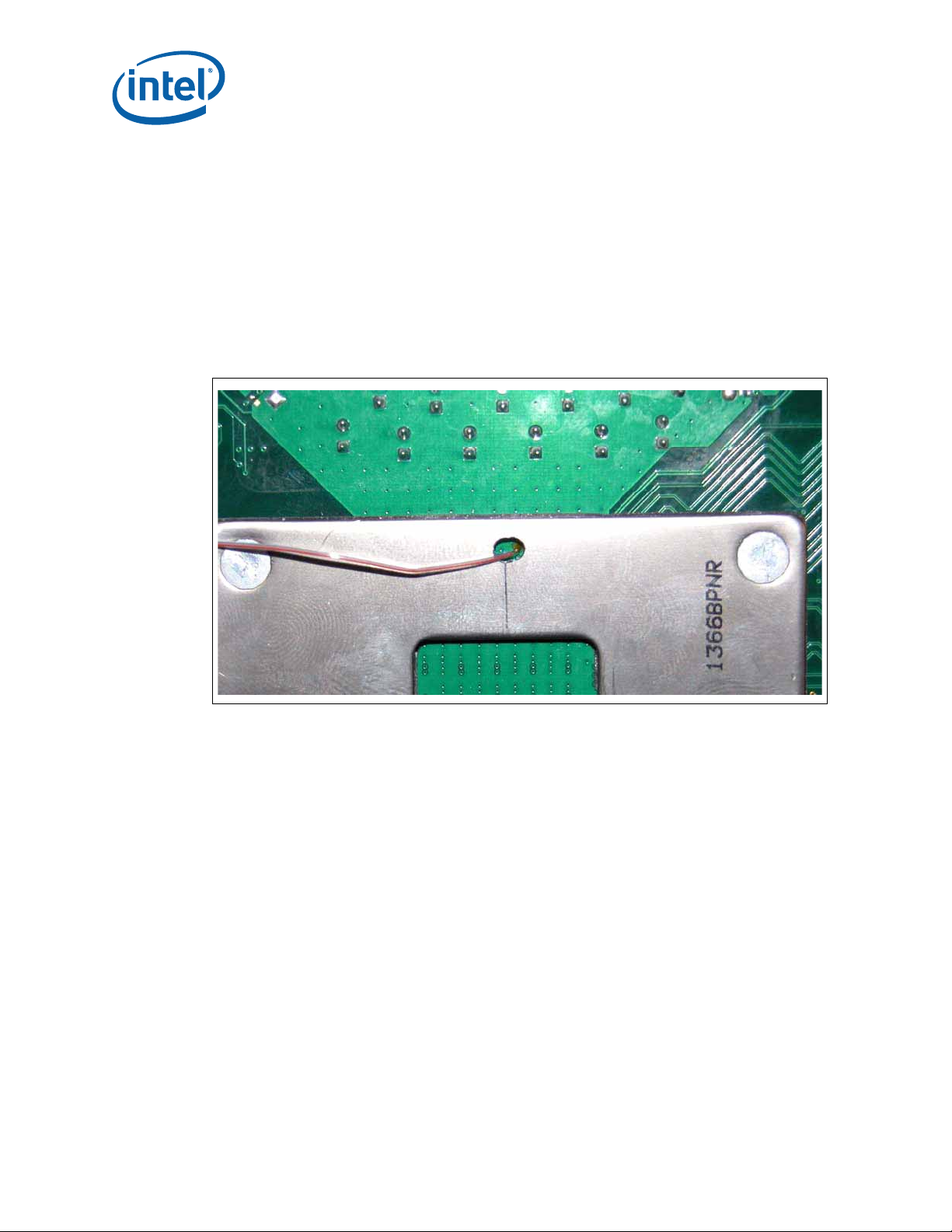

5.3 Socket Maximum Temperature

The power dissipated within the socket is a function of the current at the pin level and

the effective pin resistance. To ensure socket long term reliability, Intel defines socket

maximum temperature using a via on the underside of the motherboard. Exceeding the

temperature guidance may result in socket body deformation, or increases in thermal

and electrical resistance which can cause a thermal runaway and eventual electrical

failure. The guidance for socket maximum temperature is listed below:

• Via temperature under socket < 96 °C

The specific via used for temperature measurement is located on the bottom of the

motherboard between pins AY23, AY22, AW23, and AW22. See Figure 5-1.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 31

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 32

LGA1366 Socket and ILM Electrical, Mechanical and Environmental Specifications

The socket maximum temperature is defined at Thermal Design Current (TDC). In

addition, the heatsink performance targets and boundary conditions of Table 6-1 must

be met to limit power dissipation through the socket.

To measure via temperature:

1. Drill a hole through the back plate at the specific via defined above.

2. Thread a T-t ype therm ocouple (36 - 40 gauge) through the hole and glue it into the

specific via on the underside of the motherboard.

3. Once the glue dries, reinstall the back plate and measure the temperature.

Figure 5-1. Socket Temperature Measurement Location

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

32 Order Number: 323107-002US

Page 33

LGA1366 Socket and ILM Electrical, Mechanical and Environmental Specifications

5.4 Loading Specifications

The socket will be tested against the conditions listed in the LGA1366 Socket Validation

Reports with heatsink and the ILM attached, under the loading conditions outlined in

this chapter.

Table 5-3 provides load specifications for the LGA1366 socket with the ILM installed.

The maximum limits should not be exceeded during heatsink assembly, shipping

conditions, or standard use condition. Exceeding these limits during test may result in

component failure. The socket body should not be used as a mechanical reference or

load-bearing surface for thermal solutions.

Table 5-3. Socket and ILM Mechanical Specifications

Parameter Min Max Notes

Static compressive load from ILM cover to

processor IHS

Heatsink static compressive load 0 N [0 lbf]] 266 N [60 lbf] 1, 2, 3

Total static compressive load

(ILM plus Heatsink)

Dynamic compressive load (with heatsink

installed)

Pick & place cover insertion / removal force N/A 10.2 N [2.3 lbf]

Load lever actuation force N/A 38.3 N [8.6 lbf] in the

445 N [100 lbf] 623 N [140 lbf] 3, 4

470 N (106 lbf) 890 N (200 lbf) 3, 4

N/A 890 N [200 lbf] 1, 3, 5, 6

vertical direction.

10.2 N [2.3 lbf] in the

lateral direction.

Notes:

1. These specifications apply to uniform compressive loading in a direction perpendicular to the IHS top

surface.

2. This is the minimum and maximum static force that can be applied by the heatsink and it’s retention

solution to maintain the heatsink to IHS interface. This does not imply the Intel reference TIM is validated

to these limits.

3. Loading limits are for the LGA1366 socket.

4. This minimum limit defines the compressive force required to electrically seat the pr ocessor onto the socke t

contacts.

5. Dynamic loading is defined as an 11 ms duration average load superimposed on the static load

requirement.

6. Test co ndition used a heatsink mass of 550gm [1.21 lb] with 50 g acceleration measured at heatsink mass.

The dynamic portion of this specification in the product application can have flexibility in specific v alues, but

the ultimate product of mass times acceleration should not exceed this dynamic load.

5.4.1 Board Deflection Guidance

See Intel® Xeon® Processor 5500 Series Thermal/Mechanical Design Guide (TMDG),

Revision 2.1 for detailed board deflection guidance.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 33

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 34

LGA1366 Socket and ILM Electrical, Mechanical and Environmental Specifications

5.5 Electrical Requirements

LGA1366 socket electrical requirements are measured from the socket-seating plane of

the processor to the component side of the socket PCB to which it is attached. All

specifications are maximum values (unless otherwise stated) for a single socket

contact, but includes effects of adjacent contacts where indicated.

Table 5-4. Electrical Requirements for LGA1366 Socket

Parameter Value Comment

Mated loop inductance, loop <3.9 nH The inductance calculated for two contacts,

Mated partial mutual inductance, L NA The inductance on a contact due to any single

Maximum mutual capacitance, C <1 pF The capacitance between two contacts

Socket Average Contact Resistance

(EOL)

15.2 mΩ The socket average contact resistance target is

considering one forward conductor and one

return conductor. These values must be satisfied

at the worst-case height of the socket.

neighboring contact.

derived from average of every chain contact

resistance for each part used in testing, with a

chain contact resistance defined as the

resistance of each chain minus resistance of

shorting bars divided by number of lands in the

daisy chain.

Max Individual Contact Resistance

(EOL)

Bulk Resistance Increase ≤

Dielectric Withstand Voltage 360 Volts RMS

Insulation Resistance 800 MΩ

100 mΩ The specification listed is at room temperature

≤

3 mΩ The bulk resistance increase per contact from

The specification listed is at room temperature

and has to be satisfied at all time.

Socket Contact Resistance:

the socket contact, solderball, and interface

resistance to the interposer land.

and has to be satisfied at all time.

Socket Contact Resistance:

the socket contact, solderball, and interface

resistance to the interposer land; gaps included.

24° C to 107° C

The resistance of

The resistance of

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

34 Order Number: 323107-002US

Page 35

Establish the

market/expected use

environment for the

technology

Develop Speculative

stress conditions based on

historical data, content

experts, and literature

search

Perform stressing to

validate accelerated

stressing assumptions and

determine acceleration

factors

Freeze stressing

requirements and perform

additional data turns

LGA1366 Socket and ILM Electrical, Mechanical and Environmental Specifications

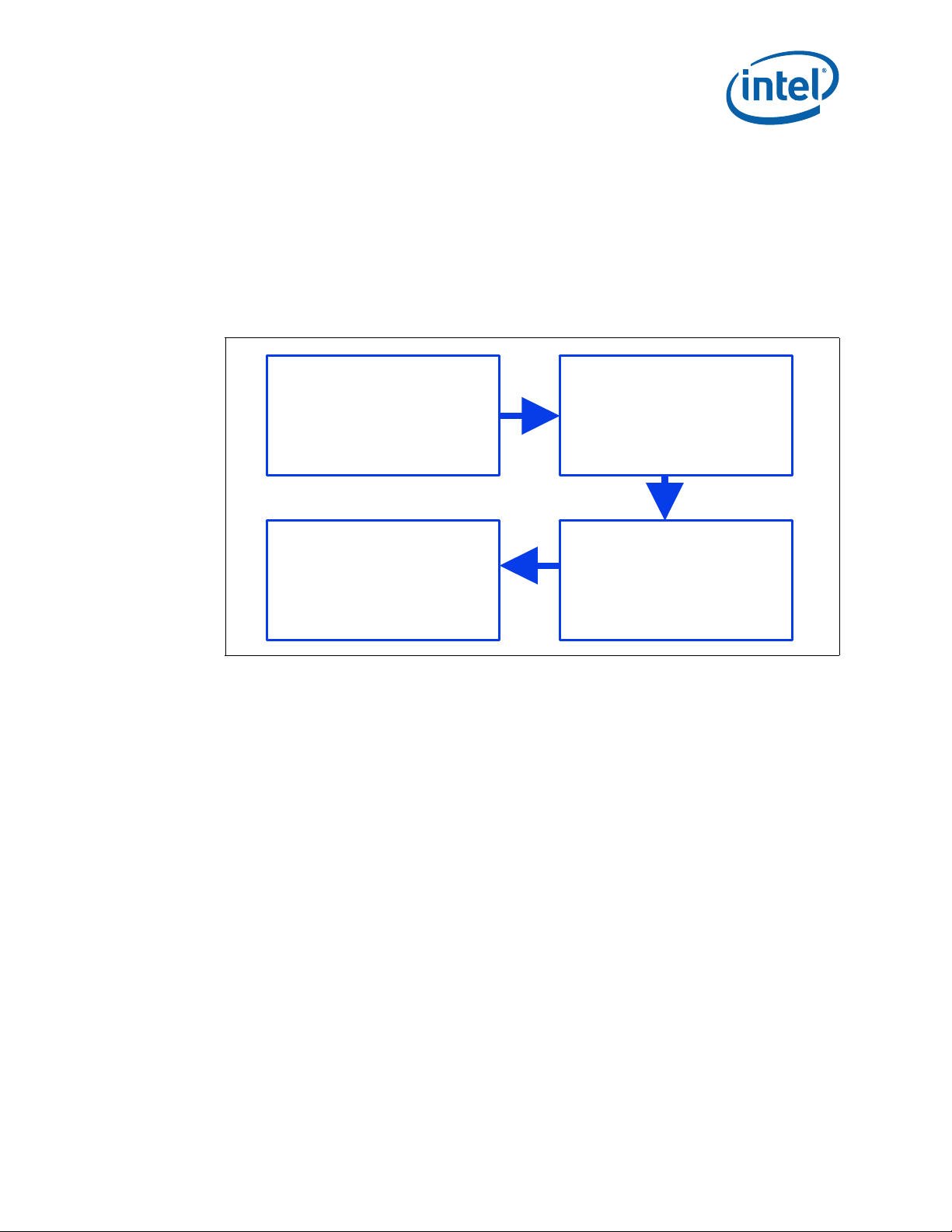

5.6 Environmental Requirements

Design, including materials, shall be consistent with the manufacture of units that meet

the following environmental reference points.

The reliability targets in this section are based on the expected field use environment

for these products. The test sequence for new sockets will be developed using the

knowledge-based reliability evaluation methodology, which is acceleration factor

dependent. A simplified process flow of this methodology can be seen in Figure 5-2.

Figure 5-2. Flow Chart of Knowledge-Based Reliability Evaluation Methodology

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 35

A detailed description of this methodology is at:

ftp://download.intel.com/technology/itj/q32000/pdf/reliability .pdf.

§

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 36

Thermal Specifications

6 Thermal Specifications

6.1 Package Thermal Specifications

The Intel® Xeon® processor C5500/C3500 series requires a thermal solution to

maintain temperatures within its operating limits. Any attempt to operate the processor

outside these operating limits may result in permanent damage to the processor and

potentially other components within the system. Maintaining the proper thermal

environment is key to reliable, long-term system operation.

A complete solution includes both component and system level thermal management

features. Component level thermal solutions can include active or passive heatsinks

attached to the processor integrated heat spreader (IHS).

This section provides data necessary for developing a complete thermal solution. For

more information on designing a component level thermal solution, see Section 7.

6.1.1 Thermal Specifications

To allow the optimal operation and long-term reliability of Intel processor-based

systems, the processor must remain within the minimum and maximum case

temperature (T

Thermal solutions not designed to provide this level of thermal capability may affect the

long-term reliability of the processor and system. These specifications are based on

pre-silicon estimates. These specifications may be further updated as more data

becomes available. Processors are listed here by TDP (Multiple SKUs may have the

same TDP and same spec).

®

The Intel

managing processor temperatures that is intended to support acoustic noise reduction

through fan speed control and to assure processor reliability. Selection of the

appropriate fan speed is based on the relative temperature data reported by the

processor’s Platform Environment Control Interface (PECI) as described in Section 6.3.

If PECI is less than TCONTROL, then the case temperature is permitted to exceed the

Thermal Profile, but PECI must remain at or below TCONTROL. If PECI >= TCONTROL,

then the case temperature must meet the Thermal Profile. The temperature reported

over PECI is always a negative value and represents a delta below the onset of thermal

control circuit (TCC) activation, as indicated by PROCHO T# (see Section 6.2, Processor

Thermal Features). Systems that implement fan speed control must be designed to use

this data. Systems that do not alter the fan speed only need to guarantee the case

temperature meets the thermal profile specifications.

The Intel

single Thermal Profile. See specifications below. For this processor, it is expected that

the Thermal Control Circuit (TCC) wo uld only be activ ated for very brief periods of time

when running the most power-intensive applications.

The Intel

single Thermal Profile. For this processor, it is expected that the Thermal Control Circuit

(TCC) would only be activated for very brief periods of time when running the most

power-intensive applications.

Xeon® processor C5500/C3500 series implements a methodology for

®

Xeon® processor EC5500 and EC3500 series (85 W and 65 W) supports a

®

Celeron® processor P1053 (30 W) (see specifications below) supports a

) specifications as defined by the applicable thermal profile.

CASE

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 36

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Page 37

Thermal Specifications

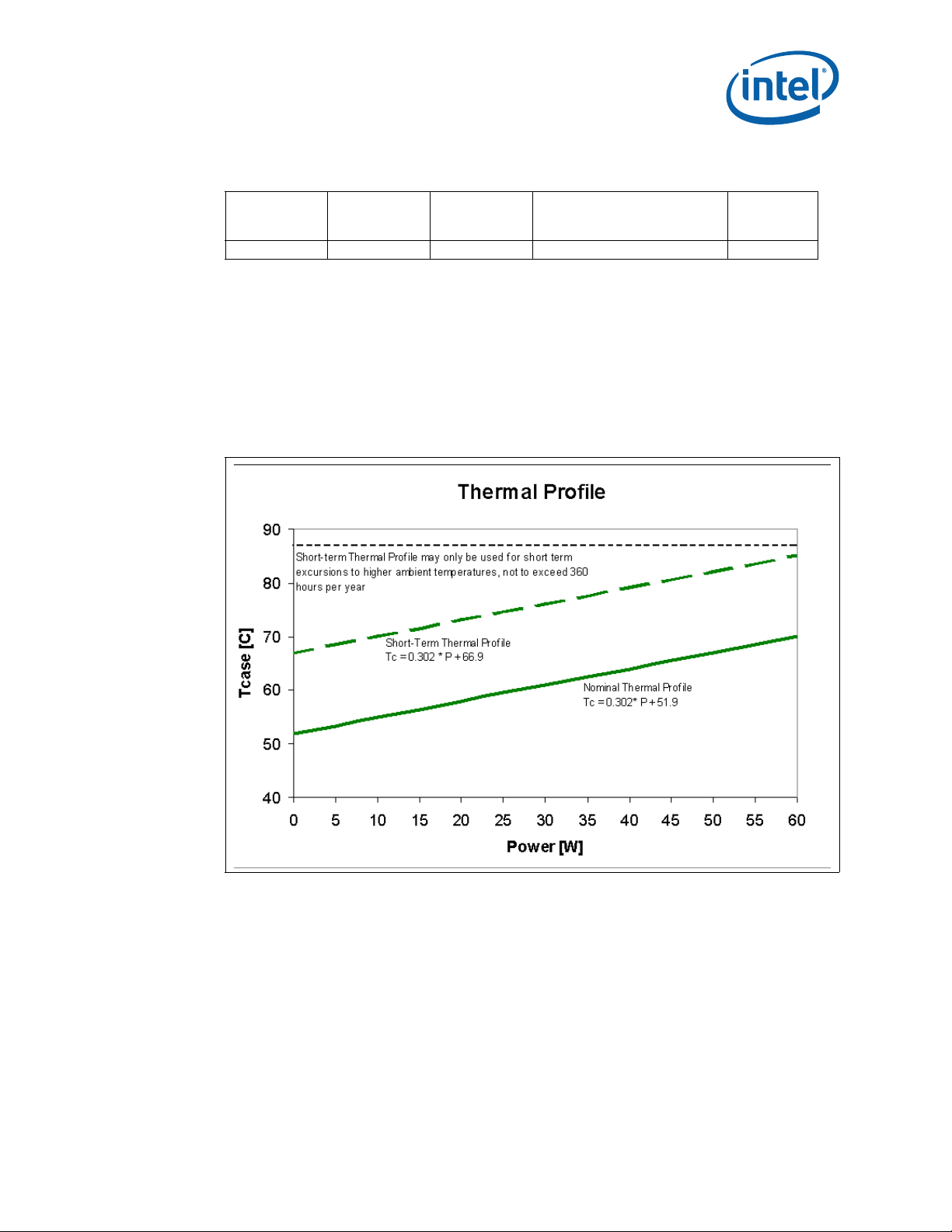

Thermal Profile

40

50

60

70

80

0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 85

Power [W ]

Tcase [C]

Thermal Profile

Tc = 0.3 03* P + 51. 8

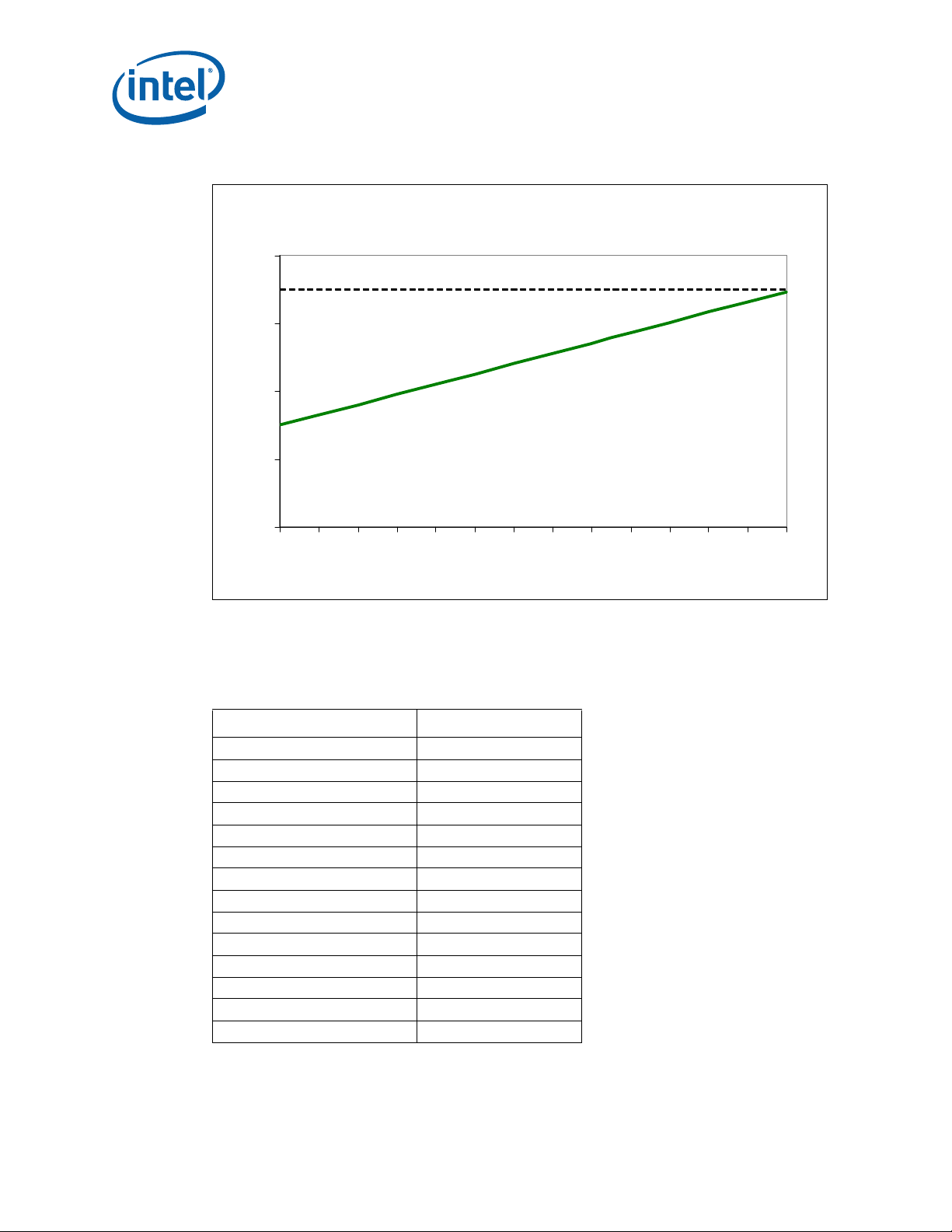

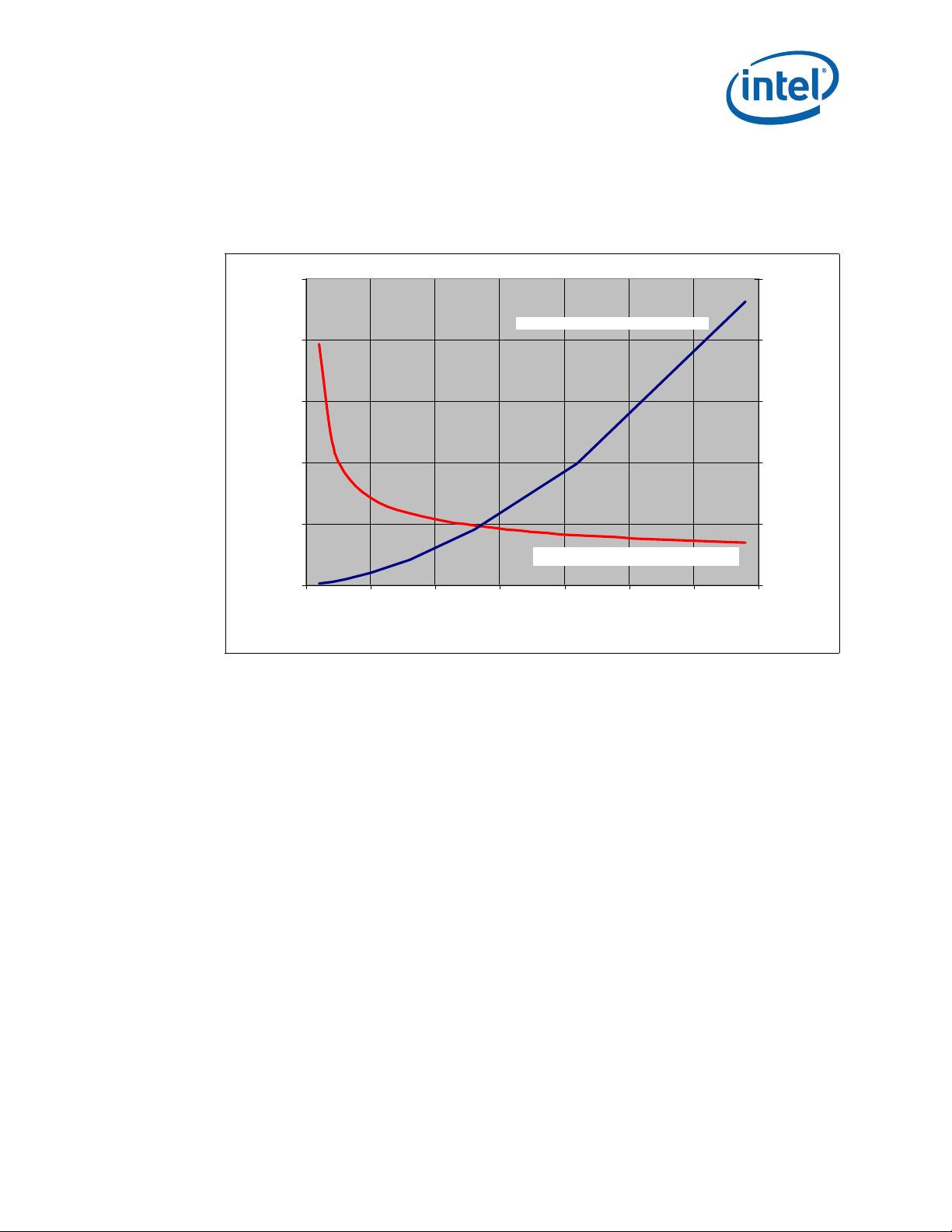

The Intel® Xeon® processor LC5500 and LC3500 series (60 W, 48 W, 35 W, and 23 W)

all support Thermal Profiles with nominal and short-term conditions designed to meet

NEBS Level 3 compliance. See specifications below. F or these SKUs, op eration at either

the nominal or short-term thermal profiles should result in virtually no TCC activation.

Analysis indicates that real applications are unlikely to cause the processor to consume

maximum power dissipation for sustained time periods. Intel recommends that

complete thermal solution designs target the Thermal Design Power (TDP), instead of

the maximum processor power consumption. The Adaptive Thermal Monitor feature is

intended to help protect the processor in the event that an application exceeds the TDP

recommendation for a sustained time period. For more details on this feature, see

Section 6.2. The Adaptive Thermal Monitor feature must be enabled for the

processor to remain within its specifications.

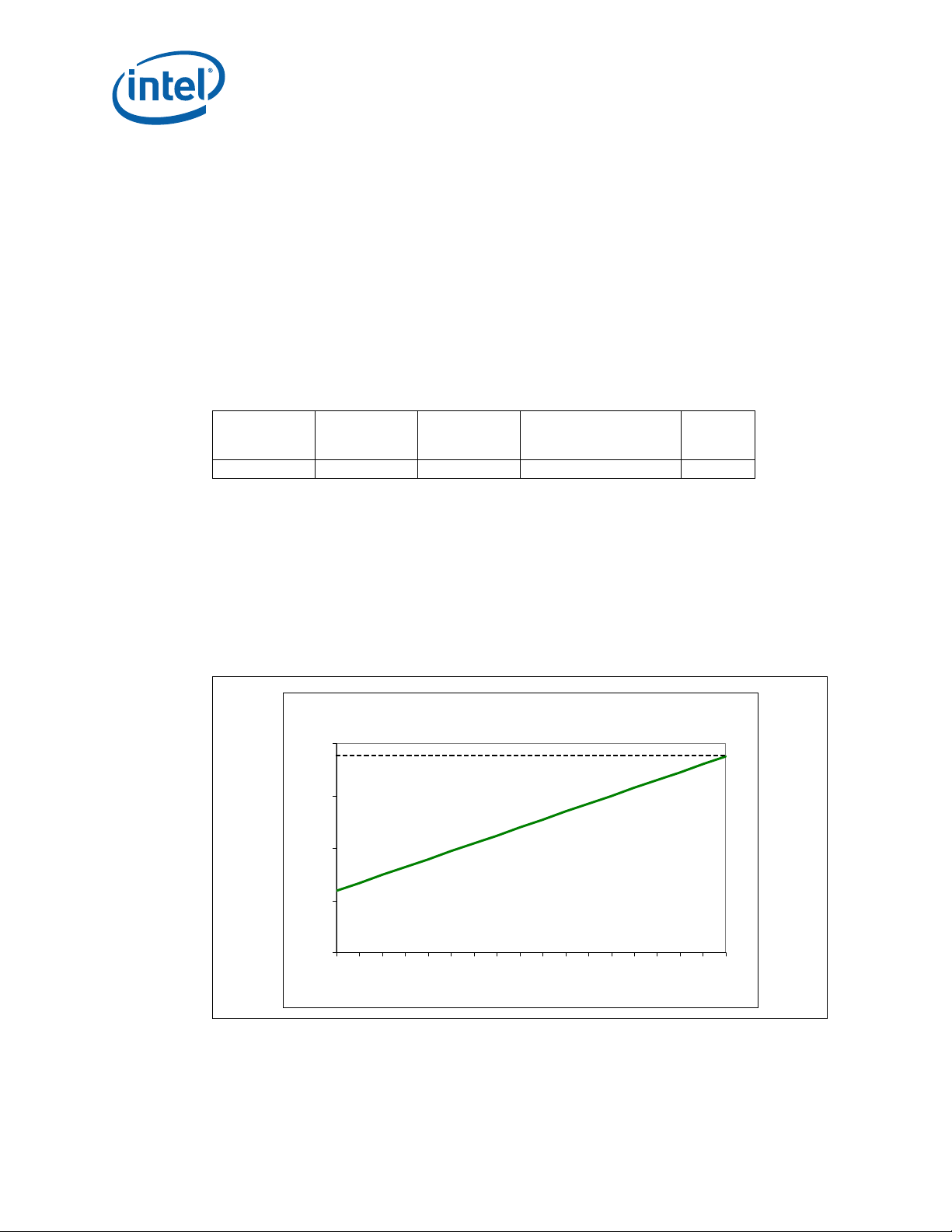

Table 6-1. Intel® Xeon® Processor EC5549 and EC5509 Thermal Specifications

Core

Frequency

Launch to FMB 85 5 See Figure 6-1; Table 6-2 1, 2, 3, 4, 5

Notes:

1. These values are specified at V

the processor is not to be subjected to any static V

specified ICC. See the loadline specifications in the Datasheet.

2. Thermal Design Power (TDP) should be used for processor thermal solution design targets. TDP is not the

maximum power that the processor can dissipate. TDP is measured at maximum T

3. These specifications are based on initial silicon characterization. These specifications may be further

updated as more characterization data becomes available.

4. Power specifications are defined at all VIDs found in the Datasheet. The Intel

C3500 series may be shipped under multiple VIDs for each frequency.

5. FMB (Flexible Motherboard) guidelines provide a design targ et for meeting all plan ned p roces sor fre quency

requirements.

Thermal Design

Power

(W)

Minimum

CASE

T

(°C)

for all processor frequencies. Systems must be designed to ensure

CC_MAX

CC

Maximum

CASE

T

(°C)

and ICC combination wherein VCC exceeds V

Notes

.

CASE

®

Xeon® processor C5500/

CC_MAX

at

Figure 6-1. Intel® Xeon® Processor EC5549 and EC5509 Thermal Profile

Notes:

1. Intel® Xeon® processor EC5549 and EC5509 Thermal Profile is representative of a volumetrically

unconstrained platform. See Table 6-2 for discrete points that constitute the thermal profile.

2. Implementation of Intel

TCC activation.

®

Xeon® processor EC5549 and EC5509 Thermal Profile should result in virtually no

®

Xeon® Processor C5500/C3500 Series and LGA1366 Socket

Intel

Thermal/Mechanical Design Guide August 2010

37 Order Number: 323107-002US

Page 38

Thermal Specifications

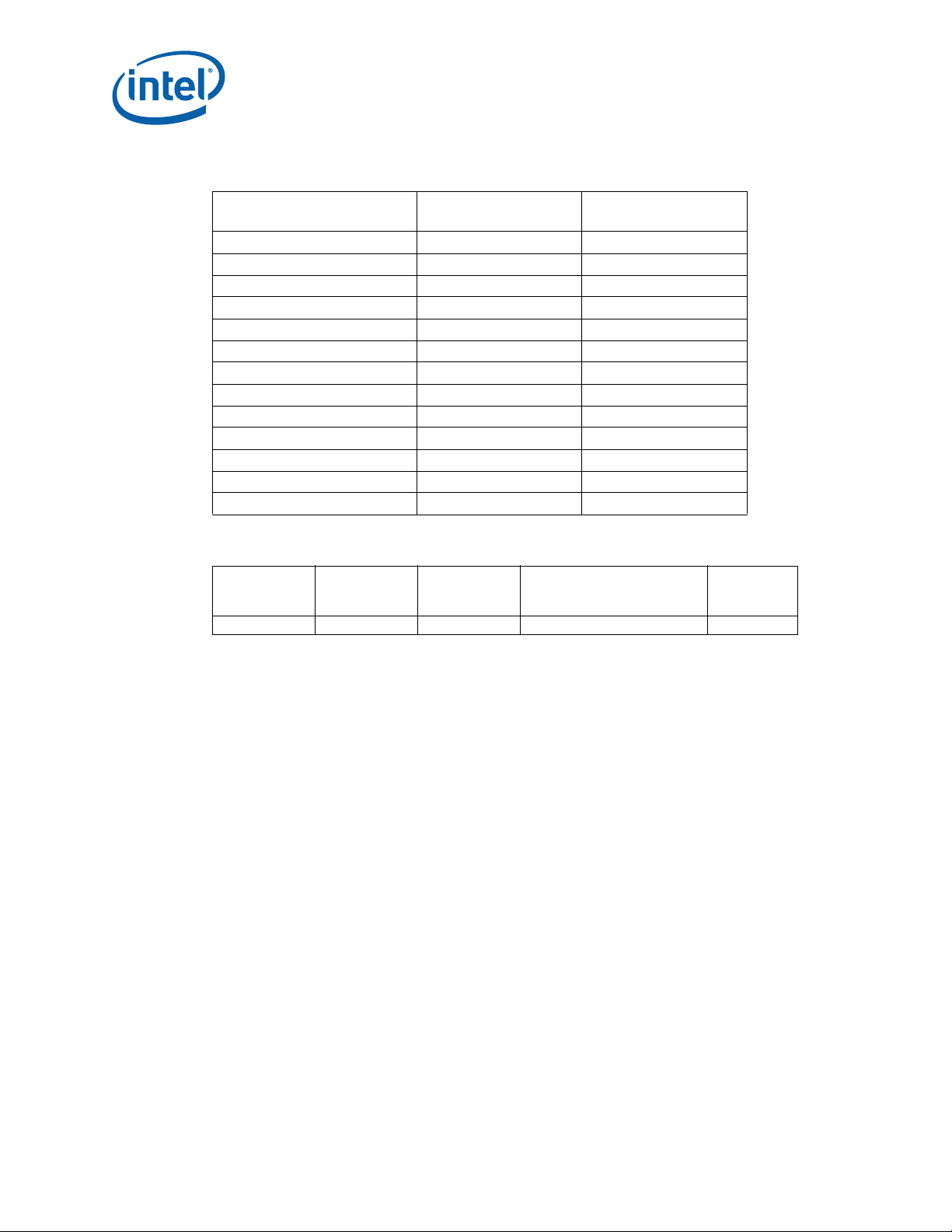

Table 6-2. Intel® Xeon® Processor EC5549 and EC5509 Thermal Profile

Power (W) T

CASE_MAX

(°C)

0 51.8

5 53.3

10 54.8

15 56.3

20 57.9

25 59.4

30 60.9

35 62.4

40 63.9

45 65.4

50 67.0

55 68.5

60 70.0

65 71.5

70 73.0

75 74.5

80 76.0

85 77.6

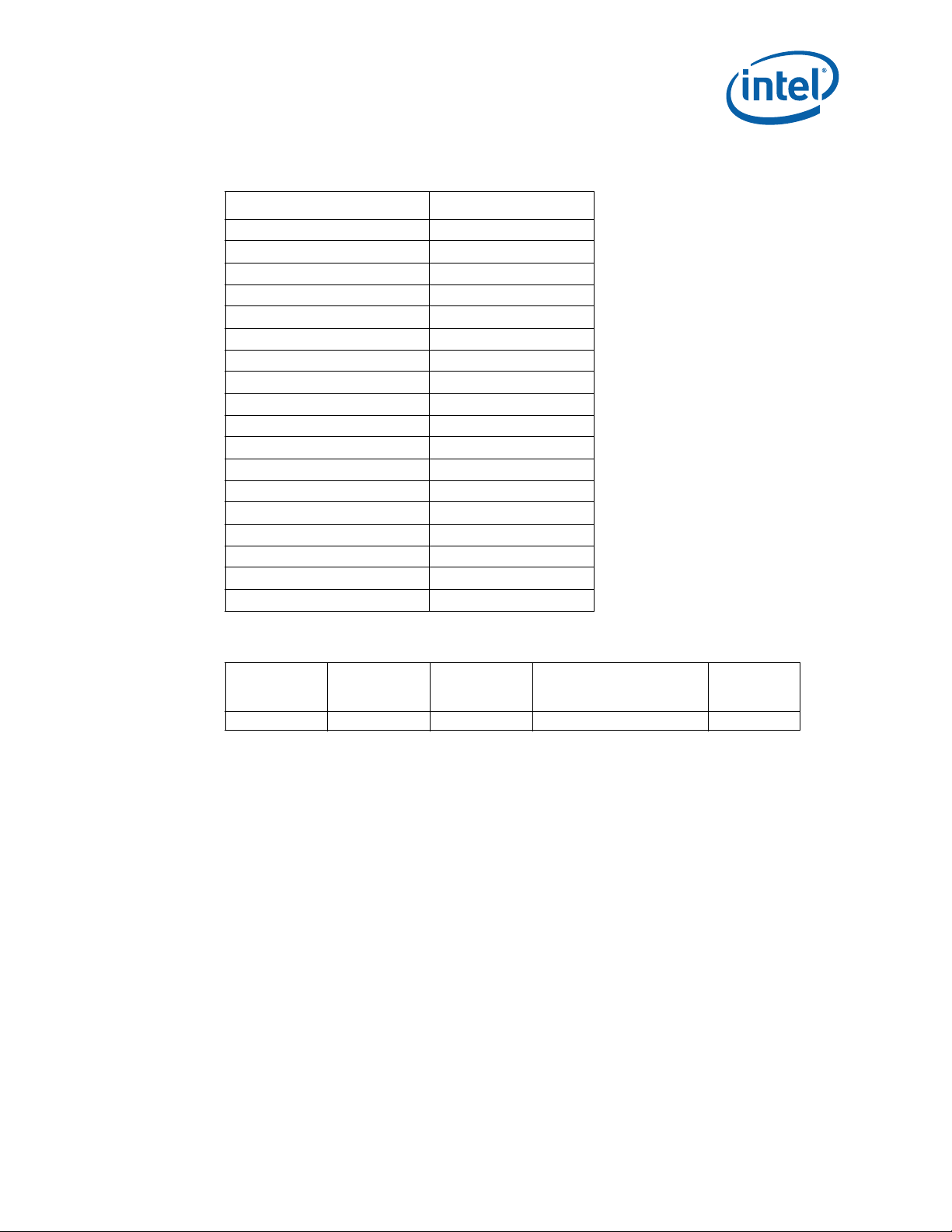

Table 6-3. Intel® Xeon® Processor EC3539 and EC5539 Thermal Specifications

Core

Frequency

Thermal Design

Power

(W)

Minimum

CASE

T

(°C)

Launch to FMB 65 5 See Figure 6-2; Table 6-4 1, 2, 3, 4, 5

Maximum

CASE

T

(°C)

Notes

Notes:

1. These values are specified at V

the processor is not to be subjected to an y static V

specified ICC. See the loadline specifications in the Datasheet.

2. Thermal Design Power (TDP) should be used for processor thermal solution design targets. TDP is not the

maximum power that the processor can dissipate. TDP is measured at maximum T

3. These specifications are based on initial silicon characterization. These specifications may be further

updated as more characterization data becomes available.

4. Power specifications are defined at all VIDs found in the Datasheet. The Intel

C3500 series Intel

frequency.

5. FMB (Flexible Motherboard) guidelines provide a design target for meeting all planned processor frequency

requirements.

August 2010 Thermal/Mechanical Design Guide

Order Number: 323107-002US 38

®

Xeon® processor C5500/C3500 series may be shipped under multiple VIDs for each

for all processor frequencies. Systems must be designed to ensure

CC_MAX

and ICC combination wherein VCC exceeds V

CC

.

CASE

®

Xeon® processor C5500/

Intel® Xeon® Processor C5500/C3500 Series and LGA1366 Socket

CC_MAX

at

Page 39