Page 1

Intel® SRMK2 Internet Server

Technical Product Specification

The Intel® SRMK2 Internet Server may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in the

Intel® SRMK2 Internet Server Specification Update.

February 26, 2001

iPN A39185-001

Page 2

Revision History

Revision Revision History Date

1.0 Original draft October 18, 2000

1.1 First update January 25, 2001

1.2 Second update February 26, 2001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale

and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

The Intel® SRMK2 Internet Server may contain design defects or errors known as errata that may cause the product to deviate

from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777,

Germany 44-0-1793-421-333, other Countries 708-296-9333.

†

Third-party brands and names are the property of their respective owners.

Copyright 2000, Intel Corporation. All rights reserved.

Page 3

Preface

This Technical Product Specification (TPS) identifies components and software integrated with

the Intel® SRMK2 Internet Server. These components include the serverboard, riser card, front

panel board, hot-swap backplane, system BIOS, Advanced Server Management (ASM) software,

chassis, and power supply. Certifications, reliability, and serviceability of the system are also

discussed.

Intended Audience

This TPS provides detailed technical information about the SRMK2 Internet Server and its internal

components. This information is intended for xSPs, OEM engineers, vendors, system integrators,

and other engineers and technicians who need this level of information. It is not intended for

general audiences.

Typographical Conventions

This section describes the conventions used in this specification. Not all of these symbols and

abbreviations appear in all specifications of this type.

!! NOTE

Notes call attention to important information.

CAUTION

Cautions are included to help you avoid damaging hardware and losing data.

WARNING

Warnings indicate conditions that, if not observed, can cause personal injury.

Intel® SRMK2 Internet Server Technical Product Specification iii

Page 4

<Blank Page: Prevention words>

Intel® SRMK2 Internet Server Technical Product Specification iv

Page 5

Conventions and Terminology

Contents

1 INTRODUCTION...............................................................................................................................................11

2 CHASSIS DESCRIPTION...............................................................................................................................13

2.1 EXTERNAL CHASSIS FEATURES..............................................................................................................13

2.1.1 Chassis Dimensions................................................................................................................................13

2.1.2 Colors of Chassis....................................................................................................................................13

2.1.3 Front View of Chassis.............................................................................................................................14

2.1.4 Rear View of Chassis ..............................................................................................................................15

2.2 INTERNAL CHASSIS FEATURES...............................................................................................................15

2.2.1 AC Power Supply....................................................................................................................................15

2.2.2 DC Power Supply....................................................................................................................................19

2.2.3 BTU information.....................................................................................................................................19

2.2.4 System Cooling........................................................................................................................................20

2.2.5 System Peripheral Bays...........................................................................................................................21

2.2.6 System Interconnection............................................................................................................................21

2.3 SYSTEM CONFIGURATION......................................................................................................................23

3 SRMK2 SERVERBOARD DE SCRIPTION..................................................................................................24

3.1 OVERVIEW.................................................................................................................................................24

3.2 SERVERBOARD LAYOUT..........................................................................................................................25

3.3 PROCESSORS...............................................................................................................................................27

3.4 CHIPSET .....................................................................................................................................................28

3.4.1 ServerWorks CNB30LE North Bridge Chip...........................................................................................28

3.4.2 ServerWorks OSB4 South Bridge Chip..................................................................................................29

3.5 MEMORY....................................................................................................................................................30

3.6 SCSI HOST BUS INTERFACE....................................................................................................................31

3.6.1 SCSI Hard Drive LED Connector (Optional)........................................................................................31

3.7 IDE INTERFACE.........................................................................................................................................31

3.8 USB.............................................................................................................................................................31

3.9 I/O CONTROLLER ..................................................................................................................................... 32

3.9.1 Serial Port...............................................................................................................................................32

3.9.2 Diskette Drive Controller .......................................................................................................................32

3.9.3 Keyboard and Mouse Interface...............................................................................................................32

3.9.4 Real-Time Clock, CMOS SRAM, and Battery.........................................................................................32

3.10 INTEL

3.11 V IDEO INTERFACE.................................................................................................................................... 33

3.12 HARDWARE MONITOR ............................................................................................................................ 34

3.13 WAKE ON RING AND RESUME ON RING ............................................................................................... 35

3.13.1 Wake on Ring.....................................................................................................................................35

3.13.2 Resume on Ring..................................................................................................................................35

3.14 SPEAKER....................................................................................................................................................35

3.15 FAN SUPPORT ...........................................................................................................................................36

3.16 BASEBOARD PROGRAMMING..................................................................................................................36

3.16.1 PCI Configuration Space Map...........................................................................................................36

3.16.2 Interrupts ...........................................................................................................................................36

3.16.3 SMI and NMI Routing........................................................................................................................37

3.16.4 System Management Bus (SMB) ........................................................................................................37

3.17 BASEBOARD CONNECTORS AND JUMPERS...........................................................................................38

®

82559 10/100 E THERNET CONTROLLERS................................................................................33

Intel® SRMK2 Internet Server Technical Product Specification v

Page 6

Conventions and Terminology

3.17.1 Back Panel I/O Connectors................................................................................................................39

3.17.2 Midboard Connectors........................................................................................................................41

3.17.3 Front Panel Connector.......................................................................................................................48

3.18 JUMPER BLOCKS.......................................................................................................................................50

3.19 THERMAL CONSIDERATIONS..................................................................................................................52

3.20 DC V OLTAGE REGULATION ...................................................................................................................53

4 PCI RISER BOARD..........................................................................................................................................54

4.1 INTRODUCTION........................................................................................................................................54

4.2 RISER BOARD PCI BUS CONNECTORS....................................................................................................54

4.3 PCI ADD-IN CARDS...................................................................................................................................54

4.4 RISER BOARD PCI INTERRUPT ROUTING MAP ...................................................................................55

5 FRONT PANEL BOARD..................................................................................................................................57

5.1 INTRODUCTION........................................................................................................................................57

5.2 FRONT PANEL SWITCHES.......................................................................................................................57

5.3 FRONT PANEL LED INDICATORS...........................................................................................................58

5.4 FRONT PANEL I/O CONNECTOR............................................................................................................58

6 SCSI BACKPLANE ...........................................................................................................................................59

6.1 INTRODUCTION........................................................................................................................................59

7 BIOS DESCRIPTION.......................................................................................................................................61

7.1 OVERVIEW.................................................................................................................................................61

7.2 SYSTEM BIOS............................................................................................................................................61

7.2.1 Configuration Utility...............................................................................................................................62

7.2.2 CMOS Configuration RAM Summary .....................................................................................................62

7.2.3 Flash Memory Update Utility..................................................................................................................62

7.2.4 Fail-Safe BIOS Extensions......................................................................................................................62

7.2.5 System Flash ROM Layout......................................................................................................................62

7.3 SYSTEM BIOS............................................................................................................................................63

7.3.1 Auto-Configuration Features ..................................................................................................................63

7.3.2 Performance Features.............................................................................................................................67

7.3.3 Reliability Features..................................................................................................................................69

7.3.4 System Services.......................................................................................................................................71

7.3.5 Boot Options...........................................................................................................................................74

7.3.6 OEM Customization................................................................................................................................75

7.3.7 SMBIOS Support .....................................................................................................................................78

7.3.8 Soft Power Switch....................................................................................................................................79

7.3.9 POST Memory Manager Support...........................................................................................................80

7.3.10 ACPI Support.....................................................................................................................................80

7.4 FAIL-SAFE BIOS E XTENSIONS................................................................................................................81

7.4.1 LAN Alerts...............................................................................................................................................81

7.4.2 WatchDog Timer (WDT)........................................................................................................................81

7.4.3 Paging Support.......................................................................................................................................82

8 FLASH MEMORY UPDATE UTILITY...........................................................................................................83

8.1 LOADING THE SYSTEM BIOS.................................................................................................................83

9 ERROR HANDLING, MESSAGES & BEEP CODES..................................................................................84

9.1 ERROR SOURCES AND TYPES..................................................................................................................84

9.2 ERROR HANDLERS....................................................................................................................................84

Intel® SRMK2 Internet Server Technical Product Specification vi

Page 7

Conventions and Terminology

9.3 ISA BUS ERROR.........................................................................................................................................85

9.3.2 Processor Bus Error...............................................................................................................................86

9.3.3 Memory Bus Error..................................................................................................................................87

9.3.4 System Limit Error..................................................................................................................................87

9.3.5 Processor Failure...................................................................................................................................87

9.4 ERROR MESSAGES AND ERROR CODES..................................................................................................87

10 BIOS SETUP PROGRAM...........................................................................................................................90

10.1 MAINTENANCE MENU ............................................................................................................................ 91

10.2 MAIN MENU..............................................................................................................................................91

10.3 ADVANCED MENU...................................................................................................................................92

10.4 SECURITY MENU......................................................................................................................................93

10.5 BOOT MENU..............................................................................................................................................93

10.6 SYSTEM MANAGEMENT MENU.............................................................................................................94

10.7 EXIT MENU ...............................................................................................................................................96

11 CERTIFICATION..........................................................................................................................................97

11.1 SAFETY STANDARDS / CERTIFICATIONS.............................................................................................97

11.2 ELECTROMAGNETIC COMPATIBILITY (EMC) REGULATIONS ......................................................... 97

11.3 ELECTROMAGNETIC COMPATIBILITY NOTICES (SRMK2S)............................................................98

11.3.1 Japan..................................................................................................................................................98

11.3.2 Canada...............................................................................................................................................98

11.3.3 FCC/emissions disclaimer – Class A (USA)......................................................................................98

11.3.4 Taiwan (BSMI)...................................................................................................................................99

11.4 ELECTROMAGNETIC COMPATIBILITY NOTICES (SRMK2D)...........................................................99

11.4.1 Japan..................................................................................................................................................99

11.4.2 Canada...............................................................................................................................................99

11.4.3 FCC/emissions disclaimer – class B (USA).......................................................................................99

11.5 FCC DECLARATION OF CONFORMITY................................................................................................100

11.5.1 SRMK2D..........................................................................................................................................100

11.5.2 Taiwan (BSMI).................................................................................................................................100

11.6 MANDATORY / STANDARD: CERTIFICATIONS, REGISTRATION, DECLARATIONS ..................... 101

11.7 ENVIRONMENTAL LIMITS.....................................................................................................................101

12 RELIABILITY AND SERVICEABILITY ................................................................................................102

12.1 RELIABILITY...........................................................................................................................................102

12.2 SERVICEABILITY .................................................................................................................................... 102

13 COMPATIBILITY TESTING...................................................................................................................103

14 SPECIFICATIONS AND CUSTOMER SUPPORT.............................................................................104

14.1 ONLINE SUPPORT ..................................................................................................................................104

14.2 SPECIFICATIONS.....................................................................................................................................104

Intel® SRMK2 Internet Server Technical Product Specification vii

Page 8

Conventions and Terminology

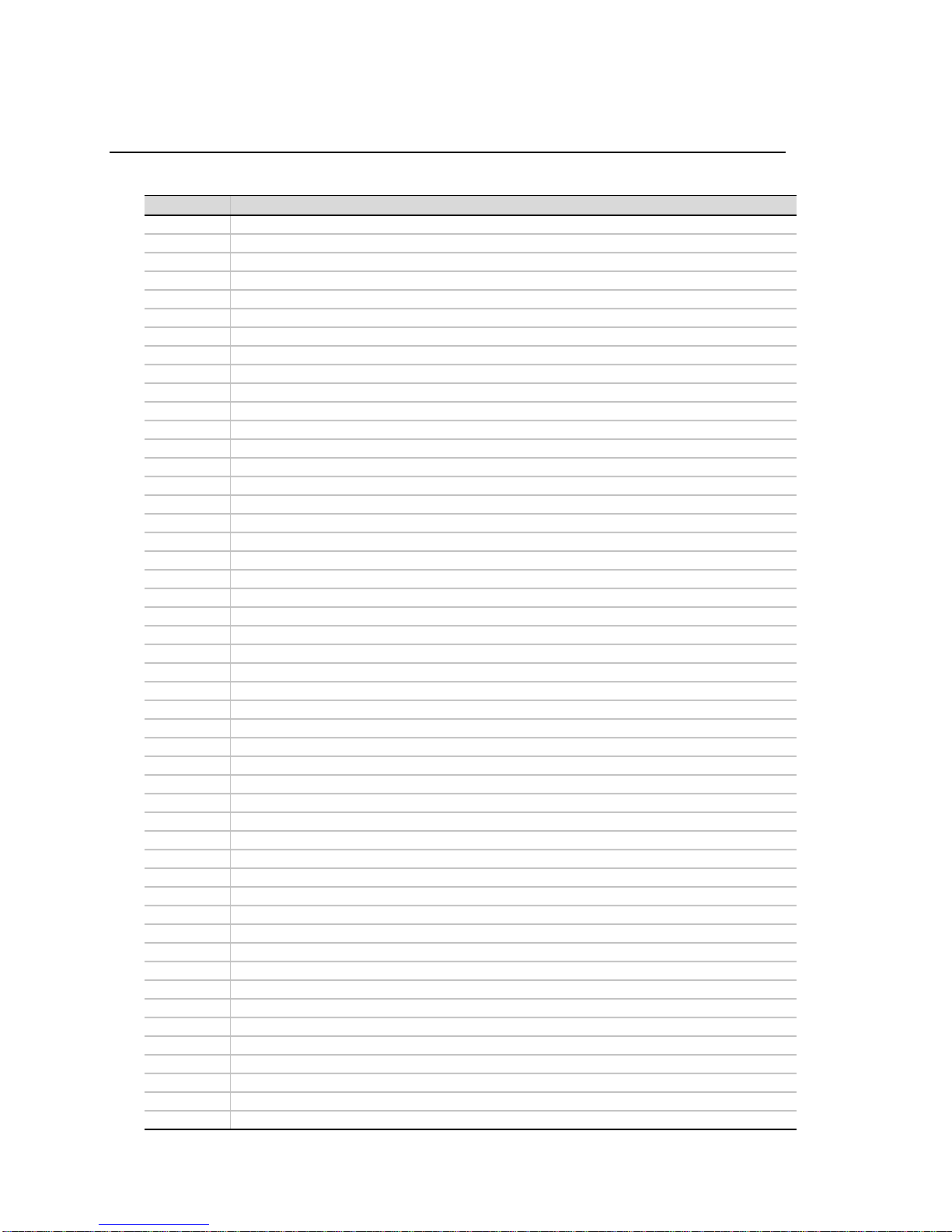

Conventions and Terminology

This document uses the following terms and abbreviations:

Term Definition

Ω

µA 0.000001 amperes

µF microfarad

A amperes (amps)

AC Alternating Current

ACPI Advanced Configuration Power Interface

AGP Accelerated Graphics Port

ASCII American Standard Code for Information Interchange

ASIC Application Specific Integrated Circuit

BIOS Basic Input Output System

Byte 8-bit quantity

C Centigrade

CD Compact Disk

CD-ROM Compact Disk Read Only Memory

CE Community European

cfm Cubic feet per minute

CMOS Complementary Metal-Oxide Semiconductor

CPU Central Processing Unit

DC Direct Current

DCD Data Carrier Detect

DEMKO Danishe Elektriske Materiellkontroll (Danish Board of Testing and Approval of Electrical Equipment)

DIMM Dual Inline Memory Module

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

ECC Error Correction Code

EDO Extended Data Out

EEPROM Electrically Erasable Programmable Read Only Memory

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

EN European Standard (Norme Européenne or Europäische Norm)

ESD Electrostatic Discharge

EU European Union

F Fahrenheit

FC-PGA Flip Chip Pin Grid Array

FCC Federal Communications Commission (USA)

FD Floppy Disk

FET Field Effect Transistor

FP Front Panel

FPC Front Panel Controller

FRU Field Replaceable Unit

GB gigabyte (1024 MB)

Hz Hertz (cycles per second)

I/O Input/Output

I2C Inter-Integrated Circuit

IDE Integrated Drive Electronics

ISA Industry Standard Architecture

KB kilobyte (1024 bytes)

kg Kilograms

kV Kilovolts

Ohms

Intel® SRMK2 Internet Server Technical Product Specification viii

Page 9

Conventions and Terminology

LED Light Emitting Diode

LVD Low Voltage Differential

mA milliamps

MB megabyte (1024 KB)

MBE Multi-bit Error

MIF Management Information database

mm millimeters

ms milliseconds

MTBF Mean Time Between Failure

MTTR Mean Time To Repair

NEMKO Norges Elektriske Materiellkontroll (Norwegian Board of Testing and Approval of Electrical

Equipment)

NIC Network Interface Card

NMI Non-Maskable Interrupt

NVRAM Non-Volatile Random Access Memory

OCP Over-Current Protection

OEM Original Equipment Manufacturer

OTP Over-Temperature Protection

OVP Over-Voltage Protection

PAC PCI/AGP Controller

PCI Peripheral Component Interconnect

Pf picofarad (10

PFC Power Factor Correction

OSB4 PCI-ISA IDE Xcelerator controller

PIO Programmed Input/Output

PLD Programmable Logic Device

POST Power-On Self Test

PPGA Plastic Pin Grid Array

PXE Preboot Execution Environment

RAM Random Access Memory

RPM Revolutions Per Minute

RxD Receive Data

SBE Single-bit Error

SCL Serial Clock

SCSI Small Computer Systems Interface

SDA Serial Data

SE Single Ended

SEEPROM Serial Electrically Erasable Programmable Read Only Memory

SEL System Event Log

SEMKO Sverge Elektriske Materiellkontroll (Swedish Board of Testing and Approval of Electrical

Equipment)

SIO Super I/O

SMB System Management Bus

SMC Standard Microsystems Corporation

SMBIOS System Management BIOS

SMI System Management Interrupt

SMM System Management Module

TTL Transistor-Transistor Logic

TxD Transmit Data

UART Universal Asynchronous Receiving/Transmitting

UL Underwriter’s Laboratories

USB Universal Serial Bus

V Volt

VA Volt amperes

Vac Volts alternating current

-12

)

Intel® SRMK2 Internet Server Technical Product Specification ix

Page 10

Conventions and Terminology

VCCI Voluntary Control Council for Interference (by data processing and electronic office equipment)

Vdc Volts direct current

Vin Volts in

VRM Voltage Regulator Module

Vrms Volts root-mean-square

W Watts

Wdc Watts direct current

WOL Wake on LAN

WOR Wake on Ring

ZIF Zero Insertion Force

Intel® SRMK2 Internet Server Technical Product Specification x

Page 11

1 Introduction

This document provides a detailed description of the chassis and system level features of the

Intel® SRMK2 Internet Server. This system is a high-density rackmount server consisting of a

1U chassis and the SRMK2 serverboard. The server will come in two models: A SCSI based

system (SRMK2S) and a SCSI based system with a –48V DC power supply (SRMK2D). Since

both of these systems are based off of the SRMK2S product, this guide has been written to

represent the SRMK2S. Notes and additions have been added to identify discrepancies between

the SRMK2S and the SRMK2D.

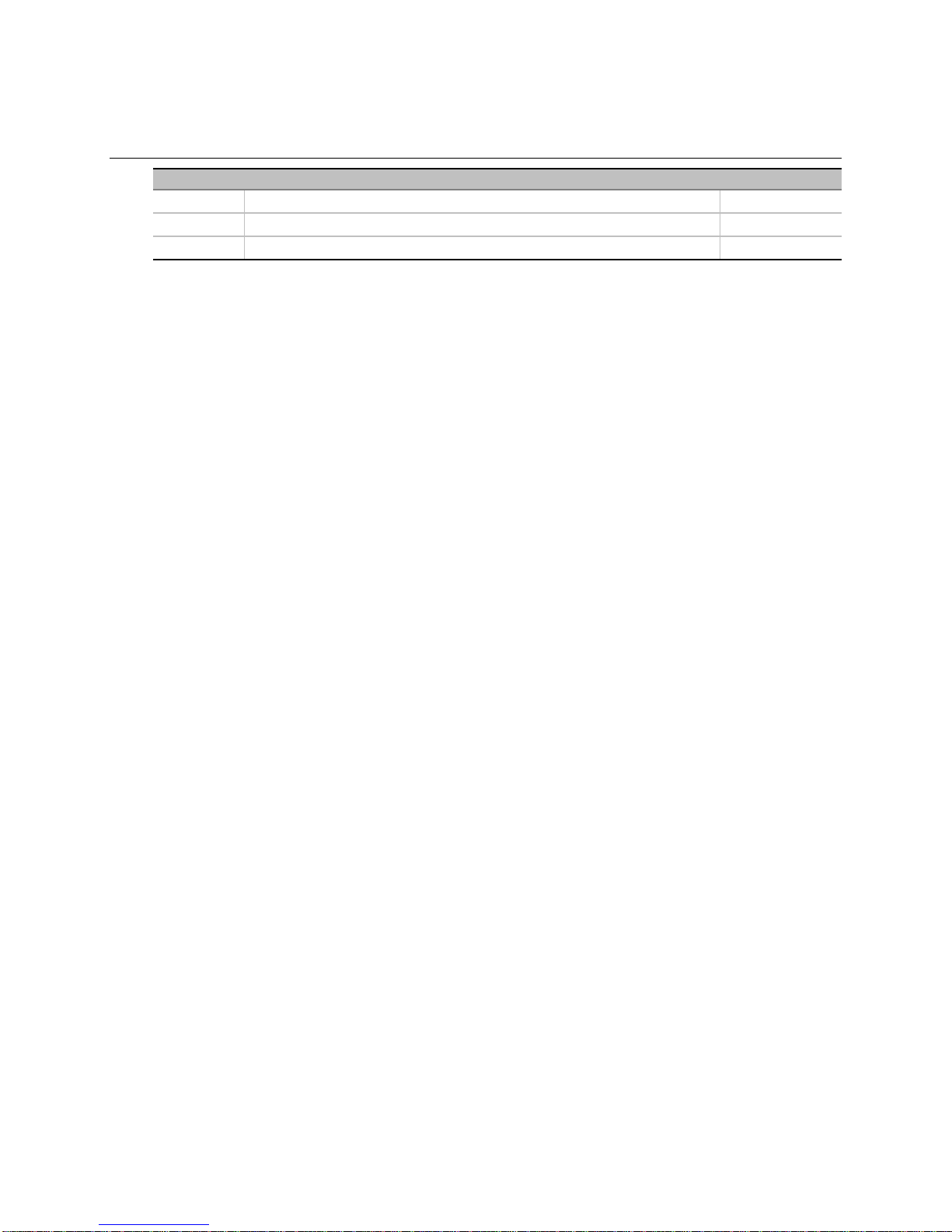

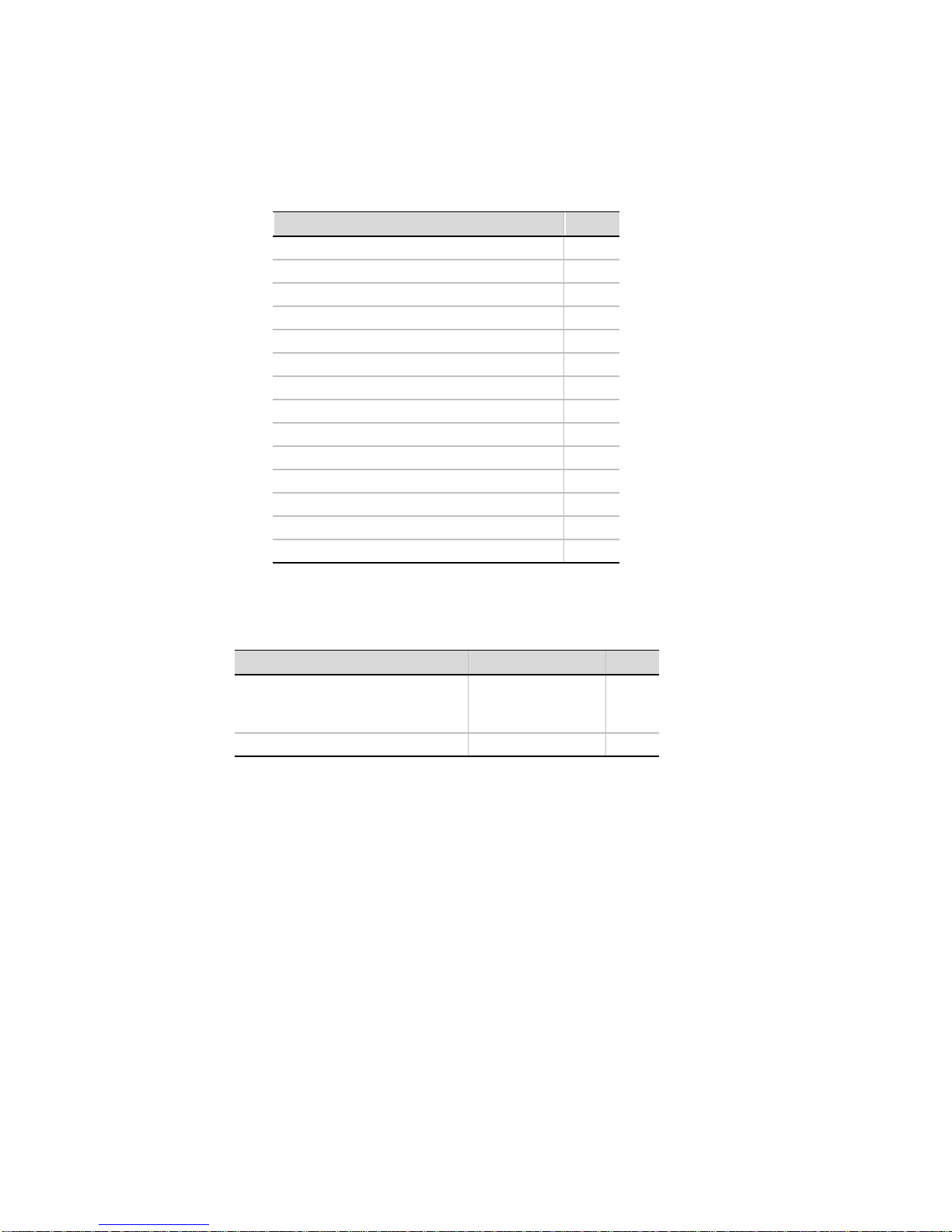

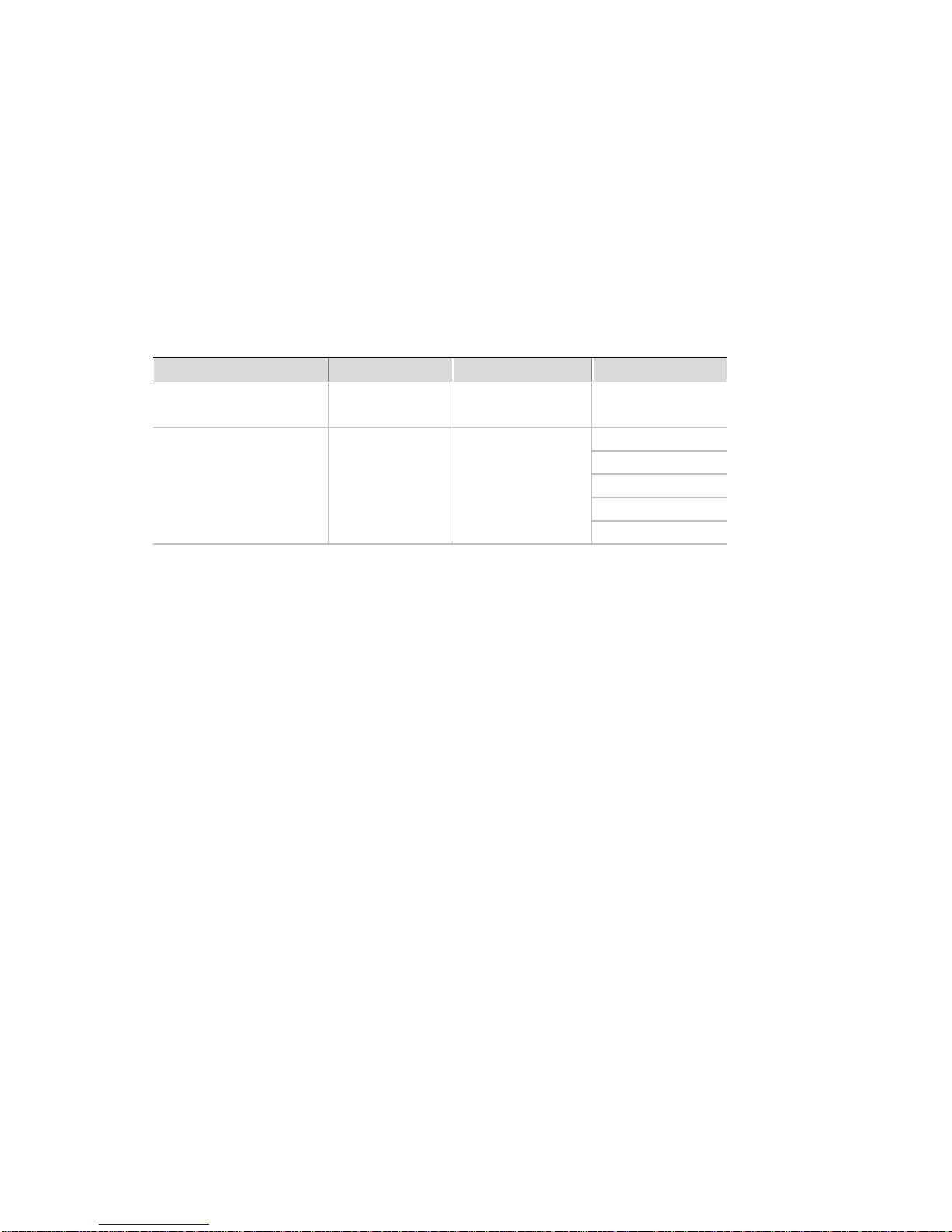

Table 1 provides a list and brief description of the SRMK2 Internet Server’s key features.

Table 1: Intel® SRMK2S Internet Server key features

Feature Description

1U chassis 1.70” (height) x 16.75” (width behind bezel) x 24” (depth)

Weight Approximately 30lbs in-box shipping weight

Power supply Single 200W AC power supply (200W DC supply comes with the SRMK2D)

Cooling Nine system fans (Eight 40mm and one 17mm)

Rackmounting Two midmount and Front mounting brackets or sliding rails (optional)

Hard disk capacity Support for two 1” U160 Hot Swappable SCSI hard drives for internal

configuration along with an external SCSI channel for external drives

Peripheral bays Single standard slim diskette drive included with system. Optional slim-line

CD-ROM drive available (works in conjunction with the standard diskette).

Peripheral Interfaces Two Ultra 160 SCSI channels, one internal and one external (The internal

channel has two SCA2 connector ports out the front of the machine)

One IDE interface with UDMA support

One rear serial port

Two 10/100 82559 LAN Connectors

One slim-line diskette interface

LED Panel Interface

Two USB ports

Video Interface

Two PS/2 ports

Microprocessor Dual Pentium® III processors in PGA370 sockets

Memory capacity Up to 4 GB of registered PC-100 or PC-133 ECC SDRAM DIMMs

LAN support Integrated dual Intel® 82559 Pro/100+ Ethernet controllers featuring PXE 2.0 option

ROM for network installation and booting of operating systems

Add-in card support Passive PCI riser (64-bit/66MHz) supports a low-profile and a full-length (13”) PCI

card

System management Two Heceta 3 hardware monitoring ASIC’s which work in conjunction with Web-

based management software (ASM).

BIOS Intel/AMI BIOS with extensions to enhance server management capabilities

Intel® SRMK2 Internet Server Technical Product Specification 11

Page 12

<This page was intentionally left blank>

Intel® SRMK2 Internet Server Technical Product Specification 12

Page 13

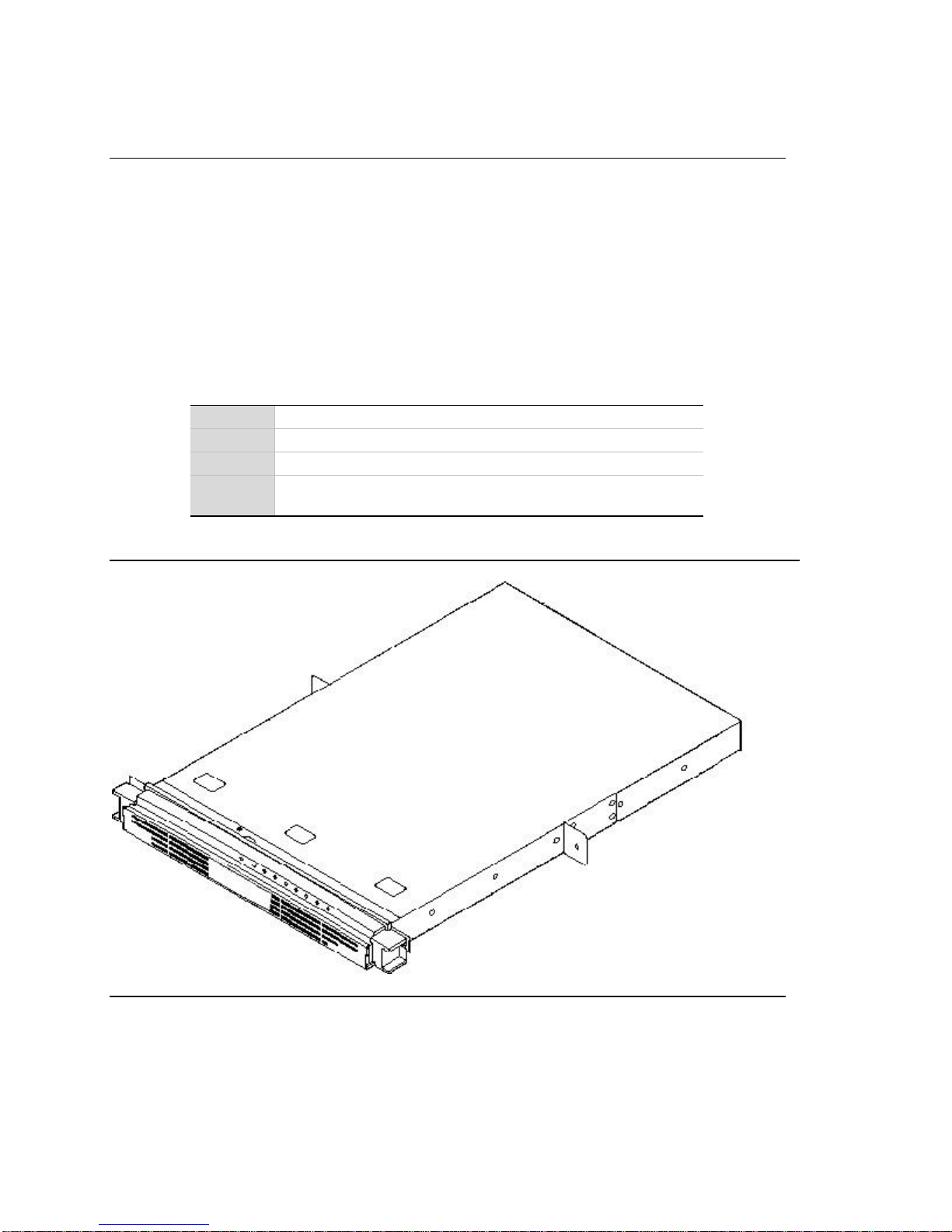

2 Chassis Description

This section describes the features of the Intel® SRMK2 Internet Server chassis.

2.1 External Chassis Features

2.1.1 Chassis Dimensions

The chassis is 1.70 inches high by 16.75 inches wide behind the bezel by 24.00 inches deep

(measured from the front of the bezel to the deepest portion of the rear bulkhead). The chassis is

designed to be mounted in a relay-style rack using the two right-angle midmount or front mount

brackets provided with the base system that attach to the chassis and two brackets that attach to

the rack . It can also be installed in a standard 19” rack using a sliding rails kit (Optional).

Table 2: Chassis dimensions

Height

Width

Depth

Shipping

Weight

1.70” (1U)

16.75” between the slide mounting surfaces

24” including bezel, 22.41” from front mounting flange to the rear panel

30lbs. maximum configuration (Fully loaded weight including box and all

accessories)

Figure 1: Isometric View of Chassis

2.1.2 Colors of Chassis

The primary exterior of the chassis is unpainted. The bezel is a molded black (GE701) plastic.

Intel® SRMK2 Internet Server Technical Product Specification 13

Page 14

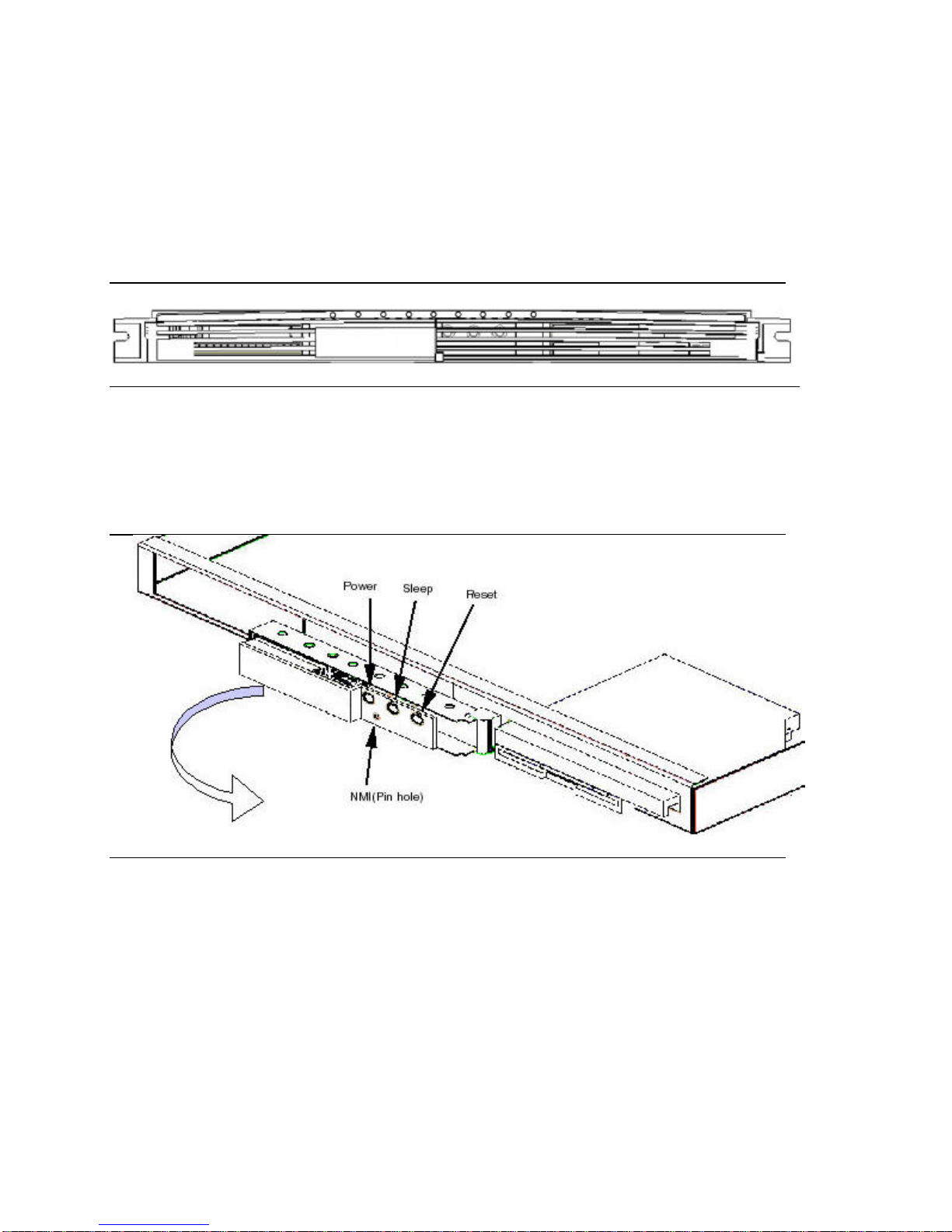

2.1.3 Front View of Chassis

The front bezel is a multiple-part plastic molding that contains the buttons, the LED indicator light

pipes, and a flip -down door that spans half the width of the bezel and folds down (right striated

portion in Figure 2 below). After pulling the flip door down the Power, Sleep, and Reset buttons

as well as the NMI pin hole are revealed. This also reveals the floppy and CD-ROM bays. See

Figure 3 for button placement. See Section 5 Front Panel Board for a complete description of the

buttons and LEDs.

Figure 2: Front view of chassis with bezel on

Additionally, the front bezel can be removed to reveal the front of the chassis. To access the hot

swappable SCSI hard disk drives, pivot the front panel out and to the right. Figure 3 shows the

chassis with the front bezel removed and the front panel in the closed position.

Figure 3: Front view of chassis without bezel

Upon pivoting the front panel out and to the right, the SCSI hard disk drive bays are revealed as

shown in Figure 4 below.

Intel® SRMK2 Internet Server Technical Product Specification 14

Page 15

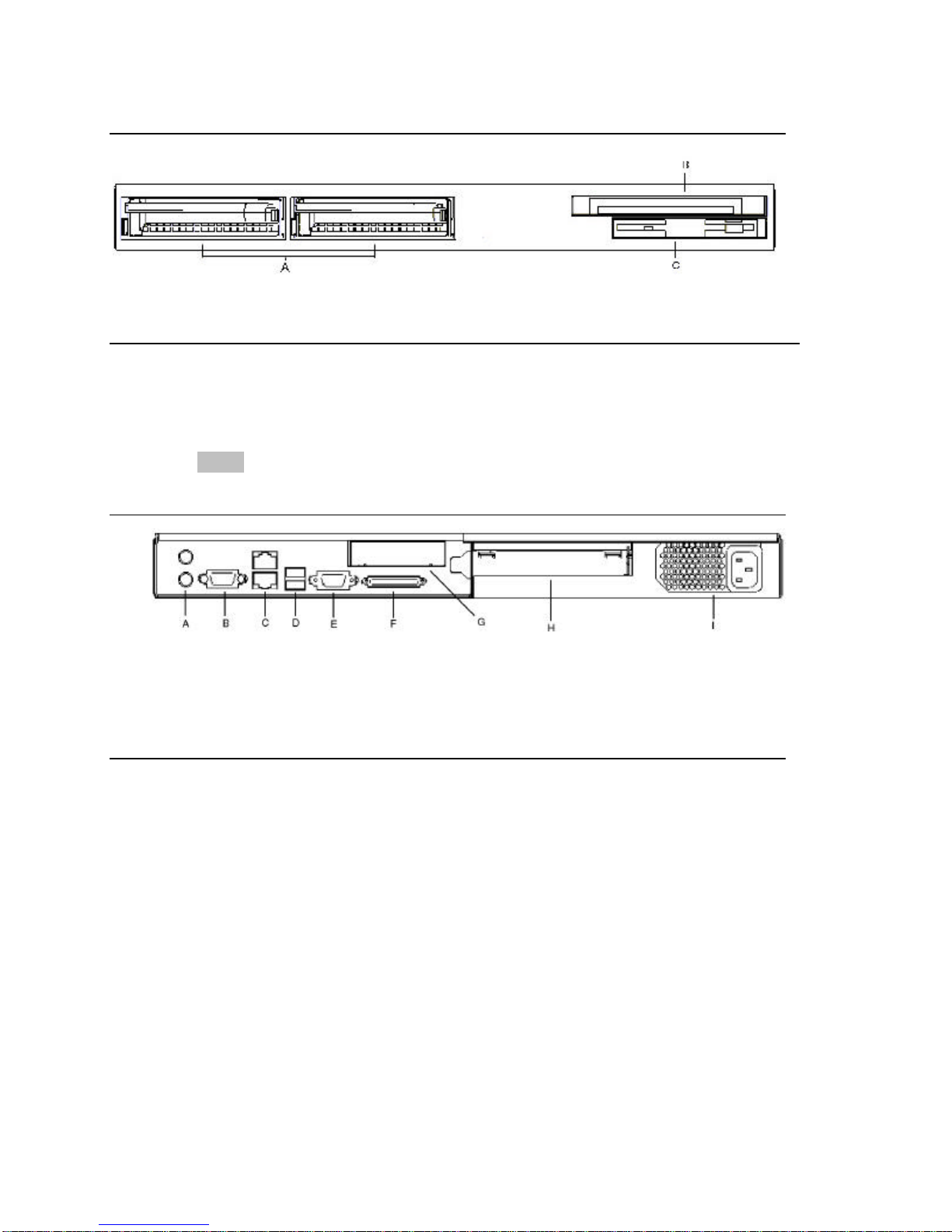

A Hot Swappable SCSI Drives

C Slimline Floppy

B

Slimline CDROM (Optional)

Figure 4: Front view of chassis without bezel (Does not show Front Panel swung out)

2.1.4 Rear View of Chassis

The input/output connectors are accessible at the back panel of the chassis as shown in Figure 5.

See Section 3.17.1 Back Panel I/O Connectors for detailed descriptions of the rear panel I/O

connectors.

A PS/2 Kbd / Mouse

B Video E Serial Port A H Full Length PCI slot

C Dual RJ-45 F U160 SCSI I Power Supply *

* The power supply in the SRMK2D has a different connector

D

USB

Figure 5: Rear view of chassis

G

Low Profile PCI slot

2.2 Internal Chassis Features

2.2.1 AC Power Supply

The SRMK2 Internet Server can use two different power supplies, one being an AC 200W

version which ships with the SRMK2S model and a –48V DC 200W version that ships with the

SRMK2D model. For information on the DC model, see the Section 2.2.2 entitled DC Power

Supply . The AC power supply uses a standard IEC 320 power cord and is a single auto-ranging

power factor corrected power supply. The AC power supply rating is described in Table 3.

Intel® SRMK2 Internet Server Technical Product Specification 15

Page 16

Table 3: 200W power supply output summary

DC Power

Total power from supply

AC line voltage

AC line frequency

+3.3VDC at 13.0A Max.

+5 VDC at 22A Max.

+12 VDC at 3.5A Max.

-12 VDC at 0.25A

5V Standby 1A

202.9W

90-135,180-265VAC PFC: auto sense

47 / 63 Hz

2.2.1.1 Power Supply Mechanical Outline

Both AC and DC power supplies are 3.30”wide by 1.60” high by 9.60”in length. The output cable

bundle is separated into two cables; one cable with two connectors for the serverboard, and the

other with a connector for the backplane which in turn powers the HDD’s. The backplane also

has a CDROM power connector.

2.2.1.2 Power Supply Fan Requirements

The power supply relies on cooling provided by two 40mm fans mounted in the chassis in front of

the power supply. These fans are monitored by hardware on the motherboard and the Advanced

Server Management software that comes on the Resource CD in the accessory kit.

2.2.1.3 AC Power Line

The system is specified to operate over two input voltage ranges that are automatically selected

and rated from 100-120VAC and 200-240VAC, at 50 or 60Hz. The power supply incorporates

Power Factor Correction (PFC) as a standard feature. The system is tested to meet these line

voltages, and has been tested (but not specified) at +10% and -10% of the voltage ranges, and ±

3Hz on the line input frequency. The system is specified to operate without error with line source

interruptions not to exceed 20 milliseconds at nominal line conditions and full power supply output

load. The system is not damaged by AC surge ring wave to 2.5kV/500A. This ring wave is a

100kHz damped oscillatory wave with a specified rise-time for the linear portion of the initial half cycle of 0.5µsec. Additionally , the system will not be damaged by a unidirectional surge

waveform of 2.0kV /3000A, with a 1.2µsec rise time and 50µsec duration. Further details on

these waveforms can be obtained in ANSI/IEEE STD C62.45-1987.

Intel® SRMK2 Internet Server Technical Product Specification 16

Page 17

1

6

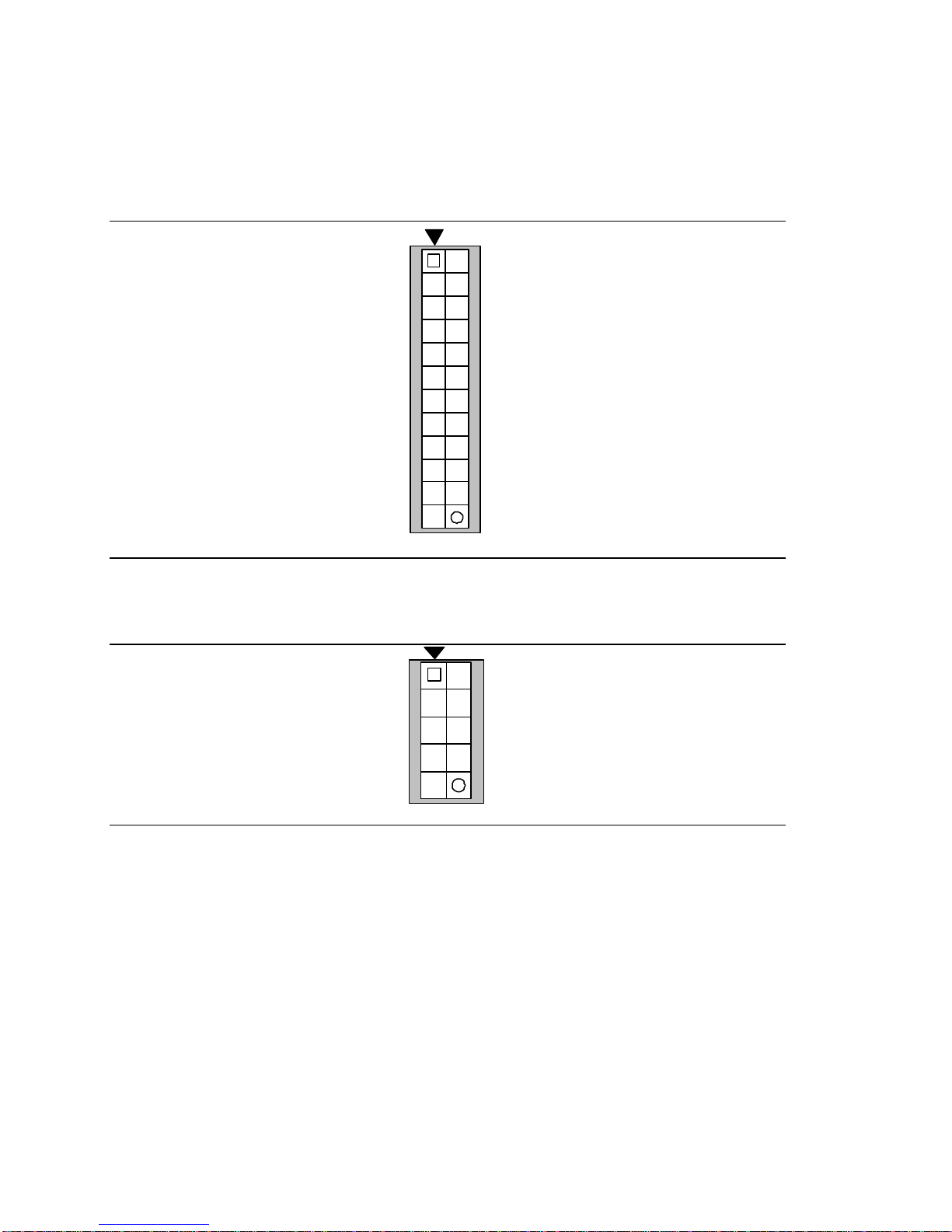

2.2.1.4 DC Connector Requirements

Figure 6 and Figure 7 show the connector pinouts for the serverboard power connectors. These

mate with the power supply connectors at connector J27 and J39.

1 13

Ground

Ground

Ground

Ground

+3.3V

+3.3V

+3.3V

+3.3V

Ground

Ground

+5VSB

Ground

VRM Input Voltage

VRM Input Voltage

VRM Input Voltage

VRM Input Voltage

Ground

Ground

Ground

Ground

+5V

+5V

Ground

+12V

12 24

Figure 6: DC connector pinout (J27)

HECALERT#

Ground

Ground Sense

PWR_ON#

-12V

5 10

Figure 7: DC connector pinout (J39)

SMB_Data

SMB_CLK

+3.3V Sense

PWRGOOD

+5V Sense

Intel® SRMK2 Internet Server Technical Product Specification 17

Page 18

2.2.1.5 Power Supply Wiring Requirements

The wiring length and the desired wire color -coding are specified in Figure 8.

Wire exit hole in

power

supply.

Edge of supply to center of connector on

Only one wire tie

at exit of supply

this bundle.

Bundle A

PCB.

3.5" (87.5mm)

pin 1

Main

Board

pin 13

P2

Wire lengths should vary to

0.25"

Max

Bundle B

Bundle C

Mini wire ties at

one inch spacing

length of bundle.

3.5" ±0.25"

(87.5mm ±6mm)

7.75" ±0.25"

(196mm ±6mm)

ensure no loops or slack wire.

Main board 2

Conn.

Figure 8: DC output wire harness

Table 4: Baseboard Power Connector (P2)

Signal

Pin

Name

1 Ground Black 13 VRM Input Red

2 Ground Black 14 VRM Input Red

3 Ground Black 15 VRM Input Red

4 Ground Black 16 VRM Input Red

5 +3.3V Orange 17 Ground Black

6 +3.3V Orange 18 Ground Black

7 +3.3V Orange 19 Ground Black

8 +3.3V Orange 20 Ground Black

9 Ground Black 21 +5V Red

10 Ground Black 22 +5V Red

11 +5VSB Purple 23 Ground Black

12 Ground Black 24 +12V Yellow

20 AWG

Wire

Pin

Signal

Name

20 AWG

Wire

P3

P4

SCSI Backplane

Connector

Intel® SRMK2 Internet Server Technical Product Specification 18

Page 19

Table 5: Baseboard Power Connector (P3)

Pin Signal Name 20 AWG Wire Pin Signal Name 20 AWG Wire

1 HECALERT#* N/A 6 SMB_Data* N/A

2 Ground Black 7 SMB_CLK* N/A

3 Ground Sense Black 8 +3.3V Sense Brown

4 PWR_ON# Green 9 PWRGOOD Grey

5 -12V Blue 10 +5V Sense Red

* These pins are not stuffed or used on the SRMK2 power supply

Table 6: SCSI Backplane Power Connector (P4)

Pin Signal Name 20 AWG Wire

1 +12V Yellow

2 +12V Yellow

3 Ground Black

4 Ground Black

5 +3.3V Orange

6 +5V Red

2.2.2 DC Power Supply

The SRMK2D model ships with a –48V DC power supply. The output of the DC power supply is

electrically identical to that of the AC power supply (see Table 3 for reference), it shares the

same physical dimensions as the AC power supply, the same mounting, and the same power

cabling to the motherboard. It does vary, however, in it’s electrical specification for line input and

has a different interface on the rear of the chassis than the AC module. The interface on the

back of the DC power supply has four phillips screws that are pr otected by a cover for shipping.

Removing the cover reveals the four screws. A label should show the screw markings to be: A+

A- B+ B- . The A+ and A- connectors can be attached to a primary power source for the

server, while the B+ and B- leads can be connected to a secondary power source for redundant

power sourcing in case of primary source failure. Table 7 shows the input parameters for the –

48V DC power supply.

Table 7: -48V DC Power Supply Input Parameters

Parameter Min Nom Max Unit

Vin (-48VDC) -36.0 -48.0 -72.0 VDC

2.2.3 BTU information

BTU’s (British Thermal Units) are a standard for measuring the thermal output of a device. For

reference, one BTU equals the heat that will raise the temperature of one pound of water by one

degree Fahrenheit. In physical terms, 1 BTU = 1054 joules. Listed below is the maximum BTU

output of the SRMK2 system and a loaded system BTU output. System configuration of the

loaded system is describe d in Table 9.

The BTU maximum rating was derived by taking the maximum wattage output of the power

supply (202.9W), dividing it by the lowest efficiency of the power supply (70% or 0.70) and

multiplying by the BTU conversion number of 3.41. Remember that these numbers are rated at

Intel® SRMK2 Internet Server Technical Product Specification 19

Page 20

the worst case (lowest efficiency) of the power supply. Under nominal conditions the power

supply should perform above the 70% efficiency level which will lower the BTU rating.

Table 8: Overall BTU Ratings

BTU (Loaded) BTU (Max)

314 BTU 988 BTU

Table 9: Loaded System Configuration

Device Configuration

CPU #1 733MHz (133 FSB) Intel Pentium III

CPU #2 733MHz (133 FSB) Intel Pentium III

Memory 256MB Micron 133

HDD #1 SCSI 9.1GB Quantum Atlas V

HDD #2 SCSI 9.1GB Quantum Atlas V

CD Slimline CD Teac CD224EB

Floppy Slimline Floppy Sony MPF 720-3

Manufacturer /

Type

Table 10: Loaded System Power Draw

Voltage Rail

+3.3V 4.1A 13.53 W

+5V 6.7A 33.5 W

-5V 0.1A 0.5 W

+12V 1.3A 15.6 W

-12V 0.1A 1.2 W

+5VSB 0.1A 0.5 W

Total 64.83 W

Current

(Measured)

Power (W)

2.2.4 System Cooling

Nine 40mm fans provide cooling for the system. Two of the nine fans are dedicated to cooling the

power supply. Six of the fans provide cooling for the processor, memory, and serverboard. One

fan cools the full-length PCI slot (this last fan is 40mm x 17mm and is a bit thinner than the other

40mm x 28mm fans). A two-speed control circuit powers the fans and is located on the SCSI

backplane. The control circuit is driven by a sensor that is located on the front panel to monitor

the incoming air temperature. The fans have a tachometer output that can be sampled through the

ServerWorks® ServerSet™ III LE chipset. The fans can be replaced by removing the top cover,

unplugging the fan connector from the serverboard, lifting the fan out of the fan bracket, and then

inserting the new fan. Additionally, a baffle will be added to help keep the processors and the

memory cool. You should always replace the baffle in the system when you are through working

on the system.

Intel® SRMK2 Internet Server Technical Product Specification 20

Page 21

2.2.5 System Peripheral Bays

2.2.5.1 CD-ROM and Diskette Drive Bay

The right side of the system (as viewed from the front) contains the CD-ROM and diskette drive

bays. Opening the door in the bezel exposes these peripherals. A slim-line diskette drive is

provided with the system and a slim-line CD-ROM is an optional addition. For information on how

to add/remove the CD-ROM and floppy, please refer to the instruction sheet that comes with the

optional CD-ROM.

2.2.5.2 Internal 3.5” SCSI Hard Drive Bay

Space is provided for two 3.5” long, 1-inch thick hard drives. There are two removable Hudson

drive carriers provided that slide into two front disk drive bays on the front left side of the chassis

(behind the removable front bezel). Each drive can be accessed and replaced by removing the

front bezel, rotating the front panel out of the way (See Figure 3), releasing the handle on the

HDD carrier, and pulling the carrier from the drive bay. A pair of LEDs on the front panel flash

green to indicate drive activity for each drive (LED’s 8 and 9). In addition, the two SCSI HDD

bays are hot swappable.

2.2.6 System Interconnection

2.2.6.1 System Internal Cables

Table 11 lists the internal cables within the system. An italicized item is an optional accessory kit

and is not supplied with the base system.

Table 11: System internal cables

Cable Purpose

SCSI hard drives 1 Standard 68-pin Wide SCSI cable with a LVD/SE terminator which connects

Front panel 1 50-pin flex cable; connects from front panel connector on the serverboard

Fan backplane 1 High density cable connects from the serverboard to the backplane to

Slim -line diskette drive 1 26-pin flex cable; connects from high-density diskette drive connector on

Slim-line CD-ROM

drive*

* Optional Accessory

Qty

to the serverboard and the SCSI backplane

to the front panel board.

provide system management monitoring of the system fans.

the serverboard to one slim-line diskette drive

1 Standard 40-pin IDE cable with 2 connectors; connects from secondary IDE

connector on the serverboard to one slim-line CD-ROM drive

Description

Intel® SRMK2 Internet Server Technical Product Specification 21

Page 22

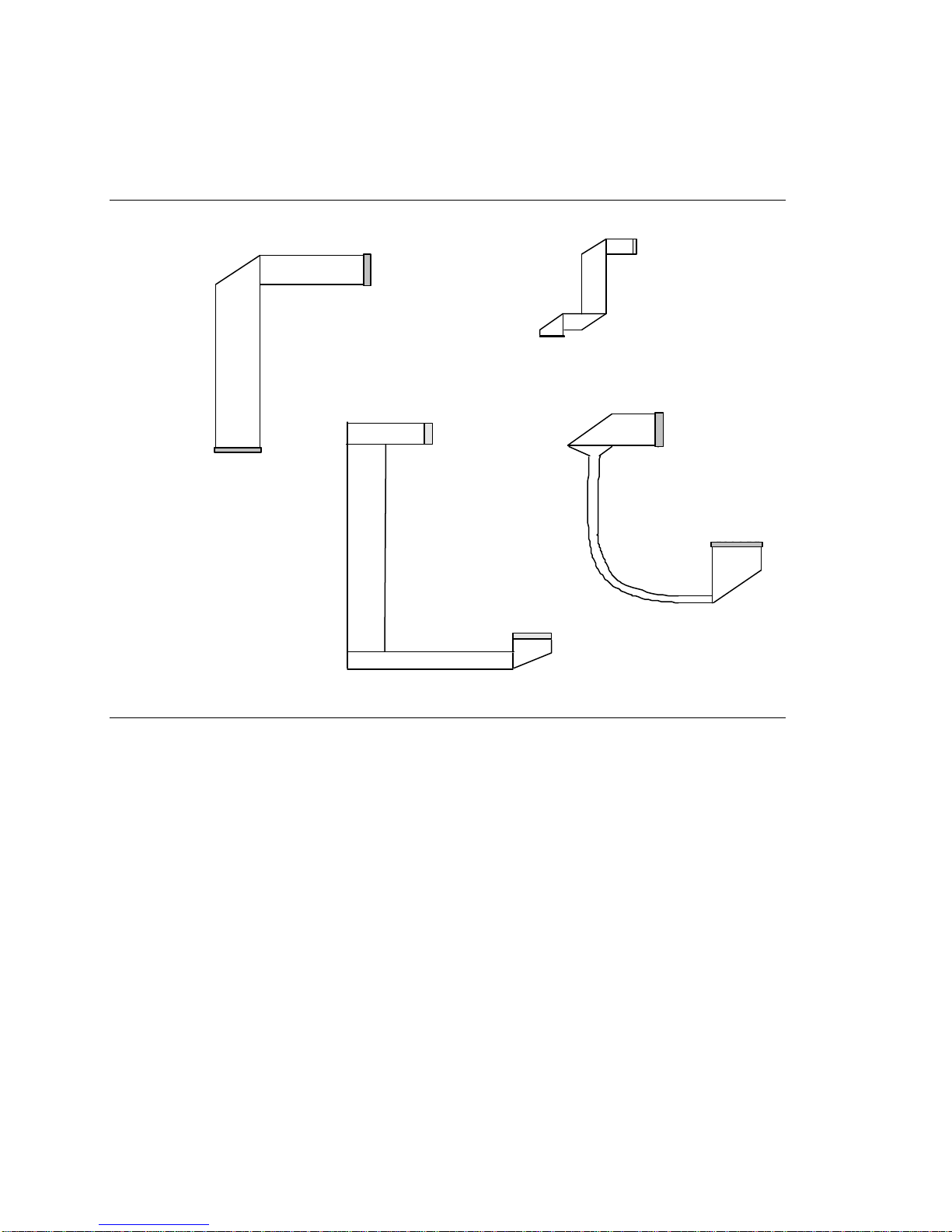

2.2.6.2 System Cable Drawings

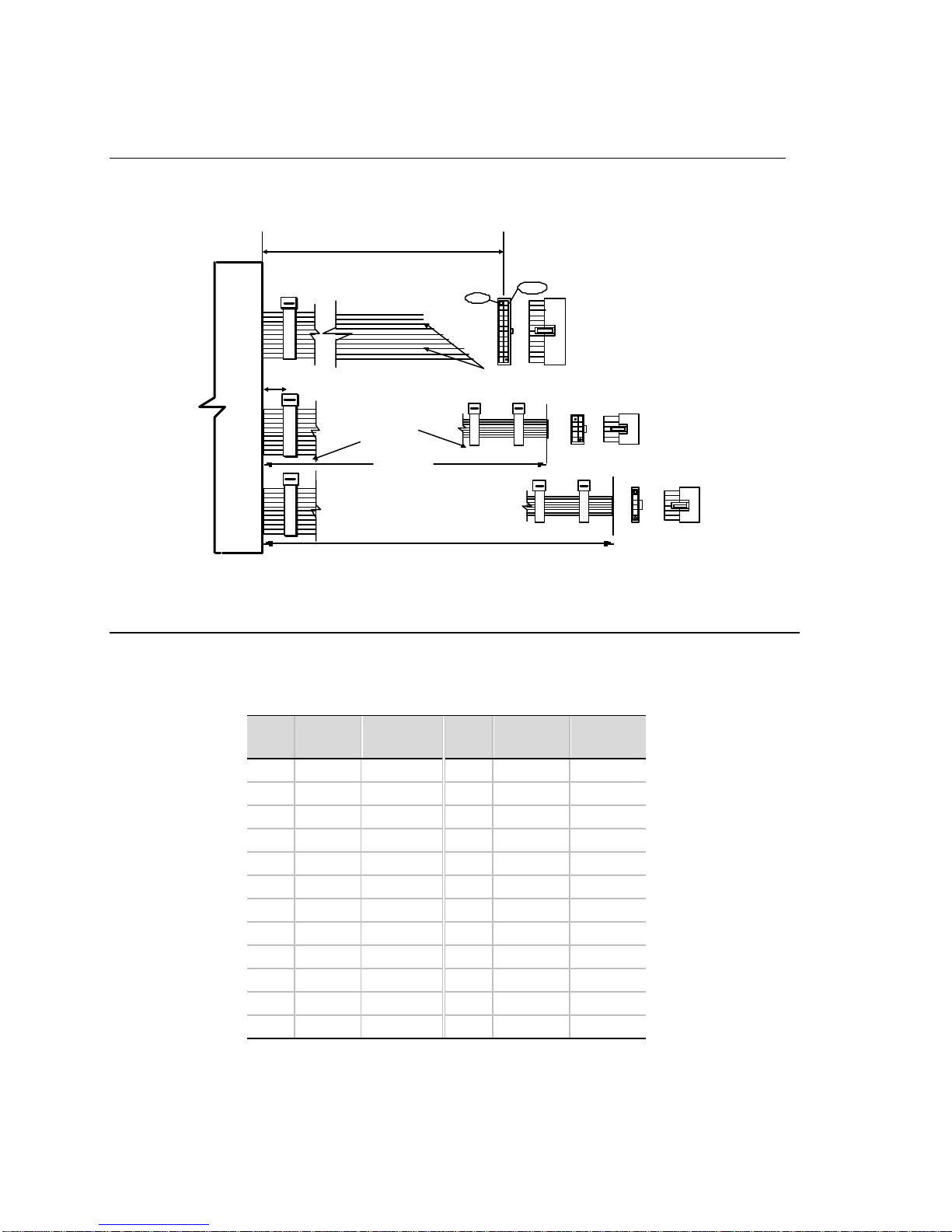

Figure 9 shows drawings of all the internal cables within the system and the locations of their

folds. Where applicable, the darker line indicates pin 1.

SCSI hard

drives

Slim-line diskette

drive

Front panel

Slim-line CD-ROM drive

(optional)

Figure 9: Internal cables

Intel® SRMK2 Internet Server Technical Product Specification 22

Page 23

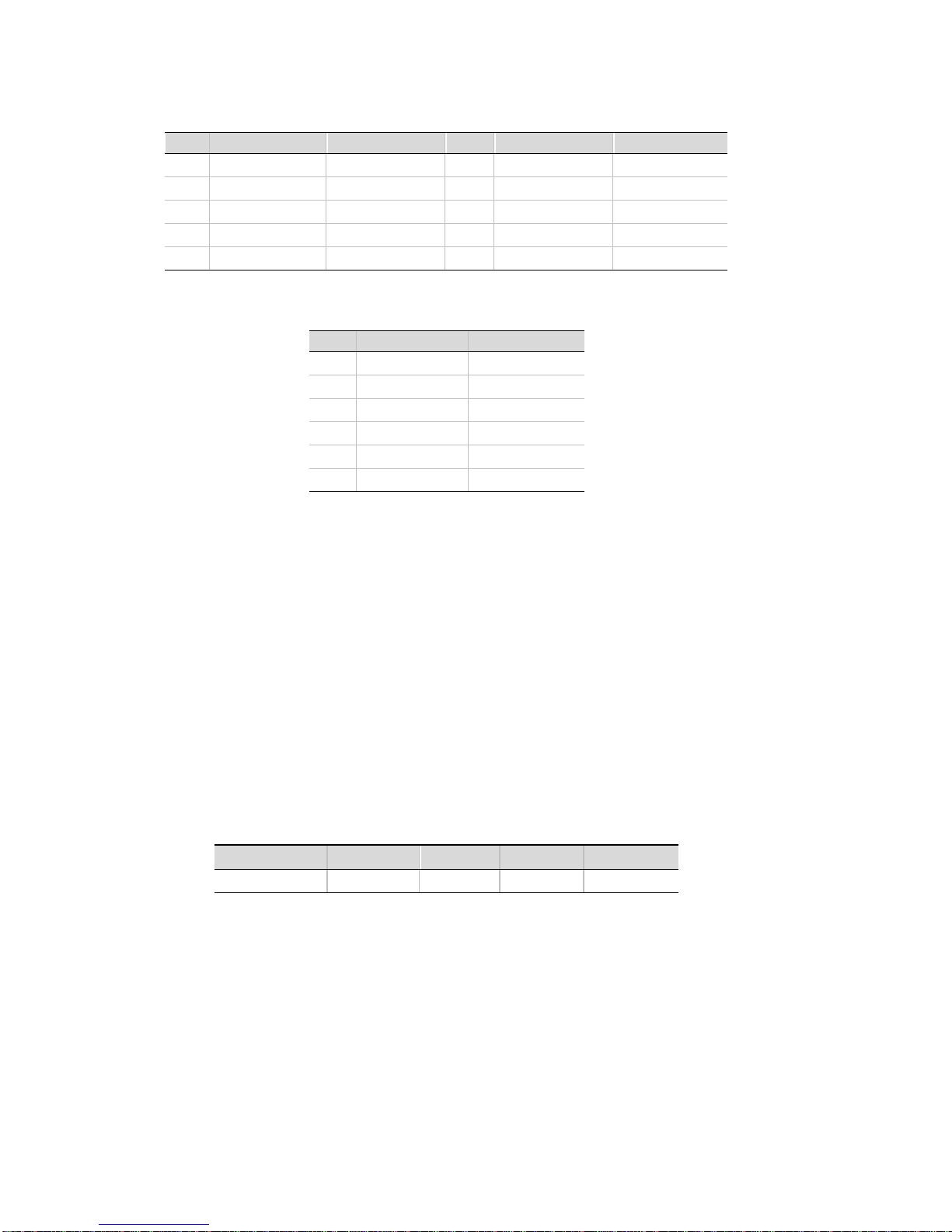

2.3 System Configuration

Table 12 lists the base configuration of the SRMK2S Internet Server.

Table 12: Standard configuration

Description Qty

SRMK2 serverboard 1

Dual-slot 66/64 PCI riser 1

Front panel board 1

200W power supply 1

System fans 9

SCSI Hard drive carriers 2

3.5” slime-line diskette drive with bracket 1

SCSI Hot swap backplane 1

SCSI backplane cable 1

Slimline floppy diskette drive cable 1

Front panel cable 1

Fan backplane cable 1

Front and Midmount brackets * 2

Heatsinks * 2

* Items that come in the Accessory Kit

Table 13 lists optional accessories. These accessories can be ordered:

Table 13: Optional accessories

Description Product Code Qty

Slim -line CD-ROM comes with one IDE

cable, installation instructions, and

backplane for slim-line CD-ROM drive

Jonathan Manufacturing sliding rail kit ACCRAILKIT001 1

ACCCDROM001 1

Intel® SRMK2 Internet Server Technical Product Specification 23

Page 24

3 SRMK2 Serverboard Description

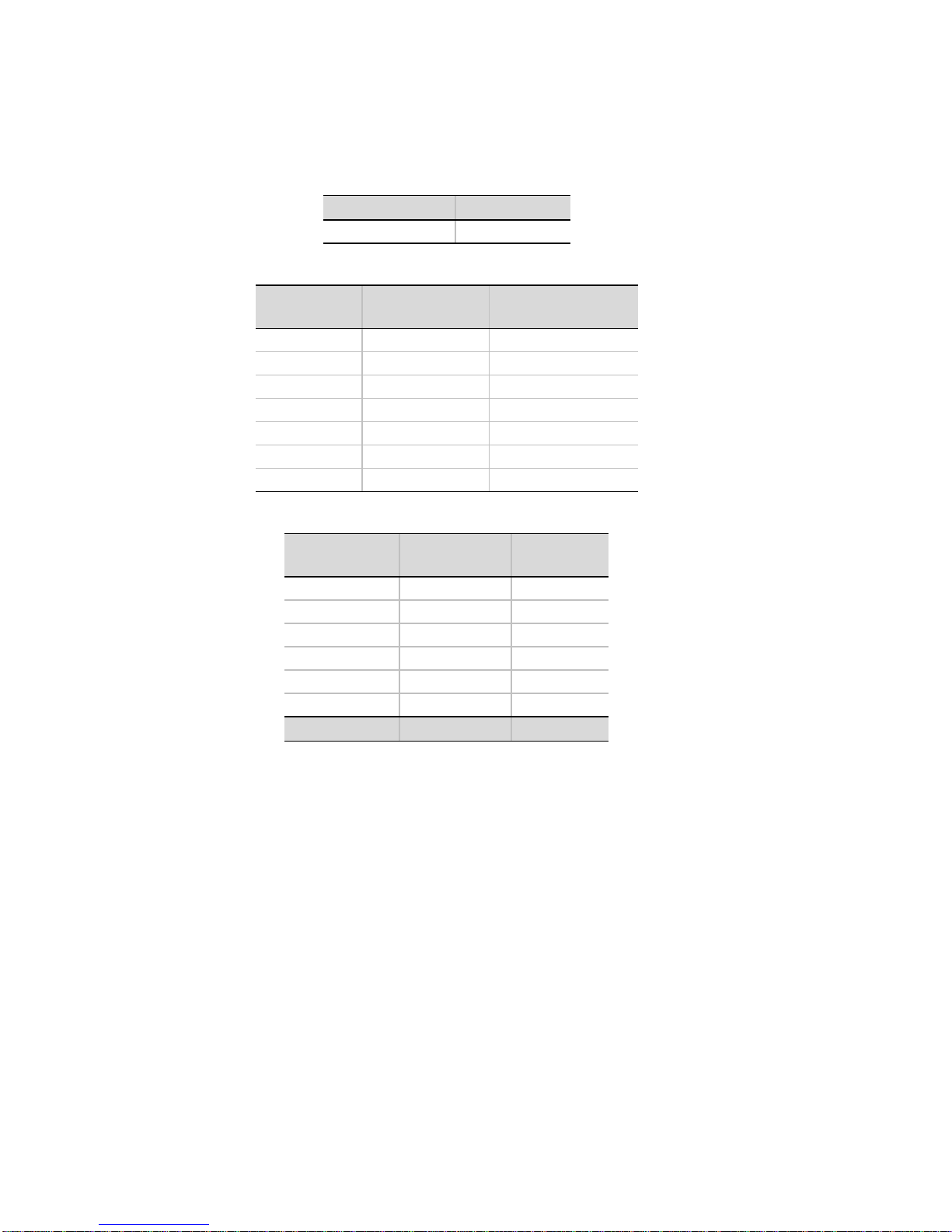

3.1 Overview

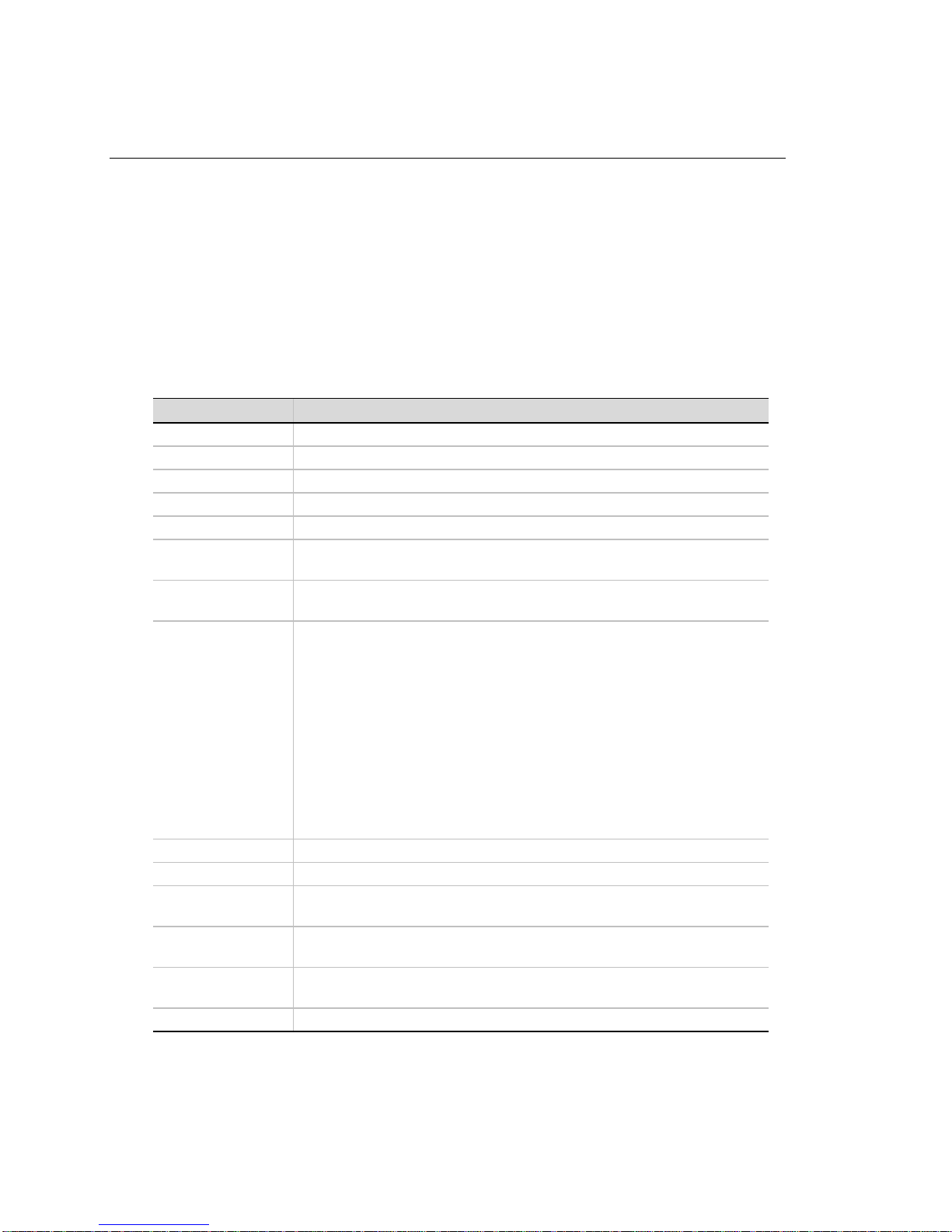

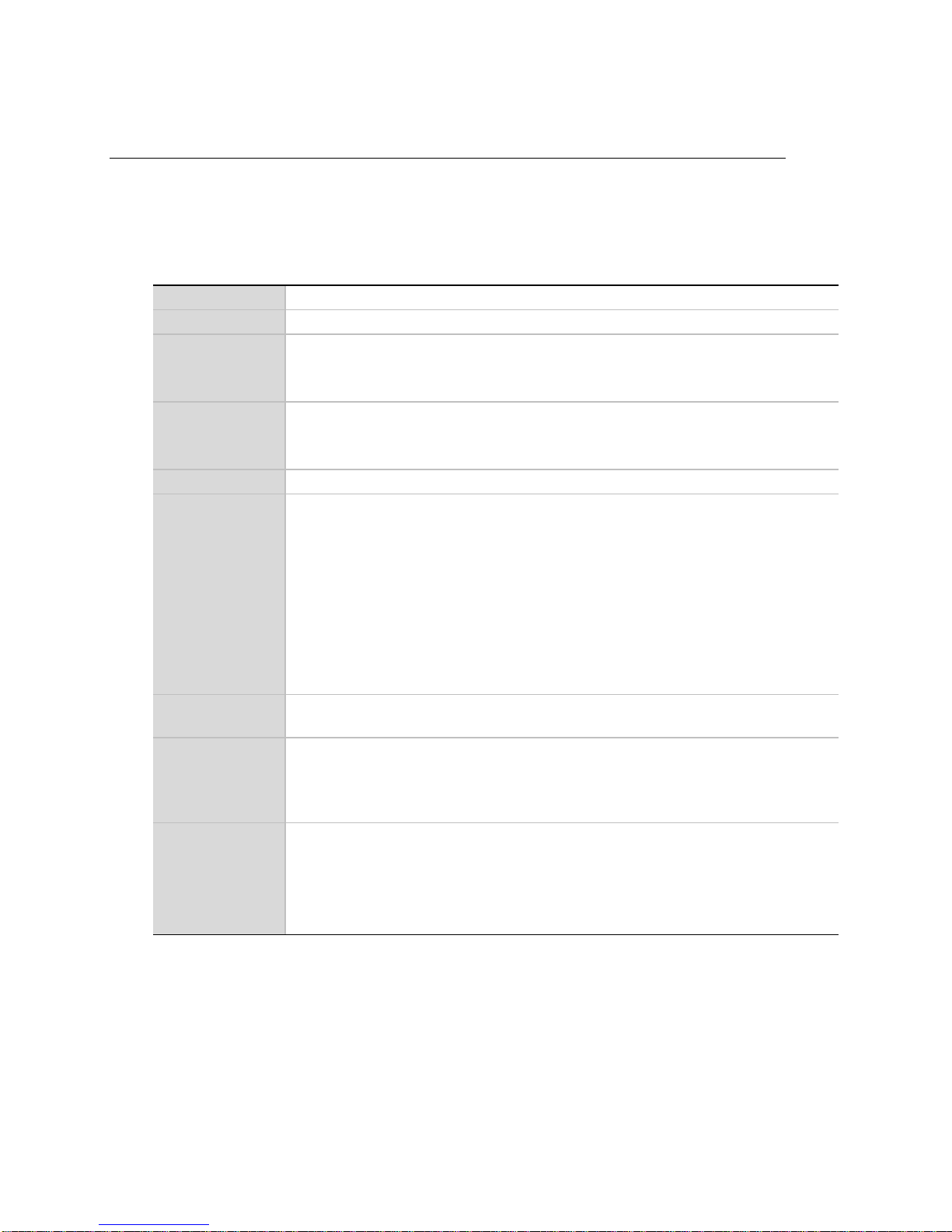

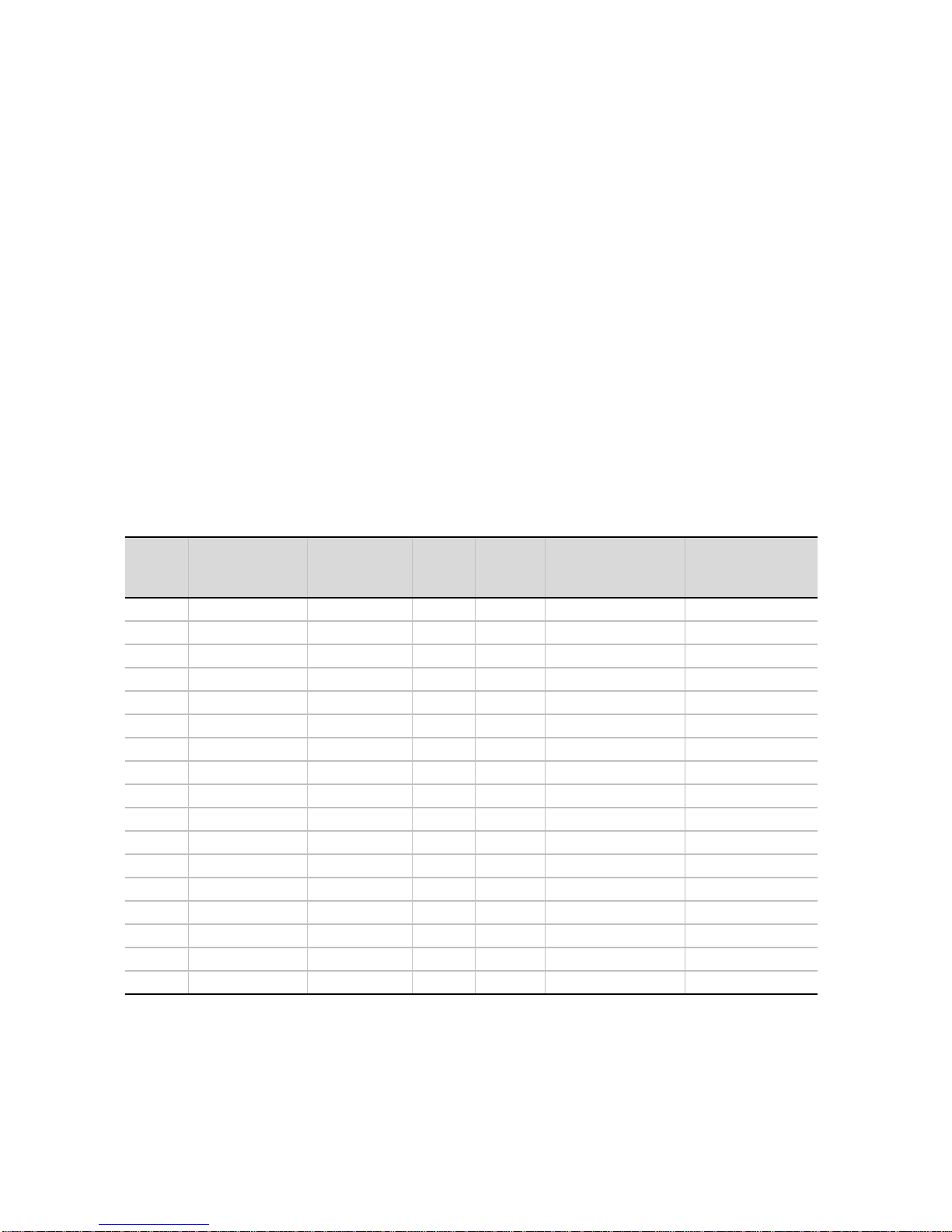

The SRMK2 serverboard features are summarized in Table 14.

Form Factor

Processor

Memory

Chipset

I/O Control

Peripheral

Interfaces

Expansion

Capabilities

BIOS

Other Features

Table 14: SRMK2 feature summary

Serverboard dimension: 10.4” x 11.3”

Supports Dual Pentium® III processors using PGA370 sockets

• Four 168-pin dual inline memory module (DIMM) sockets

• Supports only registered SDRAM DIMMs

• Supports up to 4 GB of ECC, SPD Registered SDRAM DIMMs

ServerWorks® ServerSet™III LE Chipset, consists of:

• ServerWorks CNB30LE North Bridge Front Side Bus Interface chip

• ServerWorks OSB4 South Bridge chip

SMSC FDC37B782 I/O controller

• Two integrated Intel® 82559 10/100BASE-T Ethernet controllers

• One high-density diskette drive interface for slimline diskette drive

• Two U160 SCSI channels (one internal and one external wide interface connector)

• One IDE interface with low profile CD support

• One serial port

• Two USB ports

• Two PS/2 interfaces for keyboard and mouse

• LED panel interface

• One rear panel video interface

One 64/66 plug-in riser card expansion PCI bus slot which can fit a 2x11 riser sideband

connector supporting two PCI slots – One full length card and the other low profile.

• Intel/AMI BIOS

• Intel® 8-Mbit boot block flash memory

• Supports SMBIOS, Advanced Configuration and Power Interface (ACPI), and Plug and Play

(see section 14.2 Specifications for specification compliance levels)

• Speaker

• (2) Hardware monitor chips

• Wake on Ring

• Wake on LAN

• SCSI LED connector

Intel® SRMK2 Internet Server Technical Product Specification 24

Page 25

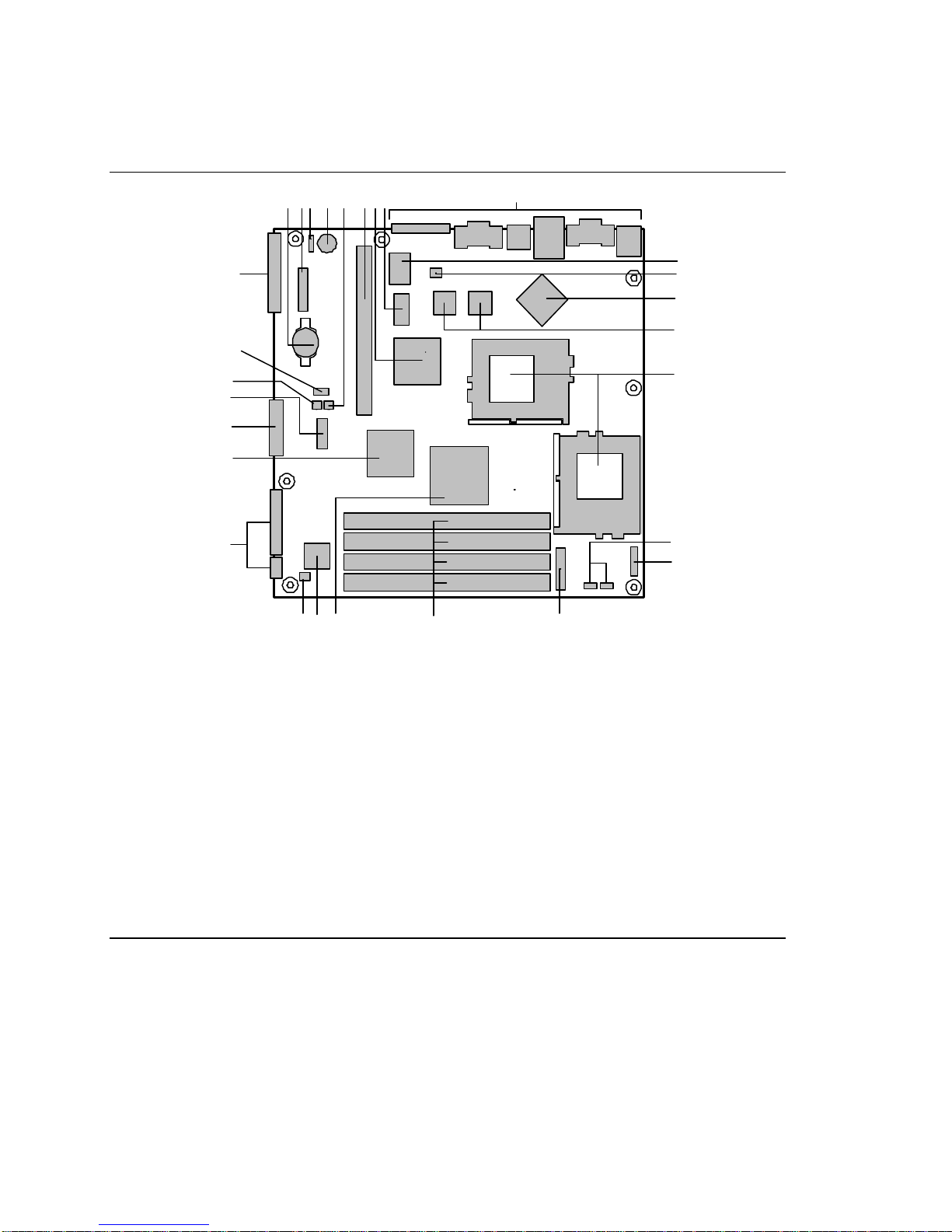

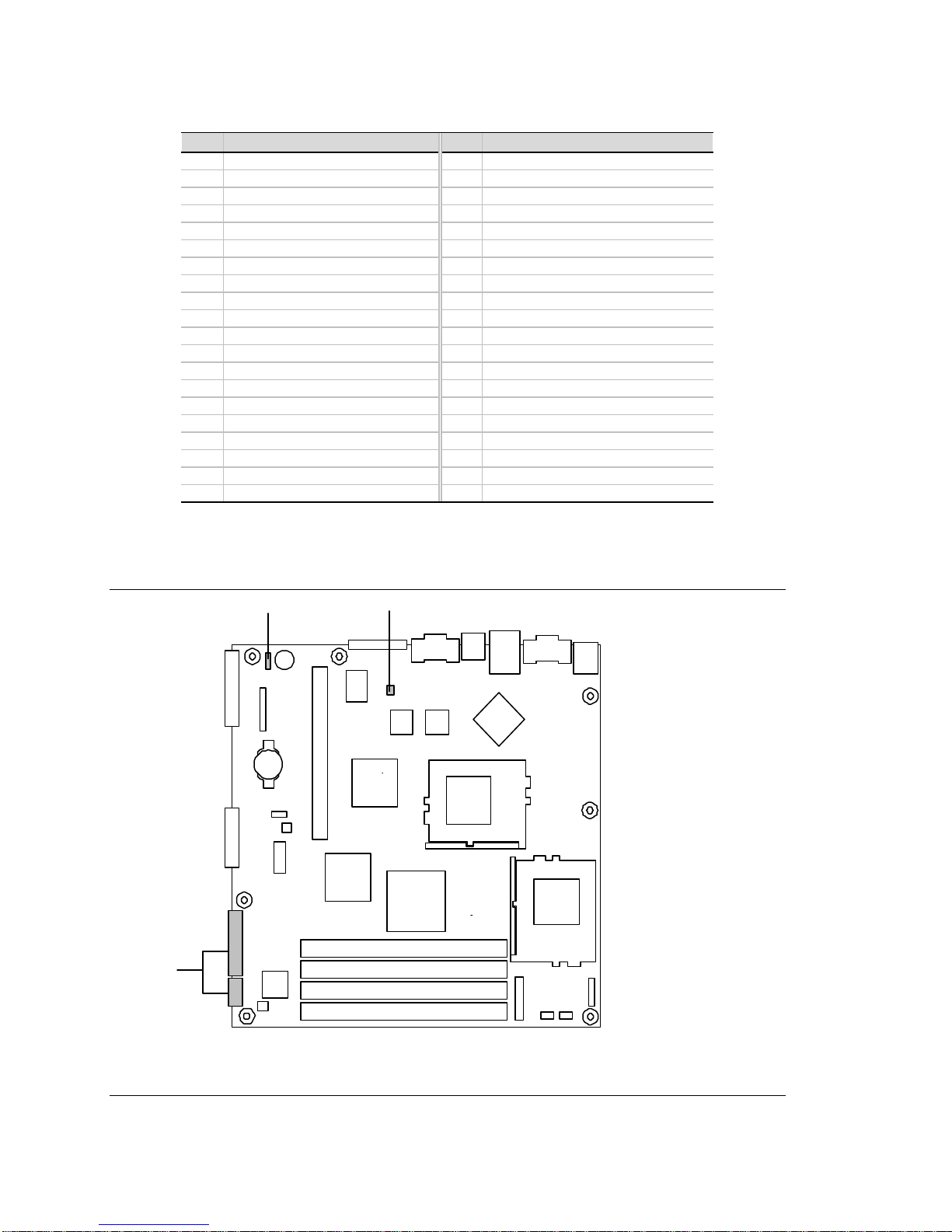

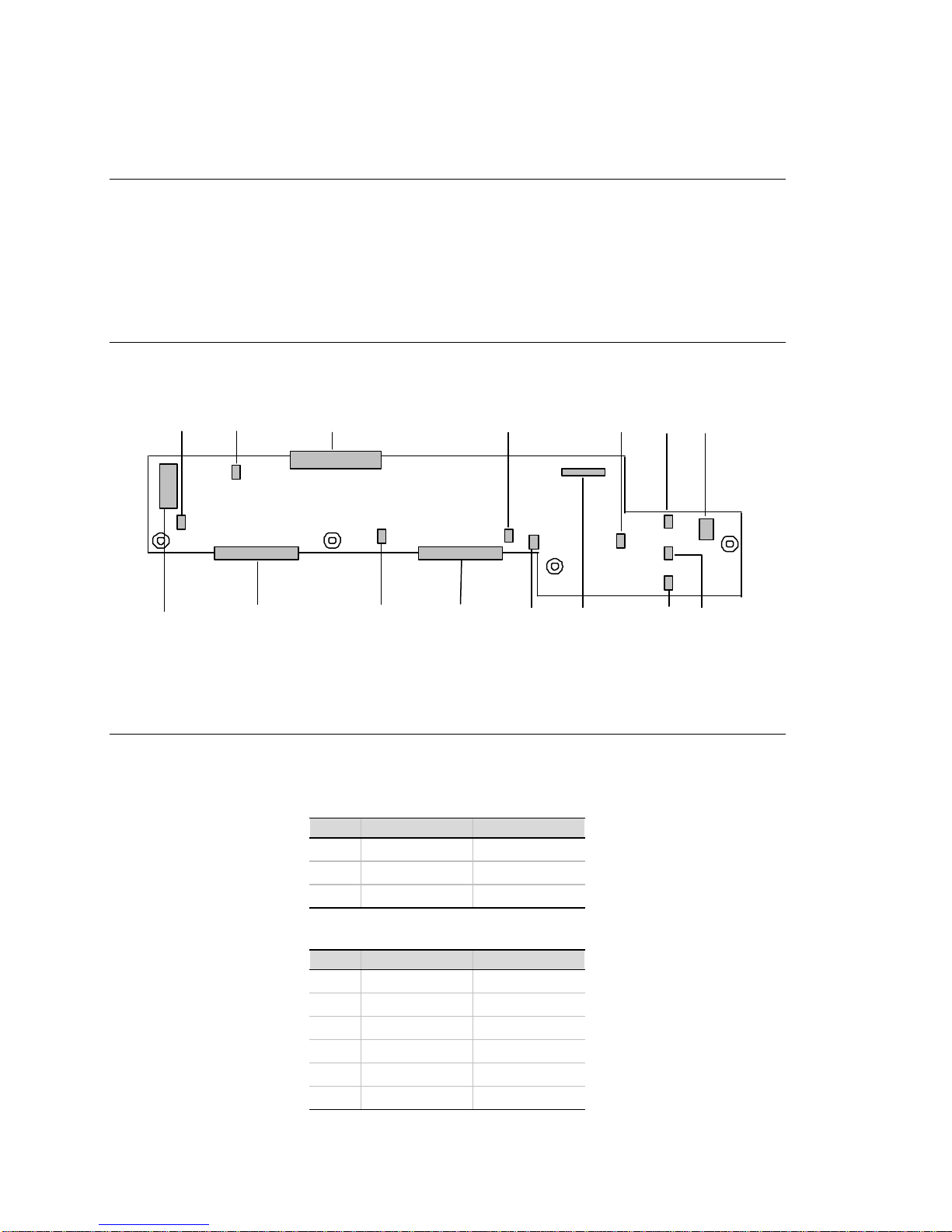

3.2 Serverboard Layout

Figure 10 shows the location of the major components on the serverboard.

DB F

C

A G

BB

AA

Z

Y

X

W

V

U

ST

A Battery N PGA370 processor sockets

B Slimline Floppy Connector O Heceta 3 hardware monitor controllers

C Wake on LAN Header P Fan backplane connector

D Speaker Q Front panel connector

E Clear Password Jumper R DIMM sockets

F 64/66 PCI Bridge Connector S SCSI LED Header

G ServerWorks® ServerSet™ South Bridge T Gluechip

H BIOS Flash memory U Power supply connector

I Back panel I/O connectors V ServerWorks® ServerSet™ North Bridge

J SMSC I/O controller W Adaptec® 7899 SCSI controller

K Wake on Ring Header X Password override jumper

L ATI Rage XL Video Y Clock generator

M Intel® 82559 10/100 Ethernet controllers Z Whitebox / Appliance Jumper

AA

HE

R

I

Internal SCSI connector

BB

Primary IDE connector

Q

Figure 10: Serverboard components

J

K

L

M

N

O

P

Intel® SRMK2 Internet Server Technical Product Specification 25

Page 26

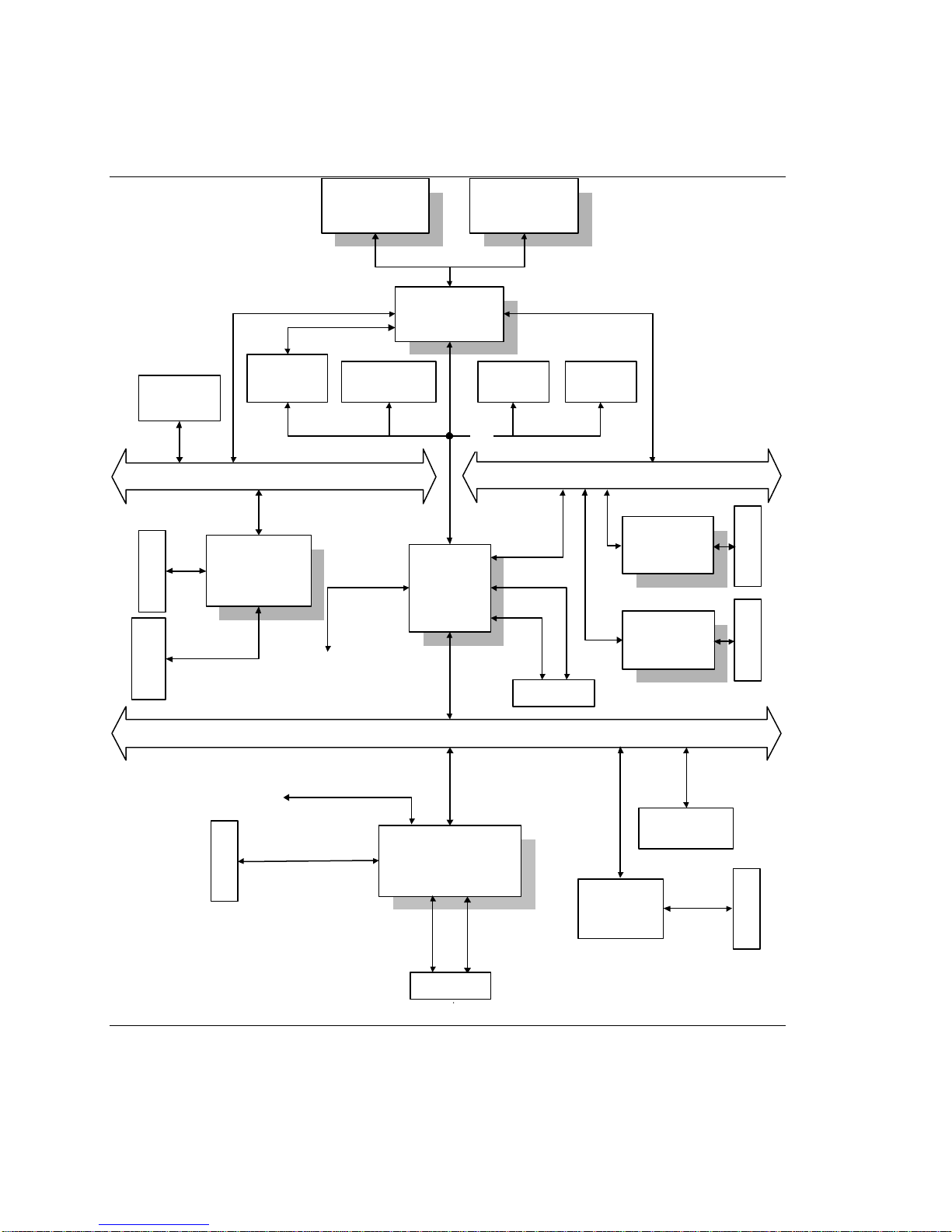

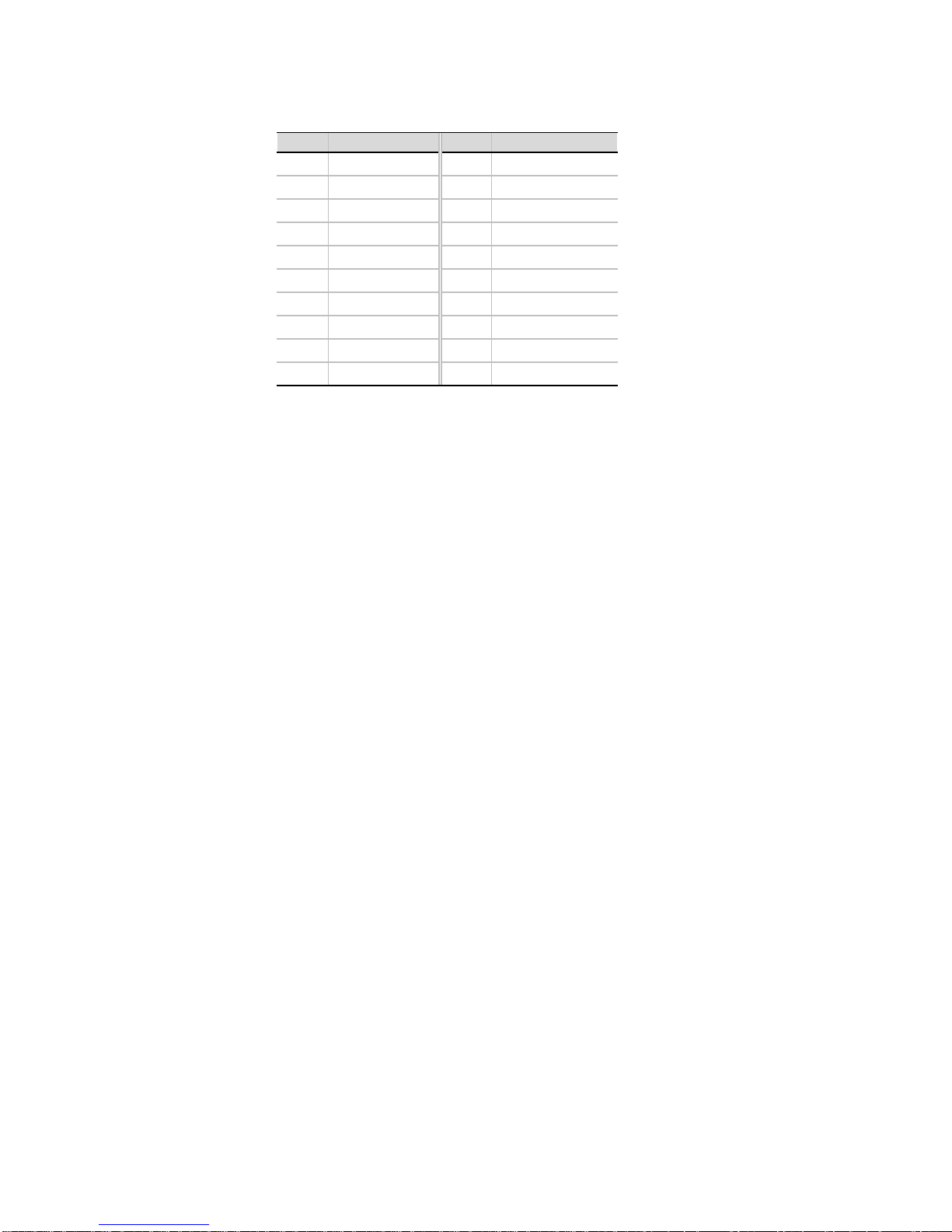

Figure 11 is a block diagram of the SRMK2 serverboard.

Dual-Slot

64/66 PCI

Riser

Back Panel

Bay

Front Drive

SDRAM

DIMMs

64/66 PCI Bus

Adaptec 7899

Dual Channel

SCSI

Processor

Clock

Generator

Pri IDE

CNB30LE

OSB4

Hardware

SM

Bus

Processor

Monitor

USB Port 0

USB Port 1

Back Panel

Hardware

Monitor

32/33 PCI Bus

Back Panel

Dual 82559

Ethernet

Controllers

ATI Rage XL

Video

Controller

ISA Bus

Diskette

Boot Block

Flash Memory

Serial Port A

Back Panel

FDC37B782

I/O Controller

Back Panel

Front PanelBack Panel

Front Panel

Controller

KeyboardMouse

Figure 11: Serverboard block diagram

Intel® SRMK2 Internet Server Technical Product Specification 26

Page 27

3.3 Processors

The SRMK2 serverboard supports dual Pentium® III processors. The host bus spe ed (100 MHz

or 133 MHz) is automatically selected based on the speed of the processors placed in the PGA370

sockets. The processors must be secured by pushing the Zero-Insertion-Force (ZIF) socket’s

lever down. The Intel SRMK2 serverboard can run in either a Uniprocessor (UP) mode or Dual

Processor (DP) mode. A terminator must be placed in the second processor PGA370 socket for

UP mode operation. A terminator card is shipped with the unit and is installed in the second

processor socket in the factory. Remove the terminator card if you wish to run in dual processor

mode. Table 15 lists processors supported by the SRMK2.

Table 15: Processors supported by the SRMK2S serverboard

Processor Type L2 Cache Size FSB Speed Speed

Pentium® III 256 KB

Pentium® III 256 KB 133 MHz

100 MHz

800 MHz

1.0 GHz

933 MHz

866 MHz

800 MHz

733 MHz

!! NOTE

The serverboard supports Pentium® III processors with a 133 MHz host bus. The serverboard may not

operate reliably if a processor with a 133 MHz host is paired with 100 MHz SDRAM.

Intel® SRMK2 Internet Server Technical Product Specification 27

Page 28

3.4 Chipset

The ServerWorks® ServerSet™ III LE chipset consists of the ServerWorks CNB30LE North

Bridge chip and the ServerWorks OSB4 South Bridge chip. The CNB30LE provides an optimized

DRAM controller. The I/O subsystem of the ServerWorks chipset is based on the OSB4 South

Bridge, which is a highly integrated PCI ISA IDE Xcelerator Bridge.

3.4.1 ServerWorks CNB30LE North Bridge Chip

The ServerWorks CNB30LE North Brid ge chip provides bus-control signals, address paths, and

data paths for transfers between the processor’s host bus, the PCI bus, and main memory.

The North Bridge features:

Processor Interface Control

• Support for processor host bus frequency of 100MHz and 133MHz

• 32-bit addressing

• Desktop-optimized GTL+ compliant host bus interface

Integrated DRAM Controller

• +3.3V only DIMM DRAM configurations

• Up to four double-sided DIMMs

• 100MHz or 133MHz SDRAM

• Support for up to 4GB of registered SDRAM

• DIMM serial presence detect via SMBus interface

• 16-, 64- and 128-Mbit devices with 2 KB, 4 KB, and 8 KB page sizes

• x 4, x 8, and x 16 DRAM widths

• Single error correction, multiple error detection

• Symmetrical and asymmetrical DRAM addressing

• ECC SEC/DED

PCI Bus Interface

• Complies with the PCI specification Rev. 2.1

• 64 bit, 33/66 MHz Secondary PCI bus interface with integrated PCI arbiter

• Asynchronous coupling to the host-bus frequency

• PCI parity generation support

• Data streaming support from PCI-to-DRAM

• Support for four PCI bus masters in addition to the host and PCI-to-ISA I/O bridge

• Support for concurrent host and PCI transactions to main memory

Data Buffering

• DRAM write buffer with read-around-write capability

• Dedicated host-to-DRAM, PCI0-to-DRAM, and PCI1-to-DRAM read buf fers

Power Management

• Support for system suspend/resume

• Compliant with ACPI power management

SMBus Support for desktop management functions

Support for System Management Mode (SMM)

Glueless Serial interface with OSB4 South Bridge chip

Intel® SRMK2 Internet Server Technical Product Specification 28

Page 29

3.4.2 ServerWorks OSB4 South Bridge Chip

The OSB4 South Bridge chip is a multifunctional PCI device implementing the PCI-to-ISA bridge,

PCI IDE functionality, USB host/hub functionality, and enhanced power management. The OSB4

South Bridge features:

• Multifunctional PCI-to-ISA Addr ess / Data bridge

• PCI Slave

• PCI Arbiter

• PCI Master

• Full ISA bus support

• ISA Arbiter

• One 8253 Counter/Timer

• Client Management

– Temperature Sensing Inputs

– Two I2C Bit Bang Interfaces for (GPOC)

– Four general purpose I/O (GPMs)

• Support for the PCI bus at 33 MHz

• Support for PCI Rev 2.1 Specification

• Integrated dual-channel enhanced IDE interface

– Support for up to four IDE devices

– PIO Mode 4 transfers at up to 16 MB/sec

– Support for Ultra DMA/33 synchronous DMA mode transfers at up to 33 MB/sec

– Bus master mode with an 8 x 32-bit buffer for bus master PCI IDE burst transfers

• Enhanced DMA controller

– Two 8237-based DMA controllers

– Support for PCI DMA with three PC/PCI channels and distributed DMA protocols

– Fast type -F DMA for reduced PCI bus usage

• Interrupt controller based on 82C59

– Support for 15 interrupts

– Programmable for edge/level sensitivity

• Power management logic

– Sleep/resume logic

– Support for Wake on Ring and Wake on LAN† technology

– Support for APM and ACPI Revision 1.0

• Internal APIC Controller

• USB Interface

• SMB bus interface

• Glueless Serial interface with CNB30LE North Bridge chip

• Black Box Security Functions

– 2X Passwords

– CMOS Protection

– Super I/O Security

• Real-Time Clock

– 256-byte battery-backed CMOS SRAM

– Date alarm

– 16-bit counters/timers based on 82C54

Intel® SRMK2 Internet Server Technical Product Specification 29

Page 30

3.5 Memory

The serverboard has four DIMM sockets. The serial presence detect (SPD) data structure which

is programmed into an E2PROM on the DIMM instructs the BIOS on the SDRAM’s siz e and

speed. The minimum memory size is 64MB; the maximum memory size is 4GB. DIMMs can be

populated in any order, but due to the 25 degree angle of the DIMM socket mountings it is

physically easier to populate DIMMs starting with DIMM0 and moving towards DIMM3.

Memory size can vary between sockets and slot vacancy between DIMMs is permitted. Mixing

of DIMM size is allowed as long as they are all registered DIMMs. For a list of compatible tested

memory please visit the support site at support.intel.com.

The serverboard supports the following memory features:

• 168-pin SPD DIMMs with gold -plated contacts.

• 133 MHz and 100 MHz registered SDRAM DIMMs, 72-bit ECC, 3.3V memory.

• Single- or double-sided DIMMs in the sizes listed in Table 16.

• Registered DIMMs of the following sizes: 64M, 128M, 256M, 512M and 1G for a

maximum memory size of 4 GB. Double stacked DIMMs may only be used if they

are within the 4.33 mm maximum thickness imposed by the 25 degree DIMM socket

spacing on the baseboard.

Table 16: Supported memory sizes and configurations

DIMM

Size

64 MB 8 Mbit x 72 64Mb 4Mb 16 bit X 8MB X 8B = 64MB

64 MB 8 Mbit x 72 64Mb 8Mb 8 bit 8MB X 8B = 64MB X

128 MB 16 Mbit x 72 64Mb 8Mb 8 bit X 16MB X 8B = 128MB

128 MB 16 Mbit x 72 64Mb 16Mb 4 bit 16MB X 8B = 128MB X

64 MB 8 Mbit x 72 128Mb 8Mb 16 bit 8MB X 8B = 64MB X

128 MB 16 Mbit x 72 128Mb 8Mb 16 bit X 16MB X 8B = 128MB

128 MB 16 Mbit x 72 128Mb 16Mb 8 bit 16MB X 8B = 128MB X

256 MB 32 Mbit x 72 128Mb 16Mb 8 bit X 32MB X 8B = 256MB

256 MB 32 Mbit x 72 128Mb 32Mb 4 bit 32MB X 8B = 256MB X

64 MB 8 Mbit x 72 256Mb 8Mb 32 bit 8M B X 8B = 64MB X

128MB 16 Mbit x 72 256Mb 8Mb 32 bit X 16MB X 8B = 128MB

128 MB 16 Mbit x 72 256Mb 16Mb 16 bit 16MB X 8B = 128MB X

256MB 32 Mbit x 72 256Mb 16Mb 16 bit X 32MB X 8B = 256MB

256 MB 32 Mbit x 72 256Mb 32Mb 8 bit 32MB X 8B = 256MB X

512 MB 64 Mbit x 72 256Mb 32Mb 8 bit X 64MB X 8B = 512MB

512 MB 64 Mbit x 72 256Mb 64Mb 4 bit 64MB X 8B = 512MB X

1GB 128 Mbit x 72 256Mb 64Mb 4 bit X 128MB X 8B = 1GB

Configuration DRAM

Technology

DRAM

Depth

DRAM

Width

Single-sided

DIMM Size x 64

bit

Double-sided

DIMM Size x 64

bit

! NOTE

All memory components and DIMMs used with this motherboard must comply with the following

PC SDRAM specifications:

• PC SDRAM Specification (memory component specific)

• PC SDRAM Registered DIMM Specification

Intel® SRMK2 Internet Server Technical Product Specification 30

Page 31

3.6 SCSI Host bus Interface

The SRMK2 motherboard uses an Adaptec® AIC-7899 Ultra 160 SCSI controller for the SCSI

Host bus interface. The AIC provides two independent Ultra 160/m SCSI channels combined with

a full-featured PCI 2.1/2.2-compliant bus master. The AIC-7899 operates at up to 66MHz and

functions as a 64-bit bus master capable of supporting zero wait state 64-bit memory transfers at a

maximum data burst rate of 533 Mbytes/sec. The AIC-7899 SCSI controller complies with the

SCSI-3 standard providing multimode SCSI support for both single-ended (SE) and Low Voltage

Differential (LVD) SCSI peripherals. The SRMK2 motherboard has two SCSI Ultra 160, 68-pin

D-shell connectors, one internal and one external on the rear panel. Both SCSI connectors are

protected from over-current conditions via a separate polyfuse.

3.6.1 SCSI Hard Drive LED Connector (Optional)

The optional SCSI hard drive LED connector is a 1 x 2-pin connector that allows add-in

SCSI controller applications to use the same LED as the IDE controller. This connector

can be connected to the LED output of the add-in controller card (J35 is the designator

number on the motherboard)

3.7 IDE Interface

Through the ServerWorks® ServerSet™ OSB4 South bridge, the serverboard has one independent

bus-mastering IDE interface. This interface supports:

• ATAPI devices (such as CD-ROM drives)

• ATA devices

One 40-pin connector is populated on boa rd. The connector at J9 provides the primary IDE

interface (only this one is populated). The BIOS supports logical block addressing (LBA) and

extended cylinder head sector (ECHS) translation modes. The drive reports the transfer rate and

translation mode to the BIOS.

3.8 USB

The serverboard has two USB ports; one USB peripheral can be connected to each port. For

more than two USB devices, an external hub can be connected to either port. The two USB ports

are implemented with stacked back panel I/O connectors. The serverboard fully supports UHCI

and uses UHCI-compatible software drivers. See section 14.2 for information about the USB and

UHCI specifications. (Note that NT 4.0 does not have USB support). Addit ionally, Legacy

USB devices are not supported by the system BIOS. This means that a Legacy USB keyboard

will not be operable during the system POST and you will not be able to enter the system BIOS

with a Legacy USB keyboard because of this restriction. To work around this problem, use a

PS/2 keyboard for changing BIOS settings. This restriction does not affect the use of Legacy

USB keyboards under operating systems that support USB devices.

The SRMK2 USB ports feature:

• Self-identifying peripherals tha t can be plugged in while the computer is running

• Automatic mapping of function to driver and configuration

Intel® SRMK2 Internet Server Technical Product Specification 31

Page 32

• Support for isochronous and asynchronous transfer types over the same set of wires

• Guaranteed bandwidth and low latencies appropriate for telephony, audio, and other

applications

• Error-handling and fault -recovery mechanisms built into the protocol

! NOTE

Computer systems that have an unshielded cable attached to a USB port may not meet FCC Class B

requirements, even if no device or a low -speed USB device is attached to the cable. Use shielded cable that

meets the requirements for full-speed devices.

3.9 I/O Controller

The FDC37B782 I/O controller from SMSC is an ISA Plug and Play-compatible, multifunctional

I/O device that provides the following features:

• One serial port

• FIFO support on both serial and diskette drive interfaces

• PS/2-style mouse and keyboard interfaces

• Support for serial IRQ packet protocol

• Intelligent power management, including:

− Shadowed write -only registers for ACPI compliance

− Programmable wake up event interface

3.9.1 Serial Port

The motherboard supports one serial port via 9-pin D-Sub connector. The populated serial port is

located on the back panel. The serial port is NS16C550-compatible UARTs and support data

transfers at speeds up to 460 Kbits/sec with BIOS support. Additionally, this port supports the

Wake On Ring functionality.

3.9.2 Diskette Drive Controller

The I/O controller supports a single diskette drive that is compatible with the 82077 diskette drive

controller and support both PC-AT† and PS/2 modes. The baseboard supports only a slimline

floppy drive interface connector.

3.9.3 Keyboard and Mouse Interface

The PS/2 keyboard and mouse connectors are located on the back panel. The +5V lines to these

connectors are protected with a Poly Switch† circuit that, like a self -healing fuse, reestablishes the

connection after an overcurrent condition is removed.

! NOTE

The mouse and keyboard can be plugged into either of the PS/2 connectors. Turn off power to

the computer before connecting or disconnecting a keyboard or mouse.

3.9.4 Real-Time Clock, CMOS SRAM, and Battery

The real-time clock is provided by the SMC FDC37B782 Super I/O chip and is compatible with

DS1287 and MC146818 components. The clock provides a time -of-day clock and a multicentury

Intel® SRMK2 Internet Server Technical Product Specification 32

Page 33

calendar with alarm features and century rollover. The real-time clock supports 256 bytes of

battery-backed CMOS SRAM in two banks that are reserved for BIOS use.

A coin -cell battery powers the real-time clock and CMOS memory. When the computer is not

pl ugged into a wall socket, the battery has an estimated life of three years. When the computer is

plugged in, the 3.3V standby current from the power supply extends the life of the battery. The

clock is accurate to ± 13 minutes/year at 25ºC with 3.3VSB applied. The time, date, and CMOS

values can be specified in the BIOS Setup program.

! NOTE

The recommended method of accessing the date in systems with Intel ® serverboards is indirectly from the

Real Time Clock (RTC) via the BIOS. The BIOS on Intel ® serverboards contains a century checking and

maintenance feature. This feature checks the two least significant digits of the year stored in the RTC

during each BIOS request (INT 1Ah) to read the date and, if less than 80 (i.e., 1980 is the first year suppor ted

by the PC), updates the century byte to 20. This feature enables operating systems and applications using

the BIOS date/time services to reliably manipulate the year as a four -digit value.

For more information on a proper date access in systems with Intel serverboards, please visit:

http://support.intel.com/support/year2000/

3.10 Intel® 82559 10/100 Ethernet Controllers

Two Intel 82559 LAN controllers provide two 10/100 Base-T RJ-45 interfaces. The two LAN

ports are brought out through a double stacked RJ45 connector on the rear of the chassis.

The LAN circuitry supports Wake on LAN technology on both LAN ports. Wake on LAN

technology enables remote wakeup of the computer through a network. If a PCI add-in network

interface card (NIC) with remote wakeup capabilities is desired, the remote wakeup connector on

the NIC must be connected to the onboard Wake on LAN header at J8. The on-board LAN

controllers or an add-in NIC will monitor network traffic at the MII interface; upon detecting a

Magic Packet† the LAN controllers or NIC will assert a wakeup signal that will power up the

computer. Alert and wake on LAN features are supported by the SRMK2 and the SMBus

interface of the Intel 82559s.

CAUTION

For Wake on LAN, the +5V standby line for the power supply must be capable of delivering +5V ± 5% at

720mA. Failure to provide adequate standby current when implementing Wake on LAN can damage the

power supply.

3.11 Video Interface

The on-board video interface is implemented using the ATI RAGE XL video controller. The

video controller is accessed over the 32-bit PCI bus interface on the ServerWorks® North Bridge.

Some of the key features of the video interface are listed below:

• Comprehensive AGP support, in cluding 2X mode, Sideband addressing.

• Fully PC 98 compliant.

• 32-bit wide memory-mapped registers.

• Programmable flat or paged memory model with linear frame buffer access.

• Triple 8-bit palette DAC with gamma correction for true WYSIWYG color.

• Pixel rates up to 230 MHz.

Intel® SRMK2 Internet Server Technical Product Specification 33

Page 34

• 4M bytes of video SDRAM organized as 2Mx32-bits, accessible over the 64-bit

interface of the controller.

• DDC1 and DDC2B+ for plug and play monitors.

• Power management for full VESA DPMS and EPA Energy Star compliance.

• Integrated hardware diagnostic tests performed automatically upon initialization.

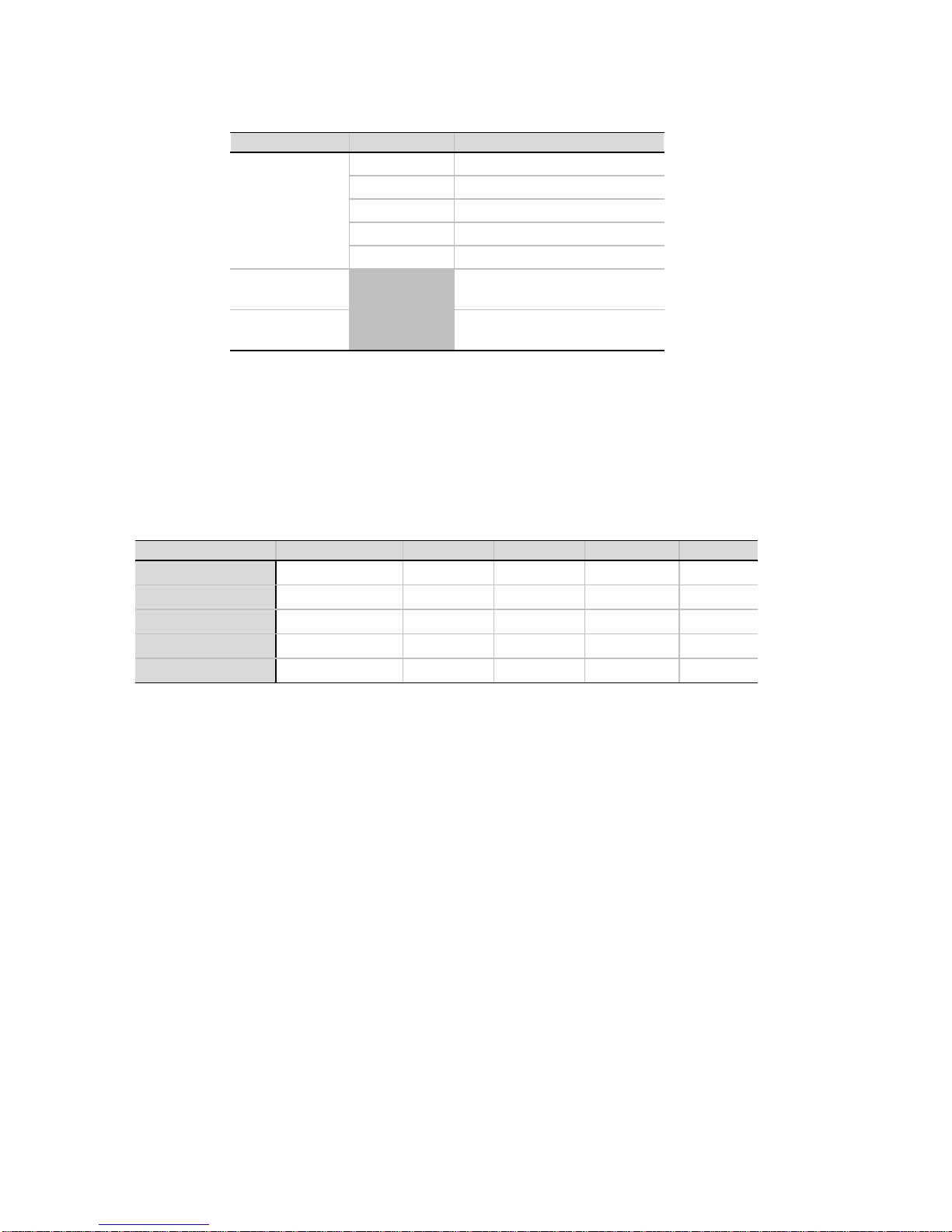

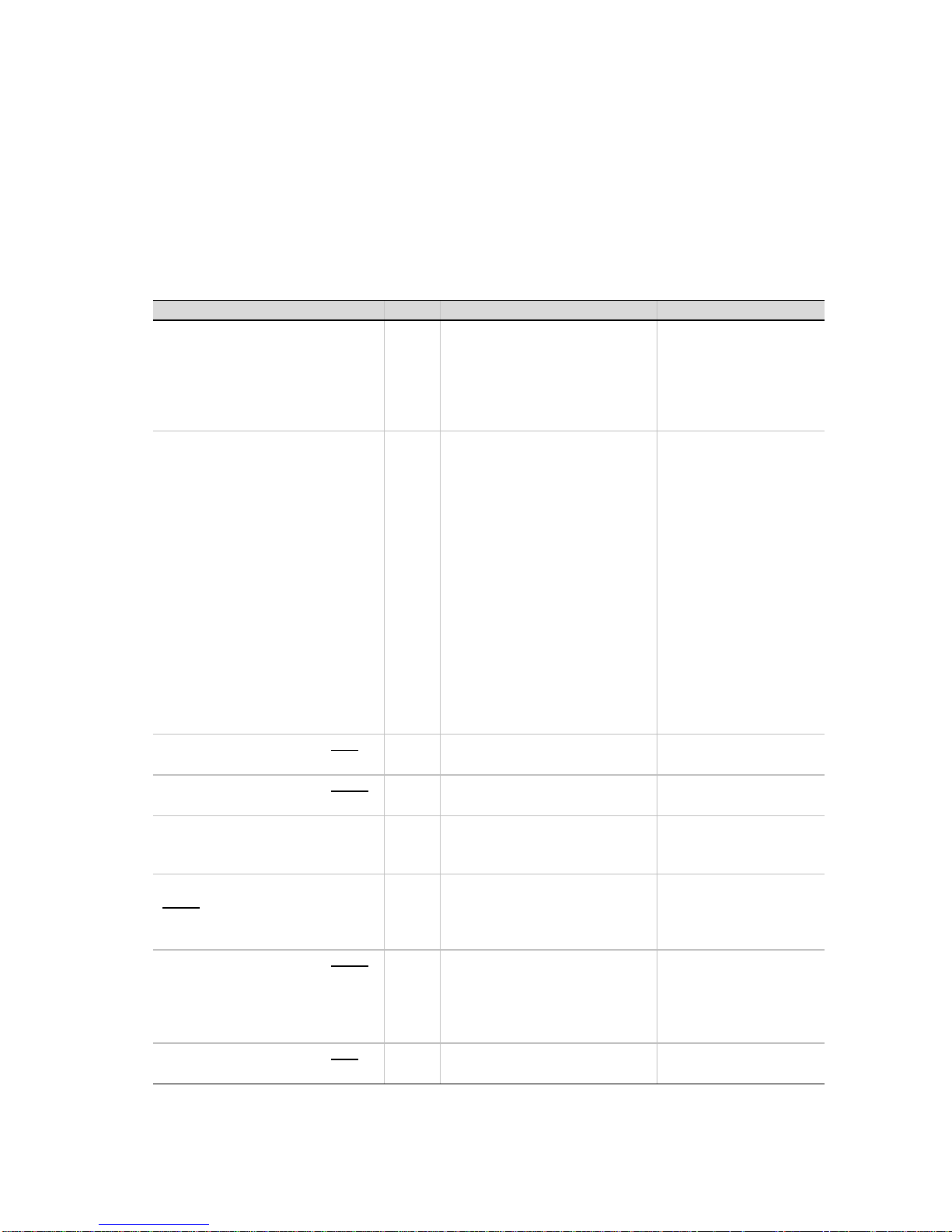

3.12 Hardware Monitor

Two Heceta 3 controllers are provided on the motherboard to monitor temperature, voltage, and

fan speed. In addition to the on chip temperature sensor, each Heceta provides input pin s for

connection to an external temperature sensor. These inputs are connected to the Pentium® III

thermistor outputs.

Access to the two Heceta controllers is provided through the SMB bus. Heceta #1 is mapped

onto SMB address [0101 101x]. Heceta #2 is mapped onto SMB address [0101 110x], where x is

the Read/Write bit of the SMB bus. These can also be listed as 0x2d and 0x2e. Table 17 shows

the functions monitored by each Heceta controller.

When the Heceta is configured in the monitoring mode, it cycles sequentially through the

measurement of analog inputs and the temperature sensor, while at the same time the fan speed

inputs are independently monitored. Measured values from these inputs are stored in Value

Registers. These can be read out over the serial bus or can be compared with programmed limits

stored in the Limit Registers. The results of out of limit comparisons are stored in the Interrupt

Status Registers and will generate an interrupt on the INT line, if enabled. Any or all of the

Interrupt Status Bits can be masked by appropriate programming of the Interrupt Mask Register.

There are 9 Fans in the SRMK2 System which are multiplexed into the Fan1/Fan2 inputs of the

Heceta chips, as shown in Table 17. The Mux1/Mux0 control signals are software controlled bits

located in the front panel EPLD and are used to control the fan tachometer multiplexer located on

the Backplane. The software control is located in the Advanced Server Management software.

Table 17: Functions monitored by the Heceta controllers

Heceta Pin Mux1/Mux0 Control

00 Fan Tach 1 Fan Tach 3

Fan 1

Fan 2

CHS

+VCCP1 VCORE N/A

+2.5V VTT +2.5V

+3.3V +3.3V +3.3V STBY

+5V +5V +5V STBY

01 Fan Tach 5 Fan Tach 7

10 Fan Tach 9 N/A

11 N/A N/A

00 Fan Tach 2 Fan Tach 4

01 Fan Tach 6 Fan Tach 8

10 N/A N/A

11 N/A N/A

Chassis Intrusion

Heceta #1 Function

SMB addr 0101 101x

(Not functional on SRMK2)

Heceta #2 Function

SMB addr 0101 110x

N/A

Intel® SRMK2 Internet Server Technical Product Specification 34

Page 35

+12V +12V N/A

D1+/D1- CPU 0 Thermistor CPU 1 Thermistor

For more details on accessing the Heceta registers please refer to the ADM1024 data sheet from

Analog Devices.

3.13 Wake on Ring and Resume on Ring

The SRMK2 baseboard provides three methods for implementing Wake on Ring (WOR). An

external modem connected to the serial port can toggle the super I/O controller’s Ring Indicator

pin which should be enabled to cause a wakeup event. The WOR output of an internal modem

card may be connected to an internal 2-pin WOR header (J11) to cause a wakeup event. Finally,

a PCI modem may implement a WOR circuit that uses PCI PME# to cause a wakeup event.

This section describes two technologies that enable telephony devices to access the computer

when it is in a power-managed state. The method used depends on the type of telephony device

(external or internal) and the power management mode being used (APM or ACPI).

NOTE

/

Wake on Ring and Resume on Ring technologies require the support of an operating system that

provides full ACPI functionality.

3.13.1 Wake on Ring

The operation of Wake on Ring can be summarized as follows:

• Powers up the computer from either the APM soft-off mode or the ACPI S5 state

• Detects incoming calls differently for external and internal modems:

− For external modems, the serverboard hardware monitors the Ring Indicator (RI)

input of the serial port.

− For internal modems, a cable must be routed from the modem to the Wake on Ring

connector

3.13.2 Resume on Ring

The operation of Resume on Ring can be summarized as follows:

• Resumes operation from either the APM sleep mode or the ACPI S1 to S4 state

• Detects incoming calls similarly for external and internal modems; does not use the

Wake on Ring connector.

• Requires that modem interrupt be unmasked for correct operation.

3.14 Speaker

A 47 Ω inductive speaker is mounted on the motherboard. The speaker provides audible error

code (beep code) information during the power-on self test (POST).

Intel® SRMK2 Internet Server Technical Product Specification 35

Page 36

3.15 Fan Support

The backplane powers nine 40mm syste m fans. Additionally, it incorporates logic to control and

monitor the tachometer speed of fans. Eight of those fans are 40mm x 28mm. The ninth fan is

40mm x 17mm and provides cooling to the PCI add-in card area.

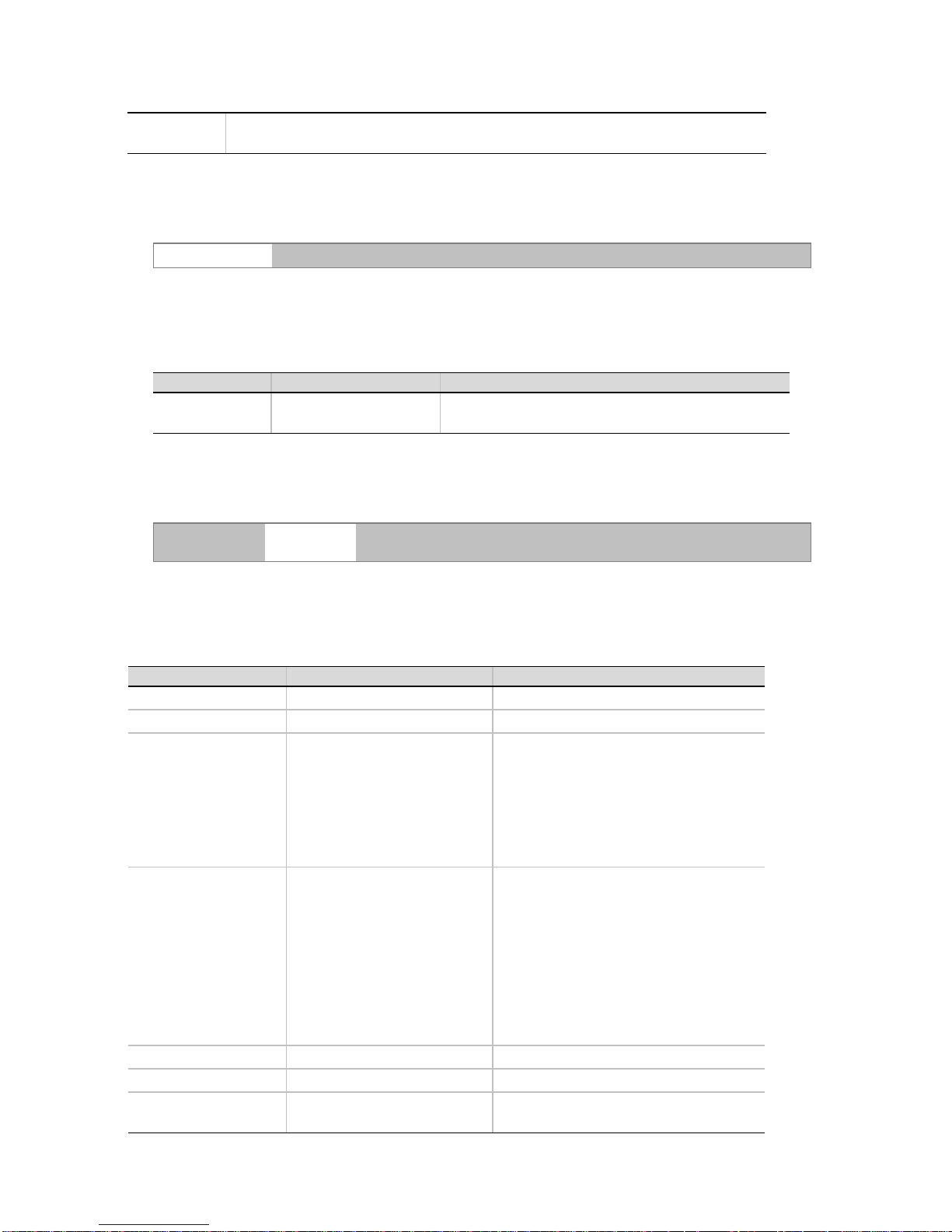

3.16 Baseboard Programming

3.16.1 PCI Configuration Space Map

Table 18: PCI Configuration Space Map

Bus

Number

(hex)

00 00 00 CNB30LE Host Bridge Function 32 bit PCI (P1_AD[16])

00 00 01 CNB30LE 2nd Host Bridge Function 64 Bit PCI (P1_AD[16])

00 01 NA PCI32 VIDEO (P1_AD[17])

00 02 NA PCI32 SLOT1 (P1_AD[18])

00 03 NA PCI32 SLOT2 (P1_AD[19])

00 05 NA PCI32 LAN1 (P1_AD[23])

00 06 NA PCI32 LAN2 (P1_AD[24])

00 0F 00 OSB4 SMB Bus, PCI Configuration Registers (P1_AD[31])

00 0F 01 OSB4 Ultra DMA IDE bus master (P1_AD[31])

01 02 NA PCI64 SLOT1 (P2_AD[18])

01 03 NA PCI 64 SLOT2 (P2_AD[19])

01 04 NA PCI 64 SCSI (P2_AD[20])

3.16.2 Interrupts

Table 19 lists the system interrupts for the SRMK2.

Device

Number

(hex)

Table 19: PCI Interrupt to OSB4 IRQ Input Mapping

OSB4 Input PCI Interrupt

PCIIRQ0 LAN1 IRQ#

PCIIRQ1 LAN2 IRQ#

PCIIRQ2 P1S1_INTAC# (PCI32 Slot1 Interrupts A & C)

PCIIRQ3 P1S1_INTBD# (PCI32 Slot1 Interrupts B & D)

PCIIRQ4 P1S2_INTAC# (PCI32 Slot2 Interrupts A & C)

PCIIRQ5 P1S2_INTBD# (PCI32 Slot2 Interrupts B & D)

PCIIRQ6 FP_IRQ# (Front Panel IRQ#)

PCIIRQ7 VID_IRQ# (Video IRQ#)

PCIIRQ8 SCSI_IRQA#

PCIIRQ9 SCSI_IRQB#

PCIIRQ10 P2S1_INTAC# (PCI64 Slot1 Interrupts A & C)

PCIIRQ11 P2S1_INTBD# (PCI64 Slot1 Interrupts B & D)

Function

Number

(hex)

Description

Intel® SRMK2 Internet Server Technical Product Specification 36

Page 37

PCIIRQ12 P2S2_INTAC# (PCI64 Slot2 Interrupts A & C)

PCIIRQ13 P2S2_INTBD# (PCI64 Slot2 Interrupts B & D)

PCIIRQ14 Not Used

PCIIRQ15 Not Used

3.16.3 SMI and NMI Routing

There are numerous SMI/NMI sources. SMI/NMI sources are routed either to OSB4 or SIO

GPI input pins. Software must configure the OSB4 and SIO GPI input pins to control whether the

corresponding events will generate SMI, NMI or wake up events to the processors. The

SMI/NMI sources on the SRMK2 are shown in Table 20. Note that some inputs are the wired

OR of several sources. Signal names are in parenthesis.

Table 20: SRMK2 SMI and NMI sources

SMI Source OSB4 Input Pin SIO Input Pin

Processor #0 IERR (IERR#0) GEVENT_0

Processor #1 IERR (IERR#1) GEVENT_1

Processor #0 Thermal Trip (THERMTRIP#0) GEVENT_2

Processor #1 Thermal Trip (THERMTRIP#0) GEVENT_3

CNB30LE Chipset PCI SERR# - used for ECC Errors (SALERT#) GEVENT_4

Wired OR of HECETA #1 & #2 INT output and LAN 1 & 2 SMBALERT

output (SMBALERT#)

Gluechip’s EXTSMI# output – used for +5VSB errors (EXTSMI#) GEVENT_6

Debug NMI from Front Panel or NMI jumper (DBG_NMI#) GEVENT_7

SIO SMI (SIO_SMI#) GEVENT_19

SIO WAKE UP (SIO_WAKEUP#) SIO_WAKEUP

32-bit PCI SERR (P1_SERR#) SERR#

64-bit PCI SERR (P2_SERR#) FRWP#

Wired OR of 32-bit PCI PME, External WOL, LAN1 PME, and LAN2 PME

(P1_PME#)

64-bit PCI PME (P2_PME#) GP16

Wake on Ring (WOR#) GP11

GEVENT_5

GEVNT_21

GP17

3.16.4 System Management Bus (SMB)

The SRMK2 baseboard supports a simple I2C compatible Bus to provide a method to manage

system resources. To implement this feature, the ServerWorks South Bridge device becomes the

master controller and communicates with several other devices in the system. Some of the

functions the processor can monitor though the SMB bus are the following: Fan Speed

(Tachometer), temperatures, voltage rails, LAN controllers, DIMM presence and size. Table 21

shows the address map of the various devices on the SM Bus.

Table 21: SMB Bus Address Map

Device Master/Slave I2C Address

OSB4 Master Controller N/A

LAN Controller 1 Slave :84

Intel® SRMK2 Internet Server Technical Product Specification 37

Page 38