Page 1

SPSH4 Server System

Technical Product Specification

Intel reference number 10736

Revision 1.11

March, 2003

Enterprise Platforms and Services Marketing

Page 2

Revision History SPSH4 Server System Technical Product Specification

Revision History

Date Revision

Number

6/21/01 0.5 Preliminary Draft for Review

8/20/02 1.0 Revisions to Roll to 1.0 for publication

1/2003 1.1 Revisions to include Adaptec U320 SCSI Controller 100 MHz support

March

2003

1.11 Corrected section 5.3.4 on page 45 to reflect 4Mb Video rather than 2 mb video

memory to be consistent with the SRSH4 TPS

Modifications

Revision 1.11

ii

Page 3

SPSH4 Server System Technical Product Specification Disclaimers

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express

or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel

assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property

right. Intel products are not intended for use in medical, life saving, or life sustaining

applications. Intel may make changes to specifications and product descriptions at any time,

without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked

"reserved" or "undefined." Intel reserves these for future definition and shall have no

responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not

finalize a design with this information. Revised information will be published when the product is

available. Verify with your local sales office that you have the latest datasheet before finalizing a

design.

The SPSH4 Server System may contain design defects or errors known as errata which may

cause the product to deviate from published specifications. Current characterized errata are

available on request.

This document and the software described in it is furnished under license and may only be used

or copied in accordance with the terms of the license. The information in this manual is

furnished for informational use only, is subject to change without notice, and should not be

construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or

liability for any errors or inaccuracies that may appear in this document or any software that may

be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a

retrieval system, or transmitted in any form or by any means without the express written consent

of Intel Corporation.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2001.

Revision 1.11

iii

Page 4

Table of Contents SPSH4 Server System Technical Product Specification

Table of Contents

1. Introduction ..........................................................................................................................1

2. SPSH4 Server Chassis Feature Overview.......................................................................... 2

2.1 Front Panel ......................................................................................................................5

2.2 Rear Features..................................................................................................................7

3. Physical Specifications .......................................................................................................9

3.1 SSH4 Boardset ..............................................................................................................11

3.2 Guidelines For Installing Memory in the SSH4 Server Board........................................ 14

4. Power supply Subsystem.................................................................................................. 15

4.1 Mechanical Dimensions................................................................................................. 18

4.2 Airflow Requirements..................................................................................................... 20

4.2.1 Over-Temperature Protection ..................................................................................20

4.2.2 Connectors and Pinouts........................................................................................... 20

4.2.3 AC Electrical Specifications .....................................................................................22

4.2.4 DC Output Specification........................................................................................... 25

4.2.5 Electrical Protection Circuits ....................................................................................32

4.2.6 Control Signals......................................................................................................... 33

4.3 Cooling Subsystem........................................................................................................ 38

4.3.1 Redundancy and Ambient Temperature Control...................................................... 38

4.3.2 Cooling Summary..................................................................................................... 39

5. Cables and Connectors ..................................................................................................... 40

5.1 Interconnect Block Diagram........................................................................................... 40

5.2 Cable and Interconnect Descriptions............................................................................. 41

5.3 Operator-Accessible Interconnects................................................................................ 42

5.3.1 Keyboard and Mouse Ports...................................................................................... 42

5.3.2 Serial Ports............................................................................................................... 43

5.3.3 Parallel Port.............................................................................................................. 44

5.3.4 Video Port ................................................................................................................45

5.3.5 Universal Serial Bus (USB) Interface ....................................................................... 45

5.3.6 ICMB Connectors..................................................................................................... 46

5.3.7 100/10 Ethernet Connector (LAN 1)......................................................................... 46

5.3.8 1000/100/10 Ethernet Connector (LAN 2)................................................................ 47

5.3.9 Internal SCA-2 HDD Connector ............................................................................... 47

Revision 1.11

iv

Page 5

SPSH4 Server System External Product Specification Table of Contents

5.3.10 External SCSI......................................................................................................... 49

5.3.11 AC Power Input ...................................................................................................... 50

6. SCSI Bay Boardset............................................................................................................. 51

6.1 Hot Swap Hard Drive Backplane ................................................................................... 51

6.1.1 Architectural Overview ............................................................................................. 52

6.2 Design Constraints and Assumptions............................................................................ 52

6.2.1 SCSI Bus Considerations......................................................................................... 52

6.3 Functional Description ................................................................................................... 53

6.3.1 Wide SCSI Connector .............................................................................................. 53

6.3.2 SCA-2 Connectors ................................................................................................... 53

6.3.3 SCSI Multi-ModeTermination ...................................................................................54

6.3.4 SCSI Interface.......................................................................................................... 54

6.3.5 Power Control ..........................................................................................................54

6.3.6 FET Short Protection................................................................................................ 54

6.3.7 Microcontroller.......................................................................................................... 55

6.3.8 Device SCSI ID ........................................................................................................ 55

6.3.9 Hard Drive Activity LED............................................................................................ 55

6.3.10 Hard Drive Fault LED ............................................................................................. 56

6.3.11 IMB (I2C bus).......................................................................................................... 56

6.3.12 Fan Support ...........................................................................................................56

6.3.13 Temperature........................................................................................................... 56

6.3.14 Serial EEPROM......................................................................................................56

6.4 Board Functions............................................................................................................. 57

6.4.1 Reset........................................................................................................................ 57

6.4.2 Microcontroller.......................................................................................................... 57

6.4.3 SCSI Controller ........................................................................................................ 59

6.4.4 Multi-Mode SCSI Termination ..................................................................................59

6.5 Memory Map.................................................................................................................. 59

6.5.1 Memory Map ............................................................................................................ 60

6.5.2 I/O Ports ................................................................................................................... 63

6.6 Programming Information .............................................................................................. 65

6.6.1 Firmware Support Requirements ............................................................................. 66

6.7 External Interface Specifications ...................................................................................66

6.7.1 Connector Specifications .........................................................................................66

6.7.2 SCSI Input Connector 68P....................................................................................... 67

Revision 1.11

Intel reference number 10736

v

Page 6

Table of Contents SPSH4 Server System Technical Product Specification

6.7.3 I2C Connector........................................................................................................... 69

6.7.4 Power Connector .....................................................................................................70

6.7.5 Fan 3-pin Connector ................................................................................................70

6.7.6 SAF-TE PCI Connector Interface............................................................................. 70

6.8 Cables............................................................................................................................ 73

6.8.1 Signal Cables ........................................................................................................... 73

6.8.2 Power Cables........................................................................................................... 73

6.9 Mechanical Specifications .............................................................................................73

7. System Boards ...................................................................................................................75

7.1 Power Distribution Board ...............................................................................................75

7.1.1 Board Layout............................................................................................................ 76

7.1.2 Connector Pinouts.................................................................................................... 76

7.2 Front Panel Board.......................................................................................................... 79

7.2.1 Board Layout............................................................................................................ 80

7.2.2 Connector Pinouts.................................................................................................... 81

7.3 Fan Distribution Board ................................................................................................... 83

7.3.1 Board Layout............................................................................................................ 83

7.3.2 Connector Pinouts.................................................................................................... 83

7.4 HPIB Board.................................................................................................................... 85

7.4.1 Board Layout............................................................................................................ 86

7.4.2 Connector Pinouts.................................................................................................... 86

7.5 ICMB Board ................................................................................................................... 87

7.5.1 Board Layout............................................................................................................ 87

7.5.2 Connector Pinouts.................................................................................................... 87

8. Hardware Configuration .................................................................................................... 89

8.1 System Configuration ....................................................................................................89

8.2 Spares / Accessories ..................................................................................................... 90

9. Product Regulatory Compliance Specifications .............................................................91

9.1 Product Safety Compliance ........................................................................................... 91

9.2 Product EMC Compliance ............................................................................................. 91

9.3 Regulatory Markings...................................................................................................... 92

9.4 Product Safety Markings................................................................................................ 93

9.5 Power supply Regulatory Agency Certifications ............................................................93

9.6 Regulatory Compliance Notices, Statements and Information ......................................94

9.6.1 USA FCC Verification Notice ...................................................................................94

Revision 1.11

vi

Page 7

SPSH4 Server System External Product Specification Table of Contents

9.6.2 Canada..................................................................................................................... 95

9.6.3 European Union ....................................................................................................... 95

9.6.4 Australia / New Zealand ........................................................................................... 95

9.6.5 Japan .......................................................................................................................95

9.6.6 Taiwan...................................................................................................................... 96

9.7 Replacing The Back Up Battery..................................................................................... 96

10. Environmental Specifications ........................................................................................... 97

11. Serviceability and Usability............................................................................................... 98

11.1 Mean Time to Repair.................................................................................................. 98

11.2 Special Usability Features.......................................................................................... 99

12. Index ......................................................................................................................................V

Revision 1.11

Intel reference number 10736

vii

Page 8

List of Figures SPSH4 Server System Technical Product Specification

List of Figures

Figure 1: Front View of Pedestal Configuration ............................................................................ 3

Figure 2: Front View of Rack Configuration .................................................................................. 3

Figure 3: Front View of System (Shown with Bezel Removed)..................................................... 4

Figure 4: Front Panel Details (Rack Bezel Shown)....................................................................... 5

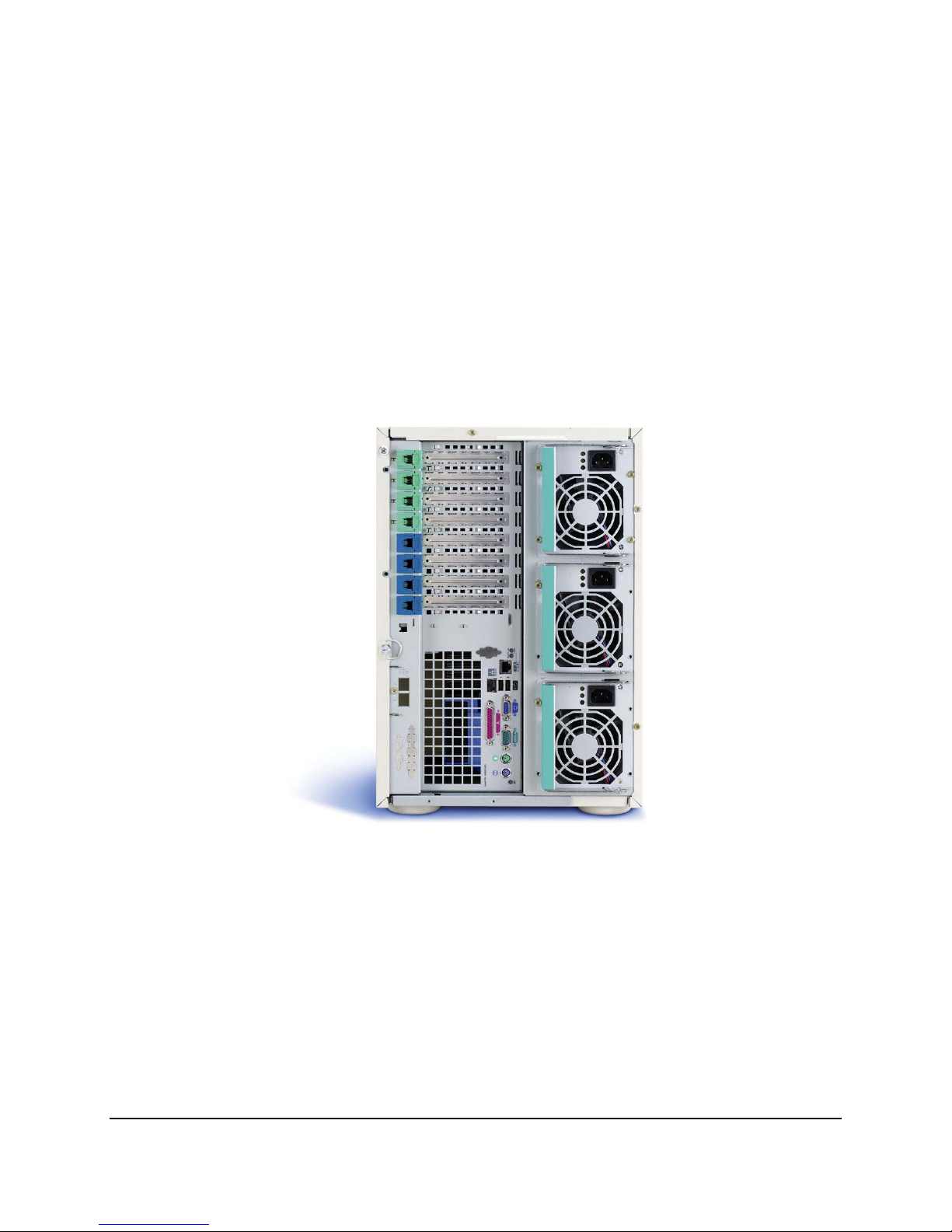

Figure 5: Rear View Of Chassis.................................................................................................... 7

Figure 6: SPSH4 Server System Photograph with Side Panels and Front Panel Removed ......10

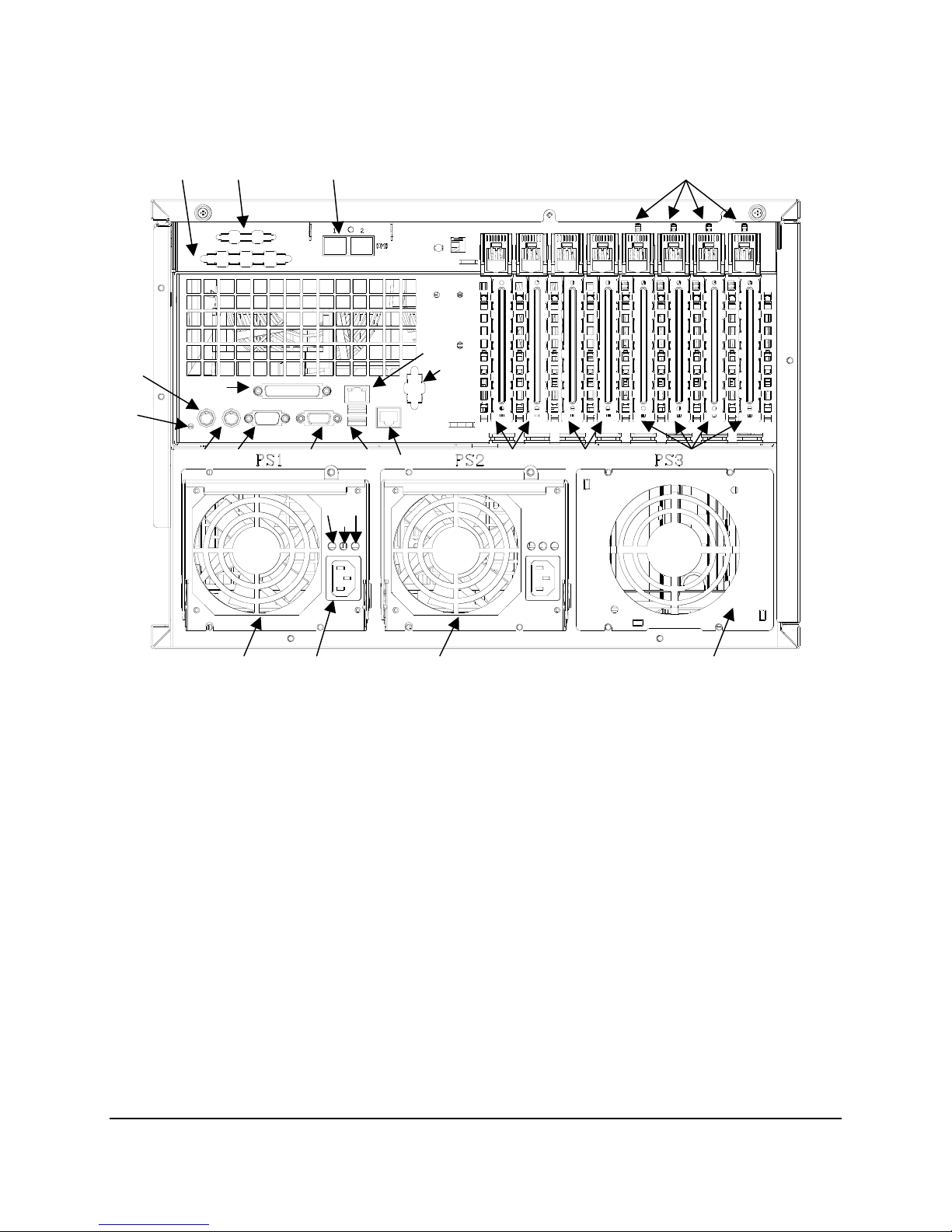

Figure 7: Functional Block Diagram of SSH4 Boardset ..............................................................11

Figure 8: SPSH4 Power supply ..................................................................................................16

Figure 9: Rear view of SPSH4 Power Supply Bay...................................................................... 17

Figure 10: SPSH4 Power supply Outline Drawing...................................................................... 19

Figure 11: Connector Pin Locations............................................................................................ 21

Figure 12: Inrush Curve ..............................................................................................................25

Figure 13: Differential Noise Test Setup ..................................................................................... 29

Figure 14: Output Voltage Timing ............................................................................................... 30

Figure 15: Turn On/Off Timing .................................................................................................... 31

Figure 16: Fan Bay (Shown with all Fan Banks Installed) ..........................................................38

Figure 17: SPSH4 System Interconnect Block Diagram............................................................. 40

Figure 18: SCA-2 Connector....................................................................................................... 48

Figure 19: AC Power Input Connector ........................................................................................50

Figure 20: Functional Block Diagram.......................................................................................... 53

Figure 21: Microcontroller Memory Map ..................................................................................... 60

Figure 22: SCSI Input connector 68P Non-Shielded ..................................................................67

Figure 23: SCA-2 Connector 80P ............................................................................................... 68

Figure 24: Hotswap Backplane Mechanical Drawing.................................................................. 73

Figure 25: SAF-TE Addin Card Mechanical Drawing.................................................................. 74

Figure 26: Fan Board Layout ......................................................................................................76

Figure 27: Power supply Mating Connector Pin Locations ......................................................... 77

Figure 28: Fan Board Layout ......................................................................................................80

Figure 29: Fan Board Layout ......................................................................................................83

Figure 30: HPIB Board Layout ....................................................................................................86

Figure 31: ICMB Board Layout ...................................................................................................87

Revision 1.11

viii

Page 9

SPSH4 Server System External Product Specification List of Tables

List of Tables

Table 1: Front Panel Features ...................................................................................................... 6

Table 2: System Features - Rear..................................................................................................8

Table 3: Physical Specifications ...................................................................................................9

Table 4: LED Indicators ..............................................................................................................18

Table 5: Airflow Requirements....................................................................................................20

Table 6: Signal Descriptions .......................................................................................................21

Table 7: Output Connector Pin-out ............................................................................................. 21

Table 8: AC Input Voltage Rating ...............................................................................................22

Table 9: AC Line Sag Transient Performance ............................................................................ 23

Table 10: AC Line Surge Transient Performance .......................................................................23

Table 11: Electrostatic Discharge, IEC 801-2/IEC 1000-4-2....................................................... 23

Table 12: Electrical Fast Transient/Burst, IEC 801-4/IEC 1000-4-4 ...........................................23

Table 13: Radiated Immunity, IEC 801-3/IEC1000-4-3 .............................................................. 23

Table 14: Surge Immunity IEC 1000-4-5 .................................................................................... 24

Table 15: Ring Wave ..................................................................................................................24

Table 16: DC Output Voltage Limits ...........................................................................................26

Table 17: 600W Load Ratings ....................................................................................................27

Table 18: Total System Load at Line AC Input ........................................................................... 27

Table 19: Absolute Worst Case System Power Budget.............................................................. 27

Table 20: Remote Sense Drops.................................................................................................. 28

Table 21: Dynamic Tolerance Requirement ...............................................................................28

Table 22: Ripple and Noise......................................................................................................... 29

Table 23: Output Voltage Timing ................................................................................................ 30

Table 24: Turn On/Off Timing ..................................................................................................... 30

Table 25: Over-Voltage Limits ....................................................................................................32

Table 26: Over Current Protection Limits.................................................................................... 32

Table 27: PSON Signal Characteristic........................................................................................ 33

Table 28: PWOK Signal Characteristics ..................................................................................... 33

Table 29: PSKILL Signal Characteristics .................................................................................... 34

Table 30: FAIL Signal Characteristics......................................................................................... 35

Table 31: PRFL Signal Characteristics ....................................................................................... 35

Table 32: PRESENT# Signal Characteristics .............................................................................. 36

Revision 1.11

Intel reference number 10736

ix

Page 10

List of Tables SPSH4 Server System Technical Product Specification

Table 33: Fan Speed Control......................................................................................................36

Table 34: Pins for Power supply Connector FRU Information .................................................... 37

Table 35: System Interconnect Descriptions ..............................................................................41

Table 36: Keyboard and Mouse Ports ........................................................................................42

Table 37: Serial Port A Connector .............................................................................................. 43

Table 38: Parallel Port Connector...............................................................................................44

Table 39: Video Connector .........................................................................................................45

Table 40: Dual USB Connector................................................................................................... 45

Table 41: ICMB Connector .........................................................................................................46

Table 42: Ethernet Connector.....................................................................................................46

Table 43: Ethernet Connector.....................................................................................................47

Table 44: SCA-2 Connector........................................................................................................47

Table 45: SCSI Connector .......................................................................................................... 49

Table 46: SCSI ID Assignments .................................................................................................55

Table 47: Hard Drive Activity LED ..............................................................................................55

Table 48: Hard Drive Fault LED..................................................................................................56

Table 49: Drive Power Status Byte Format................................................................................. 61

Table 50: Fault Indicator Control Byte Format ............................................................................62

Table 51: Drive Presence Status Byte Format............................................................................ 62

Table 52: P1 Functions ............................................................................................................... 64

Table 53: P3 Functions ............................................................................................................... 65

Table 54: Connector Specifications ............................................................................................ 66

Table 55: SCSI Input connector (J1D1) ...................................................................................... 67

Table 56: SCA-2 Connectors (J3E1, J3D1, J3C1, J3B1, J3A1) ................................................. 68

Table 57: I2C Connector (J2A1) .................................................................................................. 69

Table 58: Power Connector (J4A1, J3A2) ..................................................................................70

Table 59: Fan Connector ............................................................................................................70

Table 60: PCI connector (J5C1) .................................................................................................71

Table 61: Signal Pins and Power Blades (PS1, PS2, PS3) ........................................................76

Table 62: Main Power #1 Connector (P5)................................................................................... 77

Table 63: Main Power #2 Connector (P4)................................................................................... 77

Table 64: Main Power Control Connector (P6) ...........................................................................78

Table 65: Fan/Peripheral Power Connector (P1)........................................................................ 78

Table 66: Primary SCSI Bay Power Connector (P2)................................................................... 78

Table 67: Seconday SCSI Bay Power Connector (P3)............................................................... 78

Revision 1.11

x

Page 11

SPSH4 Server System External Product Specification List of Tables

Table 68: Front Panel Signal Connector (P5) ............................................................................. 81

Table 69: USB Port 3 Input Connector (P7)................................................................................ 81

Table 70: USB Port 3 (P2) ..........................................................................................................81

Table 71: Serial Port B Input Connector (P6) .............................................................................82

Table 72: RJ45 Serial Port B (P1)...............................................................................................82

Table 73: Chassis Intrusion Connector 1 (P4) ............................................................................ 82

Table 74: Chassis Intrusion Connector 2 (P3) ............................................................................ 82

Table 75: Power Connector (P5) ................................................................................................83

Table 76: Front 120mm Fan Bank Connector (P1)..................................................................... 84

Table 77: Front 80mm Fan Connector (P2) ................................................................................84

Table 78: Rear 120mm Fan Bank Connector (P3) ..................................................................... 84

Table 79: Rear 80mm Fan Connector (P4)................................................................................. 84

Table 80: Fan Signal Connector (P6) .........................................................................................85

Table 81: HPIB Signal Connector (P1) ....................................................................................... 86

Table 82: Keyed RJ45 ICMB Port Connectors (P1 & P2)........................................................... 87

Table 83: ICMB Signal Connector to Baseboard (P3) ................................................................ 88

Table 84: System Configuration..................................................................................................89

Table 85: Spare / Accessory List ................................................................................................90

Table 86: Product Safety Compliance ........................................................................................91

Table 87: Product EMC Compliance........................................................................................... 91

Table 88: Regulatory Markings ...................................................................................................92

Table 89: Product Safety Markings............................................................................................. 93

Table 90: Environmental Specifications Summary .....................................................................97

Revision 1.11

Intel reference number 10736

xi

Page 12

Page 13

SPSH4 Server SystemTechnical Product Specification

1. Introduction

This product specification details the features of the SPSH4 server system. Low cost, time to

market, modularity, and utilization for multiple configurations are primary considerations in the

design. The chassis has user friendly features and is accessible and serviceable.

The SPSH4 server system also incorporates features for high availablity servers. This includes

power and cooling systems with optional redundancy, hot swap or easy to replace fans hot-plug

PCI slots, and a mass storage system with hot-swappable hard drives. These are the key

components for increasing availability of the server. Since the fans and power supplies typically

have the lowest Mean Time Between Failure (MTBF) specifications, the optional redundancy of

these components will permit the system to continue to operate with a failed fan or power

supply. With the use of RAID technology the system can continue to operate with hard drive

failures The hot-plug hard drives allow a failed hard drive to be replaced while the system

continues to operate.

This product specification details the following:

SPSH4 chassis features.

Power supply subsystem.

Chassis cooling.

Front panel.

System boards.

I/O and interconnects.

System configuration.

System Certifications.

Environmental limits.

Reliability, serviceability, and availability.

Revision 1.11

Intel reference number 10736

1

Page 14

SPSH4 Server Chassis Feature Overview SPSH4 Server System External Product Specification

2. SPSH4 Server Chassis Feature Overview

The SPSH4 MP server Chassis is 12.22 inches wide, 18.06 inches high, and 25.25 inches

deep. The chassis is designed to be modular with a base unit with two easily removable units,

one to hold the front panel and drive bays (C-tilt) and one to hold the baseboard, processor

board and I/O panels (E-Bay). The Base section is U shaped and holds the power supplies and

power distribution board. The E-bay drops in at the rear of the base unit and the C-tilt drops in

from the front. The two captive screws in the front cover fasten both the E-bay and the C-tilt to

the base unit. The E-bay fans are plugged in to a hot-swap fan holder and installed above the

drives and infron to the E-bay. Three bays are supplied in the back of the chassis base unit for

power supplies.

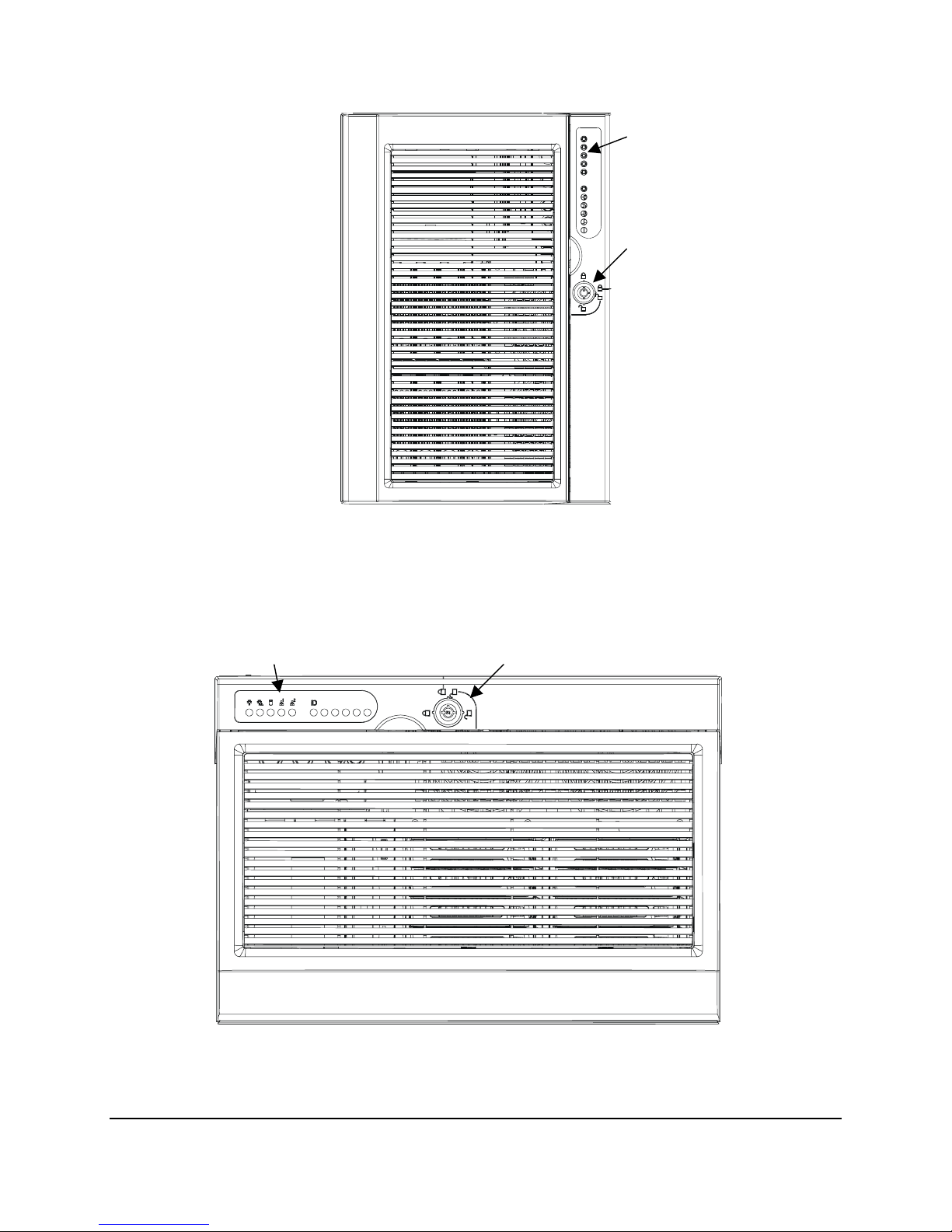

Figure 1 and Figure 2 show the system front view with both rack and pedestal bezel attached.

The rack bezel has the standard color specific GE Cycoloy C6600-701 black. The pedestal

bezel comes in two colors and has the standard color specific of GE Cycoloy C6600-701 black

or GE Cycoloy C6600-BR7026 dusty beige. Only front panel status LEDs and chassis security

lock are visible without opening bezel door. Figure 3 shows the system front view with the front

bezel removed. Opening the front bezel door provides access to the following:

• Front panel control buttons

• One USB and one serial port

• Three 5¼” device bays (one 5¼” CD-ROM installed)

• One 3½” bay for a 1” floppy drive

• Two SCSI bays holding up to ten 1” hard drives

Revision 1.11

2

Page 15

SPSH4 Server SystemTechnical Product Specification

Front Panel LEDs

Security Lock

Figure 1: Front View of Pedestal Configuration

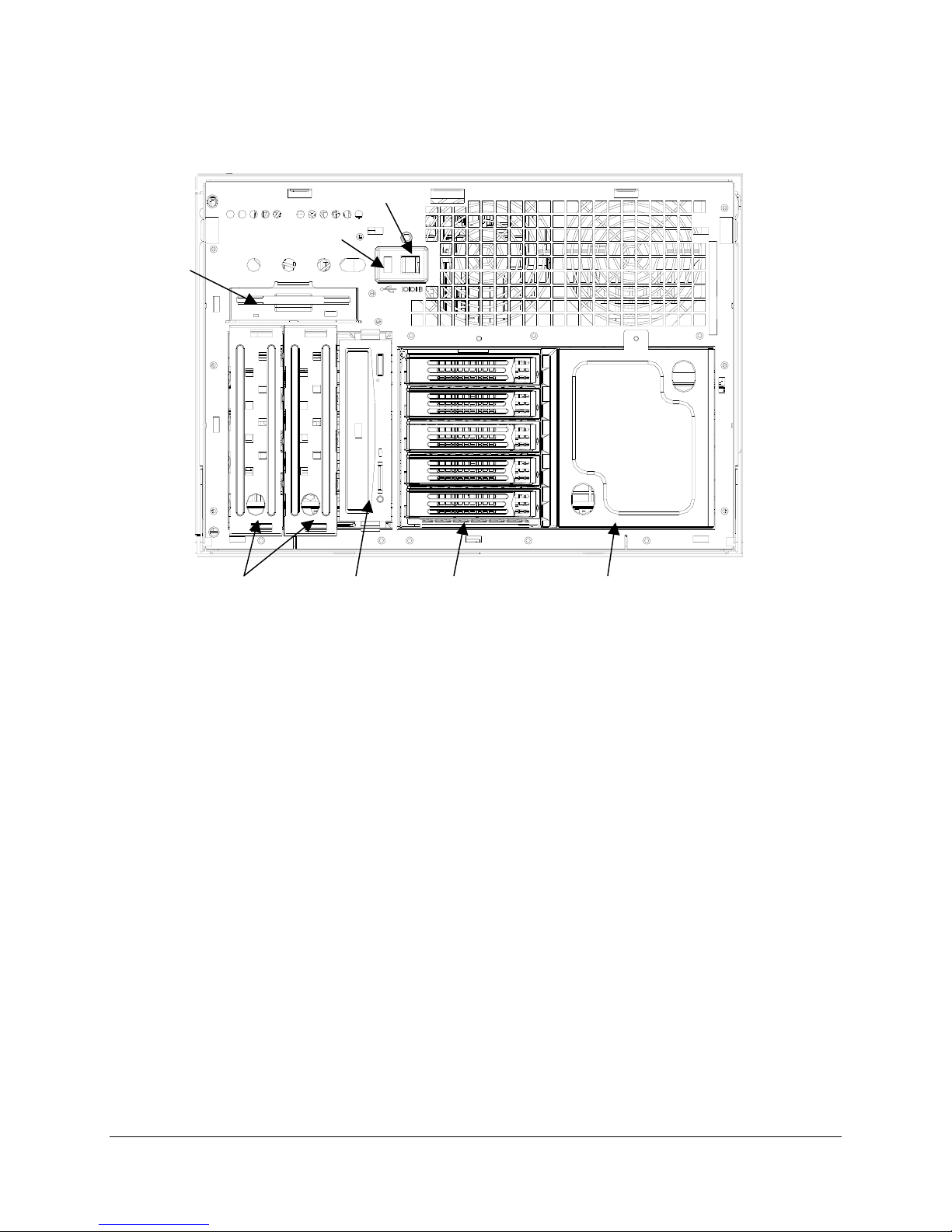

Front Panel LEDs

Security Lock

Figure 2: Front View of Rack Configuration

Revision 1.11

Intel reference number 10736

3

Page 16

SPSH4 Server Chassis Feature Overview SPSH4 Server System External Product Specification

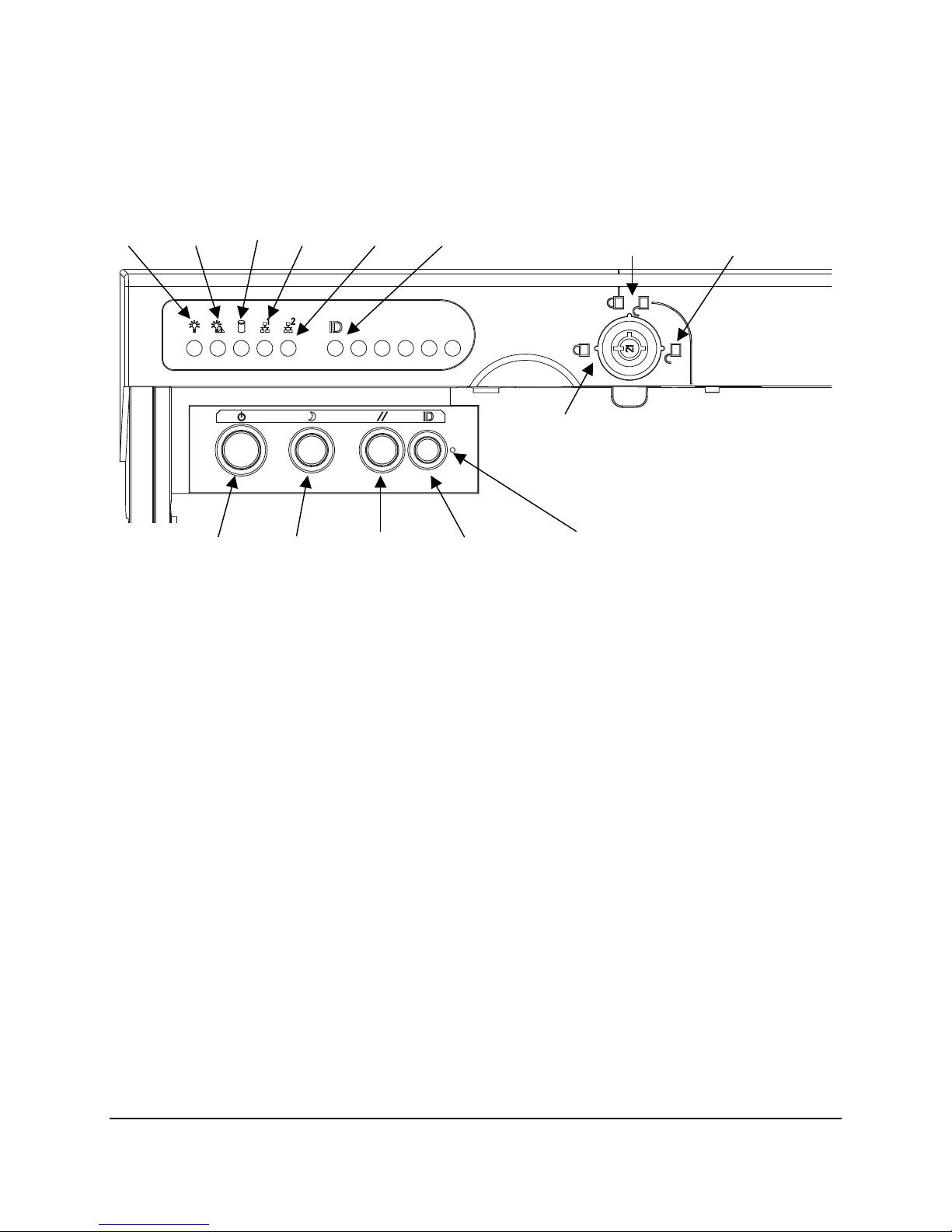

A

Serial Port B

USB Port 3

Floppy

5¼“ Peripheral Bays Primary Hard Drive Bay

CD-ROM

Figure 3: Front View of System (Shown with Bezel Removed)

vailable Secondary

Hard Drive Bay

Revision 1.11

4

Page 17

SPSH4 Server SystemTechnical Product Specification

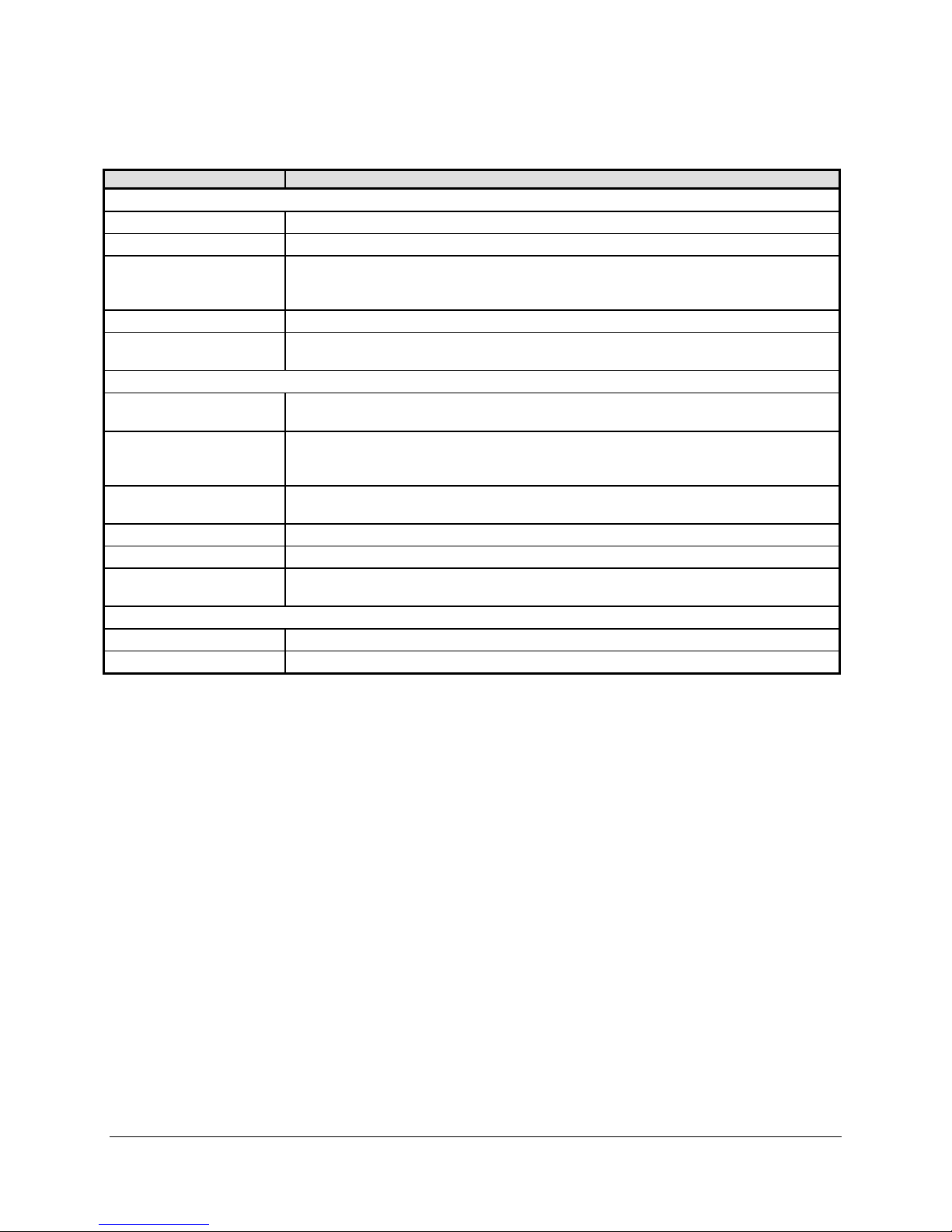

2.1 Front Panel

The front panel contains system control switches and status indicators. Front panel features are

shown in Figure 4 and are described in Table.

Power

LED

Power Button

Fault

LED

HDD

LED

Sleep Button

LAN1

LED

Figure 4: Front Panel Details (Rack Bezel Shown)

LAN2

LED

Reset Button

Chassis

ID LED

Bezel & Top Cover Locked Position

Chassis ID Button

Top Cover Locked &

Bezel Locked

Position

NMI Switch

Bezel & Top Cover

Unlocked Position

Revision 1.11

Intel reference number 10736

5

Page 18

SPSH4 Server Chassis Feature Overview SPSH4 Server System External Product Specification

Table 1 Front Panel Features

Feature Description

Front Panel Button

Reset Resets system power.

Sleep Activates the sleep mode.

NMI (Hidden Behind

Bezel)

Power Toggles system power.

Chassis ID Activates the chassis LED on both the front panel board and on the baseboard at the

Front Panel LEDs

Chassis ID (blue) Indicates that matching chassis ID LED will be present at rear panel of chassis to ease

Power (green) When continuously lit, indicates the presence of DC power in the server. The LED

HDD Activity/Fault

(green/amber)

LAN1 (green) Indicates 100/10Mb Ethernet port activity.

LAN2 (green) Indicates 1000/100/10Mb Ethernet port activity.

System Status/Fault

(green/amber)

Front Panel IO Connectors

USB Connector USB port 3

RJ45 Connector Serial port B.

Causes a non-maskable interrupt. This switch is located behind the front bezel door to

prevent inadvertent activation. The front bezel door must be opened to access this

switch. A narrow tool is required to activate the switch.

rear panel of the chassis.

identification when servicing rear of system in a rack.

goes out when the power is turned off or the power source is disrupted. When flashing

it indicates the system is in ACPI sleep mode.

Indicates any system hard drive activity or fault condition.

Indicates system status or fault condition.

Revision 1.11

6

Page 19

SPSH4 Server SystemTechnical Product Specification

G

R

2.2 Rear Features

X

U

B A

C

O

P

D

V W T

SQ

FE

L M N

J K I H

Figure 5: Rear View Of Chassis

Revision 1.11

Intel reference number 10736

7

Page 20

SPSH4 Server Chassis Feature Overview SPSH4 Server System External Product Specification

Table 1: System Features - Rear

Item Description

A Optional External VHDCI SCSI port

B Optional External SCSI3 port

C Optional ICMB connector ports, keyed RJ45 8-pin connector

D Hot Plug PCI-X Power/Fault LEDs

E Two non hot plug 32-bit, 33 MHz PCI add-in card slots

F Two non hot plug 64-bit, 100 MHz PCI-X add-in card slots

G Four hot plug 64-bit, 100 MHz PCI-X add-in card slots

H Filler panel for power bay 3

I Power supply 2

J Power supply IEC320-C14 AC inlet

K Power supply 1

L Power supply on LED (Green)

M Power supply predictive failure LED (Amber)

N Power supply failure LED (Amber)

O LAN1 100/10 RJ45 connector

P Knockout for optional serial port B, 9-pin RS-232 connector

Q LAN2 Gigabit port (1000/100/10)

R USB ports 1 (upper) and 2 (lower), 4-pin connectors

S Video connector

T Serial port A, 9-pin RS-232 connector

U PS/2-compatible parallel port (LPT), 25-pin bi-directional subminiature D connector

V PS/2-compatible mouse port, 6-pin connector

W PS/2-compatible keyboard port, 6-pin connector

X Chassis ID LED (Blue)

Revision 1.11

8

Page 21

SPSH4 Server SystemTechnical Product Specification

3. Physical Specifications

Table 2 describes the physical specifications of the SPSH4 system.

Table 2: Physical Specifications

Specification Black or Beige

Pedestal Value

Height 18.06 inches with feet 7U

Width 12.22 inches Fits 19” standard rack

Depth 25.25 inches 25.25 inches

Clearance Front 3 inches 3 inches

Clearance Rear 4.5 inches 4.5 inches

Clearance Side 0 inches 0 inches

Weight 90 lbs. minumum / 125 lbs.

maximum configuration

Heat Output 3686 BTU/hr (typical) 3686 BTU/hr (typical)

96 lbs. minumum / 125 lb.

Maximum configuration

Rack

Value

Revision 1.11

Intel reference number 10736

9

Page 22

Physical Specifications SPSH4 Server System External Product Specification

Figure 6: SPSH4 Server System Photograph with Side Panels and Front Panel Removed

Revision 1.11

10

Page 23

SPSH4 Server SystemTechnical Product Specification

3.1 SSH4 Boardset

This section highlights the main features of the SSH4 baseboard, memory board and processor

board Refer to the SSH4 Baseboard, Processor Board and Memory Module Technical Product

Specification for a detailed description of the SSH4 baseboard.

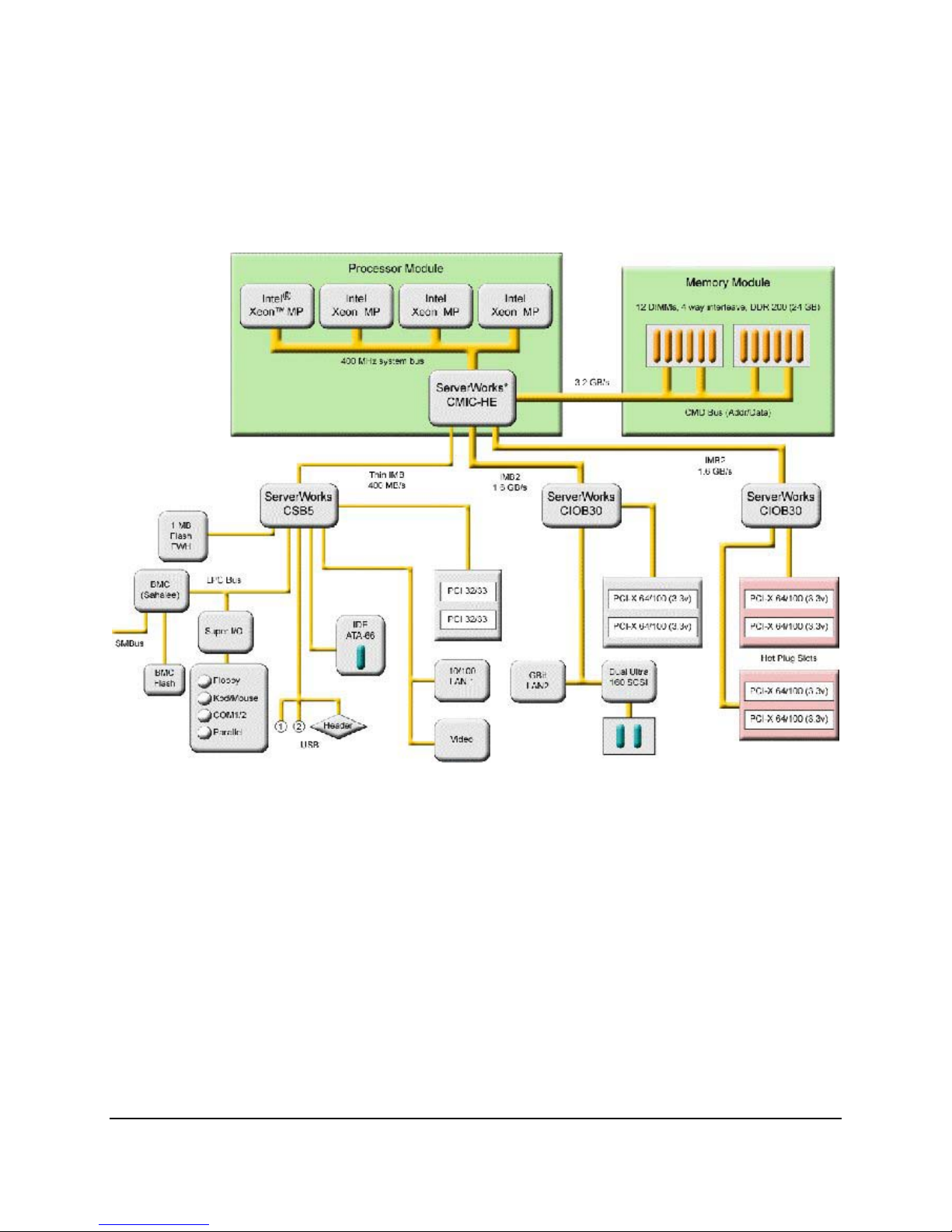

Figure 7: Functional Block Diagram of SSH4 Boardset

The SSH4 boardset is designed around the Intel® MP Xeon™ processor and the ServerWorks

*

ServerSet* IV Grand Champion High End (GCHE) chipset. This combination provides the basis

for a high performance system with leading edge processor, memory, and I/O performance.

The SSH4 baseboard architecture supports quad processing operation using Intel Intel MP

Xeon processors. It also provides eight industry standard PCI expansion slots supporting a

mixture of 32-bit, 33MHz (two), and 64-bit, 100/66 MHz (six) slots. The baseboard includes an

array of embedded I/O devices, see figure 8 and table 4 below

Revision 1.11

Intel reference number 10736

11

Page 24

Physical Specifications SPSH4 Server System External Product Specification

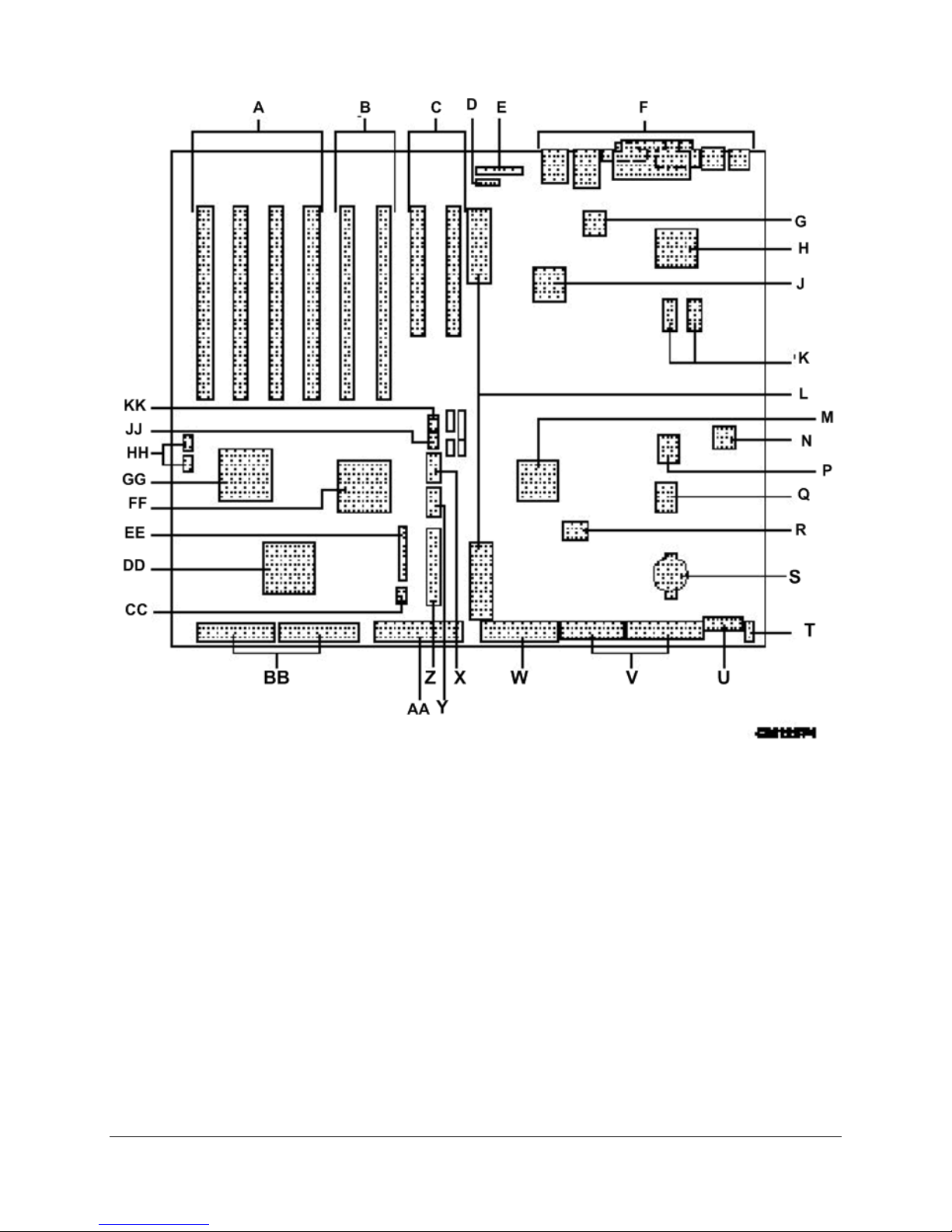

Figure 8 SSH4 Baseboard layout

Revision 1.11

12

Page 25

SPSH4 Server SystemTechnical Product Specification

Table 4 SSH4 Baseboard Components

Key Component Key Component

A PCI bus 64 bit, 100 MHz, Hot Plug T Chassis Intrusion Detect connector (P36)

B PCI bus 64 bit, 100 MHz, Non-Hot Plug U 14-pin Power Control connector (P35)

C PCI bus 32 bit, 33 MHz, Non-Hot Plug V 24-pin Power connector (P32)

D ICMB connector (P24) W 20-pin Power connector (P28)

E HPIB connector (P23) X Serial port B connector (P17)

F Back Panel I/O connectors) Y USB #3 Header (P18)

G Intel 82550 Ethernet controller Z Front Panel Header (P19)

H ATI* Rage* XL 2D/3D graphics accelerator AA IDE Connector (P13)

J Intel 82544 Ethernet controller BB SCSI LVD connectors (P4 and P7)

K Video RAM (VRAM) (4 MB total) CC IPMB connector (P12)

L Processor board connectors (P21 and P22) DD AIC7899 or AIC 7902 SCSI controller

M ServerWorks South Bridge Controller (CSB5) EE Fan connector (P11)

N BMC (Sahalee) component FF ServerWorks PCI-X Bus Bridge Controller (CIOB30)

P BIOS Flash component GG ServerWorks PCI-X Bus Bridge Controller (CIOB30)

Q PC87417 Super I/O controller HH RAID LED connectors (P1 and P2)

R BMC Flash component JJ HSBP connector (P16)

S Battery KK HSBP connector (P15)

The SSH4 memory subsystem consists of a single memory expansion board. This board

supports up to 12 DDR registered ECC SDRAM memory modules. The SSH4 baseboard

implementation in SPSH4 server supports both stacked and unstacked memory modules for up

to 24 GB of system memory.

The SSH4 boardset provides the following features:

• Three interleaved memory banks.

• Four 184 pin DIMMS per bank.

• Banks must be populated in order.

• Single bit error correction – If a single-bit error is detected, the ECC logic generates a new

Qword with a pattern that corresponds to the originally received 8-bit ECC parity code and

returned to the requestor (the processor or the PCI master)

• Multi Bit error detection – Additional errors within the same Qword constitute a multibit error

which may be unrecoverable. In the case of a multi-bit error, a non-maskable interrupt (NMI)

is issued that instructs the system to shut down to avoid data corruption. ( multibit errors are

very rare ).

• Memory Scrubbing – Error correction is performed on data being read from memory. The

correction is the passed to the requestor and at the same time is “scrubbed” or corrected in

Revision 1.11

Intel reference number 10736

13

Page 26

Physical Specifications SPSH4 Server System External Product Specification

main memory. Memory scrubbing prevents the accumulation of single –bit errors in main

memory tha would become unrecoverable mult-bit errors.

• Chipkill* - Chipkill is the ability of the memory system to wothstand a mult-bit failure within

DRAM device, including a failure that causes incorrect data on all bits of the device.

Figure 9 SSH4 Memory Module

3.2 Guidelines For Installing Memory in the SSH4 Server Board.

• Install only memory modules validated with this particular board. Refer to the Tested

Hardware and Operating System List and/or Http:// support.intel.com.

• Bank 1 must be populated with Dimms first. See figure 9 above.

• All four Dimms within a bank must be identical

• Baseboard Management Controller (BMC) providing monitoring, alerting, and logging of

critical system information obtained from embedded sensors on baseboard

• 8 megabit Flash device for system BIOS

• Three externally accessible USB ports; two at rear bulkhead and one at front panel

• One IDE connector, supporting up to two ATA 66 compatible devices

Revision 1.11

14

Page 27

SPSH4 Server SystemTechnical Product Specification

4. Power supply Subsystem

This section defines the features and functionality of the SSI compliant 600 watt power supply,

a universal input switching power supply. The power supplies are located in the power supply

bay mounted near the rear of the chassis. The system may be configured either with two 600 W

power supplies in a non-redundant configuration, or three 600 W power supplies for a

redundant power (2 + 1) configuration. Each power supply requires an individual power cord.

When the system is configured with three power supplies the following features are supported:

• The user can replace a failed power supply without interrupting system functionality under

any loading condition.

• AC power to one of the power cords can be interrupted without loss of functionality.

Power from the power supply subsystem is carried to internal system boards and peripheral

devices via discrete cables. Two 600 watt power supplies are capable of handling the worst

case power requirements for a fully configured SPSH4 system. This includes four 75 watt Intel

Xeon – MP processors, 24 GB of memory and ten hard drives at 20 watts per drive. Figure 8

shows the SPSH4 power supply.

Revision 1.11

Intel reference number 10736

15

Page 28

Power supply Subsystem SPSH4 Server System External Product Specification

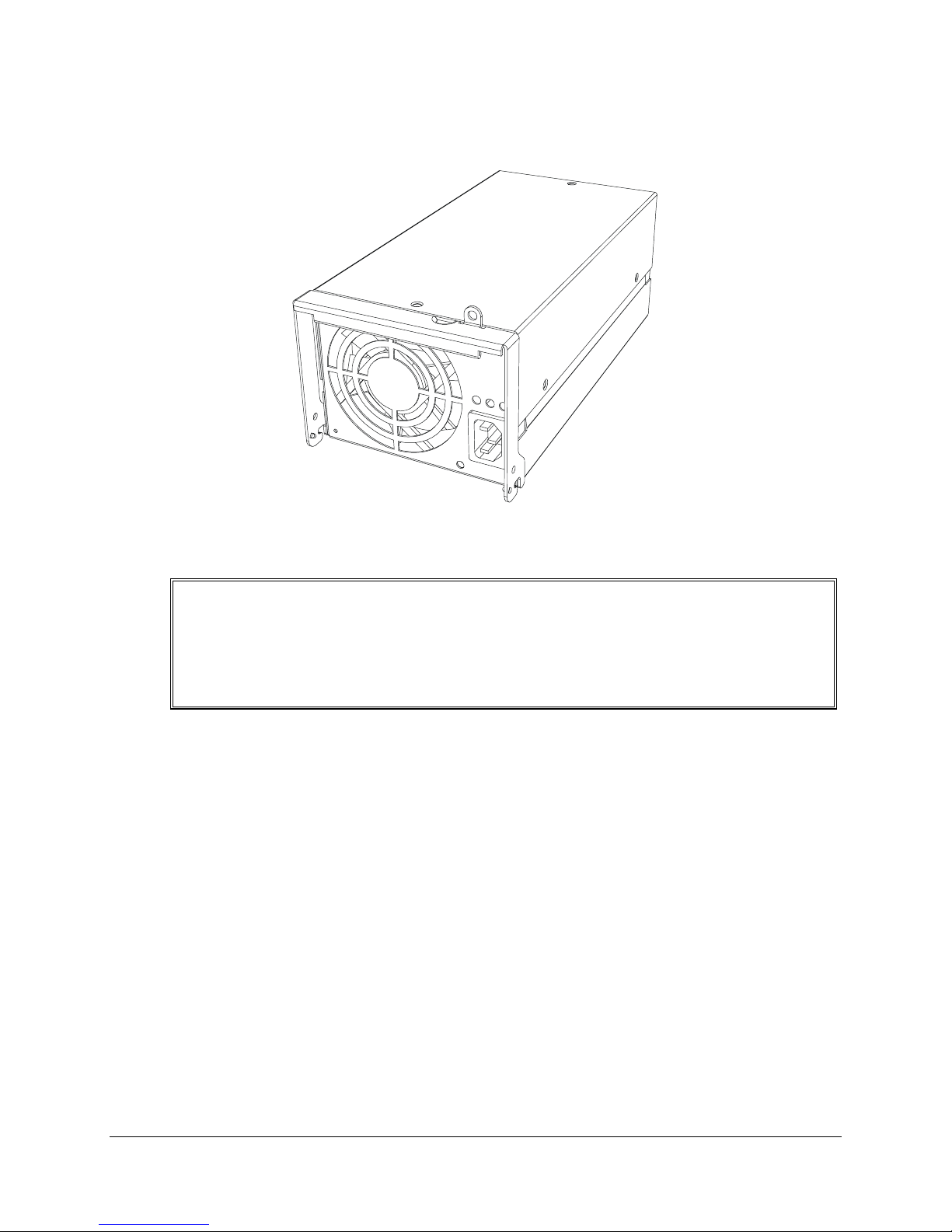

Figure 8: SPSH4 Power supply

!WARNING!

The total power requirement for the SPSH4 server system exceeds the

240VA energy hazard limit that defines an operator accessible area. As a

result, only qualified service personnel should access the processor,

memory, and non-hot plug I/O areas on the system baseboard while the

system is energized.

The following are the main features of the power supply subsystem:

• 1140 W output capability for two or three power supplies in full AC input voltage range

• Up to three 600 watt PFC power factor correcting power supplies for 2+1 power

redundancy

• Power good indication LED

• Predictive failure warning LED

• Failure warning LED

• Internal cooling fans with multi-speed capability

• Remote sense of +3.3V, +5V, and +12V outputs

• AC_OK circuitry for brown out protection

• Built-in load sharing capability

• Built-in overloading protection capability

• On board field replaceable unit (FRU) information for each module

2

C interface for server management functions

• I

Revision 1.11

16

Page 29

SPSH4 Server SystemTechnical Product Specification

• Integral handle for insertion/extraction

• Separate power cords for AC redundancy

The power supplies are populated in the chassis in a specific order as viewed from the rear of

the server system. See Figure 9. For a rack configuration, the power supplies are installed from

left to right. In a pedestal configuration the modules are installed from the bottom to the top. All

of the power supplies implement blind mating connectors for easy installation. Each power

supply implements two AC input fuses rated at 250V/15A, one for line and one neutral. Power

supplies are not required to be on the same AC power phase. The power supply is held to the

chassis frame with four 6-32 screws. These four screws and the AC cord must be removed to

hot swap the power supply.

Figure 9: Rear view of SPSH4 Power Supply Bay

The power supply has four externally enabled outputs: +12V,+5V,+3.3V,-12V, and one +5VSB

(standby) output. The +5VSB standby output is present whenever AC power is applied to any

single power supply. The power supply has a minimum efficiency of 60% to its DC output pins at

maximum load currents at rated nominal input voltages and frequencies.

Several LEDs on each power supply can be viewed from the rear of the server system. These

indicate the power state for that particular module. Looking at the system from rear of the power

supply, from left to right the LEDs are power, predictive fail, and fail.

Revision 1.11

Intel reference number 10736

17

Page 30

Power supply Subsystem SPSH4 Server System External Product Specification

• The power LED is green and blinks to indicate that AC is applied to the power supply and

+5VSB standby output voltage is available. This LED will turn a solid green to indicate the

power supply is on and all the power output voltages are available.

• The predictive fail LED blinks amber LED and indicates the power supply will fail in the near

future due to a poorly performing fan.

• The fail LED is amber and indicates that the power supply has experienced a failure of some

type.

When the power supply configuration changes, the SDR utility must be run so that server

management will properly monitor the new configuration.

A power LED on the front panel, labeled PWR, is green when power is applied to the system.

Table 3 describes the conditions of the LEDs for the power supply.

Table 3: LED Indicators

Power supply LEDs

Power supply Condition Power LED

(green)

No AC power to all PSU OFF OFF OFF

No AC power to this PSU only OFF OFF ON

AC present / Standby Outputs On Blinking OFF OFF

Power supply DC outputs ON and OK ON OFF OFF

Power supply failure OFF OFF ON

Current limit ON OFF Blinking

Predictive failure ON Blinking/Latched OFF

Predictive Fail LED

(amber)

Fail LED

(amber)

4.1 Mechanical Dimensions

Mechanical drawings and dimensions, in millimeters, for the power supply are shown in the

Figure 10 below. The power supply has a handle that pivots to assist insertion and extraction

and provides retention.

Revision 1.11

18

Page 31

SPSH4 Server SystemTechnical Product Specification

Figure 10: SPSH4 Power supply Outline Drawing

Revision 1.11

Intel reference number 10736

19

Page 32

Power supply Subsystem SPSH4 Server System External Product Specification

4.2 Airflow Requirements

Airflow enters the power supply at the DC connector face and is exhausted at the handle face.

Fan speed is controlled by the server system via the FANC signal to the power supply. The

power supply may override the FANC signal and operate the fan at HIGH speed if the

conditions of the power supply exceed those specified in Table 4. The minimum airflow required

by the power supply for high and low intake temperatures are shown in Table 4 also.

Table 4: Airflow Requirements

Item Description Minimum CFM

High Ambient Temperature Airflow through power supply;

max load, T

Low Ambient Temperature Airflow through power supply;

max load, T

=50°C, 5000 ft elevation

intake

=35°C, 5000 ft elevation

intake

4.2.1 Over-Temperature Protection

The power supply is protected against over temperature conditions caused by loss of fan

cooling or excessive ambient temperature. In the event of an OTP condition, the power supply is

shutdown. When the power supply temperature returns to within specified limits, the power

supply will automatically restore power.

21

17

The power supply sends an alert to the system of the OTP condition via the power supply FAIL

signal and the amber FAIL LED at the rear of the failed power supply is illuminated. When

temperatures read by the over temperature sensors in power supply return to within the normal

operating range, DC power is automatically restored. The power supply has built in hysteresis

circuits to prevent the power supply from oscillating on and off due to over temperature recovery

conditions.

4.2.2 Connectors and Pinouts

4.2.2.1 AC Inlet

The power supply AC inlet is an IEC320 C-14 receptacle. The AC power pins and wiring prior to

the protective fuse(s) have a peak current rating higher than the peak inrush current or

maximum fault current drawn by the power subsystem. The safety ground pin of the power

supply is the first pin to connect and the last to disconnect when the AC cord is inserted or

removed from the power subsystem housing.

4.2.2.2 DC Output Connector

The blind-mate DC output connector is the interface to the server system for output voltages,

control signals, and alarm signals. Connector pin descriptions and assignments are listed in

Table 5 and Table 6. Pin A6 is shortened to disabling power supply just prior to disconnecting

the DC output connector during a hot swap operation. The connector is keyed to the power

supply by the positioning of the guide/keying pins on either side of the connector. The keying

location for the connector is A1.

Revision 1.11

20

Page 33

SPSH4 Server SystemTechnical Product Specification

Table 5: Signal Descriptions

Signal Description Signal Description Signal Description

12LS 12V load share bus PWOK

5LS 5V load share bus ACOK

#

Power OK output 5VSB 5V standby output

AC OK output -12 V -12V output

3.3LS 3.3V load share bus ACRange AC input range select SCL I2C Clock signal

12VS 12V remote sense PSKILL Supply fast shutdown SDA I2C Data signal

5VS 5V remote sense FAIL Failure signal A0 I2C address bit 0

3.3VS 3.3V remote sense PRFL Predictive failure signal A1 I2C address bit 1

ReturnS Return remote sense PRESENT

#

PSON

Power enable input

#

Power supply present FANC Fan control signal

Note:

ACOK and AC-Range are reserved for use internal to the power supply.

Table 6: Output Connector Pin-out

Signal Pins

1 2 3 4 5 6

D 12LS PWOK

C A0 SCL FAIL

B A1 SDA 3.3VS 5VS Reserved +5VSB

A 3.3LS PRESENT

P1 P2 P3 P4 P5 P6 P7 P8 P9 P10 P11

+12V +12V GND GND GND GND GND +5 V +5 V +3.3V +3.3V

Notes:

1 The 3.3VSB output is an optional output.

Signals defined as low true use the following convention: signal# = low true

#

#

ACOK

ACRange ReturnS -12 V

PRFL

12VS

FANC 5LS PSON

3.3VSB

#

PSKILL

1

Power Blades

Short Pin

Revision 1.11

Intel reference number 10736

Figure 11: Connector Pin Locations

21

Page 34

Power supply Subsystem SPSH4 Server System External Product Specification

4.2.3 AC Electrical Specifications

4.2.3.1 AC / DC Supply Redundancy

The power sub-system has three AC inlets, one for each power supply. Each power supply

does not rely on other modules for any functionality except for load sharing. AC input to the

power supply is fully isolated. Therefore, it is not subject to AC phase differential issues. All DC

outputs have a device to isolate the power supply from the main system power during a power

supply failure or during a hot swap operation. The SPSH4 server system has power redundancy

for any DC load condition in a 2+1 power supply configuration.

4.2.3.2 AC Input Voltage Ranges

The power supply incorporates universal power input with active power factor correction, which

reduces line harmonics in accordance with the EN61000-3-2 and JEIDA MITI standards. The

power supply operates within all specified limits over the input voltage range specified in Table

7. Harmonic distortion of up to 10% THD will not cause the power supply to go out of specified

limits. The power supply has a minimum efficiency of 60% to the DC output pins at maximum

load currents, at rated nominal input voltages and frequencies.

Table 7: AC Input Voltage Rating

Parameter Minimum Rated Maximum Max Input Current

(600W)

Voltage (110) 90 V

Voltage (220) 180 V

Frequency 47 Hz 50/60 Hz 63 Hz -

100-127 V

rms

200-240 V

rms

132 V

rms

264 V

rms

12 A

rms

6 A

rms

rms

rms

4.2.3.3 AC Line Dropout and Hold-up Time

An AC line dropout is defined as when the AC input drops to 0VAC for one cycle or less during

any phase of the AC line. During an AC dropout, the power supply meets the dynamic voltage

regulation requirements over the rated load. Dynamic voltage regulation requirements may be

seen in Table 20.

An AC line dropout will not cause any tripping of control signals or protection circuits. If the AC

dropout lasts longer than one cycle then the power supply may shutdown but will recover and

meet all turn on requirements. The power supply meets the AC dropout requirements over all

rated AC voltages, frequencies, and output loading conditions. Any dropout of the AC line will

not cause damage to the power supply.

4.2.3.4 AC Line Transient Specification

AC line transient conditions are defined as “sag” and “surge” conditions. The sag conditions are

also commonly referred to as “brownout”. The sag condition is defined as the AC line voltage

dropping below nominal voltage. The surge conditions are defined as when the AC line voltage

rises above nominal voltage. The power supply meets the performance requirements under the

AC line sag and surge conditions shown in Table 8 and Table 9, respectively.

Revision 1.11

22

Page 35

SPSH4 Server SystemTechnical Product Specification

Table 8: AC Line Sag Transient Performance

Duration Sag Operating AC Voltage Line

Continuous 10% 100VAC-127VAC

200VAC-240VAC

0 to 1 AC cycle 100% 100VAC-127VAC

200VAC-240VAC

> 1 AC cycle >10% No loss of function or

performance

50/60Hz No loss of function or performance

50/60Hz No loss of function or performance

50/60Hz Loss of function acceptable,

Frequency

Performance Criteria

self recoverable

Table 9: AC Line Surge Transient Performance

Duration Surge Operating AC Voltage Line

Frequency

Continuous 10% 100VAC-120VAC

200VAC-240VAC

0 to ½ cycle 30% 110VAC, 220VAC 50/60Hz No loss of function or performance.

50/60Hz No loss of function or performance.

Performance Criteria

4.2.3.5 Susceptibility

The power supply complies with the limits defined in EN50082-2 while maintaining normal

performance within the specification limits.

Table 10: Electrostatic Discharge, IEC 801-2/IEC 1000-4-2

Level Test Voltage, Contact

Discharge

3 8Kv 15Kv

Test Voltage, Air

Discharge

Table 11: Electrical Fast Transient/Burst, IEC 801-4/IEC 1000-4-4

Level AC Inlet

3 1Kv

Table 12: Radiated Immunity, IEC 801-3/IEC1000-4-3

Field Strength Frequency Range Step Size Modulation

5V/meter 26MHz to 500MHz 1% of previous frequency None

4.2.3.6 Surge Immunity

In addition to complying with EN50082-2 for Surge immunity, the product must also comply with

ANSI C62.45-1992. The requirements of the Intel Environmental & Reliability Board and System

Revision 1.11

Intel reference number 10736

23

Page 36

Power supply Subsystem SPSH4 Server System External Product Specification

Validation Test Handbook for surge withstand capability indicates the test methods and levels

used during Intel system qualification testing, which are derived from these standards.

Table 13: Surge Immunity IEC 1000-4-5

Level Open Circuit

Voltage

3

2.0Kv ± 10%

Minimum time between

Surges

20 sec

Table 14: Ring Wave

Open Circuit

Voltage

3.0Kv ± 10%

Minimum time between

Surges

20 sec

4.2.3.7 AC Line Fast Transient Response

The power supply meets the EN61000-4-5 directive and any additional requirements in

IEC1000-4-5: 1995 and the Level 3 requirements for surge-withstand capability.

Revision 1.11

24

Page 37

SPSH4 Server SystemTechnical Product Specification

4.2.3.8 AC Line Inrush

AC line inrush current does not exceed 25A peak for quarter of the AC cycle. The inrush current

must not exceed the I

2

t curve shown in Figure 12. The inrush current must not exceed 100A

peak for any duration of time.

The power supply meets the inrush requirements for any rated AC voltage, during turn on at any

phase of AC voltage, during hot plug, during any AC dropout condition, over the specified

temperature range, and during AC power cycling.

120

100

80

60

amps

40

20

0

0 5 10 15 20

ms ec

Figure 12: Inrush Curve

4.2.3.9 Dielectric Strength Requirements

The power supply meets all safety agency requirements for dielectric strength.

4.2.3.10 AC Line Fuse

Each power supply has two line fuses, one for each side of the AC input. AC line-fusing meets

all safety agency requirements.

4.2.3.11 AC Inlet Connector

The AC input connector is an IEC 320 C-14 power inlet. This inlet is rated for 15A / 250VAC.

4.2.4 DC Output Specification

The SPSH4 server system runs with either two or three power supplys installed. The power

supplys operate with their outputs directly paralleled. The power supplys equally share the total

load currents within the limits specified. Equal power sharing of paralleled power supplys is

required to prevent life shortening stress concentration in individual power supplys. Power

sharing is accomplished by actively matching the output currents on the high power outputs.

The current sharing load deviation is defined as follows:

Load_Deviation = [(Actual_Load – Mean_ Load)/(Mean Load)] * 100%

Revision 1.11

Intel reference number 10736

25

Page 38

Power supply Subsystem SPSH4 Server System External Product Specification

Steady state DC output voltages at the remote sense points always remain within the limits

specified by Table 15 for all combinations of operating line, load, load transient, and

environment specified herein.

Table 15: DC Output Voltage Limits

Parameter Minimum Nominal Maximum Units Tolerance

+3.3V + 3.25 + 3.30 + 3.35 V

+5V + 4.90 +5.00 + 5.10 V

+12V + 11.76 +12.00 + 12.24 V

-12V - 13.08 -12.00 - 11.40 V + 9% and -5%

+5V Standby1 + 4.85 +5.00 + 5.20 V + 4% and -3%

Note:

1 +5V standby is in reference to the common remote sense returning potential.

± 1.5%

± 2%

± 2%

Revision 1.11

26

Page 39

SPSH4 Server SystemTechnical Product Specification

4.2.4.1 DC Output Rating

The power supply meets the static regulation requirements under the loading conditions

specified in Table 16. The combined continuous output load applied to the power supply will not

exceed 600 W. If the power exceeds 600 W, the power supply should not be subjected to this

maximum current draw for more than 12 seconds.

Table 16: 600W Load Ratings

Voltage

+3.3V 1 A 40 A

+5V 1 A 34 A

+12V 0 A 36 A 42 A

-12V 0 A 1.0 A

+5V Standby 0 A 2 A

Minimum Continuous Maximum Continuous Peak

Single Power supply Maximum Output Current

The total system maximum load condition is shown in Table 17. Either two or three power

supplys can support the total system maximum load.

Table 17: Total System Load at Line AC Input

Total System Maximum Load Condition

Voltage Minimum Continuous Maximum Continuous Peak

+3.3V 1.5 A 76 A

+5V 1.5 A 64.6 A

+12V 1.5 A 68.4 A 79.8A

-12V 0.0 A 1.0 A

+5V Standby 0.0 A 2.0 A

Table 18: Absolute Worst Case System Power Budget

Subsystem Qty +5V +3.3V +12V -12V +5VSB Total (W)

Board Set 1 4.36 10.76 1.15 0.01 0.38 73.13

CPU 4 30.85 370.20

DDR DRAM 12 1.97 6.10 79.70

FAN 6 6.32 75.84

HDD 10 11.00 9.00 163.00

CD-ROM 1 0.40 0.70 10.40

FDD 1 0.24 1.20

5½" Device 2 1.54 0.80 17.30

PCI-X (64bit/100MHz) 6 9.00 13.64 0.31 91.56

Revision 1.11

Intel reference number 10736

27

Page 40

Power supply Subsystem SPSH4 Server System External Product Specification

Subsystem Qty +5V +3.3V +12V -12V +5VSB Total (W)

PCI (32bit/33MHz) 2 6.00 0.03 30.15

System Total 32.54 26.37 54.92 0.01 0.72 912.48

Power Subsystem Spec 64.60 76.00 68.40 1.00 2.00 1140.00

Margin 32.06 49.63 13.48 0.99 1.28 227.52

4.2.4.2 Remote Sense

The power supply has remote sense return (ReturnS) to regulate out ground drops for all output

voltages (+3.3V, +5V, +12V, -12V and +5VSB). The power supply operates within the

specification shown in Table 19 over the full range of voltage drops from the power supply’s

output connector to the remote sense points on the server system boardset.

Table 19: Remote Sense Drops

Output Max Drops Units

+3.3V 250 mV

+5V 250 mV

+12V 500 mV

Remote Sense return 100 mV

4.2.4.3 DC and Transient Load Output Voltage Limit

The power supply will maintain regulation specified in Table 20 under all specified conditions,

including parallel operation with other power supplys, line variations, load variations, transient

load conditions, peak ripple/noise, maximum remote sense drops, subsystem hot swap, and

temperature change. The +3.3V, +5V, and +12V output voltages should be measured at their

respective remote sense points. The output voltages must stay within regulation requirements

with the remote sense regulating out the maximum drops shown in Table 19.

Table 20: Dynamic Tolerance Requirement

Output Min. Output [V] Max. Output [V] Tolerance

+3.3V 3.20 3.43 +4% & -3 %

+5V 4.85 5.20 +4% & -3 %

-12V 11.4 13.08 +9 & -5%

+12V 11.64 12.48 +4% & -3 %

+5V standby 4.85 5.20 +4% & -3 %

Revision 1.11

28

Page 41

SPSH4 Server SystemTechnical Product Specification

D

4.2.4.4 Ripple and Noise

The maximum allowed ripple/noise output of the power supply is defined in Table 21. This is

measured over a bandwidth of 0Hz to 20MHz at the power supply output connector. A 10µF

tantalum capacitor in parallel with a 0.1µF ceramic capacitor are placed at the point of

measurement. The test setup is shown in Figure 13.

V

OUT

AC

Earth GND

POWER SUPPLY

V

RETURN

GENERAL NOTES:

1. LOAD THE OUTPUT WITH ITS MINIMUM

LOAD CURRENT.

2. CONNECT THE PROBES AS SHOWN.

3. REPEAT THE MEASUREMENTS WITH THE

MAXIMUM LOAD ON THE OUTPUT.

SCOPE NOTE:

USE A TEKTRONIX 7834 OSCILLOSCOPE WITH 7A13 AN

P6055 PROBES OR EQUIVALENT.

Figure 13: Differential Noise Test Setup

Table 21: Ripple and Noise

LOAD

10uF

(low ESR)

SCOPE

Voltage Ripple / Noise pk-pk Ripple/Noise pk-pk

+3.3V 1.5% 50 mV

+5V 1% 50 mV

+12V 1% 120 mV

-12V 1% 120 mV

+5V Standby 1% 50 mV

Revision 1.11

Intel reference number 10736

29

Page 42

Power supply Subsystem SPSH4 Server System External Product Specification

4.2.4.5 Power Timing

Power timing refers to the timing requirements for single power supply operation. The output

voltages must rise from 10% to within regulation limits (T

) within 5 to 200ms. The +3.3V,

vout_rise

+5V and +12V output voltages should start to rise approximately at the same time. All outputs

must rise monotonically. The +5V output needs to be greater than the +3.3V output during any

point of the voltage rise, however, never by more than 2.25V.

Each output voltage reaches regulation within 100ms (T

off within 100ms (T

power supply being turned on and off via the AC input, with PSON held low and the PSON

signal, with the AC input applied. The ACOK

) of each other. Figure 14 shows the timing requirements for a single

vout_on

#

signal is not being used to enable the turn on

) of each other and begin to turn

vout_on

timing of the power supply.

Table 22: Output Voltage Timing

Item Description Min Max Units

T

Output voltage rise time from each main output. 5 200 msec

vout_rise

T

All main outputs must be within regulation of each other within this time. 300 msec

vout_off

T

All main outputs must be within regulation of each other within this time. 100 msec

vout_on

10% Vout

T

T

vout rise

T

vout_off

Figure 14: Output Voltage Timing

Table 23: Turn On/Off Timing

Revision 1.11

30

Page 43

SPSH4 Server SystemTechnical Product Specification

_

Item Description Min Max Units

T

sb_on_delay

T

ac_on_delay

T

vout_holdup

T

pwok_holdup

T

pson_on_delay

T

pson_pwok

T

acok_delay

T

pwok_on

T

pwok_off

T

pwok_low

T

sb_vout

Delay from AC being applied to 5VSB being within regulation. 1500 msec

Delay from AC being applied to all output voltages being within regulation. 2500 msec

Time all output voltages, including 5VSB, stay within regulation after loss of

21 msec

AC.

Delay from loss of AC to deassertion of PWOK

20 msec

Delay from PSON# active to output voltages within regulation limits. 5 400 Msec

Delay from PSON# deactive to PWOK being deasserted. 50 Msec

Delay from loss of AC input to deassertion of ACOK#. 20 Msec

Delay from output voltages within regulation limits to PWOK asserted at

100 1000 Msec

turn on.

Delay from PWOK deasserted to output voltages (3.3V, 5V, 12V, -12V,

1 Msec

5VSB) dropping out of regulation limits.

Duration of PWOK being in the deasserted state during an off/on cycle

100 Msec

using AC or the PSON signal.

Delay from 5VSB being in regulation to 5V being in regulation at AC turn

50 1000 Msec

on.

AC Input

Vout

PWOK

5VSB

PSON

ACOK#

T

sb_on_delay

T

vout_holdup

T

T

AC_on_delay

T

T

pwok_holdup

T

acok_delay

pwok_off

T

sb

vout

AC turn on/off cycle

T

pwok_on

pwok_low

T

sb_on_delay

T

pwok_on

T

pson_on_delay

PSON turn on/off cycle

T

pwok_off

T

pson_pwok

T

pson_off_delay

Revision 1.11

Intel reference number 10736

Figure 15: Turn On/Off Timing

31

Page 44

Power supply Subsystem SPSH4 Server System External Product Specification

4.2.5 Electrical Protection Circuits

Protection circuits inside the power supply will cause only the power supply’s main outputs to

shutdown during either an over-voltage or over-current condition. The 5VSB output remains

powered on if the failure does not involve this output. When a protection circuit shuts down the

power supply, both the FAIL LED and the FAIL signal will be activated.

4.2.5.1 Over-Voltage Protection

Over-voltage protection is sensed inside the power supply. The power supply will shutdown and

latch off following an over-voltage condition. This latch can be cleared by toggling the power

supply PSON

limit applies to all specified AC input voltages and output load conditions. Table 24 contains the

over-voltage limits. The values are measured at the output of the power supply DC connector.

#

signal or by an AC power interruption of greater than 1 second. This over-voltage

Table 24: Over-Voltage Limits

Output Voltage Protection Point [ V]

+3.3 V 3.8 – 4.5

+5 V 5.6 – 6.5

+12 V 13 – 14.5

4.2.5.2 Over- Current Protection

The power supply has over-current protection on +3.3V, +5V, and +12V outputs. The current

limiting is of the voltage fold-back type. The over-current limit levels specified in Table 25 are

maintained for a period of 2.6-second minimum and 3.6-second maximum. After this time the

power supply will latch off. The power supply cannot be damaged from repeated power cycling

in this condition.

Table 25: Over Current Protection Limits

Voltage Over-current Limit

+3.3V 44.0 A minimum; 60.0 A maximum

+5V 37.4 A minimum; 51.0 A maximum

+12V 39.6 A minimum; 54.0 A maximum

Note:

Limits specified are per 600W power supply.

Revision 1.11

32

Page 45

SPSH4 Server SystemTechnical Product Specification

4.2.6 Control Signals

4.2.6.1 PSON

The PSON

signal that turns on the 3.3V, 5V, 12V, and -12V power rails. When this signal is not pulled low