Page 1

SKA4 Baseboard Product Guide

Order Number: A09429-003

A Guide for Technically Qualified Assemblers of Intel® Identified Subassemblies/Products

Page 2

Disclaimer

Intel Corporation (Intel) mak es no warranty of any kind with regard t o this material, includi ng, but not limited to, the im pl i ed

warranties of merchantability and fitness for a particular purpose. Int el as sumes no responsibility for any errors t hat may

appear in this document. Intel makes no commitm ent to update nor to keep current the inform ation contained in this

document. No part of this document may be copied or reproduced in any form or by any means without prior wri t ten

consent of Intel.

®

An Intel

product, when used in accordance wi th its associated doc um entation, is "Year 2000 Capable" when, upon

installation, it accurately stores, di splays, processes , provides, and/or receives dat e data from, into, and between the

twentieth and twenty-first centuries, includi ng l eap year calculations, provi ded that all other technology used i n combination

with said product properly exchanges date data with it.

†

Third party brands and names are the property of their respective owners.

Copyright © 1998-2000 Intel Corporation.

Page 3

Contents

Part I: User’s Guide........................................................................................................ 11

1 Baseboard Description

Baseboard Features........................................................................................................... 13

Baseboard Connector and Component Locations...................................................... 14

Processor........................................................................................................................... 15

Memory..............................................................................................................................16

Peripherals......................................................................................................................... 18

Super I/O Chip (SIO)................................................................................................. 18

Add-in Board Slots ............................................................................................................. 18

DesotoE2 Hot-Plug PCI Controller ..................................................................................... 19

IDE Interface...................................................................................................................... 19

USB Interface..................................................................................................................... 20

Network Interface Controller (NIC) ..................................................................................... 20

Video.................................................................................................................................. 20

SCSI Controller .................................................................................................................. 21

IDE Controller..................................................................................................................... 22

Keyboard and Mouse......................................................................................................... 22

Server Management........................................................................................................... 23

Baseboard Management Controller (BMC)................................................................ 23

System Security.................................................................................................................24

Software Locks via the SSU or BIOS Setup............................................................... 24

2 Configuration Software and Utilities

Hot Keys............................................................................................................................. 28

Power-On Self Test (POST)............................................................................................... 28

Using BIOS Setup.............................................................................................................. 29

Record Setup Settings............................................................................................... 29

If Setup is Not Accessible.......................................................................................... 29

Starting Setup............................................................................................................ 29

Setup Menus ............................................................................................................. 30

Main Menu................................................................................................................. 31

Advanced Menu......................................................................................................... 33

Security Menu............................................................................................................ 39

Server Menu.............................................................................................................. 40

Boot Menu................................................................................................................. 42

Exit Menu................................................................................................................... 43

Changing the Boot Device Priority Temporarily.................................................................. 44

Changing the Boot Device Priority Permanently................................................................. 44

Running the SCSI

When to Run the SCSI

Running the SCSI

Configuring the Adaptec AIC-7880 SCSI Adapter...................................................... 46

Configuring the Adaptec AIC-7899 SCSI Adapter...................................................... 46

Select

Utility........................................................................................... 45

Select

Select

Utility........................................................................... 45

Utility................................................................................... 45

iii

Page 4

Using the System Setup Utility (SSU)................................................................................. 47

When to Run the SSU ............................................................................................... 47

What You Need to Do................................................................................................ 48

Running the SSU Remotely....................................................................................... 48

Creating SSU Diskettes............................................................................................. 48

Running the SSU....................................................................................................... 49

Direct Platform Control (DPC) Console.............................................................................. 49

DPC Console Modes of Operation............................................................................. 50

Running the DPC Console......................................................................................... 50

FRU and SDR Load Utility.................................................................................................. 51

What You Need to Do................................................................................................ 51

How You Use the FRUSDR Load Utility..................................................................... 51

Cleaning Up and Exiting ............................................................................................ 53

Upgrading the BIOS........................................................................................................... 53

Preparing for the Upgrade......................................................................................... 53

Upgrading the BIOS................................................................................................... 54

Recovering the BIOS................................................................................................. 55

Changing the BIOS Language................................................................................... 55

Using the Firmware Update Utility...................................................................................... 56

Running the Firmware Update Utility ......................................................................... 56

Part II: Service Technician’s Guide ........................................................................... 57

3 Removing and Installing Baseboard Components.......................................... 59

Tools and Supplies Needed................................................................................................ 59

Safety: Before You Work with the Baseboard.................................................................... 59

Warnings and Cautions...................................................................................................... 59

Memory..............................................................................................................................61

Removing the Memory Module.................................................................................. 61

Installing the Memory Module.................................................................................... 62

Removing DIMMs...................................................................................................... 62

Installing DIMMs........................................................................................................ 62

Processors......................................................................................................................... 63

Removing a Processor .............................................................................................. 64

Installing a Processor ................................................................................................ 65

Removing Processor Retention Mechanisms ............................................................ 65

Installing Processor Retention Mechanisms.............................................................. 65

Installing Processor Handles ..................................................................................... 65

Installing Processor Heatsinks................................................................................... 66

Voltage Regulator Modules (VRMs) ................................................................................... 66

Removing a VRM....................................................................................................... 67

Installing a VRM......................................................................................................... 67

Replacing the Backup Battery ............................................................................................ 68

Add-in Boards.....................................................................................................................69

Removing a 32-bit, 33 MHz Half-Length PCI Add-in Board........................................ 70

Installing a 32-bit, 33 MHz Half-Length PCI Add-in Board.......................................... 70

Removing a 64-bit, 66/33 MHz Hot-Plug PCI Add-in Board....................................... 71

Installing a 64-bit, 66/33 MHz Hot-Plug PCI Add-in Board......................................... 72

iv SKA4 Baseboard Product Guide

Page 5

ICMB Card.........................................................................................................................73

Installing an ICMB Card............................................................................................. 74

Removing an ICMB Card........................................................................................... 75

4 Solving Problems

Boot Issues........................................................................................................................77

Issue 1: My server will not power on......................................................................... 77

Issue 2: Upon boot, my server starts beeping........................................................... 78

Issue 3: My HDD lights went on, I heard t he dr ives spin up, and my

floppy drive light turned on – but I’m not seeing video................................. 78

Issue 4: I’m installing adapters in my powered-down system, and my

system boots up when I install a PCI adapter!............................................. 79

Issue 5: My system boots up automatically when I power on my power-strip ........... 80

Issue 6: The boot up process takes too long............................................................. 80

Issue 7: I put one processor in my system but it doesn’t boot................................... 81

Other Issues....................................................................................................................... 82

Issue 8: Some of my hard drives show up during POST and some don’t.................. 82

Issue 9: My hard drives don’t show up under Windows NT....................................... 83

Checking Field Replaceable Units (FRU) with the Diagnostic Wizard................................. 84

Starting the Service Partition & Test Menu................................................................ 84

Running Tests ........................................................................................................... 85

5 Technical Reference

Connectors......................................................................................................................... 90

Power Distribution Board Interface Connectors (J9B1, J9D1, J9B2).......................... 92

Front Panel Interface (J9E3)...................................................................................... 94

Hot-Plug PCI Indicator Board Interface (J3D1).......................................................... 96

Memory Module Interface (J6F1)............................................................................... 97

Processor Module Connector (J7A1, J7B1, J7C1, J7D1)........................................... 99

Processor Termination, Regulation, and Power....................................................... 102

Termination Card..................................................................................................... 103

Server Monitor Module Connector (J7H1)................................................................ 103

SM Bus Connector (J9E4)....................................................................................... 104

ICMB Connector (J1D2) .......................................................................................... 105

2

Auxiliary I

Baseboard Fan Connectors (J3C1, J3A1, J4A1, J4C1)........................................... 105

Internal USB Header (J1B3).................................................................................... 106

Internal Disk Drive LED Connection......................................................................... 106

Baseboard Jumpers......................................................................................................... 107

Changing Jumper Settings....................................................................................... 108

CMOS Clear Jumper ............................................................................................... 109

Password Clear Jumper........................................................................................... 110

Recovery Boot Jumper............................................................................................ 110

Interrupts.......................................................................................................................... 111

Video Modes.................................................................................................................... 112

C Connector (J9E4)................................................................................ 105

Contents v

Page 6

A Equipment Log and Configuration Worksheets

Equipment Log ........................................................................................................ 113

Configuration Worksheets........................................................................................ 115

Power Configuration Worksheet.............................................................................. 115

SSU Worksheets..................................................................................................... 115

B Regulatory Specifications

Environmental Specifications and Regulatory Compliance............................................... 125

Environmental Specifications................................................................................... 125

Regulatory Compliance............................................................................................ 125

Installation Instructions ..................................................................................................... 126

Ensure EMC Compliance......................................................................................... 126

Ensure Host Computer and Accessory Module Certifications.................................. 127

Prevent Power Supply Overload.............................................................................. 127

Place Battery Marking on Computer........................................................................ 128

Use Only for Intended Applications.......................................................................... 128

Installation Precautions .................................................................................................... 128

C Warnings

WARNING: English (US)................................................................................................. 129

AVERTISSEMENT: Français........................................................................................... 129

WARNUNG: Deutsch ...................................................................................................... 129

AVVERTENZE: Italiano................................................................................................... 130

ADVERTENCIAS: Español.............................................................................................. 130

Index.................................................................................................................................... 131

Figures

1. Baseboard Connector and Component Locations..................................................... 14

2. Memory Module DIMM Installation Sequence............................................................ 16

3. Memory Module DIMM Installation Sequence............................................................ 61

4. Installing DIMMs: Orientation of DIMM in a Memory Module..................................... 63

5. Processor Orientation and Components.................................................................... 64

6. Installing a VRM ........................................................................................................ 67

7. Example of a Front Hot-Plug Retention Mechanism.................................................. 69

8. ICMB Card................................................................................................................. 73

9. Section of ICMB Internal Cable.................................................................................. 74

10. Example of an ICMB Card Attached to a Chassis...................................................... 74

11. Internal Cable Attached to the ICMB Card................................................................. 75

12. External Cable Attached to the Card ......................................................................... 75

13. Detailed Diagram of Connector Locations ................................................................. 90

14. SKA4 Configuration Jumpers................................................................................... 107

Tables

1. Baseboard Features.................................................................................................. 13

2. SKA4 Pentium Xeon Processor Family Support Matrix.............................................. 15

3. Slot State Indicators .................................................................................................. 19

4. Software Security Features....................................................................................... 25

vi SKA4 Baseboard Product Guide

Page 7

5. Configuration Utilities................................................................................................. 27

6. Hot Keys.................................................................................................................... 28

7. Main Menu................................................................................................................. 31

8. Primary IDE Master and Slave Submenu.................................................................. 32

9. Processor Settings Submenu .................................................................................... 32

10. Advanced Menu......................................................................................................... 33

11. Embedded Video Controller Submenu....................................................................... 33

12. Embedded Legacy SCSI Submenu........................................................................... 33

13. Embedded Dual Ultra 160 SCSI Submenu................................................................ 34

14. Embedded NIC Submenu.......................................................................................... 34

15. PCI Device, Slot 1 Submenu..................................................................................... 34

16. PCI Device, Slot 2 Submenu..................................................................................... 35

17. PCI Device, Slot 3 Submenu..................................................................................... 35

18. PCI Device, Slot 4 Submenu..................................................................................... 35

19. PCI Device, Slot 5 Submenu..................................................................................... 36

20. PCI Device, Slot 6 Submenu..................................................................................... 36

21. PCI Device, Slot 7 Submenu..................................................................................... 36

22. PCI Device, Slot 8 Submenu..................................................................................... 37

23. Hot-Plug PCI Control Submenu................................................................................. 37

24. Integrated Peripheral Configuration Submenu........................................................... 37

25. Advanced Chipset Control Submenu......................................................................... 38

26. Security Menu............................................................................................................ 39

27. Server Menu.............................................................................................................. 40

28. System Management Submenu................................................................................. 40

29. Console Redirection Submenu.................................................................................. 41

30. EMP Configuration Submenu.................................................................................... 41

31. PEP Management Submenu ..................................................................................... 42

32. Boot Menu................................................................................................................. 42

33. Boot Device Priority Submenu................................................................................... 42

34. Hard Drive Submenu................................................................................................. 43

35. Removable Devices Selection Submenu................................................................... 43

36. Exit Menu.................................................................................................................. 43

37. Navigation Keys......................................................................................................... 45

38. Main Menu................................................................................................................. 46

39. Exit Menu.................................................................................................................. 46

40. Main Menu................................................................................................................. 46

41. Menu for each SCSI Channel.................................................................................... 46

42. Exit Menu.................................................................................................................. 47

43. Command Line Format.............................................................................................. 51

44. VRM/Processor Power Sequence ............................................................................. 66

45. Processor/VRM Population Sequencing.................................................................... 66

46. Standard BIOS Port-80 Codes................................................................................... 78

47. Recovery BIOS Port-80 Codes .................................................................................. 78

48. Main Power Connector A (J9B1) ............................................................................... 92

49. Main Power Connector B (J9D1)............................................................................... 93

50. Auxiliary Power Connector (J9B2)............................................................................. 93

51. Front Panel Connector (J9E3)................................................................................... 94

52. Hot-Plug Indicator Board Connector Pin Out (J3D1).................................................. 96

Contents vii

Page 8

53. Memory Module Interface.......................................................................................... 97

54. Processor Card Connector Pin Out (J7A1, J7B1, J7C1, J7D1).................................. 99

55. Processor VRM Connectors (J2A2, J2B1, J2C1): Add-in VRM Connector

Pin Listing.............................................................................................................. 102

56. Server Monitor Module Connector Pin Out.............................................................. 103

57. SM Bus Connector (J9E4)....................................................................................... 104

58. ICMB Connector (J1D2).......................................................................................... 105

59. IMB Connector Pin out (J8F1)................................................................................. 105

60. Processor Fan Connector #1 (J3C1)....................................................................... 105

61. Processor Fan Connector #2 (J3A1) ....................................................................... 106

62. Processor Fan Connector #3 (J4A1) ....................................................................... 106

63. Processor Fan Connector #4 (J4C1)....................................................................... 106

64. Internal USB Connector (J1B3)............................................................................... 106

65. Internal USB Connector (J1B3)............................................................................... 106

66. Configuration Jumper Settings................................................................................. 107

67. Configuration of Jumpers......................................................................................... 108

68. Beep Codes............................................................................................................. 111

69. Interrupt Definitions................................................................................................. 111

70. Standard VGA Modes.............................................................................................. 112

71. Equipment Log........................................................................................................ 113

72. Devices Worksheet 1............................................................................................... 115

73. Systems Group Worksheet 2................................................................................... 115

74. On-board Disk Controllers Worksheet 3.................................................................. 115

75. Onboard Communications Devices Worksheet 4..................................................... 116

76. Diskette Drive Subsystems Group Worksheet 5...................................................... 116

77. IDE Subsystem Group Worksheet 6........................................................................ 116

78. On-Board PCI Devices Group Worksheet 7............................................................. 116

79. Multiboot Group Worksheet 8.................................................................................. 117

80. Security Subsystems Worksheet 9.......................................................................... 117

81. Main Menu Worksheet 10........................................................................................ 119

82. Primary Master and Slave Submenu Worksheet 11 ................................................ 119

83. Processor Settings Submenu Worksheet 12 ........................................................... 119

84. Advanced Menu Worksheet 13................................................................................ 119

85. Embedded Video Controller Submenu Worksheet 14.............................................. 120

86. Embedded Legacy SCSI Submenu Worksheet 15 .................................................. 120

87. Embedded Dual Ultra 160 SCSI Submenu Worksheet 16....................................... 120

88. Embedded NIC Submenu Worksheet 17................................................................. 120

89. PCI Device, Slot 1 Submenu Worksheet 18............................................................ 120

90. PCI Device, Slot 2 Submenu Worksheet 19............................................................ 120

91. PCI Device, Slot 3 Submenu Worksheet 20............................................................ 120

92. PCI Device, Slot 4 Submenu Worksheet 21............................................................ 120

93. PCI Device, Slot 5 Submenu Worksheet 22............................................................ 121

94. PCI Device, Slot 6 Submenu Worksheet 23............................................................ 121

95. PCI Device, Slot 7 Submenu Worksheet 24............................................................ 121

96. PCI Device, Slot 8 Submenu Worksheet 25............................................................ 121

97. Hot-Plug PCI Control Submenu Worksheet 26........................................................ 121

98. Integrated Peripheral Configuration Submenu Worksheet 27.................................. 121

99. Advanced Chipset Control Submenu Worksheet 28................................................ 122

viii SKA4 Baseboard Product Guide

Page 9

100. Security Menu Worksheet 29................................................................................... 122

101. Server Menu Worksheet 30..................................................................................... 122

102. System Management Submenu Worksheet 31........................................................ 122

103. Console Redirection Submenu Worksheet 32......................................................... 123

104. EMP Configuration Submenu Worksheet 33............................................................ 123

105. PEP Management Submenu Worksheet 34 ............................................................ 123

106. Boot Menu Worksheet 35........................................................................................ 123

107. Boot Priority Submenu Worksheet 36 ...................................................................... 123

108. Hard Drive Submenu Worksheet 37........................................................................ 123

109. Removable Devices Selection Submenu Worksheet 38.......................................... 124

110. Safety Regulations .................................................................................................. 125

111. Verification to EMC Regulations.............................................................................. 125

Contents ix

Page 10

x SKA4 Baseboard Product Guide

Page 11

Part I: User’s Guide

1 Baseboard Description

2 Configuration Software and Utilities

11

Page 12

12 SKA4 Baseboard Product Guide

Page 13

1 Baseboard Description

Baseboard Features

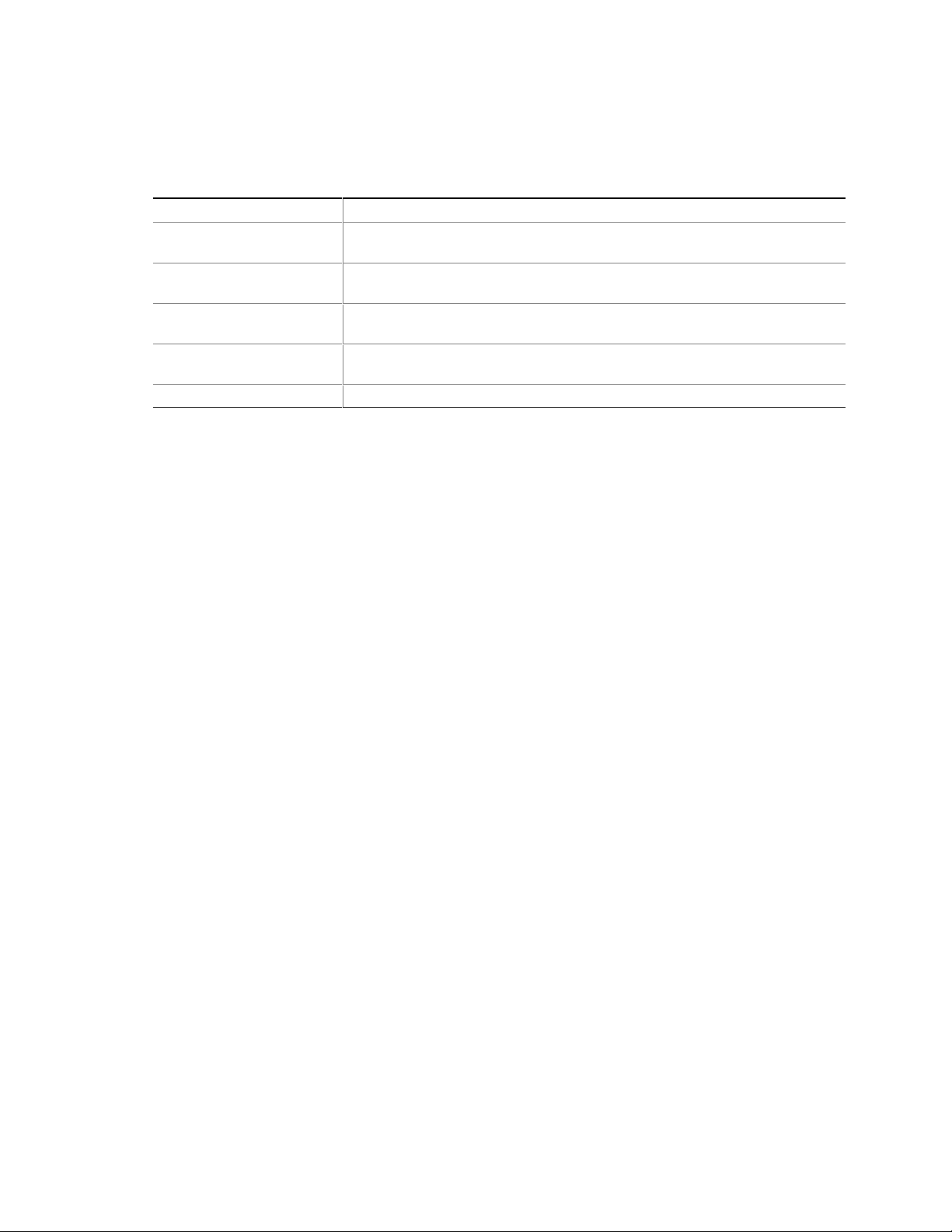

Table 1. Baseboard Features

Feature Description

Processor Installed: Up to four Intel® Pentium® III Xeon™ processors, packaged in single

edge contact (S.E.C.) cartridges and installed in 330-pin SC330.1 compliant

edge connectors, operating at 1.8 V to 3.5 V. The baseboard’s voltage regulator

is automatically programmed by the processor’s VID pins to provide the required

voltage. The baseboard includes connectors for three 8.3-compliant plug-in

voltage-regulator modules (VRM).

Memory, dynamic

random access (DRAM)

Video memory (DRAM) Installed: 2 MB of video memory.

PCI Segment A bus

PCI Segment B bus

PCI Segment C bus

PCI Bus Master IDE

Interface

USB Interface The baseboard provides a dual external USB connector and one internally

Server Management Thermal/voltage monitoring and error handling.

Graphics ATI Rage IIc VGA Graphics Accelerator, along with video SGRAM and support

SCSI Two embedded SCSI controllers:

System I/O PS/2†-compatible keyboard and mouse ports, 6-pin DIN.

Form Factor Form-factor, 16 × 13 inches, ATX-style backpanel I/O.

Single plug-in module containing 64/72-bit four-way-interleaved pathway to main

memory supporting SDRAM.

Installed: 256 MB to 16 GB of error correcting code (ECC) memory. A minimum

of four DIMMs must be installed.

PCI-A—Two full length connectors and one embedded device:

• Two 184-pin, 3.3 V keyed, 64-bit PCI expansion connectors (66/33 MHz).

• One DesotoE2 Hot-Plug PCI controller.

PCI-B—Four full length connectors and two embedded devices:

• One Adaptec

• Four 184-pin, 5 V keyed, 64-bit PCI expansion connectors (33 MHz).

• One DesotoE2 Hot-Plug PCI controller.

PCI-C—Two half length connectors and several embedded devices:

• Two 120-pin, 32-bit PCI expansion connectors (33 MHz).

• OSB4 I/O APIC.

• PCI network interface controller.

• ATI Rage

• PCI narrow/wide Adaptec AIC-7880 Ultra SCSI controller.

The baseboard supports Ultra DMA33 Synchronous Direct Memory Access

(DMA) mode transfers.

accessible header.

Front panel controls and indicators (LEDs).

circuitry for an embedded SVGA video subsystem.

Adaptec AIC-7899 SCSI Controller—Dual Channel Wide Ultra/Ultra II/Ultra

160/M SCSI controller.

Adaptec AIC-7880 SCSI Controller—PCI narrow/wide Ultra SCSI controller.

Advanced parallel port, supporting Enhanced Parallel Port (EPP) levels 1.7 and

1.9, ECP, compatible 25-pin.

VGA video port, 15-pin.

Two serial ports, 9-pin (serial port A is the top connector).

†

AIC-7899 dual channel SCSI-3 Ultra 160/m SCSI controller.

†

IIc video controller.

13

Page 14

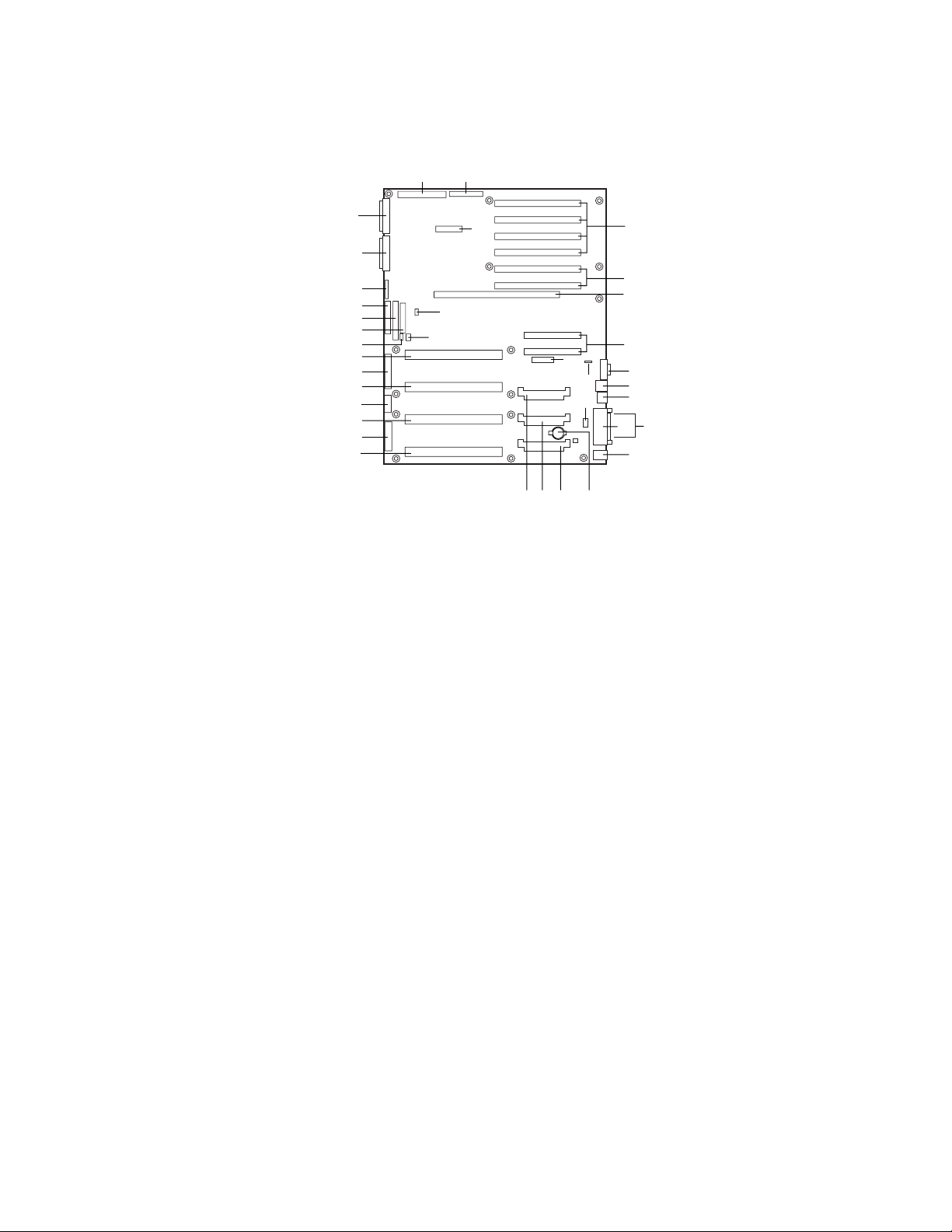

Baseboard Connect or and Component Locations

A B

Z

Y

X

W

V

U

T

AA

S

BB

R

CC

Q

DD

C

D

E

F

H

FFEE

GG

G

I

JJ

I I

J

HH

K

L

M

N

P

OM09918

O

Figure 1. Baseboard Connector and Component Locations

A. Legacy Narrow SCSI B. Legacy Wide SCSI

C. SMM Connector D. IMB Connector

E. HDD Activity F. HPIB Connector

G. ICMB Connector H. Internal USB Connector

I. Lithium Battery J. Memory Module Connector

K. Video Connector L. USB, External Connector

M. Network Connector N. Parallel Connector

O. COM1, COM2 Connector P. Keyboard/Mouse

Q. Main Power 1 R. Auxiliary Power

S. Main Power 2 T. SMBus

U. Front Panel V. IDE Connector

W. Floppy Connector X. Configuration Jumpers

Y. Ultra 160 SCSI A Z. Ultra 160 SCSI BA. Legacy

Narrow SCSI

AA. Processor #1 BB. Processor #2

CC. Processor #3 DD. Processor #4

EE. Voltage Regulator Module (VRM)

Connector #2

GG. Voltage Regulator Module (VRM)

Connector #4

II. 64-bit, 66/33 MHz Hot-Plug PCI

Slots

FF. Voltage Regulator Module (VRM)

Connector #3

HH. 32-bit, 33 MHz Half-length PCI

Slots

JJ. 64-bit, 33 MHz Hot-Plug PCI Slots

14 SKA4 Baseboard Product Guide

Page 15

CAUTION

Lithium Battery: See "Replacing the Backup Battery" on page 68 of this

product guide for instructions on replacing and disposing of the Lithium

Battery.

Processor

Each Intel Pentium III Xeon processor is packaged in a single edge contact (S.E.C.) cartridge. The

cartridge includes the processor core with an integrated 32 KB primary (L1) cache, the secondary

(L2) cache, a thermal plate, and a plastic cover.

The processor core and L2 cache components are on a pre-assembled printed circuit board,

approximately 5 inches by 6 inches. The L2 cache and processor core L1 cache interface use a

private bus isolated from the processor host bus. The L2 cache bus operates at the processor core

frequency.

Each S.E.C. cartridge connects to the baseboard through a 330-pin SC330.1 compliant edge

connector. A retention module attached to the baseboard secures the cartridge. Depending on

configuration, the system supports one to four processors.

The processor external interface is MP-ready and operates at 100 MHz. The processor contains a

local Advanced Configuration and Power Interface (APIC) unit for interrupt handling in

multiprocessor (MP) and uniprocessor (UP) environments.

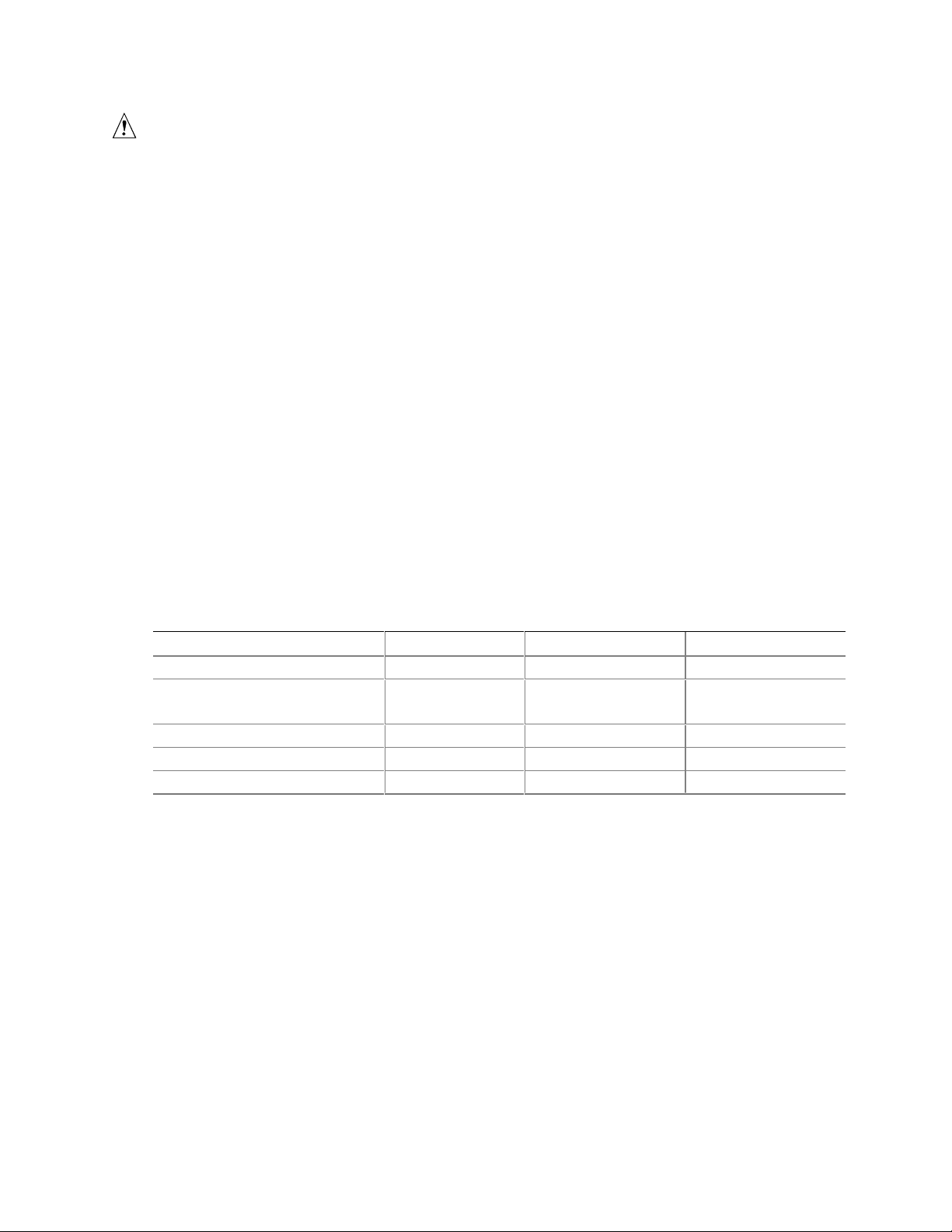

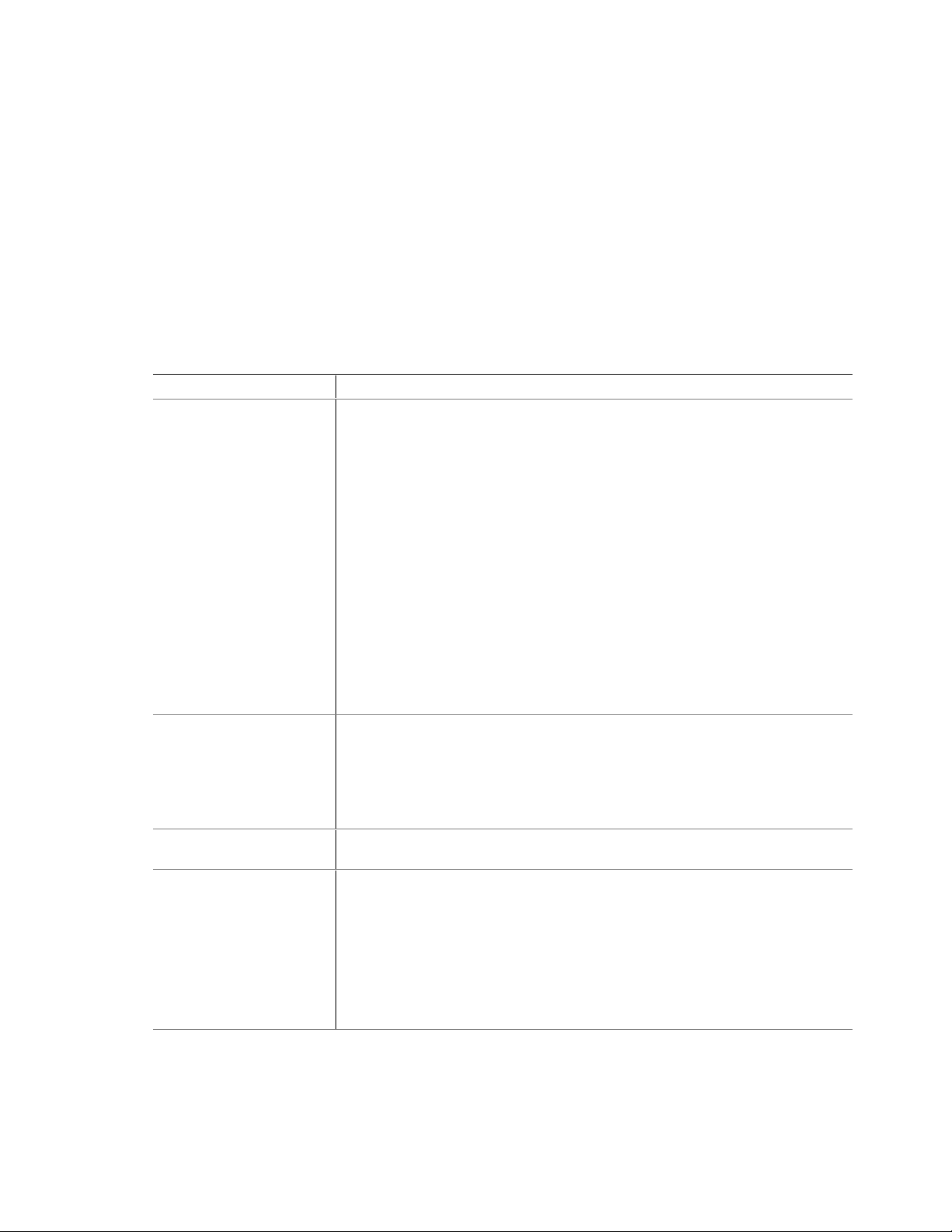

Table 2. SKA4 Pentium Xeon Processor Family Support Matrix

Name Frequency Cache Size Support (Y/N)

Pentium II Xeon processor 400 MHz, 450 MHz 512k, 1M, 2M No

Pentium III Xeon processor 500 MHz

550 MHz

Pentium III Xeon processor 600 MHz + 256k No

2.8 V Pentium III Xeon processor 600 MHz + 1M, 2M Yes

5/12 V Pentium III Xeon processor 600 MHz + 1M, 2M No

512k, 1M, 2M Yes

The L2 cache is located on the substrate of the S.E.C. cartridge. The cache:

• Is offered in 512 KB, 1 MB, and 2 MB configurations

• Has ECC

• Operates at the full core clock rate

Baseboard Description 15

Page 16

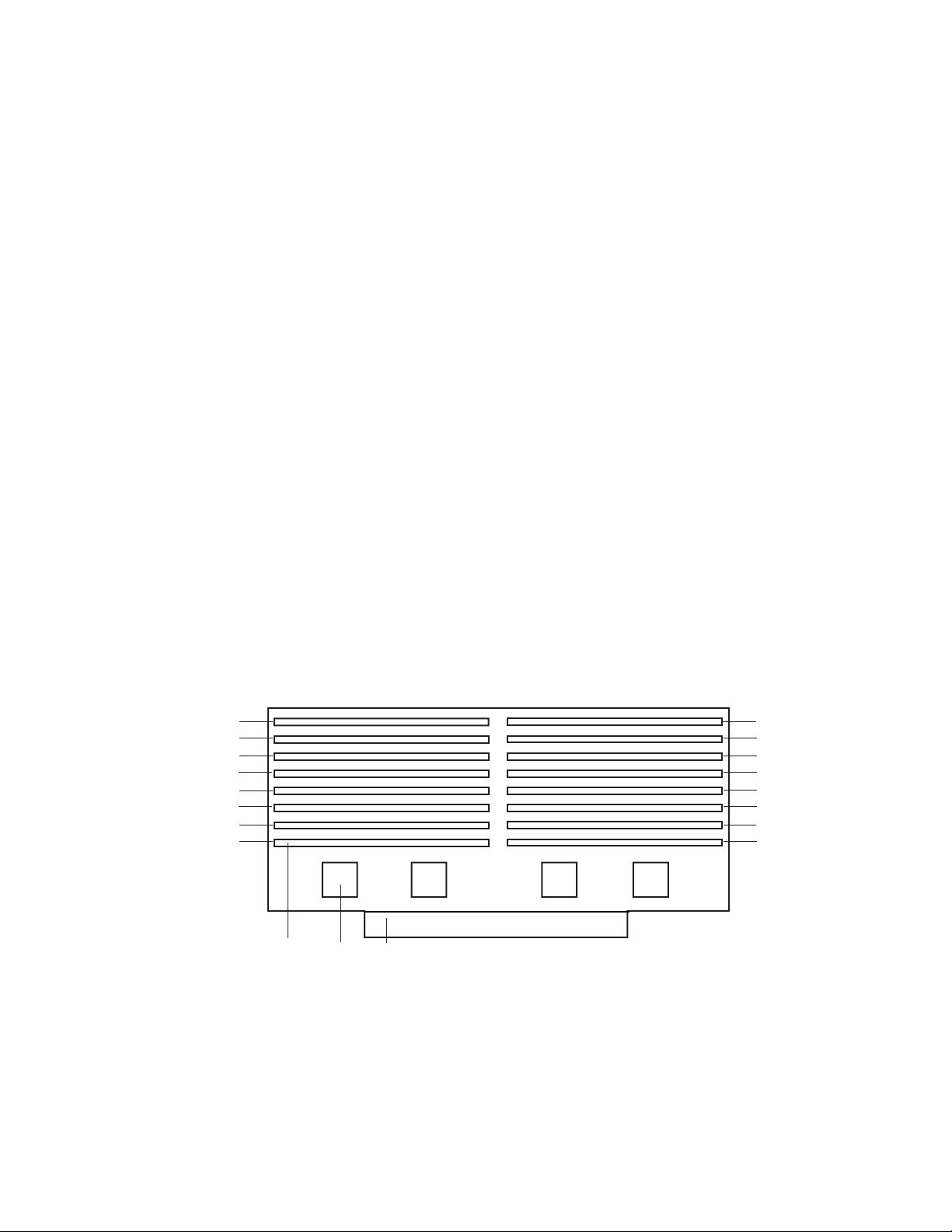

Memory

Main memory resides on an add-in board, called a memory module, designed for the SKA4

baseboard. The memory module contains slots for 16 DIMMs, each of which must be at least

64 MB, and is attached to the baseboard through a 330-pin connector, called the Memory

Expansion Card Connector (MECC). The memory module supports PC-100 compliant registered

ECC SDRAM memory modules. The ECC used for the memory module is capable of correcting

single-bit errors (SBEs) and detecting 100 percent of double-bit errors over one code word. Nibble

error detection is also provided.

System memory begins at address 0 and is continuous (flat addressing) up to the maximum amount

of DRAM installed (exception: system memory is noncontiguous in the ranges defined as memory

holes using configuration registers). The system supports both base (conventional) and extended

memory.

• Base memory is located at addresses 00000h to 9FFFFh (the first 1 MB).

• Extended memory begins at address 0100000h (1 MB) and extends to 3FFFFFFFFh (16 GB),

which is the limit of supported addressable memory. The top of physical memory is a

maximum of 16 GB (to 3FFFFFFFFh).

Memory amounts from 256 MB to 16 GB of DIMM are supported, with a 64/72-bit

four-way-interleaved pathway to main memory, which is also located on the module. Therefore,

data transfers between MADPs and DIMMs is in four-way interleave fashion. Each of the four

DIMMs must be populated in a bank. The 16 slots are divided into four banks of four slots each.

They are labeled A through D. Bank A contains DIMM sockets A1, A2, A3, and A4. Banks B, C,

and D each contain 4 DIMM sockets and are named in the same fashion. There are silk screens on

the module next to each DIMM socket to label its bank number. For the best thermal results,

populate the banks from A to D. For example, populate bank A and then bank B. For best

performance results, populate adjacent banks. For example, populate bank A and then bank C.

A3

C3

B3 B4

D3

A1

C1

B1

D1

XY

Figure 2. Memory Module DIMM Installation Sequence

Z

X. One of sixteen DIMM sockets

Y. One of four Memory Address Data Paths (MADP)

Z. Memory Expansion Card Connector (MECC)

A4

C4

D4

A2

C2

B2

D2

OM09919

16 SKA4 Baseboard Product Guide

Page 17

Each slot is identified by another notation. Sockets A1 through A4 are identified as J1 through J4

respectively. Sockets B1 through B4 are identified as J5 through J8. Sockets C1 through C4 are

identified as J9 through J12. Sockets D1 through D4 are identified as J13 through J16.

NOTE

✏

Based on the chipset, addressable memory can be extended to 16 GB.

However, some server systems are not thermally configured to support all

16 GB. Consult the documentation accompanying your server system to

determine the maximum memory configuration of your server system.

Some operating systems and application programs use base memory while others use both

conventional and extended memory. Examples are

†

• Base memory: Microsoft MS-DOS

†

UNIX

• Conventional and extended memory: IBM OS/2, Microsoft Windows NT, and various UNIX

MS-DOS does not use extended memory; however, some MS-DOS utility programs like RAM

disks, disk caches, print spoolers, and windowing environments use extended memory for better

performance.

The BIOS automatically detects, sizes, and initializes the memory array, depending on the type,

size, and speed of the installed DIMMs, and reports memory size and allocation to the system via

configuration registers.

, IBM OS/2†, Microsoft Windows NT†, and various

✏

NOTE

DIMM sizes and compatibility: Use DIMMs that have been tested for

compatibility with the baseboard. For a list of approved DIMMs, see the

SKA4 Memory Qualification List. The document can be found on

http://support.intel.com/support/motherboards/server/SKA4/compat.htm.

Baseboard Description 17

Page 18

Peripherals

Super I/O Chip (SIO)

The National† PC97317VUL Super I/O Plug and Play Compatible with ACPI Compliant

Controller/Extender device supports two serial ports, one parallel port, diskette drive, and

PS/2-compatible keyboard and mouse. The system provides the connector interface for each port.

Serial Ports

Both serial ports can be relocated. Each serial port can be set to one of four different COMx ports,

and each can be enabled separately. When disabled, serial port interrupts are available to add-in

boards.

Parallel Port

The SKA4 baseboard provides a 25-pin Parallel Port connector. The SIO provides an IEEE

1284-compliant 25-pin bi-directional parallel port. BIOS programming of the SIO registers enable

the parallel port, and determine the port address and interrupt. When disabled, the interrupt is

available to add-in cards.

Add-in Board Slots

The baseboard has eight slots for PCI add-in boards supported by three PCI bus segments called

PCI-A, PCI-B, and PCI-C. There are two on PCI-A, four on PCI-B, and two on PCI-C. PCI-C

supports half-length boards (5.6" to 6.3") only; the other slots support full-length boards.

The two slots for the PCI bus segment PCI-C consume a maximum of 375 mA of standby current

on a 3.3V AUX power line. The remaining six slots do not have any 3.3V Aux capabilities.

Both PCI segments A and B allow you to add, remove, or replace PCI add-in boards installed in

their slots without interrupting normal operation or powering down the system. To use this PCI

Hot-Plug (PHP) feature, a server system requires PCI Hot-Plug software and PCI Hot-Plug capable

add-in boards. PCI Hot-Plug software usually is a driver loaded for a specific operating system.

Each Hot-Plug PCI slot has two LEDs. The green LED indicates the state of power on each slot.

The amber LED indicates an error condition with that slot.

18 SKA4 Baseboard Product Guide

Page 19

The table below summarizes typical LED states that you may encounter during a system’s

operation.

Table 3. Slot State Indicators

LED State Status

Green On

Amber Off

Green On

Amber On

Green Off

Amber On

Green blinking

Amber Off

Off The slot is powered off.

The slot is on and functioning normally.

The slot is on and the card requires attention.

The slot is off and the card in the slot requires attention.

Slot power is transition from either ON to OFF or OFF to ON.

PCI features include:

• 33 or 66 MHz bus speed

• 32-bit or 64-bit memory addressing

• 3.3V or 5V signaling environment

• Independent bus structure supports transfers up to 1.2 GB/sec

• 8-, 16-, 32-, or 64-bit data transfers

• Plug and Play ready

• Parity enabled

DesotoE2 Hot-Plug PCI Controller

The DesotoE2 Hot-Plug PCI controller is a 32-bit PCI bus agent that operates at either 33 or

66 MHz. The PCI controller manages PHP functionality for the PCI segment it resides on. There

is a DesotoE2 controller on PCI segments A and B. The DesotoE2 PHP controller is:

• ACPI compliant

†

• Compatible with Compaq’s

PHP controller design

• Supports either a 3.3 V or 5 V PCI bus

The DesotoE2 is responsible for:

• Managing power application and removal to individual slots

• Properly resetting newly-added PCI boards prior to bringing the board online

• Managing connection and disconnection of the PCI signals between the P CI bus and the add-

in board

• Managing seamless addition and removal of individual PCI add-in boards without impacting

bus functionality

IDE Interface

The Open South Bridge (OSB4) acts as a PCI-based fast IDE controller. The controller supports

programmed I/O and bus master transfers. While the OSB4 supports two IDE channels, the SKA4

baseboard uses only the primary IDE channel and provides a single 40 pin IDE connector.

Baseboard Description 19

Page 20

USB Interface

The SKA4 baseboard provides a dual external USB connector for the back panel of a server

system. The connector is defined by the USB Specification, Revision 1.0. Both ports function

identically with the same bandwidth. The SKA4 baseboard also provides a proprietary internal

USB header.

Network Interface Controller (NIC)

The SKA4 baseboard supports a 10BASE-T/100BASE-TX network subsystem based on the

®

82559 Fast Ethernet Multifunction PCI/CARDBus controller. The Intel 82559 controller is

Intel

a highly integrated PCI LAN controller in a 196-pin Ball Grid Array (BGA) supporting 10 or

100 Mbps fast Ethernet networks.

Supported network features include:

• Glueless 32-bit PCI Bus Master Interface compatible with the PCI Local bus Specification

• 82596-like chained memory structure with improved dynamic transmit chaining for enhanced

performance

• Programmable transmit threshold for improved bus utilization

• Early receive interrupt for concurrent processing of receive data

• On-chip counters for network management

• Auto-detect and auto-switching for 10 or 100 Mbps network speeds

• Support for both 10 and 100 Mbps networks

• Integrated physical interface to TX magnetics

• The magnetics component terminates the 100BASE-TX connector interface and a flash device

stores the network ID

Video

The SKA4 baseboard provides an ATI Rage IIc VGA Graphics Accelerator, along with video

Synchronous Graphics RAM (SGRAM) and support circuitry for an embedded Super VGA

(SVGA) video subsystem. The ATI Rage IIc chip contains an SVGA video controller, clock

generator, BitBLT engine, and a RAM digital-to-analog Converter (RAMDAC) in a 208-pin

PQFP. One 256K x 32 SGRAM chip provides 2 MB of 10-ns video memory. The baseboard does

not support adding video memory to the system. The SVGA subsystem supports a variety of

modes, up to 1600 x 1200 resolution, or up to 16.7 M colors.

The SVGA subsystem also supports analog VGA monitors, single- and multi-frequency, interlaced

and non-interlaced, up to 100 Hz vertical retrace frequency. The SKA4 baseboard provides a

standard 15-pin VGA connector and video blanking logic for server management console

redirection support.

Depending on the environment, the controller displays up to 16.7 M colors in some video

resolutions.

20 SKA4 Baseboard Product Guide

Page 21

SCSI Controller

The baseboard includes two SCSI controllers. A dual function SCSI controller

(Adaptec AIC-7899) is on the PCI-B bus, and a PCI wide SCSI controller (Adaptec AIC-7880) is

on the PCI-C bus.

The Adaptec AIC-7899 SCSI controller contains two independent SCSI controllers that share a

single PCI bus master interface as a multifunction device, packaged in a 352-pin ball grid array

(BGA). Internally, each controller is identical, capable of operations using either 16-bit SE or Low

Voltage Differential (LVD) SCSI providing 40 MBps (Ultra-wide SE), 80 MBps (Ultra 2), or

160 MBps (Ultra 160/m).

In the SKA4 implementation, both controller A and controller B attach to a 68-pin 16-bit

differential SCSI connector LVD interface. Each controller has its own set of PCI configuration

registers and SCSI I/O registers. As a PCI bus master, the AIC-7899 controller supports burst data

transfers on PCI up to the maximum rate of 266 MBps using on-chip buffers.

The AIC-7880 controller contains a single SCSI controller with full-featured PCI bus master

interface in a 160-pin Plastic Quad Flat Pack (PQFP). The controller supports either 8- or 16-bit

Fast SCSI providing 10 MBps or 20 MBps (Fast-10) throughput, or Fast-20 SCSI that can burst

data at 20 MBps or 40 MBps. As a PCI 2.1 bus master, the AIC-7880 controller supports burst

data transfers on PCI up to the maximum rate of 133 MBps using the on-chip 256-byte FIFO.

The SKA4 AIC-7880 implementation offers 8-bit or 16-bit SCSI connectors and operation at data

transfer rates of 10, 20, or 40 MBps. The AIC-7880 controller also offers active negation outputs,

controls for external differential transceivers, a disk activity output, and a SCSI terminator powerdown control. Active negation outputs reduce the chance of data errors by actively driving both

polarities of the SCSI bus, avoiding indeterminate voltage levels and common-mode noise on long

cable runs. The SCSI output drivers can directly drive a 48-mA single-ended SCSI bus with no

additional drivers. The SCSI segment can support up to 15 devices.

The AIC-7880 controller can be used as an 8-bit controller via the narrow, 50-pin connector and as

a 16-bit controller via the wide, 68-pin connector. As a result, the AIC-7880 controller is not

always at one end of the SCSI bus, and termination is controlled through some simple circuitry.

The circuitry senses whether there is a device attached through the narrow 50-pin connector or the

wide 68-pin connector. When there are devices off both connectors, the termination is on for the

upper 8 bits of data and the parity bit associated with these data lines. All other signals are not

terminated on board and are terminated by the devices attached through the connector. When there

is a device on only one connector (either wide or narrow), all on-board termination is on.

Baseboard Description 21

Page 22

IDE Controller

IDE is a 16-bit interface for intelligent disk drives with AT† disk controller electronics onboard.

The Open South Bridge (OSB4) acts as a PCI-based fast IDE controller. The device controls:

• PIO and IDE DMA/bus master operations

• Mode 4 timings

• Transfer rates up to 33 MB/sec

• Ultra DMA 33 capacity

• Buffering for PCI/IDE burst transfers

• Master/slave IDE mode

• Up to two drives for one IDE channel

NOTE

✏

18-inch maximum length of IDE cable: An IDE signal cable can be

connected up to the IDE connector on the baseboard. However, the

maximum length of the cable is 18 inches. The cable supports up to two

devices, one at the end of the cable and the other six inches from the end.

Keyboard and Mouse

The PS/2-compatible keyboard and mouse connectors are mounted in a single-stacked housing

with the mouse connector over the keyboard. External to the system, they appear as two

connectors.

The user can plug in the keyboard and mouse to either connector before powering up the system.

BIOS detects these and configures the keyboard controller accordingly.

®

The keyboard controller is functionally compatible with the Intel

system can be locked automatically if no keyboard or mouse activity occurs for a predefined length

of time, if specified through the SSU. Once the inactivity (lockout) timer has expired, the

keyboard and mouse do not respond until the previously stored password is entered.

8042A microcontroller. The

22 SKA4 Baseboard Product Guide

Page 23

Server Management

Server management features are implemented using one microcontroller called the Baseboard

Management Controller (BMC).

Baseboard Management Controller (BMC)

The BMC and associated circuitry are powered from 5V_Standby, which remains active when

system power is switched off. The BMC is IPMI 1.0 compliant.

The primary function of the BMC is to autonomously monitor system platform management events

and log their occurrence in the nonvolatile System Event Log (SEL). The BMC is compliant to the

Intelligent Platform Management Interface Specification, Version 1.0. These events include

overtemperature and overvoltage conditions, fan failure, or chassis intrusion. While monitoring,

the BMC maintains the nonvolatile Sensor Data Record Repository (SDRR), from which run-time

information can be retrieved. The BMC provides an interface to SDRR information, so software

running on the server can poll and retrieve the current status of the platform. A shared register

interface is defined for this purpose.

Field service personnel can retrieve SEL contents after system failure for analysis by using system

®

management tools like Intel

Platform control (DPC). Because 5V_Standby provides power the BMC, SEL (and SDRR)

information is also available via the interperipheral management bus (IPMB). During monitoring,

the BMC performs the following functions:

• Baseboard temperature and voltage monitoring

• Processor presence monitoring and FRB control

• Baseboard fan failure detection and indicator control

• SEL interface management

• Sensor Data Record Repository (SDRR) interface management

• SDR/SEL timestamp clock

• Baseboard Field Replaceable Unit (FRU) information interface

• System management watchdog timer

• SMI/NMI Status Monitor

• Front panel NMI handling

• Event receiver

• IPMB Management Controller Initialization Agent

• Secure mode control, front panel lock/unlock initiation, and video blank and diskette write

protect monitoring and control

• ACPI Support

• Direct Platform Control (DPC) support

• Platform Event Paging (PEP) / Platform Event Filtering (PEF)

• Power distribution board monitoring

• Speaker beep capability. When the system is powered up, this capability is used to indicate

conditions such as "empty processor slot"

• Pentium III Xeon processor SEEPROM interface for Processor Information ROM (PIROM)

and Scratch EEPROM access

LANDesk® Server Manager, Intel Server Control (ISC), or Direct

Baseboard Description 23

Page 24

• Processor temperature monitoring

• Hot-Plug PCI slot status reporting

• Processor bus speed setting

• Chassis fan failure light control

• Chassis power fault light control

• Chassis power light control

System Security

To help prevent unauthorized entry or use of the system, the system includes a three-position key

lock/switch to permit selected access to drive bays (position is communicated to BMC). The

system also includes server management software that monitors the chassis intrusion switch.

Software Locks via the SSU or BIOS Setup

The SSU provides a number of security features to prevent unauthorized or accidental access to the

system. Once the security measures are enabled, access to the system is allowed only after the user

enters the correct password(s). For example, the SSU allows:

• Enable the keyboard lockout timer so the server requires a password to reactivate the keyboard

and mouse after a specified time-out period of 1 to 120 minutes

• Set and enable administrator and user passwords

• Set secure mode to prevent keyboard or mouse input and to prevent use of the front panel reset

and power switches

• Activate a hot key combination to enter secure mode quickly

• Disable writing to the diskette drive when secure mode is set

Using Passwords

If a user password is set and enabled, but an administrator password is not set, a user password

must be entered to boot the system and run the SSU.

If both a user and administrator password is set:

• Enter either one to boot the server and enable the keyboard and mouse

• Enter the administrator password to access the SSU or BIOS Setup to change the system

configuration

Secure Mode

Configure and enable the secure boot mode by using the SSU. When secure mode is in effect,

• The system can boot and the operating system runs, but the user password must be entered for

a user to use the keyboard or mouse

• The system cannot be turned off or reset from the front panel switches

Secure mode has no effect on functions enabled via the Server Manager Module or power control

via the real-time clock (RTC).

24 SKA4 Baseboard Product Guide

Page 25

Taking the system out of secure mode does not change the state of system power. That is, if you

press and release the power switch while secure mode is in effect, the system will not power off

when secure mode is later removed. However, if the front panel power switch remains depressed

when secure mode is removed, the system will power off.

Summary of Software Security Features

Table 4 lists the software security features and describes what protection each offers. In general,

to enable or set the features listed here, the SSU must be run and configured with the Security

Menu (described in this manual on page 39.) The table also refers to other SSU menus and to the

Setup utility. For greater detail, see Chapter 2, beginning on page 27.

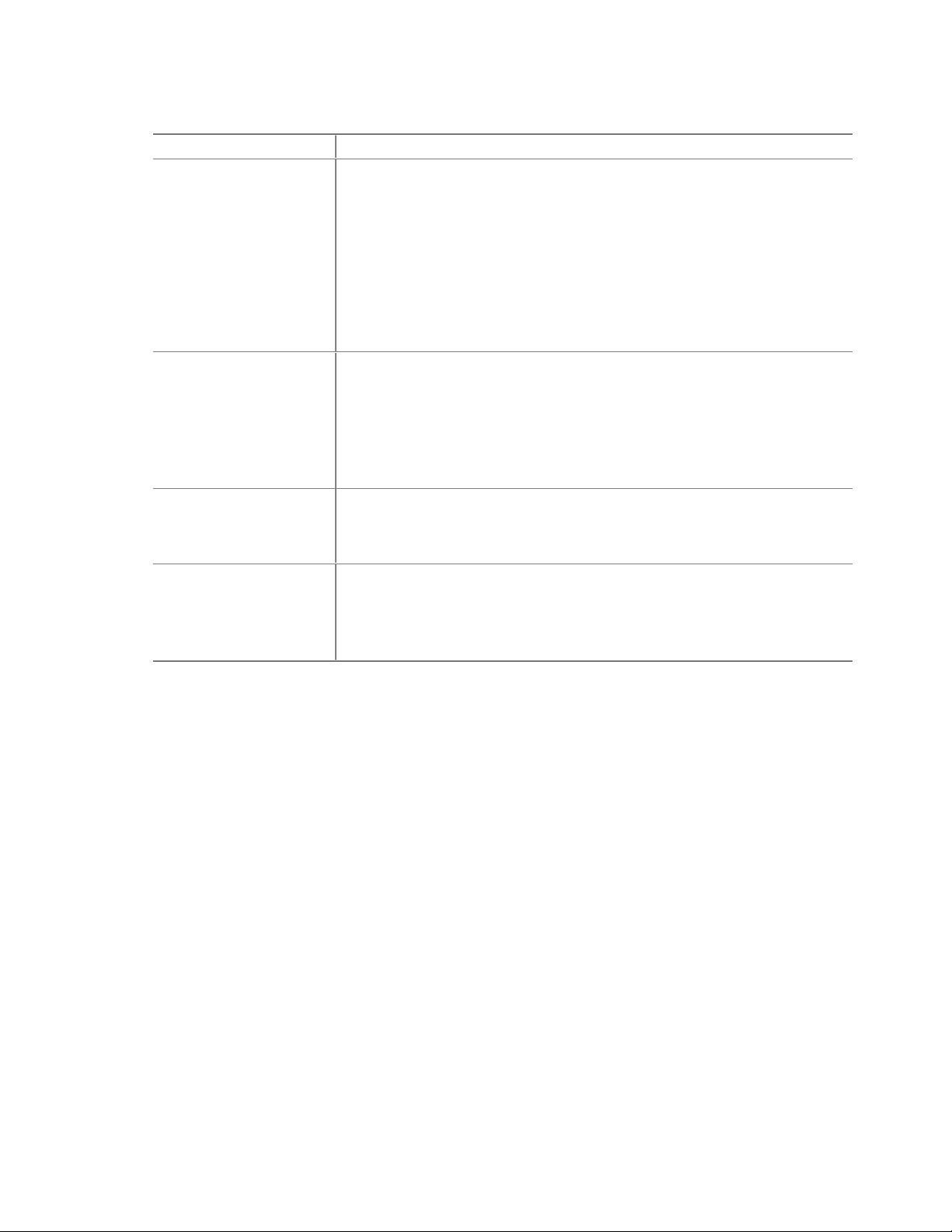

Table 4. Software Security Features

Feature Description

Secure mode

Disable writing to diskette In secure mode, the server will not boot from or write to a diskette unless a

Disable the power and

reset buttons

Set a time out period so

that keyboard and mouse

input are not accepted

Also, screen can be

blanked, and writes to

diskette can be inhibited

How to enter secure mode:

• Setting and enabling passwords automatically places the system in secure

mode.

• If a hot key combination is set (through the SSU or Setup), the system can be

secured simply by pressing the key combination. This means that the user

does not have to wait for the inactivity time-out period.

When the system is in secure mode:

• The server can boot and run the operating system, but mouse and keyboard

input is not accepted until the user password is entered.

• At boot time, if a CD is detected in the CD-ROM drive or a diskette in drive A,

the system prompts for a password. When the password is entered, the

server boots from CD or diskette and disables the secure mode.

• If there is no CD in the CD-ROM drive or diskette in drive A, the server boots

from drive C and automatically goes into secure mode. All enabled secure

mode features go into effect at boot time.

To leave secure mode, enter the correct password(s).

password is entered. To set this feature, use the SSU Secur ity Subsystem

Group.

To write protect access to diskette whether the server is in secure mode or not,

use the Setup main menu, Floppy Options, and specify Floppy Access as

read only.

Power and reset buttons are always disabled when the server is in secure mode.

Specify and enable an inactivity time out period of from 1 to 120 minutes.

If no keyboard or mouse action occurs for the specified period, attempted

keyboard and mouse input will not be accepted.

The monitor display will go blank, and the diskette drive will be write protected

(if these security features are enabled through Setup or the SSU and using

onboard video).

To resume activity, enter the user password.

continued

Baseboard Description 25

Page 26

Table 4. Software Security Features (continued)

Feature Description

Control acce ss to using

the SSU: set

administrative password

Control acce ss to the

system other than SSU:

set user password

Boot without keyboard The system can boot with or without a keyboard. During POST, before the

Specify the boot

sequence

To control access to setting or changing the system configuration, set an

administrative password and enable it through Setup or the SSU.

If both the administrative and user passwords are enabled, either can be used to

boot the server or enable the keyboard and/or mouse, but only the

administrative password will allow Setup and the SSU to be changed.

To disable a password, change it to a blank entry or press CTRL-D in the

Change Password menu of the Administrative Password Option menu found in

the Security Subsystem Group.

If you cannot access Setup or the SSU to clear the password, change the Clear

Password jumper. See "CMOS Clear Jumper" on page 109.

To control access to usin g the system, se t a user passwo rd and enable it

through Setup or the SSU.

To disable a password, change it to a blank entry or press CTRL-D in the

Change Password menu of the User Password Option menu found in the

Security Su bsystem Group.

If you cannot access Setup or the SSU to clear the password, change the Clear

Password jumper. See "CMOS Clear Jumper" on page 109.

system complet es the boot sequence, the BIOS automatically detects and tests

the keyboard if it is present and displays a message. There is no entry in the

SSU to enable or disable a keyboard.

The sequence specified on the menu in the SSU MultiBoot Group will determine

the boot order. If secure mode is enabled (a user password is set), then the

user is prompted for a password before the server fully boots. If secure mode is

enabled and the “Secure Boot Mode” option is also enabled, the server fully

boots but requires a password before accepting any keyboard or mouse input.

26 SKA4 Baseboard Product Guide

Page 27

2 Configuration Software and Utilities

This chapter describes the Power-On Self Test (POST) and system configuration utilities. The

table below briefly describes the utilities.

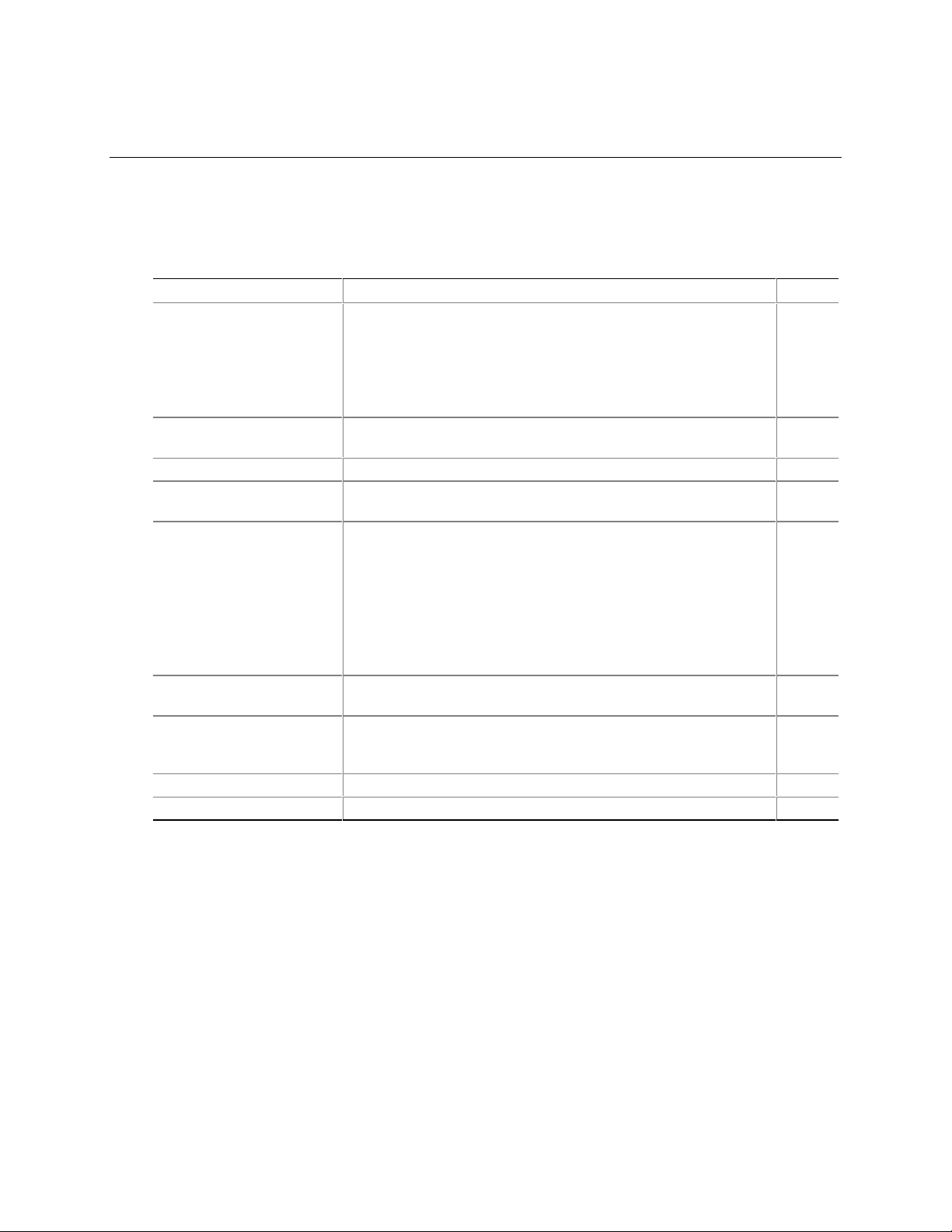

Table 5. Configuration Utilities

Utility Description and brief procedure Page

BIOS Setup If the system does not have a diskette drive, or the drive is

disabled or misconfigured, use Setup to enable it.

Or, you can move the CMOS jumper on the system board from the

default setting (Protect CMOS memory) to the Clear setting; this

will allow most system configurations to boot. For the procedure to

do this, see “CMOS Clear Jumper” on page 109.

Changing Boot Device

Priority

SCSI

Select

Utility Use to configure the SCSI controllers in the system. 45

Adaptec SCSI Utility Use to configure or view the settings of the SCSI host adapters

Server Setup Utility (SSU) Use for extended system configuration of onboard resources and

Direct Platform Control

(DPC) Console

FRUSDR Load Utility Use to update the Field Replacement Unit (FRU), Sensor Data

BIOS Update Utility Use to update the BIOS or recover from a corrupted BIOS update. 53

Firmware Update Utility Use to update BMC flash ROM. 56

Use this option to change the boot device priority temporarily or

permanently.

and onboard SCSI devices in the system.

add-in boards, viewing the system event log (SEL), setting boot

device pri ority, or setting system security options.

The SSU can be run from either the configuration software CD or

from a set of bootable diskettes. You can create the diskettes from

the CD.

Information entered via the SSU overrides information entered via

Setup.

Use to access and monitor the server remotely. 49

Record (SDR), and Desktop Management Interface (DMI) flash

components.

29

44

46

47

51

27

Page 28

Hot Keys

Use the keyboard’s numeric pad to enter numbers and symbols.

Table 6. Hot Keys

To do this: Press these keys

Clear memory and reload the operating

systemthis is a system reset.

Secure your system immediately. <Ctrl+Alt>+hot key (Set yo ur hot key combination

Enter the Adaptec SCSI Utility during BIOS POST. <Ctrl+A>

Enter BIOS Setup during BIOS POST. F2

Abort memory test during BIOS POST. ESC (Press while BIOS is updating memory size on

<Ctrl+Alt+Del>

with the SSU or Setup.)

screen.)

Power-On Self Test (POST)

Each time you turn on the system, the BIOS begins execution of the Power-On Self Test (POST).

POST discovers, configures, and tests the processors, memory, keyboard, and most installed

peripheral devices. The length of time needed to test memory depends on the amount of memory

installed. POST is stored in flash memory.

1. Turn on your video monitor and system. After a few seconds, POST begins to run and a splash

screen is displayed.

2. While the splash screen is displayed, you can either

• press <F2> to enter the BIOS Setup (see "Using BIOS Setup" on page 29)

OR

• press <Esc> to change the boot device priority for this boot only (see "Changing the Boot

Device Priority Temporarily" on page 44).

3. After pressing <F2> or <Esc> during POST, you can press <Ctrl+A> to run the SCSISelect

Utility. For more information, see "Running the SCSISelect Utility" on page 45.

4. If you do not press <F2> or <Esc> and do NOT have a device with an operating system

loaded, the boot process continues and the system beeps once. The following message is

displayed:

Operating System not found

5. At this time, pressing any key causes the system to attempt a reboot. The system searches all

removable devices in the order defined by the boot priority.

6. If you want to boot from a hard drive loaded with an operating system, make sure that the hard

drive is installed and push the Reset button on the front panel.

28 SKA4 Baseboard Product Guide

Page 29

Using BIOS Setup

This section describes the BIOS Setup options. Use Setup to change the system configuration

defaults. You can run Setup with or without an operating system being present. Setup stores most

of the configuration values in battery-backed CMOS; the rest of the values are stored in flash

memory. The values take effect when the system is booted. POST uses these values to configure

the hardware; if the values and the actual hardware do not agree, POST generates an error

message. You must run Setup to specify the correct configuration.

†

Run Setup: Run Setup to modify any standard PC-AT

• Select diskette drive

• Select parallel port

• Select serial port

• Set time/date (to be stored in RTC)

• Configure hard drive(s)

• Specify boot device sequence

• Enable SCSI BIOS

Run SSU, not Setup: Run the SSU instead of Setup to do the following:

• Enter or change information about a board

• Alter system resources (e.g., interrupts, memory addresses, I/O assignments) to user-selected

choices instead of choices selected by the BIOS resource manager

baseboard feature such as:

Record Setup Set tings

If the default values ever need to be restored (after a CMOS clear, for example), Setup must be run

again. Referring to the worksheets could make the task easier.

If Setup is Not Accessible

If the diskette drive is misconfigured and you cannot use Setup to correct the problem, you might

need to clear CMOS memory. You must open the system, change a jumper setting, use Setup to

check and set diskette drive options, and change the jumper back. For a step-by-step procedure,

see “CMOS Clear Jumper” on page 109.

Starting Setup

Setup can be entered under several conditions:

• When you turn on the system, after POST completes the memory test.

• When you reboot the system by pressing <Ctrl+Alt+Del> while at the DOS operating system

prompt.

• When you have moved the CMOS jumper on the baseboard to the “Clear CMOS” position

(enabled); for a step-by-step procedure, see “CMOS Clear Jumper” on page 109.

In the three conditions listed above, the following prompt is displayed:

Press <F2> to enter SETUP

Configuration Software and Utilities 29

Page 30

In a fourth condition, when CMOS/NVRAM has been corrupted, these other prompts are

displayed, but not the <F2> prompt:

Warning: cmos checksum invalid

Warning: cmos time and date not set

In this condition, the BIOS loads default values for CMOS and attempts to boot.

Setup Menus

Setup has six major menus and several submenus:

1. Main Menu

• Primary IDE Master and Slave Adapters

• Processor Settings Information

2. Advanced Menu

• PCI Configuration

Embedded Video Controller

Embedded Legacy SCSI

Embedded Dual Ultra 160 SCSI

Embedded NIC

PCI Devices, Slots 1 - 8

Hot-Plug PCI Control

• Integrated Peripheral Configuration

• Advanced Chipset Control

3. Security Menu

• Passwords

• Lockout features

4. Server Menu

• System Management

• Console Redirection

• EMP Configuration

• PEP Management

5. Boot Menu

• Boot Device Priority

• Hard Drive

• Removable Devices Selections

6. Exit Menu

30 SKA4 Baseboard Product Guide

Page 31

Navigation

To: Press:

Get general help <F1> or <Alt+H>

Move between menus ← →

Go to the previous item ↑

Go to the next Item ↓

Change the value of an item + or Select an item or display a submenu <Enter>

Leave a submenu or exit Setup <Esc>

Reset to Setup defaults <F9>

Save and exit Setup <F10>

Display

When you see this: What it means:

On screen, an option is shown but you cannot

select it or move to that field.

On screen, the phrase Press Enter appears next

to the option.

You cannot change or configure the option in that

menu screen for one of the following reasons:

• The option is auto-configured or auto-detected.

• You must use a different Setup screen to change it.

• You must use the SSU.

Press <Enter> to display a submenu that is either a

separate full-screen menu or a pop-up menu with one

or more choices.

The rest of this section lists the features that display onscreen after you press <F2> to enter Setup.

Not all of the option choices are described, because (1) a few are not user-selectable but are

displayed for your information, and (2) many of the choices are relatively self-explanatory.

Main Menu

Table 7 lists the selections you can make on the Main Menu itself. Use the submenus for other

selections. Default values are in bold.

Table 7. Main Menu

Feature Choices Description

System Time HH:MM:SS Sets the system time.

System Date MM/DD/YYYY Sets the system date .

Legacy Diskette A: Disabled

1.44/1.25 MB 3½"

2.88 MB 3½"

Legacy Diskette B:

Primary IDE Master N/A Enters submenu.

Primary IDE Slave N/A Enters submenu.

Processor Settings N/A Enters submenu.

Language

Disabled

1.44/1.25 MB 3½"

2.88 MB 3½"

English (US)

French

Spanish

German

Italian

Japanese (Kanji)

Selects the diskette type.

Selects the diskette type.

Selects which language BIOS displays.

NOTE

✏

Serial redirection does

not work with Kanji.

Configuration Software and Utilities 31

Page 32

Primary IDE Master and Slave Submenu

In the following table, the features other than “Type” appear only for Type Auto if a drive is

detected.

Table 8. Primary IDE Master and Slave Submenu

Feature Choices Description

Type User

Auto

CD-ROM

ATAPI Removable

Multi-Sector

Transfers

LBA Mode

Control

32 Bit I/O

Transfer Mode

Ultra DMA Mode

Disabled

2, 4, 8, or 16 sectors

Disabled

Enabled

Disabled

Enabled

Standard

Fast PIO 1

Fast PIO 2

Fast PIO 3/DMA 1

Fast PIO 4/DMA 2

Disabled

Enabled

User allows the manual entry of all fields described below.

Auto allo ws the system to at tempt auto-detection of the drive

type.

CD-ROM allows the manual entry of fields described below.

Determines the number of sectors per block for multisector

transfers.

For Type Auto, this field is informational only.

For Type Auto, this field is informational only.

Enabling allows 32-bit IDE data transfers.

For Type Auto, this field is informational only.

Selects the method for moving data to and from the drive.

For Type Auto, this field is informational only.

For use with Ultra DMA drives. Ultra DMA is disabled by

default to work around a chipset erratum.

For Type Auto, this field is informational only.

Processor Settings Submenu

Table 9. Processor Settings Submenu

Feature Choices Description

Processor Rete st

Processor Serial Number

Memory Cache

Measured Processor Speed N/A Reports the speed of Processor 1.