Page 1

Intel®StrongARM*SA-1110

Microprocessor

Developer’s Manual

October 2001

Notice: Verify with your local Intel sales office that you have the latest technical information before

finalizing a design.

Order Number: 278240-004

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever,and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SA-1110 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current

characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © Intel Corporation, 2001

*Other names and brands may be claimed as the property of others.

SA-1110 Developer’s Manual

Page 3

Contents

1 Introduction

1.1 Intel® StrongARM SA-1110 Microprocessor ..............................................................................21

1.2 Overview.....................................................................................................................................24

1.3 Example System.........................................................................................................................25

1.4 ARM Architecture........................................................................................................................26

1.4.1 26-Bit Mode....................................................................................................................26

1.4.2 Coprocessors .................................................................................................................26

1.4.3 Memory Management.....................................................................................................26

1.4.4 Instruction Cache............................................................................................................26

1.4.5 Data Cache.....................................................................................................................26

1.4.6 Write Buffer.....................................................................................................................27

1.4.7 Read Buffer ....................................................................................................................27

2 Functional Description

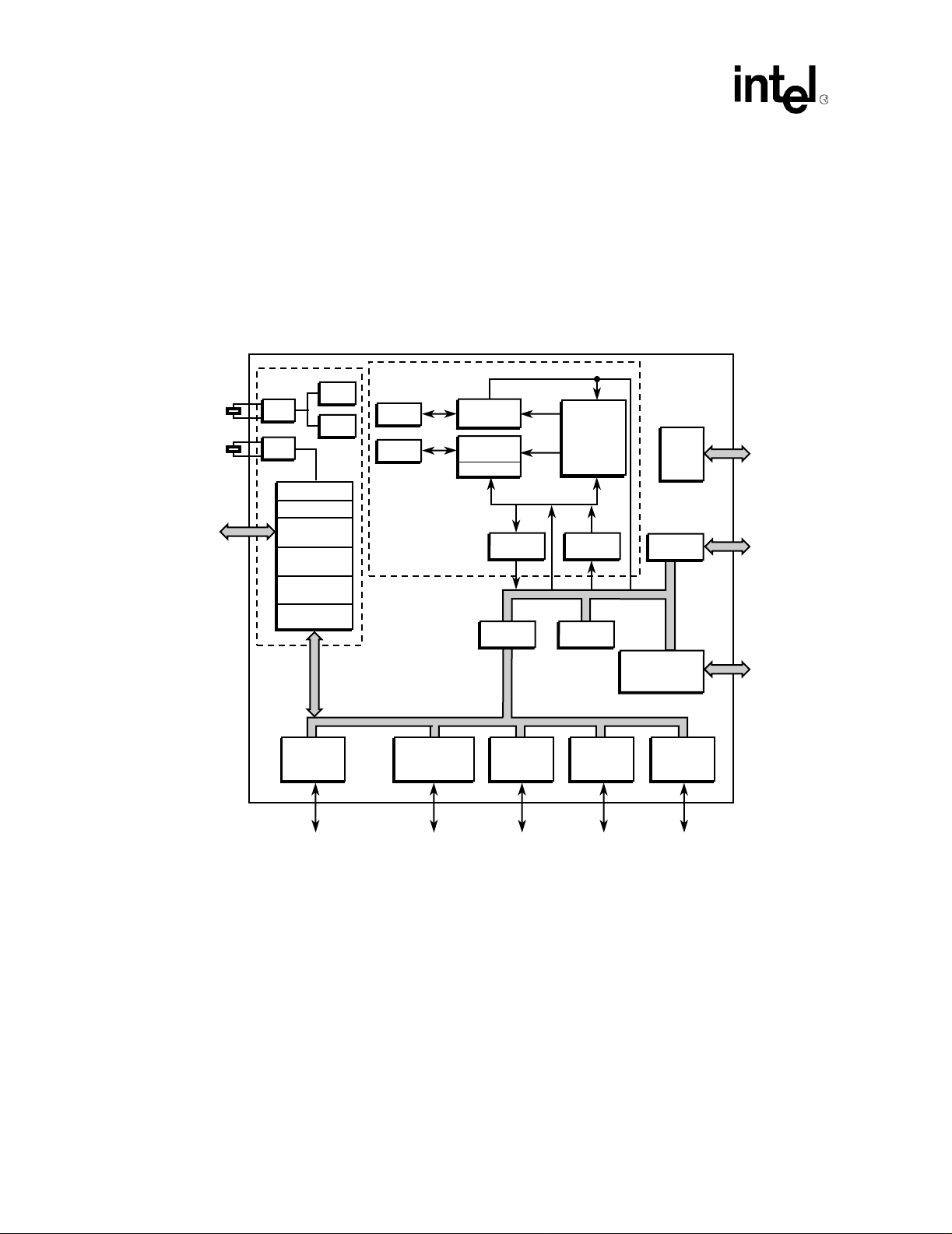

2.1 Block Diagram.............................................................................................................................29

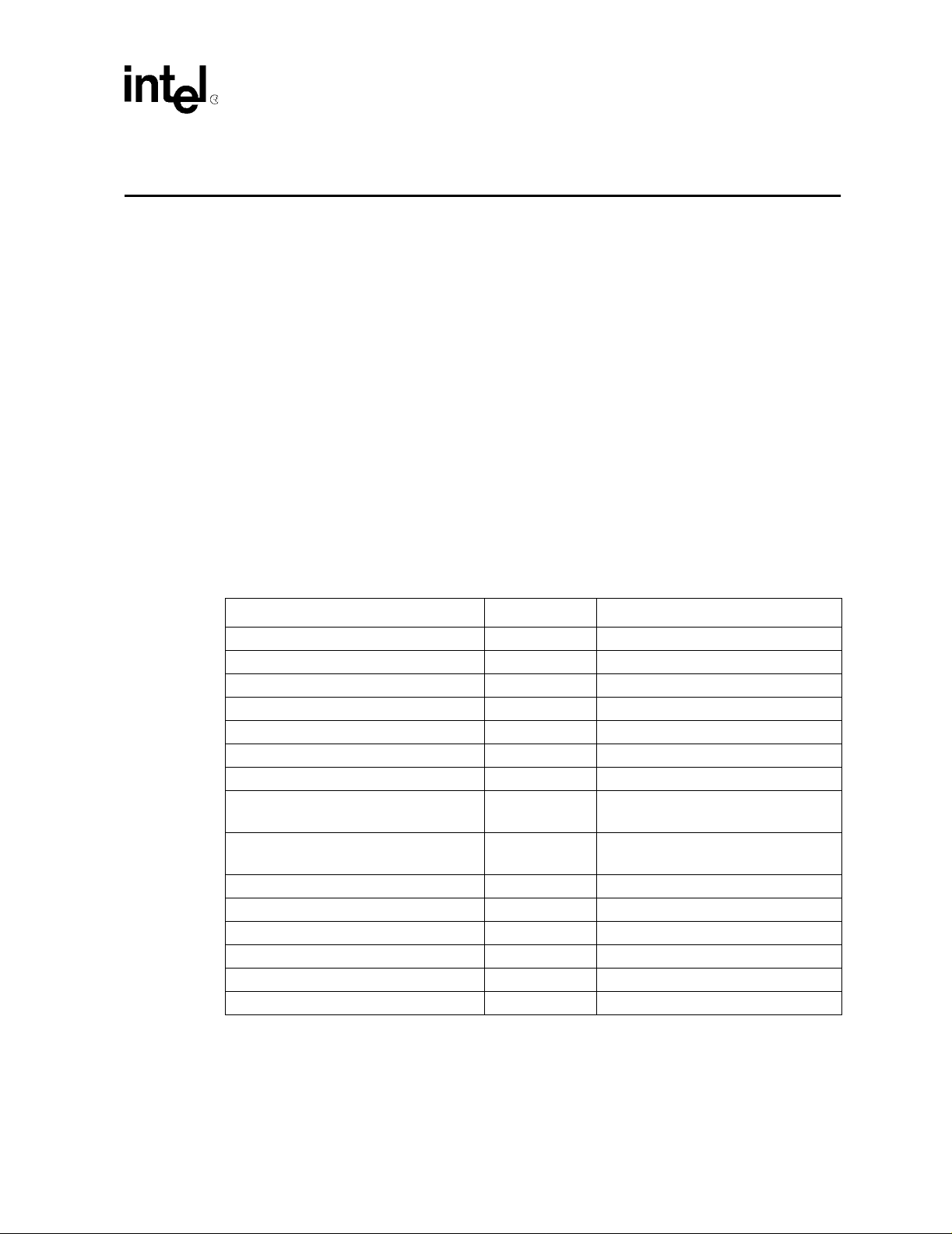

2.2 Inputs/Outputs.............................................................................................................................31

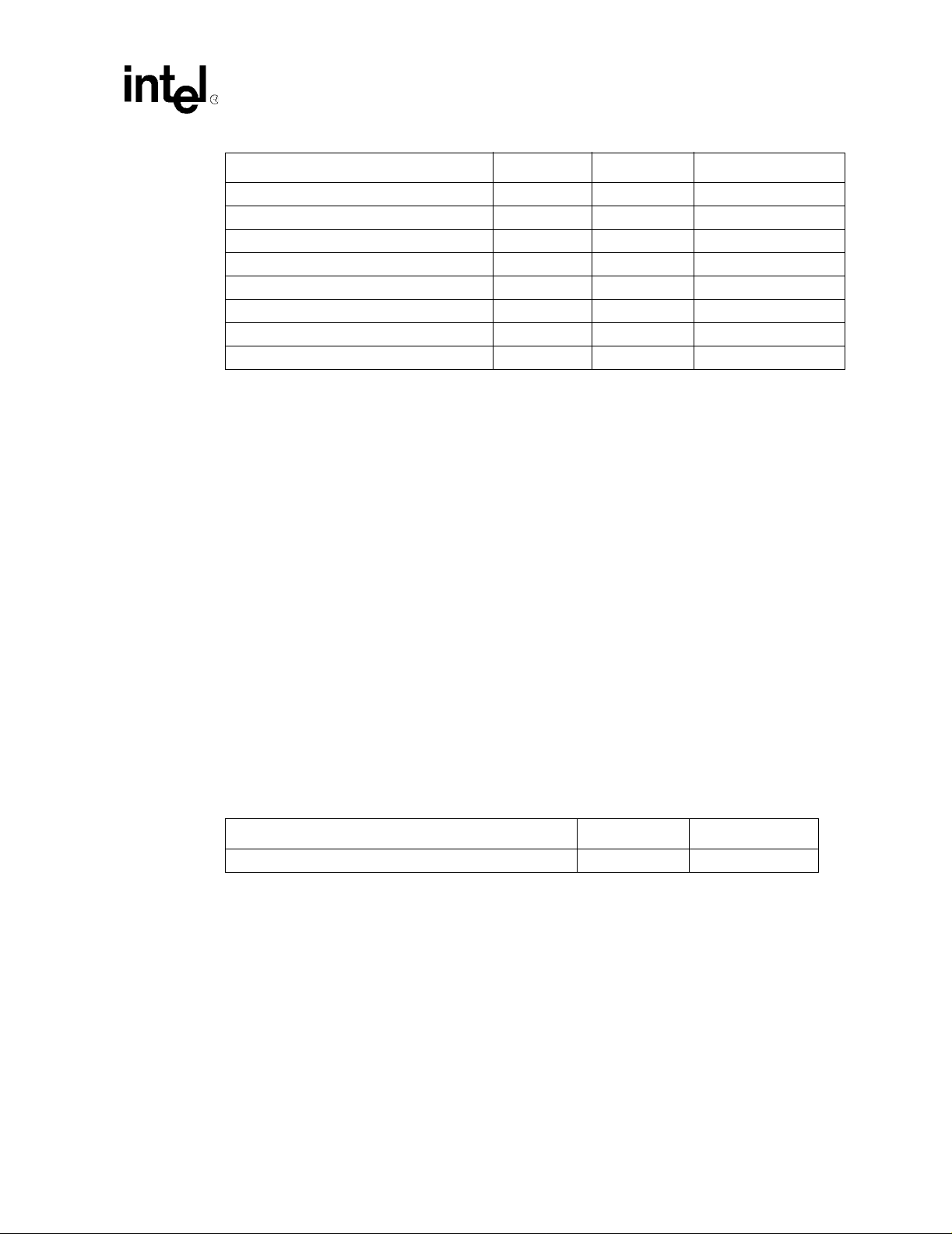

2.3 Signal Description .......................................................................................................................32

2.4 Memory Map...............................................................................................................................36

3 ARM Implementation Options

3.1 Big and Little Endian...................................................................................................................39

3.2 Exceptions...................................................................................................................................39

3.2.1 Power-Up Reset.............................................................................................................40

3.2.2 ROM Size Select............................................................................................................40

3.2.3 Abort...............................................................................................................................41

3.2.4 Vector Summary.............................................................................................................42

3.2.5 Exception Priorities.........................................................................................................42

3.2.6 Interrupt Latencies and Enable Timing...........................................................................43

3.3 Coprocessors..............................................................................................................................43

4 Instruction Set

4.1 Instruction Set.............................................................................................................................45

4.2 Instruction Timing........................................................................................................................45

5 Caches, Write Buffer, and Read Buffer

5.1 Instruction Cache (Icache) ..........................................................................................................47

5.1.1 Icache Operation ............................................................................................................47

5.1.2 Icache Validity ................................................................................................................47

5.1.2.1 Software Icache Flush..................................................................................... 47

5.1.3 Icache Enable/Disable and Reset ..................................................................................48

5.1.3.1 Enabling the Icache......................................................................................... 48

5.1.3.2 Disabling the Icache........................................................................................ 48

5.2 Data Caches (Dcaches)..............................................................................................................48

5.2.1 Cacheable Bit – C...........................................................................................................49

5.2.1.1 Cacheable Reads – C = 1............................................................................... 49

SA-1110 Developer’s Manual 3

Page 4

5.2.1.2 Noncacheable Reads – C = 0..........................................................................49

5.2.2 Bufferable Bit – B ...........................................................................................................49

5.2.3 Software Dcache Flush ..................................................................................................50

5.2.3.1 Doubly Mapped Space.....................................................................................50

5.2.4 Dcaches Enable/Disable and Reset...............................................................................50

5.2.4.1 Enabling the Dcaches......................................................................................51

5.2.4.2 Disabling the Dcaches .....................................................................................51

5.3 Write Buffer (WB)........................................................................................................................51

5.3.1 Bufferable Bit..................................................................................................................51

5.3.2 Write Buffer Operation....................................................................................................51

5.3.2.1 Writes to a Bufferable and Cacheable Location (B=1,C=1).............................51

5.3.2.2 Writes to a Bufferable and Noncacheable Location (B=1,C=0) .......................52

5.3.2.3 Unbufferable and Noncacheable Writes (B=0, C=0)........................................52

5.3.2.4 Writes to a Non-Bufferable and Cacheable Location (B=0, C=1)....................52

5.3.3 Enabling the Write Buffer ...............................................................................................52

5.3.3.1 Disabling the Write Buffer ................................................................................52

5.4 Read Buffer (RB) ........................................................................................................................52

6 Coprocessors

6.1 Internal Coprocessor Instructions...............................................................................................55

6.2 Coprocessor 15 Definition...........................................................................................................56

6.2.1 Register 0 – ID ...............................................................................................................56

6.2.2 Register 1 – Control .......................................................................................................57

6.2.3 Register 2 – Translation Table Base..............................................................................58

6.2.4 Register 3 – Domain Access Control .............................................................................58

6.2.5 Register 4 – RESERVED ...............................................................................................59

6.2.6 Register 5 – Fault Status................................................................................................59

6.2.7 Register 6 – Fault Address.............................................................................................59

6.2.8 Register 7 – Cache Control Operations .........................................................................59

6.2.9 Register 8 – TLB Operations..........................................................................................60

6.2.10 Register 9 – Read-Buffer Operations.............................................................................60

6.2.11 Registers 10 – 12 RESERVED ......................................................................................61

6.2.12 Register 13 – Process ID Virtual Address Mapping .......................................................61

6.2.13 Register 14 – Debug Support (Breakpoints) ..................................................................62

6.2.14 Register 15 – Test, Clock, and Idle Control....................................................................63

7 Memory Management Unit (MMU)

7.1 Overview.....................................................................................................................................65

7.1.1 MMU Registers...............................................................................................................65

7.2 MMU Faults and CPU Aborts......................................................................................................65

7.3 Data Aborts.................................................................................................................................65

7.3.1 Cacheable Reads (Linefetches).....................................................................................66

7.3.2 Buffered Writes...............................................................................................................66

7.4 Interaction of the MMU, Icache, Dcache, and Write Buffer.........................................................66

7.5 Mini Data Cache .........................................................................................................................67

8Clocks

8.1 Intel® StrongARM SA-1110 Crystal Oscillators..........................................................................69

8.2 Core Clock Configuration Register .............................................................................................70

8.2.1 Restrictions on Changing the Core Clock Configuration................................................71

4 SA-1110 Developer’s Manual

Page 5

8.3 Driving Intel® StrongARM SA-1110 Crystal Pins from an External Source................................71

8.4 Clocking During Test...................................................................................................................72

9 System Control Module

9.1 General-Purpose I/O...................................................................................................................73

9.1.1 GPIO Register Definitions ..............................................................................................74

9.1.1.1 GPIO Pin-Level Register (GPLR).................................................................... 75

9.1.1.2 GPIO Pin Direction Register (GPDR).............................................................. 76

9.1.1.3 GPIO Pin Output Set Register (GPSR) and Pin Output

Clear Register (GPCR) ................................................................................... 77

9.1.1.4 GPIO Rising-Edge Detect Register (GRER) and

Falling-Edge Detect Register (GFER)............................................................. 78

9.1.1.5 GPIO Edge Detect Status Register (GEDR)................................................... 79

9.1.1.6 GPIO Alternate Function Register (GAFR) ..................................................... 80

9.1.2 GPIO Alternate Functions...............................................................................................81

9.1.2.1 3.6864 MHz Option for GP 27 Alternate Output Function............................... 82

9.1.3 GPIO Register Locations................................................................................................82

9.2 Interrupt Controller ......................................................................................................................83

9.2.1 Interrupt Controller Register Definitions .........................................................................84

9.2.1.1 Interrupt Controller Pending Register (ICPR).................................................. 84

9.2.1.2 Interrupt Controller IRQ Pending Register (ICIP) and

FIQ Pending Register (ICFP).......................................................................... 86

9.2.1.3 Interrupt Controller Mask Register (ICMR)...................................................... 87

9.2.1.4 Interrupt Controller Level Register (ICLR)....................................................... 88

9.2.1.5 Interrupt Controller Control Register (ICCR)................................................... 89

9.2.2 Interrupt Controller Register Locations...........................................................................90

9.3 Real-Time Clock..........................................................................................................................90

9.3.1 RTC Counter Register (RCNR)......................................................................................90

9.3.2 RTC Alarm Register (RTAR)..........................................................................................91

9.3.3 RTC Status Register (RTSR) .........................................................................................91

9.3.4 RTC Trim Register (RTTR).............................................................................................93

9.3.5 Trim Procedure...............................................................................................................93

9.3.5.1 Oscillator Frequency Calibration..................................................................... 93

9.3.5.2 RTTR Value Calculations................................................................................ 94

9.3.6 Real-Time Clock Register Locations ..............................................................................95

9.4 Operating System Timer .............................................................................................................95

9.4.1 OS Timer Count Register (OSCR) .................................................................................96

9.4.2 OS Timer Match Registers 0–3 (OSMR 0, OSMR 1, OSMR 2, OSMR 3)......................96

9.4.3 OS Timer Watchdog Match Enable Register (OWER)...................................................96

9.4.4 OS Timer Status Register (OSSR).................................................................................97

9.4.5 OS Timer Interrupt Enable Register (OIER)...................................................................98

9.4.6 Watchdog Timer.............................................................................................................98

9.4.7 OS Timer Register Locations .........................................................................................99

9.5 Power Manager..........................................................................................................................99

9.5.1 Run Mode.......................................................................................................................99

9.5.2 Idle Mode........................................................................................................................99

9.5.2.1 Entering Idle Mode........................................................................................ 100

9.5.2.2 Exiting Idle Mode........................................................................................... 100

9.5.3 Sleep Mode ..................................................................................................................101

SA-1110 Developer’s Manual 5

Page 6

9.5.3.1 CPU Preparation for Sleep Mode ..................................................................101

9.5.3.2 Events Causing Entry into Sleep Mode .........................................................101

9.5.3.3 The Sleep Shutdown Sequence ....................................................................101

9.5.3.4 During Sleep Mode ........................................................................................102

9.5.3.5 The Sleep Wake-Up Sequence .....................................................................103

9.5.3.6 Booting After Sleep Mode..............................................................................103

9.5.3.7 Reviving the DRAMs from Self-Refresh Mode...............................................104

9.5.4 Notes on Power Supply Sequencing............................................................................104

9.5.5 Assumed Behavior of an Intel® StrongARM SA-1110 System in Sleep Mode ............104

9.5.6 Pin Operation in Sleep Mode .......................................................................................106

9.5.7 Power Manager Registers............................................................................................107

9.5.7.1 Power Manager Control Register (PMCR).....................................................107

9.5.7.2 Power Manager General Configuration Register (PCFR)..............................108

9.5.7.3 Power Manager PLL Configuration Register (PPCR)....................................110

9.5.7.4 Power Manager Wake-Up Enable Register (PWER).....................................110

9.5.7.5 Power Manager Sleep Status Register (PSSR).............................................111

9.5.7.6 Power Manager Scratch Pad Register (PSPR) .............................................113

9.5.7.7 Power Manager GPIO Sleep State Register (PGSR)....................................113

9.5.7.8 Power Manager Oscillator Status Register (POSR) ......................................114

9.5.8 Power Manager Register Locations .............................................................................114

9.6 Reset Controller........................................................................................................................115

9.6.1 Reset Controller Registers ...........................................................................................115

9.6.1.1 Reset Controller Software Reset Register (RSRR) .......................................115

9.6.1.2 Reset Controller Status Register (RCSR)......................................................116

9.6.2 Reset Controller Register Locations.............................................................................117

10 Memory and PC-Card Control Module

10.1Overview of Operation ..............................................................................................................120

10.1.1 Types of Memory Accesses .........................................................................................122

10.1.2 Reads...........................................................................................................................122

10.1.3 Writes...........................................................................................................................123

10.1.4 Transaction Summary ..................................................................................................123

10.1.5 Read-Lock-Write ..........................................................................................................123

10.1.6 Aborts and Nonexistent Memory..................................................................................124

10.2Memory Interface Reset and Initialization.................................................................................124

10.2.1 Hardware or Sleep Reset Procedures..........................................................................125

10.2.2 Software or Watchdog Reset Procedures....................................................................126

10.3Memory Configuration Registers ..............................................................................................127

10.3.1 DRAM Configuration Register (MDCNFG)...................................................................128

10.3.2 DRAM Refresh Control Register (MDREFR) ...............................................................132

10.3.3 CAS Waveform Rotate Registers (MDCAS00, MDCAS01, MDCAS02,

MDCAS20, MDCAS21, MDCAS22) .............................................................................136

10.3.3.1 MDCAS Registers with Asynchronous DRAM...............................................136

10.3.3.2 MDCAS Registers with SDRAM and SMROM...............................................137

10.3.4 Static Memory Control Registers (MSC2 – 0) ..............................................................139

10.3.5 Expansion Memory (PC-Card) Configuration Register (MECR) ..................................142

10.4SMROM Configuration Register (SMCNFG) ............................................................................144

10.4.1 Changing SMROM RAS Latency .................................................................................147

10.5Dynamic Interface Operation ....................................................................................................148

6 SA-1110 Developer’s Manual

Page 7

10.5.1 DRAM Overview...........................................................................................................148

10.5.2 DRAM Timing...............................................................................................................150

10.5.3 SDRAM Overview.........................................................................................................152

10.5.4 SDRAM Commands .....................................................................................................154

10.5.5 SDRAM State Machine.................................................................................................155

10.5.6 DRAM/SDRAM Refresh ...............................................................................................160

10.5.7 DRAM/SDRAM Self-Refresh in Sleep Mode................................................................161

10.6Static Memory Interface............................................................................................................162

10.6.1 ROM Interface Overview ..............................................................................................163

10.6.2 ROM Timing Diagrams and Parameters ......................................................................163

10.6.3 SRAM Interface Overview ............................................................................................167

10.6.4 SRAM Timing Diagrams and Parameters ....................................................................167

10.6.5 Variable Latency I/O Interface Overview......................................................................169

10.6.6 Variable Latency I/O Timing Diagrams and Parameters ..............................................169

10.6.7 FLASH Memory Interface Overview.............................................................................172

10.6.8 FLASH Memory Timing Diagrams and Parameters.....................................................172

10.6.9 SMROM Overview........................................................................................................173

10.6.10SMROM Commands ....................................................................................................173

10.6.11SMROM State Machine................................................................................................174

10.7PC-Card Overview....................................................................................................................177

10.7.1 8-, 16-, and 32-Bit Data Bus Operation ........................................................................179

10.7.2 External Logic for PC-Card Implementation.................................................................180

10.7.3 PC-Card Interface Timing Diagrams and Parameters..................................................183

10.8Alternate Memory Bus Master Mode.........................................................................................185

10.9Memory System Examples .......................................................................................................186

10.10SA1110 Memory Configuration Tool .......................................................................................190

11 Peripheral Control Module

11.1Read/Write Interface .................................................................................................................205

11.2Memory Organization................................................................................................................206

11.3Interrupts...................................................................................................................................207

11.4Peripheral Pins..........................................................................................................................208

11.5Use of the GPIO Pins for Alternate Functions...........................................................................209

11.6DMA Controller..........................................................................................................................210

11.6.1 DMA Register Definitions .............................................................................................211

11.6.1.1 DMA Device Address Register (DDARn)...................................................... 211

11.6.1.2 DMA Control/Status Register (DCSRn) ........................................................ 213

11.6.1.3 DMA Buffer A Start Address Register (DBSAn)............................................ 215

11.6.1.4 DMA Buffer A Transfer Count Register (DBTAn).......................................... 216

11.6.1.5 DMA Buffer B Start Address Register (DBSBn)............................................ 216

11.6.1.6 DMA Buffer B Transfer Count Register (DBTBn).......................................... 216

11.6.2 DMA Register List.........................................................................................................217

11.7LCD Controller ..........................................................................................................................219

11.7.1 LCD Controller Operation.............................................................................................220

11.7.1.1 DMA to Memory Interface............................................................................. 221

11.7.1.2 Frame Buffer ................................................................................................. 221

11.7.1.3 Input FIFO..................................................................................................... 226

11.7.1.4 Lookup Palette .............................................................................................. 226

11.7.1.5 Color/Gray-Scale Dithering ........................................................................... 226

SA-1110 Developer’s Manual 7

Page 8

11.7.1.6 Output FIFO...................................................................................................227

11.7.1.7 LCD Controller Pins .......................................................................................227

11.7.2 LCD Controller Register Definitions .............................................................................228

11.7.3 LCD Controller Control Register 0................................................................................229

11.7.3.1 LCD Enable (LEN).........................................................................................229

11.7.3.2 Color/Monochrome Select (CMS)..................................................................229

11.7.3.3 Single-/Dual-Panel Select (SDS) ...................................................................229

11.7.3.4 LCD Disable Done Interrupt Mask (LDM) ......................................................231

11.7.3.5 Base Address Update Interrupt Mask (BAM).................................................232

11.7.3.6 Error Interrupt Mask (ERM)............................................................................232

11.7.3.7 Passive/Active Display Select (PAS) .............................................................232

11.7.3.8 Big/Little Endian Select (BLE)........................................................................233

11.7.3.9 Double-Pixel Data (DPD) Pin Mode...............................................................234

11.7.3.10Vertical Slant Line Correction (VSC).............................................................234

11.7.3.11Palette DMA Request Delay (PDD)...............................................................234

11.7.4 LCD Controller Control Register 1................................................................................236

11.7.4.1 Pixels Per Line (PPL).....................................................................................237

11.7.4.2 Horizontal Sync Pulse Width (HSW)..............................................................237

11.7.4.3 End-of-Line Pixel Clock Wait Count (ELW)....................................................237

11.7.4.4 Beginning-of-Line Pixel Clock Wait Count (BLW)..........................................237

11.7.5 LCD Controller Control Register 2................................................................................238

11.7.5.1 Lines Per Panel (LPP) ...................................................................................238

11.7.5.2 Vertical Sync Pulse Width (VSW) ..................................................................239

11.7.5.3 End-of-Frame Line Clock Wait Count (EFW).................................................239

11.7.5.4 Beginning-of-Frame Line Clock Wait Count (BFW) .......................................240

11.7.6 LCD Controller Control Register 3................................................................................241

11.7.6.1 Pixel Clock Divider (PCD)..............................................................................242

11.7.6.2 AC Bias Pin Frequency (ACB).......................................................................242

11.7.6.3 AC Bias Pin Transitions Per Interrupt (API)...................................................242

11.7.6.4 Vertical Sync Polarity (VSP) ..........................................................................243

11.7.6.5 Horizontal Sync Polarity (HSP)......................................................................243

11.7.6.6 Pixel Clock Polarity (PCP) .............................................................................243

11.7.6.7 Output Enable Polarity (OEP)........................................................................243

11.7.7 LCD Controller DMA Registers ....................................................................................245

11.7.8 DMA Channel 1 Base Address Register ......................................................................245

11.7.9 DMA Channel 1 Current Address Register ..................................................................246

11.7.10DMA Channel 2 Base and Current Address Registers ................................................247

11.7.11LCD Controller Status Register....................................................................................248

11.7.11.1 LCD Disable Done Flag (LDD) (read/write, maskable interrupt) ..................249

11.7.11.2Base Address Update Flag (BAU) (read-only, maskable interrupt)...............249

11.7.11.3 Bus Error Status (BER) (read/write, maskable interrupt) .............................249

11.7.11.4 AC Bias Count Status (ABC) (read/write, nonmaskable interrupt)...............249

11.7.11.5 Input FIFO Overrun Lower Panel Status (IOL)

(read/write, maskable interrupt) .....................................................................249

11.7.11.6 Input FIFO Underrun Lower Panel Status (IUL)

(read/write, maskable interrupt) .....................................................................250

11.7.11.7 Input FIFO Overrun Upper Panel Status (IOU)

8 SA-1110 Developer’s Manual

Page 9

(read/write, maskable interrupt) .................................................................... 250

11.7.11.8 Input FIFO Underrun Upper Panel Status (IUU)

(read/write, maskable interrupt) .................................................................... 250

11.7.11.9 Output FIFO Overrun Lower Panel Status (OOL)

(read/write, maskable interrupt) .................................................................... 250

11.7.11.10 Output FIFO Underrun Lower Panel Status (OUL)

(read only, maskable interrupt) ..................................................................... 250

11.7.11.11 Output FIFO Overrun Upper Panel Status (OOU)

(read/write, maskable interrupt) .................................................................... 250

11.7.11.12Output FIFO Underrun Upper Panel Status (OUU)

(read/write, maskable interrupt) .................................................................... 251

11.7.12LCD Controller Register Locations...............................................................................252

11.7.13LCD Controller Pin Timing Diagrams ...........................................................................254

11.8Serial Port 0 – USB Device Controller (UDC)...........................................................................259

11.8.1 USB Operation .............................................................................................................261

11.8.1.1 Signalling Levels........................................................................................... 261

11.8.1.2 Connecting the USB to the SA-1110............................................................. 262

11.8.1.3 Bit Encoding.................................................................................................. 263

11.8.1.4 Field Formats................................................................................................ 264

11.8.1.5 Packet Types ................................................................................................ 265

11.8.1.6 Transaction Formats..................................................................................... 267

11.8.1.7 SA-1110 UDC Device-Request Commands ................................................. 269

11.8.1.8 Using DMA.................................................................................................... 271

11.8.1.9 Software Control of the SA-1110 UDC.......................................................... 271

11.8.1.10SA-1110 USB Example Code....................................................................... 278

11.8.2 SA-1110 UDC Register Definitions...............................................................................278

11.8.3 UDC Control Register (UDCCR) ..................................................................................279

11.8.3.1 UDC Disable (UDD) ...................................................................................... 280

11.8.3.2 UDC Active (UDA)......................................................................................... 280

11.8.3.3 Resume Interrupt Mask (RESIM).................................................................. 280

11.8.3.4 Endpoint 0 Interrupt Mask (EIM)................................................................... 281

11.8.3.5 Receive Interrupt Mask (RIM)....................................................................... 281

11.8.3.6 Transmit Interrupt Mask (TIM)....................................................................... 281

11.8.3.7 Suspend Interrupt Mask (SUSIM)................................................................. 282

11.8.3.8 Reserved/B5 ................................................................................................. 282

11.8.4 UDC Address Register (UDCAR).................................................................................282

11.8.5 UDC OUT Maximum Packet Register (UDCOMP).......................................................283

11.8.6 UDC IN Maximum Packet Register (UDCIMP).............................................................284

11.8.7 UDC Endpoint 0 Control/Status Register (UDCCS0) ...................................................284

11.8.7.1 OUT Packet Ready (OPR)............................................................................ 285

11.8.7.2 IN Packet Ready (IPR).................................................................................. 285

11.8.7.3 Sent Stall (SST) ............................................................................................ 286

11.8.7.4 Force Stall (FST)........................................................................................... 286

11.8.7.5 Data End (DE)............................................................................................... 286

11.8.7.6 Setup End (SE) ............................................................................................. 286

11.8.7.7 Serviced OPR (SO)....................................................................................... 286

11.8.7.8 Serviced Setup End (SSE)............................................................................ 286

SA-1110 Developer’s Manual 9

Page 10

11.8.8 UDC Endpoint 1 Control/Status Register (UDCCS1) ...................................................286

11.8.8.1 Receive FIFO Service (RFS) .........................................................................287

11.8.8.2 Receive Packet Complete (RPC)...................................................................287

11.8.8.3 Receive Packet Error (RPE) ..........................................................................288

11.8.8.4 Sent Stall (SST).............................................................................................288

11.8.8.5 Force Stall (FST)............................................................................................288

11.8.8.6 Receive FIFO Not Empty (RNE)....................................................................288

11.8.9 UDC Endpoint 2 Control/Status Register (UDCCS2) ...................................................288

11.8.9.1 Transmit FIFO Service (TFS).........................................................................289

11.8.9.2 Transmit Packet Complete (TPC)..................................................................289

11.8.9.3 Transmit Packet Error (TPE)..........................................................................289

11.8.9.4 Transmit Underrun (TUR) ..............................................................................290

11.8.9.5 Sent STALL (SST).........................................................................................290

11.8.9.6 Force STALL (FST)........................................................................................290

11.8.10UDC Endpoint 0 Data Register (UDCD0).....................................................................290

11.8.11UDC Endpoint 0 Write Count Register (UDCWC)........................................................291

11.8.12UDC Data Register (UDCDR) ......................................................................................292

11.8.13UDC Status/Interrupt Register (UDCSR) .....................................................................292

11.8.13.1Endpoint 0 Interrupt Request (EIR)...............................................................293

11.8.13.2Receive Interrupt Request (RIR)...................................................................294

11.8.13.3Transmit Interrupt Request (TIR) ..................................................................294

11.8.13.4Suspend Interrupt Request (SUSIR).............................................................294

11.8.13.5Resume Interrupt Request (RESIR)..............................................................294

11.8.13.6 Reset Interrupt Request (RSTIR).................................................................294

11.8.14SA-1110 UDC Register Locations................................................................................294

11.9Serial Port 1 – GPCLK/UART ...................................................................................................295

11.9.1 GPCLK Operation ........................................................................................................295

11.9.1.1 Simultaneous Use of the UART and GPCLK.................................................296

11.9.2 GPCLK Control Register 0 ...........................................................................................296

11.9.2.1 GPCLK/UART Select (SUS) ..........................................................................296

11.9.2.2 Sample Clock Enable (SCE)..........................................................................296

11.9.2.3 Sample Clock Direction (SCD).......................................................................296

11.9.3 GPCLK Control Register 1 ...........................................................................................297

11.9.3.1 Transmit Enable (TXE) ..................................................................................297

11.9.4 GPCLK Control Registers 2 and 3 ...............................................................................298

11.9.4.1 Baud Rate Divisor (BRD)...............................................................................298

11.9.5 UART Register Locations.............................................................................................299

11.9.6 GPCLK Register Locations ..........................................................................................300

11.10 Serial Port 2 – Infrared Communications Port (ICP) ..............................................................300

11.10.1Low-Speed ICP Operation ...........................................................................................301

11.10.1.1HP-SIR Modulation........................................................................................301

11.10.1.2UART Frame Format.....................................................................................302

11.10.2High-Speed ICP Operation...........................................................................................302

11.10.2.14PPM Modulation..........................................................................................302

11.10.2.2HSSP Frame Format.....................................................................................303

11.10.2.3Address Field ................................................................................................304

11.10.2.4Control Field..................................................................................................304

10 SA-1110 Developer’s Manual

Page 11

11.10.2.5Data Field ..................................................................................................... 304

11.10.2.6CRC Field..................................................................................................... 304

11.10.2.7Baud Rate Generation.................................................................................. 305

11.10.2.8Receive Operation........................................................................................ 305

11.10.2.9Transmit Operation....................................................................................... 306

11.10.2.10Transmit and Receive FIFOs...................................................................... 307

11.10.2.11CPU and DMA Register Access Sizes....................................................... 308

11.10.3UART Register Definition .............................................................................................308

11.10.4UART Control Register 4..............................................................................................308

11.10.4.1HP-SIR Enable (HSE) .................................................................................. 308

11.10.4.2Low-Power Mode (LPM)............................................................................... 308

11.10.5 HSSP Register Definitions309

11.10.6HSSP Control Register 0..............................................................................................309

11.10.6.1IrDA Transmission Rate (ITR) ...................................................................... 309

11.10.6.2Loopback Mode (LBM) ................................................................................. 310

11.10.6.3Transmit FIFO Underrun Select (TUS)......................................................... 310

11.10.6.4Transmit Enable (TXE)................................................................................. 311

11.10.6.5Receive Enable (RXE).................................................................................. 311

11.10.6.6Receive FIFO Interrupt Enable (RIE) ........................................................... 311

11.10.6.7Transmit FIFO Interrupt Enable (TIE)........................................................... 312

11.10.6.8Address Match Enable (AME)...................................................................... 312

11.10.7 HSSP Control Register 1.............................................................................................313

11.10.7.1Address Match Value (AMV)........................................................................ 313

11.10.8 HSSP Control Register 2.............................................................................................314

11.10.8.1Transmit Pin Polarity Select (TXP)............................................................... 314

11.10.8.2Receive Pin Polarity Select (RXP)................................................................ 315

11.10.9 HSSP Data Register....................................................................................................316

11.10.10 HSSP Status Register 0.............................................................................................317

11.10.10.1 End/Error in FIFO Status (EIF) (read-only, nonmaskable interrupt).......... 318

11.10.10.2 Transmit Underrun Status (TUR) (read/write, maskable interrupt)............ 318

11.10.10.3 Receiver Abort Status (RAB) (read/write, nonmaskable interrupt)............ 318

11.10.10.4 Transmit FIFO Service Request Flag (TFS)

(read-only, maskable interrupt)..................................................................... 318

11.10.10.5 Receive FIFO Service Request Flag (RFS)

(read-only, maskable interrupt)..................................................................... 319

11.10.10.6 Framing Error Status (FRE) (read/write, nonmaskable interrupt).............. 319

11.10.11 HSSP Status Register 1.............................................................................................320

11.10.11.1 Receiver Synchronized Flag (RSY) (read-only, noninterruptible).............. 321

11.10.11.2 Transmitter Busy Flag (TBY) (read-only, noninterruptible)........................ 321

11.10.11.3 Receive FIFO Not Empty Flag (RNE) (read-only, noninterruptible) .......... 321

11.10.11.4 Transmit FIFO Not Full Flag (TNF) (read-only, noninterruptible) .............. 321

11.10.11.5 End-of-Frame Flag (EOF) (read-only, noninterruptible) ............................ 321

11.10.11.6 CRC Error Flag (CRE) (read-only, noninterruptible).................................. 321

11.10.11.7 Receiver Overrun Status (ROR) (read-only, noninterruptible)................... 322

11.10.12 UART Register Locations...........................................................................................323

11.10.13 HSSP Register Locations...........................................................................................324

11.11Serial Port 3 – UART...............................................................................................................325

11.11.1UART Operation...........................................................................................................325

SA-1110 Developer’s Manual 11

Page 12

11.11.1.1Frame Format................................................................................................326

11.11.1.2Baud Rate Generation...................................................................................326

11.11.1.3Receive Operation.........................................................................................326

11.11.1.4Transmit Operation........................................................................................327

11.11.1.5Transmit and Receive FIFOs ........................................................................327

11.11.1.6CPU and DMA Register Access Sizes..........................................................327

11.11.2UART Register Definitions ...........................................................................................327

11.11.3UART Control Register 0..............................................................................................328

11.11.3.1Parity Enable (PE).........................................................................................328

11.11.3.2Odd/Even Parity Select (OES) ......................................................................328

11.11.3.3Stop Bit Select (SBS) ....................................................................................328

11.11.3.4Data Size Select (DSS).................................................................................329

11.11.3.5Sample Clock Enable (SCE).........................................................................329

11.11.3.6Receive Clock Edge Select (RCE)................................................................329

11.11.3.7Transmit Clock Edge Select (TCE) ...............................................................329

11.11.4UART Control Registers 1 and 2..................................................................................330

11.11.4.1Baud Rate Divisor (BRD) ..............................................................................330

11.11.5UART Control Register 3..............................................................................................331

11.11.5.1Receiver Enable (RXE).................................................................................332

11.11.5.2Transmitter Enable (TXE)..............................................................................332

11.11.5.3Break (BRK) ..................................................................................................332

11.11.5.4Receive FIFO Interrupt Enable (RIE)............................................................332

11.11.5.5Transmit FIFO Interrupt Enable (TIE)............................................................333

11.11.5.6Loopback Mode (LBM)..................................................................................333

11.11.6UART Data Register.....................................................................................................334

11.11.7UART Status Register 0...............................................................................................335

11.11.7.1Transmit FIFO Service Request Flag (TFS) (read-only, maskable interrupt)336

11.11.7.2Receive FIFO Service Request Flag (RFS) (read-only, maskable interrupt) 336

11.11.7.3Receiver Idle Status (RID) (read/write, maskable interrupt)..........................336

11.11.7.4Receiver Begin of Break Status (RBB) (read/write, nonmaskable interrupt).337

11.11.7.5Receiver End of Break Status (REB) (read/write, nonmaskable interrupt)....337

11.11.7.6Error in FIFO Flag (EIF) (read-only, nonmaskable interrupt) ........................337

11.11.8UART Status Register 1...............................................................................................339

11.11.8.1Transmitter Busy Flag (TBY) (read-only, noninterruptible)............................339

11.11.8.2Receive FIFO Not Empty Flag (RNE) (read-only, noninterruptible) ..............339

11.11.8.3Transmit FIFO Not Full Flag (TNF) (read-only, noninterruptible) ..................339

11.11.8.4Parity Error Flag (PRE) (read-only, noninterruptible) ....................................339

11.11.8.5Framing Error Flag (FRE) (read-only, noninterruptible) ................................339

11.11.8.6Receiver Overrun Flag (ROR) (read-only, noninterruptible)..........................340

11.11.9UART Register Locations.............................................................................................341

11.12Serial Port 4 – MCP / SSP ......................................................................................................342

11.12.1MCP Operation.............................................................................................................343

11.12.1.1Frame Format................................................................................................343

11.12.1.2Audio and Telecom Sample Rates and Data Transfer..................................345

11.12.1.3MCP Transmit and Receive FIFO Operation ................................................346

11.12.1.4Codec Control Register Data Transfer..........................................................347

11.12.1.5External Clock Operation ..............................................................................348

12 SA-1110 Developer’s Manual

Page 13

11.12.1.6Alternate SSP Pin Assignment..................................................................... 348

11.12.1.7CPU and DMA Register Access Sizes ......................................................... 348

11.12.2MCP Register Definitions .............................................................................................349

11.12.3MCP Control Register 0................................................................................................349

11.12.3.1Audio Sample Rate Divisor (ASD)................................................................ 349

11.12.3.2Telecom Sample Rate Divisor (TSD) ........................................................... 350

11.12.3.3Multimedia Communications Port Enable (MCE) ......................................... 351

11.12.3.4External Clock Select (ECS)......................................................................... 351

11.12.3.5A/D Sampling Mode (ADM) .......................................................................... 352

11.12.3.6Telecom Transmit FIFO Interrupt Enable (TTE)........................................... 352

11.12.3.7Telecom Receive FIFO Interrupt Enable (TRE) ........................................... 352

11.12.3.8Audio Transmit FIFO Interrupt Enable (ATE)............................................... 352

11.12.3.9Audio Receive FIFO Interrupt Enable (ARE)................................................ 353

11.12.3.10Loopback Mode (LBM)............................................................................... 353

11.12.3.11External Clock Prescaler (ECP) ................................................................. 353

11.12.4MCP Control Register 1................................................................................................355

11.12.4.1Clock Frequency Select (CFS)..................................................................... 355

11.12.5MCP Data Registers.....................................................................................................356

11.12.5.1MCP Data Register 0.................................................................................... 356

11.12.5.2MCP Data Register 1.................................................................................... 357

11.12.5.3MCP Data Register 2.................................................................................... 358

11.12.6MCP Status Register....................................................................................................360

11.12.6.1Audio Transmit FIFO Service Request Flag (ATS)

(read-only, maskable interrupt)..................................................................... 360

11.12.6.2Audio Receive FIFO Service Request Flag (ARS)

(read-only, maskable interrupt)..................................................................... 360

11.12.6.3Telecom Transmit FIFO Service Request Flag (TTS)

(read-only, maskable interrupt)..................................................................... 361

11.12.6.4Telecom Receive FIFO Service Request Flag (TRS)

(read-only, maskable interrupt)..................................................................... 361

11.12.6.5Audio Transmit FIFO Underrun Status (ATU)

(read/write, nonmaskable interrupt) .............................................................. 361

11.12.6.6Audio Receive FIFO Overrun Status (ARO)

(read/write, nonmaskable interrupt) .............................................................. 361

11.12.6.7Telecom Transmit FIFO Underrun Status (TTU)

(read/write, nonmaskable interrupt) .............................................................. 362

11.12.6.8Telecom Receive FIFO Overrun Status (TRO)

(read/write, nonmaskable interrupt) .............................................................. 362

11.12.6.9Audio Transmit FIFO Not Full Flag (ANF) (read-only, noninterruptible)....... 362

11.12.6.10Audio Receive FIFO Not Empty Flag (ANE) (read-only, noninterruptible) . 362

11.12.6.11Telecom Transmit FIFO Not Full Flag (TNF) (read-only, noninterruptible). 362

11.12.6.12Telecom Receive FIFO Not Empty Flag (TNE)

(read-only, noninterruptible).......................................................................... 362

11.12.6.13Codec Write Completed Flag (CWC) (read-only, noninterruptible) ............ 363

11.12.6.14Codec Read Completed Flag (CRC) (read-only, noninterruptible)............. 363

11.12.6.15Audio Codec Enabled Flag (ACE) (read-only, noninterruptible)................. 363

11.12.6.16Telecom Codec Enabled Flag (TCE) (read-only, noninterruptible) ............ 363

11.12.7SSP Operation..............................................................................................................365

SA-1110 Developer’s Manual 13

Page 14

11.12.7.1Frame Format................................................................................................366

11.12.7.2Baud Rate Generation...................................................................................370

11.12.7.3SSP Transmit and Receive FIFOs................................................................370

11.12.7.4CPU and DMA Register Access Sizes..........................................................371

11.12.7.5Alternate SSP Pin Assignment......................................................................371

11.12.8SSP Register Definitions..............................................................................................371

11.12.9SSP Control Register 0................................................................................................372

11.12.9.1Data Size Select (DSS)............................................................................... 372

11.12.9.2Frame Format (FRF) .....................................................................................372

11.12.9.3Synchronous Serial Port Enable (SSE).........................................................372

11.12.9.4Serial Clock Rate (SCR)................................................................................373

11.12.10SSP Control Register 1...............................................................................................374

11.12.10.1Receive FIFO Interrupt Enable (RIE)..........................................................374

11.12.10.2Transmit FIFO Interrupt Enable (TIE)..........................................................374

11.12.10.3Loopback Mode (LBM)................................................................................375

11.12.10.4Serial Clock Polarity (SPO).........................................................................375

11.12.10.5Serial Clock Phase (SPH) ...........................................................................375

11.12.10.6External Clock Select (ECS) .......................................................................376

11.12.11SSP Data Register......................................................................................................377

11.12.12SSP Status Register ...................................................................................................379

11.12.12.1Transmit FIFO Not Full Flag (TNF) (read-only, noninterruptible) ................379

11.12.12.2Receive FIFO Not Empty Flag (RNE) (read-only, noninterruptible) ............379

11.12.12.3SSP Busy Flag (BSY) (read-only, noninterruptible) ....................................379

11.12.12.4Transmit FIFO Service Request Flag (TFS)

(read-only, maskable interrupt)......................................................................379

11.12.12.5Receive FIFO Service Request Flag (RFS)

(read-only, maskable interrupt)......................................................................380

11.12.12.6Receiver Overrun Status (ROR) (read/write, nonmaskable interrupt).........380

11.12.13MCP Register Locations .............................................................................................381

11.12.14SSP Register Locations..............................................................................................382

11.13Peripheral Pin Controller (PPC)..............................................................................................382

11.13.1PPC Operation .............................................................................................................382

11.13.2PPC Register Definitions..............................................................................................383

11.13.3PPC Pin Direction Register ..........................................................................................383

11.13.4PPC Pin State Register ................................................................................................385

11.13.5PPC Pin Assignment Register......................................................................................387

11.13.5.1UART Pin Reassignment (UPR) ...................................................................387

11.13.5.2SSP Pin Reassignment (SPR)......................................................................387

11.13.6PPC Sleep Mode Pin Direction Register......................................................................388

11.13.7PPC Pin Flag Register .................................................................................................390

11.13.8PPC Register Locations ...............................................................................................392

12 DC Parameters

12.1Absolute Maximum Ratings ......................................................................................................393

12.2DC Operating Conditions..........................................................................................................394

12.3Power Supply Voltages and Currents.......................................................................................395

13 AC Parameters

13.1Test Conditions.........................................................................................................................397

14 SA-1110 Developer’s Manual

Page 15

13.2Model Considerations ...............................................................................................................398

13.3Memory Bus and PCMCIA Signal Timings ...............................................................................398

13.4LCD Controller Signals..............................................................................................................399

13.5MCP Signals .............................................................................................................................399

13.6Timing Parameters....................................................................................................................401

13.6.1 Asynchronous Signal Timing Descriptions ...................................................................403

14 Package and Pinout

15 Debug Support

15.1Instruction Breakpoint ...............................................................................................................411

15.2Data Breakpoint ........................................................................................................................411

16 Boundary-Scan Test Interface

16.1Overview...................................................................................................................................413

16.2Reset.........................................................................................................................................414

16.3Pull-Up Resistors ......................................................................................................................414

16.4Instruction Register...................................................................................................................414

16.5Public Instructions.....................................................................................................................414

16.5.1 EXTEST (00000) ..........................................................................................................415

16.5.2 SAMPLE/PRELOAD (00001) .......................................................................................415

16.5.3 CLAMP (00100)............................................................................................................415

16.5.4 HIGHZ (00101).............................................................................................................416

16.5.5 IDCODE (00110) ..........................................................................................................416

16.5.6 BYPASS (11111)..........................................................................................................416

16.6Test Data Registers ..................................................................................................................417

16.6.1 Bypass Register ...........................................................................................................417

16.6.2 Intel® StrongARM SA-1110 Device Identification (ID)

Code Register418

16.6.3 Intel® StrongARM SA-1110 Boundary-Scan (BS) Register .........................................418

16.7Boundary-Scan Interface Signals..............................................................................................419

A Register Summary

B 3.6864–MHz Oscillator Specifications

B.1 Specifications............................................................................................................................433

B.1.1 System Specifications ..................................................................................................433

B.1.1.1. Parasitic Capacitance Off-chip Between PXTAL and PEXTAL......................434

B.1.1.2. Parasitic Capacitance Off-chip Between PXTAL or PEXTAL and VSS.........434

B.1.1.3. Parasitic Resistance Between PXTAL and PEXTAL .....................................434

B.1.1.4. Parasitic Resistance Between PXTAL or PEXTAL and VSS.........................434

B.1.2 Quartz Crystal Specification .........................................................................................435

C 32.768–KHz Oscillator Specifications

C.1 Specifications............................................................................................................................437

C.1.1 System Specifications ..................................................................................................437

C.1.1.1. Temperature Range.......................................................................................437

C.1.1.2. Current Consumption.....................................................................................437

C.1.1.3. Startup Time...................................................................................................437

C.1.1.4. Frequency Shift Due to Temperature Effect on the Circuit ............................438

C.1.1.5. Parasitic Capacitance Off-chip Between TXTAL and TEXTAL......................438

C.1.1.6. Parasitic Capacitance Off-chip Between TXTAL or TEXTAL and VSS..........438

C.1.1.7. Parasitic Resistance Between TXTAL and TEXTAL......................................438

SA-1110 Developer’s Manual 15

Page 16

C.1.1.8. Parasitic Resistance Between TXTAL or TEXTAL and VSS .........................438

C.1.2 Quartz Crystal Specification .........................................................................................439

D Internal Test

D.1 Test Unit Control Register (TUCR) ...........................................................................................441

Figures

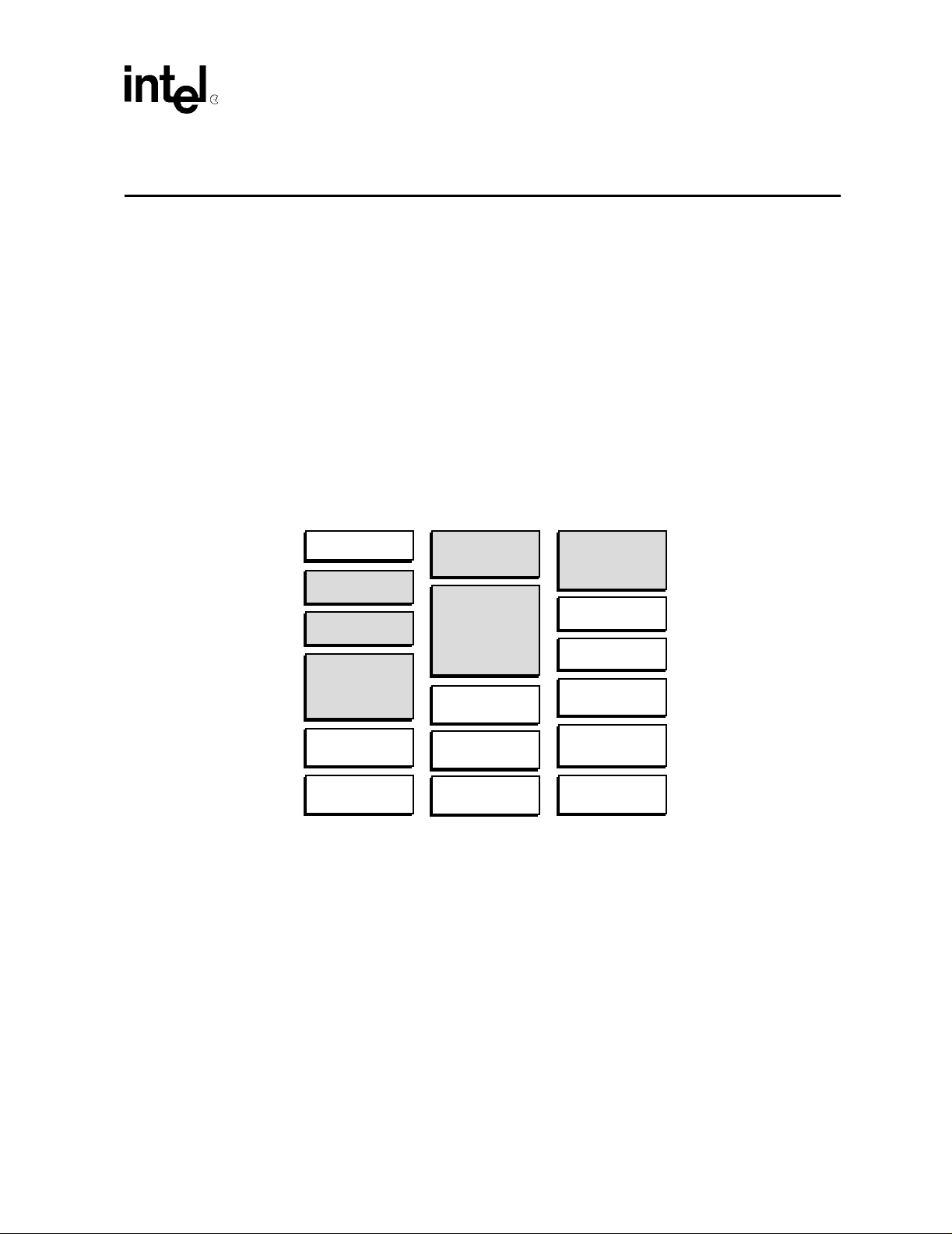

1-1 SA-1110 Features ......................................................................................................................21

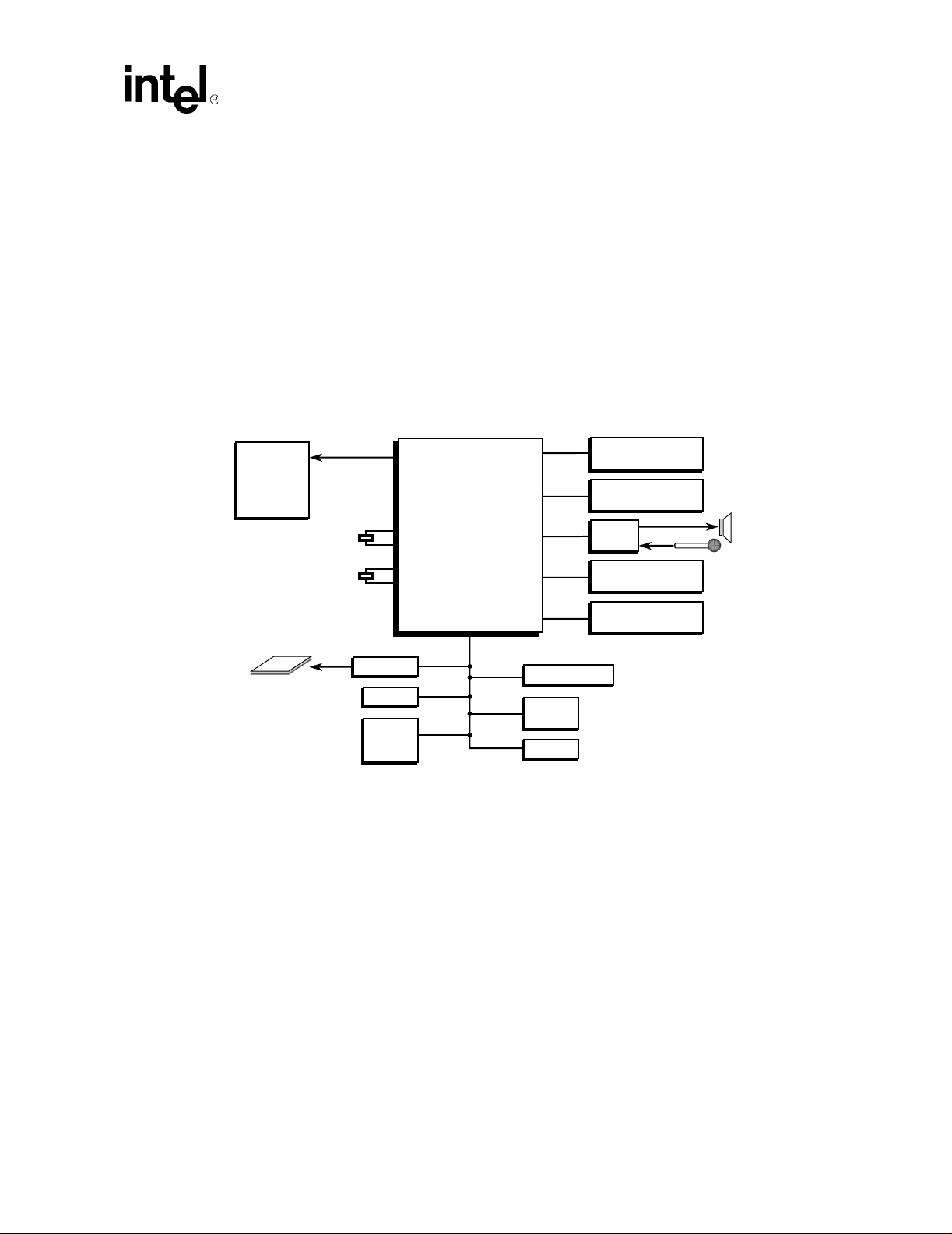

1-2 SA-1110 Example System..........................................................................................................25

2-1 SA-1110 Block Diagram .............................................................................................................30

2-2 SA-1110 Functional Diagram .....................................................................................................31

2-3 SA-1110 Memory Map................................................................................................................38

6-1 Format of Internal Coprocessor Instructions MRC and MCR.....................................................55

8-1 SA-1110 Clock System Block Diagram ......................................................................................69

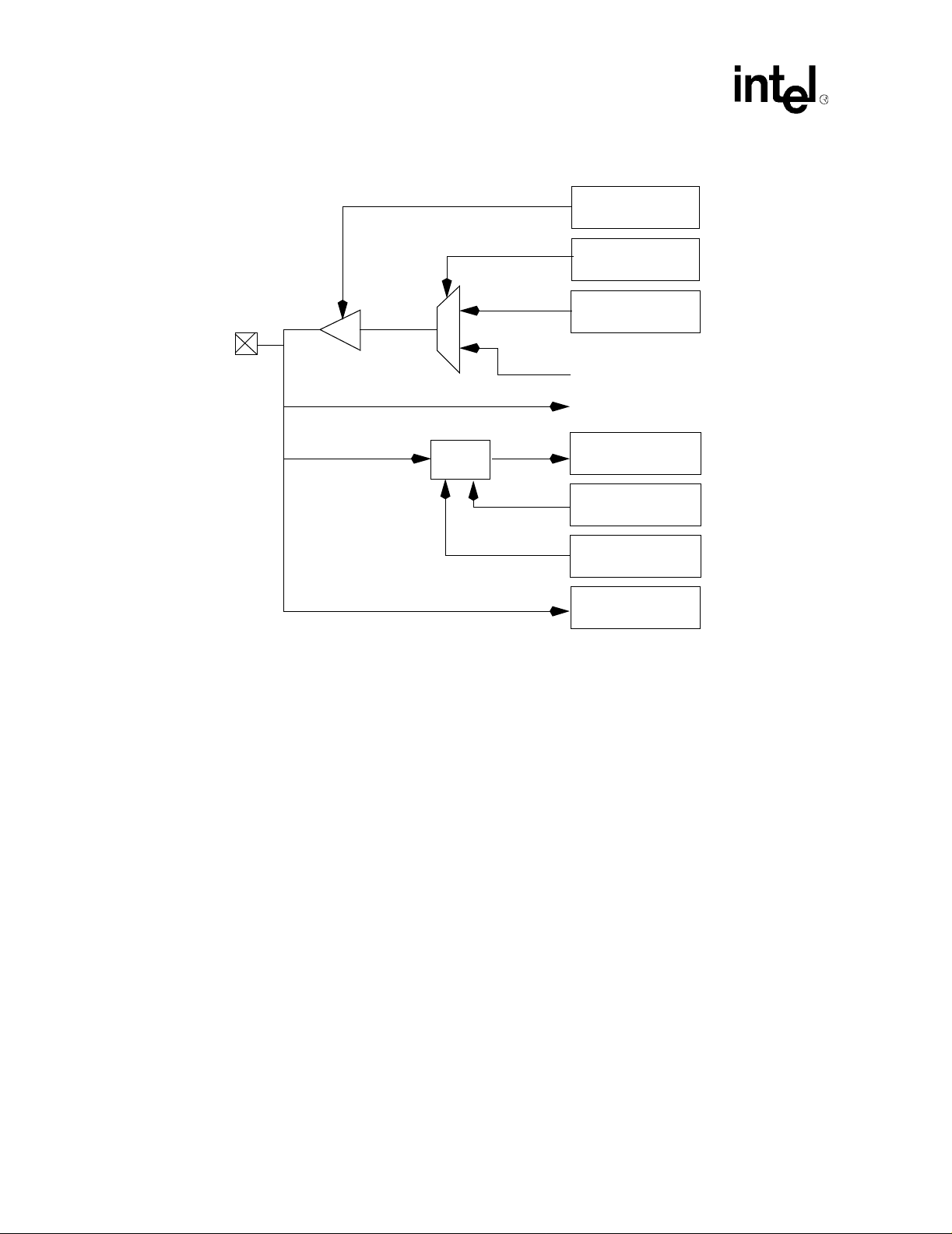

9-1 General-Purpose I/O Block Diagram ..........................................................................................74

9-2 Interrupt Controller Block Diagram .............................................................................................83

9-3 Transitions Between Modes of Operation ................................................................................105

10-1 General Memory Interface Configuration .................................................................................120

10-2 Memory Pins and Memory Controller State after Hardware Reset .........................................124

10-3 DRAM Single-Beat Transactions..............................................................................................151

10-4 Dram Burst-of-Eight Transactions............................................................................................152

10-5 SDRAM State Machine.............................................................................................................156

10-6 SDRAM 1-Beat Read/Write/Read Timing for 4 Bank x 4 M x 4 Bit

Organization (64 Mbit)..............................................................................................................157

10-7 SDRAM 1-Beat Read/Write Timing for 4 Bank x 4 M x 4 Bit Organization

(64 Mbit) at Half-Memory Clock Frequency (MDREFR:KnDB2=1)) .........................................158

10-8 SDRAM 8-Beat Read/Write Timing for 4 Bank x 4 M x 4 Bit

Organization (64 Mbit)..............................................................................................................159

10-9 DRAM/SDRAM CBR Refresh Cycle.........................................................................................161

10-10 Burst-of-Eight ROM or Flash Read Timing Diagram ................................................................164

10-11 Eight-Beat Burst Read from Burst-of-Four ROM or Flash........................................................165

10-12 Nonburst ROM, SRAM, or Flash Read Timing Diagram – Four Data Beats)...........................166

10-13 SRAM Write Timing Diagram (4–Beat Burst) ...........................................................................168

10-14 Variable Latency I/O Read Timing (Burst-of-Four)...................................................................170

10-15 Variable Latency I/O Write Timing (Burst-of-Four) ...................................................................171

10-16 Flash Write Timing Diagram (2 Writes) ....................................................................................173

10-17 SMROM State Machine............................................................................................................176

10-18 SMROM Eight-Beat and Two-Beat Timing for 2 M x 16 Bit Organization

(32 Mbit) at Half-Memory Clock Frequency (MDREFR:K0DB2=1)...........................................177

10-19 PC-Card Memory Map..............................................................................................................178

10-20 PC-Card External Logic for a Two-Socket Configuration .........................................................181

10-21 PC-Card External Logic for a One-Socket Configuration .........................................................182

10-22 PC-Card Memory or I/O 16-Bit Access.....................................................................................183

10-23 PC-Card I/O 16-Bit Access to 8-Bit Device ..............................................................................184