Page 1

Intel® StrongARM® SA-1100

Microprocessor

Developer’s Manual

August 1999

Order Number: 278088-004

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

This document is an intermediate draft for comment only and is subject to change without notice. Readers should not design products based on this

document.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SA-1100 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current

characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel’s website at http://www.intel.com.

Copyright © Intel Corporation, 1999

*Third-party brands and names are the property of their respective owners.

ARM and the ARM Powered logo are trademarks and StrongARM is a registered trademark of ARM Limited.

SA-1100 Developer’s Manual

Page 3

Contents

1 Introduction......................................................................................................................1-1

1.1 Intel® StrongARM® SA-1100 Microprocessor .................................................. 1-1

1.2 Overview............................................................................................................ 1-4

1.3 Example System........................... ...... ....................................... ...... ....... ...... ..... 1-5

1.4 ARM™ Architecture........................................................................................... 1-6

1.4.1 26-Bit Mode .......................................................................................... 1-6

1.4.2 Coprocessors........................................................................................ 1-6

1.4.3 Memory Management........................................................................... 1-6

1.4.4 Instruction Cache.................................................................................. 1-6

1.4.5 Data Cache...................... ...... ....... ...... ....... ...... ..................................... 1-6

1.4.6 Write Buffer........................................................................................... 1-7

1.4.7 Read Buffer........................................................................................... 1-7

2 Functional Description. ....... ...... ....... ...... ....... ...................................... ....... ...... ....... ...... ...2-1

2.1 Block Diagram ................................................................................................... 2-1

2.2 Inputs/Outputs ................................................................................................... 2-3

2.3 Signal Description.............................................................................................. 2-4

2.4 Memory Map...................................................................................................... 2-7

3 ARM™ Implementation Options...... ...... ....... ...... ...... ....................................... ....... ...... ...3-1

3.1 Big and Little Endian.......................................................................................... 3-1

3.2 Exceptions ......................................................................................................... 3-1

3.2.1 Power-Up Reset ................................................................................... 3-2

3.2.2 ROM Size Select .................................................................................. 3-2

3.2.3 Abort..................................................................................................... 3-3

3.2.4 Vector Summary................................................................................... 3-4

3.2.5 Exception Priorities............................................................................... 3-4

3.2.6 Interrupt Latencies and Enable Timing................................................. 3-5

3.3 Coprocessors..................................................................................................... 3-5

4 Instruction Set .................................................... ...... ....... ...... ....... ...... ....... ......................4-1

4.1 Instruction Set.................................................................................................... 4-1

4.2 Instruction Timings............................................................................................. 4-1

5 Coprocessors..................................................................................................................5-1

5.1 Internal Coprocessor Instructions...................................................................... 5-1

5.2 Coprocessor 15 Definition ................................................................................. 5-2

5.2.1 Register 0 – ID...................................................................................... 5-2

5.2.2 Register 1 – Control.............................................................................. 5-3

5.2.3 Register 2 – Translation Table Base ................................................... 5-4

5.2.4 Register 3 – Domain Access Control.................................................... 5-4

5.2.5 Register 4 – RESERVED...................................................................... 5-4

5.2.6 Register 5 – Fault Status ...................................................................... 5-4

5.2.7 Register 6 – Fault Address................................................................... 5-4

5.2.8 Register 7 – Cache Control Operations................................................ 5-5

5.2.9 Register 8 – TLB Operations................................................................ 5-5

5.2.10 Register 9 – Read-Buffer Operations ................................................... 5-6

SA-1100 Developer’s Manual iii

Page 4

5.2.11 Registers 10 – 12 RESERVED............................................................. 5-6

5.2.12 Register 13 – Process ID Virtual Address Mapping.............................. 5-7

5.2.13 Register 14 – Debug Support (Breakpoints)......................................... 5-8

5.2.14 Register 15 – Test, Clock, and Idle Control.......................................... 5-9

6 Caches, Write Buffer, and Read Buffer...........................................................................6-1

6.1 Instruction Cache (Icache)................................................................................. 6-1

6.1.1 Icache Operation .................................................................................. 6-1

6.1.2 Icache Validity ...................................................................................... 6-1

6.1.2.1 Software Icache Flush ........................................ ...... ............... 6-1

6.1.3 Icache Enable/Disable and Reset ........................................................ 6-2

6.1.3.1 Enabling the Icache ................................................................. 6-2

6.1.3.2 Disabling the Icache ................................................................ 6-2

6.2 Data Caches (Dcaches) .................................................................................... 6-2

6.2.1 Cacheable Bit – C................................................................................. 6-3

6.2.1.1 Cacheable Reads – C = 1 ....................................................... 6-3

6.2.1.2 Noncacheable Reads – C = 0.................................................. 6-3

6.2.2 Bufferable Bit – B.................................................................................. 6-3

6.2.3 Software Dcache Flush ................................ ...................................... .. 6-4

6.2.3.1 Doubly Mapped Space ............................................................ 6-4

6.2.4 Dcaches Enable/Disable and Reset..................................................... 6-4

6.2.4.1 Enabling the Dcaches.............................................................. 6-5

6.2.4.2 Disabling the Dcaches............................................................. 6-5

6.3 Write Buffer (WB) .............................................................................................. 6-5

6.3.1 Bufferable Bit............... ....... ...... ....... ...... ....... ...... .................................. 6-5

6.3.2 Write Buffer Operation.......................................................................... 6-5

6.3.2.1 Writes to a Bufferable and Cacheable Location (B=1,C=1)..... 6-5

6.3.2.2 Writes to a Bufferable and Noncacheable Location (B=1,C=0)6-6

6.3.2.3 Unbufferable Writes (B=0)....................................................... 6-6

6.3.3 Enabling the Write Buffer...................................................................... 6-6

6.3.3.1 Disabling the Write Buffer........................................................ 6-6

6.4 Read Buffer (RB) ............................................................................................... 6-6

7 Memory-Management Unit (MMU)..................................................................................7-1

7.1 Overview............................................................................................................ 7-1

7.1.1 MMU Registers..................................................................................... 7-1

7.2 MMU Faults and CPU Aborts ............................................................................ 7-1

7.3 Data Aborts........................................................................................................ 7-1

7.3.1 Cacheable Reads (Linefetches) ........................................................... 7-2

7.3.2 Buffered Writes..................................................................................... 7-2

7.4 Interaction of the MMU, Icache, Dcache, and Write Buffer ............................... 7-2

7.5 Mini Data Cache.... ...... ....... ...... ....... ...... ....... ...... ....... ...... ...... ............................ 7-3

8 Clocks .. ....... ...... ....... ...... ....... ...... ....... ...... ....... ...................................... ....... ...... ....... . .....8-1

8.1 SA-1100 Crystal Oscillators............................................................................... 8-1

8.2 Core Clock Configuration Register.................................................................... 8-2

8.2.1 Restrictions on Changing the Core Clock Configuration ...................... 8-2

8.3 Driving SA-1100 Crystal Pins from an External Source .................................... 8-3

8.4 Clocking During Test ......................................................................................... 8-4

iv SA-1100 Developer’s Manual

Page 5

9 System Control Module...................................................................................................9-1

9.1 General-Purpose I/O.......................................................................................... 9-1

9.1.1 GPIO Register Definitions..................................................................... 9-2

9.1.1.1 GPIO Pin-Level Register (GPLR) ............................................ 9-3

9.1.1.2 GPIO Pin Direction Register (GPDR) ...................................... 9-4

9.1.1.3 GPIO Pin Output Set Register (GPSR) and

Pin Output Clear Register (GPCR).......................................... 9-5

9.1.1.4 GPIO Rising-Edge Detect Register (GRER) and

Falling-Edge Detect Register (GFER) ..................................... 9-6

9.1.1.5 GPIO Edge Detect Status Register (GEDR)............................ 9-7

9.1.1.6 GPIO Alternate Function Register (GAFR).............................. 9-8

9.1.2 GPIO Alternate Functions..................................................................... 9-9

9.1.3 GPIO Register Locations.................................................................... 9-10

9.2 Interrupt Controller........................................................................................... 9-11

9.2.1 Interrupt Controller Register Definitions.............................................. 9-11

9.2.1.1 Interrupt Controller Pending Register (ICPR) ........................ 9-12

9.2.1.2 Interrupt Controller IRQ Pending Register (ICIP) and

FIQ Pending Register (ICFP)................................................. 9-13

9.2.1.3 Interrupt Controller Mask Register (ICMR) ............................ 9-14

9.2.1.4 Interrupt Controller Level Register (ICLR) ............................. 9-15

9.2.1.5 Interrupt Controller Control Register (ICCR).......................... 9-16

9.2.2 Interrupt Controller Register Locations............................................... 9-17

9.3 Real-Time Clock.............................................................................................. 9-17

9.3.1 RTC Counter Register (RCNR) .......................................................... 9-17

9.3.2 RTC Alarm Register (RTAR) .............................................................. 9-18

9.3.3 RTC Status Register (RTSR).............................................................. 9-18

9.3.4 RTC Trim Register (RTTR)................................................................. 9-19

9.3.5 Trim Procedure................................................................................... 9-19

9.3.5.1 Oscillator Frequency Calibration............................................ 9-19

9.3.5.2 RTTR Value Calculations ...................................................... 9-20

9.3.6 Real-Time Clock Register Locations .................................................. 9-21

9.4 Operating System Timer.................................................................................. 9-21

9.4.1 OS Timer Count Register (OSCR)...................................................... 9-22

9.4.2 OS Timer Match Registers 0–3

OSMR<0>, OSMR<1>, OSMR<2>, OSMR<3>)................................. 9-22

9.4.3 OS Timer Watchdog Match Enable Register (OWER)....................... 9-22

9.4.4 OS Timer Status Register (OSSR)..................................................... 9-23

9.4.5 OS Timer Interrupt Enable Register (OIER) ....................................... 9-24

9.4.6 Watchdog Timer ................................. ....... ...... ...... ....... ...... ....... ...... ... 9-24

9.4.7 OS Timer Register Locations.............................................................. 9-25

9.5 Power Manager ................................. ....... ...... ....................................... ...... ... 9-26

9.5.1 Run Mode ........................................................................................... 9-26

9.5.2 Idle Mode............................................................................................ 9-26

9.5.2.1 Entering Idle Mode................................................................. 9-26

9.5.2.2 Exiting Idle Mode ................................ ...... ....... ...... ....... ...... ... 9-27

9.5.3 Sleep Mode............... ....... ...... ....................................... ...... ....... ...... ... 9-27

9.5.3.1 CPU Preparation for Sleep Mode .......................................... 9-27

9.5.3.2 Events Causing Entry into Sleep Mode ................................. 9-27

9.5.3.3 The Sleep Shutdown Sequence ............................................ 9-28

9.5.3.4 During Sleep Mode................................................................ 9-28

9.5.3.5 The Sleep Wake-Up Sequence ............................................. 9-28

SA-1100 Developer’s Manual v

Page 6

9.5.3.6 Booting After Sleep Mode...................................................... 9-29

9.5.3.7 Reviving the DRAMs from Self-Refresh Mode ...................... 9-30

9.5.4 Notes on Power Supply Sequencing.................................................. 9-30

9.5.5 Assumed Behavior of an SA-1100 System in Sleep Mode................. 9-30

9.5.6 Pin Operation in Sleep Mode.............................................................. 9-32

9.5.7 Power Manager Registers.................................................................. 9-33

9.5.7.1 Power Manager Control Register (PMCR) ............................ 9-33

9.5.7.2 Power Manager General Configuration Register (PCFR)...... 9-34

9.5.7.3 Power Manager PLL Configuration Register (PPCR)............ 9-35

9.5.7.4 Power Manager Wake-Up Enable Register (PWER)............. 9-36

9.5.7.5 Power Manager Sleep Status Register (PSSR) .................... 9-37

9.5.7.6 Power Manager Scratch Pad Register (PSPR)..................... 9-39

9.5.7.7 Power Manager GPIO Sleep State Register (PGSR)............ 9-39

9.5.7.8 Power Manager Oscillator Status Register (POSR) .............. 9-40

9.5.8 Power Manager Register Locations ................................................... 9-40

9.6 Reset Controller............................................................................................... 9-41

9.6.1 Reset Controller Registers .................... ....... ...... ...... ....... ................... 9-42

9.6.1.1 Reset Controller Software Reset Register (RSRR) ............... 9-42

9.6.1.2 Reset Controller Status Register (RCSR).............................. 9-43

9.6.2 Reset Controller Register Locations......................... ....... ...... ....... ...... 9-43

10 Memory and PCMCIA Control Module..........................................................................10-1

10.1 Overview of Operation..................................................................................... 10-1

10.1.1 Example Memory System.................................................................. 10-3

10.1.2 Types of Memory Accesses ............................................................... 10-4

10.1.3 Reads ................................................................................................. 10-4

10.1.4 Writes ................................................................................................ 10-4

10.1.5 Transaction Summary ....................................................................... 10-4

10.1.6 Read-Lock-Write................................................................................. 10-5

10.1.7 Aborts and Nonexistent Memory ....................................................... 10-5

10.2 Memory Configuration Registers.................................................................... 10-6

10.2.1 DRAM Configuration Register (MDCNFG) ......................................... 10-7

10.2.2 DRAM CAS Waveform Shift Registers

(MDCAS0, MDCAS1, MDCAS2) ........................................................ 10-9

10.2.3 Static Memory Control Registers (MSC1–0)..................................... 10-10

10.2.4 Expansion Memory (PCMCIA) Configuration Register (MECR)....... 10-12

10.3 Dynamic Interface Operation......................................................................... 10-14

10.3.1 DRAM Overview............................................................................... 10-14

10.3.2 DRAM Timing ................................................................................... 10-15

10.3.3 DRAM Refresh ................................................................................. 10-18

10.3.4 DRAM Self-Refresh in Sleep Mode.................................................. 10-18

10.4 Static Memory Interface................................................................................. 10-18

10.4.1 ROM Interface Overview .................................................................. 10-19

10.4.2 ROM Timing Diagrams and Parameters........................................... 10-19

10.4.3 SRAM Interface Overview ............... ...... ....... ...... ...... ....... ...... ........... 10-22

10.4.4 SRAM Timing Diagrams and Parameters........... ...... ....... ...... ....... .... 10-22

10.4.5 FLASH EPROM Interface Overview................................................ 10-23

10.4.6 FLASH EPROM Timing Diagrams and Parameters ........................ 10-24

10.5 General Memory BUS Timing........................................................................ 10-25

10.5.1 Static Access Followed by a DRAM Access..................................... 10-25

10.5.2 DRAM Access Followed by a Static Access..................................... 10-25

vi SA-1100 Developer’s Manual

Page 7

10.5.3 DRAM Access Followed by a Refresh Operation............................. 10-25

10.6 PCMCIA Overview............................. ....................................... ...... ....... ...... . 10-26

10.6.1 32-Bit Data Bus Operation............................................................... 10-27

10.6.2 External Logic for PCMCIA Implementation ................................... 10-28

10.6.3 PCMCIA Interface Timing Diagrams and Parameters..................... 10-31

10.7 Initialization of the Memory Interface............................................................. 10-34

10.7.1 Flow of Events After Reset or Exiting Sleep Mode........................... 10-34

10.8 Alternate Memory Bus Master Mode............................................................. 10-35

11 Peripheral Control Module.............................................................................................11-1

11.1 Read/Write Interface........................................................................................ 11-1

11.2 Memory Organization ...................................................................................... 11-2

11.3 Interrupts.......................................................................................................... 11-4

11.4 Peripheral Pins ................................................................................................ 11-5

11.5 Use of the GPIO Pins for Alternate Functions ................................................. 11-6

11.6 DMA Controller ................................................................................................ 11-7

11.6.1 DMA Register Definitions.................................................................... 11-7

11.6.1.1DMA Device Address Register (DDARn)............................... 11-8

11.6.1.2DMA Control/Status Register (DCSRn)............................... 11-11

11.6.1.3DMA Buffer A Start Address Register (DBSAn) ..................11-12

11.6.1.4DMA Buffer A Transfer Count Register (DBTAn) ................ 11-12

11.6.1.5DMA Buffer B Start Address Register (DBSBn) ..................11-13

11.6.1.6DMA Buffer B Transfer Count Register (DBTBn) ................ 11-13

11.6.2 DMA Operation.................................. ....... ...... ...... ....... ...... ....... ...... . 11-13

11.6.3 DMA Register List.............................................................................11-14

11.7 LCD Controller............................................................................................... 11-16

11.7.1 LCD Controller Operation ................................................................. 11-18

11.7.1.1DMA to Memory Interface.................................................... 11-18

11.7.1.2Frame Buffer........................................................................ 11-18

11.7.1.3Input FIFO............................................................................11-23

11.7.1.4Lookup Palette..................................................................... 11-23

11.7.1.5Color/Gray-Scale Dithering.................................................. 11-24

11.7.1.6Output FIFO.........................................................................11-24

11.7.1.7LCD Controller Pins............................................................. 11-25

11.7.2 LCD Controller Register Definitions.................................................. 11-25

11.7.3 LCD Controller Control Register 0.................................................... 11-26

11.7.3.1LCD Enable (LEN)............................................................... 11-26

11.7.3.2Color/Monochrome Select (CMS)........................................11-26

11.7.3.3Single-/Dual-Panel Select (SDS)......................................... 11-26

11.7.3.4LCD Disable Done Interrupt Mask (LDM)............................ 11-29

11.7.3.5Base Address Update Interrupt Mask (BAM).......................11-29

11.7.3.6Error Interrupt Mask (ERM) .................................................11-29

11.7.3.7Passive/Active Display Select (PAS)................................... 11-29

11.7.3.8Big/Little Endian Select (BLE).............................................. 11-31

11.7.3.9Double-Pixel Data (DPD) Pin Mode.....................................11-31

11.7.3.10Palette DMA Request Delay (PDD)................................... 11-31

11.7.4 LCD Controller Control Register 1.................................................... 11-34

11.7.4.1Pixels Per Line (PPL)........................................................... 11-34

11.7.4.2Horizontal Sync Pulse Width (HSW).................................... 11-34

11.7.4.3End-of-Line Pixel Clock Wait Count (ELW) .........................11-34

11.7.4.4Beginning-of-Line Pixel Clock Wait Count (BLW)................ 11-35

11.7.5 LCD Controller Control Register 2.................................................... 11-36

SA-1100 Developer’s Manual vii

Page 8

11.7.5.1Lines Per Panel (LPP)......................................................... 11-36

11.7.5.2Vertical Sync Pulse Width (VSW)........................................ 11-36

11.7.5.3End-of-Frame Line Clock Wait Count (EFW)....................... 11-37

11.7.5.4Beginning-of-Frame Line Clock Wait Count (BFW)............. 11-37

11.7.6 LCD Controller Control Register 3.................................................... 11-39

11.7.6.1Pixel Clock Divider (PCD).................................................... 11-39

11.7.6.2AC Bias Pin Frequency (ACB)............................................. 11-39

11.7.6.3AC Bias Pin Transitions Per Interrupt (API)......................... 11-40

11.7.6.4Vertical Sync Polarity (VSP)................................................ 11-40

11.7.6.5Horizontal Sync Polarity (HSP)............................................ 11-40

11.7.6.6Pixel Clock Polarity (PCP)................................................... 11-40

11.7.6.7Output Enable Polarity (OEP).............................................. 11-41

11.7.7 LCD Controller DMA Registers......................................................... 11-42

11.7.8 DMA Channel 1 Base Address Register........................................... 11-43

11.7.9 DMA Channel 1 Current Address Register....................................... 11-44

11.7.10 DMA Channel 2 Base and Current Address Registers..................... 11-45

11.7.11 LCD Controller Status Register ........................................................ 11-46

11.7.11.1LCD Disable Done Flag (LDD)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-46

11.7.11.2Base Address Update Flag (BAU)

(read-only, maskable interrupt)............................................ 11-46

11.7.11.3Bus Error Status (BER)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-46

11.7.11.4AC Bias Count Status (ABC)

(read/write, nonmaskabl e inter rupt )....... ...... ....... ................. 11-47

11.7.11.5Input FIFO Overrun Lower Panel Status (IOL)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-47

11.7.11.6Input FIFO Underrun Lower Panel Status (IUL)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-47

11.7.11.7Input FIFO Overrun Upper Panel Status (IOU)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-47

11.7.11.8Input FIFO Underrun Upper Panel Status (IUU)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-47

11.7.11.9Output FIFO Overrun Lower Panel Status (OOL)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-47

11.7.11.10Output FIFO Underrun Lower Panel Status (OUL)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-48

11.7.11.11Output FIFO Over run Upper Panel Status (OOU)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-48

11.7.11.12Output FIFO Underrun Upper Panel Status (OUU)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-48

11.7.12 LCD Controller Register Locations................................................... 11-50

11.7.13 LCD Controller Pin Timing Diagrams................................................ 11-51

11.8 Serial Port 0 – USB Device Controller........................................................... 11-56

11.8.1 USB Operation ................................................................................. 11-56

11.8.1.1Signalling Levels.................................................................. 11-57

11.8.1.2Bit Encoding ........................................................................ 11-58

11.8.1.3Field Formats....................................................................... 11-59

11.8.1.4Packet Formats .................. ...... ....... ...... ...... ....... ...... ....... .... 11-60

11.8.1.5Transaction Formats............................................................ 11-61

11.8.1.6UDC Device Requests......................................................... 11-62

11.8.2 UDC Register Definitions.................................................................. 11-63

11.8.3 UDC Control Register....................................................................... 11-64

viii SA-1100 Developer’s Manual

Page 9

11.8.3.1UDC Disable (UDD)............................................................. 11-64

11.8.3.2 UDC Active (UDA) .............................................................. 11-64

11.8.3.3Bit 2 Reserved ..................................................................... 11-64

11.8.3.4Endpoint 0 Interrupt Mask (EIM).......................................... 11-64

11.8.3.5Receive Interrupt Mask (RIM).............................................11-64

11.8.3.6Transmit Interrupt Mask (TIM) ............................................ 11-64

11.8.3.7Suspend/Resume Interrupt Mask (SRM)............................. 11-65

11.8.3.8Reset Interrupt Mask (REM)................................................ 11-65

11.8.4 UDC Address Register .....................................................................11-66

11.8.5 UDC OUT Max Packet Register....................................................... 11-66

11.8.6 UDC IN Max Packet Register........................................................... 11-67

11.8.7 UDC Endpoint 0 Control/Status Register.......................................... 11-68

11.8.7.1OUT Packet Ready (OPR)................................................... 11-68

11.8.7.2IN Packet Ready (IPR) ........................................................ 11-68

11.8.7.3Sent Stall (SST)................................................................... 11-68

11.8.7.4Force Stall (FST) ...................................... ....... ...... ....... ...... . 11-68

11.8.7.5Data End (DE) .... ...... ....... ...... ....... ...... ...... ........................... 11-68

11.8.7.6Setup End (SE).................................................................... 11-68

11.8.7.7Serviced OPR (SO) .. ....... ...... ....................................... ...... . 11-68

11.8.7.8Serviced Setup End (SSE) .................................................. 11-69

11.8.8 UDC Endpoint 1 Control/Status Register.......................................... 11-70

11.8.8.1Receive FIFO Service (RFS)............................................... 11-70

11.8.8.2Receive Packet Complete (RPC) ........................................11-70

11.8.8.3Receive Packet Error (RPE)................................................ 11-70

11.8.8.4Sent Stall (SST)................................................................... 11-70

11.8.8.5Force Stall (FST) ...................................... ....... ...... ....... ...... . 11-70

11.8.8.6Receive FIFO Not Empty (RNE).......................................... 11-70

11.8.8.7Bits 7..6 Reserved ............................................................... 11-71

11.8.9 UDC Endpoint 2 Control/Status Register.......................................... 11-72

11.8.9.1Transmit FIFO Service (TFS) ..............................................11-72

11.8.9.2Transmit Packet Complete (TPC)........................................11-72

11.8.9.3 Transmit Packet Error (TPE) ..............................................11-72

11.8.9.4Transmit Underrun (TUR)............. ...... ................................. 11-72

11.8.9.5Sent STALL (SST)............................................................... 11-72

11.8.9.6Force STALL (FST) .. ....... ...... ....... ...... ...... ....... ...... ....... ...... . 11-72

11.8.9.7Bits 7..6 Reserved ............................................................... 11-73

11.8.10 UDC Endpoint 0 Data Register......................................................... 11-74

11.8.11 UDC Endpoint 0 Write Count Register ............................................. 11-74

11.8.12 UDC Data Register........................................................................... 11-75

11.8.13 UDC Status/Interrupt Register.......................................................... 11-76

11.8.13.1Endpoint 0 Interrupt Request (EIR) ...................................11-76

11.8.13.2Receive Interrupt Request (RIR) ....................................... 11-76

11.8.13.3Transmit Interrupt Request (TIR)....................................... 11-76

11.8.13.4Suspend Interrupt Request (SUSIR) .................................11-76

11.8.13.5Resume Interrupt Request (RESIR) .................................. 11-76

11.8.13.6 Reset Interrupt Request (RSTIR) ..................................... 11-77

11.8.14 UDC Register Locations ................................................................... 11-78

11.9 Serial Port 1 – SDLC/UART........................................................................... 11-78

11.9.1 SDLC Operation ............................................................................... 11-79

11.9.1.1Bit Encoding......................................................................... 11-79

11.9.1.2Frame Format...................................................................... 11-80

11.9.1.3Address Field....................................................................... 11-80

11.9.1.4Control Field ........................................................................ 11-80

SA-1100 Developer’s Manual ix

Page 10

11.9.1.5Data Field ............................................................................ 11-81

11.9.1.6CRC Field............................................................................ 11-81

11.9.1.7Baud Rate Generation......................................................... 11-81

11.9.1.8Receive Operation............................................................... 11-82

11.9.1.9Transmit Operation.............................................................. 11-83

11.9.1.10Simultaneous Use of the UART and SDLC....................... 11-83

11.9.1.11Transmit and Receive FIFOs............................................. 11-84

11.9.1.12CPU and DMA Register Access Sizes .............................. 11-84

11.9.2 SDLC Register Definitions................................................................ 11-84

11.9.3 SDLC Control Register 0 .................................................................. 11-85

11.9.3.1SDLC/UART Select (SUS)................................................... 11-85

11.9.3.2Single/Double Flag Select (SDF)......................................... 11-85

11.9.3.3Loopback Mode (LBM) ........................................................ 11-85

11.9.3.4Bit Modulation Select (BMS)................................................ 11-86

11.9.3.5Sample Clock Enable (SCE) ............................................... 11-86

11.9.3.6Sample Clock Direction (SCD) ............................................ 11-86

11.9.3.7Receive Clock Edge Select (RCE) ...................................... 11-87

11.9.3.8Transmit Clock Edge Select (TCE)...................................... 11-87

11.9.4 SDLC Control Register 1 .................................................................. 11-88

11.9.4.1Abort After Frame (AAF)...................................................... 11-88

11.9.4.2Transmit Enable (TXE)........................................................ 11-89

11.9.4.3Receive Enable (RXE)......................................................... 11-89

11.9.4.4Receive FIFO Interrupt Enable (RIE)................................... 11-89

11.9.4.5Transmit FIFO Interrupt Enable (TIE).................................. 11-89

11.9.4.6Address Match Enable (AME) ............................................. 11-90

11.9.4.7Transmit FIFO Underrun Select (TUS)................................ 11-90

11.9.4.8Receiver Abort Interrupt Enable(RAE)................................. 11-90

11.9.5 SDLC Control Register 2 .................................................................. 11-92

11.9.5.1Address Match Value (AMV) ............................................... 11-92

11.9.6 SDLC Control Registers 3 and 4 ...................................................... 11-93

11.9.6.1Baud Rate Divisor (BRD)..................................................... 11-93

11.9.7 SDLC Data Register ......................................................................... 11-94

11.9.8 SDLC Status Register 0 ................................................................... 11-96

11.9.8.1End/Error in FIFO Status (EIF)

(read-only, nonmaskable interrupt)...................................... 11-96

11.9.8.2Transmit Underrun Status (TUR)

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-96

11.9.8.3Receiver Abort Status (RAB )

(read/write, maskable interrupt)................... ....... ...... ....... .... 11-96

11.9.8.4Transmit FIFO Service Request Flag (TFS)

(read-only, maskable interrupt)............................................ 11-97

11.9.8.5Receive FIFO Service Request Flag (RFS)

(read-only, maskable interrupt)............................................ 11-97

11.9.9 SDLC Status Register 1 ................................................................... 11-99

11.9.9.1Receiver Synchronized Flag (RSY)

(read-only, noninterruptible)................................................. 11-99

11.9.9.2Transmitter Busy Flag (TBY)

(read-only, noninterruptible)................................................. 11-99

11.9.9.3Receive FIFO Not Empty Flag (RNE)

(read-only, noninterruptible)................................................. 11-99

11.9.9.4Transmit FIFO Not Full Flag (TNF)

(read-only, noninterruptible)................................................. 11-99

x SA-1100 Developer’s Manual

Page 11

11.9.9.5Receive Transition Detect Status (RTD)

(read/write, noninterruptible)................................................ 11-99

11.9.9.6End of Frame Flag (EOF)

(read-only, noninterruptible)................................................. 11-99

11.9.9.7CRC Error Status (CRE)

(read-only, noninterruptible)............................................... 11-100

11.9.9.8Receiver Overrun Status (ROR)

(read-only, noninterruptible)............................................... 11-100

11.9.10 UART Register Locations ............................................................... 11-102

11.9.11 SDLC Register Locations ............................................................... 11-103

11.10 Serial Port 2 – Infrared Communications Port (ICP).................................... 11-103

11.10.1 Low-Speed ICP Operation.............................................................. 11-104

11.10.1.1HP-SIR* Modulation......................................................... 11 -104

11.10.1.2 UART Frame Format ...................................................... 11-104

11.10.2 High-Speed ICP Operation............................................................. 11-105

11.10.2.14PPM Modulation ............................................................ 11-105

11.10.2.2HSSP Frame Format ....................................................... 11-106

11.10.2.3Address Field................................................................... 11-107

11.10.2.4Control Field .................................................................... 11-107

11.10.2.5Data Field ........................................................................ 11-107

11.10.2.6CRC Field ........................................................................ 11-107

11.10.2.7Baud Rate Generation..................................................... 11-108

11.10.2.8Receive Operation........................................................... 11-108

11.10.2.9Transmit Operation.......................................................... 11-109

11.10.2.10Transmit and Receive FIFOs......................................... 11-110

11.10.2.11CPU and DMA Register Access Sizes .......................... 11-110

11.10.3 UART Register Definition................................................................ 11-111

11.10.4 UART Control Register 4................................................................ 11-111

11.10.4.1HP-SIR Enable (HSE)...................................................... 11-111

11.10.4.2Low-Power Mode (LPM).................................................. 11-111

11.10.5 HSSP Register Definitions.............................................................. 11-112

11.10.6 HSSP Control Register 0................................................................ 11-112

11.10.6.1IrDA Transmission Rate (ITR) ......................................... 11-112

11.10.6.2Loopback Mode (LBM) .................................................... 11-112

11.10.6.3Transmit FIFO Underrun Select (TUS)............................ 11-113

11.10.6.4Transmit Enable (TXE).................................................... 11-113

11.10.6.5Receive Enable (RXE)..................................................... 11-114

11.10.6.6Receive FIFO Interrupt Enable (RIE)............................... 11-114

11.10.6.7Transmit FIFO Interrupt Enable (TIE).............................. 11-114

11.10.6.8Address Match Enable (AME) ......................................... 11-114

11.10.7 HSSP Control Register 1................................................................ 11-116

11.10.7.1Address Match Value (AMV) ........................................... 11-116

11.10.8 HSSP Control Register 2................................................................ 11-117

11.10.8.1Transmit Pin Polarity Select (TXP) .................................. 11-117

11.10.8.2Receive Pin Polarity Select (RXP)................................... 11-117

11.10.9 HSSP Data Register....................................................................... 11-119

11.10.10HSSP Status Register 0 ................................................................ 11-121

11.10.10.1End/Error in FIFO Status (EIF)

(read-only, nonmaskable interrupt).................................... 11-121

11.10.10.2Transmit Underrun Status (TUR)

(read/write, maskable interrupt)......................................... 11-121

11.10.10.3Receiver Abort Status (RAB)

(read/write, nonmaskable interrupt)................................... 11-121

SA-1100 Developer’s Manual xi

Page 12

11.10.10.4Transmit FIFO Service Request Flag (TFS)

(read-only, maskable interrupt).......................................... 11-122

11.10.10.5Receive FIFO Service Request Flag (RFS)

(read-only, maskable interrupt).......................................... 11-122

11.10.10.6Framing Error Status (FRE)

(read/write, nonmaskabl e inter rupt )....... ...... ....... ............... 11-123

11.10.11HSSP Status Register 1 ................................................................ 11-124

11.10.11.1Receiver Synchronized Flag (RSY)

(read-only, noninterruptible)............................................... 11-124

11.10.11.2Transmitter Busy Flag (TBY)

(read-only, noninterruptible)............................................... 11-124

11.10.11.3Receive FIFO Not Empty Flag (RNE)

(read-only, noninterruptible)............................................... 11-124

11.10.11.4Transmit FIFO Not Full Flag (TNF)

(read-only, noninterruptible)............................................... 11-124

11.10.11.5End-of-Frame Flag (EOF)

(read-only, noninterruptible)............................................... 11-124

11.10.11.6CRC Error Status (CRE)

(read-only, noninterruptible)............................................... 11-125

11.10.11.7Receiver Overrun Status (ROR)

(read-only, noninterruptible)............................................... 11-125

11.10.12UART Register Locations.............................................................. 11-127

11.10.13HSSP Register Locations.............................................................. 11-127

11.11 Serial Port 3 - UART.................................................................................... 11-128

11.11.1 UART Operation............................................................................. 11-128

11.11.1.1Frame Format.................................................................. 11-129

11.11.1.2Baud Rate Generation..................................................... 11-129

11.11.1.3Receive Operation........................................................... 11-129

11.11.1.4Transmit Operation.......................................................... 11-130

11.11.1.5Transmit and Receive FIFOs........................................... 11-130

11.11.1.6CPU and DMA Register Access Sizes ............................ 11-131

11.11.2 UART Register Definitions.............................................................. 11-131

11.11.3 UART Control Register 0................................................................ 11-131

11.11.3.1Parity Enable (PE)........................................................... 11-131

11.11.3.2Odd/Even Parity Select (OES) ........................................ 11-131

11.11.3.3Stop Bit Select (SBS) ............. ....... ...... ...... ....... ............... 11-132

11.11.3.4Data Size Select (DSS) ................................................... 11-132

11.11.3.5Sample Clock Enable (SCE) ........................................... 11-132

11.11.3.6Receive Clock Edge Select (RCE) .................................. 11-132

11.11.3.7Transmit Clock Edge Select (TCE).................................. 11-133

11.11.4 UART Control Registers 1 and 2.................................................... 11-134

11.11.4.1Baud Rate Divisor (BRD)................................................. 11-134

11.11.5 UART Control Register 3................................................................ 11-135

11.11.5.1Receiver Enable (RXE) ................................................... 11-135

11.11.5.2Transmitter Enable (TXE)................................................ 11-135

11.11.5.3Break (BRK) .................................................................... 11-135

11.11.5.4Receive FIFO Interrupt Enable (RIE)............................... 11-135

11.11.5.5Transmit FIFO Interrupt Enable (TIE).............................. 11-136

11.11.5.6Loopback Mode (LBM) .................................................... 11-136

11.11.6 UART Data Register....................................................................... 11-137

11.11.7 UART Status Register 0 ................................................................. 11-139

11.11.7.1Transmit FIFO Service Request Flag (TFS)

(read-only, maskable interrupt).......................................... 11-139

xii SA-1100 Developer’s Manual

Page 13

11.11.7.2Receive FIFO Service Request Flag (RFS)

(read-only, maskable interrupt).......................................... 11-139

11.11.7.3Receiver Idle Status (RID)

(read/write, maskable interrupt)......................................... 11-140

11.11.7.4Receiver Begin of Break Status (RBB)

(read/write, nonmaskable interrupt)................................... 11-140

11.11.7.5Receiver End of Break Status (REB)

(read/write, nonmaskable interrupt)11-140

11.11.7.6Error in FIFO Flag (EIF)

(read-only, nonmaskable interrupt).................................... 11-140

11.11.8 UART Status Register 1 ................................................................. 11-142

11.11.8.1Transmitter Busy Flag (TBY

(read-only, noninterruptible)............................................... 11-142

11.11.8.2Receive FIFO Not Empty Flag (RNE)

(read-only, noninterruptible)............................................... 11-142

11.11.8.3Transmit FIFO Not Full Flag (TNF)

(read-only, noninterruptible)............................................... 11-142

11.11.8.4Parity Error Flag (PRE)

(read-only, noninterruptible)............................................... 11-142

11.11.8.5Framing Error Flag (FRE)

(read-only, noninterruptible)............................................... 11-143

11.11.8.6Receiver Overrun Flag (ROR)

(read-only, noninterruptible)............................................... 11-143

11.11.9 UART Register Locations ............................................................... 11-145

11.12 Serial Port 4 – MCP / SSP........................................................................... 11-145

11.12.1 MCP Operation............................................................................... 11-146

11.12.1.1Frame Format...................... ....... ..................................... 11 -147

11.12.1.2Audio and Telecom Sample Rates and Data Transfer .... 11-148

11.12.1.3MCP Transmit and Receive FIFO Operation................... 11-149

11.12.1.4Codec Control Register Data Transfer ............................ 11-150

11.12.1.5External Clock Operation................................................. 11-151

11.12.1.6Alternate SSP Pin Assignment ........................................ 11-151

11.12.1.7CPU and DMA Register Access Sizes ............................ 11-151

11.12.2 MCP Register Definitions................................................................ 11-152

11.12.3 MCP Control Register..................................................................... 11-152

11.12.3.1Audio Sample Rate Divisor (ASD)................................... 11-152

11.12.3.2Telecom Sample Rate Divisor (TSD)............................... 11-153

11.12.3.3 Multimedia Communications Port Enable (MCE) .......... 11-154

11.12.3.4External Clock Select (ECS)............................................ 11-154

11.12.3.5A/D Sampling Mode (ADM) ............................................. 11-154

11.12.3.6Telecom Transmit FIFO Interrupt Enable (TTE).............. 11-155

11.12.3.7Telecom Receive FIFO Interrupt Enable (TRE)............... 11-155

11.12.3.8Audio Transmit FIFO Interrupt Enable (ATE) .................. 11-155

11.12.3.9Audio Receive FIFO Interrupt Enable (ARE) ................... 11-155

11.12.3.10Loopback Mode (LBM) .................................................. 11-156

11.12.3.11External Clock Prescaler (ECP)..................................... 11-156

11.12.4 MCP Control Register 1.................................................................. 11-158

11.12.4.1Clock Frequency Select (CFS) ........................................ 11-158

11.12.5 MCP Data Registers....................................................................... 11-158

11.12.5.1MCP Data Register 0....................................................... 11-159

11.12.5.2MCP Data Register 1....................................................... 11-160

11.12.5.3MCP Data Register 2....................................................... 11-161

11.12.6 MCP Status Register ...................................................................... 11-163

SA-1100 Developer’s Manual xiii

Page 14

11.12.6.1Audio Transmit FIFO Service Request Flag (ATS)

(read-only, maskable interrupt).......................................... 11-163

11.12.6.2Audio Receive FIFO Service Request Flag (ARS)

(read-only, maskable interrupt).......................................... 11-163

11.12.6.3Telecom Transmit FIFO Service Request Flag (TTS)

(read-only, maskable interrupt).......................................... 11-164

11.12.6.4Telecom Receive FIFO Service Request Flag (TRS)

(read-only, maskable interrupt).......................................... 11-164

11.12.6.5Audio Transmit FIFO Underrun Status (ATU)

(read/write, nonmaskabl e inter rupt )....... ...... ....... ............... 11-164

11.12.6.6Audio Receive FIFO Overrun Status (ARO)

(read/write, nonmaskabl e inter rupt )....... ...... ....... ............... 11-164

11.12.6.7Telecom Transmit FIFO Underrun Status (TTU)

(read/write, nonmaskabl e inter rupt )....... ...... ....... ............... 11-165

11.12.6.8Telecom Receive FIFO Over run Sta t us (TRO)

(read/write, nonmaskabl e inter rupt )....... ...... ....... ............... 11-165

11.12.6.9Audio Transmit FIFO Not Full Flag (ANF)

(read-only, noninterruptible)............................................... 11-165

11.12.6.10Audio Receive FIFO Not Empty Flag (ANE)

(read-only, noninterruptible)............................................... 11-165

11.12.6.11Telecom Transmit FIFO Not Full Flag (TNF)

(read-only, noninterruptible)............................................... 11-165

11.12.6.12Telecom Receive FIFO Not Empty Flag (TNE)

(read-only, noninterruptible)............................................... 11-166

11.12.6.13Codec Write Completed Flag (CWC)

(read-only, noninterruptible)............................................... 11-166

11.12.6.14Codec Read Completed Flag (CRC)

(read-only, noninterruptible)............................................... 11-166

11.12.6.15Audio Codec Enabled Flag (ACE)

(read-only, noninterruptible)............................................... 11-166

11.12.6.16Telecom Codec Enabled Flag (TCE)

(read-only, noninterruptible)............................................... 11-166

11.12.7 SSP Operation ....... ...... ....... ...... ....... ...... ....................................... .. 11-169

11.12.7.1Frame Format.................................................................. 11-169

11.12.7.2Baud Rate Generation..................................................... 11-173

11.12.7.3 SSP Transmit and Receive FIFOs.................................. 11-173

11.12.7.4CPU and DMA Register Access Sizes ............................ 11-174

11.12.7.5Alternate SSP Pin Assignment ........................................ 11-174

11.12.8 SSP Register Definitions ................. ...... ....... ...... ...... ....... ...... ....... .. 11-174

11.12.9 SSP Control Register 0 .................................................................. 11-174

11.12.9.1Data Size Select (DSS) ................................................... 11-175

11.12.9.2Frame Format (FRF)........................................................ 11-175

11.12.9.3Synchronous Serial Port Enable (SSE)........................... 11-175

11.12.9.4Serial Clock Rate (SCR)............................ ...................... 1 1-176

11.12.10SSP Control Register 1 ................................................................. 11-177

11.12.10.1Receive FIFO Interrupt Enable (RIE)............................. 11-177

11.12.10.2Transmit FIFO Interrupt Enable (TIE)............................ 11-177

11.12.10.3Loopback Mode (LBM) .................................................. 11-177

11.12.10.4Serial Clock Polarity (SPO)............................................ 11-177

11.12.10.5Serial Clock Phase (SPH) ............................................. 11-178

11.12.10.6External Clock Select (ECS).......................................... 11-179

11.12.11SSP Data Register ........................................................................ 11-180

11.12.12SSP Status Register...................................................................... 11-181

xiv SA-1100 Developer’s Manual

Page 15

11.12.12.1Transmit FIFO Not Full Flag (TNF)

(read-only, noninterruptible)............................................... 11-181

11.12.12.2Receive FIFO Not Empty Flag (RNE)

(read-only, noninterruptibl11-181

11.12.12.3SSP Busy Flag (BSY)

(read-only, noninterruptible)............................................... 11-181

11.12.12.4Transmit FIFO Service Request Flag (TFS)

(read-only, maskable interrupt)............................................ 1-181

11.12.12.5Receive FIFO Service Request Flag (RFS)

(read-only, maskable interrupt).......................................... 11-182

11.12.12.6Receiver Overrun Status (ROR)

(read/write, nonmaskable interrupt)................................... 11-182

11.12.13MCP Register Locations................................................................ 11-183

11.12.14SSP Register Locations................................................................. 11-183

11.13 Peripheral Pin Controller (PPC)................................................................... 11-184

11.13.1 PPC Operation................................................................................ 11-184

11.13.2 PPC Register Definitions ................................................................ 11-185

11.13.3 PPC Pin Direction Register............................................................. 11-185

11.13.4 PPC Pin State Register .................................................................. 11-187

11.13.5 PPC Pin Assignment Register........................................................ 11-189

11.13.5.1UART Pin Reassignment (UPR)......................................11-189

11.13.5.2SSP Pin Reassignm ent (SPR)......................................... 11-1 89

11.13.6 PPC Sleep Mode Pin Direction Register ........................................ 11-190

11.13.7 PPC Pin Flag Register.................................................................... 11-192

11.13.8 PPC Register Locations.................................................................. 11-193

12 DC Parameters......................... ....... ...... ....... ...... ...... ....... ...... ....... ...... ...........................12-1

12.1 Absolute Maximum Ratings............................................................................. 12-1

12.2 DC Operating Conditions................................................................................. 12-2

12.3 Power Supply Voltages and Currents.............................................................. 12-3

13 AC Parameters..............................................................................................................13-1

13.1 Test Conditions...................... ....... ...... ....................................... ...... ....... ...... ... 13-1

13.2 Module Considerations.................................................................................... 13-2

13.3 Memory Bus and PCMCIA Signal Timings...................................................... 13-2

13.4 LCD Controller Signals .................................................................................... 13-3

13.5 MCP Signals.................................................................................................... 13-3

13.6 Timing Parameters .......................................................................................... 13-4

13.6.1 Asynchronous Signal Timing Descriptions ......................................... 13-5

14 Package and Pinout ......................................................................................................14-1

14.1 Mechanical Data and Packaging Information .................................................. 14-1

14.2 Mini-Ball Grid Array – (mBGA)......................................................................... 14-3

15 Debug Support..............................................................................................................15-1

15.1 Instruction Breakpoint...................................................................................... 15-1

15.2 Data Breakpoint.................................. ....................................... ...... ....... ...... ... 15-1

16 Boundary-Scan Test Interface.......................................................................................16-1

16.1 Overview.......................................................................................................... 16-1

16.2 Reset ............................................................................................................... 16-2

16.3 Pull-Up Resistors....................................... ...... ....... ...................................... ... 16-2

SA-1100 Developer’s Manual xv

Page 16

16.4 Instruction Register.......................................................................................... 16-2

16.5 Public Instructions ........................................................................................... 16-2

16.5.1 EXTEST (00000) ................................................................................ 16-3

16.5.2 SAMPLE/PRELOAD (00001) ............................................................. 16-3

16.5.3 CLAMP (00100).................................................................................. 16-3

16.5.4 HIGHZ (00101)................................................................................... 16-4

16.5.5 IDCODE (00110) ................................................................................ 16-4

16.5.6 BYPASS (11111)................................................................................ 16-4

16.6 Test Data Registers......................................................................................... 16-5

16.6.1 Bypass Register ................................................................................. 16-5

16.6.2 SA-1100 Device Identification (ID) Code Register.............................. 16-6

16.6.3 SA-1100 Boundary-Scan (BS) Register ............................................. 16-6

16.7 Boundary-Scan Interface Signals.................................................................... 16-7

A Register Summary ......................................................................................................... A-1

B 3.6864–MHz Oscillator Specifications............................................................................ B-1

B.1 Specifications ....................................................................................................B-1

B.1.1 System Specifications ........ ...... ....... ...... ....... ...... ..................................B-1

B.1.1.1.Parasitic Capacitance Off-chip

Between PXTAL and PEXTAL.................................................B-2

B.1.1.2.Parasitic Capacitance Off-chip

Between PXTAL or PEXTAL and VSS....................................B-2

B.1.1.3.Parasitic Resistance Between PXTAL and PEXTAL...............B-2

B.1.1.4.Parasitic Resistance Between PXTAL or PEXTAL and VSS...B-2

B.1.2 Quartz Crystal Specification .................................................................B-3

C 32.768–kHz Oscillator Specifications.............................................................................C-1

C.1 Specifications ....................................................................................................C-1

C.1.1 System Specifications . ....... ...... ....... ...... ....... ...................................... ..C-1

C.1.1.1.Temperature Range.................................................................C-1

C.1.1.2.Current Consumption...............................................................C-1

C.1.1.3.Startup Time............................................................................C-1

C.1.1.4.Frequency Shift Due to Temperature Effect on the Circuit......C-2

C.1.1.5.Parasitic Capacitance Off-chip

Between TXTAL and TEXTAL.................................................C-2

C.1.1.6.Parasitic Capacitance Off-chip

Between TXTAL or TEXTAL and VSS................ ...... ....... ........C-2

C.1.1.7.Parasitic Resistance Between TXTAL and TEXTAL ...............C-2

C.1.1.8.Parasitic Resistance Between TXTAL or TEXTAL and VSS...C-2

C.1.2 Quartz Crystal Specification .................................................................C-3

D Internal Test................................................................................................................... D-1

D.1 Test Unit Control Register (TUCR)....................................................................D-1

xvi SA-1100 Developer’s Manual

Page 17

Figures

1-1 SA-1100 Features.............................................................................................. 1-1

1-2 SA-1100 Example System................................................................................. 1-5

2-1 SA-1100 Block Diagram .................................................................................... 2-2

2-2 SA-1100 Functional Diagram............................................................................. 2-3

2-3 SA-1100 Memory Map....................................................................................... 2-8

5-1 Format of Internal Coprocessor Instructions MRC and MCR ............................ 5-1

9-1 General-Purpose I/O Block Diagram................................................................. 9-2

9-2 Interrupt Controller Block Diagram .................................................................. 9-11

9-3 Transitions Between Modes of Operation........................................................ 9-31

10-1 General Memory Interface Configuration........................................................ 10-1

10-2 Example Memory Configuration ............................. ...................................... ... 10-3

10-3 DRAM Single-Beat Transactions................................................................... 10-16

10-4 DRAM Burst-of-Eight Transactions................................................................ 10-17

10-5 DRAM Refresh Cycle..................................................................................... 10-18

10-6 Burst-of-Eight ROM Timing Diagram............................................................. 10-20

10-7 Eight Beat Burst Read from Burst-of-Four ROM ...........................................10-21

10-8 Nonburst ROM, SRAM, or Flash Read Timing Diagram – Four Data Beats . 10-21

10-9 SRAM Write Timing Diagram (4–Beat Burst) ................................................ 10-22

10-10 Flash Write Timing Diagram (2 Writes).......................................................... 10-24

10-11 PCMCIA Memory Map........................ ....... ...................................... ....... ...... . 10-26

10-12 PCMCIA External Logic for a Two-Socket Configuration .............................. 10-29

10-13 PCMCIA External Logic for a One-Socket Configuration ..............................10-30

10-14 PCMCIA Voltage-Control Logic .............................. ...... ...... ....... ...... ....... ....... 10-31

10-15 PCMCIA Memory or I/O 16-Bit Access............................................ ....... ...... . 10-32

10-16 PCMCIA I/O 16-Bit Access to 8-Bit Device.................................................... 10-33

11-1 Peripheral Control Module Block Diagram....................................................... 11-2

11-2 Big and Little Endian DMA Transfers............................................................... 11-9

11-3 Palette Buffer Format..................................................................................... 11-19

11-4 4 Bits Per Pixel Data Memory Organization (Little Endian)........................... 11-20

11-5 8-Bits Per Pixel Data Memory Organization (Little Endian)........................... 11-21

11-6 12-Bits Per Pixel Data Memory Organization (Passive Mode Only).............. 11-21

11-7 16-Bits Per Pixel Data Memory Organization (Active Mode Only)................. 11-21

11-8 LCD Data-Pin Pixel Ordering......................................................................... 11-28

11-9 Frame Buffer/Palette Bits Output to LCD Data Pins in Active Mode ............. 11-30

11-10 Passive Mode Beginning-of-Frame Timing.................................................... 11-51

11-11 Passive Mode End-of-Frame Timing............................................................. 11-52

11-12 Passive Mode Pixel Clock and Data Pin Timing............................................ 11-53

11-13 Active Mode Timing ....................................................................................... 11-54

11-14 Active Mode Pixel Clock and Data Pin Timing............................................... 11-55

11-15 NRZI Bit Encoding Example.......................................................................... 11-58

11-16 IN, OUT, and SETUP Token Packet Format................................................. 11-60

11-17 SOF Token Packet Format............................................................................ 11-60

11-18 Data Packet Format............................ ....... ...... ....... ...... ................................. 11-60

11-19 Handshake Packet Format ............................................................................ 11-60

11-20 Bulk Transaction Formats................................................... ....... ...... ....... ...... . 11-61

11-21 Control Transaction Formats ......................................................................... 11-62

11-22 FM0/NRZ Bit Encoding Example (0100 1011)............................................... 11-80

11-23 SDLC Frame Format ..................................................................................... 11-80

SA-1100 Developer’s Manual xvii

Page 18

11-24 HP-SIR Modulation Example....................................................................... 11-104

11-25 UART Frame Format for IrDA Transmission (<= 115.2 Kbps) .................... 11-105

11-26 4PPM Modulation Encodings ...................................................................... 11-105

11-27 4PPM Modulation Example ......................................................................... 11-106

11-28 High-Speed Serial Frame Format for IrDA Transmission (4.0 Mbps).......... 11-106

11-29 Example UART Data Frame........................................................................ 11-128

11-30 NRZ Bit Encoding Example – (0100 1011).................................................. 11-129

11-31 MCP Frame Data Format ............................................................................ 11-147

11-32 MCP Frame Pin Timing ............................................................................... 11-147

11-33 MPC/Codec Sampling Counter Synchronization......................................... 11-148

11-34 Audio/Telecom Transmit/Receive FIFO Data Format ................................. 11-150

11-35 Texas Instruments* Synchronous Serial Frame Format.............................. 11-170

11-36 Motorola* SPI Frame Format....................................................................... 11-171

11-37 National Microwire* Frame Format.............................................................. 11-172

11-38 Transmit/Receive FIFO Data Format .......................................................... 11-173

11-39 Motorola* SPI Frame Formats for SPO and SPH Programming ................. 11-178

13-1 Memory Bus AC Timing Definitions................................................................. 13-2

13-2 LCD AC Timing Definitions.............................................................................. 13-3

13-3 MCP AC Timing Definitions............................................................................. 13-3

14-1 Quad Flat Pack – 1.4mm (LQFP) .................................................................... 14-1

14-2 SA-1100 256 Mini-Ball Grid Array Mechanical Drawing.................................. 14-3

16-1 Test Access Port (TAP) Controller State Transitions ...................................... 16-1

16-2 Boundary-Scan Block Diagram ....................................................................... 16-5

16-3 Boundary-Scan General Timing ...................................................................... 16-7

16-4 Boundary-Scan Tristate Timing....................................................................... 16-8

16-5 Boundary-Scan Reset Timing.......................................................................... 16-8

Tables

1-1 Features of the SA-1100 CPU for AA and EA Parts.......................................... 1-2

1-2 Features of the SA-1100 CPU for CA and DA Parts ......................................... 1-2

1-3 Changes to the SA-1100 Core from the SA-110 ............................................... 1-3

1-4 Additional Features Built into SA-1100 Chipset................................................. 1-3

2-1 Signal Descriptions............................................................................................ 2-4

3-1 Vector Summa ry.............................. ...................................... ....... ...... ....... ...... .. 3-4

4-1 Instruction Timings ............................................................................................ 4-1

5-1 Cache and MMU Control Registers (Coprocessor 15)...................................... 5-2

6-1 Effects of the Cacheable and Bufferable Bits on the Data Caches ................... 6-3

7-1 Valid MMU, Dcache, and Write Buffer Combinations........................................ 7-2

8-1 Core Clock Configurations................................................................................. 8-2

9-1 OS Timer Register Locations .......................................................................... 9-25

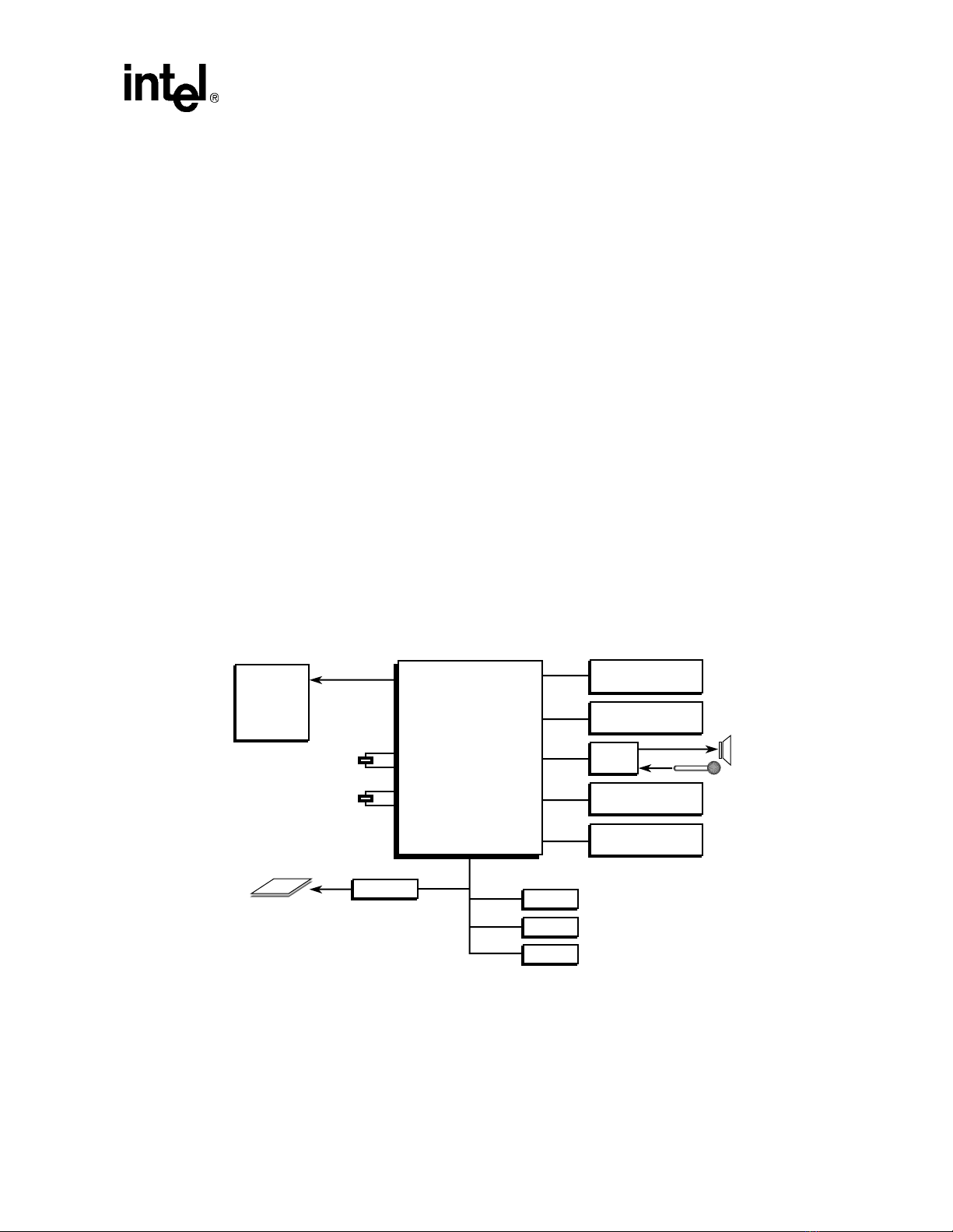

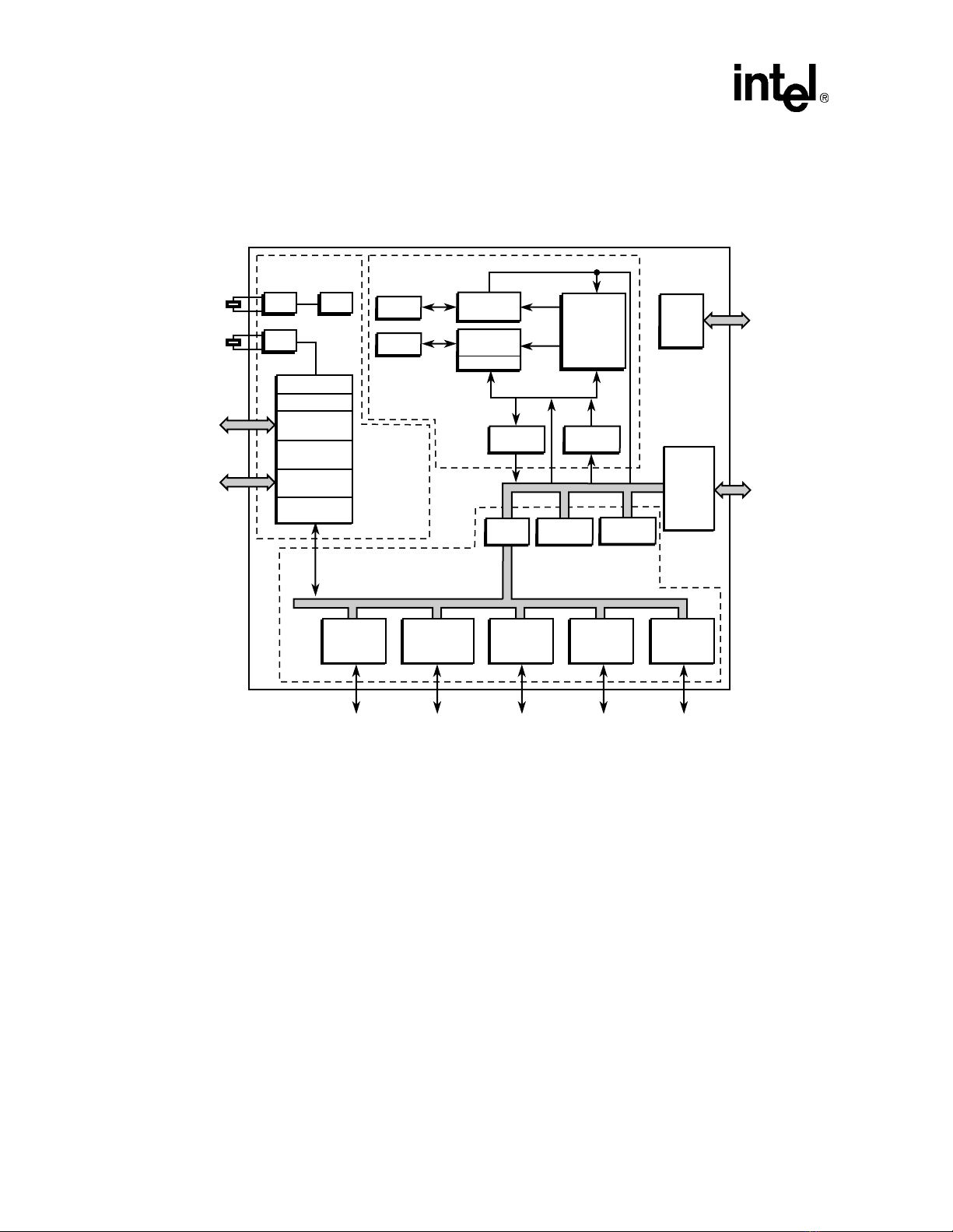

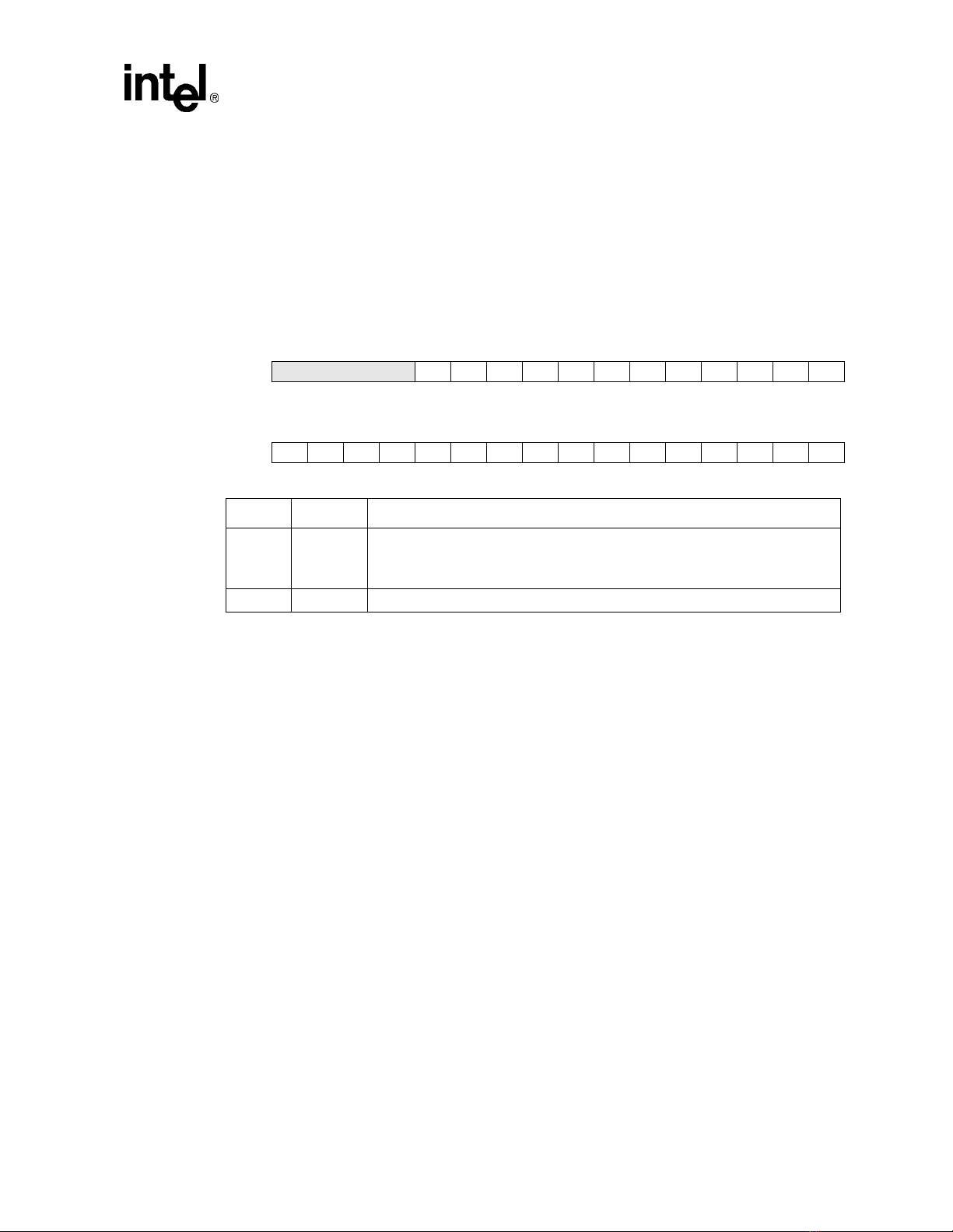

9-2 SA-1100 Power and Clock Supply Sources and States