Page 1

Intel

®

Core

TM

2 Duo Processor

and Intel

®

Q45 Express Chipset

Development Kit

User’s Manual

October 2008

Page 2

INFORMATION IN THIS DOCUMENT I S PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR

IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS

PROVIDED IN

INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL

DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR

WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT

OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves

these for future

definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Eagle Lake chipset may contain design defects or errors known as errata which may cause the product to deviate from published

specifications. Current

characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other

countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2008 Intel Corporation

All rights reserved.

2

Page 3

Contents

1.0 About this Manual 5

1.2 Text Conventions 6

1.3 Glossary of Terms and Acronyms 7

1.4 Support Options 8

1.4.1 Electronic Support Systems 8

1.4.2 Additional Technical Support 8

1.5 Product Literature 8

2.0 Development Kits Hardware Features 9

2.1 Intel® Q45 Development Kits Overview 9

2.2 System Block diagram 10

2.3 Development Kits Inventory Checklists 11

2.4 Processor Supported 12

2.5 System Memory 12

2.5.1 Dual Channel (Interleaved) Mode Configurations 13

2.5.2 Single Channel (Asymmetric) Mode Configurations 15

2.6 Back-Panel Connector 16

2.6.1 Audio-Connectors 16

2.6.2 RJ-45 LAN Connector with Integrated LEDs 17

2.6.3 USB Port 17

2.6.5 HDMI Port 17

2.7 Debug Features 18

2.7.1 Extended Debug Probe (XDP) 18

2.7.2 Power LEDs 19

2.7.3 Port 80 POST Code LEDs 19

2.7.4 Voltage Reference 19

2.8 Development Kit’s Major connector and Jumper 20

2.8.1 Jumper Functions 20

2.8.2 USB 2.0 Front Panel 21

2.8.3 1394a Header 21

2.9 SPI Removal/Installation Technique 23

2.9.1 SPI Device Installation 23

2.9.2 SPI Device Removal 26

3.0 Setting Up and configuring the development Kits 27

3.1 Overview 27

3.2 BTX Heatsink Setup 28

3.2.1 SRM Alignment on any BTX board 28

3.3 Board Setup and Configuration before Boot 29

3.4 Post Codes Definitions 31

4.0 BIOS Setup Utility 35

1.1 Content Overview 5

4.1 Main 35

4.1.1 System Overview 35

4.2 Advance 35

4.2.1 CPU Configuration 35

4.2.2 IDE Configuration 36

4.2.3 Floppy Configuration 37

4.2.4 ACPI Configuration 37

4.2.5 AHCI Configuration 38

3

Page 4

4.2.6 Intel AMT Configuration 38

4.2.7 MPS Configuration 39

4.2.8 SMBIOS Configuration 39

4.2.9 Remote Access Configuration 39

4.2.10 Trusted Computing 39

4.2.11 USB Configuration 40

4.3 PCIPnP 40

4.4 Boot 40

4.4.1 Boot setting Configuration 40

4.5 Security 41

4.6 Chipset 41

4.6.1 Northbridge Configuration 41

4.6.2 Southbridge Configuration 43

4.6.3 ME System Configuration 44

4.6.4 PCI Express Configuration 46

4.6.5 VE Subsystem Configuration 47

4.7 Virtual Appliance 47

4.8 SV 48

4.8.1 SV SMI Management 48

4.8.2 SV SATA Management 48

4.9 Exit 49

4

Page 5

1.0 About This Manual

This user’s manual describes the use of the Intel

manual has been written for OEMs, system evaluators, and embedded system developers. All

jumpers, headers, LED functions, and their locations on the board, along with subsystem

features and POST codes, are defined in this document.

For the latest information about the Intel

reference platform, visit:

http://developer.intel.com/design/intarch/devkits/index.htm?iid=embed_body+devkits

For design documents related to this platform, such as schematics and layout, please contact

your Intel Representative.

®

1.1 Content Overview

Chapter 1: “About This Manual”

This chapter contains a description of conventions used in this manual. The last few

sections explain how to obtain literature and contact customer support.

Chapter 2: “Development Kits Hardware Features”

This chapter provides information on the development kit features and the board

capability. This includes the information on board component features, jumper settings,

pin-out information for connectors and overall development kit board capability.

Chapter 3: “Development Kits Board ”

This chapter provides instructions on how to configure the evaluation board and

processor assembly by setting ATX heatsink, jumpers, connecting peripherals, providing

power, and configuring the BIOS.

Chapter 4: “BIOS Setup Utility”

This chapter provides the BIOS function and how to configure the BIOS features. This include

the BIOS option tab function like the Main System Overview, Advance, PCIPnP, Boot, Security,

Chipset, SV, Exit.

®

Q45 Express Chipset Development Kit. This

Q45 Express Chipset Development Kit

5

Page 6

1.2 Text Conventions

The following notations may be used throughout this manual.

# The pound symbol (#) appended to a signal name indicates that the

signal is active low.

Variables Variables are shown in italics. Variables must be replaced with correct

values.

Instructions Instruction mnemonics are shown in uppercase. When you are

programming, instructions are not case-sensitive. You may use either

upper-case or lower-case.

Numbers Hexadecimal numbers are represented by a string of hexadecimal

digits followed by the character H. A zero prefix is added to numbers

that begin with A through F. (For example, FF is shown as 0FFH.)

Decimal and binary numbers are represented by their customary

notations. (That is, 255 is a decimal number and 1111 1111 is a binary

number.) In some cases, the letter B is added for clarity.

Units of Measure The following abbreviations are used to represent units of measure:

GByte gigabytes

KByte kilobytes

MByte megabytes

MHz megahertz

W watts

V volts

Signal Names Signal names are shown in uppercase. When several signals share a

common name, an individual signal is represented by the signal name

followed by a number, while the group is represented by the signal

name followed by a variable (n). For example, the lower chip-select

signals are named CS0#, CS1#, CS2#, and so on; they are collectively

called CSn#. A pound symbol (#) appended to a signal name identifies

an active-low signal. Port pins are represented by the port

abbreviation, a period, and the pin number (e.g., P1.0).

6

Page 7

1.3 Glossary of Terms and Acronyms

This section defines conventions and terminology used throughout this document.

Term Description

ADD2 Card Advanced Digital Display Card – 2nd Generation. This card provides digital

ACPI Advanced Configuration and Power Interface

Core The internal base logic in the (G)MCH

DDR3 A third generation Double Data Rate SDRAM memory technology

DMI (G)MCH-Intel® ICH10 Direct Media Interface

DVI Digital Video Interface. Specification that defines the connector and

FSB Front Side Bus. FSB is synonymous with Host or processor bus

GMA 4500 Intel® Graphic Media Accelerator 4500

Intel® ICH10 Ninth generation I/O Controller Hub component that contains additional

IGD Internal Graphics Device.

LVDS Low Voltage Differential Signaling. A high speed, low power data

MCH Memory Controller Hub component that contains the processor interface,

MEC Media Expansion Card, also known as ADD2+ card. Refer to ADD2+ term for

PCI Express* Third Generation input/output graphics attach called PCI Express* Graphics.

Primary PCI The Primary PCI is the physical PCI bus that is driven directly by the ICH10

display options for an Intel Graphics Controller that supports ADD2+ cards.

It plugs into a x16 PCI Express* connector but uses the multiplexed SDVO

interface. The card adds Video In capabilities to platform. This Advanced

Digital Display Card will not work with an Intel Graphics Controller that

supports DVO and ADD cards. It will function as an ADD2 card in an ADD2

supported system, but video in capabilities will not work. T

interface for digital displays.

functionality compared to previous ICHs. The I/O Controller Hub component

contains the primary PCI interface, LPC interface, USB2, ATA-100, and other

I/O functions. It communicates with the (G)MCH over a proprietary

interconnect called DMI.

transmission standard used for display connections to LCD panels.

DRAM controller, and x16 PCI Express* port (typically, the external graphics

interface). It communicates with the I/O controller hub (Intel® ICH10) and

other I/O controller hubs over the DMI interconnect. In this document MCH

refers to the Intel® Q45 MCH component.

description.

PCI Express* is a high-speed serial interface whose configuration is software

compatible with the existing PCI specifications. The specific PCI Express*

implementation intended for connecting the (G)MCH to an external Graphics

Controller is a x16 link and replaces AGP.

component. Communication between Primary PCI and the (G)MCH occurs

over DMI. Note that the Primary PCI bus is not PCI Bus 0 from a

configuration standpoint.

7

Page 8

Term Description

SDVO Serial Digital Video Out (SDVO). SDVO is a digital display channel that

SDVO Device Third party codec that uses SDVO as an input. May have a variety of output

SMI System Management Interrupt. SMI is used to indicate any of several

Rank A unit of DRAM corresponding to eight x8 SDRAM devices in parallel or four

serially transmits digital display data to an external SDVO device. The SDVO

device accepts this serialized format and then translates the data into the

appropriate display format (i.e., TMDS, LVDS, TV-Out). This interface is not

electrically compatible with the previous digital display channel - DVO. For

the 82Q965 GMCH, it will be multiplexed on a portion of the x16 graphics

PCI Express* interface.

formats, including DVI, LVDS, HDMI, TV-out, etc.

system conditions (such as, thermal sensor events, throttling activated,

access to System Management RAM, chassis open, or other system state

related activity).

x16 SDRAM devices in parallel, ignoring ECC. These devices are usually, but

not always, mounted on a single side of a DIMM.

1.4 Support Options

1.4.1 Electronic Support Systems

Intel’s site on the World Wide Web (http://www.intel.com/) provides up-to-date technical

information and product support. This information is available 24 hours per day, 7 days per

week, providing technical information whenever you need it.

Product documentation is provided online in a variety of web-friendly formats at:

http://developer.intel.com/literature/index.asp

1.4.2 Additional Technical Support

If you require additional technical support, please contact your field sales representative or

local distributor.

1.5 Product Literature

Product literature can be ordered from the following Intel literature centers:

Location Telephone Number

U.S. and Canada 1-800-548-4725

U.S. (from overseas) 708-296-9333

Europe (U.K.) 44(0)1793-431155

Germany 44(0)1793-421333

France 44(0)1793-421777

Japan (fax only) 81(0)120-47-88-32

Table 1: Intel Literature Centers

8

Page 9

2.0 Development Kits Hardware Features

PCI Slot

SATA Port

This chapter describes the development kit features of the Intel® Q45 Development Kits.

These recommendations would largely apply to other designs incorporating Intel® Q45

chipset. This documentation should be used in conjunction with the Intel® Q45/ICH10

datasheet, specification updates and platform design guides. Contact your local Intel

representative for the availability of these documents.

2.1 Intel® Q45 Development Kits Overview

Figure 2-1 shows overview of the major features present on the development kit board. Refer

to next page for system block diagram of the development kit’s motherboard.

Port 80 LED

2x2

Standard

Power

Supply

PCI Express

PCI Express

X16 Graphic

Power On

Intel® I/O

Controller

Hub (ICH)

2-DIMM per

channel DDR2

667/800

(Channel-B)

Figure 2-1 Board Features

LGA775

Processor

Socket

Intel® Q45

Memory

Controller

Hub (MCH)

2-DIMM per

channel DDR2

667/800

(Channel-A)

2x12 Standard

Power Supply

9

Page 10

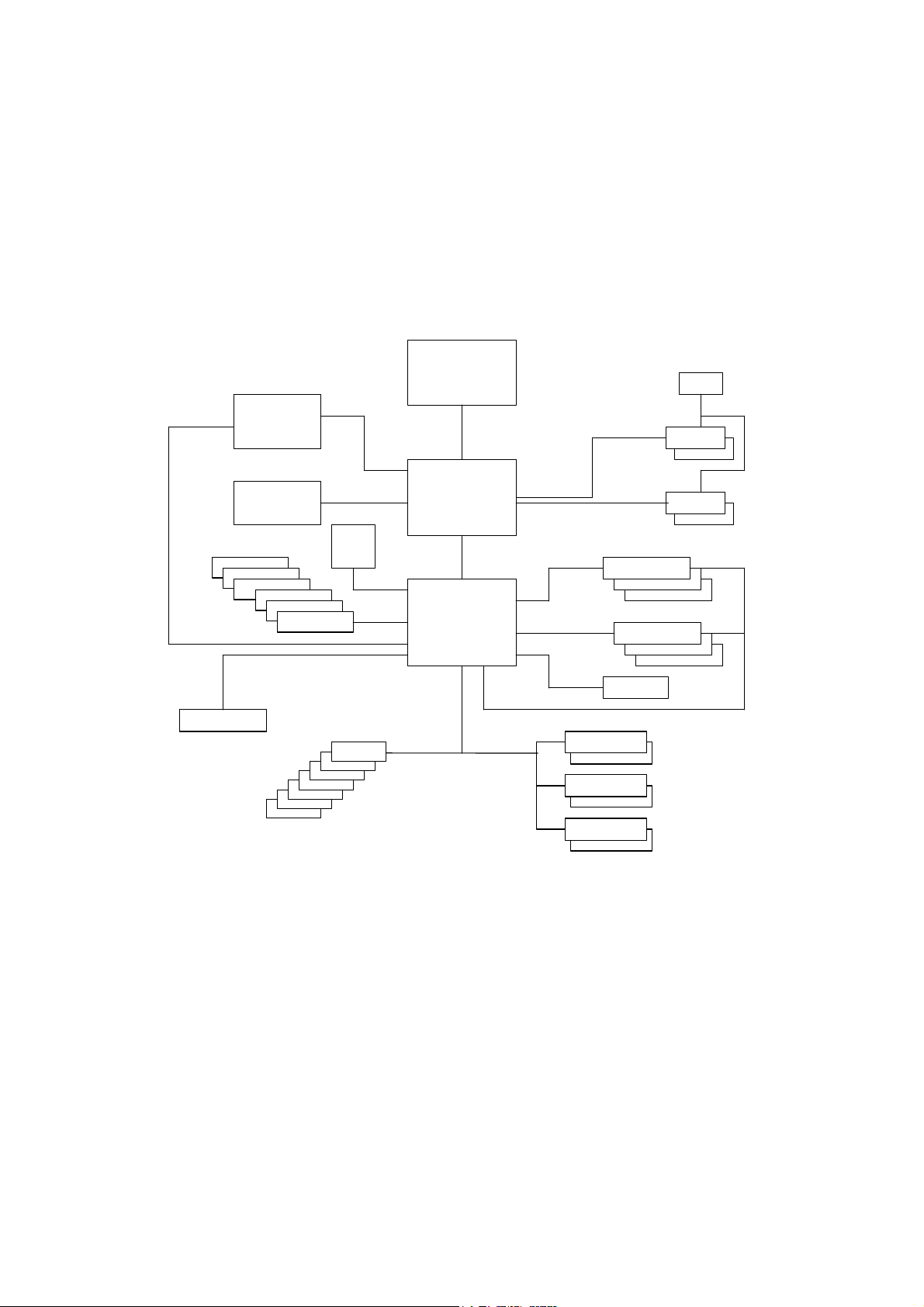

2.2 System Block Diagram

Dual

USB

SATA port

5

SATA port

4

SATA port

3

SATA port

2

SATA port 1

SATA port 0

PCI Slot

SP

This section will document the common features that are applicable to Intel® Q45 Express

Chipset Development Kits. Figure 2-2 show a simple block diagram of the Intel® Q45 Express

Chipset development kits.

SMBus Resume

PCI Express

Graphic

X16 slot

(Primary)

X16 PCI Express

Integrated

Graphic VGA

Output

Flash

Devic

SPI

HD Audio

USB 2.0

Figure 2-2 Intel® Q45 Development Kits block diagram.

LGA775

Processor

1033 MT/s

Graphics

Memory

Controller Hub

(GMCH)

I/O Controller

Hub

(ICH)

Back Panel Front Panel

SMBus

Channel

DDR3

1066

X1 PCI Express

PCI Bus

PCI

USB or LAN

USB or 1394

USB

PCIE Slot

1394

Clock

SMBus Main

DDR3

DDR3

SMBus Resume

10

Page 11

2.3 Development Kits Inventory Checklists

Development Kits Inventory Checklists

This section descripts major hardware items which should be available on this development

kits.

Development Kits Hardware Items

1x 4-Layer Micro-ATX form factor (targeted dimensions: 10.5” x 10.4”) motherboard

1x Intel® CoreTM 2 Duo E8400 Processors in the LGA775 Socket

2x 1 GBytes DDR3 800 DIMM

1x ATX Heatsink with fan

1x CD-ROM contain chipset drivers (this include Intel® GMA4500 driver)

Development Kits board Specification

1 PCI Express x16, 3 PCIe x1, 3 PCI expansion slots

1394a

o 1 front panel headers for support of 1 port

o 1 back panel port

Universal Serial Bus 2.0

o 3 front panel headers for support of 6 ports

o 6 back panel ports

6 SATA 3 Gb/sec ports

• Internal I/O headers

2x5 Front Panel I/O header

2x5 Front Panel audio header

1x2 Chassis intrusion header

3 four-wire fan headers

2x8 High Definition audio header

• Additional Features

5 Analog audio connectors and 1 high definition media interface (HDMI)

Piezo speaker for BIOS POST codes

BIOS configuration jumper

Clear CMOS jumper

Power Button

Reset Button

XDP connector

11

Page 12

2.4 Processor Support

Intel® Q45 Development Kits support the following processors in the LGA775 Socket with FSB

of 800/1067/1333 MHz. Processors listed here has long-life support and also supported by this

development kits.

• Intel® CoreTM 2 Duo E8400 Series

• Intel® CoreTM 2 Duo E6400 Series

• Intel® CoreTM 2 Duo E4300 Series

• Intel® Celeron 440

Refer to this link for other processors which is also supported by Intel® Q45 Express Chipset.

http://developer.intel.com/products/chipsets/Q35_Q33/index.htm

2.5 System Memory

The Intel® Q45 MCH supports two types of memory organization. These are interleaved mode

and asymmetric mode. Listed here are the summary of the system memory supported.

• Non-ECC DDR3 (800/1066)

• 512Mb, 1Gb and 2Gb technology

• 4 DIMMs, 8GB maximum per channel, 16GB total memory

• Dual channel (Interleaved) mode. This mode offers the highest throughput for real world

applications. Dual channel mode is enabled when the installed memory capacities of both

DIMM channels are equal. Technology and device width can vary from one channel to the

other but the installed memory capacity for each channel must be equal. If different speed

DIMMs is used between channels, the slowest memory timing will be used.

• Single channel (Asymmetric) mode. This mode is equivalent to single channel bandwidth

operation for real world applications. This mode is used when only a single DIMM is

installed or the memory capacities are unequal. Technology and device width can vary

from one channel to the other. If different speed DIMMs is used between channels, the

slowest memory timing will be used.

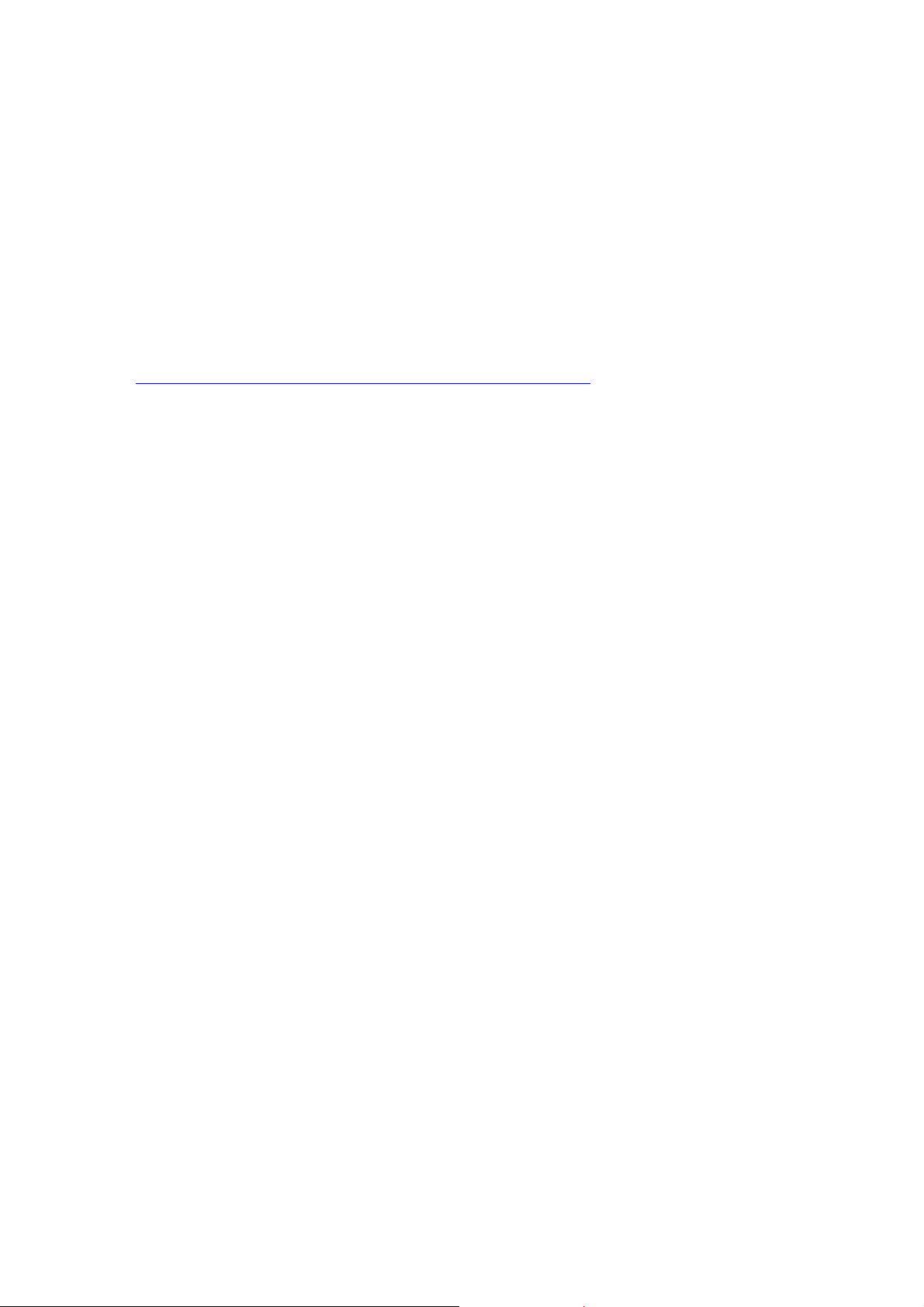

Figure 2-3 illustrates the memory channel and DIMM configuration.

12

Page 13

Channel A DIMM 0

Channel A DIMM 1

Channel B DIMM 0

Channel B DIMM 1

Figure 2-3 Memory Channel and DIMM Configuration

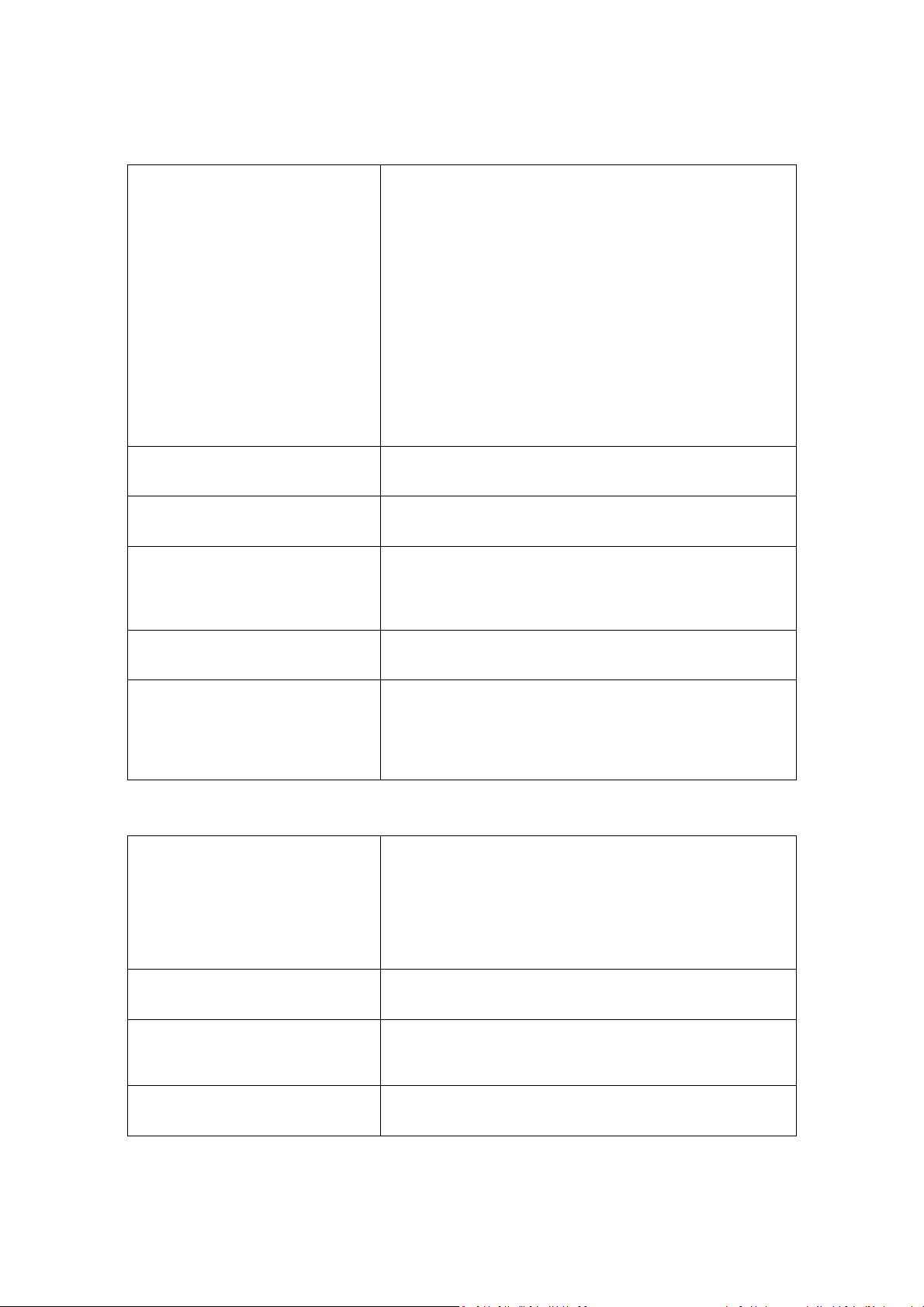

2.5.1 Dual Channel (Interleaved) Mode Configurations

Figure 2-4 shows a dual channel configuration using two DIMMs. In this example, the DIMM 0

sockets of both channels are populated with identical DIMMs.

Figure 2-4: Dual Channel (Interleaved) Mode Configuration with 2x DIMMs

13

Page 14

Figure 2-5 shows a dual channel configuration using 3 DIMMs. In this example, the combined

capacity of the two DIMMs in Channel A equal the capacity of the single DIMM in the DIMM 0

socket of Channel B.

Figure 2-5: Dual Channel (Interleaved) Mode Configuration with 3x DIMMs

Figure 2-6 shows a dual channel configuration using 4 DIMMs. In this example, the combined

capacity of the 2x DIMMs in Channel A equals the combined capacity of the 2x DIMMs in

Channel B. Also, the DIMMs are matched between DIMM 0 and DIMM 1 of both channels.

Figure 2-6: Dual Channel (Interleaved) Mode Configuration with 4x DIMMs

14

Page 15

2.5.2 Single Channel (Asymmetric) Mode Configurations

Figure 2.7 shows a single channel configuration using 1x DIMM. In this example, only the

DIMM 0 socket of Channel A is populated. Channel B is not populated.

Figure 2.7: Single Channel (Asymmetric) Mode Configuration with 1x DIMM

Figure 2.8 shows a single channel configuration using 3x DIMMs. In this example, the

combined capacity of the 2x DIMMs in Channel A does not equal the capacity of the single

DIMM in the DIMM 0 socket of Channel B.

Figure 2.8: Single Channel (Asymmetric) Mode Configuration with 3x DIMMs

15

Page 16

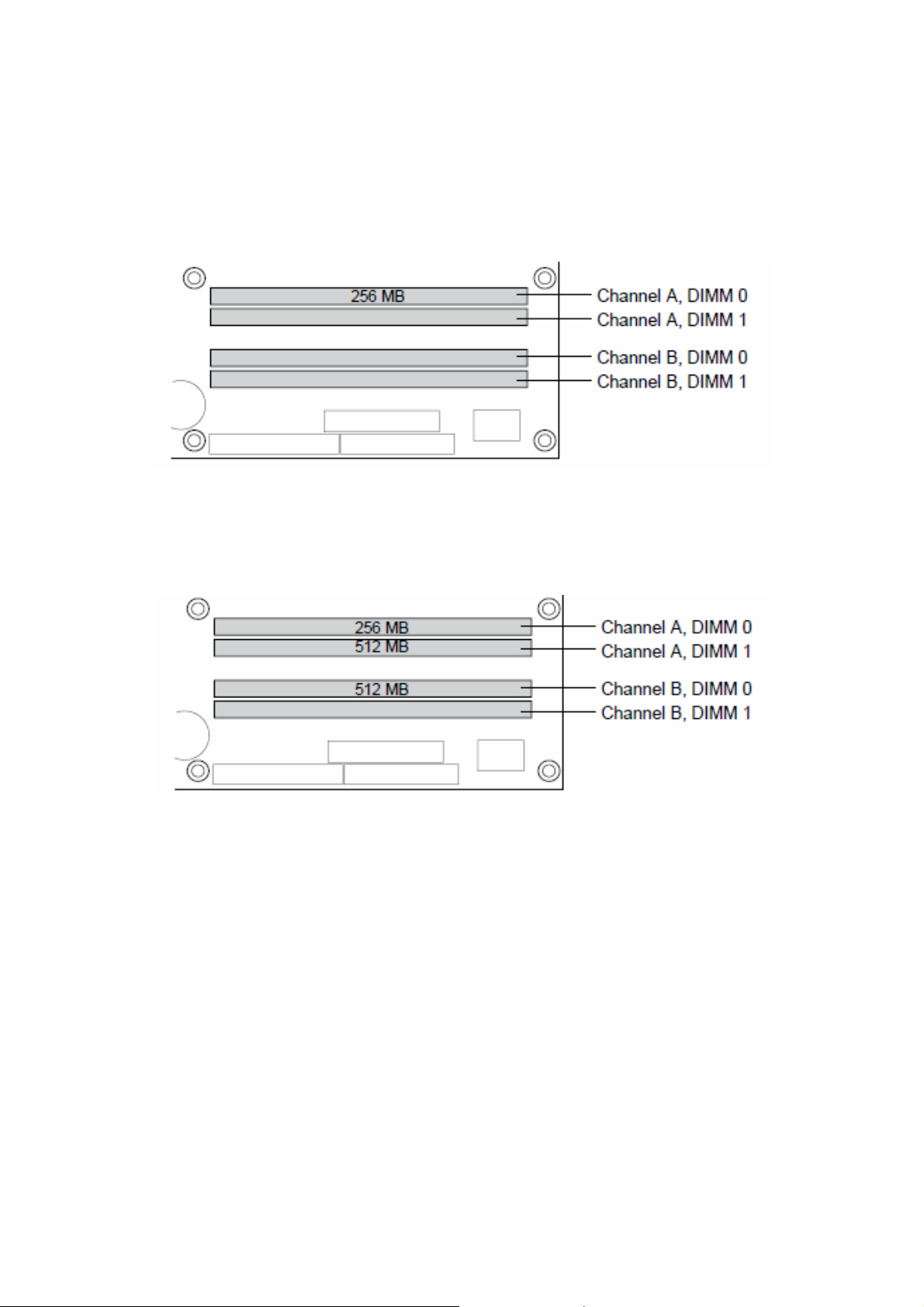

Port

Mic In Jack

HDMI Port

SPIF Port

2.6 Back-Panel Connectors

Figure 2-9 show back-panel connectors for the development kits.

1394a port

USB Port

VGA Analog

Display

RJ-45 LAN

Speaker Out

Center/Subw

oofer

Speaker Out

Rear

Line

In

Jack

Line

Out

Jack

2.6.1 Audio-Connectors

This development kits board support up to 5.1-channel audio configuration. It’s backward

compatible with 5.1, 2.1 and high definition media interface audio/video configuration as well.

Line In Jack (Light Blue)

This audio jack is used to for line in devices. It’s used in some optical devices and much more.

Line Out Jack (Light Green)

This audio jack is used for line out devices. It’s used in 2.1, 5.1 and 7.1 channel- audio

configuration. It can be used for headphone and stereo speaker as well.

Mic In Jack (Pink)

This audio jack is use for microphone input.

Center/Subwoofer Speaker Out Jack (Orange)

This audio jack is used to connect to center/subwoofer speakers in a 5.1 and 7.1-channel

audio configuration. Left it no connects if other than 5.1 and 7.1-channel audio configuration is

used.

Rear Speaker Out (Black)

This audio jack is used to connect to rear speakers in a 5.1 and 7.1-channel audio

configuration.

16

Page 17

2.6.2 RJ-45 LAN Connector with Integrated LEDs

Two LEDs are built into the RJ-45 LAN connector (as shown in Figure 2-10). Table 2-1

describes the LED states when the board is powered up and the Gigabit LAN subsystem is

operating.

Figure 2-10: LAN Connector LED locations

LED Color LED State Condition

Left

Right

Green

N/A Off 10 Mbits/sec data rate is selected

Green On 100 Mbits/sec data rate is selected

Yellow On 1000 Mbits/sec data rate is selected

Off LAN link is not established.

On LAN link is established.

Blinking LAN activity is occurring.

Table 2-1: LAN Connector LED status

2.6.3 USB Port

The USB port supports the USB 1.1/2.0 specification.

2.6.4 HDMI Port

This connector provides digital audio input and output from external audio system that

supports digital audio data. Please ensure that the audio system provides a HDMI connector.

17

Page 18

2.7 Debug Features

2.7.1. Extended Debug Probe (XDP)

The reference board provides a JTAG-compliant test access port (TAP) for attachment of an

XDP

connector. The XDP connector and associated circuitry enable the use of the ITP for the

particular processor to interrupt the boot sequence and view processor status.

The XDP connector is located on the backside of the board at location J2BC. Refer to figure 211 to the XDP connector location. Take notes that ITP-XDP SSA connector is needed. Refer to

diagram below for the ITP-XDP SSA connector.

Figure 2-11 ITP-XDP Connector location (J2BC)

ITP-XDP

ITP-XDP SSA Connector

is needed in order to

connect to

ITP-XDP2/3 tools

18

Page 19

2.7.2 Power LEDs

Power LEDs on the board indicate when standby power is being applied to the standby planes.

When lit they indicate that no DIMM modules should be inserted or removed. To install or

replace DIMM modules insure that AC power to the power supply is removed by unplugging the

AC power cord from the power supply or placing the switch on the power supply to the open

position. Caution: Removing DIMM modules when the standby power LEDs is lit could result in

damage to the memory devices on those modules.

2.7.3 Port 80 POST Code LEDs

Two LEDs display the POST codes output from Port 80 to indicate the progress of the boot

sequence or display the POST code of the last operation successfully completed during the boot

sequence. Please refer to Chapter 3.4 for more information on Port 80 code reference.

2.7.4 Voltage Reference

See Table 2-2 for details of the expected voltage levels for each voltage rail on the CRB.

Table 2-2 Voltage Reference detail

Voltage Rail Expected Voltage Voltage Rail Expected Voltage

VCC 5.0 V_1P1_CORE 1.1

VCC3 3.3 V_1P1_CL_MCH 1.1

+12V 12 V_1P1_PCIEXPRESS 1.1

-12V -12 V_SM 1.5

V_5P0_STBY\G 5.0 V_SM_VTT 0.75

V_3P3_STBY\G 3.3 V_1P1_CL 1.1

V_1P5_ICH 1.5 V_3P3_PCIVAUX 3.3

VCC_DMI 1.1 VDD_CLK 3.3

V_FSB_VTT 1.1 VCC_CPU_IO 1.1

VCCP 1.15-1.50

19

Page 20

J115LB

J7LB

J4LB/J10LB

J15LB

J6LB

J16LB

J14LB

2.8 Development Kit’s Major Connector & Jumper

Figure 2-12 shows major jumpers and headers use on the development kits.

Figure 2-12 Major jumpers and headers location on the development kits.

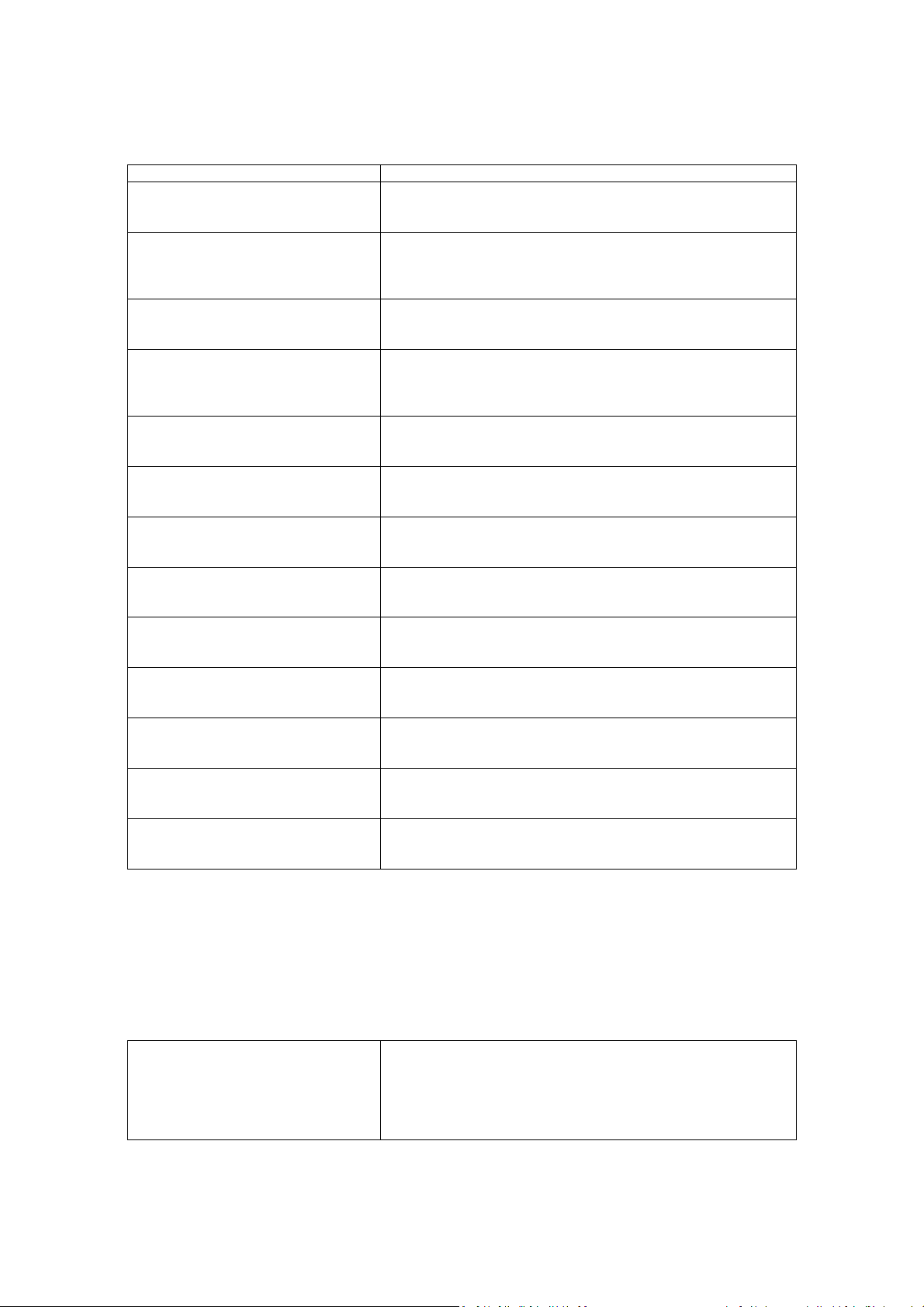

2.8.1 Jumper Functions

Table 2-3 provides a list of the setting definitions Eaglelake CRB.

Table 2-3 Eaglelake CRB Board Jumpers Description

Jumper Description Default Position

J6LB

J115LB

J7LB

J4LB/J10LB

Clear CMOS

(1-2: Normal, 2-3: Clear CMOS)

RTC Reset

(1-2: Normal, 2-3: Clear)

Config /Recovery

(1-2: Normal, 2-3: Configure, jumper removed –

recovery)

Manufacturing mode

(enable if jumper plug-in)

1-2

1-2

1-2

Empty

20

Page 21

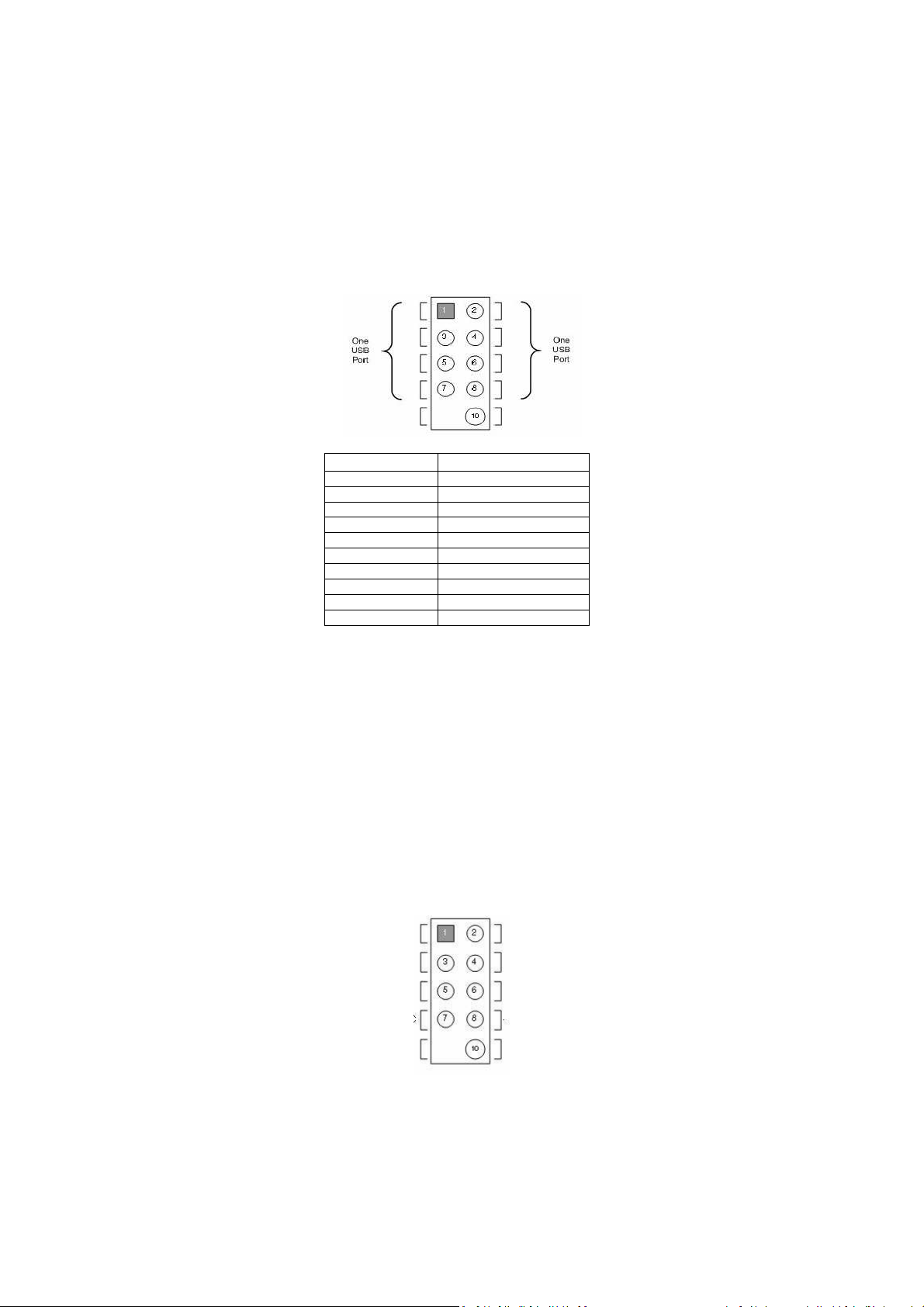

2.8.2 USB 2.0 Front Panel

There are 4 USB 2.0 Front Panel can be found in the development kits board. Front panel

USB header thermistor protection is required. USB front panel is label as J14LB, J15LB,

J16LB and J1FW on the boards. Refer to figure 2-12 for header location of U14LB, U15LB

and U16LB. Refer to Figure 2-13 for U1FW.

Pin Number Definition

1 5V

2 5V

3 USB Dx4 USB Dy5 USB Dx+

6 USB Dy+

7 GND

8 GND

9 No pin

10 No connect

Table 2-4 USB Front Panel

2.8.3 1394a Header

1394a solution on the PCIe bus. Single 1394a port on the back panel; refer to

figure 2.9 for the back panel 1394a locations. There’s another header supporting

1394a port, which is shown in figure 2-13. Front panel 1394a header thermistor

protection required. The IEEE 1394a connectors are colored blue. The +12 V

DC power on the IEEE 1394a connectors is fused. Each IEEE 1394a connector

provides one IEEE 1394a port.

21

Page 22

Pin Number Definition

1 TP A+

2 TP A3 Ground

4 Ground

5 TP B+

6 TP B7 +12V DC

8 +12V DC

9 No Pin

10 Ground

Table 2-5 1394a Header

USB front

panel

Figure 2-13 Location for 1394a Header and USB front panel.

J24LB

1394a

Header

22

Page 23

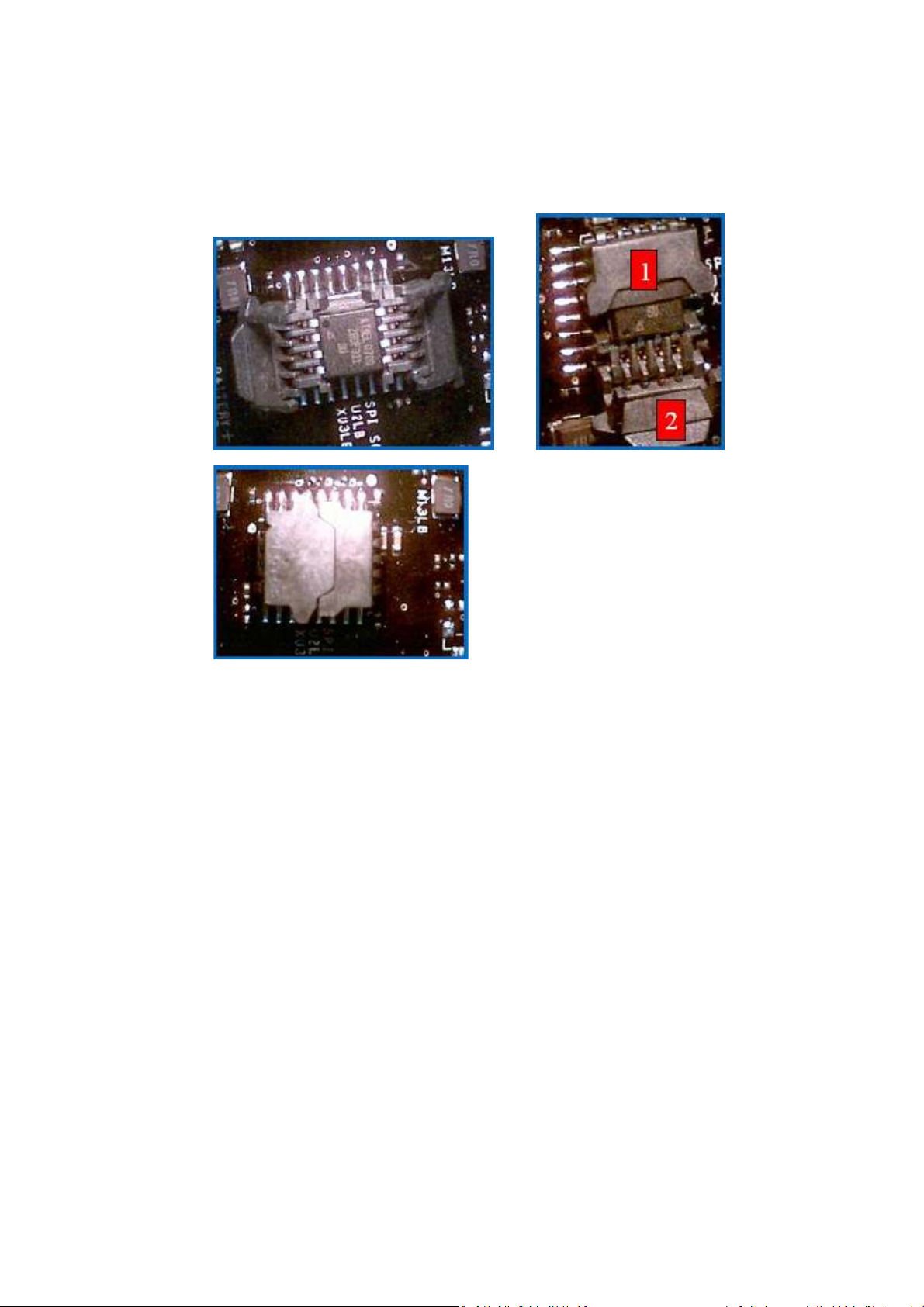

2.9 SPI Removal / Installation Technique

When removing or installing the SPI device care must be taken to avoid damage to the SPI

socket. The cap is constructed of plastic and can easily be damaged.

2.9.1 SPI Device Installation

Suggested tooling to use for install and removal other basic FA equipment may be needed but

not necessary.

Figure 2-14 : Pick and tweezer

i. Door identified prior to install or removal of SPI device

Figure 2-15 : Door 1 and 2

ii. As shown door must be opened in order to avoid damage to the socket. Door 1 is

identified by the lip as pointed out. Using pick, gently push up from under the lip to

open door 1.

Figure 2-16 : Opening door 1

23

Page 24

iii. Follow the same steps as opening door 1 for door 2

Figure 2-17 : Opening door 2

iv. With socket doors open, SPI device can be installed.

Align SPI device with guide slots. No pressure need be applied.

Note: early versions of the Lotes socket does not account for pin 1 orientation on

the socket

Figure 2-18 : Installing SPI device

24

Page 25

v. Gently close each socket door in reverse order until socket doors are close.

Note : Pressure will be applied with the socket doors closed to ensure contact

Between socket and SOIC 8 component.

Figure 2-19 : Closing door 1 and 2

25

Page 26

2.9.2 SPI Device Removal

Follow same steps to get doors open. Using tweezers gently remove SPI device from socket.

Gently close socket doors if not in use to avoid any damage to socket doors.

Figure 2-20 : Removing SPI device

26

Page 27

3.0 Setting Up and Configuring the Development Kits

This chapter identifies the evaluation kit basic board’s set up and operation. Please refer to

chapter 2 for the board layout, jumper setting location and the component reference

designator.

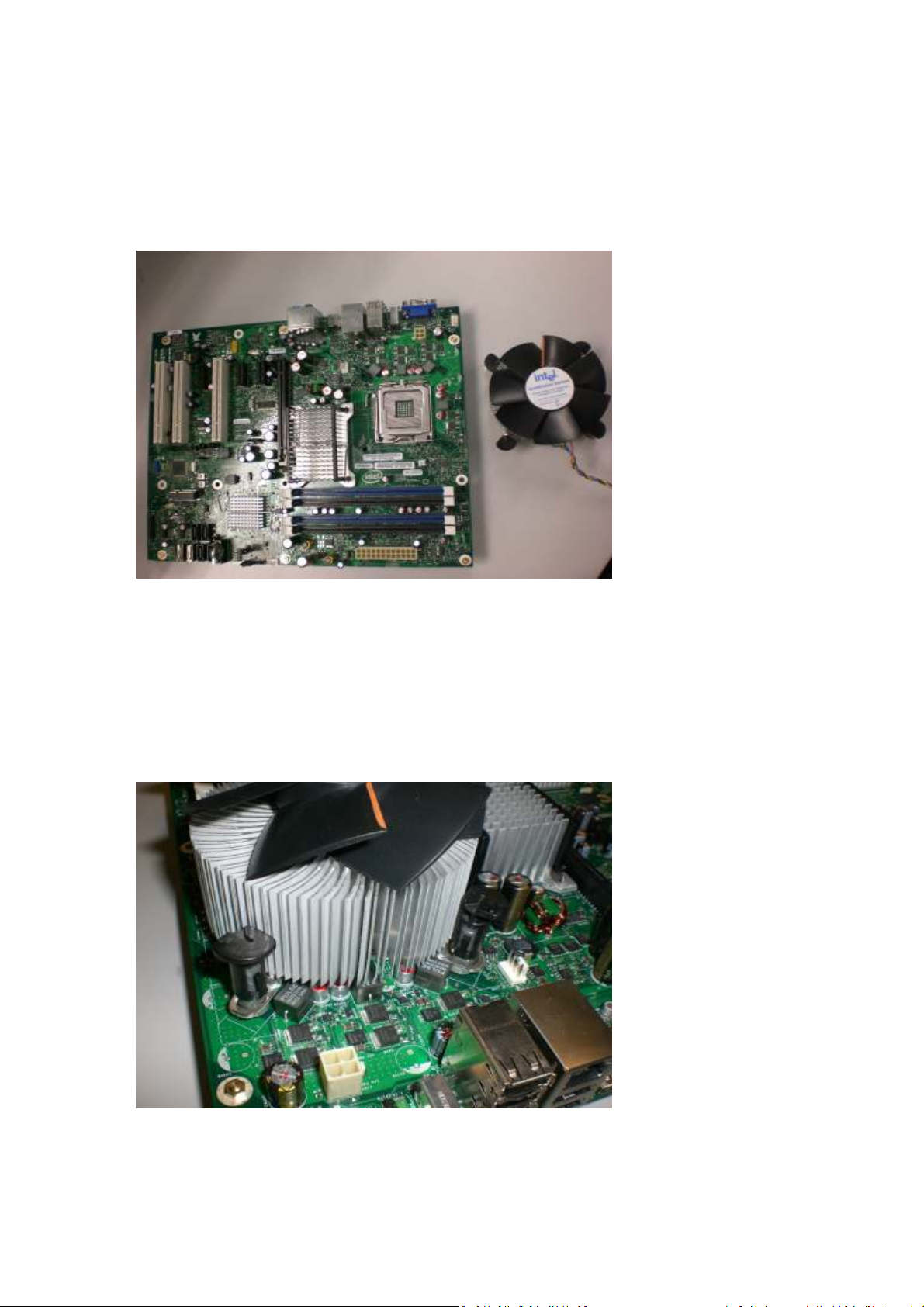

3.1 Overview

Figure 3-1 Intel® Q45 Development Kits

27

Page 28

3.2 ATX Heatsink Setup

Depending on the ATX casing that user use, this guide only provides guides for install the ATX

heatsink. Refer to Figure 3-2 for the heatsink figure.

Figure 3-2 : Eagle Lake Q45 platform and the ATX heatsink

3.2.1 ATX heatsink alignment on the Eagle lake Q45 platform

Attach the ATX Heatsink over the processor to the Eagle Lake Q45 platform by following

procedures described below.

Step 1: Place the ATX Heatsink on the Eagle Lake Q45 board so that the hole on the board line

up with the corresponding ATX Heatsink location. The board and the ATX heatsink

should look like figure 3-3.

Figure 3-3 : ATX Heatsink alignment on the Eagle Lake Q45 board

28

Page 29

Step 2: Press the ATX Heatsink pin toward the hole on the board until “tick” sound can be

4-pin CPU Fan power

hear. Remember to hold the board while pressing the pin. Refer to figure 3-4

Figure 3-4 Pressing the ATX Heatsink while holding the board

3.3 Board Setup and Configuration before Boot

Follow the steps below to operate the reference board. Start at step 1 with the power supply

not connected to the board.

1. Physically inspect the motherboard for obvious defects. Note that each reference board has

been tested prior to distribution; however, a visual check should be performed to ensure no

damage has occurred in shipping.

2. Set jumpers to default positions. Refer to table 2-3 for default position.

3. Install the processor and ensure the 4-pin CPU fan power connector is installed on header

shown below:

Figure 3-5 CPU Fan location

29

Page 30

4. Install DDR3 DIMM in Channel A Slot 0 connector. DIMMs should never be inserted or

Power

-

on Button

removed unless the power supply is disconnected from the AC power source. Refer to Chapter

2.5 for system memory configuration.

5. Connect SATA hard drive, USB keyboard, USB mouse, and VGA monitor (video card is

optional).

6. Connect an 2x12 Standard power supply and 2x2 also. Refer to figure 3-3 for the location.

2x2 Standard

power supply

2x12 Standard

power supply

Figure 3-6 2x12 Standard power supply and 2x2 power supply

7. Press the power button. Refer to figure 3-6 or 2-1 for power-on button location.

30

Page 31

3.4. Post Codes Definitions

The CRB BIOS writes progress and error codes to Port 80 during POST. These codes are

defined below.

3.4.1. Normal Post Codes

Boot block Initialization Code Checkpoints

Post Code Description

Before D0h Verify that CMOS is valid. Interrupts are disabled.

D0h Go to flat mode with 4GB limit and GA20 enabled. Performs early chipset

initialization.

D1h Initializes SIO devices. Programs the KBC command byte. Loads Ucode.

Checks if waking from power management suspend state. Saves power-on

CPUID value in scratch CMOS.

D2h Verify Boot Block checksum.

D3h Prepare memory for detection and sizing and jump to memory initialization

code.

A0h Sets default values used in memory initialization.

A1h Calculates system bus frequency.

A2h Enable MMIO space behind BAR and set base address for memory BAR.

Read and store SPD data for later for all DIMMs present.

A3h Set bus ratio.

A4h Get column latency.

A5h Check rTAS, tRP, tRCD, and refresh timings.

A6h Verify that DIMMS are populated from farthest to closest slot away from

MCH.

A7h Jump to SDRAM program.

A8h Save DIMM layout in CMOS.

7Ah Handles DDR2 dual rank special case. Enable clocks used by DIMMs.

A9h Program DRAMISCTRL, SDRC, DDRCSR

B9h Program DRM.

AAh Translate logical DIMM number to physical DIMM number.

B1h Calculate size variable (contains row, column and bank).

B2h Get MCH row memory size and attribute.

ABh Program the DRAs and DRBs.

ACh Perform Jedec sequence on each row.

ADh Make call to program DRT register.

B3h Program MCH timings in DRT register.

B4h Program ODT mode for DDR2 DIMMs.

90h Check for S3 resume.

91h Enable cache for data storage to be used with receive enable and DQS

calibration.

92h Copies data to Cache As Ram (CAR).

93h Call receives enable calibration function.

B6h Performs receive enable calibration.

94h Just before call to perform DQS calibration.

B7h Performs the DQS calibration variable initialization.

70h Determine which rows are populated according to the DRBs.

71h Step 1 of DQS calibration.

72h Step 5 of DQS calibration.

73h Step 6 of DQS calibration.

31

Page 32

74h End of DQS calibration.

9Fh Set Top Of Memory register

B9h Program MCH for particular refresh mode.

BAh Perform memory test.

B2h Program ECC mode.

AEh Set the DDRCSR register.

BCh Enable memory scrubbing.

B3h Initializes other recommended MCH settings.

BDh Program the IC complete bit.

AFh Save S3 data, start the refresh signal, and perform SB early initialization.

D4h Test base 512K memory. Adjust policies and cache first 8MB. Set stack.

D5h Boot block code is copied from ROM to lower system memory and control is

given to it. BIOS now executes out of RAM. Initialize DMA and interrupt

controller. Form ROM image. Check BIOS checksum.

D6h Control is in segment 0. If either <Ctrl> <Home> was pressed, the BIOS

checksum is bad, or the recovery bit is set in CMOS, next will go to

checkpoint code E0h. Otherwise, going to checkpoint code D7h.

D7h Restore CPUID value back into register. The Boot block-Runtime interface

module is moved to system memory and control is given to it. Determine

whether to execute serial flash.

D8h The runtime module is uncompressed into memory. CPUID information is

stored in memory.

D9h Store uncompressed pointer for future use in PMM. Copy Main BIOS into

memory. Leaves all RAM below 1MB read-write including E000 and F000

shadow areas but closing SMRAM.

DAh Passing control to the main system BIOS in shadow RAM next. Initialize the

interrupt vectors.

Boot Block Recovery Code Check Points

Post Code Description

E0h The onboard floppy controller if available is initialized. Next, beginning the

base 512 KB memory test.

E9h Look for floppy drive and read the new rom image from it.

EAh Enable ATAPI hardware. Attempt to red from ARMD and ATAPI CDROM.

EBh Disable ATAPI hardware. Jump back to checkpoint E9h.

D7h Recovery code not present.

EFh A read error occurred on media. Jump back to checkpoint EBh.

F0h Search for pre-defined recovery file name in root directory.

F1h Recovery file not found.

F2h Start reading FAT table and analyze FAT to find the clusters occupied by the

recovery file.

F3h Start reading the recovery file cluster by cluster.

F5h Disable L1 cache.

FAh Check the validity of the recovery file configuration to the current

configuration of the flash part.

FBh Make flash write enabled through chipset and OEM specific method. Detect

proper flash part. Verify that the found flash part size equals the recovery

file size.

F4h The recovery file size does not equal the found flash part size.

FCh Erase the flash part.

FDh Program the flash part.

FFh The flash has been updated successfully. Make flash write disabled. Disable

ATAPI hardware. Restore CPUID value back into register. Give control to

F000 ROM at F000:FFF0h.

32

Page 33

Runtime POST code checkpoints

Post Code Description

03h The NMI is disabled. Next, checking for a soft reset or a power on condition.

04h Performs CMOS reliability checks and initialization. Initialize PICs.

05h Enable interrupts.

06h Initializes the 8254 timer and enables IRQ0. Installs an interrupt at the 1Ch

vector.

07h Initialize the data area.

08h Initialize the CPU.

C0h Early CPU Init Start – Disable Cache – Init Local APIC.

C1h Set up boot strap processor information.

C2h Set up boot strap processor for POST.

C3h Setup CPU information.

C4h Program all application processors to lowest frequency.

C5h Enumerate and set up application processors.

C6h Re-enable cache for boot strap processor.

C7h Run the BAT test on the keyboard controller. Auto detects the keyboard and

mouse ports. Enable keyboard and mouse interface.

0Ah Initializes the 8042 compatible keyboard controller.

0Bh Detect the presence of a PS2 mouse.

0Ch Detect the presence of a PS2 keyboard.

0Eh Set the IRQ1 vector in INT09h. Write CNvram to CMOS.

13h Early POST initialization of chipset registers. Size and test external cache.

20h Validates GPNV area and initializes with defaults if GPNV not found. Handles

un-compression and initialization of all language modules. Uncompress BIOS

logo and silent logo modules.

24h Add IO to motherboard resources.

2Ah Initializes different devices through DIM. Initialize different buses and

perform the following functions: Reset, Detect, and Disable (disables all

device nodes, PCI devices and PnP ISA cards. Assigns PCI bus numbers);

Static Device Initialization (initializes all static devices that include manual

configured onboard peripherals, memory and I/O decode windows in PCI-PCI

bridges and non-compliant PCI devices); Boot Output Device Initialization

(searches for and initializes any PnP, PCI, or AGP video devices).

FFh Detect and update BDA for all available serial ports in the system.

2Ch Initializes different devices. Detects and initializes the video adapter

installed in the system.

2Eh Initializes all output devices.

31h Allocate memory for ADM module and uncompress it. Give control to ADM

Module for initialization. Initialize language and font modules for ADM.

Activate ADM module.

33h Initializes the silent boot module. Set the window for displaying text

information.

37h Display sign-on message, CPU information, setup key message, and any

OEM specific information.

38h Initializes different devices through DIM. Initialize different buses and

perform the following functions: Boot Input Device Initialization (searches

for and configures PCI input devices and detects if system has standard

keyboard controller); IPL Device Initialization (searches for and configures all

PnP and PCI boot devices); General Device Initialization (configures all

onboard peripherals that are set to an automatic configuration and

configures all remaining PnP and PCI devices).

39h Initializes DMAC-1 and DMAC-2.

3Ah Initialize RTC date / time. Test for total memory installed in the system.

33

Page 34

Check for DEL or ESC keys to limit memory test and display the total

memory.

3Ch Mid POST initialization of chipset registers.

40h Detect different devices (parallel ports, serial ports, and coprocessor in CPU,

… etc.) successfully installed in the system and update the BDA, EBDA… etc.

FFh Detect serial ports.

50h Programming the memory hole or any kind of implementation that needs an

adjustment in system RAM size if needed.

52h Updates CMOS memory size from memory found in memory test. Allocates

memory for Extended BIOS Data Area from base memory.

60h Initializes NUM-LOCK status and programs the KBD typematic rate.

75h Initialize Int 13 and prepare for IPL detection.

78h Initialize IPL devices controlled by BIOS and option ROMs.

7Ch Generate and write contents of ESCD in NVRAM.

84h Log errors encountered during POST.

85h Display errors to the user and gets the user response for error.

87h Execute BIOS setup if needed / requested.

8Ch Late POST initialization of chipset registers.

8Dh Build ACPI tables (if ACPI is supported).

8Eh Program the peripheral parameters. Enable / disable NMI as selected.

8Fh Generate final ESCD data. Initialize WDT.

90h Late POST initialization of system management interrupt.

99h Invalid instruction ISR

A1h Clean up work needed before booting OS.

A2h Takes care of runtime image preparation for different BIOS modules. Fills

the free area in F000h segment with FFh. Initializes the Microsoft IRQ

routing table. Prepares the runtime module language. Disables the system

configuration display if needed.

A4h Initialize runtime language module.

A7h Displays the system configuration screen if enabled. Initialize the CPU’s

before boot, which includes the MTRRs.

A9h Wait for user input at config display if needed.

AAh Uninstalls POST INT1Ch and INT09h vectors.

ABh Prepare BBS for Int 19 boot.

ACh End of POST initialization of chipset registers. De-initializes the ADM module.

00h Passes control to OS loader (typically INT19h).

34

Page 35

4.0 BIOS SETUP UTILITY

4.1 Main

4.1.1 System overview

AMIBIOS

• Version : 08.00.15

• Build date : 04/22/08

• ID : CGELIA38

These three items only show the respective current

statuses. They cannot be changed in the BIOS setup

Processor

• Type : Intel® Core™ 2 CPU

• Speed : 1800 MHz

• CPU Cores : 2

• Total CPUs : 2

System Memory

• Size : 989 MB

System Time

System Date

4.2 Advance

4.2.1 CPU Configuration

Ratio CMOS setting

C1E Support

Hardware Prefetcher

Adjacent Cache Line Prefetch

Max CPUID Valve Unit

This section showed the Processor that being used.

Note: It should be difference when difference

processor was installed on the board.

This section showed the RAM capacity that being

install on the platform

Note: difference memory size will be shown

depending on the RAM size that being

installed.

Shows the time of the day in format hh:mm:ss

Shows the date of the day in format mm:dd:yy

Set the ratio between CPU Core Clock and the FSB

frequency

This should be enable in order to enable or disable the “

Enhance Half State “

This should be enable in order to enable or disable the “

Hardware Prefetcher Disable Feature”

This should be enable in order to enable or disable the “

Adjacent Cache Line Prefetch Disable Feature”

Disable for Window XP

35

Page 36

Execute Disable Bit Capability

SMRR

PECI

Core Multi-Processing

Intel® Speedstep™ Technology

4.2.2 IDE Configuration

SATA#1 configuration

• Configure SATA#1

- IDE

- RAID

- AHCI

Primary IDE Master

Primary IDE Slave

Secondary IDE Master

When disable, force the XD feature flag to always return

0

Enable or disable SMRR feature

Note : Only affects CPU SMRR feature

When enable, enables PECI Interface.

With the interface, user can control the fan speed.

When disable, disable one execution of each CPU die

Disable : Disable GV3

Enable : Enable GV3

Select the status of the SATA#1

RAID — which stands for Redundant Array of Inexpensive

Drives (as named by the inventor) or Redundant Array of

Independent Disks (a name which later developed within

the computing industry) — is a technology that employs

the simultaneous use of two or more hard disk drives to

achieve greater levels of performance, reliability, and/or

larger data volume sizes.

AHCI- a hardware mechanism that allows software to

communicate with Serial ATA (SATA) devices (such as

host bus adapters) that are designed to offer features not

offered by Parallel ATA (PATA) controllers, such as hotplugging and native command queuing. The specification

details a system memory structure for computer

hardware vendors in order to transfer data between

system memory and the device.

While entering setup, BIOS auto detects the presence of

IDE device

Display the status

While entering setup, BIOS auto detects the presence of

IDE device

Display the status

While entering setup, BIOS auto detects the presence of

IDE device

Display the status

36

Page 37

Secondary IDE Slave

Third IDE Master

Fourth IDE Master

IDE detect timeout

4.2.3 Floppy Configuration

Floppy A

Floppy B

4.2.4 ACPI Configuration

ACPI Aware OS

General ACPI configuration

- Suspend mode

- Repost Video on S3

resume

While entering setup, BIOS auto detects the presence of

IDE device

Display the status

While entering setup, BIOS auto detects the presence of

IDE device

Display the status

While entering setup, BIOS auto detects the presence of

IDE device

Display the status

Select the time for detecting ATA/ATAPI devices

Note : AT Attachment with Packet Interface (ATA/ATAPI)

is a standard interface for connecting storage

devices such as hard disks, solid state disks and

CD-ROM drives inside personal computers

Select the type of the floppy drive connected to the

system

Select the type of the floppy drive connected to the

system

Enable or disable ACPI support for operating system

Enable : if OS supports ACPI

Disable : if OS does not support ACPI

Note : Advanced Configuration and Power Interface

(ACPI) specification, an open industry standard

first released in December 1996 (developed by HP,

Intel, Microsoft, Phoenix, and Toshiba) defines

common interfaces for hardware recognition,

motherboard and device configuration and power

management.

Select the ACPI state used for system suspend

S3(STR) : suspending to DRAM if the system support this

mode

S1(POS) : power on under ACPI mode

Determines whether to invoke VGA BIOS post on S3/STR

resume

37

Page 38

Advance ACPI configuration

Chipset ACPI configuration

- USB Device wakeup from

S3/S4

Section to configure additional ACPI option

Enable or disable USB device makeup from S3/S4

4.2.5 AHCI Configuration

AHCI Port 0-5

- SATA Port 0-5

- Port type [internal/external]

- Port Hot Plug capability

- S.M.A.R.T.

Staggered Spin Up

SATA Link Power Management

Select the type of device connected to the system

Enable port for eSATA support.

Enable the hot plug capable bit in the PXC register for this

support.

Self Monitoring, Analysis and reporting Technology

Note : monitoring system for computer hard disks to

Enable : The BIOS will clear the staggered speed up

supported bit in the AHCI generic has capabilities

register.

Enable aggressive management and slumber and partial

(AIPE&ASP) on all port

4.2.6 Intel AMT configuration

Intel AMT support

Force IDER

Activate Healing Process

Enable or disable

Note : Active Management Technology (AMT) is a

Disable or

Enable or disable

detect and report on various indicators of

reliability, in the hope of anticipating failures.

hardware-based technology that facilitates remote

out-of-band management of computers by use of a

small secondary processor located on the

motherboard.

i. IDER primary master

ii. IDER primary slave

iii. IDER secondary master

iv. IDER secondary slave

38

Page 39

Activate Healing Time Out

Ctrl-P Delay

MEBX Debug

How many second selected for activate healing time out

Auto or disable

Enable or disable

4.2.7 MPS Configuration

Configure the multi-processor table

4.2.8 SMBIOS Configuration

SMBIOS Configuration

System Management BIOS (SMBIOS) is a specification to

lay out data structures (and access methods) in BIOS

which allows a user or application to store and retrieve

information specifically about the PC in question.

4.2.9 Remote Access Configuration

Remote Access Select Remote Access type

Note: Remote access is the ability to get access to a

computer or a network from a remote distance.

4.2.10 Trusted Computing

TCG/TPM support

Enable or disable TCG( TPM 1.1/1.2) support in the BIOS

Note : Configure setting related to trusted computing

innovative. A Trusted Platform Module offers

facilities for the secure generation of cryptographic

keys, and limitation of their use, in addition to a

hardware pseudo-random number generator.

4.2.11 USB Configuration

Legacy USB support

Enables or disable support for USB legacy

i. enabled

39

Page 40

ii. disabled

iii. auto

Note : Auto option disables the legacy support if no USB

4.3 PCIPnP

PCI Latency timer

Value in units of PCI Clocks for PCI device latency timer

register

Note : Latency is a time delay between the moment

4.4 Boot

4.4.1 Boot setting configuration

Configure setting during system boot.

Quiet Boot

Boot-up Num-Lock

Wait for ‘F1’ if error

Disabled : displays normal POST massage

Enabled : displays OEM logo instead of POST

Massage

Select Power-On state for the Num-Lock

Allows user to toggle between On (default) or Off to

control the state of the NumLock keys when the system

boot.

Note: If On, the numeric keypad is in numeric mode. If

Wait for ‘F1’ key to be pressed if error have occur

Setting: Disable/Enable

4.5 Security

devices are connected.

something is initiated, and the moment one of its

effects begins or becomes detectable.

Off, the numeric keypad is in cursor control mode.

40

Page 41

The BIOS provides both a Supervisor and a User password. If wanted to use both password,

the Supervisor password must be set first.

Change Supervisor Password

Change User Password

Hard disk security

Install or change the password

Install or change the password

If hard disk detected, the hard disk can be safekeeping

4.6 Chipset

4.6.1 Northbridge Configuration

Integrated Graphics Option

i. IGD as the secondary

display

ii. Internal Graphic Mode

select

iii. GTT memory size

iv. Device 2, function 1

v. IGD BAR size

vi. IGD displays clock

vii. IGD sample clock

viii. IGD render clock

ix. PAVP

Initiate Graphic Adapter

Device 2 (IGD) Enable

Set the IGD as a secondary displays device

Note : when enabled, this sets MCH D0.F0.R:52h[1]=1

which changes the internal graphics device classcode to 0380h(non-VGA)

Select the amount of system memory used by the

internal graphic device

Select the amount of system memory used for Graphic

Transition Table (GTT).

Select the type of device 2, function 1

i. auto

ii. enabled

iii. disabled

select the IGD BAR size

set IGD displays clock speed

set IGD sample clock speed

set IGD render clock speed

protected Audio Video

Select which graphic controller to be use as the primary

boot device

Auto : IGD enabled/disable is based on the GFX card

detection and primary video device setup

option.

Disable : IGD is disabled regardless of card detection

And the primary video device option

41

Page 42

Memory Remap feature Enabled : allow remapping of the overlapped PCI

memory above the total physical memory

Disabled : do not allow remapping of memory

Flex Memory Mode

DRAM frequency

Configure DRAM time by SPD

Dynamic ODT

Write levelization

Memory hole

T2 Dispatch

Auto PCI MMIO Allocation

TSEG Allocation

Video function configuration

i. DVMT mode select

ii. DVMT/Fixed memory

iii. Boot displays device

iv. Flat panel type

v. Backlight control

support

vi. BIA Control

vii. TV standard

Enabled : Flex mode channels interleaved when

possible

Disabled : Non flex mode channels stacked

Select the DRAM frequency

Note : Setting auto, the DRAM frequency will auto

adjusted

Enable or disable

Power cycling is required after changing this option

Enabled or disabled write levelization ( DDR3 only )

Reserve place in the memory. Select the amount that to

be reserve.

Enable T2 dispatch for increase memory performance

Enabled or disabled the auto PCI MMIO Allocation

Note : MMIO stands for memory mapped input output

Select the type of TSEG allocation

i. disabled

ii. enabled, 1MB

iii. enabled, 2MB

iv. enabled, 8MB

Fixed or DVMT mode

Select the boot displays device

Select the flat panel type from type 1~type 9

Select the backlight control support

Select the BIA control support

Select the TV standard type

42

Page 43

viii. Spread spectrum

clock

VT-d

Enabled or disabled this feature

Note : Spread-spectrum techniques are methods by

VT-d support

Note : VT-d is a technology that enables guest virtual

4.6.2 Southbridge Configuration

Enable/disable ICH Internal

Devices

i. cUSB controller #1

enable

ii. cUSB controller #2

enable

iii. cUSB controller #3

enable

iv. cUSB controller #4

enable

v. cUSB controller #5

enable

vi. cUSB controller #6

enable

vii. cUSB controller #6

location

viii. eUSB controller #1

enable

ix. eUSB controller #2

enable

x. GbE controller

Disable device 29, function 0

UHCI USB controller #1

Disable device 29, function 1

UHCI USB controller #2

Disable device 29, function 2

UHCI USB controller #3

Disable device 26, function 0

UHCI USB controller #4

Disable device 26, function 1

UHCI USB controller #5

Disable device 26, function 2

Or disable device 29, function 3

Choose where cUSB6 respect to device 26 function 2 or

device 29 function 3

Note : Universal Host Controller Interface (UHCI) was

Disable device 26, function 7

EHCI USB controller #1

Disable device 29, function 7

EHCI USB controller #2

Note : Enhanced Host Controller Interface (EHCI) is a

The GbE controller should only be enabled if the SPI soft

straps in the descriptor enable the GbE

which energy generated in a particular bandwidth

is deliberately spread in the frequency domain,

resulting in a signal with a wider bandwidth. These

techniques are used for a variety of reasons,

including the establishment of secure

communications, increasing resistance to natural

interference and jamming, and to prevent

detection

machines to directly use peripheral devices,

primarily through DMA and interrupt remapping

created by Intel for USB 1.0 (full and low speeds

only).

high speed controller standard which is publicly

specified.

43

Page 44

xi. GbE LAN Boot

xii. HDA controller

xiii. Thermal sensor

Audio Codec Detection

Reserved page routed

W0L via GPIO9

External 1394 controller

HPET

Note : Gigabit Ethernet (GbE or 1 GigE) is a term

describing various technologies for transmitting

Ethernet frames at a rate of a gigabit per second,

as defined by the IEEE 802.3-2005 standard.

Enable or disable this feature

Enable or disable option for device 27, function 0

Note : Intel High Definition Audio (HD Audio or "Azalia")

refers to the specification released by Intel in 2004

for delivering high-definition audio that is capable

of playing back more channels at higher quality

than previous integrated audio codecs like AC97

Enable or hide option for device 31, function 6

Enable down codec

PCI or LPC selection option

Enabled : GP_LVL[9] set

Disabled : GP_LVL[9] clear

Note : used for wake on LAN

Disable or enable the external 1394 controller

Enable or disable the HPET feature

Note : The High Precision Event Timer (HPET, formerly

known as Multimedia Timer) is a hardware timer

used in computers

4.6.3 ME Subsystem Configuration

Boot Block HECI massage

HECI message

ME Alias check

MRC/ME Debug (NoTimeOut)

Enable or disable

Note : Host Embedded Controller Interface, abbreviated

as HECI, is a recent (introduced in 2006)

technology used for Active Management

Technology (AMT) in Intel chipsets that support

Core 2 Duo microprocessors.

Enable or disable

Enable or disable ME Alias in MRC

Note : ME is the manageability engine

MRC will wait forever for expected HECI message

Note : MRC is the memory reference code

44

Page 45

End of POST S5 HECI message

Delay entering MEBx

Unconfigure ME

1MB ME memory hole

ME_HECI

Fan speed monitor1

Fan speed monitor2

Fan speed monitor3

AFSC Configuration

AFSC SST Bus

AFSC sensor thresholds

AFSC manual fan control

AFSC chipset

Enable or disable

Select the delay time for entering MEBx

Note : MEBx is the Manageability Engine BIOS Extension

No or yes option for unconfigure Manageability Engine

Enable or disable the reserve 1 MB memory range from

0X1000000 to 0X1100000

Enable or disable

Enable or disable

Enable or disable

Enable or disable

Unlock or lock

Unlock or lock

Unlock or lock

Unlock or lock

Unlock or lock

4.6.4 PCI Express Configuration

Northbridge PCI Express

i. PEG port

Select the type of PEG port

i. auto

ii. disable

iii. enable

45

Page 46

ii. PEG Scramble Bypass

iii. PEG Retry Buffer

Depth

iv. PEG Force Link Width

v. PEG1 Force Link Width

vi. PEG Link disable

vii. PEG endpoint Active

State PM

viii. PEG ASPM RXL0s

ix. SERR# on Non-Fatal

error

x. SERR# on Fatal error

xi. Link Stability

Algorithm

Southbridge PCI Express

PCIE port0 – port5

VC1/TC map

GFX Card : BIOS forces the scrambles to

be bypassed without a link

disable

Enable : BIOS forces the scrambles to be

bypassed by disabling and

enabling the link

If forced, Retry buffer is Force to less than Optimal Value

Select the PEG force link width

i. Auto

ii. X1

iii. Reserve

iv. X4

v. X8

Select the PEG1 force link width

Enable or disable this feature

Enable : BIOS will disable the PEG link, Device 1 will

be visible

Force ASPM setting on PEG endpoint device. Does not

specify ASPM setting on the PEG link

Enable or disable

SERR# is generated if a non-fatal error is detected on the

PEG port

SERR# result in NMI or SMI depending upon state of NMI

to SMI setup option

SERR# is generated if a fatal error is detected on the PEG

port

SERR# result in NMI or SMI depending upon state of NMI

to SMI setup option

Note : A non-maskable interrupt (NMI) is a computer

processor interrupt that can not be ignored by

standard interrupt masking techniques in the

system. It is typically used to signal attention for

non-recoverable hardware errors.

Enable or disable this feature

Disable the PCIe link stability algorithm

Select the type of PCIE port0 to port5

i. Auto

ii. Enable

iii. Disable

VC1 will be mapped to TC specified

46

Page 47

Remove non-PORTCs from VCO Enable or disable

Lock PCIE credits register

Writes once to the PCIE credit register to prevent them

from being modified

4.6.5 VE Subsystem Configuration

VE-VECI

Unhide all physical HC

Max VE delay

Enable or disable VECI message

Enable or disable

Call for VE init for maximum number of seconds or init

reached

4.7 Virtual Appliance

Virtual Appliance (VA) is a software stack that brings to the personal computer unprecedented

levels of security and manageability for the IT professional.

Virtual appliance

VA ACPI Interface

Confirm Pending Operation

Enable or disable the VA

Note : valid for VA 3.0 only

Lock or unlock VA ACPI Interface for changing VA

parameters

Note : valid for VA 3.0 only

Disable : User confirmation is not required

to perform pending operation

Enable : User confirmation is required to

perform pending operation

Note : valid for VA 3.0 only

Virtual appliances are a subset of the broader class

of software appliances. Like software appliances,

virtual appliances are aimed to eliminate the

installation, configuration and maintenance costs

associated with running complex stacks of

software.

4.8 SV

SV is the system validation. This section is for computer technical use only, for validating the

system.

4.8.1 SV SMI Management

Global SMI

CPU SMBASE relocation will not occur if set to disable

47

Page 48

Periodic SMI Enable periodic SMI PMBASE + 30h, bit 14. this setup

option must be enabled for standby and suspend timer as

well as the USB RCOMP w/a

4.8.2 SV SATA Management

SATA Port Speed Setting

SATA port multiplier

FIS Based SATA Port Multiplier

For CPU SV use only

Note : Change this option only if you wish to boot to add-

in card

Enable or disable

Enable or disable

Note : A SerialATA port multiplier is a device that in

essence allows multiple devices to communicate along a

single SATA line in a similar manner to that of a USB hub

4.9 Exit

Save changes and exit

Exit system setup after saving the change

When user has completed the system configuration

changes, select this option to leave. Setup and reboot the

computer so the new system configuration parameters

can take effect.

Note : F10 key can be used

48

Page 49

Discard changes and exit Exit system setup without saving any changes

Note : ESC key can be used

Discard changes

Load optimal default

Load failsafe default

Discards changes done so far to any of setup questions

Note : F7 key can be used

Load optimal default value for all the setup questions

The optimal settings are designed for maximum system

performance, but may not best for all computer

applications.

Note : F9 key can be used

Load failsafe default value for all the setup questions

The BIOS automatically sets all setup option to a

complete set of default setting when this option was

selected

Note : F8 key can be used

49

Loading...

Loading...