Page 1

Intel® PXA27x Processor Family

Specification Update

October 2004

.Notice: The Intel® PXA27x Processor Family may contain design defects or errors known as

errata that may ca use the pr oduct to deviate from pu blish ed spe cificati ons. Cur rent c haracter ized

errata are documented in this s pecification update.

Order Number: 280071-003

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEP T AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WH A TSOEVER, AND INTEL DISCLAI MS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABIL ITY OR WA RRANTIES

RELA TING TO FITNESS FOR A PA RTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or charact erist ics of any featu res or instruc tions m ark ed "res erve d" or "und efined. " In tel reserves these for

future definition and shall have no responsibilit y wha tso ever for conflicts or incom pati bilities ar ising f rom future changes t o them.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled

platforms may require licenses from various entiti es, includi ng Intel Corpor ation.

Contact your local Intel sales office or your distributor to obtain the latest specifi cation s and befo re placi ng your product o rder.

Copies of documents which have an ordering number and are refer enced in this docum ent , or other Intel literature ma y be obtained by cal ling 1-800-

548-4725 or by visiting Intel’s website at http://www.intel.com.

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, Cable Port, Cel eron , Chips, Com me rce Car t, CT Connect, CT Media, Dialogic,

DM3, EtherExpress, ETOX, FlashFile, GatherRoun d, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel

NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Team Stati on,

Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPor t, Netpo rtE xpre ss, Optimizer

logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pent ium II Xeon, Pent ium I II Xeon, Performance at Your Command, ProShare,

RemoteExpress, Screamline, S hiva, Sm artD ie, Solu tions9 60, Sound Mar k, Storage E xpress, The Comput er Insi de, The Journey Inside, This Way In,

TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademar ks of Intel Corp oration or its subs idiar ies in the United States and

other countries.

Copyright © Intel Corporation, 2004. All Rights Re serv ed.

*Third-party brands and names are the property of their respective owners.

Page 3

Revision History

Revision Date Version Description

October, 2004 003 Added Errata 51, 52, 53, 54

August, 2004 002

April, 2004 001 First publication

Added Errata 48, 49, 50

Added Documentation Changes 5 - 15

Revision History

Intel® PXA27x Processo r Family Specification Update 3

Page 4

Preface

Preface

This document contains updates to the specifications for the Intel® PX A27 x Processor Family,

listed in Table 1.

clarifications, and spec ification changes.

software developers of applications, operating systems, a nd tools.

Intel Corporation has endeavored to incl ude a ll documented errata in the cons olidation pr oc ess.

However, Intel makes no representa tions or warranties concerning the com ple teness of the Intel®

PXA27x Processor Family Specification Upda te .

Information types defined in Nomenclature are consolidated into the Intel® PXA27x Processor

Family Specification Update a nd are no longer published in other documents.

This document might also contain information that was not previously published.

This document is a co mpilation of device and docu mentation errata, specif ication

It is intended for hardware system m anufacturers and

4 Intel® PXA27x Processor Family Specification Update

Page 5

Affected and Rel ated Documents

Affected and Related Documents

Table 1 lists the documents affected by and related to this errata update.

Contact an Intel® representative to obtain the latest revisio ns of these documents.

Table 1. Affect ed Do cument s / Related Documents

Title

Intel® PXA27x Processor Family Developer’s Manual

Intel® PXA27x Processor Family Design Guide

Intel® PXA27x Processor Family Electrical, Mechanical, and Thermal Specification

Intel® PXA27x Processo r Family Specification Update 5

Page 6

Nomenclature

Nomenclature

Errata are design defects or errors. These errata mi ght cause the Inte l® PXA27x Pro c e ssor

Family’s behavior to deviate from publishe d specifications.

used with any given processor stepping must assume that all errata documented for that stepping

are present on all devices unless oth erw is e noted.

Document at io n cha ng es include typos, errors, and omissions from the c urrent published

specifications. These changes will be incorporated in the next release of the document.

Specification clarifications describe a specification in greater detail or further highlight a

specification’s impact to a complex design situation.

any new release of the document.

Specification changes are modifications to the current published specifications. These changes

will be incorporated in the next release of the document.

Note: Errata remain in the specification update thr oughout the produ ct’s life cycle, or until a partic ular

stepping is no longer commercially available. Under these circumstances, errata removed from the

specification update are arch ived and made available upon request. Specif ication changes,

specification clarif ications, and documentation changes are removed f rom the specification update

when the appropriate changes are made to the appropriate product specification or user

documentat ion (data sheets, manuals, a nd so forth).

Hardware and software designed to be

These clarifications will be in corporated in

6 Intel® PXA27x Processor Family Specification Update

Page 7

Intel® PXA27x Processor Family Package Markings

Intel® PXA27x Processor Family

Package Markings

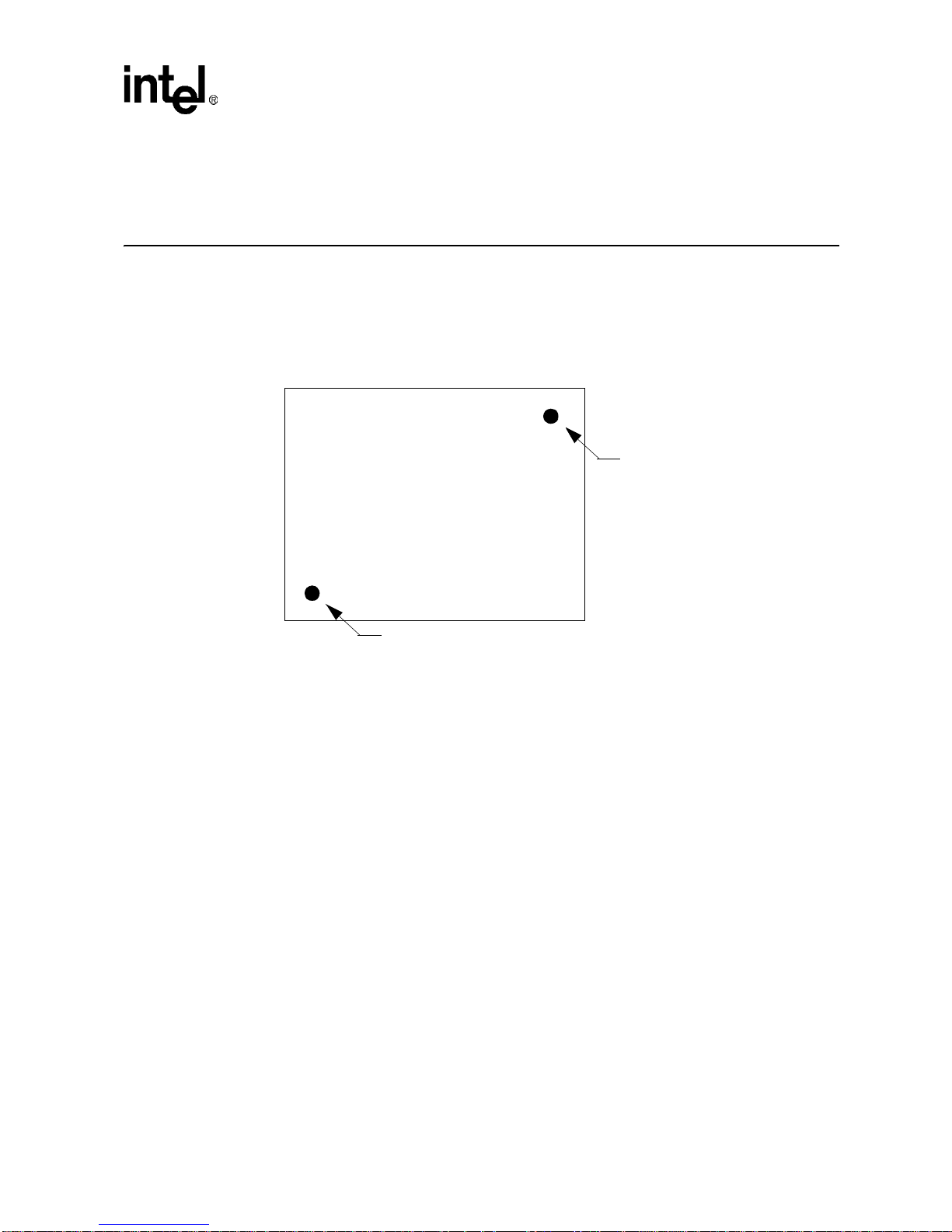

The following figure depicts the location, on specific Intel® PXA27x Processor Family packages,

where the actual markings are located. Actual markings are described in Table 2.

Figure 1.Intel® PXA27x Processor Family Package Ma rkings Locations

“LINE 1”

PIN 1 INDICATOR

for PXA271 and PXA272

Processor Family

i

“LINE 2”

“LINE 3”

“LINE 4”

“LINE 5”

“LINE 6”

PIN 1 INDICATOR for PXA270 Processor

Table 2 describes the actual markings that are on th e package at the locat ion indicated by “LINE x”

for each package offered.

Intel® PXA27x Processo r Family Specification Update 7

Page 8

Intel® PXA27x Processor Family Package Markings

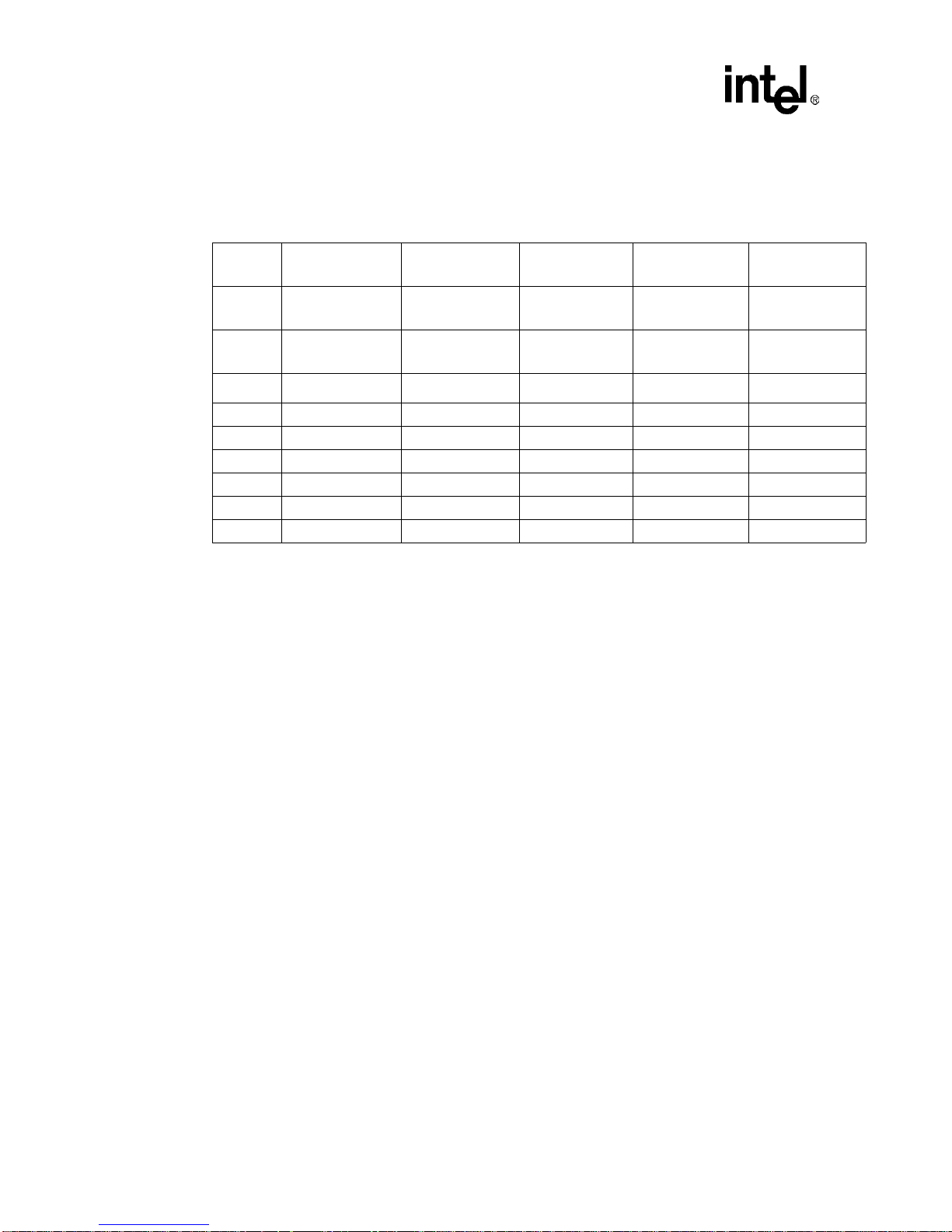

Note: This table is for example only. It must not be used to determine fina l production offerings.

Table 2. Example Processor Package Markings (For Example Only)

Discrete/

MCP

Max.

Freq.

Lead/

Lead Free

Stepping C0 C0 C0 C0 C0

Line 1 RCPXA270C0C624 RTPXA270C0C416 LVPXA271FC0312 RVPXA272FC0520 RVPXA272FC0416

Line 2 {FPO#} {FPO#} {MCP FPO#} {MCP FPO#} {MCP FPO#}

Line 3 {QDF#} {QDF#} {QDF#} {QDF#} {QDF#}

Line 4 {M} {C} ’04 {M} {C} ’04 {M} {C} ’04 {M} {C} ’04 {M} {C} ’04

Line 5 ATPO# ATPO# ATPO #

Line 6 COO COO COO

13x13 T-PBGA 13x13 T-PBGA

624 MHz 416 MHz 312 MHz 520 MHz 416 MHz

Lead (Pb) Lead (Pb) Free Lead (Pb) Lead (Pb) Free Lead (Pb) Free

14x14 FFCSP/

256LTyax/256SD

14x14 FFCSP/

256LTyax/256SD

14x14 FFSCP/

2x256L Tyax

8 Intel® PXA27x Processor Family Specification Update

Page 9

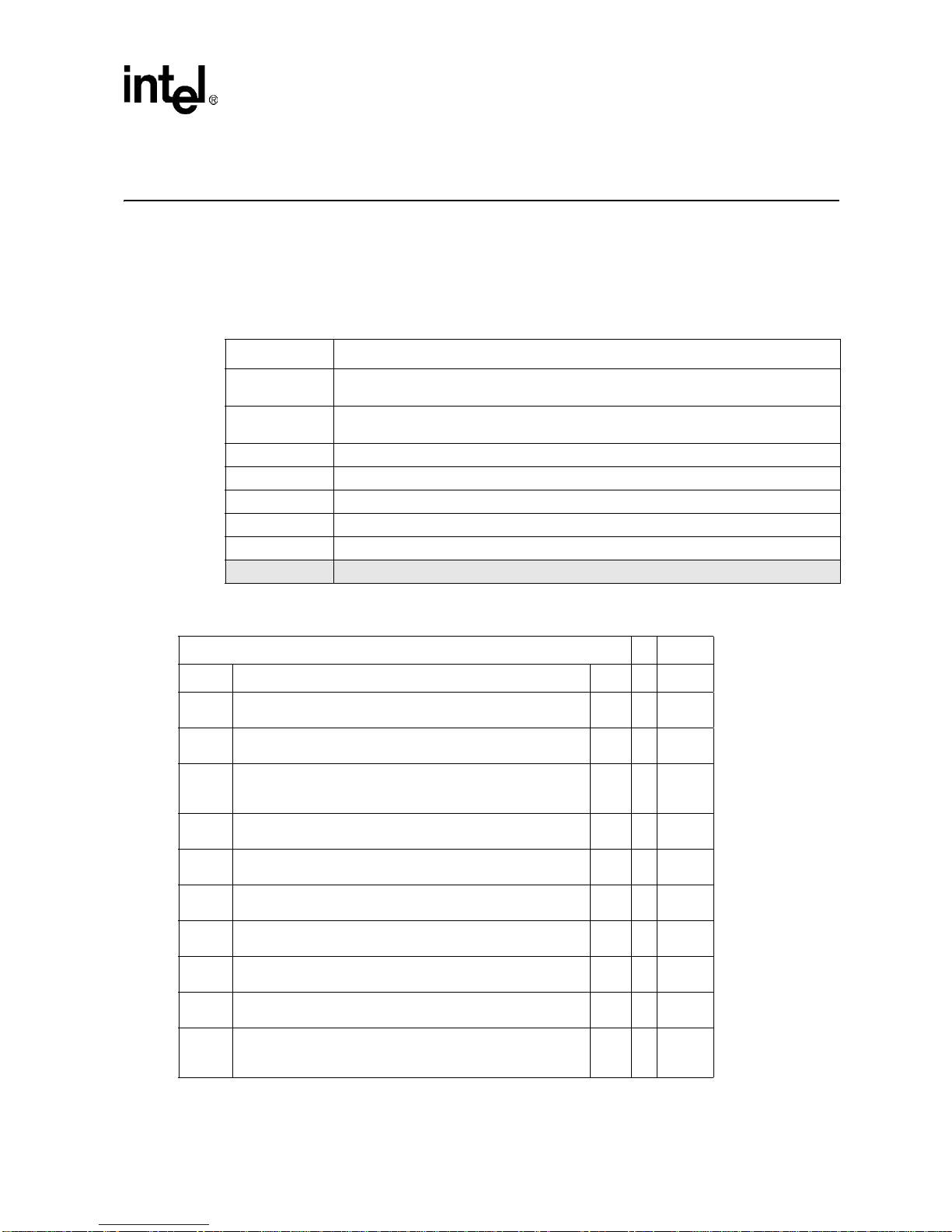

Summary of Changes

The following tables summarize the er rata, specification changes, specification clarifi cations, and

documentation chang es that apply to the In tel® PXA2 7x Process or Family .

the errata in a future steppi ng of the component and account for the other ou ts tanding issues

through documentatio n or specification changes a s noted.

Notation Meaning

Summary of Ch an ges

Intel migh t fi x s ome of

These tables use the following notations:

X

(No mark) or

(Blank Box)

Plan Fix This erratum might be fixed in a future stepping of the product.

Fixed This erratum has been previously fixed.

No Fix There are no plans to fix this erratum.

Doc Intel plans to update the appropriate documentation in a future revision.

No Bug This erratum has been determined to be a false erratum.

Shaded This item is either new or modified from the previous version of the document.

This erratum exists in the stepping indicated. specification change or clarification that

applies to this stepping.

This erratum is fixed in the listed stepping, or the specification change doe s n ot app ly to th e

listed stepping.

Table 3. Summ ary of Errata (Sheet 1 of 3)

References C0 Status

Number Title Page

1

2

3

4

5

6

7

8

9

10

CORE: IFU misses an external abort when a lock command is

outstanding

CORE: Aborted store that hits D-cache might mark write-back

data as dirty

CORE: Performance Monitor Unit Counts, using performance

monitoring event number 0x1, can be incremented erroneously

by unrelated core events

CORE: In SDS mode, back-to-back memory operations where

the first instruction aborts might hang

CORE: Lock aborts resulting from I-cache or I-TLB lock

operations are not presented properly on the trace interface

CORE: CP15 ID register accesses with opcode2 > 0b001 r eturn

unpredictable values

CORE: Disabling and re-enabling the MMU can hang the core

or cause it to execute the wrong code

CORE: JTAG parallel register updates require an extra TCK

rising edge

MMC: SPI mode – if card is deselected, PROG_DONE will not

be set

MEMC: No MRS command is given when exiting from Alternate

Bus Master Mode when SA1111 Address Muxi ng Mode is

enabled

13 X No Fix

13 X No Fix

14 X No Fix

14 X No Fix

14 X No Fix

15 X No Fix

15 X No Fix

16 X No Fix

16 X No Fix

16 X No Fix

Intel® PXA27x Processo r Family Specification Update 9

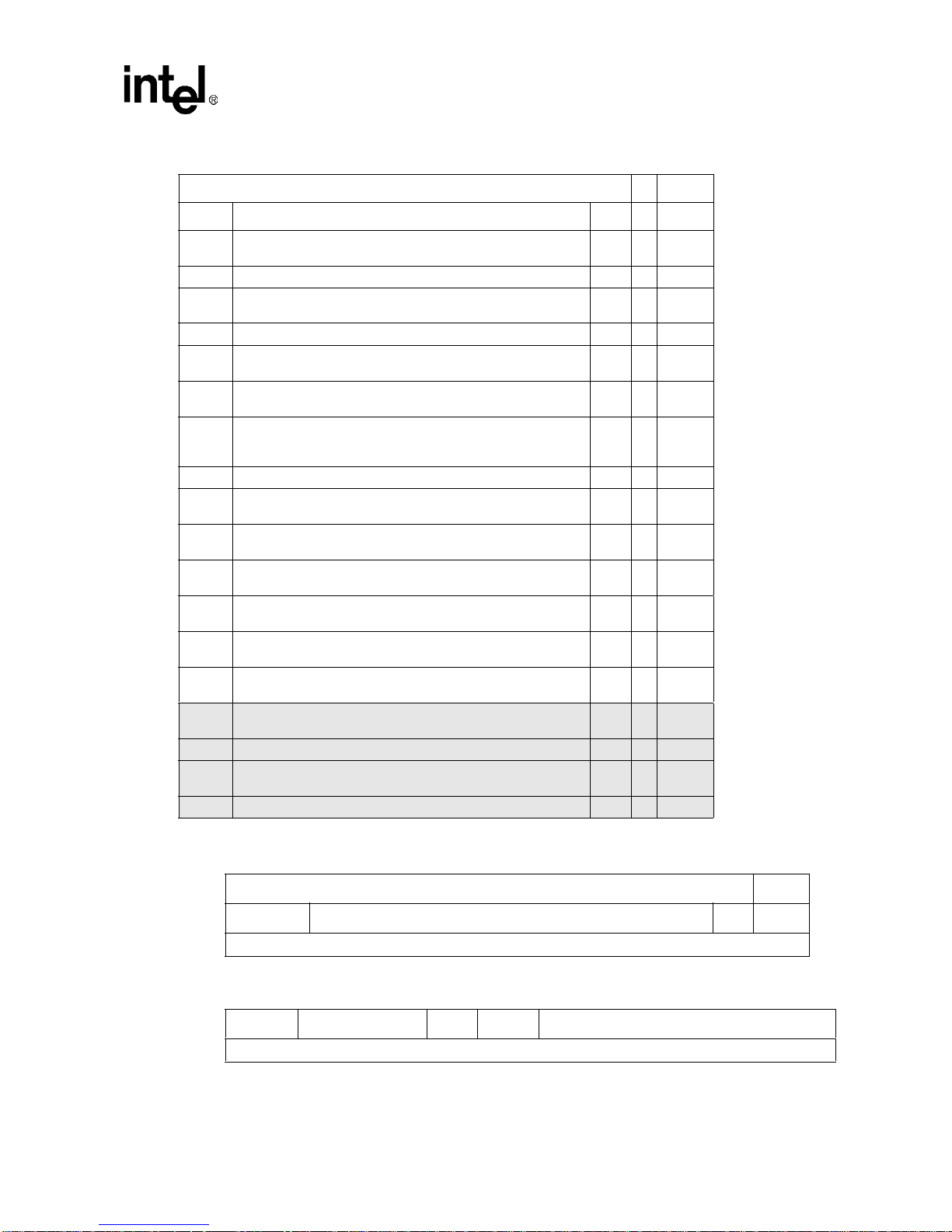

Page 10

Summary of Changes

Table 3. Summary of Errata (Sheet 2 of 3)

Number Title Page

11 KBD: Extra Keypad matrix interrupt in IMKP Mode 16 X No Fix

12

13 AC97: Command Done bit remains set after an AC97 cold reset 17 X No Fix

14

15

16

17

18

19

20

21 LCD: LCD not enabling in dual panel mode. 21 X No Fix

22 UDC: UDC does not correctly support alternate interfaces. 22 X No Fix

23

24

25 LCD: Enabling Overlay 2 for YUV420 hangs LCD controller. 23 X Plan Fix

26

27

28

29

30

31

32

33 SSP: TXD line does not tristate when SSP is Slave to Frame 29 X No Fix

34

35

36

USBH: USBH Register UHCRHPSx[CCS] Bit Set Incorrectly

After Power On

POWER MANAGER: Fast Ramp rates on voltage pins can

cause high current consumption.

LCD: Reconfiguring the LCD controller retains the previous PPL

value for the first line.

MSHC: Memory Stick does not come out of SLEEP mode after

wake up process.

LCD: Overlay1 is not enabled intermittently after re-enabling

LCD.

POWER MANAGER: Processor ignores BA TT/V CC faults while

exiting sleep mode.

KBD: Keyboard Edge-Detect Status Register Incorrect After

Standby Mode Wakeup.

UART: Character Timeout interrupt remains set under certain

software conditions

ICP: Receiver Aborts randomly occur prematurely and without

End of frame/Error in FIFO interrupt

SSP: OSTimer counter increments incorrectly for SSP Frames

in Network mode

USBOTG: Unable to measure duration of Single-Ended Zero

(SE0) for Session Request Protocol (SRP)

MEMC: Write/Read to/from SDRAM can collide with alternate

bus master mode when MDREFR:ALTREFB is set.

Power Manger: Core hangs during voltage change when there

are outstanding transactions on the bus

MMC: MMC unit in SPI mode always waits a minimum of 1 Ncx

cycles, even though the MMC spec dictates that SPI mode

CMD9 can have a minimum of 0 Ncx cycles.

SD: SD Controller in SPI mode not receiving data response for

CMD9 and CMD10 from some SD Cards

MEMC: SDRAM Refresh Commands are issued too often

during a VLIO access while BREQ is asserted.

Interrupt Controller: Unexpected exception vector when

ICCR[DIM]=0 and ICMR=0.

PowerManager: Simultaneous BATT and VDD faults results in

going to DeepSleep mode twice.

CORE: Non-branch instruction in vector table may execute

twice after a thumb mode exception

UART: UART does not correctly indicate a Framing Error

Interrupt in DMA mode.

References C0 Status

17 X No Fix

17 X No Fix

18 X No Fix

19 X No Fix

19 X Plan Fix

20 X No Fix

20 X No Fix

21 X No Fix

23 X No Fix

23 X No Fix

24 X Plan Fix

25 X No Fix

25 X No Fix

27 X Plan Fix

27 X Plan Fix

28 X No Fix

28 X No Fix

29 X No Fix

29 X No Fix

30 X No Fix

10 Intel® PXA27x Processor Family Specification Update

Page 11

Table 3. Summ ary of Errata (Sheet 3 of 3)

References C0 Status

Number Title Page

37

38 CLOCKS: System Hangs when enabling HalfTurbo Switching 31 X No Fix

39

40 SDIO: SDIO Devices Not Working at 19.5 Mbps 32 X Plan Fix

41

42

43

44 KBD: Keypress wakeup from Standby mode is not reliable 34 X No Fix

45

46

47

48

49

50

51

52 LCDC: Disable Done Interrupt does not always occur 38 X No Fix

53

54 AC97: AC97 CAR[CAIP] bit field can be incorrectly set 38 X No Fix

CLOCKS: System Hangs when enabling RUN/TURBO

switching at 520MHz

MEMC: Memory Controller hangs when entering Self Refresh

Mode.

AC97: Command Done bit is never set when data is written in

slot12

SD/MMC: SD/MMC controller CRC errors with some SD/MMC

cards

USBH: There is no Individual Power Sense Polarity bit for each

Host Port. The Power Sense Polarity bit controls the polarity for

all three Host Ports.

USBH: USB Host Port 3 in Transceiverless Mode may not work

correctly with an external device.

SD/MMC: SPI mode commands fail even on cards that are

compatible with SPI spec 1.0

CLOCKS AND POWER: PWM Clock Enables do not work as

specified

ICP: Occasionally EIF, EOF and CRC interrupt are missed when

a CRC error is recei ved

POWER MANAGER: Batt Fault does not always re-enable

GPIO 0 and GPIO 1 as wake-up sources.

POWER MANAGER: The processor does not exit from Sleep/

Deep-Sleep Mode.

SDIO: CMD53 multiple block data transfer with block count set

to 0 not supported

UDC: RCV can not be tied high during UDC transmission when

using an external transceiver

Summary of Ch an ges

30 X No Fix

32 X No Fix

33 X No Fix

33 X Plan Fix

33 X Plan Fix

34 X Plan Fix

35 X Plan Fix

35 X No Fix

36 X No Fix

36 X No Fix

37 X Plan Fix

37 X No Fix

38 X No Fix

Table 4. Summary of Specifi cation Changes

Number Title Page

NOTE: There are no specification changes at this time.

Table 5. Summ ary of Speci fi cation Clarifications

Number Document Revision Page Status Specification Clarifications

NOTE: There are no specification clarifications at this time.

Intel® PXA27x Processo r Family Specification Update 11

References Status

Page 12

Summary of Changes

Table 6. Summary of Documentation Changes

Number Document Revision Page Status Documentation Changes

NOTE: There are no documentation changes at this time.

12 Intel® PXA27x Processor Family Specification Update

Page 13

Errata

Errata

E1. CORE: IFU misses an external abort when a lock command is

outstanding.

Problem: A bus abort occurs on a code fetch while an I-TLB lo ck mcr is outstanding. The IFU fails to abort,

instead executing t he ins tructi on return ed on th e abort ing trans action. P arity e rrors are not aff ected.

The bus a bort might be due to either an ABORT pin asserti on or a mult i-bit ECC error on the c ore.

On the core, the bus abort can occur as th e result of a master abort, a targe t abort, or a single data

phase disconnect on the system bus.

Implication: TBD

Workaround: Branch flush after every ITLB or I-ca che lock.

Status: No Fix

E2. CORE: Aborted store that hits D- cache might mark write-back data as

dirty.

Problem: If an aborted store hits clean data in the data cache (data in an aligned four-word range that has not

been modified from the core since it was last loaded in from memory or cleaned), the data in the

array will not be modified (the store will be blocked), but the dirty bit will be set.

When that line is then aged out of the data cache or explicitly cleaned, the data in that four-wor d

range will be evicted to external memory, even though it has never been changed. In normal

operation, this will be nothing more than an extra store on the bus that writes the same data to

memory as is already there.

This problem might be visible at the following boundary condition:

1. A cache line is loaded into the cache at address A

2. Another master externally modifies address A

3. An Intel XScale® core sto re in stru ction atte mpts to mod ify A, hits the cache, aborts becau se o f

MMU permissions, and is back ed out the of cache. That lin e should no t be marked “d irty”, but

because of this defect it will be.

4. The cache line at A then ages out or is explicitly cleaned. The origin al data from location A

will be evicted to external memory, overwriting the data written by the external master.

This situation happen sonly if software is allowing an exter nal m aster to modify memory that is

write-back or w rite- allocate in the XScale pag e tables , an d depen ding o n the f act th at t he data is n ot

dirty in the XScale cache to preclu de the cached version from overwriting the ext ern al memory

version. If there are any semaphor es or any other handshaking to prevent collis ions on shared

memory, this should not be a problem.

Implication: TBD

Workaround: For a shared memory region , mark it as write-through mem ory in the XScale page table to prevent

the data from ever being written out as dirty, so the defect does not appear. Alternatively, ensure

that any cached copy of t he data in exte rnal memory is inv alidated if an ext ernal ag ent mod ifies th e

external copy.

Status: No Fix

Intel® PXA27x Processo r Family Specification Update 13

Page 14

Errata

E3. CORE: Performance monitor unit counts, using performance

monitoring event number 0x1, can be incremented erroneously by

unrelated core events.

Problem: The performance monitor unit can be used to count cycles in which the I-cache cannot del iver an

instruction. Perfor mance monitoring event number 0x1 is used for this. Accordi ng to EAS text, the

only cycles counted should be those due to an I-cac he mi s s or an I-TLB miss. The following

unrelated events in the core also cause the corresponding count to incr em ent when event number

0x1 is be i n g m o ni tored:

• Any architectural event (e.g. IRQ, data abort)

• mstr instructions that alter the CPSR control bits

• Some branch instructions, including indirect branches and those mis-predicted by the BTB

• CP15 mcr instructions to registers 7, 8, 9, or 10 which involve the I-cache or the I-TLB

Each of the items above might cause th e perfo rmance mo nitoring co unt to i ncrement s everal t imes.

The resulting performance monitor ing count might be higher than expected if the above items

occur , but never low e r. The performance monitor unit uses ic_instValid_qf2h. This si gna l asserts

not just at the proper time, but also due to th e events described above.

Implication: TBD

Workaround: There is no way to obtain the correct number of cycles stalled due to I-cache misses and I-TLB

misses. One component of the unwanted nois e may be filtered out: extra counts due to branch

instructions mis-predicted by the BTB. The number of mispredicted branches can also be

monitored using perf ormance monitoring event 0x6 during the same time period as event 0x1. The

mispredicted branch number can then be subtracted fro m the I-cache stall number generated by the

performance monitor to get a value closer to the correct one. Depending on the nature of the code

monitored, this workaround might have limited value.

Status: No Fix

E4. CORE: In SDS mode, back-to-back memory operations where the first

instruction aborts might hang.

Problem: If back-to-back memory operati ons occur in SDS (special debug state, used by ICE and debug

vendors) and the first memory operation gets a precise data abort, th e fir s t memory operation is

correctly cancelled and no abort o ccurs. However, depending on the timing, the second memory

operation might not work correctly. The data cache might internally cancel the seco nd operation,

but the regis t e r file may have scoreboarded registe rs for that se c ond memory operation.

The effect is that the part might hang (due to a permanently scoreboarded register) or that a store

operation might be cancelle d inco rr ectly .

Implication: TBD

Workaround: In SDS, any m e mo ry operation that m ight cause a precise data abort sho uld be followed by a write-

buffer-drain operation. This operation precludes additional memory operations from being in the

pipe when the abort occur s. Do not use load multiple/store multiple, which might cause precise

data aborts.

Status: No Fix

E5. CORE: Lock aborts resulting from I-cache or I-TLB lock operations

are not presented properly on the trace interface.

Problem: This problem affects only processors that use the core ’s trace interface. An I-cache or I-TLB lock

operation that r esults in lock abort crea tes a unique internal pi peline signal timing that causes

14 Intel® PXA27x Processor Family Specification Update

Page 15

Errata

trouble on the trace inter face, which results in the core reporting the event as if it came with the

next instruction executed afte r the aborting lock instruction, the data abort vector.

Implication: TBD

Workaround: None.

Status: No Fix

E6. CORE: CP15 ID register accesses with opcode2 > 0b001 return unpre-

dictable values.

Problem: The XScale core does not implement CP1 5 ID codes reg is ters other than the Main ID register

(opcode 2 = 0b000) and the Cache Type register (opcode2 = 0b 001). If any of the unimplemen te d

registers are accessed by sof tware (for example, mrc p15, 0, r3, c1 5, c15, 2), the value of the Main

ID register should be returned. Instead, an unpredictable va lue is returned.

Implication: TBD

Workaround: None.

Status: No Fix

E7. CORE: Disabling and re-enabling the MMU can hang the core or

cause it to execute the wrong code.

Problem: If the MMU is disabled via the CP15 control register after being enabled, certain timing cases can

cause the pr oc essor to hang. In addition , re-enabling the MMU after disa bling it can cause the

processor to fetch and execute code from the wrong physical address. To avoid these issues, the

code seque nce bel ow mus t be em plo yed whene ver dis abli ng th e MMU or re-ena blin g it af ter wards .

Implication: TBD

Workaround: The following code sequence must be used to disable and/or re-enable the MMU safely . The

alignment of the mcr instruction that disables or re-enables the MMU must be controlled carefully,

so that it lies in the first word of an instruction cache li ne:

;//@ The following code sequence takes r0 as a parameter. The value of r0 will be

;//@ written to the CP15 control register to either enable or disable the MMU.

mcr p15, 0, r0, c10, c4, 1 ;// @ unlock I-TLB

mcr p15, 0, r0, c8, c5, 0 ;//@ invalidate I-TLB

mrc p15, 0, r0, c2, c0, 0 ;//@ CPWAIT

mov r0, r0

sub pc, pc, #4

b AfterAlign ;//@ branch to aligned code

ALIGN 32 ;//@ align to 32 bytes

AfterAlign

mcr p15, 0, r0, c1, c0, 0 ;//@ enable/disable MMU, caches

mrc p15, 0, r0, c2, c0, 0 ;//@ CPWAIT

mov r0, r0

sub pc, pc, #4

Status: No Fix

Intel® PXA27x Processo r Family Specification Update 15

Page 16

Errata

E8. CORE: JTAG parallel register updates require an extra TCK rising

edge.

Problem: The IEEE 1149.1 spec states that the effects of updating all parallel JT AG registers should be seen

on the falling edge of TCK in the Update-DR state. The XScale core parallel JTAG registers

incorrectly requir e an extra TCK rising edge to make the update visible. Ther efo re, operations like

hold-reset, JTAG break, and vector tr aps requ ire ei ther an ex tra TCK cycle b y goin g to run-tes t-idl e

or by cycling through the state machine again to trigger the expected hardw are behavior.

Implication: TBD

Workaround: If the JTAG interface is polled continuously, this erratum has no effect. If not, an extra TCK cycle

can be caused by going to run-test-idle after writing a parallel JTAG register.

Status: No Fix

E9. M MC: SPI mode – if card is deselected, PROG_DONE will not be set.

Problem: If changing SPI chip selects, the PROG_DONE bit does not get updated with the state of the

selected card.

Implication: If programming card0, then switch to card1, then come back to card0, there is no way of know ing

if card0 ever finished programming.

Workaround: User can switch the MMDAT signal functionality to GP IO functionality an d monitor the signal by

reading the GPIO St atus register un til the signal goes high.

Status: No Fix

E10. MEMC: No MRS command is given when exiting from alternate bus

master mode when SA-1111 address muxing mode is enabled.

Problem: When using alternate bus master with MDCNFG[SA1110x] s et, after the alternate bus master has

given the bus back to the processor, if the first access by the processor is a VLIO access, the MRS

commands to switch the SDRAMs back into burs t-of-4 mode occu rs after a long delay. If SDRAM

is accessed before the MRS command is performed , data returned to the proces sor registers will n ot

be valid.

Implication: TBD

Workaround: Use any of the following options to workaround this erratum:

• D o n ot use SA-1111 a d dress mu xing mode w ith an a lternate bu s master.

• The alternate bus master can perform the MRS comm and to put the SDRAM into burst-of- 4

mode before de-asserting the MBREQ signal.

Status: No Fix

E11. KBD: Extra keypad matri x in te rr u p t in IMK P mode.

Problem: A n unexpected interrupt during keypad-matrix manual scan in ignore-multiple-keypress mode

(IMKP). The test consists of pressing one, single, valid key and holding it down, then pressing a

second, sin gle , valid key and holding it down, then both pressed keys are released simultaneously.

This test results in three vectors to the interrupt-service routine where two are expected.

The first vector to the ISR occurs on first key down. The sec ond vector is unexpected. This is

possibly caused by the second key down. The thi rd vector occurs approximately at the time of al l

keys up.

Debounce interval = 3ms, KP C[IMKP] = 1, KPC[ASACT] = 0; KPC[MI] = 1.

16 Intel® PXA27x Processor Family Specification Update

Page 17

Errata

Implication: TBD

Workaround: Do not set KPKDI[I n te rval] to le s s than 10ms.

Status: No Fix

E12. USBH: USBH register UHCRH PSx[C CS] bit set incorr ectly after power

on

Problem: The UHCRHPSx[CCS] bit may be set after power on reset. Under normal con ditions, when set,

this bit indicates th at a USB device is connected to the USB host port. The error is that this bit is

being set even though there is no device physically connected to the USB host unit.

Implication: TBD

Workaround: Disable gl obal port power for the USB host unit. Only e na ble individual port power for the USB

host ports that will be used in the system.

Status: No Fix

E13. AC97: Command-done bit remains set after an AC97 cold reset.

Problem: After an AC97 cold reset is asserted (GCR[nCRST]=0) when the AC97 controller unit is enabled

again, the command-done bit (GSR[CDONE]) is getting set when it sho uld not.

1. Enable the AC97 unit.

2. Enable the codec.

3. Write some data to the codec register using AClink.

4. Wait for comman d- done bit (GSR[CDONE]) to set and then clear it.

5. Shut down the codec by writing 0x1000 to codec address 0x26.

6. Wait for comman d- done bit (GSR[CDONE]) to set and then clear it.

7. Generate wakeup event from Codec and wait for prima ry codec resume bit (GSR[PRESINT])

or secondary codec resume bit (GSR[SRESINT] ) to set.

8. Once resume bit is set, assert a cold reset by writing 0 to GCR[nCRST].

9. Enable the AC97 controller and read the GSR. The command-don e bit is s et; however, it

should be clear.

Implication: TBD

Workaround: After asserting cold reset, the GSR[CDONE] bit must be cleared by writing a 1 to GSR[CDONE].

Status: No Fix

E14. P O WE R MANAGER: Fast ramp rates on voltage pins can cause high

current consumption.

Problem: If voltage ri se/stabilization time is too fast for any of the voltage pins (VCC_core, VCC_mem,

VCC_batt, etc.), th en the internal circuitry causes high current consumption on these vo ltage pins.

This conditio n will not damage the internal circuitry of the processor. The duration of the high

current consumption is less than 20µsec.

The following describes the current consumption in order of voltage domain bootup sequence.

• If the voltage rise/sta biliza tion time of VCC_B ATT is longer tha n 500µsec at room

temperature, then the com bined current on VCC_BATT will be less th an 100mA for less than

20µsec.

Intel® PXA27x Processo r Family Specification Update 17

Page 18

Errata

• If the voltage rise/stab ilization time of VCC_USB, VCC_IO, VCC_MEM, VCC_BB,

VCC_LCD, VC C _USIM is longer than 500µsec at room temperature, th en the combined

current on VCC_US B, VCC_IO, VCC_MEM, VCC_BB, VCC_LCD, VCC_USIM will be

less than 500mA for less than 20µsec.

• If the voltage rise/stabilization time of VCC_CORE, VCC_SRAM, VCC_PL L is lo nger than

500µsec at room temperatur e, th en the combined current on VCC_CORE, VCC_SRAM ,

VCC_PLL will be le ss than 100mA for less than 20µsec.

Example of bat te ry life consump tion:

— Assume square current spike = 85 0m A = 0.85Coulomb/sec

— Current drain of the current s pike lasting 100µsec

— 0.85 Coulomb/sec * 0.0001 sec = 85 µCoul om b total dr a in

— Assume 150mA-hr battery = 540 Coulombs

— Calculate current spik e percentage of total battery capacity: 85µC / 540C = 1.57 e-7

— Current sp ike c onsumes only 0.0000157% of b atte ry capacity.

Implication: High current c ons umpti on on pr ocess or volt age sup ply pins can caus e exter na l pow er mana ge ment

circuitry to enter into an error/shutdown condition.

Workaround: Voltage rise/stabilization time must be determined by the sy stem designer to mitigate any error

condition on external circuitry.

Status: No Fix

E15. LCD: Reconfiguring the LCD controller retains the previous PPL

value for the first line.

Problem: If you progra m th e LCD controller for one c onfiguration, then disable the LCD controller and

program it for another configuration and enable it again, the first line re tains the pixels-per-line

(PPL) value from the previous configuration.

For example, configuring the LCD to 320x200 and then disabling it and reconfiguring it to

640x480, and enab lin g it agai n, the firs t l ine r eta ins th e P PL va lue f rom the pre vious con fi gurati on,

which is 320.

This issue could effect more th an just the first frame, due to the fact that the LCD DMA is

initialized wit h a size to fit the fr ame size. Data from the fi rst fr ame c ould s pill o ver int o th e secon d

frame, and so on.

Implication: If the wrong number of pixels are sent to th e LCD panel for the first line of a frame, the displ ay on

the LCD screen could be corrupt.

Workaround: When configuring the LCD the second time, configure it to the desired LCD configuration, enable

the LCD, disable it, and then enable it agai n, for the third time. This ensures that when the LCD

controller is enab led for the third time, it will begin the frame with the right PPL value.

Status: No Fix

E16. MSHC: Memory Stick does not come out of SLEEP mode after wake

up process.

Problem: The test is tryi ng to put the memor y stick to ”SLEE P” and then wake it up by sendi ng the “RESET ”

TPC. The manual says that “Memory Stick wakes up and performs a packet processing, when a

packet transfer by SET_CMD TPC or W rite_Reg occurs at SL = 1 in Status Register 0”.

18 Intel® PXA27x Processor Family Specification Update

Page 19

The memory stick does not w ake up after sending a SET_CMD TPC or Write_Reg once. However,

it does wake up on sending SET_CMD TPC or Write_Reg twice . After reading the value of the

MSINT regi ster (addr e ss 0x4180_0008)after sending the firs t TPC, it conta ins the value

0x0000200D, indicating that a time out e rror occurred.

After reading the “SLEEP” bit in the “status register 0”, it remains “1” after the first TPC and

changes to “0” after the second TPC, indicating it was asleep after the first TPC transmission and

awake after the second TPC transmission.

How to reproduce:

• Send “SLEEP” SET_CMD TPC.

• Read the Status Register 0 (Sleep bit should be 1).

• Wake up the Memory Stick by sending “RESET” SET_CMD TPC.

• Paus e fo r 10 sec o nd s .

• Read the Status Regis ter 0 (Sleep bit should be 0 but it shows 1).

• Send “RESET” again.

• Read the Status Register 0 (Sleep bit shows 0).

Implication: TBD

Errata

Workaround: Software should send two reset TPC commands to the Memory Stick. Memory Stick wakes up

after two reset TPCs.

Status: No Fix

E17. LCD: Overlay1 is not enabled intermittently after re-enabling LCD.

Problem: When enabling and dis a bling LCD several times, intermittently, Overlay1 output is all zeros

instead of intended frame buffer overlay pattern. Overlay 2 works fi ne.

Implication: TBD

Workaround: Option1:

Users must not use Overlay 1 but can use Overlay 2.

Option2: Users can use Overlay 1 by:

1. Programming the LCD registers

2. E na b l ing the LC D (L C CR 0 [E N B] = 1)

3. Disabling the LCD (LCCR0[DIS] = 1)

4. Reprogramming the lcd registe rs but not the overlay1/cursor r e gisters. Also, do not write

DMA FDAD R regi s t ers

5. E na b l ing the LC D (L C CR 0 [E N B] = 1)

6. Performing a quick disable of the LCD (LCCR0[ENB] = 0)

7. Programming the DMA registers

8. E na b l ing the LC D (L C CR 0 [E N B] = 1)

9. Updating the overlay/cursor registers if required. Follow the instructions me ntioned in the

manual in sec tion 7.4.7 for overlay1 and 7.4.10 for curs or as to how to change the overla y/

cursor registers dynamically when the LCD is enabled.

Intel® PXA27x Processo r Family Specification Update 19

Page 20

Errata

Status: Plan Fix

E18. POWER MANAGER: Processor ignores BATT/VCC faults while exiting

sleep mode.

Problem: When asserting nBATT_FAULT or nVCC_FAULT during Sleep mode with the corresponding

IDAE set, and the fault is still present after boot, the part does not enter Deep Sleep. However, if

the IDAE bit is clear, and the fault is still present after boot, the part enters Deep Sleep as expected.

Implication: If a FAULT continues to occur while the proces s or is exiting Sleep Mode, then the processor is

going to cont inue to bootup and c onsume power. There must be enoug h ba ttery power or the

system must be able to toler a te the fault condition until the workaround below is complete.

Workaround: Before entering sleep or deep sleep via software, first write 1 to the PMCR[IAS] bit to enable

interrupts and then a separate write must be performed to set the desired PMCR[xID AE] bits.

When the chip exits sleep mode, the interrupt pertaining to Power Ma nagement Unit must be

unmasked, ICMR[PWR_I2C] = 0b1, to find out if a fault has occurred. Alternatively, the

PMCR[INTRS] bit can be checked.

Status: No Fix

E19. KBD: Keyboard Edge-Detect Status Register Incorrect After Standby

Mode Wakeup.

Problem: When the pro ces sor i s in stand by m ode and it i s prog ra mmed to wake up by a Ke yPad GP IO pul se,

the PKSR (Keyboard Edge detect Status) does not correctly report the GPIO that caused the

Wakeup.

Scenario 1 (Correct):

If only one keypad GPIO is pulsed, and it is programmed to wa keup from standby in PKWR,

the PKSR reports the correct GPIO as the source of the wakeup as expected.

Scenario 2 (Incorrect):

If ALL keypad GPIOs are pulse d but only one is programmed in PKWR to wake up , the PKSR

reports all the GPIOs (except fo r th e ones in use) as the source of the wakeup. This is wrong,

since only one GPIO was programmed to wake up, regardless of the fact that all GPIOs were

pulsed.

Therefore, the following documentation will be added to the Developer’s Manual:

"If any of the PKWR bits ar e enabled, then only the keypad r e lated to that PKWR will caus e a

wakeup. If there is any other a c tivity (active high) on any other keypad pins at this time, then

irrespective of its PKWR setting, it will be registered into the PKSR."

Implication: The user will not be able to detec t which keypress woke the processor out of S t a ndby mode.

Workaround: The workaround is to only use PKSR as an indicator that a key pr e s s woke th e proces sor. The user

will not be able to tell which key woke the processor.

Status: No Fix

E20. U ART: Character Timeout interrupt remains set under certain

software conditions

Problem: The issue is that randomly the character timeout interrupt does not clear and the DR bit is not set.

The failure was reproduced by adding a softwar e delay loop inside the character timi ng in terrupt

routine between reads from the FIFO. The test continuously repeats and increases the softw are

delay. After a few iterat ions, the tests get int o a continuous inter rupt loop, where the character

timeout interrupt is s et, but th ere is not any data in the F IFO. If the de lay lo op is placed ju st out side

20 Intel® PXA27x Processor Family Specification Update

Page 21

Errata

the loop to read out the data, the test never fails. So the issue looks to be related to the amount of

time between re ading data out of the FIFO.

Pseudo Code for the Character Timeout Interrupt Handler routine test:

1. Read LSR and check for errors

2. Read Data from FIFO

3. Software Delay (Delay increases after each test)

4. Read LSR, check for errors, and LOOP back to (2) if DR is SET.

5. DONE

if step (3) is placed in front of step (1) the issue never occurs.

Implication: The softwar e servicing the UAR T can be trapped in a n infinite loop.

Workaround: Steps 2 and 6 have been added to the Interrupt Ha ndler routine. Disabling the Receiver Time-Out

interrupt via IER[RTOIE] (step 2) prevents the Receiver Time-Out interrupt from becoming

continuously set.

1. Read the Line Status Register (LSR) and check for errors

2. Disable the Receiver Time-Out int err upt via IER[RTOIE]

3. Read Data from the UART FIFO

4. Software Delay (Increments after each test)

5. Read LSR, check for errors, and LOOP back to (2) if DR is SET.

6. No more data in FIFO: Re-enable RTO interrupt via IER[4]

7. DONE

Therefore, users must disable the Receiver Time- Ou t interrupt, then read data from t he F IFO, then

re-enable the Receiver Time-Out interrupt, before exiting the handler routine.

Status: No Fix

E21. LCD: LCD not enabling in dual panel mode.

Problem: After the LCD unit is dynami c a lly changed from single panel mo de to dual panel mode, the LCD

unit will not ou tput any data on the LCD pins.

Implication: TBD

Workaround: Do the following sequence to change from single panel mode to dual panel mo de :

Configure the L CD to Single panel m ode

Enab le the LCD

Disable the LCD

Reconfigure the LCD to Dual Panel mode without programming the DMA registers.

Enab le the LCD

Do a quick disable (not normal disable).

Program t he LCD DMA registers

Enable the LCD for operation in Dual Panel mode.

Status: No Fix

Intel® PXA27x Processo r Family Specification Update 21

Page 22

Errata

E22. U DC: UDC does not correctly support alternate interfaces.

Problem: When a SET_INTERFACE command is sent from the host, the UDC reallocates the internal FIF O

memory.

When USB Client comes up after the USB Reset and Set Con figuration is done other than

Configuration 0, it does not allow access to all the Interfaces available for that configuration.

-------------------------------------------------------Some excerpts of USB Specification describing use of Interfaces

-------------------------------------------------------As part of the configuration process, the hos t set s the dev ice configuration and, where necessary,

selects the appropriate alternate settings for the interfaces.

Interfaces are numbered from zero to one less than the number of concurrent interfaces s upp orted

by the configuration. Alte rnate settings range from zer o to one less than the number of alter na te

settings for a s pecifi c int erface. The d efa ult settin g when a dev ice is i nitiall y con figur ed i s alte rnate

setting zero.

see section: Set Interface

This request allows the host to select an alternate setting for the speci fied interface. This request

cannot be used to change the set of configur ed interfaces (the SetConfigu ration() request must be

used instead).

see section: Configuration

The descriptor describes the number of in terfaces provided by the configuration. Each interface

may operate independentl y. For example, an ISDN device mig ht be co nfigu red with t wo int erfaces,

each providing 64 Kb/s bi-directi onal channels that have sepa rate data sou rces or sinks on the host.

Another configuration migh t pr esent the ISDN device as a single interface, bon ding the two

channels into one 128 Kb/s bi-directional channel.

An endpoint is not shared among inte rf aces within a single configuration unless the endpoint is

used by alternate settings of the same in terfa ce. Endpoints may be shar ed among interf aces tha t are

part of different configurations without this restriction.

Implication: The processor USB Client does not fo llow the USB Specification when dealing with different

interfaces. External USB hos t conn ected to the processor USB Client cannot switch correctly

between alternate interfaces on the processor USB Client. This issue makes the processor USB

Client difficult to be a compound device.

Workaround: TBD

Status: No Fix

22 Intel® PXA27x Processor Family Specification Update

Page 23

Errata

E23. I CP: Receiver Aborts randomly occur prematurely and without End of

frame/Error in FIFO interrupt

Problem: Randomly, Receiver Abort (ICSR0[RAB]=1) occurs prematurely a nd without the EOF status/

interrupt bit set (ICSR1[EOF]=1). When this event occur s, there is always 2 bytes left in the RX

FIFO.

A Receiver Abort should always cause an EOF, but in the failing cases, only the Receiver Abort is

set.

Adding ~15us delay to the receive data available interrupt (IIR[I ID]=0b10) ser vic e routine causes

this failing case to pass, but limits the transfer size to the size of the FIFO since the added delay

will cause an overrun condition.

Implication: TBD

Workaround: Software must do retries af ter RAB has occurred. Once a RAB event occurs, continue to read data

out of the FIFO until the EOF fl ag sets, then th row away all th e data of that frame, and then make a

request to the host to resend/retry the last frame of data again.

Status: No Fix

E24. S SP: OST i mer counter increments incorrectly for SSP Frames in

Network mode

Problem: When SSP unit is in network mode, when PSP protocol is used, and the SSP is master to Frame

(irrespective of ssp sclk d irectio n) and FSRT bit is set to 1, OStimer fr ame coun ter incr ements more

than the frame is asserted by SSP. For example, 11 frames are ass erted as seen on a logic analyzer,

but OStimer is showing that the frame sig nal is asserted for 12 times. OS timer works fine when

FSRT is cleared and when in non-network mode.

Implication: TBD

Workaround: Subtract one from the value that is read from the OSTimer frame counter.

Status: No Fix

E25. LCD: Enabling Overlay 2 for YUV420 hangs LCD controller.

Problem: Enabling Overlay 2 in YUV 420 mo de causes the LCD controller to stop op erating (DMA activ ity

stops and the screen fades away). The test is unabl e to gracefully shutdown the LCD controller

after this failu re.

Enabling Ov e rlay 2 in RGB mode has no problems.

Implication: TBD

Workaround: To Enable/Disable Overlay 2 in 4:2:0 mode:

Step 1: a. Enable the LCD with Overlay2 disabled.

Step 2: a. Enable Overlay 2 in RGB m ode with min imum s ize possibl e so t hat only o ne fra me

worth of data fit in Channel 2 FIFO. Size of Channel 2 FIFO is 128 byte s. Progra m

the Descriptors and write to O2 CR1.

b. Run at least 1 frame with Overlay 2.

c. Disable the Overlay 2 by writing to O2CR1 and Frame Branch Registers (FB Rx) .

d. Wait for 3 base EOF interrupts.

Step 3: a. Enable Overlay 2 in YUV 420 mode. Write to O2CR1.

b. Unmask/Clear the input underrun for Channel 2. Wait for input underrun from

Channel 2. Write DMA descriptors for Cha nnels 2, 3, and 4.

Intel® PXA27x Processo r Family Specification Update 23

Page 24

Errata

Step 4: a. Now Overlay 2 in YUV 420 mode is en a ble d and running.

Step 5: a. If Overl a y 2 ne eds to be disabled, Disable the Overla y 2 by writing to O2CR1 and

Frame Branch Registers (FBRx).

b. If the Overlay 2 needs to be enabled again, Go to Step 3.

Step 6: a. If LCD needs to disabled, disable the Over la y 2 as mentione d in Step 4, then

Disable LCD, and go to Step 1.

Pseudo Code to Enable RGB Mode:

Write ovl2c2

Write ovl2c1 (O2EN = 1)

Write fdadr2

Pseudo Code to Disable RGB Mode:

Write ovl2c1 (O2EN = 0)

Clear LCSR1 BS2 bit (LCSR1 = 0x200

Write fbr2 (BRA=BRANCH_AFTER_CURRENT_FRAME, BINT=SET_SR_BS_BIT)

Wait for branc h to complete (LCSR1 == 0x200)

Pseudo Code to Enable 4:2:0 mode:

Write ovl2c2

Write ovl2c1 (O2EN = 1)

Clear LCSR1 IU2 bit (LCSR1 = 0x02000000);

Wait for un de r-run LCSR1 = 0x02000000

Write fdadr2

Write fdadr3

Write fdadr4

Pseudo Code to Disable 4:2:0 mode:

Write ovl2c1 (O2EN = 0)

Clear LCSR1 BS2 bit (L CSR = 0xe00)

Write fbr 2 (BRA=BRANCH_AFTER_CURRENT_FRAME BINT=SET_ SR_ BS_BIT)

Write fbr 3 (BRA=BRANCH_AFTER_CURRENT_FRAME BINT=SET_ SR_ BS_BIT)

Write fbr 4 (BRA=BRANCH_AFTER_CURRENT_FRAME BINT=SET_ SR_ BS_BIT)

Wait for branc h to complete (LCSR1=0xe00)

Status: Plan Fix

E26. USBOTG: Unable to measure duration of Single-Ended Zero (SE0) for

Session Request Protocol (SRP)

Problem: According to On-the- Go Supplem ent to th e USB 2.0 Specif ica tion, we must be able to de tect t hat a

Single-En de d Zero (SE0) c ondition is driven on the USB bus for at least 2 ms before we can

initiate a Session Request Protocol (SRP). See paragraph below.

24 Intel® PXA27x Processor Family Specification Update

Page 25

Errata

Sec. 5.3.2..."A second initial condition for starting a new session is that the B-device must detect

that both the D+ and D- d ata lin es m ust hav e be en low ( SE0) for at l east 2 ms (TB_SE0_S RP min.) .

This ensures that the A-device has detected a disconnect condition from th e device.”...

Software has the abi lity , through reset int errupt, to see when the SE0 state was entered, but it has no

way to determine how long it has been in this state, to determine if the 2 ms requirement has been

met.

Implication: Dual role devices (A and B devices) are required to be able to initiate and respond to an SRP,

therefore, there is the potential that the USB OTG wi ll not pass a USB OTG compliance test.

Workaround: The USB OT G spe c i fi c a ti o n s a ys, in sectio n 5.3.2:

"A second initial condition for start ing a new session is that the B-device must detect that both the

D+ and D- data lines must have been low (SE0) for at least TB_SE0_SRP min. This ensur es that

the A-device has detected a disconnect condition from the device." Currently, TB_SE0_SRP is

specified at 2 msec minimum.

The workaround is to req uire V BUS to be lo w for at least 2 msec, an d assume that th e da ta lines are

low, if VBUS is low. This assumption would work for devices that make the same assumption, but

nothing in the specification requires this.

Status: Pla n Fix

E27. MEMC: Write/Read to/from SDRAM can collide with alternate bus

master mode when MDREFR:ALTREFB is set.

Problem: When ALTREFB is programmed to 1 and an alternate bus master requests the bus, an SDRAM

access in progress may not be allowed to finish before the bus is releas ed. This issue is found in

both fly-by mode and non-fly-by mode.

Currently , th ere is a provision in the specificat ion that ALTREFA and ALTREFB cannot both be set

at the same time. Given the workaround below, this will only allow the refreshes to occur both

before and after an alternate bus master, or only before an alternate bus master.

Implication: This will potentially cause more refreshes than is necessary according to the SDRAM specifi-

cation.

Workaround: Never set MDREFR[ALTREFB]. This will cause a refresh cycle to always occur before allowing

an alternate bus master to be granted the bus.

Status: No Fix

E28. Power Manger: Core hangs during voltage change when there are

outstanding transactions on the bus

Problem: If coprocessor 14 register 7 is written for a volt age change sequ ence (PWRMODE [VC] = 0b1) and

there are outstandin g cor e transactions on the internal bus, the core hangs.

Implication: Unpredictable results can oc cur if th e core h angs.

Workaround: The workaround is to make sure all core tr ans actions are complete and no new core transactions

will attempt to get on the internal bus, then initiate a voltage change by setting PWRMOD E [VC],

then waiting unt il the PWRMODE[VC] bit is cleared. Th e VC bit will be cleared withi n 50ns of the

voltage change in itiation. If software requires the entire vo ltage change sequence to complete, i.e.

no more communication with the external power manager IC, the soft ware must wait until the

PVCR[VCSA] bit is clear.

The following workaround has been tested and will handle all cases.

Intel® PXA27x Processo r Family Specification Update 25

Page 26

Errata

@ WORKAROUND - Core hangs on voltage change at different

@ alignments and at different core clock frequencies

@ To ensure that no external fetches occur, we want to store the next

@ several instructions that occur after the voltage change inside

@ the cache. The load dependency stall near the retry label ensures

@ that any outstanding instruction cacheline loads are complete before

@ the mcr instruction is executed on the 2nd pass. This procedure

@ ensures us that the internal bus will not be busy.

@ -- Begin EnterVoltageChange__asm (void)

.section.text

.global EnterVoltageChange__asm

.align 7 @ align code to fit in one page

EnterVoltageChange__asm:

stmfd sp!, {r4}

mrs r0, CPSR @ disable interrupts

mov r4, r0

orr r0, r0, #0xC0

msr CPSR_c, r0

ldr r0, =0x41300000 @ APB register read and compare

ldr r0, [r0] @ fence for pending slow apb reads

cmp r0, #0

mov r0, #8 @ VC bit for PWRMODE

movs r1, #1 @ don’t execute mcr on 1st pass

mov r2, #0x0A000000 @ uncacheable memory to force memory read

@ CHANGE THIS ADDRESS for your environment

@ MUST be mapped into pagetable prior to

@ this function call

retry:

ldreq r3, [r2] @ only stall on the 2nd pass

cmpeq r3, #0 @ compare causes fence on memory transfers

cmp r1, #0 @ is this the 2nd pass?

mcreq p14, 0, r0, c7, c0, 0 @ write to PWRMODE on 2nd pass only

@ Read the VC bit until it is 0, indicates that the VoltageChange is done.

@ On the first pass, we never set the VC bit, so it will be clear already.

VoltageChange_loop:

mrc p14, 0, r3, c7, c0, 0

tst r3, #0x8

bne VoltageChange_loop

26 Intel® PXA27x Processor Family Specification Update

Page 27

Errata

subs r1, r1, #1 @ update conditional execution counter

beq retry

msr CPSR_c, r4 @ restore interrupts to original state

ldmfd sp!, {r4}

mov pc, lr

.data

@ -- End EnterVoltageChange__asm

Status: No Fix

E29. MMC: MMC unit in SPI mode always waits a minimum of 1 Ncx cycles,

even though the MMC spec dictates that SPI mode CMD9 can have a

minimum of 0 Ncx cycles.

Problem: The MMC unit is not compliant with the MMC Spec 3.2 in SP I Mode.

Version 2.11 of the MMC Spec, in SPI mode, requires 1 or more Ncr cycles between the end of the

response a nd the beginni ng of the data bloc k for CMD9 (SEND_CSD command).

Version 3.1 and 3. 2 o f the MMC S pec , i n SP I mod e, re qui res 0 or mor e N cx cy cle s b etw een t he end

of the respo nse and the beginning of the data block for CMD9 (SEND _CSD command).

The MMC unit always waits a minimum of 1 Ncx cycle between the response and the data block,

therefore, MMC un it is not compliant with the version 3.2 of the Spec.

Implication: TBD

Workaround: TBD

Status: Pla n Fix

E30. SD: SD Controller in SPI mode not receiving data response for CMD9

and CMD10 from some SD Cards

Problem: The SD unit is not compliant with SD Spec 1. 01 in SPI Mode.

Version 1.0 of the SD Spec, in SPI mode, requires 1 or more Ncr cycles between the end of the

response a nd the beginni ng of the data bloc k for CMD9 (SEND_CSD command).

Version 1.01 of the SD Spec, in SPI mode, requires 0 or more Ncx cycles between the end of the

response a nd the beginni ng of the data bloc k for CMD9 (SEND_CSD command).

The SD unit alw a ys waits a minimum of 1 Ncx cycle between the res ponse and the data block,

therefore, the SD unit is not compliant with the 1.01 Spec.

Implication: TBD

Workaround: TBD

Intel® PXA27x Processo r Family Specification Update 27

Page 28

Errata

Status: Plan Fix

E31. MEMC: SDRAM Refresh Commands are issued too often during a

VLIO access while BREQ is asserted.

Problem: During a VLIO access, if BREQ is asserted, the processor issues Refresh Comma nds to SDRAM

too often. This occurs after BREQ is asserted and before BGNT gets asserted. This situation lasts

for as long as VLIO CS is asserted, which can be several microseconds. During this tim e, the

processor is refreshing SDRAM at 100ns interval although programmed interval is ar ound 8usec

(80x difference). Everything goes back to normal after BGNT is released.

Implication: TBD

Workaround: TBD

Status: No Fix

E32. Interrupt Controller: Unexpected exc eption vector when I CCR[D IM]=0

and ICMR=0.

Problem: When ICCR.DIM = 0 and I CMR = 0 an d a di rec t key pr ess i s per formed, th e Inter rupt C ont rol IR Q

Pending (ICIP) register, does not indicate a pending interrupt after comin g up from idle, but the

core attempts to vector to an exception vector address (0x000 to 0x01C).

If ICMR=0x0 and ICCR[ DIM]=0b0 and a direct key press is performed, th en the correct behavior

should be:

After the ke y is press e d, the processor wake s from IDLE, ICPR gets updated, th e ICIP (or ICFP)

does not get upda ted, and the processor should not vector to any vector address (0x00 to 0 x1C).

The incorrect behavior is:

After the ke y is press e d, the processor wake s from IDLE, ICPR gets updated, th e ICIP (or ICFP)

does not get upda ted, but the processor tries to vector to 0x18 (for IRQ handler) or 0x1C (for FIQ

handler), base d on the contents of ICLR.

Keypad and DIM Bit and ICMR test failure:

ICCR = 0x00000000, ICMR = 0x04000000.

KPC = 0x0000 01C 3; KPC[DIE] = 1; KPC[DE] = 1;

KPKDI[DIRECT KEY DEBOUNCE INTERVAL] = 20 (msec).

Implication: TBD

Workaround: Code below disables interrupts to the core before going to Idle and re-enables core interru pts after

returning from Idl e.

IDLE:

.global IDLE

mrs r0, cpsr @ read current processor status register

orr r0, r0, #0xC0 @ disable core interrupts

msr cpsr_c, r0 @ update the current processor status register

mov r0, #1

mcr p14, 0, r0, c7, c0, 0 @ Set IDLE

mrc p14, 0, r0, c7, c0, 0 @ CPWAIT ROUTINE

28 Intel® PXA27x Processor Family Specification Update

Page 29

Errata

mov r1, r1 @ CPWAIT ROUTINE

sub pc, pc, #4 @ CPWAIT ROUTINE

mrs r0, cpsr @ read current processor status register

bic r0, r0, #0xC0 @ enable core interrupts

msr cpsr_c, r0 @ update the current processor status register

mov pc, r14 @ RETURN

Status: No Fix

E33. SSP: TXD line does not tristate when SSP is Slave to Frame

Problem: When the SSP i s a Slav e to F rame (S FRMDIR=1) an d Ma ster of Cl ock (SCLKDIR=0) using the TI

SSP Format, the SSP will not tri-state the TXD line at the end of the last frame when the TTE=1

and TTELP=1 and the SCR>3.

When TI protocol is used, the SSP unit is Slave to F rame and Master/Slave to clock, TTE=1,

TTELP = 1, Data Size = 4.

When a data value of 0xA is transmitted, the last data bit is zero, and when a pullup is applied to

the TXD pin, the line should go high, but it always remains low.

Similarly, when a data value of 0x5 is transmitted, the last data bit is one, and when a pull-down is

applied to the TXD pin, the line should go low, but it always rema ins high.

When TTE=1, TTELP = 0 is used, the TXD line will tristate at the beginning and end of transfer.

Also, the TXD line works fine when the SSP is Master to Frame.

Implication: TBD

Workaround: None.

Status: No Fix

E34. PowerManager: Simultaneous BATT and VDD faults results in going

to DeepSleep mode twice.

Problem: When in any m ode, asserting simultan e ous BATT_FAULT and VDD_FAULT signals, and while

BIDAE is not equ al to VIDAE, requires the user to go to DeepSleep twice, once automatically due

to one of the xIDAE bits being clear, and once via s oftware due to one of the xIDAE bits being set.

Another obs e rvation is th a t a ve ry short (approx. 332usec) nRESET_OUT assertion occurs

followed by a bootup (with no change to RCSR).

Implication: TBD

Workaround: PMCR[BIDAE] and PMCR[ VIDAE] must be identical.

Status: No Fix

E35. CORE: Non-branch instruction in vect or table may execut e twice after

a thumb mode exception

Problem: If an exception occurs in thumb mode and a non-branch instruction is executed at the corr e-

sponding exception vector, that instr uction may execute twice. Typically, inst ructions located at

exception vectors must be br anch instructions which go to the appr opriate handler, but the ARM

architecture allows the FIQ ha ndler to be placed directly at the FIQ vector (0x0000001c/

0xffff001c) without requiring a branch.

Intel® PXA27x Processo r Family Specification Update 29

Page 30

Errata

Implication: The first instruction in thumb mode of a FIQ handler may be executed twice if it is not a branch

instruction.

Workaround: If a no-op is placed at the beginning of the FIQ handler, the no-op will ex ecute twice and no

incorrect behavior will result. If a branch instruction is placed at the beginning of the handler, it

will not be executed twice.

Status: No Fix

E36. UART: UART does not correctly indicate a Framing Error Interrupt in

DMA mode.

Problem: When DMA is enabled and a "Framing Er ror" occurs, the UART generates an interrupt, but the IIR

register does not show any pending interr upts (IIR[nIP]=0b1).

Reading the registers does not clear the interrupt. The UART will continuous ly interrupt the

CORE.

If the RX FIFO is emptied until th ere i s only 4 byt es of da ta lef t in the F IFO, the U ART will finally

generate a RLS interrupt showing a "framing" error.

The UART handles errors differently in DMA mode. When an err or occurs the error gets tagged in

the rx fifo with the erroneous byte. In interrupt mode, the error is flagged (processor interrupted)

when the erro neou s byte is rea d out of the bo tto m of the fi fo. I n DMA mode , the erro r is fl a gge d as

soon as it is detected. In DMA mode, the UART correctly interrupts the pr ocessor wh en the error is

first detected but it does not upd ate the II R register until th e error is read out of the FIFO. Thus, the

processor is interrupte d with no interr upt pending. The c orrect operation is to both interrupt the

processor and update the IIR register when the error is detected.

Implication: The UART generates an interrupt, but the IIR register does not show any pending interrup ts.

Workaround: If an interrupt is genera ted, but the II R re gister does not show any pending interrupts, then read

data out of the RX FIFO until either it is empty or a valid interrupt is generated. The e rror interrupt

to the core will not cle ar until the erroneous by te is read out of the RX FIFO.

Status: No Fix

E37. CLOCKS: System Hangs when enabling RUN/TURBO switching at

520MHz

Problem: The system will hang when performing switching from Run Mode frequency to Turbo Mode

frequency.

The test flow is as follows:

—Bootup

— Perform a Frequency / Voltage change to L=16, N=2.5, A=1, B=1, K0DB4=1,

K1DB2=1,K2DB2=1. This gives core = 208MHz (run mode), Sys Bus = 208MHz, an d

MEMC = 208MHz. Note the Turbo bit (T) is not set yet.

— Display a code of “0xFFAA0000”

— Go to Turbo mode by setting the Tur bo bit.

— Display a code of “0xFFBB0000”

30 Intel® PXA27x Processor Family Specification Update

Page 31

This test interm ittently hangs afte r the “FF AA” code and before the “FF BB” code. Intermittently

means that the test can sw itch back and forth bet ween T u rbo mode and Run mode and a failu re will

most likely oc c ur between 10,000 iterations a nd 400,000 itera tions.

Implication: TBD

Workaround: Workaround for going from RUN (208MHz) to TURBO (520MHz):

Set CCCR[CPDIS] // Disable the Core PLL

Clear CCCR[PPDIS] // Enable the Peripheral PLL

Set CLKCFG[F] // Initiated a Frequency Change

// Core freq = 13MHz, Peripherals = normal freq (PPLL = 312MHz)

Set CCCR[PLL_Early_EN] // Allow the Core PLL to ramp up early

Wait for CCSR[CPLCK] to set and CCSR[PPLCK] to set.

Clear CCCR[CPDIS] // Enable the Core PLL

Set CLKCFG[F] and Set CLKCFG[T] // Initiate a Frequency Change

// Core is now running in Turbo mode @ 520Mhz

No Workaround needed for switching from TURBO (520MHz ) to RUN (208MHz). Switching

from TURBO to RUN works fine by clearing CLKCFG[T].

Errata

Estimated L a te ncy Timings:

From RUN to 13M mode is about 45us

From 13M to PLL lock is ab ou t 15us

From P L L lo c k to TURBO is about 10 0 us

Total latency is about 160us, where 15us of the ti me you can execute code while the core is

operating in 13MHz mode. This time can increase if the PLL lock time changes.

If you choose to go from 208MHz RUN mode, into a dif ferent prod uc t point, such as 416MHz

Turbo, then switch into 520MHz Tur bo, the latency is about 230us.

Status: No Fix

E38. CLOCKS: System Hangs when enabling HalfTurbo Switching

Problem: The system will hang when switching into and out of HalfTurbo, i.e. when going from Run mode

to HalfTurbo mode and from Turbo mode to HalfTur bo mode. The failure does not occur when

only switching from Run mode to Turbo mode and back.

This failure occurs on, but not limited to, the L=8, N=3, T=1, HT=1, A=1, B=1 product point (i.e.

Core = 156MHz, System Bus = 104MHz, MEMC = 104MHz)

Failures on thi s pr oduct point are intermittent. Intermittent means that on powerup, the test will

either ru n or ha ng. If the fi rs t cha nge to Half T u rbo wor ks , then the test wil l c ont inue to ru n withou t

failure. If th e first change to HalfTurbo fails, then the test hangs, and nothing else c an be done.

Implication: TBD

Workaround: Do not use HalfTurbo Mode. If you wish to run the core at a HalfTurbo Frequency, then perform a

full fre quency change to the desired frequency. For example, if you wish to run the core at 156

MHz, then set L= 8, N=1.5, T=1, HT=0, A=1, B=1.

Intel® PXA27x Processo r Family Specification Update 31

Page 32

Errata

Status: No Fix

E39. MEMC: Memory Controller hangs when entering Self Refresh Mode.

Problem: If software manually puts SDRAM int o Self Refresh Mode, then the memory controller will not

perform any more activity.

Here are the steps to recreate the issu e:

1) MDREFR[K1RUN] = 1 // make sure SDCLK1 is running.

2) MDREFR[K1FREE] = 0 // turn off free running.

3) MDREFR[SLFRSH] = 1 // enter self refresh mode.

4) wait until enter Self Refresh mode.// delay approximately 2 usec.

5) Any non-SDRAM activity will not be performed by the memory controller

Implication: Will not be able to access external non-SDRAM memories after the SDRAMs are put into Self

Refresh Mode.

Workaround: The user is allowed to assert the S L FRSH bit to the memory controller placing the SDRAMs in

Self Refresh Mode, if and only if, the very next transaction the memory controller receives is the

deassertion of the SLFRSH bit. Nothing else is permitted on the memory controller after the

assertion of the SLF RSH bi t, and be fore th e deasser tio n of the SLFR SH bit . Esse ntia lly, this means

that the user may perform internal transfers that do not eff ect the memory controller, such as reads

from Instruction Cache, r eads/w rites to Data Cache , reads/ writes to SRAM, r eads/w rites to intern al

peripherals, but cannot perf orm external accesses such as VLIO or PCMCIA

Status: No Fix

E40. SDIO: SDIO Devices Not Working at 19.5 Mbps

Problem: SD/SDIO contro ller can only suppor t up to 9.75 Mbps data transfer rate for SDIO card. However,

the SD/MMC car d works fine at 19.5 Mbps clock ra te.

The error reason is "HandleEndCommandInterrupt: respon se f or command 52, contains a CRC

error". Other commands ma y re spond with a CRC error also.

Many cards we re te sted and some fail and some pa ss a t 19.5 Mbps, however all cards pa ss at 9.75

Mbps.

T est was conducted under BSP 3.00.029, V2 Beta that supports full SDIO functionality. Test was

conducted in both 1-bit and 4-bit mode and bot h modes fail. Test was conduct e d on a Mainstone

board.

The Mainstone board has an analog switch in the SDI O path. This switch, according to the spec,

can cause up to 18ns of delay. The delay causes the clock to be later at the card and then the data

gets delayed going back to the proces so r. According to the SD spec, the output delay maximum is

15ns @ 25MHz, or 5ns of setup time be fore the rising edge of the clock. This analog switch was

taken out of the circuit, however, cards were still failing.

Implication: TBD

Workaround: Slow the speed of the interface down until the card passes. This speed could be as low as 9. 75

Mbps.

Status: Plan Fix

32 Intel® PXA27x Processor Family Specification Update

Page 33

Errata

E41. AC97: Command Done bit is never set when data is written in slot12

Problem: The “Codec Done Bit” does not get set upon completion of a write to register 0x54 in Modem IO

Space. Moreover, no AC97 controller interrupt will occur to the CPU, tel ling the software that a

register writ e to 0x54 is complete.

Implication: TBD

Workaround: Software must po ll the CAIP bit to determin e if a write was accomplished.

Status: No Fix

E42. SD/MMC: SD/MMC c o ntroller CRC e r r or s with s ome SD/MMC cards

Problem: In MMC/SD/S DIO ca rds, not i n SPI mode , CMD2 , CMD9, and CMD1 0 use an R2 typ e Respons e.

An R2 Response is a 136 bit Response, where:

— [135:128] is 0x3F

— [127:1] is the regis ter being read, where bits [7 :1] is the CRC for bits [127:8] of the

register

— [0] is the END bit, which is always 1.

The controller ignores bits [135:128] for CRC checking.

The controller shou ld use bits [127: 1] for CRC checking. The pro blem is that the controlle r is using

bits [126:1] for CRC che ckin g. If bit 127 is a 0, the n there is no pro blem, becau se the CRC ch ecker

is always initialized to 0. However, if bit 127 is a 1, then a response CRC error will occur.

Implication: TBD

Workaround: If a Response CRC error occurs for CMD2, CMD9, or CMD10, and bit 127 is a 1, ignore the erro r.

Status: Pla n Fix

E43. USBH: There is no Individual Power Sense Polarity bit for each Host

Port. The Power Sense Polarity bit controls the polarity for all three

Host Por ts.

Problem: Overcurrent indicat or signals for Host Port 1 and 2 are controlled externally by USBHPWR[2:1].

Overcurrent indicator signal for Host Port 3 is not pinned out to an external pin. This signal is

internally tied to ground.

The Power Sense Polarity bit (UHC HR[ PSPL]) controls the polarity of the Over cur rent indicator

signals for all three Host Ports .

If a usage mo del requires that the polarity o f the Host Port 1 or 2 be active low, then this will cause

a false ove rc urrent indication to occur on Host Port 3.

Also, software cann ot ignore overcurrent on just Host Port 3. I gnoring overcurrent can only be

done across all three ports by setting UHCRHDA[NOCP].

The intended silicon fix is to disconnect the Host Port 3 Overcur ren t indicator signal from internal

ground and connect it to the Power Sense Polari ty (PSPL) bit . This guarante es that Hos t Port 3 will

never see an overcurrent condition.

Note that when switching PSP L, a small gl itch might b e seen on the Overcur rent in dicator for Host

Port 3. This should not be an issue since the usa ge model for PSP L is that it is desi gne d to be set

statically at in itialization time.

Intel® PXA27x Processo r Family Specification Update 33

Page 34

Errata

Implication: TBD

Workaround: TBD.

Status: Plan Fix

E44. KBD: Keypress wakeup from Standby mode is not reliable

Problem: When the processor is put into Standby mode by correctly configuring the PKWR register, a valid

keypress doe s not reliably bring the proces sor out of Standby mode.

The failure rate is less than 10 times out of 100 attempts to wake up from Standby mode via a key

press.

Implication: TBD

Workaround: Do not put the processor in to Standby mode d uring keypress activity.

Status: No Fix

E45. USBH: USB Host Port 3 in Transceiverless Mode may not work

correctly with an external device.

Problem: The USB Host Port 3, when put into Transceiverless Mo de by setting UP3OCR [CFG] = 2, expects

a certain behavior from the attached ex ternal device.

While the device is in receive mode, i.e. while USB_P3_2 (OE_n) is deasserted, the Host Port 3

expects the device t o tran smit a steady sta te “1 ” on t he USB_P 3_6 (VPO) pin and a st eady s tate “0 ”

on the USB_P3_4 (VMO) pin.

If the device does not comply to this restriction, then please use a 2-i npu t OR gate, with one input

connected to OE_n, the other inp ut conn ected to VPO fro m the device, and the out put connected to

USB_P3_6 (VPO) of the processor.

The intended silicon fix is as follow s:

Remove the "Host Port 2 D+ Pull Up Bypa ss Enable" section of the Develo pe r’s Manual. The D+

Pull Up Bypa ss Enabl e is perm anentl y t urned of f. In o ther wor ds, the dyn amic D + p ullup r esisto r is

always enabled as specified by USBOTG.

This bit position, UP2OCR[ 6], is now UP2OCR [VPMBlockEnbN].

When VPMBlockEnbN = 0b0 (new functionality):

• When the USB is in transceiverless mode (UP3O CR[CF G] = 0x2), then USB_P3_6 (VPO)

and USB_P3_4 (VMO) are ignored by USB Host Port 3 when USB_P3_2 (OE_n) is

deasserted.

• However, thi s w ill cause the following restrictions:

— USB Host Port 3 in T rans ceiverl ess Mode can on ly be con nected to a fast speed ( 12Mbps)

device.

— The USB device cannot use the common method of indicating a connec t by pulling the

VPO line high, or disconnec t by pulling both VPO and VMO lo w. The USB device must

use another method of indicating a connect/disconnect to th e Host Port 3, such as using

another GPIO, or performing a read to the external device’s status register.

When VPMBlockEnbN = 0b1 (original functionality):

34 Intel® PXA27x Processor Family Specification Update

Page 35

Errata

• When the USB is in transceiverless mode (U P3 OCR[ CFG] = 0x2), then USB_P3_6 (VPO)

and USB_P3_4 (VMO) are not ignored by USB Host Port 3 when USB _P3_2 (OE_n) is

deasserted.

• However, this will allow the following conditions :

— USB Host Port 3 in Transceiverless Mode can be connected to a fast speed (12Mbps)

device or slow speed (1.5Mbps) devi c e .

— The USB device can use the common meth od of i ndicatin g a fast speed device con nection

by pulling the VPO line high, or a slow speed devi ce connecti on by pu lling the VMO line

high, or dis c onnect by pulling both VPO and V MO low.

Implication: TBD

Workaround: Use a 2-input OR gate, with one input connected to OE_n from the device, the other input

connected to VPO from the device, and the out put connected to USB_P3_6 (VPO) of the

processor.

Status: Pla n Fix

E46. SD/MMC: SPI mode commands fail even on cards that are compatible

with SPI spec 1.0

Problem: When the SD/MMC controller is put into SPI mode, all read commands where data is transmitted

in the DATA token, will fail, even if the card is SPI spec 1.0 compliant.

For example:

• C0 step silicon: