Page 1

Intel® PXA27x Processor Family

Design Guide

May 2005

Order No. 280001-002

Page 2

Contents

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S

TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY

EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES

RELATING T O FITNESS FOR A PARTICULAR PURPOSE, MERCH ANTABILITY, OR INFRINGEMENT OF ANY PATENT , COPYRIGHT, OR OTHER

INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the

presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by

estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facili ty appl ica tions.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled

platforms may require licenses from various entities, including Intel Corporation.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the

license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a

commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this

document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may

be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact the local Intel sales office or the distributor to obtain the latest specifications and before placing the product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2005

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic,

DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel

NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel Quick Capture T echnology , Intel SingleDriver, Intel SpeedStep, Intel

StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo,

NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at

Your Command, ProShare, Quick Capture Technology , RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress,

The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, VTune, and Wireless Intel SpeedStep Technology are

trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

PXA27x Processor Family may contain design defects or errors known as errata which may cause the product to deviate from published

ii Intel® PXA27x Processor Family Design Guide

Page 3

Contents

Contents

Part I

1 Introduction to Part I ...............................................................................................................I: 1-1

1.1 Document Organization and Overview...........................................................................I: 1-1

1.2 Functional Ov erv ie w ............ .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... ...I: 1-2

1.3 Package Introduction......................................................................................................I: 1-3

1.4 Signal Pin Descriptions...................................................................................................I: 1-4

2 PCB Design Guidelines...........................................................................................................I: 2-1

2.1 Intel

2.2 General PCB Ch ar ac ter ist ics.................. .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... ...I: 2-1

2.3 Power Supply Decoupling Requirements .....................................................................I: 2-12

2.4 Thermal Cons ide ra tio ns....... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... .I: 2-12

2.5 Package to Board Assembly Process...........................................................................I: 2-12

2.6 Silicon Daisy Chain (SDC) Evaluation Units.................................................................I: 2-12

2.7 Handling: Shipping Media.............................................................................................I: 2-12

2.8 Preconditioning and Moisture Sensitivity......................................................................I: 2-13

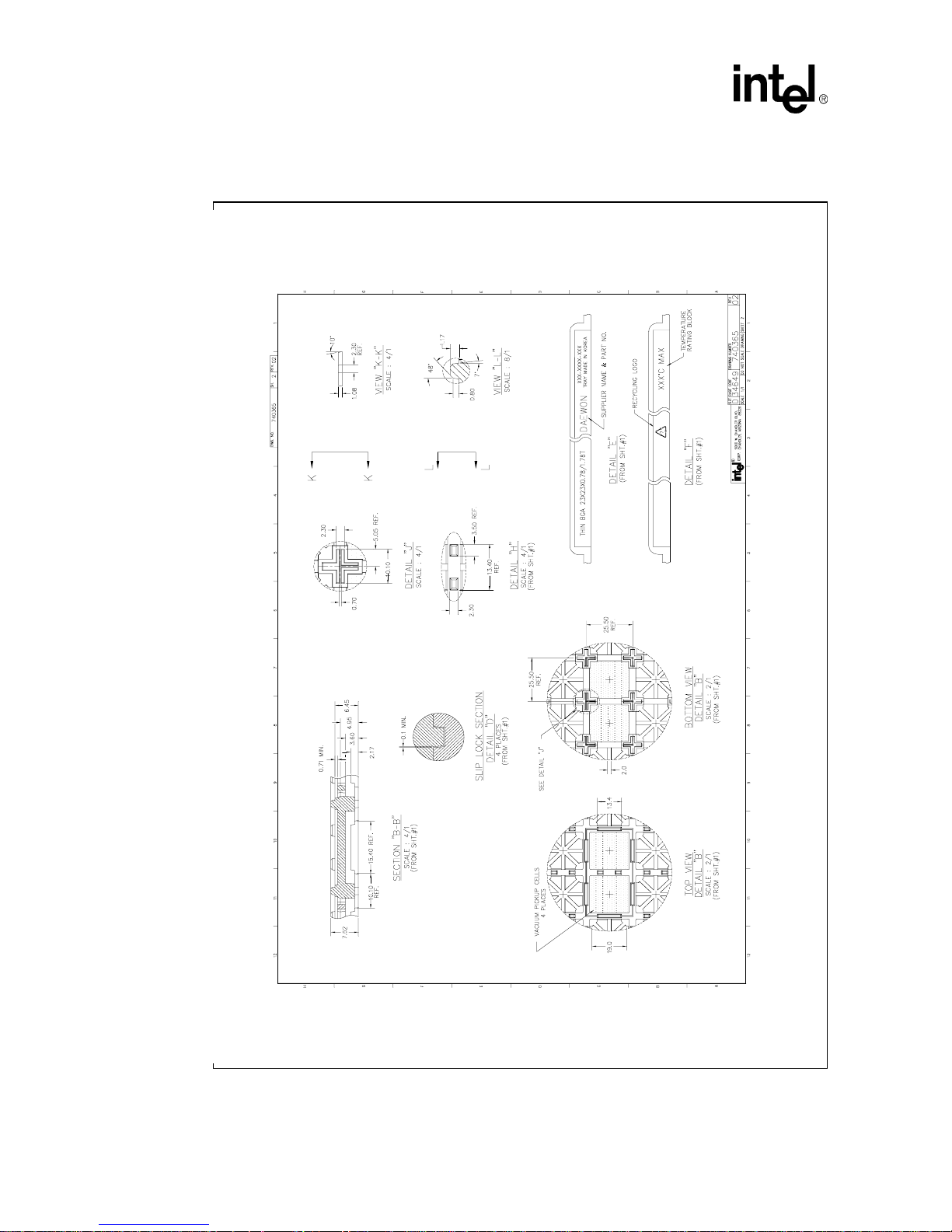

2.9 Tray Specifications .......................................................................................................I: 2-13

®

Flash Memory Design Guidelines .........................................................................I: 2-1

2.2.1 PCB Layer Assignment (Stackup) .....................................................................I: 2-2

2.2.2 PCB Compone nt Pl ace m en t.................. .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... ...I: 2-4

2.2.3 PCB Escape Routing.........................................................................................I: 2-7

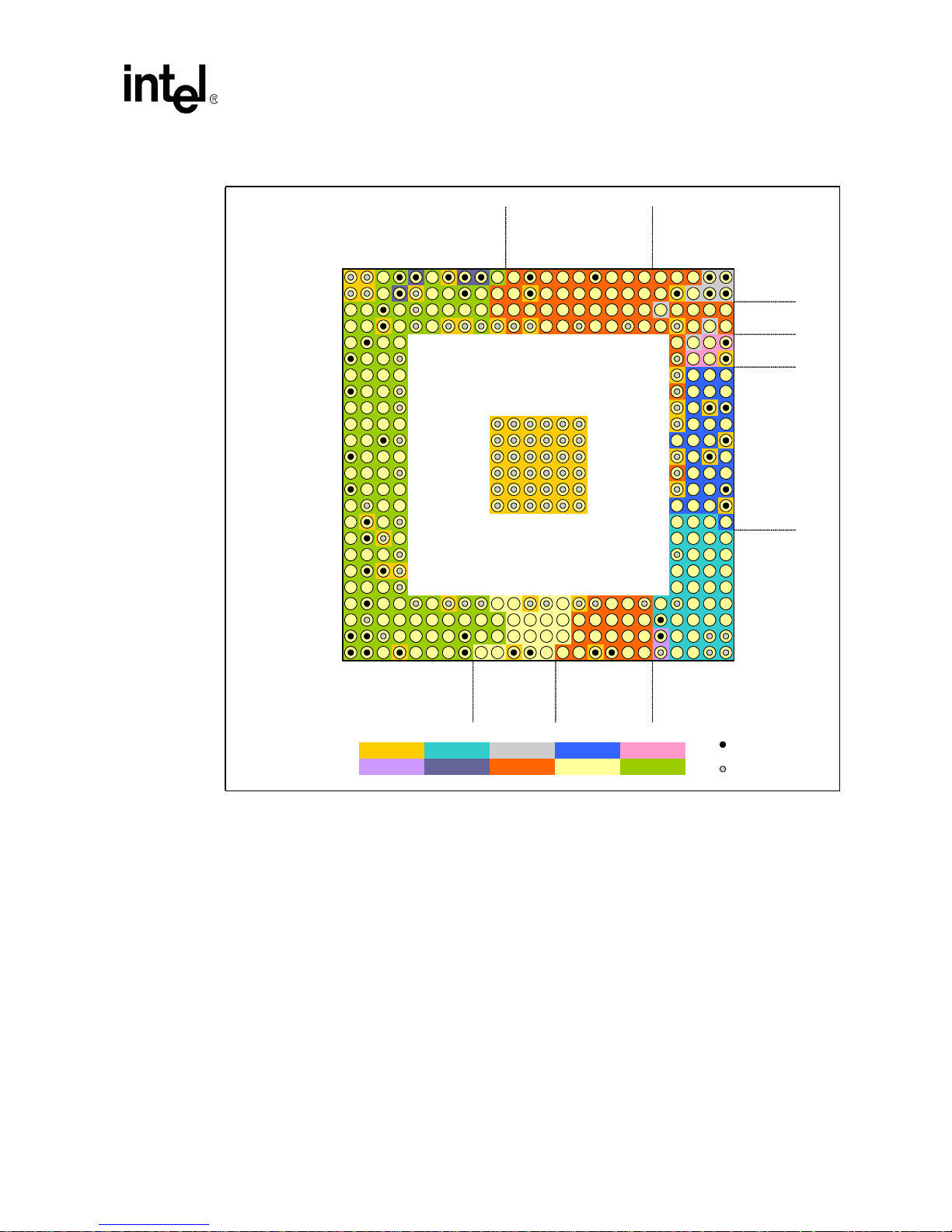

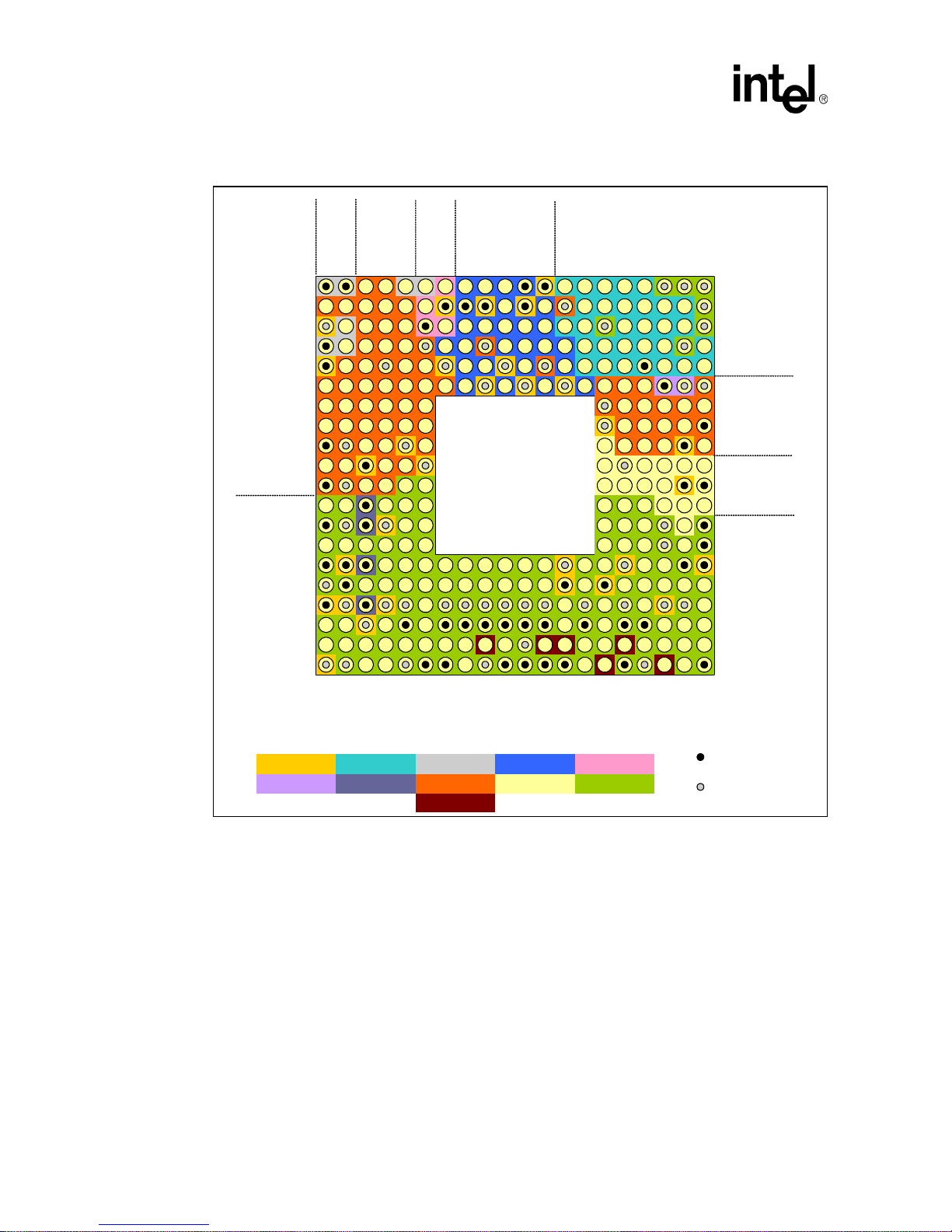

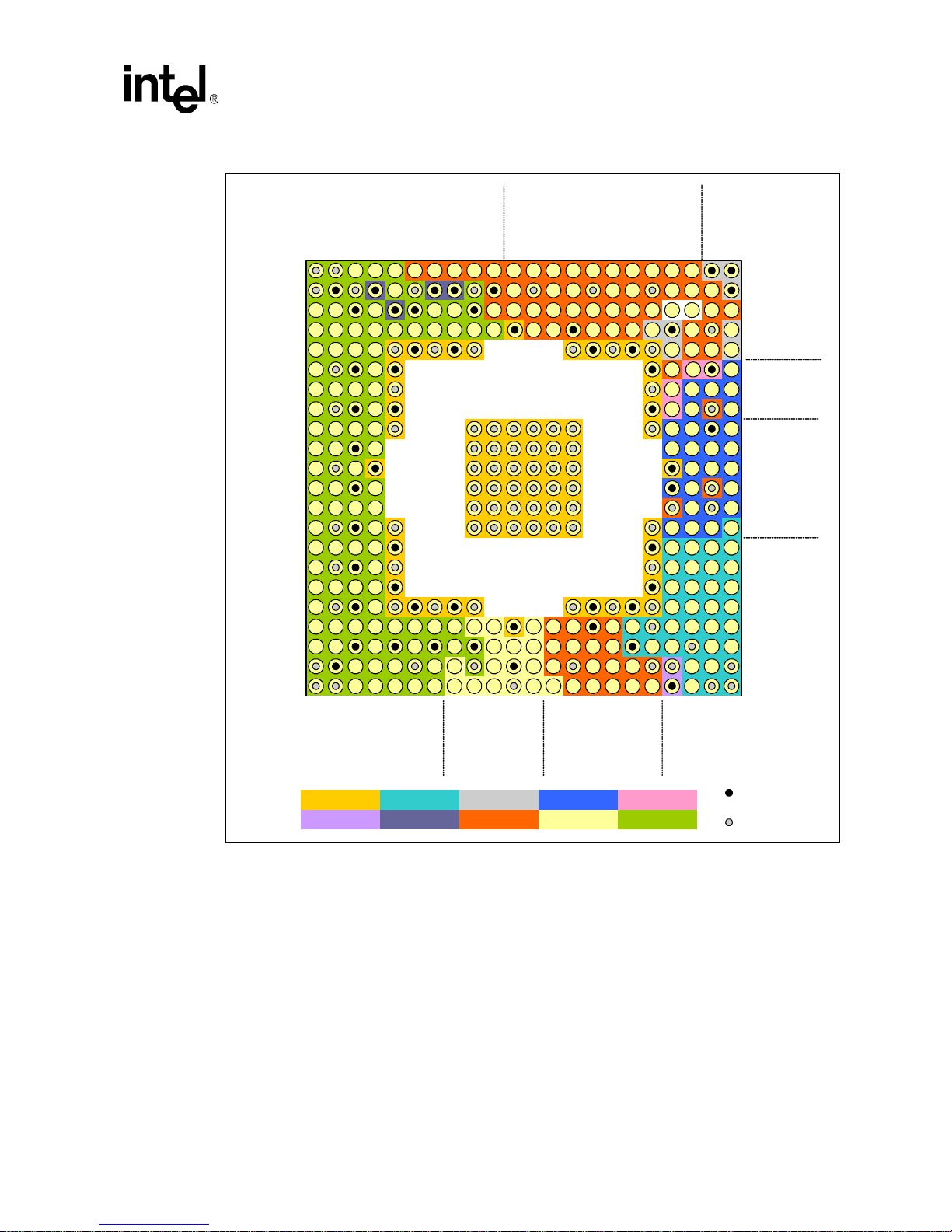

2.2.3.1 VF-BGA Escape Routing ...................................................................I: 2-8

2.2.3.2 FS-CSP Escape Routing ...................................................................I: 2-9

2.2.3.3 PBGA Escape Rout ing............... ... .... ....................... .... .... .... ... .........I: 2- 10

2.2.4 PCB Keep-out Zo ne s................. .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... .I: 2-11

2.2.5 Recommended Mobile Handset Dimensions...................................................I: 2-11

3 Design Chec k Lis t ...................................................................................................................I: 3-1

4 Mixed Voltage Design Considerations ..................................................................................I: 4-1

4.1 Overview.........................................................................................................................I: 4-1

4.2 Required Power Supplies ...............................................................................................I: 4-1

4.3 Example Power Supply Utilizing Minimal Regulators .....................................................I: 4-2

4.4 Cautions..........................................................................................................................I: 4-4

5 Power Measurements..............................................................................................................I: 5-1

5.1 Overview.........................................................................................................................I: 5-1

5.2 Measurement Guidelines................................................................................................I: 5-1

5.2.1 Measure Voltage Across a Series Resistor .......................................................I: 5-1

5.2.2 Measure Current Directly with a Current Meter in Series ..................................I: 5-1

5.3 Achieve Minimum Power Usage During All Power Modes .............................................I: 5-2

5.4 Achieve Minimum Power Usage During Deep Sleep .....................................................I: 5-2

5.5 Achieve Minimum Power Usage During Sleep...............................................................I: 5-3

5.6 Achieve Minimum Power Usage During Standby ...........................................................I: 5-3

5.7 Achieve Minimum Power Usage During Idle/13M/Run/Turbo ........................................I: 5-3

Intel® PXA27x Processor Family Desig n Guide iii

Page 4

Contents

Part II

1 Introduction to Part II .............................................................................................................II: 1-1

2 Package and Pins...................................................................................................................II: 2-1

3 Clocks and Power Interface...................................................................................................II: 3-1

3.1 Overview........................................................................................................................II: 3-1

3.2 Signals...........................................................................................................................II: 3-1

3.2.1 Clock Interfac e Sig na ls............. .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 3-1

3.2.2 Power Manager Interface Control Signals........................................................II: 3-2

3.2.3 Power Enable (PWR_EN).................................................................................II: 3-3

3.2.3.1 System Power Enable (SYS_EN).....................................................II: 3-3

3.2.3.2 Power Manager I2C Clock (PWR_SCL) ...........................................II: 3-3

3.2.3.3 Power Manager I2C Data (PWR_SDA) ............................................II: 3-3

3.2.3.4 nVDD_FAULT...................................................................................II: 3-3

3.2.3.5 nBATT_FAULT .................................................................................II: 3-4

3.3 Block Diagram ...............................................................................................................II: 3-4

3.4 Layout Notes..................................................................................................................II: 3-6

3.5 Modes of Ope rat ion s .......... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 3-6

3.5.1 Clock Interfac e.... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 3-6

3.5.1.1 Using the On-Chip Oscillator with a 32.768-KHz Crystal..................II: 3-7

3.5.1.2 Using an External 32.768- KH z Clo ck............... .... ... .... .... .... .... ... .... ...II: 3-7

3.5.1.3 Using the On-Chip Oscillator with a 13.000-MHz Crystal .................II: 3-7

3.5.1.4 Using an External 13.00-MHz Clock.................................................II: 3-8

3.5.2 Power Interface.................................................................................................II: 3-8

3.5.2.1 Power Supplies.................................................................................II: 3-8

4Internal SRAM.........................................................................................................................II: 4-1

4.1 Overview........................................................................................................................II: 4-1

4.2 Signals...........................................................................................................................II: 4-1

4.3 Block Diagram ...............................................................................................................II: 4-1

4.4 Layout Notes..................................................................................................................II: 4-2

5 DMA Controller Interface .......................................................................................................II: 5-1

5.1 Overview........................................................................................................................II: 5-1

5.2 Signals...........................................................................................................................II: 5-1

5.3 Block Diagram ...............................................................................................................II: 5-2

5.4 Layout Notes..................................................................................................................II: 5-2

5.5 Modes of Ope rat ion .................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 5-3

5.5.1 Fly-By DMA Transfers ......................................................................................II: 5-3

5.5.1.1 Signals..............................................................................................II: 5-3

5.5.1.2 Block Diagram........ ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 5-4

5.5.1.3 Layout Notes.....................................................................................II: 5-4

5.5.2 Flow-Through DMA Transfers ..........................................................................II: 5-5

5.5.2.1 Signals..............................................................................................II: 5-5

5.5.2.2 Block Diagram........ ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 5-5

5.5.2.3 Layout Notes.....................................................................................II: 5-6

6 System Memory Interface......................................................................................................II: 6-1

6.1 Overview........................................................................................................................II: 6-1

6.2 Signals...........................................................................................................................II: 6-3

iv Intel® PXA27x Processor Family Design Guide

Page 5

Contents

6.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... ..II: 6-5

6.4 Memory Contr oll er La yo ut No te s . .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... ..II: 6-6

6.4.1 Memory Controller Routing Guidelines for 0.5mm and 0.65 mm Ball Pitch......II: 6-6

6.4.1.1 System Bus Recommended Signal Routing Guidelines

(Excluding SDCLK<x> and SDCAS).................................................................II: 6-6

6.4.1.2 SDCLK and SDCAS Recommended Signal Routing Guidelines......II: 6-7

6.4.1.3 Minimum Board Stack-up Configuration used for Signal Integrity ....II: 6-8

6.5 Modes of Operation Overview .......................................................................................II: 6-9

6.5.1 SDRAM Interface..............................................................................................II: 6-9

6.5.1.1 SDRAM Signals ................................................................................II: 6-9

6.5.1.2 SDRAM Memory Block Diagram.....................................................II: 6-11

6.5.1.3 SDRAM Layout Notes.....................................................................II: 6-12

6.5.2 Flash Memory Interface (Asynchronous/Synchronous)..................................II: 6-15

6.5.2.1 Flash Memory Signals ....................................................................II: 6-15

6.5.2.2 Flash Block Diagram.......................................................................II: 6-16

6.5.2.3 Flash Layout Note...........................................................................II: 6-16

6.5.3 ROM Interface ................................................................................................II: 6-17

6.5.3.1 ROM Signals...................................................................................II: 6-17

6.5.3.2 ROM Block Diagram .......................................................................II: 6-18

6.5.3.3 ROM Layout Notes .........................................................................II: 6-18

6.5.4 SRAM Interface ..............................................................................................II: 6-18

6.5.4.1 SRAM Signals.................................................................................II: 6-19

6.5.4.2 SRAM Block Diagram ................ ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 6-20

6.5.4.3 SRAM Layout Notes .......................................................................II: 6-20

6.5.5 Variable Latency Input/Output (VLIO) Interface..............................................II: 6-21

6.5.5.1 VLIO Memory Signals.....................................................................II: 6-22

6.5.5.2 VLIO Block Diagram .......................................................................II: 6-23

6.5.5.3 VLIO Memory Layout Notes............................................................II: 6-23

6.5.6 PC Card (PCMCIA) Interface..........................................................................II: 6-23

6.5.6.1 PC Card Signals .............................................................................II: 6-25

6.5.6.2 PC-Card Block Diagr am s...................... .... .... .... ... .... .... .... .... ... .... ....II: 6-26

6.5.6.3 PC Card Layout Notes....................................................................II: 6-29

6.5.7 Alternate Bus Master Interface .......................................................................II: 6-29

6.5.7.1 Alternate Bus Master Signals..........................................................II: 6-31

6.5.7.2 Alternate Bus Master Block Diagram..............................................II: 6-32

6.5.7.3 Alternate Bus Master Layout Notes ................................................II: 6-32

7LCD Interface..........................................................................................................................II: 7-1

7.1 Overview........................................................................................................................II: 7-1

7.2 Signals...........................................................................................................................II: 7-2

7.3 Schematics/Block Diagram............................................................................................II: 7-3

7.4 Layout Notes..................................................................................................................II: 7-3

7.4.1 Contrast Voltage...............................................................................................II: 7-3

7.4.2 Backlight Inver ter ........................... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... ..II: 7-4

7.4.3 Signal Routing and Buffering............................................................................II: 7-4

7.4.4 Panel Connector...............................................................................................II: 7-5

7.5 Modes of Operation Overview .......................................................................................II: 7-6

7.5.1 Passive Monoc hr om e Sin gl e-S ca n Mo d e............. .... .... .... ... .... .... .... .... ... .... .... ..II: 7-6

7.5.1.1 Signals ..............................................................................................II: 7-6

7.5.1.2 Schematics/Block Diagram...............................................................II: 7-7

7.5.1.3 Layout Notes....... ... ....................... .... .... .... .... ....................... ... .... .... ..II: 7-7

7.5.2 Passive Monochrome Single-Scan Double-Pixel Mode....................................II: 7-8

Intel® PXA27x Processor Family Design Guide v

Page 6

Contents

7.5.2.1 Signals..............................................................................................II: 7-8

7.5.2.2 Schematics / Block Diagram.............................................................II: 7-9

7.5.2.3 Layout Notes.....................................................................................II: 7-9

7.5.3 Passive Mono ch ro me Dua l-S ca n Mo de ....... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 7-9

7.5.3.1 Signals..............................................................................................II: 7-9

7.5.3.2 Schematics / Block Diagram...........................................................II: 7-10

7.5.3.3 Layout Notes...................................................................................II: 7-11

7.5.4 Passive Color Single-Scan Mode ...................................................................II: 7-11

7.5.4.1 Signals............................................................................................II: 7-11

7.5.4.2 Schematics/Block Dia gr am........... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 7-12

7.5.4.3 Layout Notes...................................................................................II: 7-12

7.5.5 Passive Colo r Dua l-S ca n Mo de........................... .... .... .... .... ... .... .... .... .... ... .... .II: 7-12

7.5.5.1 Signals............................................................................................II: 7-12

7.5.5.2 Schematics / Block Diagram...........................................................II: 7-14

7.5.5.3 Layout Notes...................................................................................II: 7-14

7.5.6 Active Color 12-bit per pixel Mode..................................................................II: 7-14

7.5.6.1 Signals............................................................................................II: 7-14

7.5.6.2 Schematics / Block Diagram...........................................................II: 7-15

7.5.6.3 Layout Notes...................................................................................II: 7-16

7.5.7 Active Color, 16-bit per pixel Mode.................................................................II: 7-16

7.5.7.1 Signals............................................................................................II: 7-17

7.5.7.2 Schematics / Block Diagram...........................................................II: 7-17

7.5.7.3 Layout Notes...................................................................................II: 7-18

7.5.8 Active Color, 18-bit per pixel Mode.................................................................II: 7-18

7.5.8.1 Signals............................................................................................II: 7-19

7.5.8.2 Schematics / Block Diagram...........................................................II: 7-19

7.5.8.3 Layout Notes...................................................................................II: 7-20

7.5.9 Smart Panel....................................................................................................II: 7-20

7.5.9.1 Signals............................................................................................II: 7-21

7.5.9.2 Schematics / Block Diagram...........................................................II: 7-21

7.5.9.3 Layout Notes...................................................................................II: 7-22

8 SSP Port Interface ..................................................................................................................II: 8-1

8.1 Overview........................................................................................................................II: 8-1

8.2 Signals...........................................................................................................................II: 8-2

8.3 Block Diagram ...............................................................................................................II: 8-3

8.3.1 Standard SSP Configuration Scheme ..............................................................II: 8-3

8.3.2 External Clock Source Configuration Scheme..................................................II: 8-4

8.3.3 External Clock Enable Configuration Scheme..................................................II: 8-5

8.3.4 Internal (to PXA 27 x Pro ce ss or ) Cloc k En ab le Co nf igu ra tio n De sig n ..... ... .... ...II: 8-5

8.4 Layout Notes..................................................................................................................II: 8-6

9 Inter-Integrated Circuit (I2C)..................................................................................................II: 9-1

9.1 Overview........................................................................................................................II: 9-1

9.2 Signals...........................................................................................................................II: 9-1

9.3 Schemati c/B lo ck Dia g ram............... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ...II: 9-2

9.3.1 Digital-to-Analog Converter (DAC) ...................................................................II: 9-2

9.3.2 Other Uses of I2C.............................................................................................II: 9-3

9.3.3 Pull-Ups and Pull-Downs..................................................................................II: 9-4

9.4 Layout Notes..................................................................................................................II: 9-4

vi Intel® PXA27x Processor Family Design Guide

Page 7

Contents

10 UART Interfaces............. .... .... ... .... .... .... .... ... .... .... .... ....................... .... .... ... .... .... ...................II: 10-1

10.1 Overview......................................................................................................................II: 10-1

10.2 Signals.........................................................................................................................II: 10-2

10.3 Types of UARTs ..........................................................................................................II: 10-3

10.3.1 Full Function UART ........................................................................................II: 10-3

10.3.1.1 Full Function UART Signals............................................................II: 10-3

10.3.1.2 FFUART Block Diagr am ........................... .... .... ... .... .... .... .... ... .... ....II: 10-4

10.3.1.3 FFUART Layout Notes....................................................................II: 10-4

10.3.2 Bluetooth UART..............................................................................................II: 10-5

10.3.2.1 Bluetooth UART Sig na ls ................... .... .... .... .... ... .... .... .... .... ... .... ....II: 10-5

10.3.2.2 Bluetooth UART Block Diagram......................................................II: 10-5

10.3.3 Standard UART ..................... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 10-6

10.3.3.1 Standard UART Signals..................................................................II: 10-6

10.3.3.2 Standard UART Block Diagram ......................................................II: 10-6

11 Fast Infrared Interface.............. .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 11-1

11.1 Overview......................................................................................................................II: 11-1

11.2 Signals.........................................................................................................................II: 11-1

11.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 11-2

12 ‘USB Client Controller ... .... .... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 12-1

12.1 Overview......................................................................................................................II: 12-1

12.2 Signals.........................................................................................................................II: 12-1

12.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 12-2

12.4 Layout Notes................................................................................................................ II: 12 -2

12.4.1 Self-Powered Devices ....................................................................................II: 12-2

12.4.1.1 Operation if GPIOn and GPIOx are Different Pins..........................II: 12-3

12.4.1.2 Operation if GPIOn and GPIOx are the Same Pin..........................II: 12-4

12.4.2 Bus-Powered Device ......................................................................................II: 12-5

12.4.3 USB On-The-G O Tr an sce iv er Us ag e ........... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 12-6

12.4.4 Interface to External Transceiver (OTG).........................................................II: 12-8

12.4.5 Interface to External Charge Pump Device (OTG) .........................................II: 12-9

12.4.6 OTG ID .........................................................................................................II: 12-11

12.4.7 Interface to External USB Transceiver (non-OTG) .......................................II: 12-12

13 AC ’97 ....................................................................................................................................II: 13-1

13.1 Overview......................................................................................................................II: 13-1

13.2 Signals.........................................................................................................................II: 13-1

13.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 13-2

13.4 Layout Notes................................................................................................................ II: 13 -3

14 I2S Interface........... .... .... .... .... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 14-1

14.1 Overview......................................................................................................................II: 14-1

14.2 Signals.........................................................................................................................II: 14-2

14.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 14-3

14.4 Layout Notes................................................................................................................ II: 14 -3

14.5 Modes of Operation Overview .....................................................................................II: 14-4

14.5.1 PXA27x Processor Provides BITCLK signal to CODEC.................................II: 14-4

14.5.1.1 Signals .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 14-4

14.5.1.2 Block Diagram.................................................................................II: 14-5

14.5.2 CODEC Provides BITCLK Signal to PXA27x Processor................................II: 14-6

Intel® PXA27x Processor Family Desig n Guide vii

Page 8

Contents

14.5.2.1 Signals............................................................................................II: 14-6

14.5.2.2 Block Diagram........ ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 14-6

15 MultiMediaCard/SD/SDIO Card Controller..........................................................................II: 15-1

15.1 Overview......................................................................................................................II: 15-1

15.2 Signals.........................................................................................................................II: 15-2

15.3 Layout Notes................................................................................................................II: 15-2

15.4 Modes of Operation Overview .....................................................................................II: 15-4

15.4.1 MMC/SD/SDIO Mode Using MMC Protocol ...................................................II: 15-4

15.4.1.1 MMC Protocol Signals ....................................................................II: 15-4

15.4.1.2 MMC Protocol Block and Schematic Diagrams..............................II: 15-5

15.4.1.3 MMC Protocol Layout Notes...........................................................II: 15-6

15.4.2 MMC/SD/SDIO Mode Using SD or SDIO Protocols.......................................II: 15-7

15.4.2.1 SD and SDIO Protocol Signals .......................................................II: 15-7

15.4.2.2 SD and SDIO Protocol Block and Schematic Diagrams.................II: 15-8

15.4.2.3 SD and SDIO Protocol Layo ut No te s... .... .... .... .... ... .... .... .... .... ... ...II: 15-10

15.4.3 SPI Mode with MMC, SD Card, and SDIO Card Devices.............................II: 15-11

15.4.3.1 SPI Mode Signals .........................................................................II: 15-11

15.4.3.2 SPI Protocol Block and Schematic Diagrams...............................II: 15-12

15.4.3.3 SPI Protocol Layout Notes............................................................II: 15-12

16 Baseband Interface ..............................................................................................................II: 16-1

16.1 Overview......................................................................................................................II: 16-1

17 Memory Stick Host Interface...............................................................................................II: 17-1

17.1 Overview......................................................................................................................II: 17-1

17.2 Signals.........................................................................................................................II: 17-1

17.3 Schemati c/B lo ck Dia g ram............... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 17-1

17.4 Layout Notes................................................................................................................II: 17-2

18 Keypad Interface...................................................................................................................II: 18-1

18.1 Overview......................................................................................................................II: 18-1

18.2 Signals.........................................................................................................................II: 18-2

18.3 Block Diagram .............................................................................................................II: 18-3

18.4 Layout Notes................................................................................................................II: 18-4

18.4.1 Recommended Pull-down Resistors...............................................................II: 18-4

18.4.2 Alternate Function During Standby and Sleep Mode......................................II: 18-4

18.4.3 Reduce Power During Standby and Sleep Mode ...........................................II: 18-4

18.4.4 Using the Keypad Signals to Wake-up from Standby and Sleep Mode..........II: 18-4

18.4.5 How to Enable Specific Combinations of Direct Keys ....................................II: 18-4

18.4.6 Interfacing to a Matrix Keypad........................................................................II: 18-5

18.5 Modes of Operation Overview .....................................................................................II: 18-6

18.5.1 Keypad Matrix and Direct Keys and No Rotary Encoder................................II: 18-6

18.5.1.1 Signals............................................................................................II: 18-6

18.5.1.2 Block Diagram........ ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 18-7

18.5.2 Keypad Matrix and Direct Keys with One Rotary Encoder .............................II: 18-8

18.5.2.1 Signals............................................................................................II: 18-8

18.5.2.2 Block Diagram........ ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 18-9

18.5.3 Keypad Matrix and Direct Keys with Two Rotary Encoders .........................II: 18-10

18.5.3.1 Signals..........................................................................................II: 18-10

18.5.3.2 Block Diagram........ ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... ...II: 18-11

viii Intel® PXA27x Processor Family Design Guide

Page 9

Contents

19 USIM Controller Interface ........ .... .... .... .... ... .... ....................... .... .... .... .... ... ....................... ....II: 19-1

19.1 Overview......................................................................................................................II: 19-1

19.2 Signals.........................................................................................................................II: 19-2

19.2.1 PXA27x Processor USIM Interface Signals....................................................II: 19-2

19.2.2 USIM Card Interface Signals ..........................................................................II: 19-3

19.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 19-4

19.4 Layout Notes................................................................................................................ II: 19 -5

20 Universal Serial Bus Host Interface........... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 20-1

20.1 Overview......................................................................................................................II: 20-1

20.2 Signals.........................................................................................................................II: 20-1

20.3 Block Diagram s..... .... .... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 20-2

20.3.1 Block Diagram for USB Host Differential Connection (Port 1 or Port 2) .........II: 20-2

20.3.2 Block Diagrams for USB Host Port 2 (Differential or Single-Ended)...............II: 20-3

20.3.3 Block Diagram for USB Host Single-Ended Connection (Port 3)....................II: 20-4

20.4 Layout Notes................................................................................................................ II: 20 -5

21 Real Time Clock Interface. .... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 21-1

21.1 Overview......................................................................................................................II: 21-1

21.2 Signals.........................................................................................................................II: 21-1

21.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 21-2

21.4 Layout Notes................................................................................................................ II: 21 -2

22 OS Timer Interface......... .... .... ... .... .... .... .... ... .... ....................... .... .... .... .... ... ....................... ....II: 22-1

22.1 Overview......................................................................................................................II: 22-1

22.2 Signals.........................................................................................................................II: 22-1

22.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 22-2

22.3.1 Channel Acces s/C o ntr ol Blo ck ..................... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 22-2

22.3.2 PXA25x Comp ati bili ty Ch an ne ls 0-3 Blo ck .......................... .... .... .... .... ... .... ....II: 22-2

22.3.3 Channels 4 - 11 Block s.................. .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 22-3

22.3.4 Output Control .................... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 22-3

22.4 Layout Notes................................................................................................................ II: 22 -3

23 Pulse-W id t h Mo du la to r Interfa ce ....................... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 23-1

23.1 Overview......................................................................................................................II: 23-1

23.2 Signals.........................................................................................................................II: 23-1

23.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 23-2

23.4 Layout Notes................................................................................................................ II: 23 -2

24 General Purpose Input/Output Interfaces......... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 24-1

24.1 Overview......................................................................................................................II: 24-1

24.2 Signals.........................................................................................................................II: 24-1

24.3 Block Diagram /S ch em at ic........ .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 24-3

24.4 Layout Notes................................................................................................................ II: 24 -3

25 Interrupt Interface......................... .... .... .... ... ....................... .... .... .... .... .... ...................... .... ....II: 25-1

25.1 Overview......................................................................................................................II: 25-1

25.2 Signals.........................................................................................................................II: 25-2

25.3 Block Diagram ......................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 25-3

25.4 Layout Notes................................................................................................................ II: 25 -4

Intel® PXA27x Processor Family Design Guide ix

Page 10

Contents

26 JTAG Debu g..........................................................................................................................II: 26-1

26.1 Overview......................................................................................................................II: 26-1

26.2 Features.......................................................................................................................II: 26-2

26.3 Signal Desc rip tio ns............. .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 26-3

26.4 Operation.....................................................................................................................II: 26-3

26.4.1 TAP Controller Reset......................................................................................II: 26-3

26.4.2 Pull-Up Resistors............................................................................................II: 26-4

26.4.3 JTAG Instruction Register and Instruction Set................................................II: 26-5

26.4.4 Test Data Registers........................................................................................II: 26-7

26.4.4.1 Bypass Register..............................................................................II: 26-7

26.4.4.2 Boundary-Scan Regi ste r... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 26-8

26.4.4.3 Data-Specific Registe rs ........ .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 26-9

26.4.4.4 Flash Data Register........................................................................II: 26-9

26.4.4.5 Intel XScale

®

Data Registers..........................................................II: 26-9

26.4.5 Test Access Port (TAP) Controller................................................................II: 26-10

26.4.5.1 Test-Logic-Reset State.................................................................II: 26-11

26.4.5.2 Run-Test/Idle State.......................................................................II: 26-11

26.4.5.3 Select-DR-Scan State...................................................................II: 26-11

26.4.5.4 Capture-DR State .........................................................................II: 26-11

26.4.5.5 Shift-DR State....................... .... .... ... .... .... .... .... .... ... .... .... .... .... ... ...II: 26-11

26.4.5.6 Exit1-DR State ..............................................................................II: 26-12

26.4.5.7 Pause-DR State................ .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... ...II: 26-1 2

26.4.5.8 Exit2-DR State ..............................................................................II: 26-12

26.4.5.9 Update-DR State...........................................................................II: 26-12

26.4.5.10 Select-IR-Scan State ....................................................................II: 26-13

26.4.5.11 Capture-IR State...........................................................................II: 26-13

26.4.5.12 Shift-IR State.................................................................................II: 26-13

26.4.5.13 Exit1-IR Sta te.................... .... .... .... ... .... ....................... .... .... .... ... ...II: 26-1 3

26.4.5.14 Pause-IR State..............................................................................II: 26-13

26.4.5.15 Exit2-IR Sta te.................... .... .... .... ... .... ....................... .... .... .... ... ...II: 26-1 4

26.4.5.16 Update-I R Sta te .................... .... .... ... .... .... .... .... .... ... .... .... .... .... ... ...II: 26-1 4

26.5 Register Descriptions.................................................................................................II: 26-15

26.5.1 JTAG Device Identification (ID) Register......................................................II: 26-15

26.5.2 JTAG Test Data Registers............................................................................II: 26-16

26.5.3 Debug Registers...........................................................................................II: 26-16

26.6 Test Register Summary.............................................................................................II: 26-16

27 Intel

®

Quick Capture Technology.......................................................................................II: 27-1

27.1 Overview......................................................................................................................II: 27-1

27.2 Feature List..................................................................................................................II: 27-2

27.3 Signals.........................................................................................................................II: 27-2

27.4 Block Diagram .............................................................................................................II: 27-3

x Intel® PXA27x Processor Family Design Guide

Page 11

Contents

Appendix

A PXA27x DVK Block Diagram ................................................................................................ II: A-1

B PXA27x Processor Developer’s Kit (DVK) .......................................................................... II: B-1

C PXA27x DVK Bill-of-Materials............................................................................................... II: C-1

®

DIntel

E Companion Components for PXA27x Processor...............................................................II: E-1

PXA27x Processor and Intel® PXA25x Processor Differences...............................II: D-1

Glossary........................................................................................................................ Glossary-1

Index......................................................................................................................................... IX-1

Intel® PXA27x Processor Family Design Guide xi

Page 12

Contents

Figures

Part I

1-1 PXA27x Processor Block Diagram.........................................................................................I: 1-2

2-1 1+6+1 uvia PCB Stackup .......................................................................................................I: 2-2

2-2 Recommended PCB Layer Assignment for an Eight-Layer PCB ...........................................I: 2-3

2-3 Recommended I/O Power Plane Layout ................................................................................I: 2-4

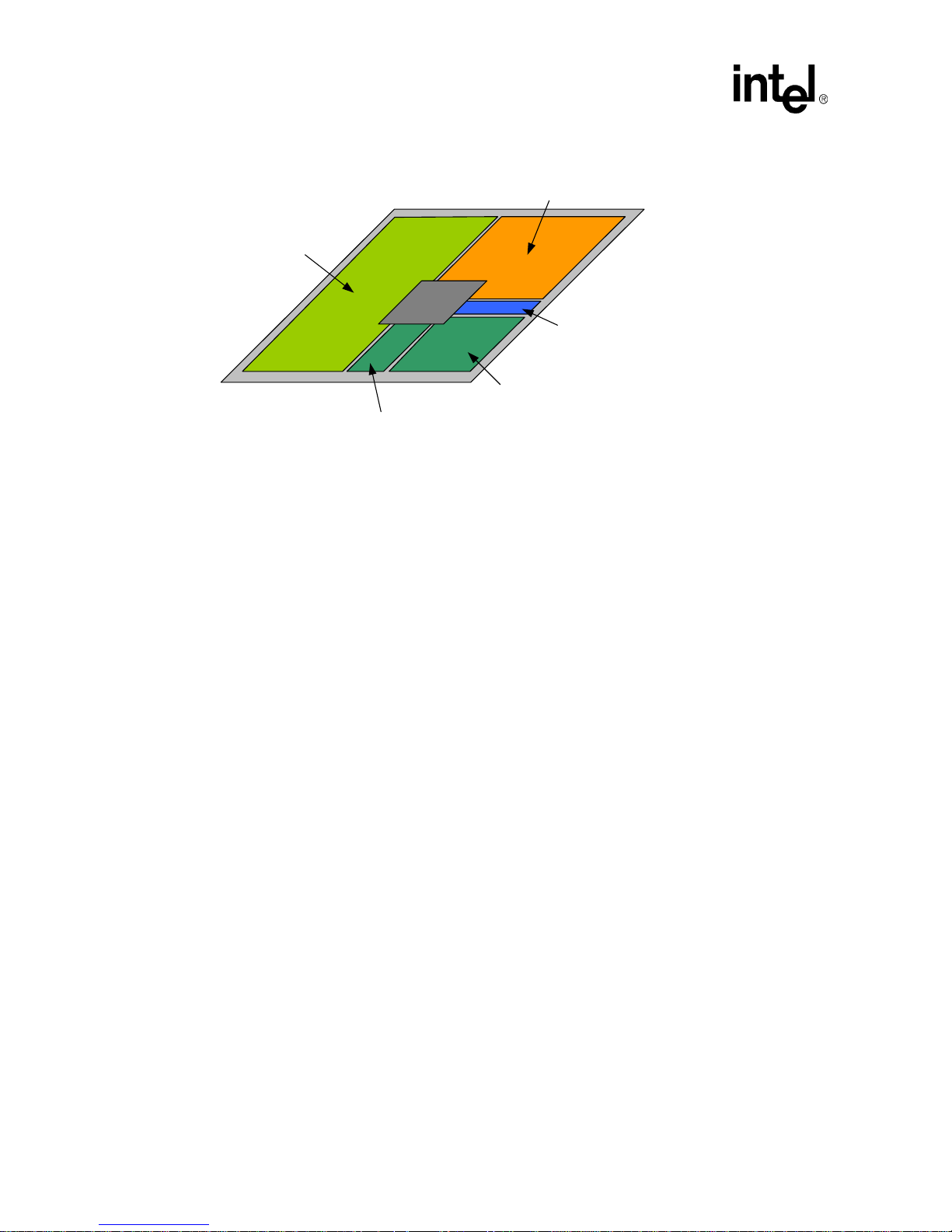

2-4 VF-BGA 13mm x 13mm Component Layout Placement Guide (Top View) ...........................I: 2-5

2-5 FS-CSP 14mm x 14mm Component Layout Placement Guide (Top View) ...........................I: 2-6

2-6 PBGA 23mm x 23mm Component Layout Placement Guide (Top View) ..............................I: 2-7

2-7 PCB Escape Routing for Copper-Defined Land Pads............................................................I: 2-8

2-8 PCB Escape Routing for Copper Defined Land Pads ............................................................I: 2-9

2-9 Recommended Mobile Handset Dimensions Diagram.........................................................I: 2-11

2-10FS-CSP (14x14) Tray Specification......................................................................................I: 2-13

2-11PBGA (23x23) Tray Specification.........................................................................................I: 2-14

4-1 Minimal Voltage Regulator Power System Design Example..................................................I: 4-3

Part II

3-1 Typical Battery and External Regulator Configuration...........................................................II: 3-5

4-1 Internal SRAM Block Diagram...............................................................................................II: 4-2

5-1 DMA controller Block Diagram ..............................................................................................II: 5-2

5-2 Companion Chip Using Fly-by DMA Transfer Interface ........................................................II: 5-4

5-3 Companion Chip Requesting Flow-Through DMA Transfers ................................................II: 5-5

6-1 General Memory Interface Configuration ..............................................................................II: 6-5

6-2 PXA27x Processor Memory System Bus Routing Topologies

(ExcludingSDCLK<x> and SDCAS) ......................................................................................II: 6-7

6-3 PXA27x Processor Memory Clock and SDCAS Routing Topology.......................................II: 6-8

6-4 Minimum Board Stack-up Configuration used for Signal Integrity.........................................II: 6-8

6-5 SDRAM Memory System Example......................................................................................II: 6-11

6-6 Block Diagram Connecting Synchronous Flash to nCS<1:0>.............................................II: 6-16

6-7 Block Diagram Connecting ROM to nCS<0> ......................................................................II: 6-18

6-8 Block Diagram Connecting SRAM to nCS<2> ....................................................................II: 6-20

6-9 Variable Latency Interface Block Diagram ..........................................................................II: 6-23

6-10External Logic for a One-Socket Configuration Expansion PC Card...................................II: 6-27

6-11External Logic for a Two-Socket Configuration Expansion PC Card...................................II: 6-28

6-12Alternate Bus Master Mode.................................................................................................II: 6-32

7-1 Passive Mon och ro me Sin gle-S ca n Display Typical Conn ec tio n ................. .... .... .... .... ... .... ...II: 7-7

7-2 Passive Monochrome Single-Scan Double-Pixel Data Display Typical Connection .............II: 7-9

7-3 Passive Monochrome Dual-Scan Display Typical Connection............................................II: 7-10

7-4 Passive Color Single-Scan Display Typical Connection......................................................II: 7-12

7-5 Passive Color Dual-Scan Display Typical Connection ........................................................II: 7-14

7-6 Active Color 12-bit per pixel Display Typical Connection ....................................................II: 7-16

7-7 Active Color 16-bit-per-pixel Display Typical Connection....................................................II: 7-18

7-8 Active Color 18-bit-per pixel Display Typical Connection....................................................II: 7-20

7-9 Active Color Display 24-bit Typical Connection...................................................................II: 7-22

xii Intel® PXA27x Processor Family Design Guide

Page 13

Contents

8-1 Standard SSP Configuration Scheme Block Diagram...........................................................II: 8-4

8-2 External Clock Source Configuration Scheme Block Diagram ..............................................II: 8-4

8-3 External Clock Enable Configuration Scheme Block Diagram ..............................................II: 8-5

8-4 Internal Clock Enable Configuration Scheme Block Diagram................................................II: 8-6

9-1 Linear Technology DAC with I2C Interface............................................................................II: 9-2

9-2 Using an Analog Switc h to All ow a Seco nd CF Ca rd . .... ... .... .... .... .... .... ... .... .... .... .... ... .... .... ..II: 9-3

2

9-3 I

C Pull-Ups and Pull-Downs.................................................................................................II: 9-4

10-1FFUART Interface Block Diagram .......................................................................................II: 10-4

10-2BTUART Interface Block Diagram.......................................................................................II: 10-5

10-3STUART Interface Block Diagram.......................................................................................II: 10-6

11-1Fast Infrared Controller Port Interface Block Diagram.........................................................II: 11-2

12-1USB Client Interface Block Diagram....................................................................................II: 12-2

12-2Self Powered Device when GPIOn and GPIOx are Different Pins ......................................II: 12-3

12-3Self-Powered Device when GPIOn and GPIOx are Same Pins ..........................................II: 12-4

12-4USB OTG Configurations ....................................................................................................II: 12-6

12-5Host Port 2 OTG Transceiver ..............................................................................................II: 12-7

12-6Conn ection to External OTG Tr a ns ce ive r.......................... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 12-8

12-7Conn ection to External OTG C h arg e Pump .......................... .... .... .... .... ... .... .... .... .... ... .... ..II: 12-10

12-8Conn ection to OTG ID ......................... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ..II: 12-11

12-9PXA27x Processor Connection to External USB Transceiver...........................................II: 12-12

13-1AC ‘97 Controller to CODEC Block Diagram .......................................................................II: 13-2

14-1I2S Controller Interface Block Diagram ...............................................................................II: 14-3

14-2PXA27x Processor Provides BITCLK..................................................................................II: 14-5

14-3PX A27 x Pro ce sso r Re ce ive s BIT C LK ................ .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 14-6

15-1MMC Protocol Interface Block Diagram...............................................................................II: 15-5

15-2MMC Protocol Interface Schematic Diagram.......................................................................II: 15-6

15-3SD and SDIO Protocol Interface Block Diagram .................................................................II: 15-8

15-4SD and SDIO Protocol Interface Schematic Diagram .........................................................II: 15-9

15-5SPI Protocol Interface Block Diagram ...............................................................................II: 15-12

17-1Memory Stick Implementation Block Diagram.....................................................................II: 17-2

18-1Keypad Interface Block Diagram .........................................................................................II: 18-3

18-2Keypad Matrix and Direct Keys Block Diagram (with No Rotary Encoder)..........................II: 18-7

18-3Keypad Matrix and Direct Keys Block Diagram (with One Rotary Encoder) .......................II: 18-9

18-4Keypad Matrix and Direct Keys Block Diagram (with Two Rotary Encoders)....................II: 18-11

19-1Connectivity USIM Card and PXA27x Processor USIM Interface using UVSx signals .......II: 19-4

19-2Connectivity USIM Card and PXA27x Processor USIM Interface Using nUEN ..................II: 19-5

20-1USB Host (Port 1 or Port 2) Differential Connections Block Diagram..................................II: 20-2

20-2PXA27x Processor Host 2 Single-Ended Connection to External Transceiver ...................II: 20-3

20-3PXA27x Processor Host 3 Connection to External USB Transceiver..................................II: 20-4

21-1Example HZ_CLK Block Diagram........................................................................................II: 21-2

22-1OS Timer Block Diagram.....................................................................................................II: 22-2

23-1PWM Block Diagram For Applications Requiring a Filter ....................................................II: 23-2

25-1Interrupt Controller Block Diagram ......................................................................................II: 25-3

26-1Test Access Port (TAP) Block Diagram...............................................................................II: 26-2

26-2PXA27x Scan Chain Arrangement ......................................................................................II: 26-5

26-3TAP Controller State Diagram ...........................................................................................II: 26-10

27-1Block Diagram for 8-bit Master Parallel Interface ................................................................II: 27-3

27-2Int erf ac e Op tio ns Sum ma ry..... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 27-4

Intel® PXA27x Processor Family Design Guide xiii

Page 14

Contents

Appendix

A-1 System Over vie w Blo ck Diag ra m .................. .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .. II: A-2

A-2 Main Board Blo ck Dia g ram..................... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .. II: A-3

A-3 Daughter Card Block Diagram.............................................................................................. II: A-4

A-4 Liquid Crystal Display Block Diagram................................................................................... II: A-5

A-5 Audio Module Block Diagram ............................................................................................... II: A-6

A-6 Keyboard Blo ck Diag ra m.................... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .. II: A-7

A-7 JTAG Block Diagram............................................................................................................ II: A-8

xiv Intel® PXA27x Processor Family Design Guide

Page 15

Contents

Tables

Part I

1-1 Related Documentation ..........................................................................................................I: 1-1

2-1 Recommended PCB Design Guidelines.................................................................................I: 2-1

2-2 PCB Dimensions for Copper-Defined Land Pads...................................................................I: 2-8

2-3 PCB Dimensions for Copper Defined Land Pads...................................................................I: 2-9

2-4 PCB Dimensions for Copper-Defined Land Pads.................................................................I: 2-10

4-1 External Power Supply Descriptions.......................................................................................I: 4-2

Part II

3-1 Clock Interface Signals..........................................................................................................II: 3-1

3-2 Power Controller Interface Signals ........................................................................................II: 3-2

5-1 DMA Interface Signals...........................................................................................................II: 5-1

5-2 Fly-By DMA Transfer Signals ................................................................................................II: 5-3

5-3 Flow-Through DMA Transfer Signals ....................................................................................II: 5-5

6-1 Memory Address Map............................................................................................................II: 6-1

6-2 PXA27x Processor Memory Controller I/O Signals ...............................................................II: 6-3

6-3 Minimum and Maximum Trace Lengths for the SDRAM Signals

(Excluding SDCLK<x> and SDCAS).............................................................................................II: 6-6

6-4 Minimum and Maximum Trace Lengths for the SDCLK<x> and SDCAS signals..................II: 6-7

6-5 SDRAM I/O Signals...............................................................................................................II: 6-9

6-6 SDRAM Memory Types Supported by PXA27x Processor .................................................II: 6-12

6-7 Normal and Alternat e Mo de Mem o ry Ad dre ss Sign al Map pin g.................... .... .... .... ... .... ....II: 6-13

6-8 SA-1110 Address Compatibility Mode Memory Address Signal Mapping...........................II: 6-14

6-9 Flash Interface Signals .......................................................................................................II: 6- 15

6-10ROM Interface Signals.........................................................................................................II: 6- 17

6-11SRAM Interface Signals.......................................................................................................II: 6- 19

6-12VLIO Memory Interface Signals...........................................................................................II: 6-22

6-13PC Card Interface Signals ...................................................................................................II: 6-25

6-14Alternate Bus Master Interface Signals ...............................................................................II: 6-31

7-1 LCD Interface Signa l List......... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ......II: 7-2

7-2 LCD Controller Data Pin Utilization........................................................................................II: 7-3

7-3 Passive Display Pins Required..............................................................................................II: 7-6

7-4 Passive Display Pins Required..............................................................................................II: 7-8

7-5 Passive Display Pins Required..............................................................................................II: 7-9

7-6 Passive Display Pins Required............................................................................................II: 7-11

7-7 Passive Display Pins Required............................................................................................II: 7-13

7-8 LCD Interface Signa l List......... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 7-15

7-9 LCD Interface Signa l List......... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 7-17

7-10LC D Int er fac e Sig na l List......... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 7-19

7-11Ac tiv e Dis pla y Pin s Re qu ire d............... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... ....II: 7-21

8-1 SSP Serial Port I/O Signals ...................................................................................................II: 8-2

9-1 I2C Signal Description ...........................................................................................................II: 9-1

10-1UART Signal Descriptions ...................................................................................................II: 10-2

10-2FFUART Interface Signals...................................................................................................II: 10-3

Intel® PXA27x Processor Family Design Guide xv

Page 16

Contents

10-3BTUART Interface Signals ..................................................................................................II: 10-5

10-4STUART Interface Signals ..................................................................................................II: 10-6

11-1FICP Signal Descr ipt i on .. .... .... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .....II: 11-1

12-1USB Client Controller Interface Signals Summary ..............................................................II: 12-1

12-2Host Port 2 OTG Transceiver Switch Control Settings........................................................II: 12-7

12-3Output to External USB Transceiver .................................................................................II: 12-13

12-4Input from External USB Transceiver ................................................................................II: 12-13

13-1External Interface to CODECs.............................................................................................II: 13-1

14-1I2S Controller Interface to CODEC......................................................................................II: 14-2

14-2I2S Controller Interface to CODEC (PXA27x Processor Providing BITCLK to CODEC) ....II: 14-4

14-3I2S Controller Interface to CODEC (CODEC Providing BITCLK

to the PXA27x Processor)...........................................................................................................II: 14-6

15-1Multimedia Card/SD/SDIO Card Controller Interface Signal Summary...............................II: 15-2

15-2MMC/SD/S DI O Co nt roll er Su pp or ted Soc ke ts and De vic es ........................... .... .... .... ... .... .II: 15-2

15-3MMC/SD/SDIO Controller Supported Device Configurations..............................................II: 15-3

15-4Multimedia Card Protocol Interface Signals ........................................................................II: 15-4

15-5MMC Pull-up and Pu ll-d ow n Re si sto rs ... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 15-6

15-6SD Card and SDIO Card Protocol Interface Signals ...........................................................II: 15-7

15-7SD/SDIO Card Pull-Up and Pull-Down Resistors..............................................................II: 15-10

15-8S PI Protocol Interface Signals. ... .... .... .... .... ... .... .... .... .... .... ... .... ....................... .... .... .... ... ...II: 15-11

17-1Memory Stick Host Interface Signal List..............................................................................II: 17-1

18-1Interface Signals Summary .................................................................................................II: 18-2

19-1PXA27x Processor Interface Signals Summary ..................................................................II: 19-2

19-2USIM Card Signals..............................................................................................................II: 19-3

20-1USB Host Controll er Int erface Signals Sum ma r y...... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 20-1

21-1RTC Interface Signal List.....................................................................................................II: 21-1

22-1OS Timer Interface Signals .................................................................................................II: 22-1

23-1P WM Interface Signa l List....... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .II: 23-1

24-1GPIO Interface Si gn al Lis t....... ... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .....II: 24-1

25-1GPIO Unit I/O Signal ...........................................................................................................II: 25-2

26-1TAP Controller Pin Definitions.............................................................................................II: 26-3

26-2IEEE 1149.1 Boundary-Scan Instruction Set.......................................................................II: 26-6

26-3IEEE 1149.1 Boundary-Scan Instruction Descriptions........................................................II: 26-6

26-4I/O Pins Excluded from Boundary-Scan Register................................................................II: 26-8

26-5JTAG Device Identification (ID) Register...........................................................................II: 26-15

26-6Test Register Summary.....................................................................................................II: 26-16

27-1Signal Descriptions for Quick Capture Technology .............................................................II: 27-2

Appendix

B-1 Processor De ve loper’s Kit (formerly NBM MNS3BVS DVK) ............. .... .... ... ....................... .. II: B-1

B-2 Processor De ve loper’s Kit (formerly NBM MNS2BVS DVK) ............. .... .... ... ....................... .. II: B-1

B-3 Processor De ve lop er ’s Kit .................. .... .... ... .... .... .... .... .... ... .... .... .... .... .... ... .... .... .... .... ... .... .. II: B-2

D-1 PXA27x Processor Operating Modes not Supported by the PXA25x Processor ................. II: D-2

E-1 Crystal Devices..................................................................................................................... II: E-1

E-2 Manufacturers of PMIC Devices........................................................................................... II: E-2

E-3 USB OTG Transceivers........................................................................................................ II: E-4

xvi Intel® PXA27x Processor Family Design Guide

Page 17

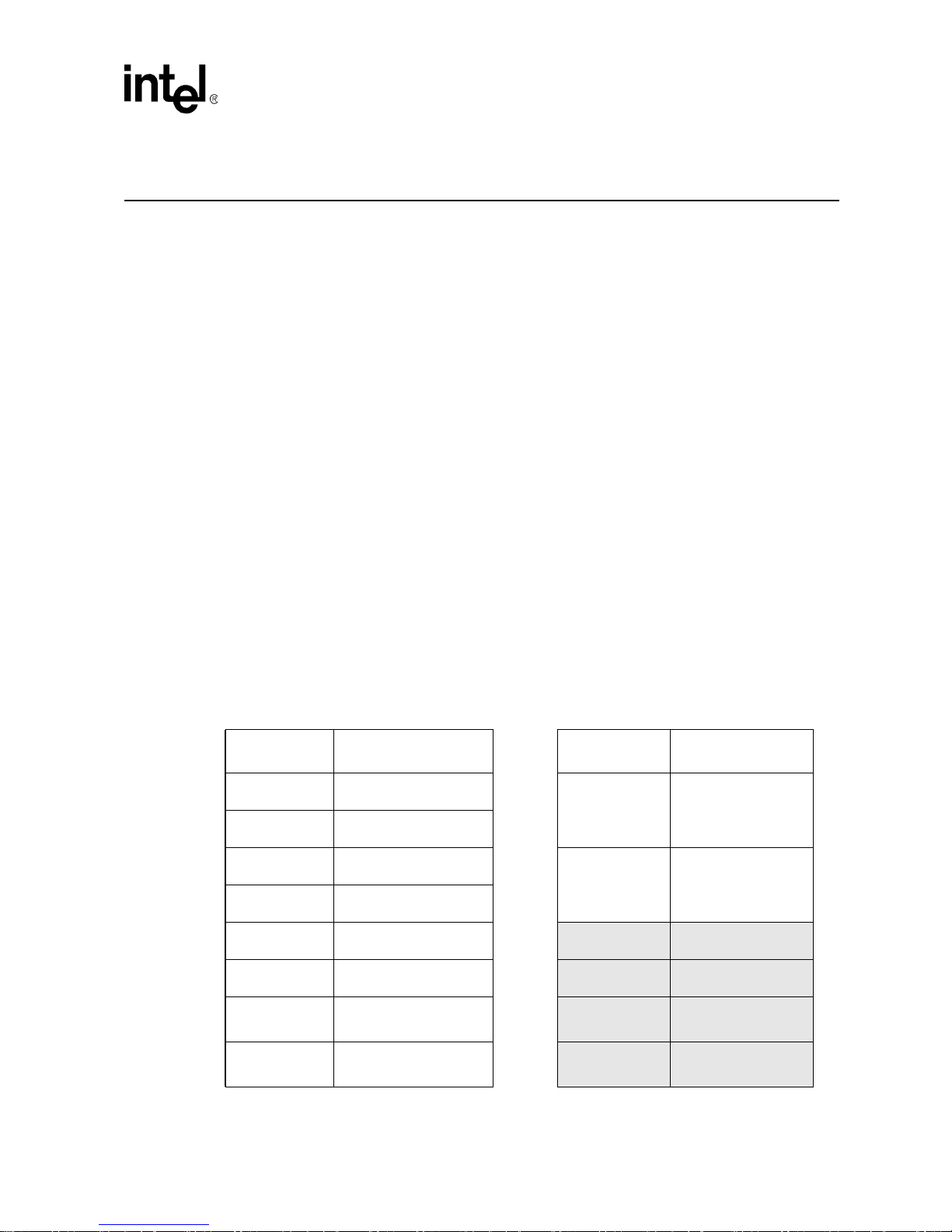

Revision History

Date Revision Description

May, 2005 002

April 2004 001 Initial release

Contents

Updated Chapter 2 “PCB Design Guidelines” on page I:2-1.

Updated Section 6.5.5, “Variable Latency Input/Output (VLIO) Interface,” on

page II: 6-21

Updated Connection to OTG ID, Figure 12-7, “Connection to External OTG

Charge Pump” on page II:12-10.

§§

Intel® PXA27x Processor Family Design Guide xvii

Page 18

Contents

xviii Intel® PXA27x Processor Family Design Guide

Page 19

Introduction to Part I 1

This document outlines the design recommendations, board schematics, and debug

recommenda tio ns for Intel

presented in this document provide maximum flexibility for board designers, while reducing the

risk of board-relate d pro ble ms . Intel

®

• Intel

• Intel

PXA270 Processor – discrete processor

®

PXA271 Processor – 32 Mbytes of Intel StrataFlash® Memory and 32 Mbytes of Low

®

PXA27x Processor Family (PXA27x processor). The guidelines

®

PXA27x Processor Family consists three devices:

Power SDRAM

®

• Intel

PXA272 Processor – 64 Mbytes of Intel StrataFlash® Memory

The schematics in Appendix B , “PXA27x Processor Developer’s Kit (DVK)” are provided as a

reference. While these schematics describe one specific design, many aspects of the schematics

remain the same for most PXA27x processor-based platforms.