Page 1

Intel® PXA26x Processor Family

Developer’s Manual

March, 2003

Order Number: 278638-002

Page 2

Contents

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEP T AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WH A TSOEVER, AND INTEL DISC LAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR W ARRANTIES

RELA TING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibilit y whatsoeve r for conf licts or incompatibil ities arisi ng from futu re chang es to them.

The Intel® PXA26x Processor Family may contain desi gn defe cts or errors known as errata which may cause the product to deviat e from published

specifications. Current characteri zed errata are available on requ est.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled

platforms may require licenses from various entities, includ ing Intel Corporat ion.

This document and the software described in it are furnished under licen se and may only be use d or copied in accorda nce w ith the terms of the

license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a

commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this

document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may

be reproduced, stored in a retrieval system, or transm itted in any form or by any means wit hout the express w ritten con sent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and befo re placi ng your product order.

Copies of documents which have an ordering number and are referenc ed in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://ww w.intel.com.

Copyright © Intel Corporation, 2003

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, C ableP ort, Celeron , Chips, Co mmer ce Ca rt, CT Con nect, CT Media, Dialogic,

DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel

NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Team Station,

Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer

logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Y our Command, ProShare,

RemoteExpress, Screamline, S hiva, Sm artD ie, Solu tions9 60, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In,

TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trade marks of Intel Corp orati on or its subsidiaries in the United States and

other countries.

*Other names and brands may be claimed as the property of others.

ii Intel® PX A26x P r oces sor Fa mil y Dev elope r’s M anual

Page 3

Contents

Contents

1 Introduction...................................................................................................................................1-1

1.1 Intel® XScale™ Core Features ..................... .... .......................... ........................... ...........1-1

1.2 System Integrati on Feat ur es................................. ........................... ..................................1-2

1.2.1 Memory Control ler...................... ... ........................... .......................... ..................1-2

1.2.2 Clocks and Power Controllers...............................................................................1 -2

1.2.3 Universal Serial Bus (USB) Client.........................................................................1-3

1.2.4 Direct Memory Access Controller (DMAC)...........................................................1-3

1.2.5 Liquid Crystal Display (LCD) Controller................................................................1-3

1.2.6 AC97 Controller....................................................................................................1-3

1.2.7 Inter-Integrated Circuit Sound (I2S) Controller.....................................................1-3

1.2.8 Multimedia Card (MMC) Controller.......................................................................1 -4

1.2.9 Fast Infrared (FIR) Communication Port...............................................................1-4

1.2.10 Synchronous Serial Protocol Controller (SSPC)...................................................1 -4

1.2.11 Inter-Integrated Circuit (I2C) Bus Interface Unit....................................................1-4

1.2.12 General Purpose Input/Output (GPIO) .................................................................1-4

1.2.13 Universal Asynchronous Receiver/Transmitters (UARTs)....................................1-4

1.2.14 Real-Time Clock (RTC).........................................................................................1-5

1.2.15 Operating System (OS) Timers.............................................................................1-5

1.2.16 Pulse-Width Modulator (PWM).............................................................................1-5

1.2.17 Interrupt Controller................................................................................................1-5

1.2.18 Integrated Synch ro n ous Flash................. ........................... .......................... ........1-5

1.2.19 Single-ended Universal Seria l Bus Client interface ..............................................1-5

1.2.20 Network Synchronous Serial Protocol Port...........................................................1-6

1.2.21 Audio Synchronou s Seri al Proto co l Port......... ... ........................... ........................1-6

1.2.22 Hardware UART (HWUART)................................................................................1-6

2 System Architecture........................................... .......................... ........................... .....................2-1

2.1 Overview............................................................................................................................2-1

2.2 Package Types..................................................................................................................2-2

2.3 Intel® XScale™ Microa rc hit ec tur e Implemen tat i on Opti o ns............... ... ............................2-3

2.3.1 CPU Core Fault Registe r — PSFS Bit............................................. .....................2-3

2.3.2 Coprocessor 14 Registers 0-3 – Performance Monitoring....................................2-3

2.3.3 Coprocessor 14 Register 6 and 7– Clo ck and Power Management.....................2-4

2.3.4 Coprocessor 15 Register 0 – ID Register Definition.............................................2-4

2.3.5 Coprocessor 15 Register 1 – P-Bit.......................................................................2-5

2.4 Input/Output Ordering........................................................................................................2-5

2.5 Semaphores......................................................................................................................2-6

2.6 Interrupts............................................................................................................................2-6

2.7 Reset .................................................................................................................................2-7

2.8 Internal Registe rs....... .......................... ........................... ...................................................2-7

2.9 Selecting Peripherals vs. General Purpose Input/Output..................................................2-8

2.10 Power on Reset and Boot Operati o n............. .............. ... ........................... ........................2-8

2.11 Power Management...........................................................................................................2-8

2.12 Pin List...............................................................................................................................2-9

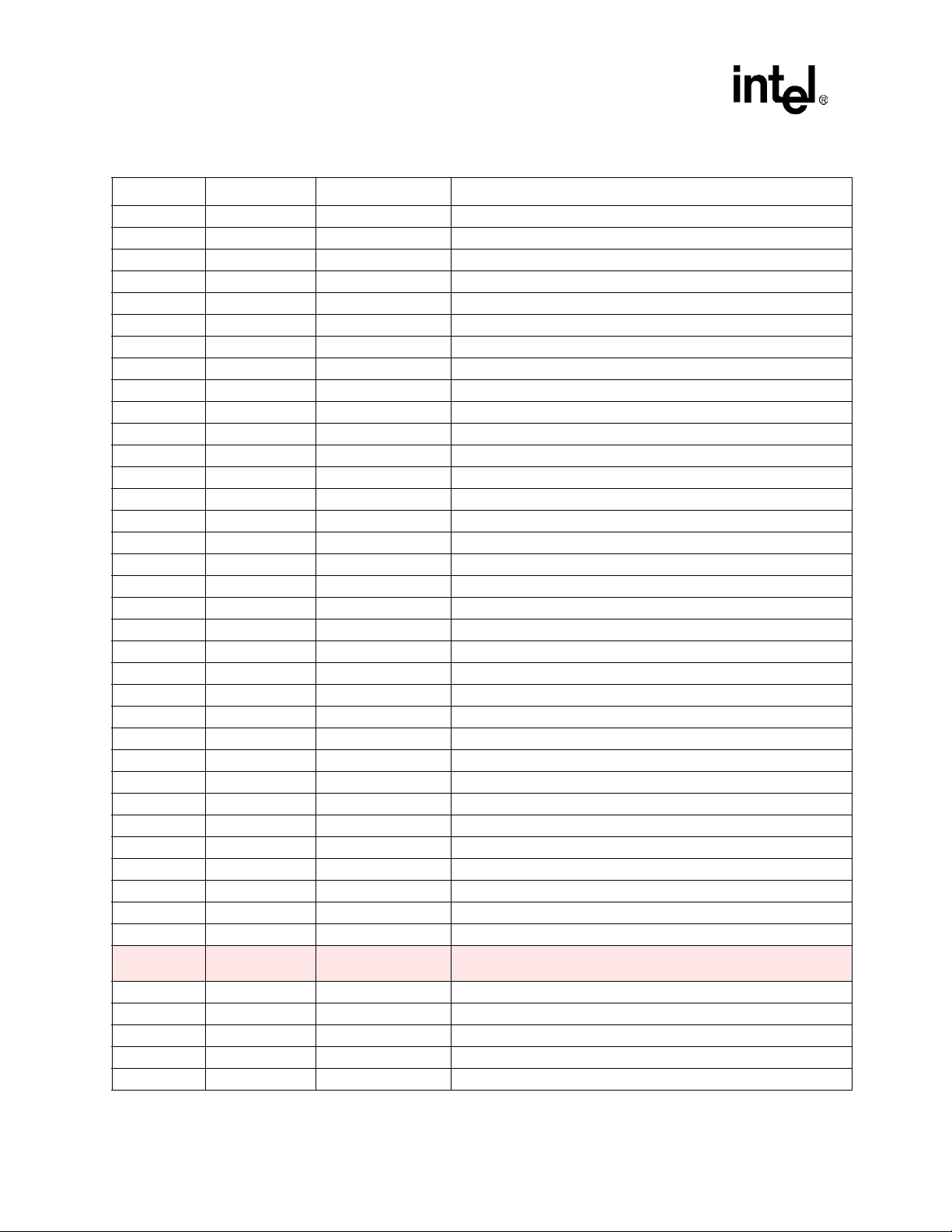

2.13 Register Address Summary.............. ........................... .......................... ..........................2-21

2.14 Memory Map....................................................................................................................2-33

Intel® PXA26x Processo r Family Develop er’s Manual iii

Page 4

Contents

3 Clocks and Power Manager.............. .......................... ........................... ......................................3-1

3.1 Clock Manager Introduction...............................................................................................3-1

3.2 Power Manager Introduction..............................................................................................3-2

3.3 Clock Manager...................................................................................................................3-2

3.3.1 32.768-KHz Oscillator...........................................................................................3-4

3.3.2 3.6864-MHz Oscillator................... .......................................................................3-4

3.3.3 Core Phase Locked Loop.....................................................................................3-4

3.3.4 95.85-MHz Peripheral Phase Locked Loop..........................................................3-5

3.3.5 147.46-MHz Pe ripheral Phase Locked Loop........................................................3-6

3.3.6 Clock Gating.........................................................................................................3-6

3.4 Resets and Power Modes..................................................................................................3-6

3.4.1 Hardware Reset....................................................................................................3-7

3.4.2 Watchdog Reset...................................................................................................3-7

3.4.3 GPIO Reset............................ ... ........................... ................................................3-8

3.4.4 Run Mode........... ... ........................... ........................... .........................................3-9

3.4.5 Turbo Mode..........................................................................................................3-9

3.4.6 Idle Mode............ ........................................ ........................... .......................... ...3-10

3.4.7 33-MHz Idle Mode............................ ... ........................... ........................... .........3-12

3.4.8 Frequency Change Sequence............................................................................3-13

3.4.9 Sleep Mode.........................................................................................................3 -15

3.4.10 Power Mode Summary.......................................................................................3-20

3.5 Power Manager Registers...............................................................................................3-22

3.5.1 Power Manager Control Register (PMCR).........................................................3-23

3.5.2 Power Manager General Configuration Register (PCFR)...................................3-24

3.5.3 Power Manager Wake-Up Enable Register (PWER)..........................................3-25

3.5.4 Power Manager Rising-Edge Detect Enable Register (PRER) ..........................3-26

3.5.5 Power Manager Falling-Edge Detect Enable Register (PFER)..........................3-27

3.5.6 Power Manager GPIO Edge Detect Status Register (PEDR).............................3 -28

3.5.7 Power Manager Sleep Status Register (PSSR) .................................................3 -29

3.5.8 Power Manager Scratch Pad Register (PSPR)..................................................3-30

3.5.9 Power Manager Fast Sleep Wake Up Configurat i on Register (PM F WR).... .......3-31

3.5.10 P ower Manage r GP IO Sleep State Registers (PGSR0, PGSR1, PGSR2).. .. . .. ..3-31

3.5.11 Reset Controller Status Register (RCSR)...........................................................3-33

3.5.12 Power Manager Register Locations....................................................................3-34

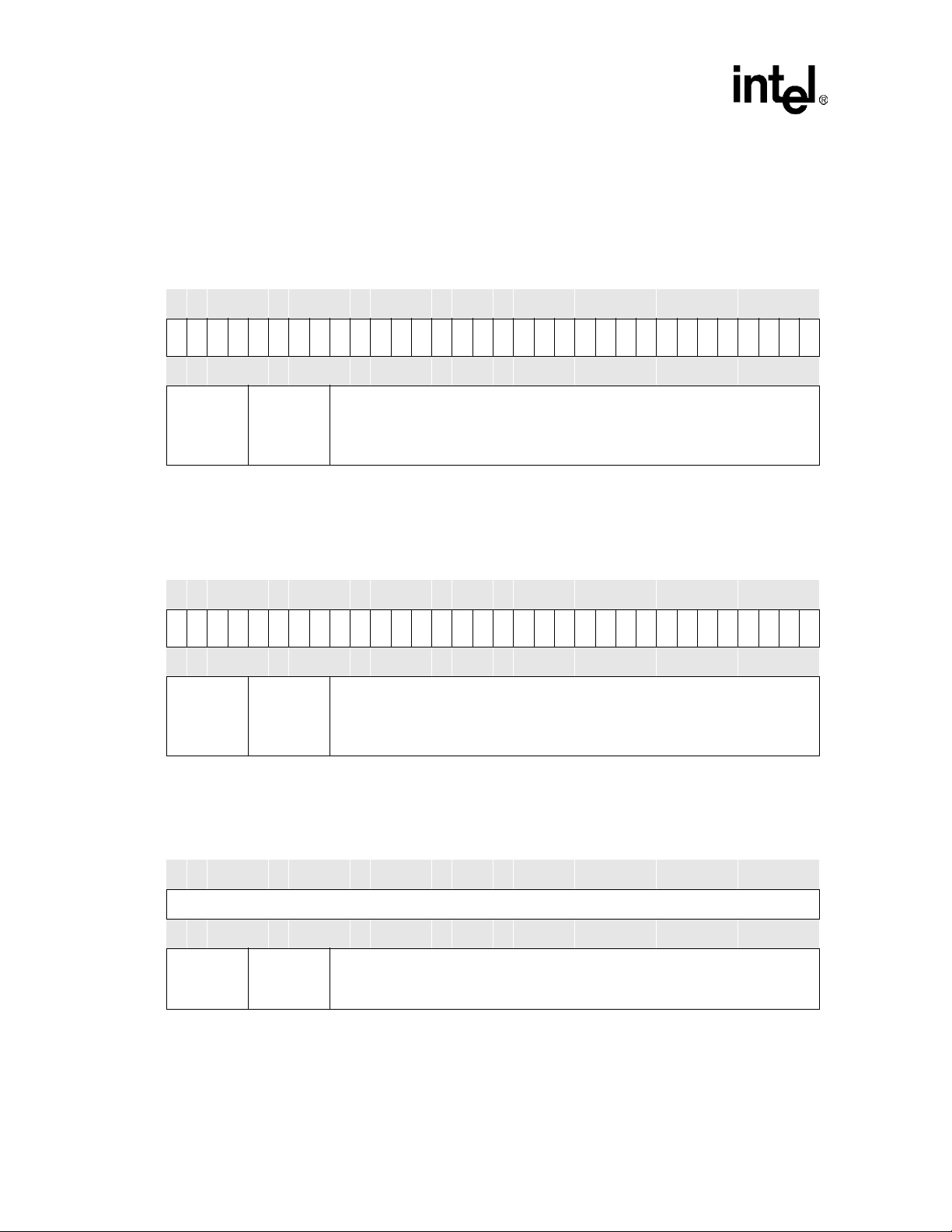

3.6 Clocks Manager Registers......... ............. .... .......................... ........................... ................3-35

3.6.1 Core Clock Configuration Register (CCCR) .......................................................3-35

3.6.2 Clock Enable Register (CKEN).................................................................. ... ......3-37

3.6.3 Oscillator Configura tio n Registe r (OSCC)................... .......................... .............3-39

3.6.4 Clocks Manager Register Locations...................................................................3-39

3.7 Coprocessor 14: Clock and Power Management............................................................3-40

3.7.1 Core Clock Configuration Register (CCLKCFG).................................................3 -40

3.7.2 Power Mode Register (PWRMODE)...................................................................3-41

3.8 External Hardwa r e Considerations......... ........................... ..............................................3-41

3.8.1 Power-On-Reset Considerations........................................................................3-41

3.8.2 Driving the Cr ystal Pins from an External Clock Sour ce.... .... .............................3-41

3.8.3 Noise Coupling Between Driven Crystal Pin s and a Crystal Oscillator...............3 -42

4 System Integration Unit................................................................................................................4-1

4.1 General-Purpose Input/Output...........................................................................................4-1

4.1.1 GPIO Operation............................................. .......................................................4-1

iv Intel® PXA26x Processor Family Developer’s Manual

Page 5

4.1.2 GPIO Alternate Functions.....................................................................................4-3

4.1.3 GPIO Register Definitions.....................................................................................4-7

4.1.4 GPIO Register Locations....................................................................................4-21

4.2 Interrupt Contro l ler............... ... ........................... ..............................................................4-22

4.2.1 Interrupt Controller Operation.............................................................................4-23

4.2.2 Interrupt Con tr olle r Re gis te r De fi n iti o ns.......... ... .................................................4-24

4.2.3 Interrupt Con tr olle r Re gis te r Lo ca tio ns........... .................................... .... ............4-31

4.3 Real-Time Clock (RTC) ...................................................................................................4-32

4.3.1 Real-Time Clock Operation.................................................................................4-32

4.3.2 Real-Time Clock Register Definitions.................................................................4-32

4.3.3 Trim Procedure...................................................................................................4-35

4.3.4 Real-Time Clock Register Locations...................................................................4-38

4.4 Operating System Timer.......................................... ........................... ........................... ..4-38

4.4.1 Watchdog Timer Operation............... .... .......................... ........................... .........4-38

4.4.2 Operating System Timer Register Definitions.....................................................4-39

4.4.3 Operating System Timer Register Locations......................................................4-42

4.5 Pulse Width Modulator.....................................................................................................4-43

4.5.1 Pulse Width Modulator Operation.......................................................................4-43

4.5.2 Register Descriptions..........................................................................................4-44

4.5.3 Pulse Width Modulator Output Wave Example...................................................4-47

4.5.4 Register Summary..............................................................................................4-48

Contents

5 Direct Memory Access Controller.................................................................................................5-1

5.1 Direct Memory Access Description....................................................................................5-1

5.1.1 Direct Memory Access Controller Channels.........................................................5-2

5.1.2 Signal Descriptions................................................................ ... ........................... .5-3

5.1.3 Direct Memory Access Channel Priority Scheme.................................................5-4

5.1.4 Direct Memory Access Descriptors.......................................................................5-6

5.1.5 Channel States.....................................................................................................5-9

5.1.6 Read and Write Order...........................................................................................5-9

5.1.7 Byte Transfer Order............................................................................................5-10

5.1.8 Trailing Bytes......................................................................................................5-11

5.2 Transferring Data.............................................................................................................5-11

5.2.1 Servicing Internal Peripherals.............................................................................5-12

5.2.2 Quick Reference for Direct Memory Access Programming ................................5-13

5.2.3 Servicing Companion Chips a nd External Peripherals.......................................5-14

5.2.4 Memory-to-Mem ory Mov es................... ............. ... ........................... ...................5-16

5.3 Direct Memory Access Controller Registers....................................................................5-17

5.3.1 DMA Interrupt Register.......................................................................................5-17

5.3.2 DMA Channel Control/Status Register...............................................................5-17

5.3.3 DMA Request to Channel Map Registers ...........................................................5-19

5.3.4 DMA Descriptor Address Registers....................................................................5-20

5.3.5 DMA Source Address Registers.........................................................................5-21

5.3.6 DMA Target Address Registers..........................................................................5-22

5.3.7 DMA Command Registers..................................................................................5-23

5.4 Examples.........................................................................................................................5-25

5.5 Direct Memory Access Controller Registers Locations....................................................5-28

6 Memory Controller........................................................................................................................6-1

6.1 Overview............................................................................................................................6-1

Intel® PXA26x Processo r Family Develop er’s Manual v

Page 6

Contents

6.2 Functional Description.......................................................................................................6-2

6.2.1 SDRAM Interface Overview..................................................................................6-2

6.2.2 Static Memory Inter fac e / Variab le Late nc y I/O Interf ac e................... ..................6-3

6.2.3 16-Bit PC Card / Compact Flash Interface...........................................................6-4

6.3 Memory System Example s............................... .... .......................... ........................... ........6-4

6.4 Memory Accesses...................................... .......................................................................6-6

6.4.1 Reads and Writes................... ........................... ...................................................6-7

6.4.2 Aborts and Nonexistent Memory .............................................. ........................... .6-7

6.5 Memory Configu rati o n Regis te rs................ .................................... .... .......................... .....6-8

6.6 Synchronous DRAM Memory Interface.............................................................................6-9

6.6.1 SDRAM MDCNFG Register..................................................................................6-9

6.6.2 SDRAM Mode Register Set Configuration Register...........................................6-12

6.6.3 SDRAM MDREFR Register................................................................................6-14

6.6.4 SDRAM Memory Options ...................................................................................6-17

6.6.5 SDRAM Command Overview.............................................................................6-25

6.6.6 SDRAM Waveforms............................................................................................6-27

6.7 Synchronous Static Memory Interface.............................................................................6-30

6.7.1 Synchronous Static Memory Configuration Register..........................................6-30

6.7.2 Sy nchronous Static Memory Mode Register Set Configuratio n Register ...........6 -36

6.7.3 Synchronous Static Memory Timing Diagrams...................................................6-37

6.7.4 Non-SDRAM Timing SXMEM Operation............................................................6-38

6.8 Asynchronous Static Memory..........................................................................................6-41

6.8.1 Static Memory Inter fac e............. ........................................ ........................... ......6-41

6.8.2 Asynchronous Static Memory Control Registers (MSC0 – 2).............................6 -44

6.8.3 ROM Interface ....................................................................................................6-48

6.8.4 SRAM Interface Overv i ew................ ........................... .......................... .............6-51

6.8.5 Variable Latency I/O (VLIO) Interface Overview.................................................6 -53

6.8.6 FLASH Memory Interface...................................................................................6-56

6.9 16-Bit PC Card/Compact Flash Interface........................................................................6-57

6.9.1 Expansion Memory Timing Configuration Register ............................................6-58

6.9.2 Expansion Memory Configuration Register (MECR)..........................................6 -61

6.9.3 16-Bit PC Card Overview....................................................................................6-61

6.9.4 External Logic for 16-Bit PC Card Implementation .............................................6-64

6.9.5 Expansion Card Interface Timing Diagrams and Parameters............................6-67

6.10 Companion Chip Inter fa ce................... ... ........................... ........................... ...................6-68

6.10.1 Alternate Bus Master Mode................................................................................6-70

6.11 Options and Settings for Boot Memory............................................................................6-72

6.11.1 Alternate Booting................................................................................................6-72

6.11.2 Boot Time Defaults................. ... ........................... ........................... ...................6-72

6.11.3 Memory Interface Reset and Initialization...........................................................6-75

6.12 Hardware, Watchdog, or Sleep Reset Operation............................................................6 -76

6.13 General Purpose Input/Output Reset Procedure.............................................................6-78

7 Liquid Crystal Display Controller..................................................................................................7-1

7.1 Overview............................................................................................................................7-1

7.1.1 Features................................................................................................................7-2

7.1.2 Pin Descriptions....................................................................................................7-4

7.2 Liquid Crystal Display Controller Operation.......................................................................7-4

7.2.1 Enabling the Controller.........................................................................................7-4

7.2.2 Disabling the Controller........................................................................................7-5

vi Intel® PXA26x Processor Family Developer’s Manual

Page 7

7.2.3 Resetting the Controller........................................................................................7-5

7.3 Detailed Module Descriptions............................................................................................7-5

7.3.1 Input FIFOs...........................................................................................................7-6

7.3.2 Lookup Palette......................................................................................................7-6

7.3.3 Temporal Modulate d Ener gy Distr i buti o n (TMED ) Dith e rin g.. ... ........................... .7-6

7.3.4 Output FIFOs................ .............. ... ........................... .......................... ..................7-9

7.3.5 Liquid Crystal Display Controller Pin Usage.........................................................7-9

7.3.6 Direct Memory Access........................................................................................7-10

7.4 Liquid Crystal Display External Palet te and Frame Bu ffe rs............. ................................7-11

7.4.1 External-Palette Buffer........................................................................................7-11

7.4.2 External-Frame Buffer ........................................................................................7-12

7.5 Functional Timing................... ........................... .......................... ....................................7-15

7.6 Liquid Crystal Di sp la y Regi ster Descriptions........... .... ....................................................7-19

7.6.1 LCD Controller Control Register 0 (LCCR0) .......................................................7-20

7.6.2 LCD Controller Control Register 1 (LCCR1) .......................................................7-28

7.6.3 LCD Controller Control Register 2 (LCCR2) .......................................................7-30

7.6.4 LCD Controller Control Register 3 (LCCR3) .......................................................7-33

7.6.5 LCD Controller DMA...........................................................................................7-37

7.6.6 LCD DMA Frame Branch Registers (FBRx).......................................................7-41

7.6.7 LCD Controller Status Register (LCSR)..............................................................7-42

7.6.8 LCD Controlle r In te rrup t ID Re gis ter (L IID R)................................................ .... ..7-46

7.6.9 TMED RGB Seed Register.................................................................................7-46

7.6.10 TMED Control Register (TCR)............................................................................7-47

7.6.11 LCD Controller Re gis te r Summary..................................... .......................... ......7-49

Contents

8 Synchronous Seri al Port Co nt ro ll er.................... ... .......................................................................8-1

8.1 Overview............................................................................................................................8-1

8.2 Signal Description..............................................................................................................8-1

8.2.1 External Interface to Synchronous Serial Peripherals..........................................8-1

8.3 Functional Descr ip ti o n...................... ..................................... ... ........................... ..............8-2

8.3.1 Data Transfer........................................................................................................8-2

8.4 Data Formats.....................................................................................................................8 -2

8.4.1 Serial Data Formats for Transfer to/from Peripherals...........................................8-2

8.4.2 Parallel Data Formats for FIFO Storage...............................................................8-6

8.5 FIFO Operation and Data Transfers..................................................................................8-6

8.5.1 Using Programmed I/O Data Tran sfers.............................................. ..................8-7

8.5.2 Using DMA Data Transfers................... .......................... ........................... ...........8-7

8.6 Baud Rate Generation.......................................................................................................8-7

8.7 SSP Serial Port Registers..................................................................................................8-7

8.7.1 SSP Control Register 0 (SSCR0).........................................................................8-8

8.7.2 SSP Control Register 1 (SSCR1).......................................................................8-11

8.7.3 SSP Data Register (SSDR)................................................................................8-15

8.7.4 SSP Status Register (SSSR)..............................................................................8-16

8.7.5 SSP Register Address Map................................................................................8-19

9 Inter-Integrated Circuit Bus Interface Unit....................................................................................9-1

9.1 Overview............................................................................................................................9-1

9.2 Signal Description..............................................................................................................9-1

9.3 Functional Descr ip ti o n...................... ..................................... ... ........................... ..............9-1

9.3.1 Operational Blocks................................................................................................9-3

Intel® PXA26x Processo r Family Develop er’s Manual vii

Page 8

Contents

9.3.2 Inter-Integrated Circuit Bus Interface Modes.......................................................9-3

9.3.3 Start and Stop Bus States....................................................................................9-4

9.4 Inter-Integ ra te d Cir cu it Bus Ope rati o n........ .......................... .............................................9-6

9.4.1 Serial Clock Line (SCL) Generation......................................................................9-7

9.4.2 Data and Addressing Management......................................................................9-7

9.4.3 Inter-Integrated Circuit Acknowledge....................................................................9-8

9.4.4 Arbitration .............................................................................................................9-9

9.4.5 Master Operations..............................................................................................9-11

9.4.6 Slave Operatio ns................. .......................... ........................... ..........................9-15

9.4.7 General Call Address..........................................................................................9-16

9.5 Slave Mode Programming Examples..............................................................................9 -18

9.5.1 Initialize Unit.......................................................................................................9-18

9.5.2 Write n Bytes as a Slave.....................................................................................9-18

9.5.3 Read n Bytes as a Slave....................................................................................9-19

9.6 Master Programming Examples......................................................................................9-19

9.6.1 Initialize Unit.......................................................................................................9-19

9.6.2 Write 1 Byte as a Master....................................................................................9-19

9.6.3 Read 1 Byte as a Master....................................................................................9-20

9.6.4 Write 2 Bytes and Repeated Start Read 1 Byte as a Master..............................9 -20

9.6.5 Read 2 Bytes as a Master - Send STOP Using the Abort..................................9-21

9.7 Glitch Suppressio n Logi c........ .......................... ........................... ....................................9-22

9.8 Reset Conditions.............................................................................................................9-22

9.9 Register Definitions..........................................................................................................9-22

9.9.1 I2C Bus Monitor Registe r- IBMR................ ........................................ ................9-22

9.9.2 I2C Data Buffer Register- IDBR..........................................................................9-23

9.9.3 I2C Control Register- ICR...................................................................................9-24

9.9.4 I2C Status Register.............................................................................................9-26

9.9.5 I2C Slave Address Register- ISAR.....................................................................9-28

10 Universal Asynchronous Receiver/Transmitter ..........................................................................10-1

10.1 Feature List............ ... ........................... ........................... .......................... .......................10-1

10.2 Overview..........................................................................................................................10-2

10.2.1 Full Function UART................ ............. .... .......................... ........................... ......10-2

10.2.2 Bluetooth UART..................................................................................................1 0-2

10.2.3 Standard UART ..................................................................................................10-2

10.2.4 Compatibility with 16550.....................................................................................10-2

10.3 Signal Descrip ti o ns.................... ... ........................... ........................................................10-3

10.4 UART Operational Description ........................................................................................10-4

10.4.1 Reset..................................................................................................................10-5

10.4.2 Internal Register Descript ion s.... ........................... ..............................................10-5

10.4.3 FIFO Interrupt Mod e Opera ti o n............................ ... ........................... ..............10-21

10.4.4 FIFO Polled Mode Operation............................................................................10-22

10.4.5 DMA Requests. ... ..............................................................................................10-22

10.4.6 Slow Infrared Asy nc hron o us Inte rfa ce........... .... .......................... .....................10-23

10.5 Register Summary.........................................................................................................10-26

10.5.1 UART Register Differences ..............................................................................10-27

11 Fast Infrared Communication Port..............................................................................................11-1

11.1 Signal Descrip ti o n............ ... .............................................................................................11-1

11.2 Fast Infrared Communic at i ons Por t Operat i on............... ... ........................... ...................11-1

viii Intel® PXA26x Processor Family Developer’s Manual

Page 9

11.2.1 Four-Positio n Puls e Modula tio n.................. ........................................ ................11-2

11.2.2 Frame Format.....................................................................................................11-3

11.2.3 Address Field......................................................................................................11-4

11.2.4 Control Field................. .... .......................... ........................... .............................11-4

11.2.5 Data Field ...........................................................................................................11-4

11.2.6 CRC Field...........................................................................................................11-4

11.2.7 Baud Rate Generation............ ........................... .................................................11-5

11.2.8 Receive Operatio n........................................................................................ ......11-5

11.2.9 Transmit Operation.............................................................................................11-6

11.2.10 Transmit and Receive FIFOs..............................................................................11-7

11.2.11 Trailing or Error Bytes in the Receive FIFO........................................................11-7

11.3 Fast Infrared Communications Port Register Descriptions..............................................11-8

11.3.1 FICP Control Regis te r 0..................................... ........................... ......................11-8

11.3.2 FICP Control Regis te r 1..................................... ........................... ....................11-10

11.3.3 FICP Control Regis te r 2..................................... ........................... ....................11-11

11.3.4 FICP Data Register...........................................................................................11-12

11.3.5 FICP Status Register 0.....................................................................................11-13

11.3.6 FICP Status Register 1.....................................................................................11-14

11.4 Fast Infrared Communications Port Register Locations................................................11-16

Contents

12 Universal Serial Bus Device Controller.......................................................................................12-1

12.1 Universal Serial Bus Overview ........................................................................................12-1

12.2 Device Configuration .......................................................................................................12-2

12.3 Universal Serial Bus Protocol..........................................................................................12-3

12.3.1 Signalling Levels.................................................................................................12-3

12.3.2 Bit Encoding........................................................................................................12-4

12.3.3 Field Formats.................... ... ............................................................... ................12-4

12.3.4 Packet Formats...................................................................................................12-5

12.3.5 Transaction Formats...........................................................................................12-7

12.3.6 UDC Device Requests ........................................................................................12-8

12.3.7 Configuration ....................................................................................................12-10

12.4 UDC Hardware Connection...........................................................................................1 2-10

12.4.1 Self-Powered De vice ............................... ........................... ..............................12-10

12.4.2 Bus-Powered De vic es................... .................................................. ... ..............12-12

12.5 UDC Operation.............................................................................................................. 12-12

12.5.1 Case 1: EP0 Control Read ............................................. ..................................12-12

12.5.2 Case 2: EP0 Control Read with a Premature Status Stage..............................12-13

12.5.3 Case 3: EP0 Control Write With or Without a Premature Status Stage............12-14

12.5.4 Case 4: EP0 No Data Command......................................................................12-15

12.5.5 Case 5: EP1 Data Transmit (BULK-IN)....... ........................... ...........................12-15

12.5.6 Case 6: EP2 Data Receive (BULK-OUT)..........................................................12-16

12.5.7 Case 7: EP3 Data Transmit (ISOCHR ON OUS-IN)............................. .... ..........12-17

12.5.8 Case 8: EP4 Data Receive (ISOCHRONOUS-OUT)........................................12-18

12.5.9 Case 9: EP5 Data Transmit (INTERRUPT-IN)............... .............. ... .................12-20

12.5.10 Case 10: RESET Interrupt................................................................................12-20

12.5.11 Case 11: SUSPEND Interrupt...........................................................................12-21

12.5.12 Case 12: RESUME Interrupt.............................................................................12-21

12.6 UDC Register Descriptions............................................................................................12-21

12.6.1 UDC Control Register.......................................................................................1 2-22

12.6.2 UDC Endpoint 0 Contro l/Sta tu s Re gis te r (UD CCS 0).......................... ..............12-24

Intel® PXA26x Processo r Family Develop er’s Manual ix

Page 10

Contents

12.6.3 UDC Endpoint x Control/Status Register (UDCCSx), Where x is 1, 6, or 11....12-26

12.6.4 UDC Endpoint x Control/Status Register (UDCCSx), Where x is 2, 7, or 12....12-28

12.6.5 UDC Endpoint x Control/Status Register (UDCCSx), Where x is 3, 8, or 13....12-31

12.6.6 UDC Endpoint x Control/Status Register (UDCCSx), Where x is 4, 9, or 14....12-33

12.6.7 UDC Endpoint x Control/Status Register (UDCCSx), Where x is 5, 10, or 15..12-35

12.6.8 UDC Interrupt Control Register 0 (UICR0).......................................................12-37

12.6.9 UDC Interrupt Control Register 1 (UICR1).......................................................12-38

12.6.10 U DC Status/Interrupt Register 0 (USIR0).........................................................12-40

12.6.11 U DC Status/Interrupt Register 1 (USIR1).........................................................12-41

12.6.12 U DC Frame Number High Register (UFNHR)..................................................12-43

12.6.13 U DC Frame Number Low Register (UFNLR)...................................................12-45

12.6.14 UDC Byte Count Register x (UBCRx), Where x is 2, 4, 7, 9, 12, or 14............12-45

12.6.15 UDC Endpoint 0 Data Register (UDDR0).........................................................12-46

12.6.16 UDC Data Register x (UDDRx), Where x is 1, 6, or 11 ....................................12-47

12.6.17 UDC Data Register x (UDDRx), Where x is 2, 7, or 12 ....................................12-48

12.6.18 UDC Data Register x (UDDRx), Where x is 3, 8, or 13 ....................................12-48

12.6.19 UDC Data Register x (UDDRx), Where x is 4, 9, or 14 ....................................12-49

12.6.20 UDC Data Register x (UDDRx), Where x is 5, 10, or 15 ..................................12-49

12.6.21 U DC Register Locations...................................................................................12-50

13 AC97 Controller Unit...................................................................................................................1 3-1

13.1 Overview..........................................................................................................................13-1

13.2 Feature List............ ... ........................... ........................... .......................... .......................13-1

13.3 Signal Descrip ti o n............ ... .............................................................................................13-2

13.3.1 Signal Configuration Steps.................................................................................13-2

13.3.2 Example AC-lin k ................................................................................................. 1 3-2

13.4 AC-link Digital Serial Interface Protocol...........................................................................13-3

13.4.1 AC-link Audio Output Frame (SDATA_OUT)......................................................13-4

13.4.2 AC-link Audio Input Frame (SDATA_IN).............................................................13-8

13.5 AC-link Low Power Mode........................................ ......................................................13-12

13.5.1 Powering Down the AC-l in k............................... ... ........................... .................13-12

13.5.2 Waking up th e AC-link......................................................................................13-13

13.6 ACUNIT Operation.........................................................................................................13-14

13.6.1 Initialization.......................................................................................................13-15

13.6.2 Trailing bytes....................................................................................................13-16

13.6.3 Operational Flow for Accessing Codec Registers............................................ 13-16

13.7 Clocks and Sampling Fre que nc ies.......................... ... ........................... ........................13-16

13.8 Functional Description...................................................................................................13-17

13.8.1 FIFOs................................................................................................................13-17

13.8.2 Interrupts...........................................................................................................13-18

13.8.3 Registers...........................................................................................................13-18

14 Inter-Integrated Circuit Sound Controller....................................................................................14-1

14.1 Overview..........................................................................................................................14-1

14.2 Signal Descrip ti o ns.................... ... ........................... ........................................................14-2

14.3 Controller Operation........................................................................................................14-3

14.3.1 Initialization.........................................................................................................14-3

14.3.2 Disabling and Enabling Audio Replay.................................................................14-4

14.3.3 Disabling and Enabling Audio Record................................................................14-4

14.3.4 Transmit FIFO Errors..........................................................................................14-5

x Intel® PXA26x Processor Family Developer’s Manual

Page 11

Contents

14.3.5 Receive FIFO Errors................... ... ............................................................... ......14-5

14.3.6 Trailing Bytes......................................................................................................14-5

14.4 Serial Audio Clocks and Sampling Frequencies..............................................................14-5

14.5 Data Formats...................................................................................................................14-6

14.5.1 FIFO and Memory Format..................................................................................14-6

14.5.2 I2S and MSB-Justified Serial Audi o Format s................................... ...................14-6

2

14.6 I

S Controller Register Descriptions................................................................................14-7

14.6.1 Serial Audio Controller Global Control Register (SACR0)..................................14-8

14.6.2 Serial Audio Contro ll e r I2S/MSB-Justified Contr ol Re gis te r (SAC R1 )..............14-10

14.6.3 Serial Audio Controller I2S/MSB-Justified Status Register (SASR0)................14-11

14.6.4 Serial Audio Clock Divider Register (SADIV)....................................................14-13

14.6.5 Serial Audio Interrupt Clear Register (SAICR)..................................................1 4-13

14.6.6 Serial Audio Interrupt Mask Register (SAIMR) .................................................14-14

14.6.7 Serial Audio Data Register (SADR)..................................................................14-14

14.6.8 Controller: Register Memory Map.....................................................................14-15

14.7 Interrupts........................................................................................................................14-16

15 MultiMediaCard Controller..........................................................................................................15-1

15.1 Overview..........................................................................................................................15-1

15.2 MultiMediaCa rd Con tr olle r Fun ct i onal De scription ................... ... ........................... .........15-4

15.2.1 Signal Descrip ti o n................... .... ........................................................................15-4

15.2.2 MultiMediaCard Controller Reset.......... ... ...........................................................15-5

15.2.3 Card Initializa tion Sequence.................... ........................... .......................... ......15-5

15.2.4 MMC and SPI Modes ..........................................................................................15-5

15.2.5 Error Detection....................................................................................................15-7

15.2.6 Interrupts.............................................................................................................15-7

15.2.7 Clock Control ......................................................................................................15-7

15.2.8 Data FIFOs.........................................................................................................15-8

15.3 Card Communication Protocol.......................................................................................15-11

15.3.1 Basic, No Data, Command and Response Sequence......................................15-11

15.3.2 Data Transfer....................................................................................................15-12

15.3.3 Busy Sequence.................................................................................................15-15

15.3.4 SPI Functionality...............................................................................................15-15

15.4 MultiMediaCard Controller Operation............................................................................15-15

15.4.1 Start and Stop Clock................... ... ........................... .......................... ..............15-16

15.4.2 Initialize.............................................................................................................15-16

15.4.3 Enabling SPI Mode...........................................................................................15-16

15.4.4 No Data Command and Response Sequence..................................................15-16

15.4.5 Erase ................................................................................................................15-17

15.4.6 Single Data Block Wri te.............. ............. ... ........................... ...........................15-17

15.4.7 Single Block Read ................................ .......................... ........................... .......15-18

15.4.8 Multiple Block Write..........................................................................................15-18

15.4.9 Multiple Block Read..........................................................................................15-19

15.4.10 Stream Write................. ........................................ ........................... .................15-19

15.4.11 Stream Read....... .... .......................... ........................... ........................... ..........15-20

15.5 MultiMediaCa rd Con tr oller Register Descri p tions..........................................................15-21

15.5.1 MMC_STRPCL Register...................................................................................15-21

15.5.2 MMC_STAT Register................................................ ........................................15-22

15.5.3 MMC_CLKRT Register.....................................................................................15-23

15.5.4 MMC_SPI Register...........................................................................................15-24

Intel® PXA26x Processo r Family Develop er’s Manual xi

Page 12

Contents

15.5.5 MMC_CMDAT Register........................................... .........................................15-25

15.5.6 MMC_RESTO Register ....................................................................................15-26

15.5.7 MMC_RDTO Register.......................................................................................15-27

15.5.8 MMC_BLKLEN Register...................................................................................15-28

15.5.9 MMC_NOB Register.........................................................................................15-28

15.5.10 MMC_PRTBUF Register ..................................................................................15-28

15.5.11 MMC_I_MASK Register....................................................................................15-29

15.5.12 MMC_I_REG Register......................................................................................15-30

15.5.13 MMC_CMD Register.......................................... .......................... .....................15-31

15.5.14 MMC_ARGH Register ......... ... ........................... .................................... .... .......15-34

15.5.15 MMC_ARGL Register.................................................................. .... .................15-34

15.5.16 MMC_RES FIFO (read only) ............... ........................... ........................... .......15-35

15.5.17 MMC_RXFIFO FIFO (read only)....................................................................... 15-35

15.5.18 MMC_TXFIFO FIFO ................................ .......................... ........................... ....15-35

16 Network/Audio Synchronous Serial Protocol Serial Ports..........................................................16-1

16.1 Overview..........................................................................................................................16-1

16.2 Features...........................................................................................................................16-1

16.3 Signal Descrip ti o n............ ... .............................................................................................16-2

16.4 Operation .........................................................................................................................16-2

16.4.1 Processor and DMA FIFO Access......................................................................16-3

16.4.2 Trailing Bytes in the Receive FIFO .....................................................................16-3

16.4.3 Data Formats......................................................................................................16-4

16.4.4 Hi-Z on SSPTXD...............................................................................................16-13

16.4.5 FIFO Operation............. ........................... .......................... ...............................16-17

16.4.6 Baud-Rate Generation......................................................................................16-17

16.5 SSP Port Register Descriptions.....................................................................................16-18

16.5.1 SSP Control Register 0 (SSCR0)..................................................................... 16-18

16.5.2 SSP Control Register 1 (SSCR1)..................................................................... 16-21

16.5.3 SSP Programmable Serial Protocol Register (SSPSP) ....................................16-27

16.5.4 SSP Time Out Register (SSTO).......................................................................16-28

16.5.5 SSP Interrupt Test Register (SSITR)................................................................16-29

16.5.6 SSP Status Register (SSSR)............................................................................16-30

16.5.7 SSP Data Register (SSDR)..............................................................................16-34

16.6 Register Summary.........................................................................................................16-34

17 Hardware UART.........................................................................................................................17-1

17.1 Overview..........................................................................................................................17-1

17.2 Features...........................................................................................................................17-2

17.3 Signal Descrip ti o ns.................... ... ........................... ........................................................17-3

17.4 Operation .........................................................................................................................17-3

17.4.1 Reset..................................................................................................................17-5

17.4.2 FIFO Operation............. ........................... .......................... .................................17-5

17.4.3 Autoflow Control .................................................................................................1 7-7

17.4.4 Auto-Baud-R at e Dete cti o n............. .....................................................................17-8

17.4.5 Slow Infrared Asy nc hron o us Inte rfa ce........... .... .......................... .......................17-8

17.5 Hardware UART Register Descriptions.........................................................................17-10

17.5.1 Receive Buffer Register (RBR).........................................................................17-10

17.5.2 Transmit Holding Register (THR).....................................................................17-11

17.5.3 Divisor Latch Registers (DLL and DLH)............................................................17-11

xii Intel® PXA26x Processor Family Devel oper’s Manual

Page 13

Contents

17.5.4 Interrupt Enable Register (IER) ........................................................................17-13

17.5.5 Interrupt Ide nti fi ca tio n Re gis te r (II R).................. ... ........................... .................17-14

17.5.6 FIFO Control Regis te r (FCR)................... ........................... ..............................17-17

17.5.7 Receive FIFO Occupa ncy Reg ister (FOR).................. ... ..................................17-18

17.5.8 Auto-Baud Control Register (ABR)...................................................................17-19

17.5.9 Auto-Baud Count Re gis ter (AC R)................... ... ..................................... ... .......17-20

17.5.10 Line Control Register (LCR)..............................................................................17-21

17.5.11 Line Status Register (LSR)...............................................................................17-23

17.5.12 Modem Control Register (MCR).............. ... ........................... ...........................17-26

17.5.13 Modem Status Register (MSR).........................................................................17-28

17.5.14 Scratchpad Register (SPR) ..............................................................................17-29

17.5.15 Infrared Selection Register (ISR)......................................................................17-30

17.6 Hardware UART Regis ter Summary............................ ... ...............................................17-31

18 Internal Flash................. ... ........................... ........................... .......................... ..........................18-1

18.1 Initialization......................................................................................................................18-1

18.1.1 Intel StrataFlash® Memory Reset Configuration................................................18-1

18.1.2 BOOT_SEL[2:0] Configuration ...........................................................................18-2

18.1.3 Determining the Size and Confi g ura ti o n of Flash Usin g Softw ar e.................... ..18-2

18.1.4 SXCNFG Configuration ......................................................................................18-2

18.1.5 Configuring the Int el Str ataF la sh ® Memory.................................. ............. ... ......18-3

18.2 Additional Intel StrataFlash® Memory Information..........................................................18-6

Figures

2-1 Block Diagram ...........................................................................................................................2-2

2-2 Memory Map (Part One) — From 0x8000 0000 to 0xFFFF FFFF ...........................................2-34

2-3 Memory Map (Part Two) — From 0x0000 0000 to 0x7FFF FFFF...........................................2-35

3-1 Clocks Manager Block Di agr am............... ........................................ .........................................3-3

4-1 General-Purpose I/O Block Diagram.........................................................................................4-2

4-2 Interrupt Con tr olle r Blo ck Di a gram.............. ........................... ..................................... ... .........4-24

4-3 PWMn Block Diagram.... .............. ... ........................... .......................... ....................................4-43

4-4 Basic Pulse Width Waveform..................................................................................................4-47

5-1 DMAC Block Diagram................................................................................................................5-2

5-2 DREQ timing requirements........................................................................................................5-3

5-3 No-Descrip to r Fetc h Mode Chann el Sta te............. ........................... ..................................... ... .5-7

5-4 Descriptor Fetch Mode Channel State.......................................................................................5-8

5-5 Little Endian Transfers.............................................................................................................5-10

6-1 General Memory Interface Configuration...................................................................................6-2

6-2 SDRAM Memory System Example............................................................................................6-5

6-3 Asynchronous Static Memory System Example........................................................................6-6

6-4 External to Internal Address Mapping Options........................................................................6-19

6-5 SDRAM Read....................... ........................... .......................... ........................... ...................6-27

6-6 SDRAM Read With a Second Read to Same Bank, Same Row.............................................6-27

6-7 SDRAM Read With a Second Read to Same Bank, Different Row.........................................6-28

6-8 SDRAM Read With a Second Read to a Differen t Bank............... .......................... ................6-28

6-9 SDRAM Write.................... ... ............................................................... ....................................6-29

6-10 SDRAM Write With a Second Write to Same Bank, Same Row .............................................6-29

6-11 SMROM Read Timing Diagram Half-Memory Cloc k Freque n cy,............... ........................... ..6-38

6-12 Burst-of-Eight Synchronous Flash Timing Diagram (non-divide-by-2 mode) ..........................6-40

6-13 MSC0/1/2 Registe r Bitmap......................................................................................................6-44

Intel® PXA26x Processo r Family Develop er’s Manual xiii

Page 14

Contents

6-14 32-Bi t Burst-of-Eig ht ROM or Flash R ead Timing Diagram (MSC0:R DF = 4,

MSC0:RDN = 1, MSC0:RRR = 1)............................................................................................6-49

6-15 Eight-Beat Burst Read from 16-B i t B urst-of-Four ROM or Flash (M S C0:RDF = 4,

MSC0:RDN = 1, MSC0:RRR = 0)............................................................................................6-50

6-16 32-Bi t Non-burst ROM, SRAM, or Flash Read Tim i ng Diagram - F our Data Beats

(MSC0:RDF = 4, MSC0:RRR = 1)...........................................................................................6 -51

6-17 32-Bit SRAM Write Timing Diagram (4-beat Burst) (MSC0:RDN = 2, MSC0:RRR = 1)..........6-52

6-18 32-Bit Variable Latency I/O Read Tim i ng (Burst-of -F our, One Wait C yc l e P e r Beat)

(MSC0:RDF = 2, MSC0:RDN = 2, MSC0:RRR = 1) ...............................................................6-54

6-19 32-Bit Variable Latency I/O Write T i m i ng (Burst-of-Four, Variabl e Wait Cycles Per Beat)......6-55

6-20 Asynchronous 32-Bit Flash Write Timing Diagram (2 Writes).................................................6-57

6-21 MCMEM1 Register Bitmap......................................................................................................6-58

6-22 MCATT1 Register Bitmap........................................................................................................6-58

6-23 MCIO1 Register Bitmap...........................................................................................................6 -59

6-24 16-Bit PC Card Memory Map ..................................................................................................6-62

6-25 Expansion Card External Logic for a One-Socket Configuration.............................................6-65

6-26 Expansion Card External Logic for a Two-Socket Configuration.............................................6-66

6-27 16-Bit PC Card Memory or I/O 16-Bit (Half-word) Access.......................................................6-67

6-28 16-Bit PC Card I/O 16-Bit Access to 8-Bit Device...................................................................6-68

6-29 Alternate Bus Master Mode..................................................................................................... 6-69

6-30 Variable Latency IO.................................................................................................................6-69

6-31 Asynchronous Boot Time Configurations and Register Defaults.............................................6-73

6-32 SMROM Boot Time Configurations and Register Defaults......................................................6-74

6-33 SMROM Boot Time Configurations and Register Defaults (Continued)..................................6-75

7-1 LCD Controller Block Diagram ..................................................................................................7-3

7-2 Temporal Dithering Concept - Single Color...............................................................................7-7

7-3 Compare Range for TMED........................................................................................................7-7

7-4 TMED Block Diagram............. ........................... .......................... .............................................7-8

7-5 Palette-Bu ffe r For mat................. ................................................................ .............................7-12

7-6 1-Bit Per Pixe l Data Memory Organization..............................................................................7 -12

7-8 4-Bits Per Pixel Data Memory Organization............................................................................7 -13

7-9 8-Bits Per Pixel Data Memory Organization............................................................................7 -13

7-10 16-Bits Per Pixel Data Memory Organization – Passive Mode ...............................................7-13

7-7 2-Bits Per Pixel Data Memory Organization............................................................................7 -13

7-11 16-Bits Per Pixel Data Memory Organization – Active Mode..................................................7-14

7-12 Passive Mode Start-of-Frame Timing ......................................................................................7-16

7-13 Passive Mode End-of-Frame Timing.......................................................................................7 -17

7-14 Passive Mode Pixel Clock and Data Pin Timing......................................................................7-17

7-15 Active Mode Timing.................................................................................................................7-18

7-16 Active Mode Pixel Clock and Data Pin Timing ........................................................................7-19

7-17 Frame Buffer/Palette Output to LCD Data Pins in Active Mode..............................................7-25

7-18 LCD Data-Pin Pixel Ordering...................................................................................................7-27

8-1 Texas Instru ments’ Synchronous Serial Fram e* For mat.................. .......................... ...............8-4

8-2 Motorola SPI* Frame Format.....................................................................................................8-5

8-3 National Micro wir e* Fra me For mat.............. ........................................ ......................................8-6

8-4 Motorola SPI* Frame Formats for SPO and SPH Programming.............................................8-14

9-1 I

2

C Bus Configuratio n Exam ple............... ... ........................... ...................................................9-2

9-2 Start and Stop Conditions..........................................................................................................9-5

9-3 START and STOP Conditio n s........... ... .......................................................................... ... ........9-6

9-4 Data Format of First Byte in Master Transaction.......................................................................9-8

xiv Intel® PXA26x Processor Family Developer’s Manual

Page 15

Contents

9-5 Acknowledge on the I2C Bus.....................................................................................................9-8

9-6 Clock Synchronization During the Arbitration Procedure.........................................................9-10

9-7 Arbitration Procedure of Two Masters.....................................................................................9-10

9-8 Master-Receiver Read from Slave-Transmitter.......................................................................9-14

9-9 Mas t er-Receiver Read from Slave-Transmit ter / Repeated Start / Master -T ransmitter

Write to Slave-Rec eiv er........ ... ................................................................ .......................... ......9-14

9-10 A Complete Data Transfer.......................................................................................................9-14

9-11 Master-Transmitter Write to Slave-Receiver............................................................................9-16

9-12 Master-Receiver Read to Slave-Transmitter...........................................................................9-16

9-13 Master-Receiver Read to Slave-Transmitter, Repeated START, Master-Transmitter

Write to Slave-Rec eiv er........ ... ................................................................ .......................... ......9-16