Page 1

Intel® PXA250 and PXA210 Applications Processors

Design Guide

February, 2002

Order Number: 278523-001

Page 2

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to the m.

The PXA250 and PXA210 applications pr ocessors m ay con tain design defect s or erro rs known as err at a whic h may ca use the product to deviate from

published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled

platforms may require licenses from various entities, including Intel Corporation.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the

license. The i nf orm at i o n i n t h is do cum en t i s f ur n is he d f o r i nf o rm ati o na l u s e o nl y, is su b jec t t o ch a ng e wi th o ut n ot i ce , an d sh o uld not be construed as a

commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this

document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may

be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2002

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic,

DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel

NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation,

Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer

logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare,

RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In,

TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and

other countries.

*Other names and brands may be claimed as the property of others.

ii PXA250 and PXA210 Applications Proc ess ors D esig n Guide

Page 3

Contents

Contents

1 Introduction.................................................................................................................................1-1

1.1 Functional Overview ..........................................................................................................1-1

1.2 Package Information..........................................................................................................1-2

1.2.1 Package Introduction ............................................................................................1-2

1.2.2 Signal Pin Descriptions.........................................................................................1-4

2 System Memory Interface..........................................................................................................2-1

2.1 Overview............................................................................................................................2-1

2.2 SDRAM Interface...............................................................................................................2-3

2.3 SDRAM memory wiring diagram .......................................................................................2-3

2.4 SDRAM Support ................................................................................................................2-5

2.5 SDRAM Address Mapping.................................................................................................2-6

2.6 Static Memory....................................................................................................................2-7

2.6.1 Overview...............................................................................................................2-7

2.6.2 Boot Time Defaults ...............................................................................................2-8

2.6.3 SRAM / ROM / Flash / Synchronous Fast Flash Memory Options.......................2-9

2.6.4 Variable Latency I/O Interface Overview ..............................................................2-9

2.6.5 External Logic for PCMCIA Implementation .......................................................2-11

2.6.6 DMA / Companion Chip Interface.......................................................................2-14

2.7 System Memory Layout Guidelines ... ...... ....... ...... ....................................... ...... ....... ...... .2-17

2.7.1 System Memory Topologies (Min and Max Simulated Loading).........................2-17

2.7.2 System Memory Recommended Trace Lengths.................................................2-18

3 LCD Display Controller ..............................................................................................................3-1

3.1 LCD Display Overview.......... ...... .......................................................................................3-1

3.2 Passive (DSTN) Displays ........................ ....... ...................................................................3-1

3.2.1 Typical Connections for Passive Panel Displays..................................................3-2

3.2.1.1 Passive Monochrome Single Panel Displays........................................3-2

3.2.1.2 Passive Monochrome Single Panel Displays, Double-Pixel Data.........3-3

3.2.1.3 Passive Monochrome Dual Panel Displays ..........................................3-3

3.2.1.4 Passive Color Single Panel Displays....................................................3-4

3.2.1.5 Passive Color Dual Panel Displays.......................................................3-4

3.3 Active (TFT) Displays ........................................................................................................3-5

3.3.1 Typical connections for Active Panel Displays......................................................3-6

3.4 PXA250 Pinout ..................... ...... ....... ...... ....................................... ...... ....... ...... ....... ...... ...3-7

3.5 Additional Design Considerations......................................................................................3-8

3.5.1 Contrast Voltage ...................................................................................................3-8

3.5.2 Backlight Inverter..................................................................................................3-8

3.5.3 Signal Routing and Buffering................................................................................3-8

3.5.4 Panel Connector...................................................................................................3-9

4 USB Interface ..............................................................................................................................4-1

4.1 Self Powered Device .........................................................................................................4-1

4.1.1 Operation if GPIOn and GPIOx are Different Pins................................................4-1

4.1.2 Operation if GPIOn and GPIOx are the Same Pin................................................4-2

4.2 Bus Powered Device .........................................................................................................4-2

PXA250 and PXA210 Applications Processors Design Guide iii

Page 4

Contents

5 MultiMediaCard (MMC)...............................................................................................................5-1

5.1 Schematics........................................................................................................................5-1

5.1.1 Signal Description.................................................................................................5-1

5.1.2 How to Wire ..........................................................................................................5-2

5.1.2.1 SDCard Socket.....................................................................................5-4

5.1.2.2 MMC Socket .........................................................................................5-4

5.1.3 Simplified Schematic ............................................................................................5-5

5.1.4 Pull-up and Pull-down...........................................................................................5-6

5.2 Utilized Features................................................................................................................5-6

6 AC97 ............................................................................................................................................6-1

6.1 Schematics........................................................................................................................6-1

6.2 Layout................................................................................................................................6-2

7I2C................................................................................................................................................7-1

7.1 Schematics........................................................................................................................7-1

7.1.1 Signal Description.................................................................................................7-1

7.1.2 Digital-to-Analog Converter (DAC) .......................................................................7-2

7.1.3 Other Uses of I2C.................................................................................................7-2

7.1.4 Pull-Ups and Pull-Downs......................................................................................7-3

7.2 Utilized Features................................................................................................................7-4

8 Power and Clocking...................................................................................................................8-1

8.1 Operating Conditions.........................................................................................................8-1

8.2 Electrical Specifications.....................................................................................................8-2

8.3 Power Consumption Specifications ...................................................................................8-2

8.4 Oscillator Electrical Specifications.....................................................................................8-4

8.4.1 32.768 kHz Oscillator Specifi ca tio ns ................ ....... ...... ....... ...... ....... ...................8-4

8.4.2 3.6864 MHz Oscillator Specifications ...................................................................8-5

8.5 Reset and Power AC Timing Specifications ......................................................................8-6

8.5.1 Power Supply Connectivity...................................................................................8-6

8.5.2 Power On Timing................................................................................................8-11

8.5.3 Hardware Reset Timing......................................................................................8-12

8.5.4 Watchdog Reset Timing .....................................................................................8-13

8.5.5 GPIO Reset Timing........... ....... ...... ....... ...... ...... ....... ....................................... ....8-13

8.5.6 Sleep Mode Timing.............................................................................................8-14

8.6 Memory Bus and PCMCIA AC Specifications .................................................................8-15

8.7 Example Form Factor Reference Design Power Delivery Example................................8-20

8.7.1 Power System.....................................................................................................8-20

8.7.1.1 Power System Configuration ..............................................................8-21

8.7.2 CORE Power ......................................................................................................8-22

8.7.3 PLL Power ..........................................................................................................8-22

8.7.4 I/O 3.3 V Power ..................................................................................................8-23

8.7.5 Peripheral 5.5 V Power.......................................................................................8-23

9 JTAG/Debug Port........................................................................................................................9-1

9.1 Description.........................................................................................................................9-1

9.2 Schematics........................................................................................................................9-1

9.3 Layout................................................................................................................................9-2

A SA-1110/Applications Processor Migration............................................................................ A-1

iv PXA250 and PXA210 Applications Processors Design Guide

Page 5

Contents

A.1 SA-1110 Hardware Migration Issues................................................................................ A-2

A.1.1 Hardware Compatibility........................................................................................A-2

A.1.2 Signal Changes ................................................................................................... A-2

A.1.3 Power Delivery..................................................................................................... A-4

A.1.4 Package............................................................................................................... A-4

A.1.5 Clocks.................................................................................................................. A-4

A.1.6 UCB1300 ............................................................................................................. A-5

A.2 SA-1110 to PXA250 Software Migration Issues ............................................................... A-5

A.2.1 Software Compatibility.......... ...... ....... ...................................... ....... ...... ....... ...... .. A-6

A.2.2 Address space..................................................................................................... A-6

A.2.3 Page Table Changes ........................................................................................... A-6

A.2.4 Configuration registers.........................................................................................A-6

A.2.5 DMA..................................................................................................................... A-7

A.3 Using New PXA250 Features ........................................................................................... A-7

A.3.1 Intel® XScale™ Microarchitecture....................................................................... A-8

A.3.2 Debugging ........................................................................................................... A-8

A.3.3 Cache Attributes .................................................................................................. A-8

A.3.4 Other features...................................................................................................... A-8

A.3.5 Conclusion........................................................................................................... A-9

B Example Form Factor Reference Design Schematic Diagrams ............................................ B-1

B.1 Notes ................................................................................................................................ B-1

B.2 Schematic Diagrams.........................................................................................................B-1

C BBPXA2xx Development Baseboard Schematic Diagram .................................................... C-1

C.1 Schematic Diagram ..........................................................................................................C-1

D PXA250 Processor Card Schemat ic Diagra m .........................................................................D-1

D.1 Schematic Diagram ..........................................................................................................D-1

E PXA21 0 Processor Card Schematic Diagram ......................................................................... E-1

E.1 Schematic Diagram .......................................................................................................... E-1

PXA250 and PXA210 Applications Processors Design Guide v

Page 6

Contents

Figures

1-1 Applications Processor Block Diagram......................................................................................1-2

1-2 PXA250 Applications Process or................................ ...... ...... ....... ...... ....... ...... ....... ...... ...........1-11

1-3 PXA210 Applications Process or................................ ...... ...... ....... ...... ....... ...... ....... ...... ...........1-15

2-1 General Memory Interface Configuration ..................................................................................2-2

2-2 SDRAM Memory System Example............................................................................................2-4

2-3 32-Bit Variable Latency I/O Read Timing (Burst-of-Four, One Wait Cycle Per Beat)..............2-10

2-4 Expansion Card External Logic for a Two-Socket Configuration.............................................2-12

2-5 Expansion Card External Logic for a One-Socket Configuration.............................................2-13

2-6 Alternate Bus Master Mode.....................................................................................................2-15

2-7 Variable Latency I/O................................................................................................................2-16

2-8 CS, CKE, DQM, CLK, MA minimum loading topology.............................................................2-17

2-9 CS, CKE, DQM, CLK, MA Maximum Loading Topology .........................................................2-17

2-10MD Minimum Loading Topology..............................................................................................2-17

2-11MD maximum loading topology ...............................................................................................2-18

3-1 Single Panel Monochrome Passive Display Typical Connection ..............................................3-3

3-2 Passive Monochrome Single Panel Displays, Double-Pixel Data Typical Connection..............3-3

3-3 Passive Monochrome Dual Panel Displays Typical Connection ...............................................3-4

3-4 Passive Color Single Panel Displays Typical Connection.........................................................3-4

3-5 Passive Color Dual Panel Displays Typical Connection............................................................3-5

3-6 Active Color Display Typical Connection...................................................................................3-7

4-1 Self Powered Device .................................................................................................................4-1

5-1 Applications Processor MMC and SDCard Signal Connections................................................5-3

5-2 Applications Processor MMC to SDCard Simplified Signal Connection....................................5-5

6-1 AC97 connection .......................................................................................................................6-1

7-1 Linear Technology DAC with I2C Interface ...............................................................................7-2

7-2 Using an Analog Switch to Allow a Second CF Card ................................................................7-3

2

7-3 I

C Pull-Ups and Pull-Downs.....................................................................................................7-3

8-1 Power-On Reset Timing ..........................................................................................................8-12

8-2 Hardware Reset Timing...........................................................................................................8-13

8-3 GPIO Reset Timing .................................................................................................................8-13

8-4 Sleep Mode Timing..................................................................................................................8-14

8-5 Example Form Factor Reference Design Power System Design............................................8-22

9-1 JTAG/Debug Port Wiring Diagram ............................................................................................9-1

Tables

1-1 Revision History.........................................................................................................................1-1

1-2 Related Documentation .............................................................................................................1-1

1-3 Signal Pin Descriptions..............................................................................................................1-4

1-4 PXA250 Applications Processor Pinout — Ballpad Number Order .........................................1-12

1-5 PXA210 Applications Processor Pinout — Ballpad Number Order .........................................1-16

2-1 Memory Address Map ...............................................................................................................2-3

2-2 SDRAM Memory Types Supported by the Applications Processor...........................................2-5

2-3 Normal Mode Memory Address Mapping..................................................................................2-6

2-4 Applications Processor Compatibility Mode Address Line Mapping..........................................2-7

2-5 Valid Booting Configurations Based on Package Type.............................................................2-8

2-6 BOOT_SEL Definitions..............................................................................................................2-8

vi PXA250 and PXA210 Applications Processors Design Guide

Page 7

Contents

2-7 SRAM / ROM / Flash / Synchronous Fast Flash AC Specifications ..........................................2-9

2-8 Variable Latency I/O Interface AC Specifications....................................................................2-10

2-9 Card Interface (PCMCIA or Compact Flash) AC Specifications..............................................2-13

2-10Minimum and Maximum Trace Lengths for the SDRAM Signals.............................................2-18

3-1 LCD Controller Data Pin Utilization............................................................................................3-1

3-2 Passive Display Pins Required..................................................................................................3-2

3-3 Active Display Pins Required.....................................................................................................3-6

3-4 PXA250 LCD Controller Ball Positions ......................................................................................3-7

5-1 MMC Signal Description ............................................................................................ ....... .........5-1

5-2 SDCard Socket Signals.............................................................................................................5-2

5-3 MMC Controller Supported Sockets and Dev ices ..................... ....................................... ...... ...5-2

5-4 SDCard Pull-up and Pull-down Resistors..................................................................................5-6

5-5 MMC Pull-up and Pull-down Resistors ......................................................................................5-6

7-1 I2C Signal Description ...............................................................................................................7-1

8-1 Voltage, Temperature, and Frequency Electrical Specifications ...............................................8-1

8-2 Absolute Maximum Ratings.......................................................................................................8-2

8-3 Power Consumption Specifications...........................................................................................8-3

8-4 32.768 kHz Oscillator Specifications .........................................................................................8-4

8-5 3.6864 MHz Oscillator Specifi ca tio ns .............................................. ....... ...... ....... ...... ....... ...... ...8-5

8-6 PXA250 and PXA210 VCCN vs. VCCQ....................................................................................8-6

8-7 Power-On Timing Specificat ion s... ...... ....... ...................................... ....... ...... ....... ...... ....... ...... .8-12

8-8 Hardware Reset Timing Specifications....................................................................................8-13

8-9 GPIO Reset Timing Specifications ..........................................................................................8-14

8-10Sleep Mode Timing Specifications...........................................................................................8-14

8-11SRAM / ROM / Flash / Synchronous Fast Flash AC Specifications (3.3 V) ............................8-15

8-12Variable Latency I/O Interface AC Specifications (3.3 V)........................................................8-16

8-13Card Interface (PCMCIA or Compact Flash) AC Specifications (3.3 V) ..................................8-16

8-14Synchronous Memory Interface AC Specifications (3.3 V)......................................................8-17

8-15SRAM / ROM / Flash / Synchronous Fast Flash AC Specifications (2.5 V) ............................8-18

8-16Variable Latency I/O Interface AC Specifications (2.5 V)........................................................8-19

8-17Card Interface (PCMCIA or Compact Flash) AC Specifications (2.5 V) ..................................8-19

8-18Synchronous Memory Interface AC Specifications (2.5 V)......................................................8-20

PXA250 and PXA210 Applications Processors Design Guide vii

Page 8

Contents

viii PXA250 and PXA210 Applications Proc ess ors D esig n Guide

Page 9

Introduction 1

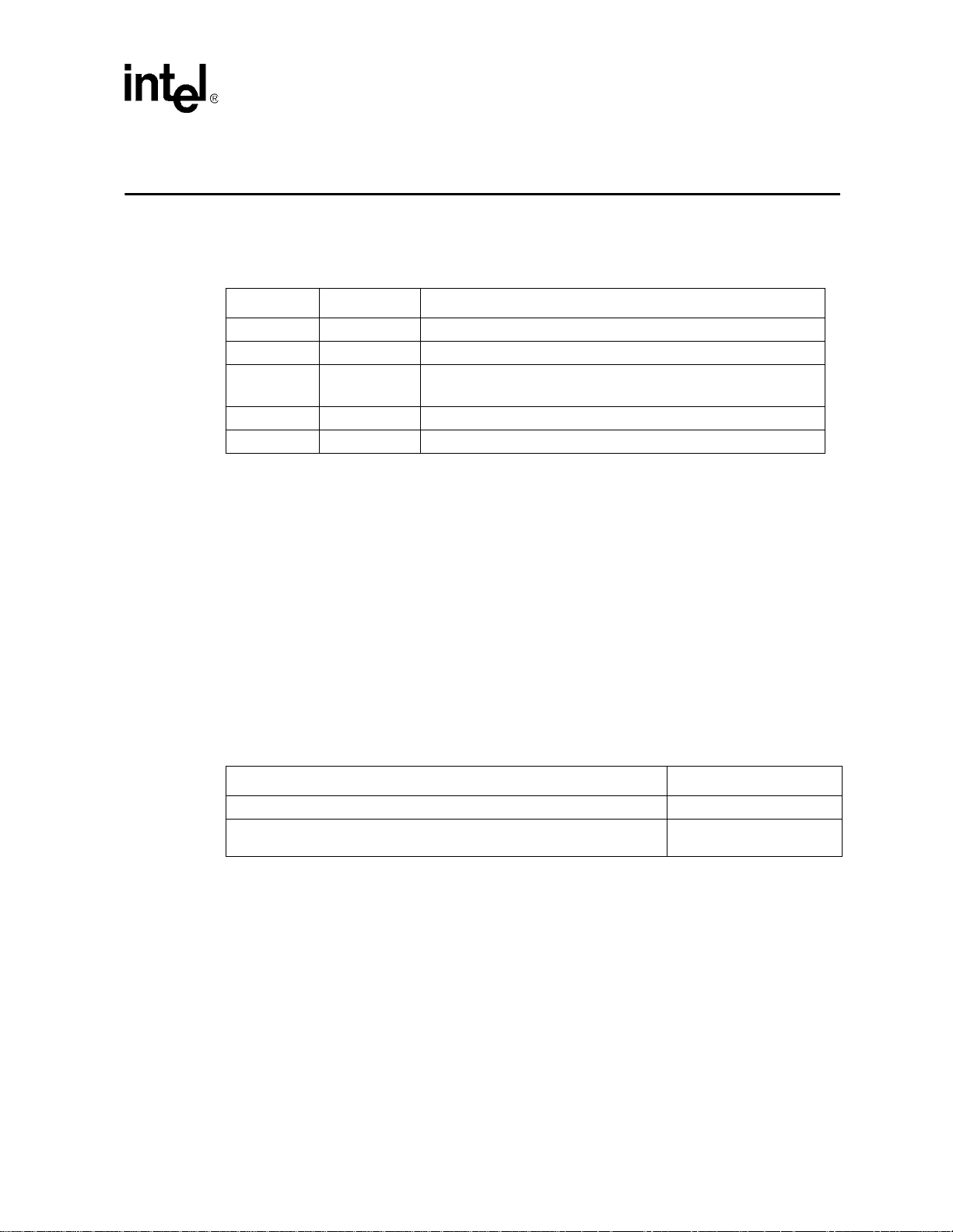

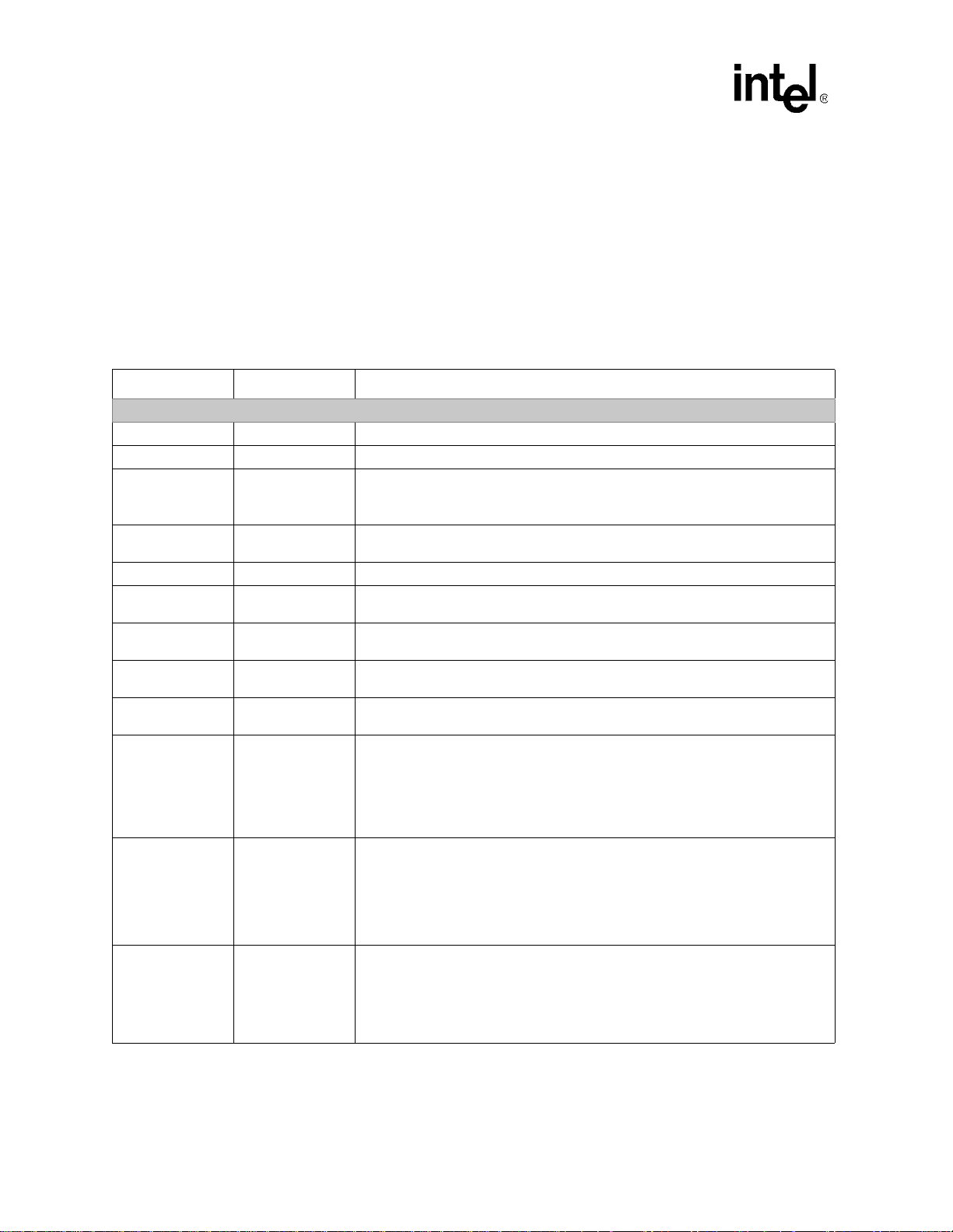

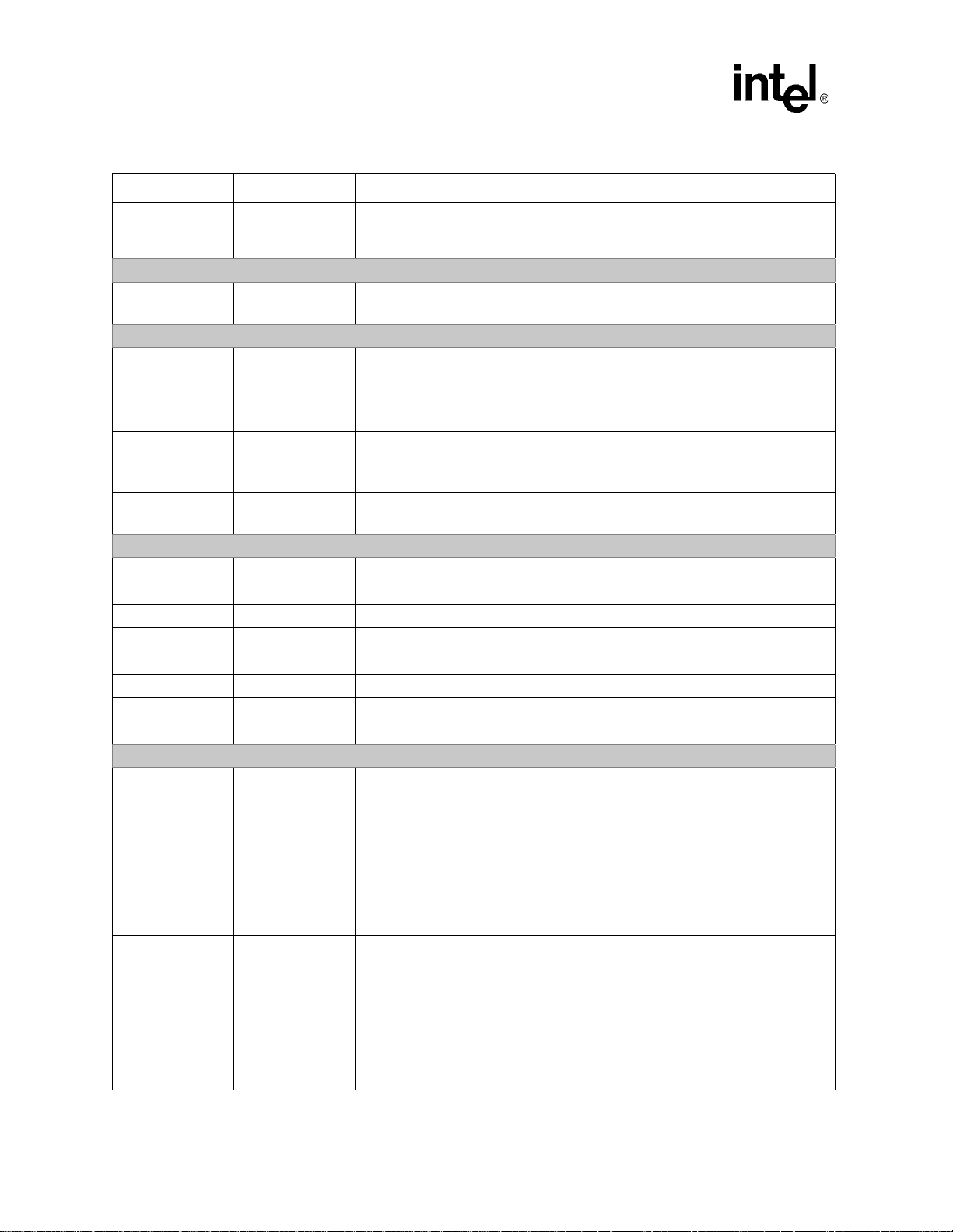

T a ble 1-1. Revision History

Date Revision Description

Nov 2000 0.1 Initial Release: RS-Intel

Nov 2000 0.2 Second draft

Jan 2001 0.3

May 2001 0.6 Added reference to PXA210 and performed editorial clean-up.

February 2002 1.0 Public Release

Corrected name of FFRTS in Table 1-4.

Reorganized Table 1-4 and Table 1-5 for readability.

This document presents design recommendations, board schematics, and debug recommendations

for the Intel® PXA250 and PXA210 applications processors. The PXA250 applications processor

is the 32-bit version of the device and the PXA210 applications processor is the 16-bit version.

This document refers to both versions as the applications processor. When differences are

discussed, the specific applications processor is called by name.

The guidelines presented in this document ensure maximum flexibility for board designers, while

reducing the risk of board-related issues. Use the schematics in Appendix B, “Example Form

Factor Reference Design Schematic Diagrams” as a reference for your own design. While the

included schematics cover a specific design, the core schematics remain the same for most

PXA250 and PXA210 applications processor based platforms. Consult the debug

recommendations when debugging an applications processor based system. To ensure the correct

implementation of the debug port (refer to Section 9 for more information), these debug

recommendations should be understood before completing board design, in addition to other debug

features.

®

PXA250 Platform Design Guide

T a ble 1-2. Related Documentation

Document Title Order Number

Intel® PXA250 and PXA210 Applications Processors Developer’s Manual 278522

Intel® PXA250 and PXA210 Applications Processors Electrical, Mechanical,

and Thermal Specification

278524

1.1 Functional Overview

The PXA250 and PXA210 applications process ors are the f irst integr ated-s ystem-on -a-chip des ign

based on the Intel® XScale™ microarchitecture. The PXA250 and PXA210 applications

processors integrate the Intel® XScale™ microarchitecture core with many peripherals to let you

design products for the handheld market.

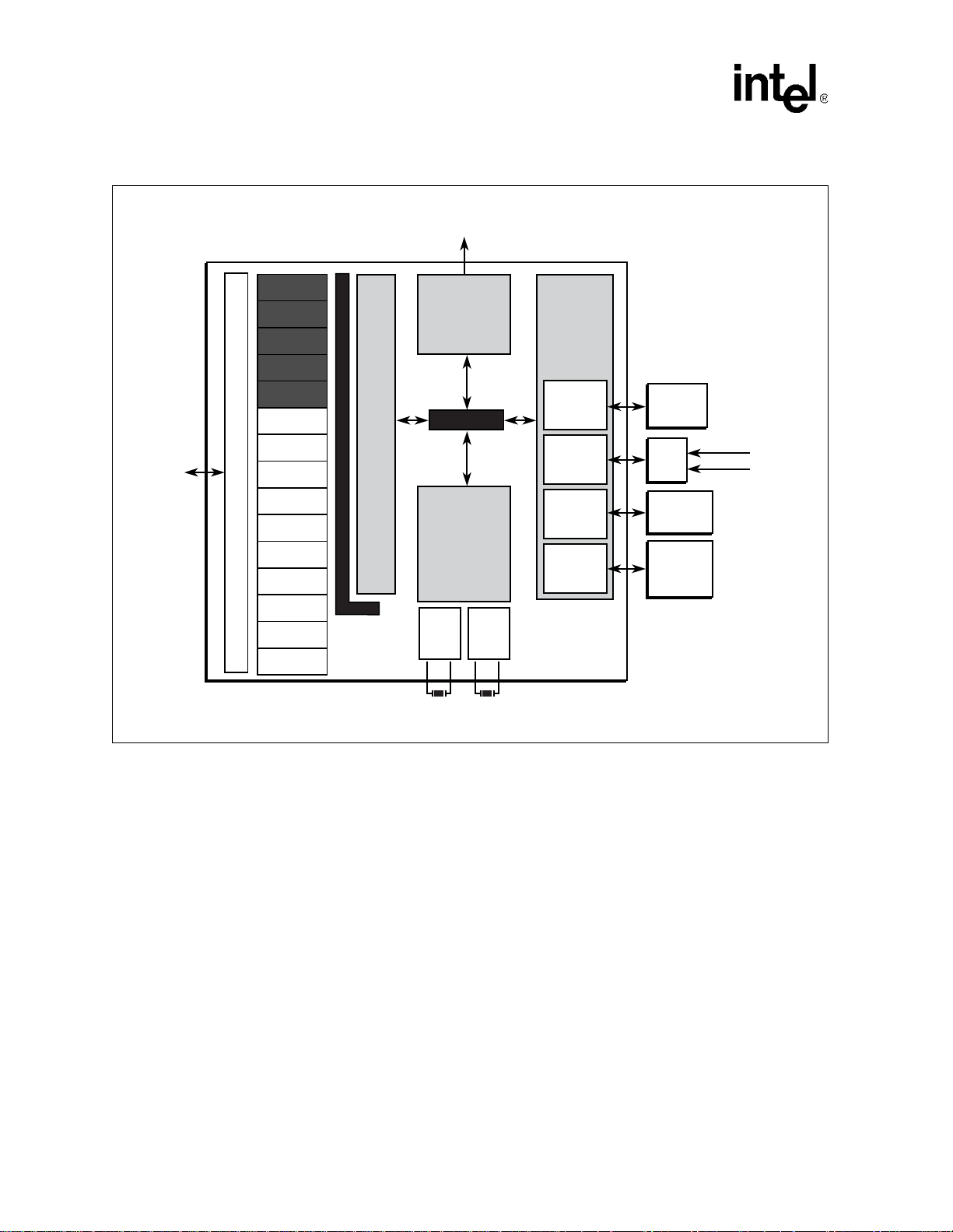

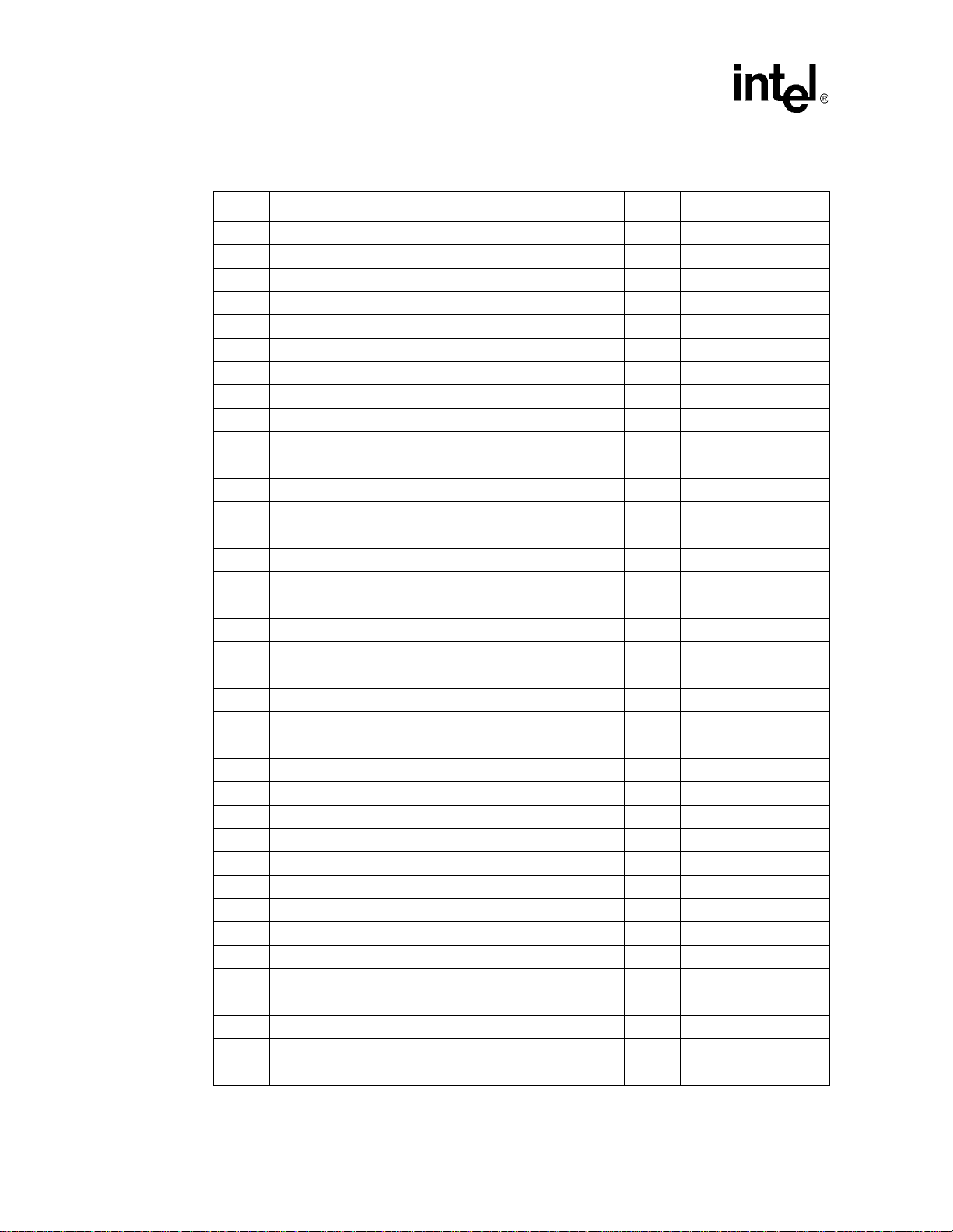

Figure 1-1 on page 1-2 is a block diagram of the applications processor.

PXA250 and PXA210 Applications Processors Design Guide 1-1

Page 10

Introduction

s

Figure 1-1. Applications Processor Block Diagram

RTC

OS Timer

PWM(2)

Int.

Controller

Clocks &

Power Man.

I2S

I2C

AC97

UART1

General Purpose I/O

UART2

Slow IrDA

Fast IrDA

SSP

USB

Client

MMC

and Bridge

Peripheral Bus

DMA Controller

Color or

Grayscale

LCD

Controller

System Bus

Megacell

Core

3.6864

MHz

Osc

32.768

KHz

Osc

Memory

Controller

Variable

Latency I/O

Control

PCMCIA

& CF

Control

Dynamic

Memory

Control

Static

Memory

Control

ASIC

XCVR

SDRAM/

SMROM

4 banks

ROM/

Flash/

SRAM

4 banks

Socket 0

Socket 1

A8651-01

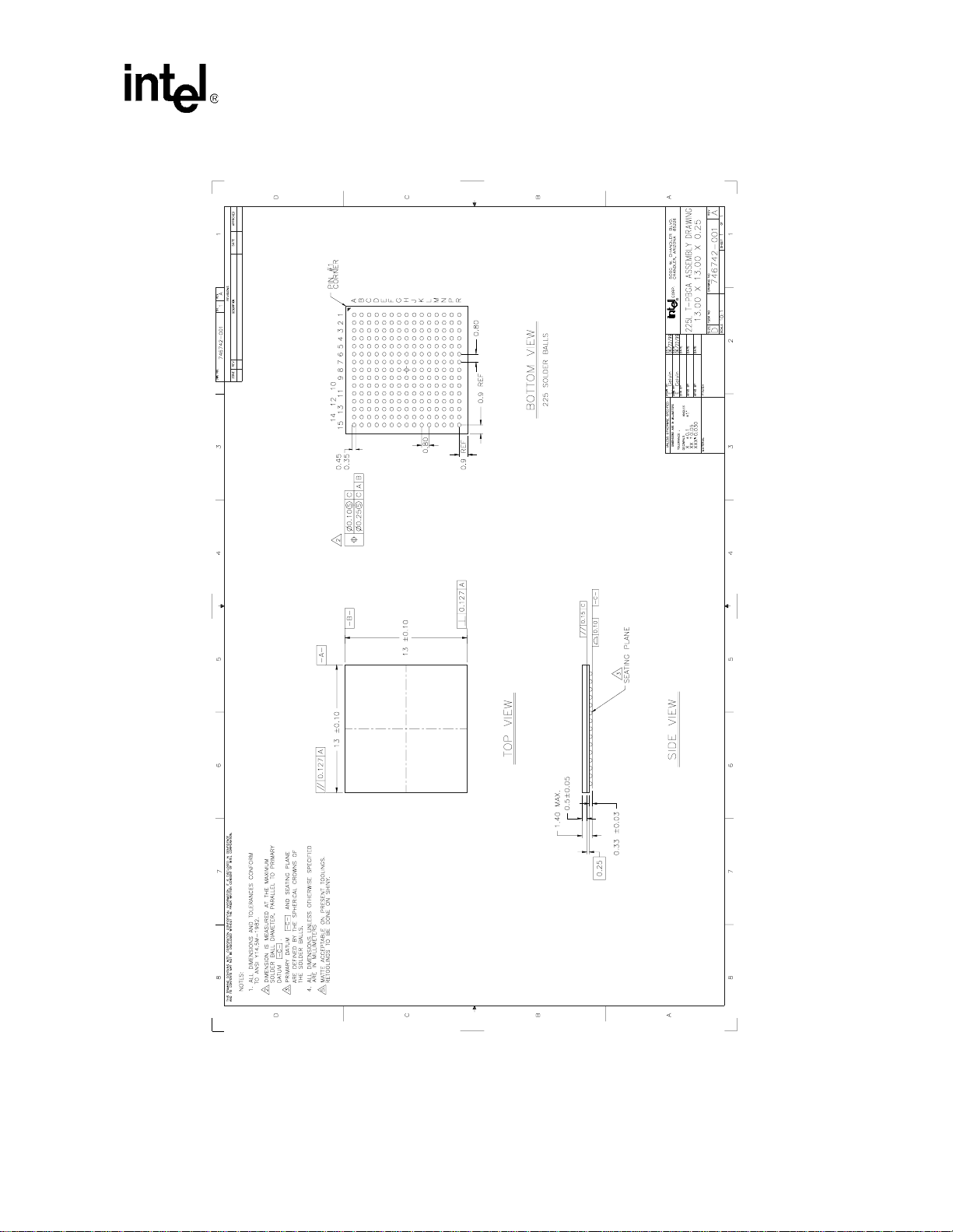

The PXA250 applications processor package is: 256 pin, 17x17 mBGA – 32-b i t funct ionality . The

PXA210 applications processor package is: 225 pin, 13x13 MMAP – 16-bit functionality, a subset

of the PXA250 applications processor feature set.

Section 1.2.1, “Package Introduction” contains a breakdown of the features supported by the two

different packages.

1.2 Package Information

This section describes the package types, pinouts, and signal descriptions.

1.2.1 Package Introduction

Package features of the PXA250 applications processor are:

• Core frequencies supported - 100 MHz - 400 MHz

1-2 PXA250 and PXA210 Applications Processors Design Guide

Page 11

Introduction

• System memory interface

—100MHz SDRAM

— 4 MB to 256 MB of SDRAM memory

— Support for 16, 64, 12 8, or 256 Mbit DRAM techno l o gies

— 4 Banks of SDRAM, each supporting 64 MB of memory

— Clock enable (1 CKE pin is provided to put the entire SDRAM interface into self refresh)

— Supports as many as 6 static memory devices (SRAM, Flash, or VLIO)

• PCMCIA/Compact Flash card control pins

• LCD Controller pins

• Full Function UART

• Bluetooth UART

• MMC Controller pins

• SSP Pins

• USB Client Pins

• AC’97 Controller Pins

• Standard UART Pins

2

• I

C Controller pins

• PWM pins

• 15 dedicated GPIOs pins

• Integrated JTAG support

Package features of the PXA210 applications processor are:

• Core frequencies supported – 100 MHz, 133 MHz, 200 MHzSystem memory interface

— 100 MHz SDRAM, 16-bit only

— 2 MB to 128 MB of SDRAM memory

— Support for 16, 64, 12 8, or 256 Mbit DRAM techno l o gies

— 2 Banks of SDRAM, each supporting 64 MB of memory

— Supports as many as 6 static memory devices (SRAM, Flash, or VLIO)

• Clock enable (1 CKE pin is provided to put the entire SDRAM interface into self refresh)

• LCD Controller pins

• Bluetooth UART

• MMC Controller pins

• SSP Pins

• USB Client Pins

• AC97 Con t roller Pins

• Standard UART Pins

PXA250 and PXA210 Applications Processors Design Guide 1-3

Page 12

Introduction

2

• I

C Controller pins

• PWM pins

• 2 dedicated GPIOs pins

• Integrated JTAG support

1.2.2 Signal Pin Descriptions

Table 1-3 defines the signal descriptions for the applications processor.

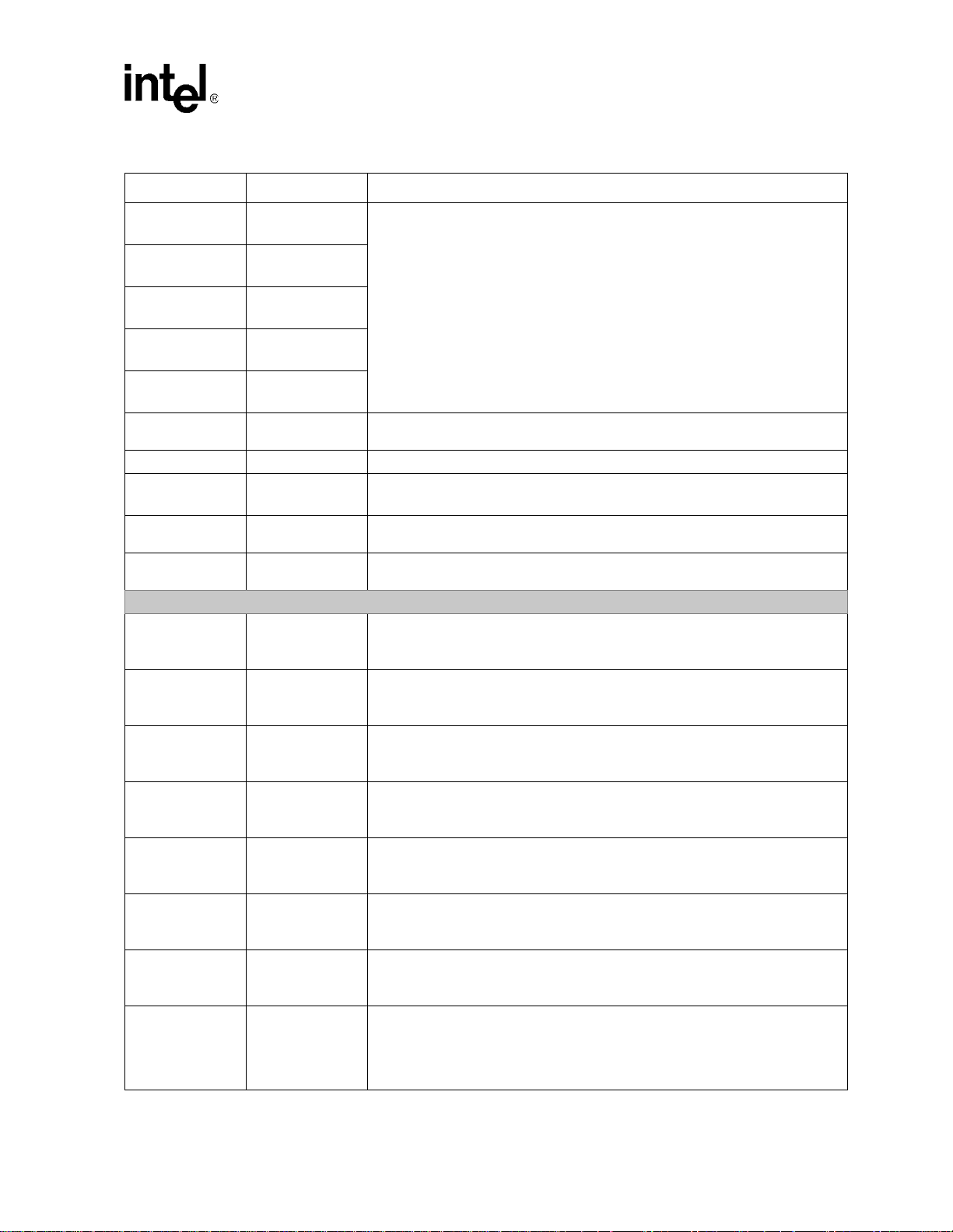

Table 1-3. Signal Pin Descriptions (Sheet 1 of 7)

Name Type Description

Memory Controller Pins

MA[25:0] OCZ Memory address bus. This bus signals the address requested for memory accesses.

MD[15:0] ICOCZ Memory data bus. D[15:0] are used for 16-bit and 32-bit data modes.

Memory data bus. D[31:16]: These signals are the upper memory data bus address

MD[31:16] ICOCZ

nOE OCZ

nWE OCZ Memory write enable. Connect this signal to the write enables of memory devices.

nSDCS[3:0] OCZ

DQM[3:0] OCZ

nSDRAS OCZ

nSDCAS OCZ

SDCKE[0] OC

SDCKE[1] OC

SDCLK[2:0] OCZ

bits.

See Note [1]

Memory output enable. Connect this signal to the output enables of memory devices

to control their data bus drivers.

SDRAM CS for banks 0 through 3. Connect these signals to the chip select (CS) pins

for SDRAM. nSDCS0 is a three-state signal, while nSDCS1-3 are not three-state.

SDRAM DQM for data bytes 0 through 3. Connect these signals to the data output

mask enables (DQM) for SDRAM.

SDRAM RAS. Connect this signal to the row address strobe (RAS) pins for all banks

of SDRAM.

SDRAM CAS. Connect this signal to the column address strobe (CAS) pins for all

banks of SDRAM.

SDRAM and/or Synchronous Static Memory/SDRAM-like synchronous Flash clock

enable clock enable.

ConnectSDCKE[0] to the CKE pins of SMROM and SDRAM-timing Synchronous

Flash.

The memory controller provides control regist er bits for deassertion of each SDCKE

pin.

SDRAM device clock enable.

Connect SDCKE[1] to the clock enable pins of SDRAM. It is de-asserted (held low)

during sleep. SDCKE[1] is always deasserted upon reset.

The memory controller provides control regist er bits for deassertion of each SDCKE

pin.

See Note [1]

Use these clocks to clock synchronous memory devices:

SDCLK0 - connected to either SMROM or synchronous Flash devices

SDCLK1 - connected to SDRAM banks 0/1

SDCLK2 - connected to SDRAM banks 2/3

See Note [1]

1-4 PXA250 and PXA210 Applications Processors Design Guide

Page 13

Introduction

Table 1-3. Signal Pin Descriptions (Sheet 2 of 7)

Name Type Description

nCS[5]/

GPIO[33]

nCS[4]/

GPIO[80]

nCS[3]/

GPIO[79]

nCS[2]/

GPIO[78]

nCS[1]/

GPIO[15]

nCS[0] ICOCZ

RD/nWR OCZ Read/Write for static interface. Intended for use as a steering signal for buffering logic

RDY/

GPIO[18]

MBGNT/GP[13] ICOCZ

MBREQ/GP[14] ICOCZ

PCMCIA/CF Control Pins - PXA250 Applications Processor only

nPOE/ GPIO[48] ICOCZ

nPWE/

GPIO[49]

nPIOW/

GPIO[51]

nPIOR/

GPIO[50]

nPCE[2:1]/

GPIO[53, 52]

nIOIS16/

GPIO[57]

nPWAIT/

GPIO[56]

nPSKTSEL/

GPIO[54]

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

Static chip selects. These signals are chip selects to static memory devices such as

ROM and Flash. They are individually programmable in the memory configuration

registers. nCS[5:3] may be used with variable data latency variable latency I/O

devices.

See Note [2]

Static chip select 0. This is the chip select for the boot memory. nCS[0] is a dedicated

pin.

Variable Latency I/O Ready pin (input)

See Note [2]

Memory Controller grant. (output) Notifies an external device that it has been granted

the system bus.

Memory Controller alternate bus master request. (input) Allows an external device to

request the system bus from the Memory Controller.

PCMCIA output enable. Output PCMCIA signal that performs reads from memory and

attribute space.

See Note [2]

PCMCIA write enable. Output signal that performs writes to memory and attribute

space.

See Note [2]

PCMCIA I/O write. Output signal that performs write transactions to the PCMCIA I/O

space.

See Note [2]

PCMCIA I/O read. Output signal that performs read transactions from the PCMCIA I/O

space.

See Note [2]

PCMCIA card enable. Output signals that selects a PCMCIA card. Bit one enables the

high byte lane and bit zero enables the low byte lane.

See Note [2]

I/O Select 16. Input signal from the PCMCIA card that indicates the current address is

a valid 16 bit wide I/O address.

See Note [2]

PCMCIA wait. Input signal that is driven low by the PCMCIA card to extend the length

of the transfers to/from the applications processor.

See Note [2]

PCMCIA socket select. Output signal used by external steering logic to route control,

address, and data signals to one of the two PCMCIA sockets. When PSKTSEL is low,

socket zero is selected. When PSKTSEL is high, socket one is selected. This signal

has the same timing as address.

See Note [2]

PXA250 and PXA210 Applications Processors Design Guide 1-5

Page 14

Introduction

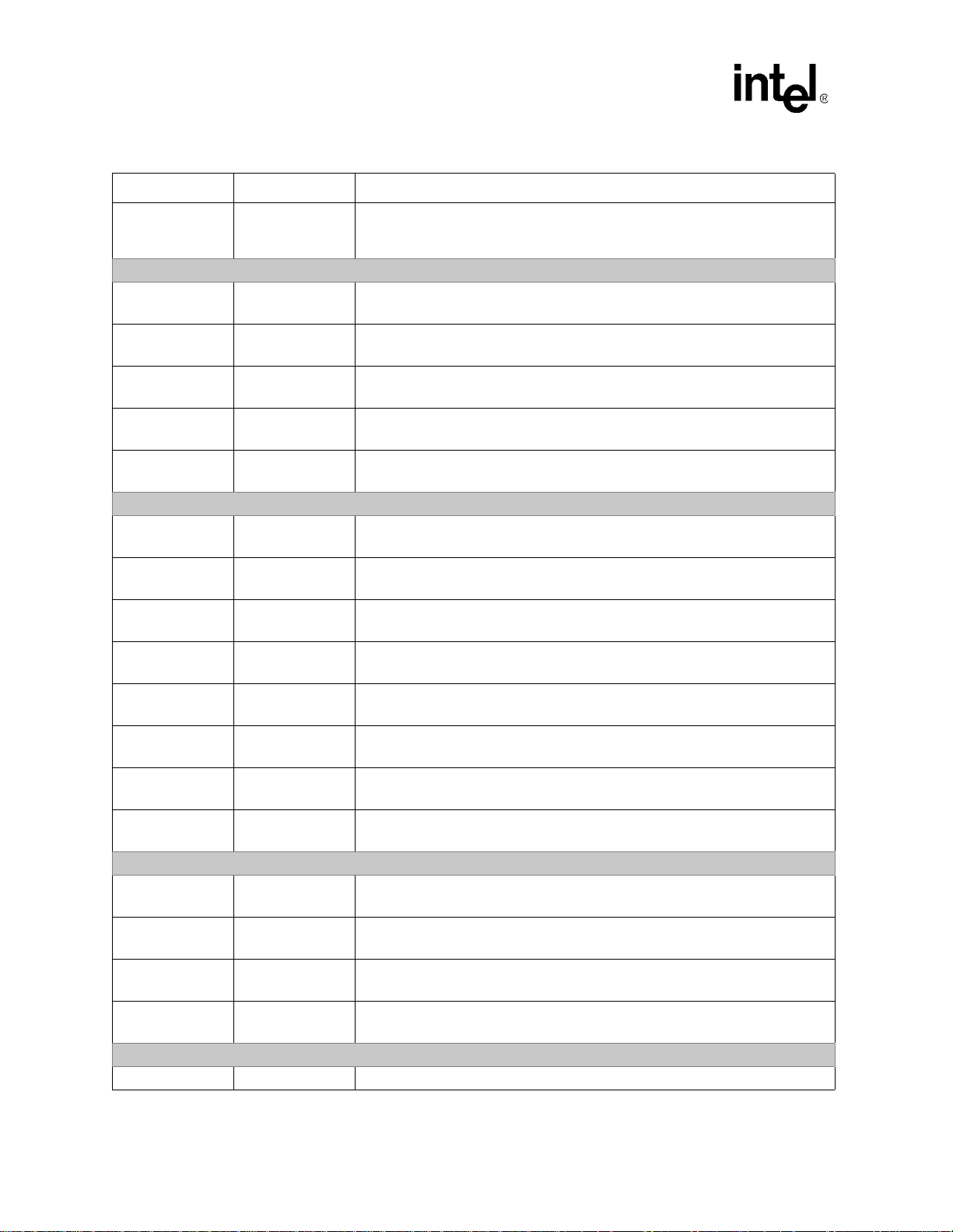

Table 1-3. Signal Pin Descriptions (Sheet 3 of 7)

Name Type Description

nPREG/

GPIO[55]

LCD Controller Pins

L_DD(15:0)/

GPIO[73:58]

L_FCLK/

GPIO[74]

L_LCLK/

GPIO[75]

L_PCLK/

GPIO[76]

L_BIAS/

GPIO[77]

Full Function UART Pins

FFRXD/

GPIO[34]

FFTXD/

GPIO[39]

FFCTS/

GPIO[35]

FFDCD/

GPIO[36]

FFDSR/

GPIO[37]

FFRI/

GPIO[38]

FFDTR/

GPIO[40]

FFRTS/

GPIO[41]

Bluetooth UART Pins

BTRXD/

GPIO[42]

BTTXD/

GPIO[43]

BTCTS/

GPIO[44]

BTRTS/

GPIO[45]

MMC Controller Pins

MMCMD ICOCZ Multimedia Card Command pin (I/O)

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

PCMCIA register select. Output signal that indicates the target address is attribute

space, on a memory transaction. This signal has the same timing as address.

See Note [2]

LCD Controller display data

See Note [2]

LCD Frame clock

See Note [2]

LCD Line clock

See Note [2]

LCD pixel clock

See Note [2]

AC Bias Drive

See Note [2]

Full Function UART Receive pin

See Note [2]

Full Function UART Transmit pin

See Note [2]

Full Function UART Clear-to-Send pin

See Note [2]

Full Function UART Data-Carrier-Detect Pin

See Note [2]

Full Function UART Data-Set-Ready Pin:

See Note [2]

Full Function UART Ring Indicator Pin

See Note [2]

Full Function UART Data-Terminal-Ready pin

See Note [2]

Full Function UART Ready-to-Send pin

See Note [2]

Bluetooth UART Receive pin

See Note [2]

Bluetooth UART Transmit pin

See Note [2]

Bluetooth UART Clear-to-Send pin

See Note [2]

Bluetooth UART Data-Terminal-Ready pin

See Note [2]

1-6 PXA250 and PXA210 Applications Processors Design Guide

Page 15

Table 1-3. Signal Pin Descriptions (Sheet 4 of 7)

Name Type Description

MMDAT ICOCZ Multimedia Card Data Pin (I/O)

MMCCLK/GP[6] ICOCZ MMC clock. (output) Clock signal for the MMC Controller.

MMCCS0/GP[8] ICOCZ MMC chip select 0. (output) Chip select 0 for the MMC Controller.

MMCCS1/GP[9] ICOCZ MMC chip select 1. (output) Chip select 1 for the MMC Controller.

SSP Pins

SSPSCLK/

GPIO[23]

SSPSFRM/

GPIO[24]

SSPTXD/

GPIO[25]

SSPRXD/

GPIO[26]

SSPEXTCLK/

GPIO[27]

USB Client Pins

USB_P IAOA USB Client port positive Pin of differential pair.

USB_N IAOA USB Client port negative Pin of differential pair.

AC97 Controller Pins

BITCLK/

GPIO[28]

SDATA_IN0/

GPIO[29]

SDATA_IN1/

GPIO[32]

SDATA_OUT/

GPIO[30]

SYNC/

GPIO[31]

nACRESET OC

Standard UART and ICP Pins

IRRXD/

GPIO[46]

IRTXD/

GPIO[47]

I2C Controller Pins

SCL ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

ICOCZ

Synchronous Serial Port Clock (output)

See Note [2]

Synchronous serial port Frame Signal (output)

See Note [2]

Synchronous serial port transmit (output)

See Note [2]

Synchronous serial port receive (input)

See Note [2]

Synchronous Serial port external clock (input)

See Note [2]

AC97 Audio Port bit clock (output)

See Note [2]

AC97 Audio Port data in (input)

See Note [2]

AC97 Audio Port data in (input)

See Note [2]

AC97 Audio Port data out (output)

See Note [2]

AC97 Audio Port sync signal (output)

See Note [2]

AC97 Audio Port reset signal (output)

This pin is a dedicated output.

IrDA Receive signal (input).

See Note [2]

IrDA Transmit signal (output).

Transmit pin for both the SIR and FIR functions.

See Note [2]

I2C clock (Bidirectional)

Bidirectional signal. When it is driving, it functions as an open collector device and

requires a pull up resistor. As an input, it expects standard CMOS levels.

Introduction

PXA250 and PXA210 Applications Processors Design Guide 1-7

Page 16

Introduction

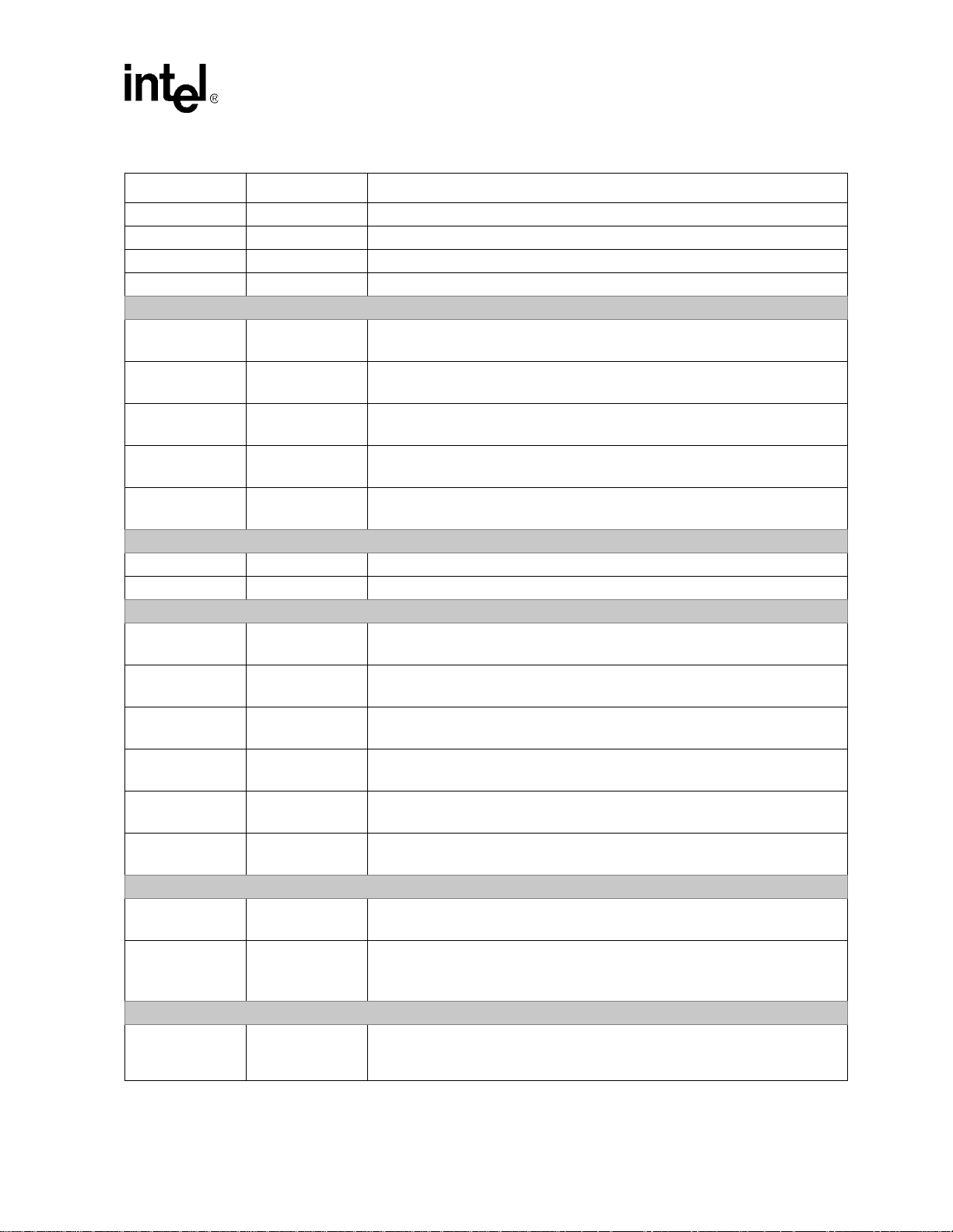

Table 1-3. Signal Pin Descriptions (Sheet 5 of 7)

Name Type Description

I2C Data signal (bidirectional).

SDA ICOCZ

PWM Pins

PWM[1:0]/

GPIO[17,16]

Dedicated GPIO Pins

GPIO[1:0] ICOCZ

GPIO[14:2]) ICOCZ

GPIO[22:21] ICOCZ

Crystal Pins

PXTAL IA Input connection for 3.6864 Mhz crystal

PEXTAL OA Output connection for 3.6864 Mhz crystal

TXTAL IA Input connection for 32.768 khz crystal

TEXTAL OA Output connection for 32.768 khz crystal

48MHz/GP[7] ICOCZ 48 MHz clock. (output) Peripheral clock output derived from the PLL.

RTCCLK/GP[10] I COC Z Real time clock. (output) HZ output derived from the 32kHz or 3.6864MHz output.

3.6MHz/GP[11] ICOCZ 3.6864 MHz clock. (output) Output from 3.6864 MHz oscillator.

32kHz/GP[12] ICOCZ 32 kHz clock. (output) Output from the 32 kHz oscillator.

Miscellaneous Pins

BOOT_SEL

[2:0]

PWR_EN OCZ

nBATT_FAULT IC

ICOCZ

IC

Bidirectional signal. When it is driving, it functions as an open collector device and

requires a pull up resistor. As an input, it expects standard CMOS levels.

Pulse Width Modulation channels 0 and 1 (outputs)

See Note [2]

General Purpose I/O: These two pins are contained in both the PXA250

applications processors. They are preconfigured at a hard reset (nRESET) as wakeup

sources for both rising and falling edge detects.

These GPIOs do not have alternate functions and are intended to be used as the main

external sleep wakeup stimulus.

General Purpose I/O

See Note [1]

See Note [2]

General Purpose I/O

Additional general purpose I/O pins.

Boot programming select pins. These pins are sampled to indicate the type of boot

device present per the following table;

BOOT_SEL[2:0] Description

000Asynchronous 32-bit ROM

001Asynchronous 16-bit ROM

100One 32-bit SMROM

101One 16 bit SMROM

110Two 16 bit SMROMs (32 bit bus)

111Reserved

Power Enable. Active high Output.

PWR_EN enables the external power supply. Negating it signals the power supply

that the system is going into sleep mode and that the VDD power supply should be

removed.

Battery Fault. Active low input.

The assertion of nBATT_FAULT causes the applications processor

Mode.The applications processor

is asserted. Use nBATT_F AUL T signal to flag a critical power failure, such as the main

battery being removed. Minimum assertion time for nBATT_FAULT is 1ms.

will not recognize a wakeup event while this signal

and PXA210

to enter Sleep

1-8 PXA250 and PXA210 Applications Processors Design Guide

Page 17

Introduction

Table 1-3. Signal Pin Descriptions (Sheet 6 of 7)

Name Type Description

VDD Fault. Active low input.

nVDD_FAULT IC

nRESET IC

nRESET_OUT OC

JTAG Pins

nTRST IC

TDI IC JTAG test interface data input. Note this pin has an internal pullup resistor.

TDO OCZ

TMS IC JTAG test interface mode select. Note this pin has an internal pullup resistor.

TCK IC

TEST IC Test Mode. You should ground this pin. This pin is for manufacturing purposes only.

TESTCLK I C Test Clock. Use this pin for test purposes only. An end user should ground this pin.

Power and Ground Pins

VCC SUP

VSS SUP

PLL_VCC SUP P ositive supply for PLLs and oscillators must be shorted to VCC.

PLL_VSS SUP Gr ound supply for the PLL. Must be connected to common ground plane on the PCB.

VCCQ SUP

VSSQ SUP

VCCN SUP

nVDD_FAULT causes the applications processor

is ignored after a wakeup event until the power supply timer completes (approximately

10 ms). use the nVDD_FAUL T signal to flag a low battery . Minimum assertion time for

nVDD_FAULT is 1 ms.

Hard reset. Active low input.

nRESET is a level sensitive input which starts the processor from a known address. A

LOW level causes the current instruction to terminate abnormally, and all on-chip state

to be reset. When nRESET is driven HIGH, the processor re-starts from address 0.

nRESET must remain LOW until the power supply is stable and the internal 3.6864

MHz oscillator has come up to speed. While nRESET is LOW the processor performs

idle cycles.

Reset Out. Active low output.

This signal is asserted when nRESET is asserted and de-asserts after nRESET is

negated but before the first instruction fetch. nRESET_OUT is also asserted for “soft”

reset events (sleep, watchdog reset, GPIO reset)

JTAG Test Interface Reset. Resets the JTAG/Debug port. If JTAG/Debug is used,

drive nTRST from low to high either before or at the same time as nRESET. If JTAG is

not used, nTRST must be either tied to nRESET or tied low. Intel recommends that a

JTAG/Debug port be added to all systems for debug and download. See Chapter 9 for

details.

JTAG test interface data output. Note this pin does NOT have an internal pullup

resistor.

JTAG test interface reference Clock. TCK is the reference clock for all transfers on the

JTAG test interface.

NOTE: This pin needs an external pulldown resistor.

Positive supply for the internal logic. Connect this supply to the low voltage (.85 -

1.65v) supply on the PCB.

Ground supply for the internal logic. Connect these pins to the common ground plane

on the PCB.

Positive supply for all CMOS I/O except memory bus and PCMCIA pins. Connect

these pins to the common 3.3v supply on the PCB.

Ground supply for all CMOS I/O except memory bus and PCMCIA pins. Connect

these pins to the common ground plane on the PCB.

Positive supply for memory bus and PCMCIA pins. Connect these pins to the common

3.3 V or 2.5 V supply on the PCB.

to enter Sleep Mode. nVDD_FAULT

PXA250 and PXA210 Applications Processors Design Guide 1-9

Page 18

Introduction

Table 1-3. Signal Pin Descriptions (Sheet 7 of 7)

Name Type Description

VSSN SUP

BATT_VCC SUP

NOTES:

1. Not pinned out for the PXA210 applications processor.

2. GPIO Reset Operation: After any reset, these pins are configured as GPIO inputs by default. The input buffers for these pins

are disabled to prevent current drain and must be enabled prior to use by clearing the Read Disable Hold (RDH) bit.

To use a GPIO pin as an alternate function, follow this sequence:

1) Program the pin to the desired direction (input or output) using the GPIO Pin Direction Registers (GPDR).

2) Enable the input buffer by clearing the RDH bit, described above.

3) If needed, select the desired alternate function by programming the proper bits in the GPIO Alternate Function

Register (GAFR).

Ground supply for memory bus and PCMCIA pins. Connect these pins to the common

ground plane on the PCB.

Backup battery connection. Connect this pin to the backup battery supply. If a backup

battery is not required then this pin may be connected to the common 3.3v supply on

the PCB.

1-10 PXA250 and PXA210 Applications Processors Design Guide

Page 19

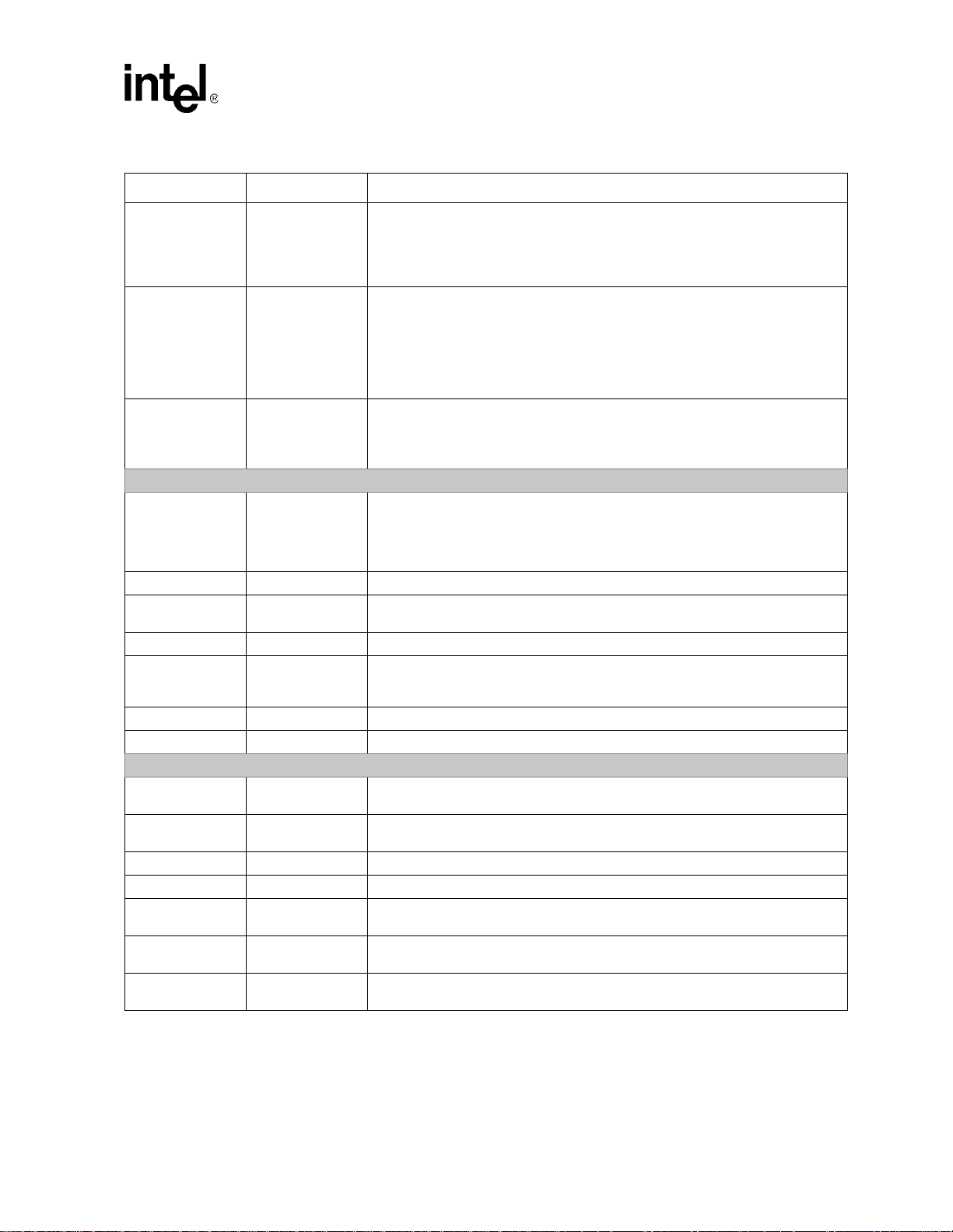

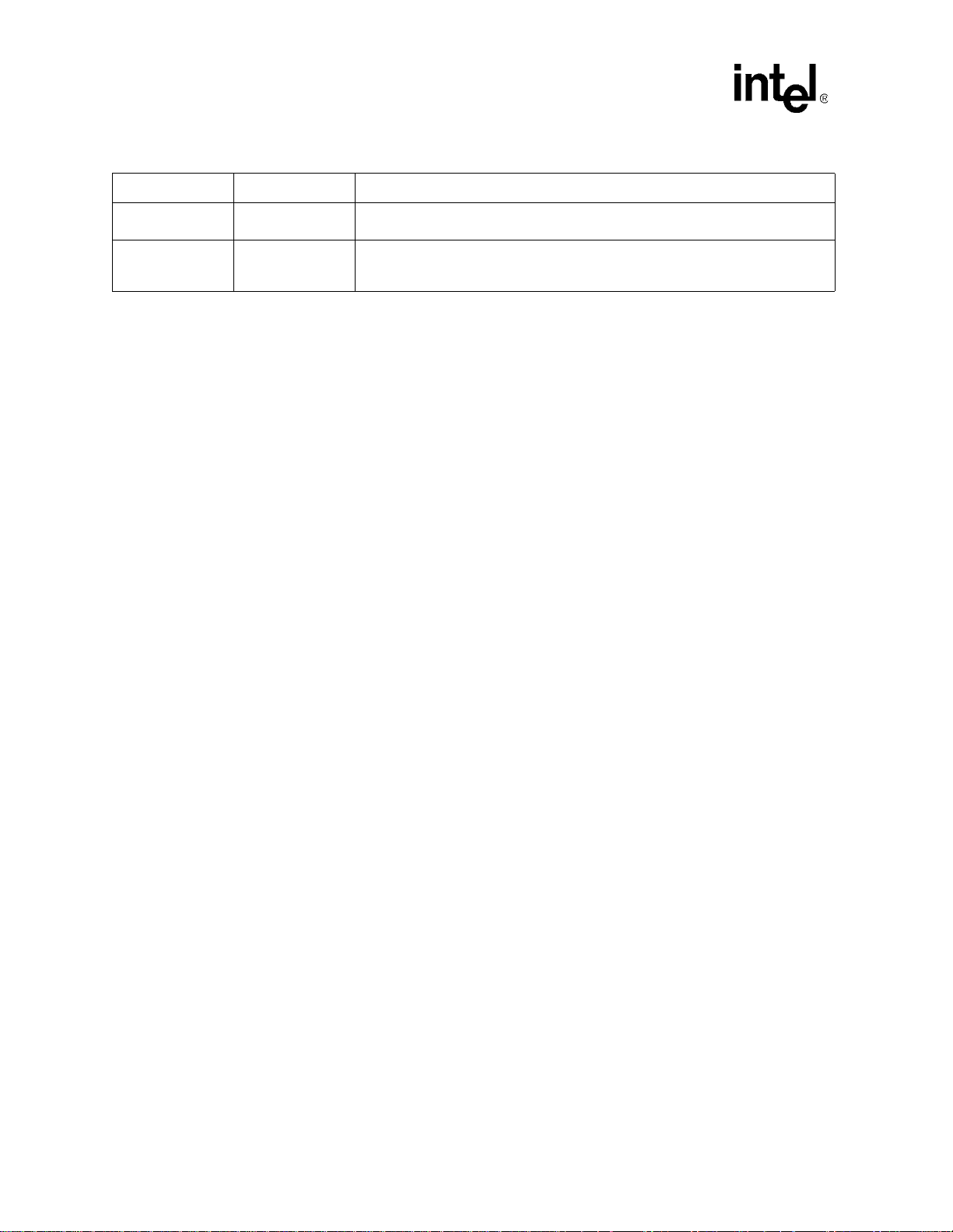

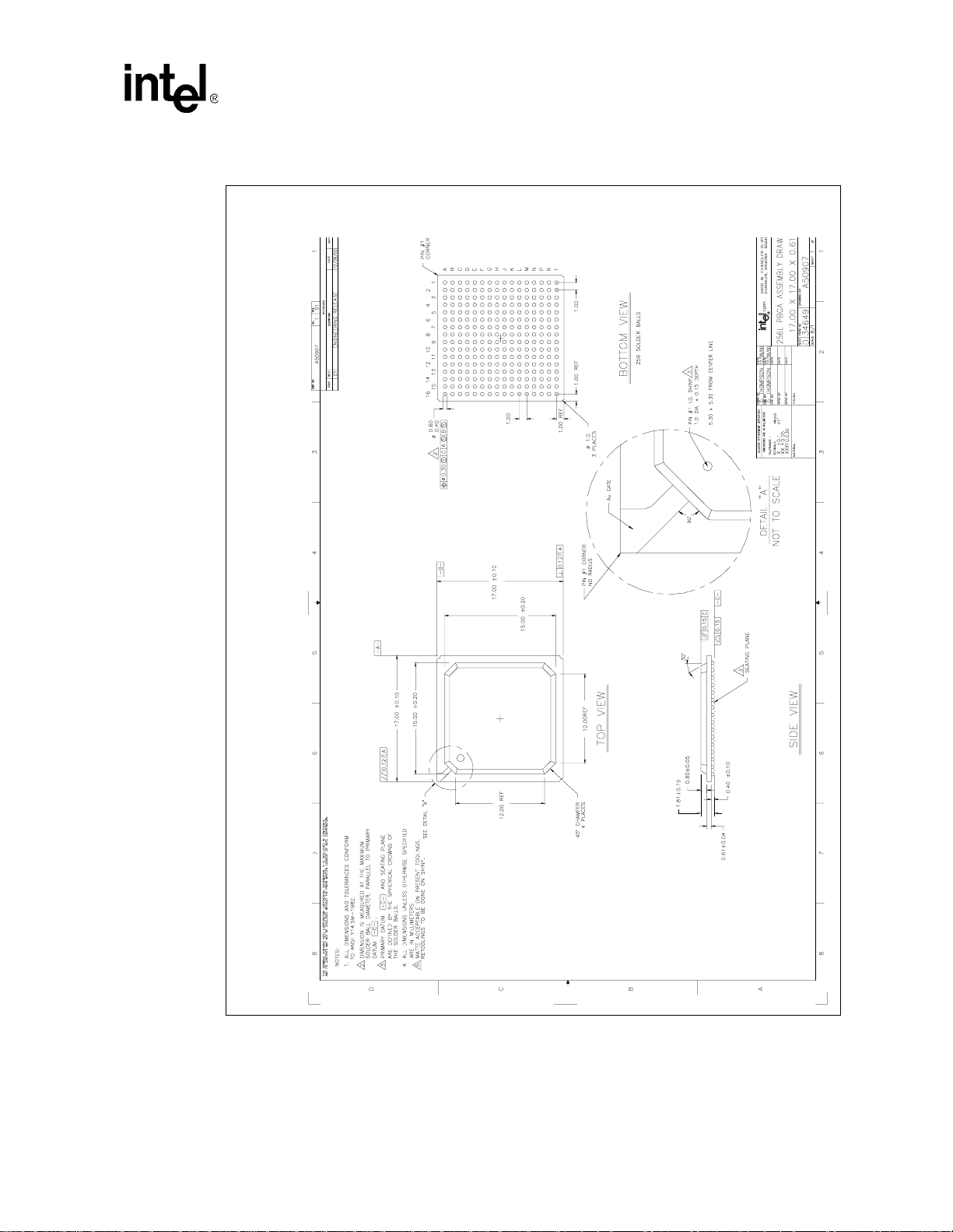

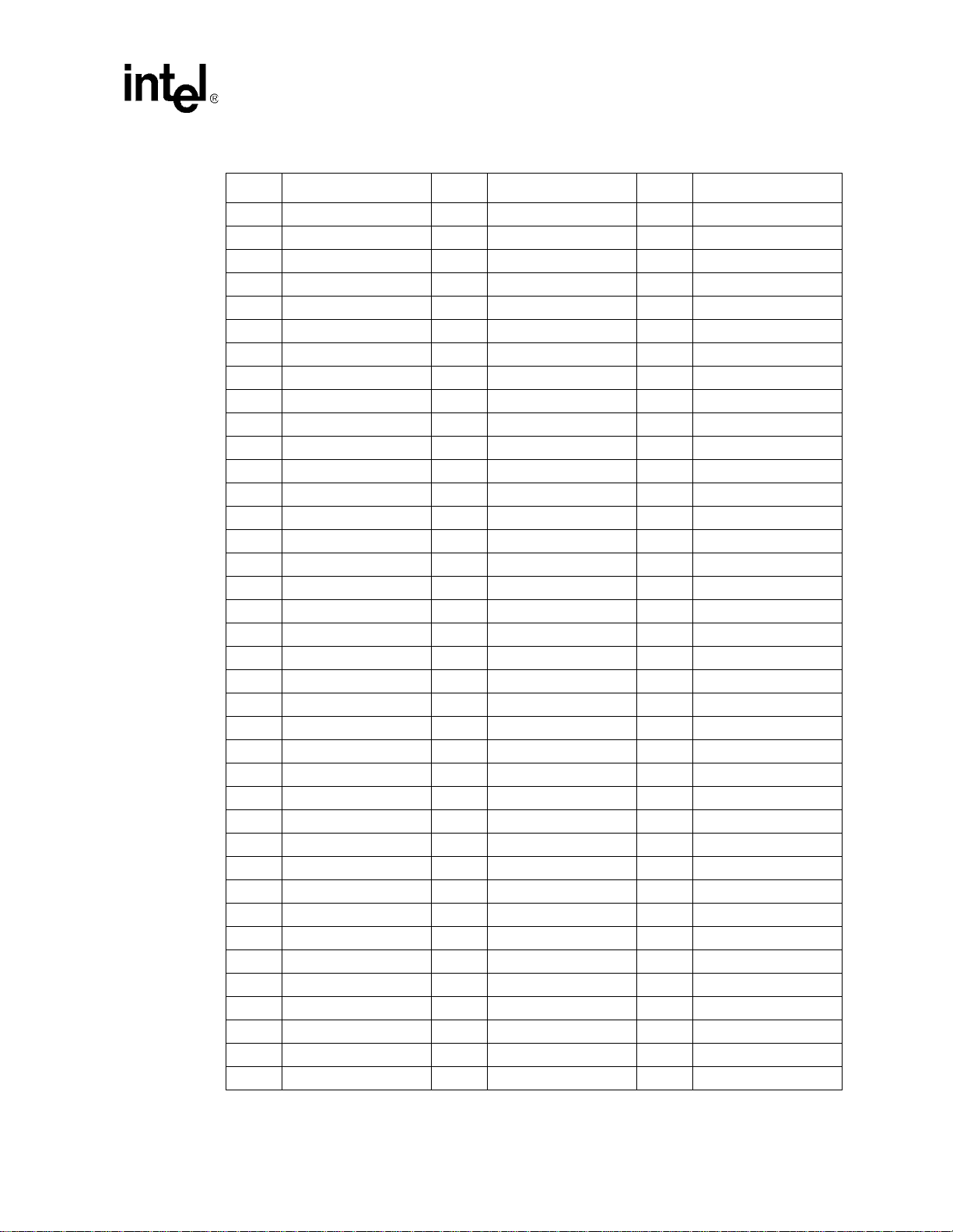

Figure 1-2. PXA250 Applications Processor

Introduction

PXA250 and PXA210 Applications Processors Design Guide 1-11

Page 20

Introduction

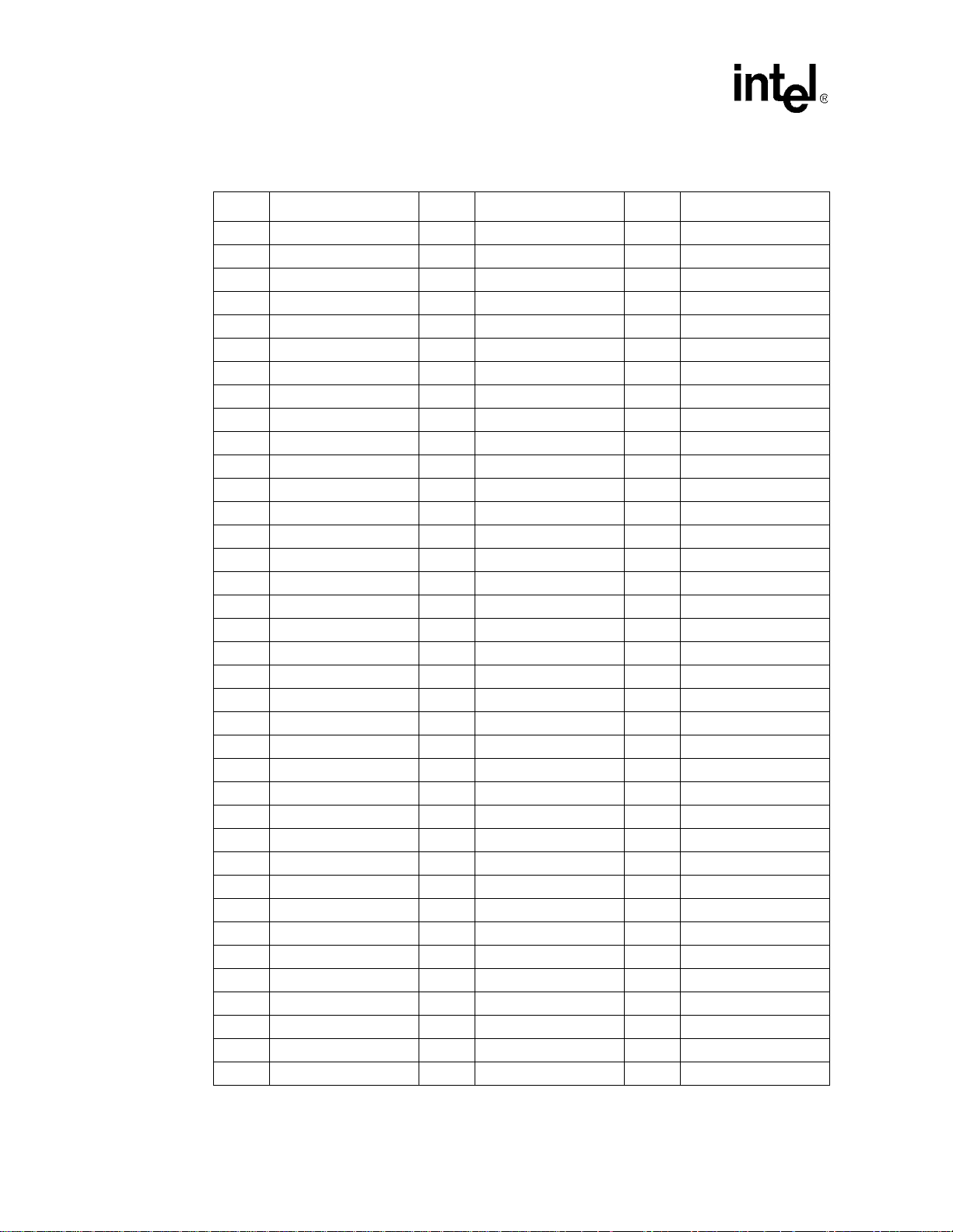

T a ble 1-4. PXA250 Applications Processor Pinout — Ballpad Number Order (Sheet 1 of 3)

Ball # Signal Ball # Signal Ball # Signal

A1 VCCN F7 GPIO[10] L13 GPIO[2]

A2 L_DD[13]/GPIO[71] F8 FFRTS/GPIO[41] L14 VSSQ

A3 L_DD[12]/GPIO[70] F9 SSPSCLK/GPIO[23] L15 TEXTAL

A4 L_DD[11]/GPIO[69] F10 FFDTR/GPIO[40] L16 TXTAL

A5 L_DD[9]/GPIO[67] F11 VCC M1 MA[14]

A6 L_DD[7]/GPIO[65] F12 GPIO[9] M2 MD[21]

A7 GPIO[11] F13 BOOT_SEL[2] M3 MA[15]

A8 L_BIAS/GPIO[77] F14 GPIO[8] M4 VCCN

A9 SSPRXD/GPIO[26] F15 VSSQ M5 MD[1]

A10 SDATA_OUT/GPIO[30] F16 VSSQ M6 MD[6]

A11 SDA G1 MA[0] M7 MD[7]

A12 FFDCD/GPIO[36] G2 VSSN M8 DQM[0]

A13 FFRXD/GPIO[34] G3 nSDCS[2] M9 MD[8]

A14 FFCTS/GPIO[35] G4 nWE M10 MD[15]

A15 BTCTS/GPIO[44] G5 nOE M11 BATT_VCC

A16 SDATA_IN1/GPIO[32] G6 nSDCS[1] M12 GPIO[22]

B1 DQM[1] G7 VCC M13 nPREG/GPIO[55]

B2 DQM[2] G8 VSSQ M14 VCCN

B3 L_DD[15]/GPIO[73] G9 VCC M15 VSSN

B4 GPIO[14] G10 VSSQ M16 nIOIS16/GPIO[57]

B5 GPIO[13] G11 TESTCLK N1 MD[22]

B6 GPIO[12] G12 TEST N2 VSSN

B7 L_DD[3]/GPIO[61] G13 BOOT_SEL[1] N3 MA[16]

B8 L_PCLK/GPIO[76] G14 VCCQ N4 MD[0]

B9 SSPEXTCLK/GPIO[27] G15 GPIO[7] N5 VCCN

B10 FFRI/GPIO[38] G16 BOOT_SEL[0] N6 MD[4]

B11 FFDSR/GPIO[37] H1 MA[2] N7 VCCN

B12 USB_N H2 MA[1] N8 nCS[0]

B13 BTRXD/GPIO[42] H3 MD[16] N9 VCCN

B14 BTRTS/GPIO[45] H4 VCCN N10 MD[13]

B15 IRRXD/GPIO[46] H5 MD[17] N11 VCCN

B16 MMDAT H6 MA[3] N12 DREQ[0]/GPIO[20]

C1 RDY/GPIO[18] H7 VSSQ N13 VCCN

C2 VSSN H8 VSS N14 DREQ[1]/GPIO[19]

C3 L_DD[14]/GPIO[72] H9 VSS N15 GPIO[21]

C4 VSSQ H10 VCC N16 nPWAIT/GPIO[56]

C5 L_DD[8]/GPIO[66] H11 nTRST P1 MA[17]

1-12 PXA250 and PXA210 Applications Processors Design Guide

Page 21

Introduction

Table 1-4. PXA250 Applications Processor Pinout — Ballpad Number Order (Sheet 2 of 3)

Ball # Signal Ball # Signal Ball # S ignal

C6 VCCQ H12 TCK P2 MA[19]

C7 L_DD[2]/GPIO[60] H13 TMS P 3 VCCN

C8 VSSQ H14 GPIO[6] P4 MA[25]

C9 BITCLK/GPIO[28] H15 TDI P5 MA[23]

C10 VCCQ H16 TDO P6 MD[24]

C11 VSSQ J1 MA[7] P7 MD[26]

C12 USB_P J2 VSSN P8 MD[27]

C13 VCCQ J3 MA[6] P9 nCS[2]/GPIO[78]

C14 V SSQ J4 MD[18] P10 MD[29]

C15 IRTXD/GPIO[47] J5 MA[5] P11 MD[12]

C16 V SS J6 MA[4] P12 MD[31]

D1 SDCLK[2] J7 VCC P13 nPO E/ GPIO[ 48]

D2 SDCLK[0] J8 VSS P 14 nPCE[1]/GPIO[52]

D3 RDnWR J9 VSS P15 VSSN

D4 VCCN J10 VSS Q P16 nPSKTSEL/GPIO[54]

D5 L_DD[10]/GPIO[68] J11 GPIO[5] R1 MA[18]

D6 L_DD[5]/GPIO[63] J12 GPIO[4] R2 VSSN

D7 L_DD[1]/GPIO[59] J13 nRESET R3 MA[20]

D8 L_LCLK/GPIO[75] J14 VSSQ R4 VSSN

D9 SSPTXD/GPIO[25] J15 PLL_VCC R5 MA[22]

D10 nA CRESET J16 PLL_VSS R6 VSSN

D11 SCL K1 MA[8] R7 MD[25]

D12 PWM[1]/GPIO[17] K2 MA[9] R8 VSSN

D13 B TTXD/GPIO[43] K3 MD[19] R9 MD[10]

D14 MMCMD K4 VCCN R10 VSSN

D15 VCCQ K5 MA[10] R11 MD[30]

D16 VSSQ K6 MA[11] R12 VSSN

E1 nSDRAS K7 VSSQ R13 nCS[4]/GPIO[80]

E2 VSSN K8 VCC R14 VSSN

E3 SDCKE[1] K9 VSSQ R15 nPIOW/GPIO[51]

E4 SDCKE[0] K10 VCC R16 nPCE[2]/GPIO[53]

E5 L_DD[6]/GPIO[64] K11 nRESET_OUT T1 VSS

E6 L_DD[4]/GPIO[62] K 12 nBATT_FAULT T2 VCCN

E7 L_DD[0]/GPIO[58] K13 nVDD_FAULT T3 MD[23]

E8 L_FCLK/GPIO[74] K 14 GPIO[3] T4 MA[21]

E9 SSPSFRM/GPIO[24] K15 PXTAL T5 MA[24]

E10 SDATA_IN0/GPIO[29] K16 PEXTAL T6 MD[3]

E11 SYNC/GPIO[31] L1 MA[12] T7 M D[5]

PXA250 and PXA210 Applications Processors Design Guide 1-13

Page 22

Introduction

T a ble 1-4. PXA250 Applications Processor Pinout — Ballpad Number Order (Sheet 3 of 3)

Ball # Signal Ball # Signal Ball # Signal

E12 PWM[0]/GPIO[16] L2 VSSN T8 nCS[1]/GPIO[15]

E13 FFTXD/GPIO[39] L3 MA[13] T9 nCS[3]/GPIO[79]

E14 VCCQ L4 MD[20] T10 MD[9]

E15 VSSQ L5 MD[2] T11 MD[11]

E16 VSSQ L6 VCC T12 MD[14]

F1 nSDCS[0] L7 DQM[3] T13 nCS[5]/GPIO[33]

F2 nSDCS[3] L8 MD[28] T14 nPWE/GPIO[49]

F3 nSDCAS L9 VCC T15 nPIOR/GPIO[50]

F4 VCCN L10 GPIO[0] T16 VCCN

F5 SDCLK[1] L11 PWR_EN

F6 VSSQ L12 GPIO[1]

1-14 PXA250 and PXA210 Applications Processors Design Guide

Page 23

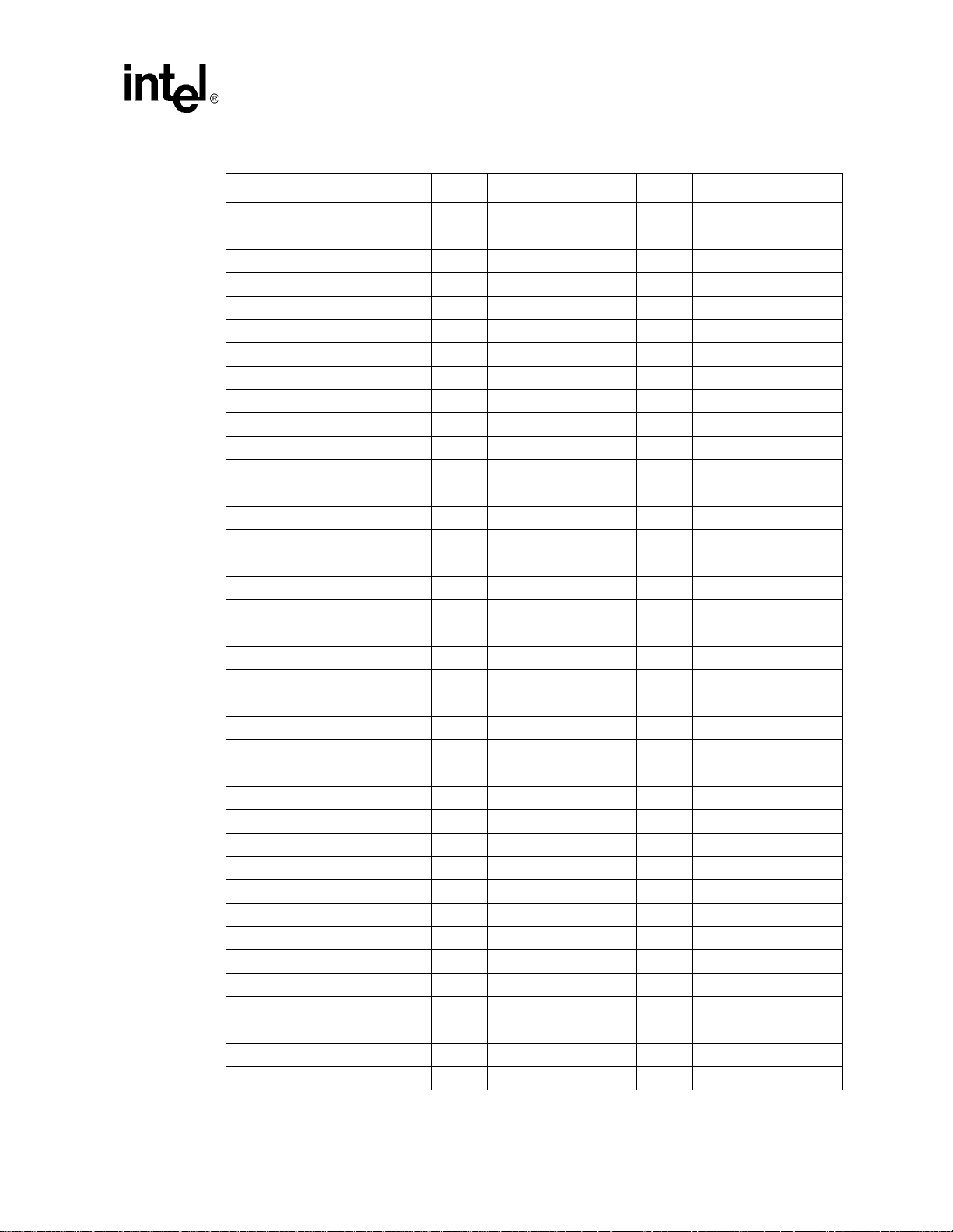

Figure 1-3. PXA210 Applications Processor

φ

Introduction

PXA250 and PXA210 Applications Processors Design Guide 1-15

Page 24

Introduction

T a ble 1-5. PXA210 Applications Processor Pinout — Ballpad Number Order (Sheet 1 of 2)

Ball # Signal Ball # Signal Ball # Signal

A1 DQM[1] F1 VSSN L1 VSSN

A2 L_DD[14]/GPIO[72] F2 nSDCS[0] L2 VCCN

A3 L_DD[10]/GPIO[68] F3 nSDRAS L3 MA[12]

A4 VSSQ F4 nSDCS[1] L4 MA[13]

A5 L_DD[6]/GPIO[64] F5 VCC L5 MA[11]

A6 L_DD[2]/GPIO[60] F6 L_DD[8]/GPIO[66] L6 VSSQ

A7 L_LCLK/GPIO[75] F7 L_FCLK/GPIO[74] L7 MD[2]

A8 SPPSCLK/GPIO[23] F8 SSPRXD/GPIO[26] L8 MD[6]

A9 SPPEXTCLK/GPIO[27] F9 VCC L9 VSSN

A10 nACRESET F10 FFTXD/GPIO[39] L10 MD[11]

A11 PWM[1]/GPIO[17] F11 VCC L11 BATT_VCC

A12 VSSQ F12 VSSQ L12 GPIO[54]

A13 FFRXD/GPIO[34] F13 TESTCLK L13 GPIO[55]

A14 BTCTS/GPIO[44] F14 BOOT_SEL[0] L14 GPIO[57]

A15 IRRXD/GPIO[46] F15 TEST L15 GPIO[0]

B1 RDY/GPIO[18] G1 MA[0] M1 MA[14]

B2 VSSN G2 nOE M2 MA[15]

B3 L_DD[13]/GPIO[71] G3 nWE M3 VCCN

B4 L_DD[9]/GPIO[67] G4 VCCN M4 MA[16]

B5 VSSQ G5 VSSN M5 VCCN

B6 L_DD[3]/GPIO[61] G6 RDnW R M6 VSSN

B7 L_PCLK/GPIO[76] G7 VSS M7 MD[3]

B8 VSSQ G8 VSS M8 MD[7]

B9 BITCLK/GPIO[28] G9 VSS M9 nCS[1]/GPIO[15]

B10 SDA G10 BTRXD/GPIO[42] M10 MD[10]

B11 VSSQ G11 nTRST M11 MD[ 13]

B12 USB_N G12 TDI M12 GPIO[48]

B13 BTRTS/GPIO[45] G13 TCK M13 GPIO[52]

B14 IRTXD/GPIO[47] G14 TMS M14 VSSN

B15 MMDAT G15 TDO M15 GPIO[56]

C1 SDCKE[1] H1 VCCN N1 VSSN

C2 SDCKE[0] H2 VSSN N2 MA[18]

C3 VCCN H3 MA[2] N3 VSS1

C4 L_DD[12]/GPIO[70] H4 MA[1] N4 MA[22]

C5 VCCQ H5 VCC N5 MA[24]

C6 L_DD[4]/GPIO[62] H6 VSSQ N6 VCCN

C7 L_BIAS/GPIO[77] H7 VSS N7 VCC

1-16 PXA250 and PXA210 Applications Processors Design Guide

Page 25

Introduction

Table 1-5. PXA210 Applications Processor Pinout — Ballpad Number Order (Sheet 2 of 2)

Ball # Signal Ball # Signal Ball # S ignal

C8 VCCQ H8 VSS N8 VSSN

C9 SDATA_IN0/GPIO[29] H9 VSS N9 DQM[0]

C10 PWM[0]/GPIO[16] H10 VSSQ N10 VCCN

C11 USB_P H11 VCC N11 MD[12]

C12 BTTXD/GPIO[43] H12 VSSQ N12 VSSN

C13 VSSQ H13 VCC N13 nCS[5]/GPIO[33]

C14 V SS H14 PLL_VCC N14 GPIO[53]

C15 VCCQ H15 PLL_VSS N15 VCCN

D1 VCC J1 MA[5] P1 MA[17]

D2 VSSQ J2 MA[6] P2 VSSN

D3 SDCLK[1] J3 VSSN P3 VCCN

D4 L_DD[15]/GPIO[73] J4 MA[4] P4 MA[23]

D5 VCC J5 MA[3] P5 MD[0]

D6 L_DD[5]/GPIO[63] J6 VSSQ P6 VSSN

D7 L_DD[0]/GPIO[58] J7 VSS1 P7 MD[4]

D8 SPPSFRM/GPIO[24] J8 VSS1 P8 VCCN

D9 SDATA_OUT/GPIO[30] J9 VSS1 P9 nCS[2]/GPIO[78]

D10 SCL J10 VSSQ P10 MD[8]

D11 SDATA_IN1/GPIO[32] J11 nRESET P11 VCCn

D12 B OOT_SEL[1] J12 nRESET_OUT P12 MD[15]

D13 VSSQ J13 P W R_EN P13 VCCN

D14 VSSQ J14 nVDD_FAULT P14 GPIO[50]

D15 VSSQ J15 nBATT_FAULT P15 VSSQ

E1 nSDCAS K1 MA[8] R1 MA[19]

E2 VCCN K2 MA[9] R2 MA[20]

E3 VSSN K3 MA[10] R3 MA[21]

E4 SDCLK[0] K4 MA[7] R4 MA[25]

E5 L_DD[11]/GPIO[69] K5 VCCN R5 MD[1]

E6 L_DD[7]/GPIO[65] K6 VCC R6 VCCN

E7 L_DD[1]/GPIO[59] K7 VSSQ R7 MD[5]

E8 SSPTXD/GPIO[25] K8 VCC R8 nCS[0]

E9 SYNC/GPIO[31] K9 VSSQ R9 nCS[3]/GPIO[79]

E10 VCCQ K10 VCC R10 MD[9]

E11 MMCMD K11 GPIO[1] R11 VSSN

E12 VCCQ K12 TEX TAL R12 MD[14]

E13 VSSQ K13 TXTAL R13 nCS[4]/GPIO[80]

E14 VSSQ K14 PEXTAL R14 nPWE/GPIO[49]

E15 BOOT_SEL[2] K15 PXTAL R15 GPIO[51]

PXA250 and PXA210 Applications Processors Design Guide 1-17

Page 26

Introduction

1-18 PXA250 and PXA210 Applications Processors Design Guide

Page 27

System Memory Interface 2

This section is the design guidelines for the system memory interface.

2.1 Overview

The external memory bus interface for the applications processor supports:

• 100 MHz SDRAM at 3.3 V

• 100 MHz SDRAM at 2.5 V

• Synchronous and asynchronous Burst mode and Page mode Flash

• Synchronous Mask ROM (SMROM)

• Page Mode ROM

• SRAM

• SRAM-like Variable Latency I/O (VLIO)

• PCMCIA expansion memory

• Compact Flash

Use the memory interface configuration registers to program the memory types. Refer to

Figure 1-1, “Applicati ons Processor Block Diagra m” on page 1-2 fo r the block diagram of the

Memory Controller configuration. Refer to Figure 2-1, “Memory Address Map” on page 2-3 for

the applications processor memory map. Refer to Table 2-3, “Normal Mode Memory Address

Mapping” on page 2-6 for alternate mode address mapping.

PXA250 and PXA210 Applications Processors Design Guide 2-1

Page 28

System Memory Interface

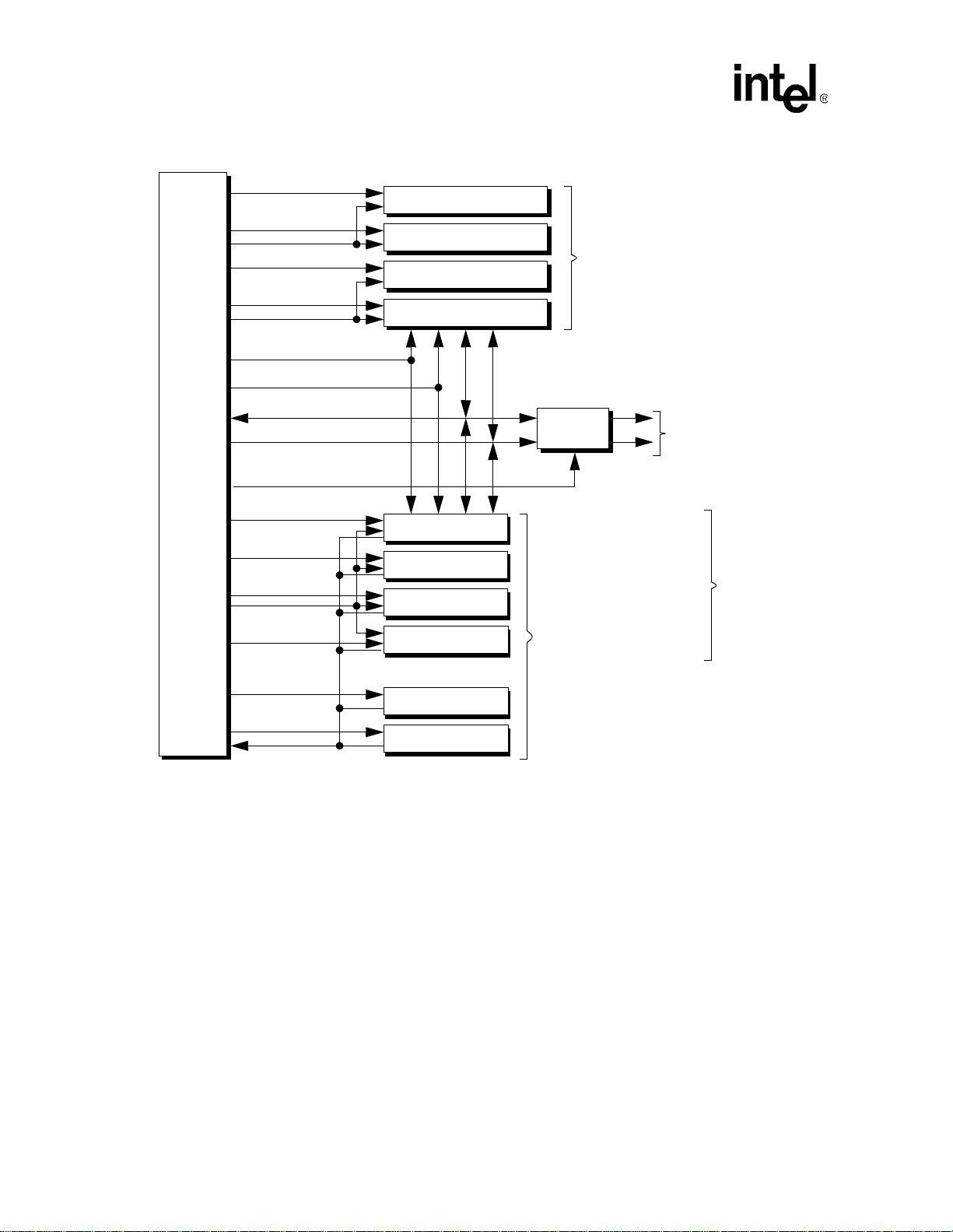

Figure 2-1. General Memory Interface Configuration

PXA250

Memory

Controller

Interface

nSDCS<0>

nSDCS<1>

SDCLK<1>, SDCKE<1>

nSDCS<2>

nSDCS<3>

SDCLK<2>, SDCKE<1>

DQM<3:0>

nSDRAS, nSDCAS

MD<31:0>

MA<25:0>

Card Control

nCS<0>

nCS<1>

nCS<2>

SDCLK<0>,

nCS<3>

SDCKE<0>

SDRAM Partition 0

SDRAM Partition 1

SDRAM Partition 2

SDRAM Partition 3

Static Bank 0

Static Bank 1

Static Bank 2

Static Bank 3

SDRAM Memory Interface

Up to 4 partitions of SDRAM

memory (16- or 32-bit wide)

Buffers and

Transceivers

Static Memory or

Variable Latency I/O Interface

Up to 6 banks of ROM, Flash,

SRAM, Variable Latency I/O,

(16- or 32-bit wide)

NOTE:

Static Bank 0 must be populated by

“bootable” memory

Card Memory Interface

Up to 2-socket support.

Requires some

external buffering.

nCS<4>

nCS<5>

RDY

Static Bank 4

Static Bank 5

Synchronous Static Memory Interface

Up to 4 banks of synchronous

static memory (nCS<3:0>).

(16- or 32-bit wide)

NOTE:

Static Bank 0 must be populated by

“bootable” memory

2-2 PXA250 and PXA210 Applications Processors Design Guide

Page 29

T a ble 2-1. Memory Address Map

0x6000 0000 Reserved Address Space

0x5C00 0000 Reserved Addres s Space

0x5800 0000 Reserved Address Space

0x5400 0000 Reserved Address Space

0x5000 0000 Reserved Address Space

0x4C00 0000 Reserved Addres s Space

0x4800 0000 Memory Mapped Registers (Memory Ctl)

0x4400 0000 Memory Mapped Registers (LCD)

0x4000 0000 Memory Mapped Registers (Peripherals)

0x3000 0000 PCMCIA/CF – Slot 1

0x2000 0000 PCMCIA/CF – Slot 0

0x1C00 0000 Reserved Addres s Space

0x1800 0000 Reserved Address Space

0x1400 0000 Static Chip Select 5

0x1000 0000 Static Chip Select 4

0x0C00 0000 Static Chip Select 3

0x0800 0000 Static Chip Select 2

0x0400 0000 Static Chip Select 1

0x0000 0000 Static Chip Select 0

System Memory Interface

2.2 SDRAM Interface

The applications processor supports an SDRAM interface at a maximum frequency of 100 MHz.

The SDRAM Interface supports four 16-bit or 32-bit wide partitions of SDRAM. Each partition is

allocated 64 MBytes of the internal memory map. However, the actual size of each partition is

dependent on the parti cular SDRAM c onfiguration used. The four partitions are divided into two

partition pairs: the 0/1 pair and the 2/3 pair. Both partitions within a pair (for example, partition 0

and partition 1) must be identical in size and configuration; however, th e two pairs can be different.

For example, the 0/1 pair can be 100 MHz SDRAM on a 32-bit data bus, while the 2/3 pair can be

50 MHz SDRAM on a 16-bit data bus.

Note: For proper SDRAM operation above 50 MHz, 22 ohm series resistors must be placed on the

memory address lines.

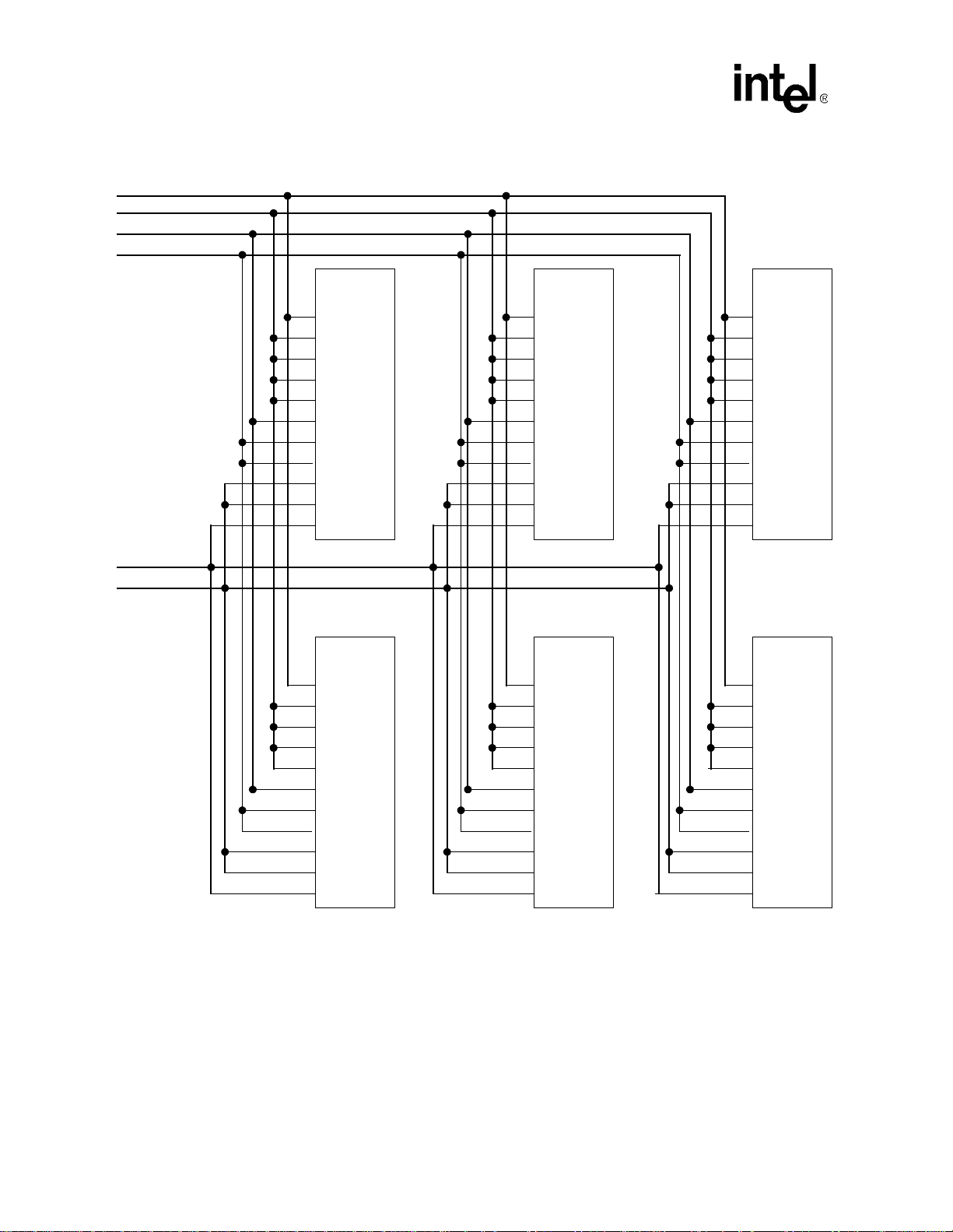

2.3 SDRAM memory wiring diagram

Figure 2-2, “SDRAM Memory System Example” on page 2-4 is a wiring diagram example that

shows a system using 1Mword x 16-bit x 4-bank SDRAM devices for a total of 48 Mbytes. Refer

to Section 2.5, “SDRAM Address Mapping” on page 2-6 to determine the individual SDRAM

component address.

PXA250 and PXA210 Applications Processors Design Guide 2-3

Page 30

System Memory Interface

Figure 2-2. SDRAM Memory System Example

nSDCS(3:0)

nSDRAS, nSDCAS, nWE, CKE(1)

SDCLK(2:1)

MA(23:10)

MD(31:0)

DQM(3:0)

15:0

31:16

2

3

0

1

0

1

0

1

4Mx16

SDRAM

nCS

nRAS

nCAS

nWE

CKE

CLK

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

nWE

CKE

CLK

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

1

1

1

1

4Mx16

SDRAM

nCS

nRAS

nCAS

nWE

CKE

CLK

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

nWE

CKE

CLK

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

21:10

23:22

2

2

2

2

4Mx16

SDRAM

nCS

nRAS

nCAS

nWE

CKE

CLK

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

nWE

CKE

CLK

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

2-4 PXA250 and PXA210 Applications Processors Design Guide

Page 31

2.4 SDRAM Support

Table 2-2 shows the SDRAM memory types and densities that are supported by the applications

.

Table 2-2. SDRAM Memory Types Supported by the Applications Processor

processor.

System Memory Interface

Partition Siz e

(Mbyte/Partition)

16-bit

Bus

2 Mbyte 4 Mbyte 1M x 16 16 Mbit 1 2 1 x 11 x 8 8 Mbyte 16 Mbyte 4 8

4 Mbyte 8 Mbyte 2 M x 8 16 Mb it 2 4 1 x 11 x 9 16 Mbyte 32 Mbyte 8 16

8 Mbyte 16 Mbyte 4 M x 4 16 Mbit 4 8 1 x 11 x 10 32 Mbyte 64 Mbyte 16 32

N/A 8 Mbyte 2 M x 32 64 Mbit N/A 1 2 x 11 x 8 N/A 32 Mbyte N/A 4

8 Mbyte 16 Mbyte 4 M x 16 64 Mbit 1 2

16 Mbyte 32 Mbyte 8 M x 8 64 Mbit 2 4

32 Mbyte 64 Mbyte 16 M x 4 64 Mbit 4 8

16 Mbyte 32 Mbyte 8 M x 16 128 Mbit 1 2 2 x 12 x 9 64 Mbyte

32 Mbyte 64 Mbyte 16 M x 8 128 Mbit 2 4 2 x 12 x 10

64 Mbyte N/A 32 M x 4 128 Mbit 4 8 2 x 12 x 11

32-bit

Bus

SDRAM

Configu-

ration

(Words x

Bits)

Chip

Size

Number Chips/

Partition

16-bit

Bus

32-bit

bus

Bank Bits x

Row bits x

Column

Bits

1 x 13 x 8

2 x 12 x 8

1 x 13 x 9

2 x 12 x 9

1 x 13 x 10

2 x 12 x 10

Maximum

Memory

(4 Partitions)

16-bit

Bus

32 Mbyte 64 Mbyte 4 8

64 Mbyte

128

Mbyte

128

Mbyte

256

Mbyte

32-bit

Bus

128

Mbyte

256

Mbyte

128

Mbyte

256

Mbyte

N/A 16 32

Total Number

of Chips

16-bit

Bus

32-bit

816

16 32

48

816

Bus

32 Mbyte 64 Mbyte

64 Mbyte N/A 32 M x 8 256 Mbit 2 4 2 x 13 x 10

16 M x

16

256 Mbit 1 2 2 x 13 x 9

128

Mbyte

256

Mbyte

256

Mbyte

N/A 8 16

48

PXA250 and PXA210 Applications Processors Design Guide 2-5

Page 32

System Memory Interface

2.5 SDRAM Address Mapping

SDRAM Address Mapping is shown in Table 2-3 and Table 2-4.

Table 2-3. Normal Mode Memory Address Mapping

SDRAM

Device Technology

1Mx16 16Mbit 1x11x8 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2Mx8 16Mbit 1x11x9 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

4Mx4 16Mbit 1x11x10 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2Mx32 64Mbit 2x11x8 BS1BS0A10A9A8A7A6A5A4A3A2A1A0

4Mx16/4Mx32 64Mbit/128Mbit 2x12x8 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

8Mx8/8Mx16 64Mbit/128Mbit 2x12x9 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

16Mx4/16Mx8 64Mbit/128Mbit 2x12x10 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

32Mx4 128Mbit 2x12x11 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

8Mx32 256Mbit 2x13x8 BS1BS0A12A11A10A9A8A7A6A5A4A3A2A1A0

16Mx16 256Mbit 2x13x9 BS1BS1A12A11A10A9A8A7A6A5A4A3A2A1A0

# Bits

Bank x

Row x

1x12x8 BS0A11A10A9A8A7A6A5A4A3A2A1A0

1x12x9 BS0A11A10A9A8A7A6A5A4A3A2A1A0

1x12x10 BS0A11A10A9A8A7A6A5A4A3A2A1A0

1x12x11 BS0A11A10A9A8A7A6A5A4A3A2A1A0

1x13x8 BS0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x13x9 BS0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x13x10 BS0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x13x11 BS0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x11x9 BS1BS0A10A9A8A7A6A5A4A3A2A1A0

2x11x10 BS1BS0A10A9A8A7A6A5A4A3A2A1A0

A24 A23 A22 A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10

Col

The applications processor pin mapping to SDRAM devices

(The address lines at the top of the columns are the processor address lines)

2-6 PXA250 and PXA210 Applications Processors Design Guide

Page 33

System Memory Interface

Table 2-4. Applications Processor Compatibility Mode Address Line Mapping

SDRAM

Device Technology

1Mx16 16Mbit 1x11x8 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2Mx8 16Mbit 1x11x9 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

4Mx4 16Mbit 1x11x10 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2Mx32 64Mbit 2x11x8 BS1BS0A10A9A8A7A6A5A4A3A2A1A0

4Mx16/4Mx32 64Mbit/128Mbit 2x12x8 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

8Mx8/8Mx16 64Mbit/128Mbit 2x12x9 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

16Mx4/16Mx8 64Mbit/128Mbit 2x12x10 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

32Mx4 128Mbit 2x12x11 BS1 BS0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

8Mx32 256Mbit 2x13x8 A12BS1BS0A11A10A9A8A7A6A5A4A3A2A1A0

16Mx16 256Mbit 2x13x9 A12BS1BS0A11A10A9A8A7A6A5A4A3A2A1A0

# Bits

Bank x

Row x

Col

1x12x8 A11BS0A10A9A8A7A6A5A4A3A2A1A0

1x12x9 A11BS0A10A9A8A7A6A5A4A3A2A1A0

1x12x10 A11BS0A10A9A8A7A6A5A4A3A2A1A0

1x12x11 A11BS0A10A9A8A7A6A5A4A3A2A1A0

1x13x8 A12 A11 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x13x9 A12 A11 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x13x10 A12 A11 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x13x11 A12 A11 BS0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x11x9 BS1BS0A10A9A8A7A6A5A4A3A2A1A0

2x11x10 BS1BS0A10A9A8A7A6A5A4A3A2A1A0

A24 A23 A22 A21 A20 A19 A18 A1 7 A16 A15 A14 A13 A12 A11 A10

The applications processor pin mapping to SDRAM devices

(The address lines at the top of the columns are the processor address lines)

2.6 Static Memory

2.6.1 Overview

The applications processor external memory bus interface supports the following static memory

types:

• Synchronous and asynchronous Burst mode and Page mode Flash

• Synchronous Mask ROM (SMROM)

• Page Mode ROM

• SRAM

• SRAM-like Variable Latency I/O (VLIO)

• PCMCIA expansion memory

• Compact Flash

PXA250 and PXA210 Applications Processors Design Guide 2-7

Page 34

System Memory Interface

Memory types are programmable through the memory interface configuration registers.

Six chip selects control the static memory interface, nCS<5:0>. All are configurable for nonburst

ROM or Flash memory, burst ROM or Flash, SRAM, or SRAM-like variable latency I/O devices.

The variable latency I/O interface differs from SRAM in that it allows the data ready input signal

(RDY) to insert a variable number of memory-cycle-wait states. The data bus width for each chip

select region may be programmed to be 16-bi t or 32-bit. nCS<3:0> are also configurable for

Synchronous Static Memory.

For SRAM and variable latency I/O implementations, DQM<3:0> signals are used for the write

byte enables, where DQM<3> corresponds to the MSB. The applications processor supplies 26bits of byte address for access of up to 64 Mbytes per chip select. However, when the address is

sent out on the MA pins, MA reflects the actual address, not the byte address. The lower one or two

internal address bits are truncated appropriately.

2.6.2 Boot Time Defaults

Booting configuration is device specific. For example, you cannot use a 32-bit memory booting

configuration with a PXA210 applications processor . Table 2-5 shows valid booting configurations

based on processor type, while Table 2-6 shows boot selection definitions. See Section 7.10.2,

“Boot-Time Configurations” in the Intel® PXA250 and PXA210 Applications Processors

Developer’s Manual for more detailed descriptions of these Boot Time Configurations.

Table 2-5. Valid Booting Configurations Based on Package Type

Processor Type Valid Booting Configurations

0 (PXA210

applications

processor)

1 (PXA250

applications

processor)

001

101

111

000

001

100

101

110

111

Table 2-6. BOOT_SEL Definitions (Sheet 1 of 2)

BOOT_SEL

210

0 0 0 Asynchronous 32-bit ROM

0 0 1 Asynchronous 16-bit ROM

100

1 32-bit Synchronous Mask ROM (64 Mbits)

2 16-bit Synchronous Mask ROMs = 32-bits (32 Mbits each)

Boot From . . .

2-8 PXA250 and PXA210 Applications Processors Design Guide

Page 35

T a ble 2-6. BOOT_SEL Definitions (Sheet 2 of 2)

System Memory Interface

BOOT_SEL

210

1 0 1 1 16-bit Synchronous Mask ROM (64 Mbits)

1 1 0 2 16-bit Synchronous Mask ROMs = 32-bits (64 Mbits each)

1 1 1 1 16-bit Synchronous Mask ROM (64 Mbits)

Boot From . . .

2.6.3 SRAM / ROM / Flash / Sync hronous Fast Flash Memory Options

Table 2-7 contains the AC specification for SRAM / ROM / Flash / Synchronous Fast Flash.

Table 2-7. SRAM / ROM / Flash / Synchronous Fast Flash AC Specifications

Symbol Description

SRAM / ROM / Flash / Synchronous Fast Flash (WRITES) (Asynchronous)

tromAS

tromAH

tromASW MA(25:0) setup to nWE asserted 30 25.5 22.5 20.4 18 ns, 3

tromAHW MA(25:0) hold after nWE de-asserted 10 8.5 7.5 6.8 6 ns, 1

tromCES nCS setup to nWE asserted 20 17 15 13.6 12 ns, 2

tromCEH nCS hold after nWE de-asserted 10 8.5 7.5 6.8 6 ns, 1

tromDS

tromDSWH

tromDH

tromNWE

NOTES:

1. This number represents 1 MEMCLK period

2. This number represents 2 MEMCLK periods

MA(25:0) setup to nOE, nSDCAS (as

nADV) asserted

MA(25:0) hold after nCS, nOE,

nSDCAS (as nADV) de-asserted

MD(31:0), DQM(3:0) write data setup to

nWE asserted

MD(31:0), DQM(3:0) write data setup to

nWE de-asserted

MD(31:0), DQM(3:0) write data hold

after nWE de-asserted

nWE high time between beats of write

data

99.5 118.0 132.7 147.5 165.9

10 8.5 7.5 6.8 6 ns, 1

10 8.5 7.5 6.8 6 ns, 1

10 8.5 7.5 6.8 6 ns, 1

20 17 15 13.6 12 ns, 2

10 8.5 7.5 6.8 6 ns, 1

20 17 15 13.6 12 ns, 2

MEMCKLK

Units

Notes

2.6.4 Variable Latency I/O Interface Overview

Both reads and writes for VLIO differ from SRAM in that the PXA250 applications processor

samples the data-ready input, RDY. The RDY signal is level sensitive and goes through a two-stage

synchronizer on input. When the internal RDY signal is high, the I/O device is ready for data

transfer. This means that for a transaction to complete at the minimum assertion time for either

nOE or nPWE (RDF+1), th e RDY signal must be high two clocks prior to the mini mum assertion

time for either nOE or nPWE (RDF-1). Data will be latched on the rising edge of memclk once the

internal RDY signal is high and the minimum assertion time of RDF+1 has been reached. Once the

PXA250 and PXA210 Applications Processors Design Guide 2-9

Page 36

System Memory Interface

data has been latched, the address may change on the next rising edge of MEMCLK or any cycles

thereafter. The nOE or nPWE signal de-asserts one MEMCLK after data is latched. Before a

subsequent data beat, nOE or nPWE remains deasserted for RDN+1 memory cycles. The chip

select and byte selects, DQM[3:0], remain asserted for one memory cycle after the burst’s final

nOE or nPWE deassertion. Refer to

Figure 2-3 for 32-Bit Variable Latency I/O read timing and

Figure 2-8 for Variable Latency I/O Interface AC Specifications

Figure 2-3. 32-Bit Variable Latency I/O Read Timing (Burst-of-Four, One Wait Cycle Per Beat)

0ns 100ns 200ns 300ns

memlk

nCS[0]

tAS

MA[25:2]

MA[1:0]

tASRW0

nOE

nPWE

RDnWR

RDY

MD[31:0]

DQM[3:0]

nCS[1]

012 3