Page 1

OCPRF100 MP

Server System

Supporting Up To Eight Intel®

®

Pentium

III Xeon™ Processors

Technical Product Specification

Intel Order #753674-001

Revision 1.0

Page 2

OPRF100 MP Board Set Technical Product Specification

Revision 1.0

Revision History

Date Rev. Modifications

September, 1999 1.0 Initial release.

Disclaimers

Except as provided in Intel’s Terms and Conditions of Sale for such product s, INTEL DISCLAIMS

ALL LIABILITIES AND WARRANTIES (EXPRESS, IMPLIED OR OTHERWISE) ASSOCIATED

WITH THE INFORMATION CONTAINED WITHIN THIS DOCUMENT, OR FOR ANY PRODUCTS OR DEVICES REFERRED TO HEREIN, INCLUDING, WITHOUT LIMIT ATION, LIABILITY

FOR INFRINGEMENT OF ANY PROPRIETAR Y RIGHTS RELA TING TO THIS DOCUMENT, OR

ANY PRODUCTS OR DEVICES REFERENCED HEREIN, OR FOR THE IMPLEMENTATION

OF INFORMA TI ON IN THIS DOCUMENT INTEL IS NOT OBLIGATED TO PROVIDE ANY SUPPORT, INSTALLATION, OR OTHER ASSISTANCE WITH REGARD TO THESE DEVICES, NOR

ANY UPDATES, CORRECTIONS OR MODIFICATIONS TO THIS DOCUMENT OR THE

INFORMATION CONTAINED HEREIN.

THE INTEL

DARD COMMERCIAL USE ONLY. CUSTOMERS ARE SOLELY RESPONSIBLE FOR

ASSESSING THE SUITABILITY OF THE PRODUCT AND/OR DEVICES FOR USE IN PARTICULAR APPLICATIONS. THE REFERENCED INTEL PRODUCT IS NOT INTENDED FOR USE

IN CRITICAL CONTROL OR SAFETY SYSTEMS OR IN NUCLEAR FACILITY APPLICATIONS.

INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE

SUSTAINING APPLICATIONS.

Information in this document is provided in connection with Intel products. This document is provided “as is” with no warranties whatsoever. Intel specifically disclaims any implied or express

warranties of any kind whatsovever, associated with this document, including without limitation:

(i) liability for infrinement of any proprietary rights (including without limitation, any intellectual

property right), merch antability, fit ness for any particular purpose, or any warranty otherwise arising out of any product or testing proposal, speci ficat ion or sample; (ii) suf fici ency, reliability, accuracy, completeness or usefulness of same, and (iii) ability or sufficiency of same to function

accurately as a representati on of any standard. No license, express, implied, or otherwise, to

any intellectual property rights is granted by this document or by the sale of Intel products. Furthermore, Intel makes no commitment to update the information contained in this document or

any test report, provided that Intel may make changes to this document, the test reports, specifications and product descriptions at any t ime, without notice.

Third parties may have intell ectual property rights which may be relevant to this document and

the technologies discussed herein, accordingly the reader is advised to seek the advice of competent counsel, as required withhout obligation to Intel.

®

PRODUCT REFERRED TO IN THIS DOCUMENT IS INTENDED FOR STAN-

Page 3

OPRF100 MP Board Set Technical Product Specification

Revision 1.0

Only approved software drivers and accessori es that are recommended for the revision number

of the boards and system being operated should be used with Int el products . Please note that, as

a result of warranty repairs or replacements, alternate software and firmware versions may be

required for proper operation of the equipment.

The hardware vendor remains solely responsibl e for the design, sale and func ti onalit y of its product, including any liability arising from product infringement or product warranty.

The OPRF100 MP Board Set and the OCPRF100 MP Server System product may contain

design defects or errors known as errata that may cause the product to deviate fr om published

specifications. Current characterized errata are availab le on request.

2

I

C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the

2

I

C bus/protocol and was developed by Intel. Implementations of the I2C bus/protocol or the

SMBus bus/protocol may require li censes from vari ous entiti es, includi ng Philips Electr onics N.V.

and North American Philips Corporation.

Copyright © 1999 Intel Corporation.

*Other brands and names are the property of their respective owners.

Page 4

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Table of Contents

Introduction........................................................................................................................... 1

Server System Chassis and Assemblies............................. .. .. ....................... ....................3

Front Panel Assembly....................................................................................................... 4

Peripheral Bay................................................................................................................... 4

Top Cover Assembly........................................ .. ...................... ..................... ....................5

Hot-plug PCI Access Door .......................................................................................... 6

Fan Bay............ ......................................................................... ........................................6

Front Panel Board.............................................................................................................8

Processor Mezzanine Board............................................................................................. 9

Processor Retention Mechanism ...................................................................................... 9

Profusion® Carrier Tray .................................................................................................. 11

Midplane As se m b l y................... .. ........................... .. ............. .. ... ............. .. ............. ... .. .... 13

I/O Carrier ....................................................................................................................... 14

Power Supply................................. .. .. ............. .. ........................... .. ........................... .. .. .. 16

OCPRF100 MP Server System Chassis..................... .. ..................... .. ........................... 16

System Over view ............. .. .. .............. .. ............. .. .. .............. .. ............. .. ... ............. .. ............. 17

Introduction..................................................................................................................... 17

External Chassis Features................................................................ .................... .. ........20

Front View of Ch a ss is .. ........................... .. ........................... .. .. ............. ... ................. 20

Rear View of Cha s sis. .. ........................... .. ............. ... .. ............. .. .............. .. ............... 2 3

Riser Board External I/O Connectors........................................................................24

Peripheral Bay........................................................................................................... 25

3.5-inch Use r- a cc e s sible Drive Bay .... ............. .. .. ............. ... .......................... .. ... ...... 26

5.25-inch User-accessible Drive Bay ........................................................................ 26

3.5-inch SCSI Hot-swap Drive Bays ....................................... .. .................... ............26

Internal Chas s is Features ........... ... .. ............. .. ........................... .. .......................... ... .. .... 27

Power Syste m . .. ... ............. .. .. .............. .. .......................... .. ........................... .. .. ......... 27

Cooling Syst e m ............... .. .. ............. ... .......................... .. ........................... .. .. ........... 29

PCI Hot-plug.... .. .............. .. .......................... ... .. ............. .. ........................... .. .. ........... 31

Server Management........................................................................................................34

Front Panel Controller...............................................................................................34

Baseboard Management Controller........................... ........................ .......................35

Hot-swap Con troller ............ ........................... .. .......................... ... .. ............. .. ........... 36

Expansion Support..........................................................................................................36

Specifications..................................................................................................................37

Environmental Specifications.................................................................................... 37

Physical Specifications.............................................................................................. 37

Cables and Connectors....................................... .................. ................................... .. ........39

Cables............................................................................................................................. 41

Connectors......................................................................................................................42

User-accessible I/O Connectors ............................................... ................................42

Serial Ports................................................................................................................ 43

Parallel Port............................................................................................................... 44

VGA Video Port.........................................................................................................44

Universal Serial Bus Interface................................................................................... 45

ICMB Connectors................. .............. .......................................................................46

i

Page 5

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Fan Connector .......................... ...................... ...................... .. ...................... .. ..........47

Peripheral Bay P o w e r C o n nec tor. .. .. .............. .. .......................... ... .. ............. .. ........... 47

Peripheral Bay Backplane Header............................................................................48

LED Board Connector................................... .. ........................ .. ........................ ........50

SCSI Connector........................................................................................................ 51

IDE Connectors.........................................................................................................52

Floppy Connectors...... ................ ................................................. .............................53

Power Supply .................................... .......................................................................... ........54

Mechanical Requirements............. ..................................................................................54

Mechanical Outline.................................................................................................... 54

Fan Requirements........................................................................ ................... ..........55

Interface Requirements................................................................................................... 55

AC Inlet Connector............................ ....................... ........................ .. .......................55

DC Output Connector(s) .......................... .................... .. .................... .. .....................55

Marking and Identification...............................................................................................56

LED Labeling............................... .. .. ........................ ............................................. .. ... 56

Internal Syst e m M ar k in g ........... .. .............. .. .. ............. .. ........................... .. .. .............. .. .... 56

Electrical Re q ui re m e n ts................................ .. ........................... .. .......................... ... .. .... 58

Efficiency................................................................................................................... 58

AC Input Voltage Specification......................................... .. .................... ...................58

AC Input Voltage Ranges........................... .. .......................................... ...................58

DC Output Specification............................................................................................ 59

Control Signals................................................................................................................ 62

Power Supply On (Input). ..........................................................................................62

AC OK Signal (Output).............................................................................................. 62

Power Good (Output). ...............................................................................................63

Power Supply Present Indicator (Output).................................................... ..............64

Predictive Failure Signal (Output).............................. .. .................. .. .................. .. ..... 64

Power Supply Failure Signal (Output)................................... .................. .. ................64

Power Supply Kill (Input)...........................................................................................65

Power Supply Field Replacement Unit Signals.........................................................66

LED Indicators........................................................................................................... 66

Fan Speed Control............................................................................. ...................... .. ..... 67

Environmental Requirements............................................................... ...........................67

Physical Environment................................................................................................ 67

Thermal Protection............................................ ................. ................ .......................67

Regulatory Agency Requirements..................................................................................67

System Softw a r e . ............. .. ........................... .. .. ............. .. ........................... .. .. .............. .. ....68

System Hardware............................................................................................................ 69

Processors ................................................................................................................ 69

Profusion® Chip Set.................................................................................................. 70

I/O Subsystem................................................................ .. .................... .................... .70

Intelligent Platform Management Bus............................................................... ........71

Industry Standards..........................................................................................................71

ACPI..........................................................................................................................71

Boot Devices a nd P e ri ph e rals. . .. ............. .. ............. ... ............. .. ............. ... .. ............. .. 7 2

Management.............................................................................................................73

Configuration............................................................................................................. 73

BIOS Setup Utility ........................................................................................................... 74

Main Menu ...................... .. .......................... ... .......................... .. ... ............. .. ............. 75

ii

Page 6

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Advanced Menu ........................................................................................................ 78

Security Men u ................. .. .. ............. ... .......................... .. ........................... .. .. ........... 82

Server Menu.... .. ... ............. .. ........................... .. .. ............. .. ........................... .. .. ......... 83

Boot Menu.............. .. ........................... .. .. ............. .. ........................... .. ...................... 85

Exit Menu ........ .. .............. .. .. ............. ... .......................... .. .. .............. .. ........................ 86

Flash Utility...................................................................................................................... 86

Regulatory Specifications............................................ ................................... ................... 88

Safety Compliance............. ... .. ............. .. ... ............. .. ........................... .. .......................... 88

Electromagnetic Compatibility.........................................................................................88

CE Mark .......................................................................................................................... 88

Electromagnetic Compatibility Notice (USA)........................ .. .................... .. ...................89

Electromagnetic Compatibility Notices (International).....................................................89

Peripheral Bay Backplane Board ......................... ........................................... .. ................90

Peripheral Bay Backplane Overview...............................................................................90

Architectural Overview .............................................................................................. 91

Placement Dia g ra m.. ............. ... .. ............. .. ........................... .. .......................... ... .. .... 91

Deviations from SAF-TE Specification...................................................................... 91

Functional Description.....................................................................................................91

Hot-swap Connectors................................................................................................ 92

SCSI Interface . .......................................................................................................... 92

LVD/SE Acti ve T e rmination........ .......................... .. .............. .. .. ............. ... ............. .. .. 9 2

Power Contr ol ...... .. .......................... ... .. ............. .. ........................... .. .. ............. ... ...... 92

FET Short Protection................................................................................................. 93

Microcontroller........................................................................................................... 93

LED Arrangement .................................. .. .. ......................... .. ............................ ........93

IPMB (I2C bus).......................................................................................................... 94

Temperature Sensor ................................................................................................. 94

Serial EEPROM ........................................................... .. .. ...................................... ...94

Board Functi o n s......... ............. .. ........................... .. .. ............. .. ........................... .. .. ......... 94

Reset......................................................................................................................... 94

Microcontroller........................................................................................................... 95

SCSI Controller.........................................................................................................97

LVDS SCSI Termination .................................... ...................... .......................................97

LVDS Termination.................................................... ................... .................. ............97

Single Ended T e rm i n a tio n.................................... .. ... ............. .. ........................... .. .... 98

Programmab le Lo g ic................. .. ........................... .. .. ............. ... .......................... .. ... ...... 98

Memory Map ........... ... ............. .. ........................... .. .......................... ... .. ............. .. ........... 98

Memory Map ..... ... ............. .. ........................... .. .......................... ... .. ............. .. ........... 98

I/O Ports.................................................................................................................. 101

Signal Descriptions....................................................................................................... 103

Power Good Signal.................................................................................................103

CONN_EN_L........................................................................................................... 103

CONN_SDI.............................................................................................................. 103

CONN_SDO............................................................................................................ 103

CONN_MODE......................................................................................................... 104

CONN_SCLK .......................................................................................................... 104

Electrical, Mechanical Specifications.................. ..................... .................................... .104

Connectors..............................................................................................................104

Peripheral Bay Board (Chassis Side).................... ..................... .................................... .111

Introduction................................................................................................................... 111

iii

Page 7

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Mechanical Description................................................................................................. 111

Board Layou t.............. .............. .. .......................... .. .............. .. .. ............. ... ............. .. 11 1

Front Panel..................... .. .. ..................... .............................................. ........................ .......... 113

Introduction................................................................................................................... 113

Board Overv ie w.... ............. .. .. .............. .. ............. .. .. .............. .. ............. .. ... ............. .. 1 1 3

Functional Description...................................................................................................114

Microcontroller......................................................................................................... 114

Memory Maps ...... .. ............. .. ........................... .. .. ............. ... .......................... .. ....... 114

Memory ................................................................................................................... 118

Front Panel Indicator LEDs..................................................................................... 122

Front Panel LCD .....................................................................................................123

System Power......................................................................................................... 123

Reset....................................................................................................................... 124

Speaker...................................................................................................................126

Fan Control ............................... .............................................. ................................126

ICMB and COM2 Redirection....................................................... .. .. .......................126

Front Panel Push Buttons.......................................................................................129

I2C Interface s............. .............. .. .. ............. .. ... ............. .. ........................... .. ............. 13 0

Miscellaneous ......................................................................................................... 132

Appendix A: Glossary ................................. .................. .. .................. .. .................. ................133

Appendix B: References .......................................................... .......................................... ... 137

iv

Page 8

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

1. Introduction

This document provides an overview of the OCPRF100 MP server system and includes information on cabling, connectors, power supply, and regulatory requirements.

Document Structure and Outline

This document is organized into ten chapters:

Chapter 1: Introduction

Provides an overview of this document.

Chapter 2: Server System Chassis and Assemblies

Provides an overview of the chassis hardware.

Chapter 3: System Overview

Provides an overview of the system hardware.

Chapter 4: Cables and Connectors

Describes the cables and connectors used to interconnect the OPRF100

board set and the server system components.

Chapter 5: Power Supply

Describes the specifications for the 750-W power supply.

Chapter 6: OCPRF100 MP Server Software

Provides an overview of the system software.

Chapter 7: Regulatory Specifications

Describes system compliance to regulatory specifications.

Chapter 8: Peripheral Bay Backplane Board

Describes the features and functional ity of the peripheral bay backplane

board.

Chapter 9: Peripheral Bay Board (Chassis Side)

Describes the design of the peripheral bay board (chass is si de).

Chapter 10: Front Panel

Describes the design and external interface of the OCPRF100 MP server

system front panel.

1

Page 9

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

This page intentionally left blank.

2

Page 10

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

2. Server System Chassis and Assemblies

This chapter describes the chassis and assembly pieces that reside within the chassis. This

chapter is divided into the following areas:

• Front panel assembly

• Peripheral bay

• Top cover assembly

• Fan bay

• Front panel board

• Processor mezzanine board

• Processor retention mechanism

®

• Profusion

carrier tray

• Midplane assembly

• I/O carrier assembly

• Power supply

• OCPRF100 MP server system chassis

Figure 2-1: OCPRF100 MP Server System Chassis

3

Page 11

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

2.1 Front Panel Assembly

The front panel assembly consists of an upper and lower bezel. The bezels serve as cosmetic

pieces only, and can be integrator specific. Finger grips are provided to make it easy to remove

the bezels. Removing the bezels exposes the front side of the fan bay, the front panel controller

(FPC) switches (power, reset, and nonmaskable interrupt (NMI)), as well as the indicator lights

(power indicator, predictive power supply failure, predictive fan failure, and hard drive failure).

From this location, the hot-swap hard drives and/or t he peripheral bay may be removed from the

system.

Figure 2-2: Front Panel

2.2 Periphera l Ba y

The peripheral bay is defined to be a customer specif ic, removable device capable of supporting

a floppy drive, dual hot-swap hard drives, and a low-voltage differential SCSI (LVDS) or single

ended SCSI device. The integrator has the option of defining the size and capacity of the hard

drives, as well as deciding whether the LVDS will support CD-ROM, tape, or other device. A single ended SCSI channel is provided for support of a SCSI device, should the integrat or so desire.

The peripheral bay is designed to be easily added and removed from the front of the server by

removing the front cover and four mounting screws. The peripheral bay connects to the

OPRF100 I/O carrier and the power supply via a blind mate board connector and cabli ng. The

blind mate board is located in front of the midplane board, on the left side of the server (when

viewing the server from the front). The blind mate connector connects to the peripheral bay’s

LVDS board upon insertion, thus connecting all peripheral devices to the I/O carrier.

The peripheral bay will contain a 1.4 MB floppy dr ive, space for a half-height 5 ¼ inch device

(typically a CD-ROM), and has two bays designed to accommodate either a 1-inch or a 1.6-i nch

SCA hard drive.

4

Page 12

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Figure 2-3: Peripheral Bay

2.3 Top Cover Assembly

The top cover assembly is released by removing the two retaining screws located on the top

toward the front (E in Figure 2-4: Hot-plug PCI Access Door) , between the fan bay assembly and

the top cover assembly marked with the AC caution icon. The cover slides towar d the rea r of the

server and then lifts straight up off of the ser ver cha ssi s, expos ing t he upper port ion o f the ser ver

for maintenance, upgrades, or adding components.

Tape and sheet metal work were done to the sides of the top cover assembly to provide a better

gripping surface for easier removal and replacement of the top cover assembly. Care should be

taken to avoid damage to the electromagnetic compatibility (EMC) gasket material on the ins ide

of the top cover.

5

Page 13

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

2.3.1 Hot-plug PCI Access Door

The hot-plug PCI access door is released by removing the two ret ai ning screws (A i n Figure 2-4:

Hot-plug PCI Access Door) located on the top, middle area of the server . The cover sli des toward

the rear of the server and lifts straight up off of the server chassis, exposing the hot-plug PCI

cards.

The hot-plug PCI access door is designed to maintain a flush surface with the top cover assembly, such that a vacuum-based hoist may be used during the assembly proc ess.

A

B

Figure 2-4: Hot-plug PCI Access Door

2.4 Fan Bay

The fan bay is a mechanical structure designed to contain six separate 120-mm cooling fans.

These fans operate at a nominal voltage of 8.4 Vdc (2% toleran ce) under normal conditions.

Each fan produces a tachometer- based output to indicat e the revolu tions per minute (RPM) read ing of the motor . Should a fa n’s t achometer out put drop below a predefined normal range of operation, the FPC notifies the server management soft ware that a fan has entered into th e predictive

fan failure condition. At t his point, the f ans will operat e at an elevated volt age of approximatel y 12

Vdc.

6

Page 14

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

The fan bay will operate at high speed on the following conditions:

• Internal temperature has reached an elevated, but noncritical set-point.

• Ambient temperate exceeds 30°C.

• A fan has entered into the predictive failure mode.

• A fan has failed.

If the FPC detects a fan entering the predictive fan failure mode, the speed of all of the fans will

be increased to maintain thermal requirements. The individu al fans within the fan bay are all hotswappable, meaning that they can be removed and inserted while the server is running. Server

management will identify that a fan has either fail ed or has entered into the predictive failure

mode. In both cases, the fan should be repl aced immediately. Removal of a fan is accompli shed

by opening the fan bay cover and pulling (A) to lift the malfunctioning fan (B) out through the top

of the server as shown in Figure 2-5: Fan Bay. The malfunctioning fan shoul d then be repl aced

with a new fan. The system will detect that the fan has been replaced, and as long as no other

thermal violations are currently occurring, the fan will resume operation at the reduced speed.

A

B

Figure 2-5: Fan Bay

OM07304

7

Page 15

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Fans are installed with th e connector on t he left side fac ing down. The cavities i n the f an bay are

keyed to prevent a fan from being install ed backwards.

The fan bay is installed after the Profusion carrier assembly is installed and completely seated

into the midplane. The fan bay is lowered into the chassis unti l it is seated on the flanges of the

Profusion tray. Two screw holes, one on each side, should now be aligned on the sides of the

chassis. Insert screws into these holes to secure the fan bay into the chassis.

The fan bay cover is hinged at the rear and captivated by the system top cover assembly. Tabs in

the rear of the fan bay cover engage with slots on the rear of the fan bay to secure the cover in

normal operation. The fan bay cover is secured by one noncap tive screw loca ted on the center of

the cover’s front flange. Remove the screw, slide the cover forward and lift. The cover remains

open while servicing the fans.

To remove the fan bay from the chassis, it is first necessary to re move all in dividual fans from the

fan bay . The fans plug direct ly into the front p anel board and must be removed before the fan bay

can be lifted out.

The fan bay cover provides critical electr omagnetic interference (EMI) containment. To avoid

electrical interference with adjacent equipment, close and secure the fan bay cover during normal system operation.

In systems with only one processor mezzanine board, an air baffle needs to be installed on the

vacant side of the CPU retention cage to ensure proper cooling for the installed processo rs.

2.5 Front Panel Board

The FPC board provides power and monitors the tach ometer readings from each individual fan

within the fan bay. The FPC also serves as a platform for the server contr oller switches, and supports circuitry required for server management.

The FPC board is located on the same plane as, and connects to the Profusion carrier board via

a connector. Both the FPC and Profusion carrier board are mounted to the topsi de of the Profusion carrier tray. On the left front edge of the FPC board are three push but ton switch es—power,

reset, and NMI. Each switch plunger has a small black cap on it s end, which is necessar y for the

proper operation of the buttons on the front bezel.

To install an FPC board, tilt the board forward as shown in Figur e 2-6: Fr ont Panel Board I nst al la tion, and insert the switches into the openings on the front flange of the Profusion carrier tray.

Lower the back of the board onto the standoff s on the tr ay. Align the board-to-board connectors

and slide the board back to engage the connectors. Secure with nine screws. Reverse this operation to remove the board.

8

Page 16

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Figure 2-6: Front Panel Board Installation

2.6 Processor Mezzanine Board

The base configuration of an OCPRF100 MP server system consists of a single processor mezzanine board. The processor mezzanine board is designed to support one to four Pentium

®

III

Xeon™ processors, providing power, ground and other connections to the processor(s) and to

the Profusion carrier. The processor mezzanine board incorporates integrated volt age regulator

modules (VRMs) to supply the internal voltage requirements to the processor cartridge.

2.7 Processor Retention Mechanism

The processors and termination cards are secured in their respective slots by means of the processor retention mechanism. The processor retention mechanism holds up to eight processors

or termination cards. In th e ev ent th e server is populat ed wit h o nly a singl e proces sor mezzan ine

card, the processor retention mechanism will be popul ated with a total of four contiguous processors and/or terminators.

9

Page 17

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

A

Captive Screw

B

Hold-down

Strap

C

Air Baffle

Figure 2-7: Processor Retention Mechanism

A processor/termination card p air is secured with a hold-down strap (B) that hooks into the back

of the retention mechanism and is fastened at the front with two capt ive screws (A). (The retention strap is for a pair of process ors or terminat ors). See Fi gure 2-7: Pro cessor Retent io n Mechanism.

The processor retention mechanism is secured t o the mezzanine boar ds with the sa me four l ock

bars that secure the mezzanine boards to the Profusion ca rrier board. In the event the server is

populated with only a single process or mezzanine car d, an air baffle (C) must be install ed on the

vacant side of the processor retention mechanism.

To remove or add a processor, first relea se the capti ve screws (A), then swi ng the reten tion strap

(B) upward. Remove the terminator card, and install the processor. Replace the retention strap

(B), and tighten the captive screw (A).

Due to space restrictions in the system, the Profusion carrier tray assembly must be removed

from the chassis to install and service the mezzanine boards. The fan bay assembly must be

removed prior to removing the Profusion carrier tray.

10

Page 18

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

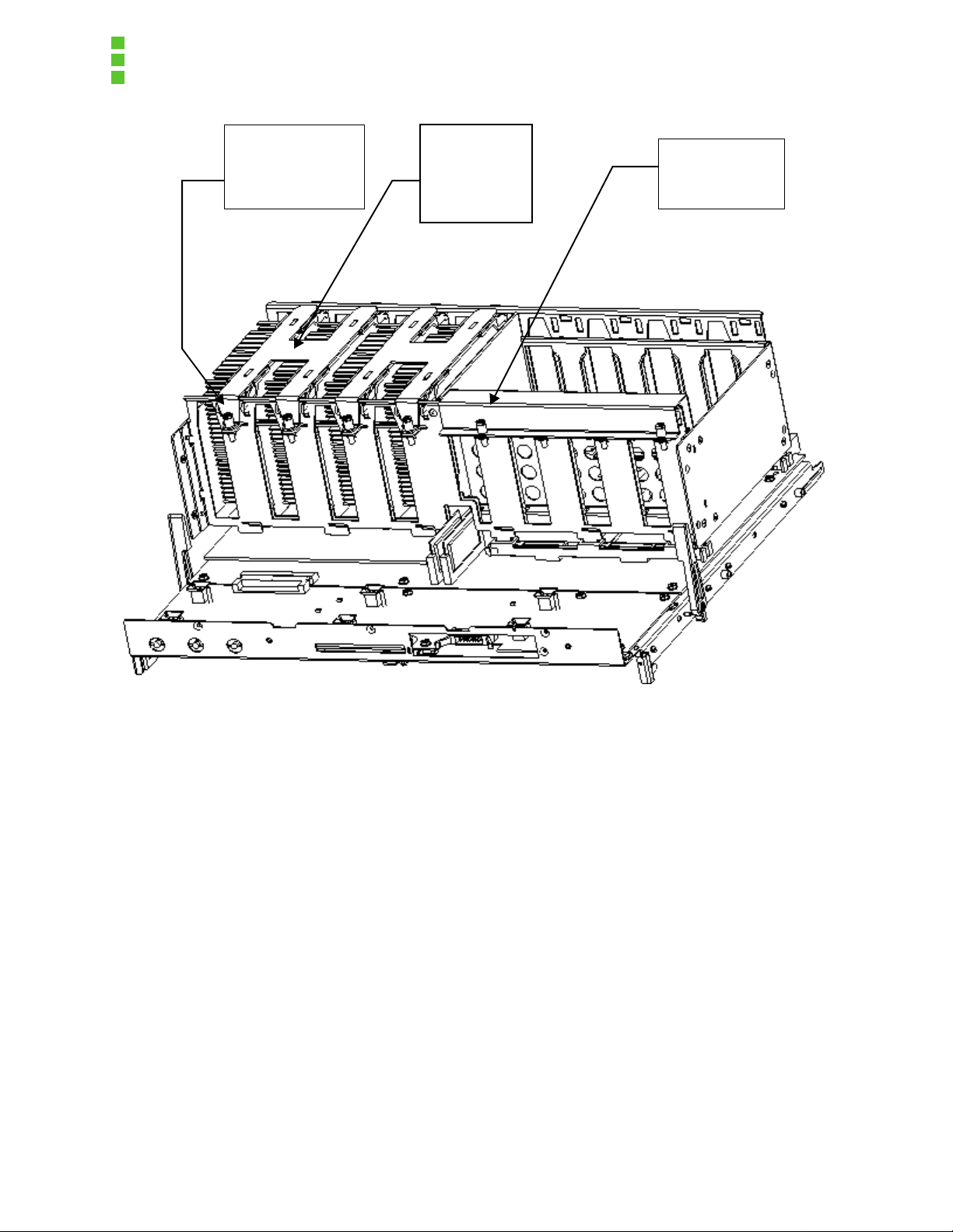

2.8 Profusion® Carrier Tray

The processor mezzanine boards plug into the Profusi on carrier tray. The Profusion carrier tray

serves as a platform to provide power and signals to the processor mezzanine board, route signals through the 1008-pin grand connector, and carry components of the Profusion chip set.

Components of the Profusion chip set th at reside on the Profu sion carrie r are the memory acces s

controller (MAC) and the data interface buffer (DIB).

The Profusion chip set allows a five-por t system data bus, with concur rent switching t aking place.

This is a requirement for an efficient eight-way server. The Profusion chip set will suppor t two

processor buses (each bus containing between one and four processors), two memory buses,

and a single I/O bus. All of the buses operate at 100 MHz for maximum throughput. The data is

routed through the Profusion tray, into the midplane connector for distribution to the appropriate

source (memory carriers or the I/O carri er).

B

Lock Bars

C

Lock Bar

Release Handle

A

Alignment Tabs

Figure 2-8: Profusion® Carrier Tray

Assembly of the Profusion carrier board, and mezzanine boards to the Profusion carrier tray, is

performed outside the cha ssis. To start the assembly, install the Profusion carrie r to the Profusi on

tray by aligning the eight tabs on the tray with the slots on the board (See Figure 2-8 (A)). Next,

install the FPC board by passing the FPC switches through the switch openings in the tray and

11

Page 19

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

then moving back into place for connection to the Profusion carrier board. Place the four lock

bars over the protruding tabs and onto the Profusi on carrier board (B). The release handles of

the lock bars (C) should be pointed to the outsid e of the board and t hey should be in t he unlocked

position. Place the first mezzanine board on the left side of the Profusion carrier board, oriented

so the mezzanine board does not extend over the 1008-pin grand connector on the Profusion

carrier board. Press down in the center of the mezzani ne board until it is seated down onto the

lock bars. If the configurat ion call s for a second mezzani ne board, i nstall it on the r ight side of the

Profusion carrier board by following th e same steps as described for the first board.

2

2

1

1

3

3

Figure 2-9: Profusion® Carrier Tray

Lower the processor retent ion mechanism onto t he mezzanine board(s) , aligning the hooks on it s

bottom with the slots in the mezzanine board(s). The processor retention mechanism should be

oriented such that the center notch for the coher ency filters is facing forward. Engage the fou r

lock bars by pushing in on their ends until they click. The Profusion carrier tray assembly is now

ready for installation in the chassis.

To install the Profusion carrier tray assembly into the chass is, set the tray on t he tray support s on

the inside walls of the chassis and slide it towared the midplane. The tray and chassis have selfaligning features to help guide the tray as it approaches the grand connector on the midplane.

When the connectors are within approximateil y 1” from connect ing, check under the Profusion

carrier tray for proper engagement of the center supports. The insertion/extraction levers (3) on

the side of the tray should be tilted forward as the connectors approach each other. As the con-

12

Page 20

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

nectors begin to engage, rotate the levers back until the connectors are fully engaged. Levers

should be in an upright or near upright position. Secure the tray and the processor retention

mechanism to the sides of the chassis with screws (1) and (2) as indi cated in Figure 2-9.

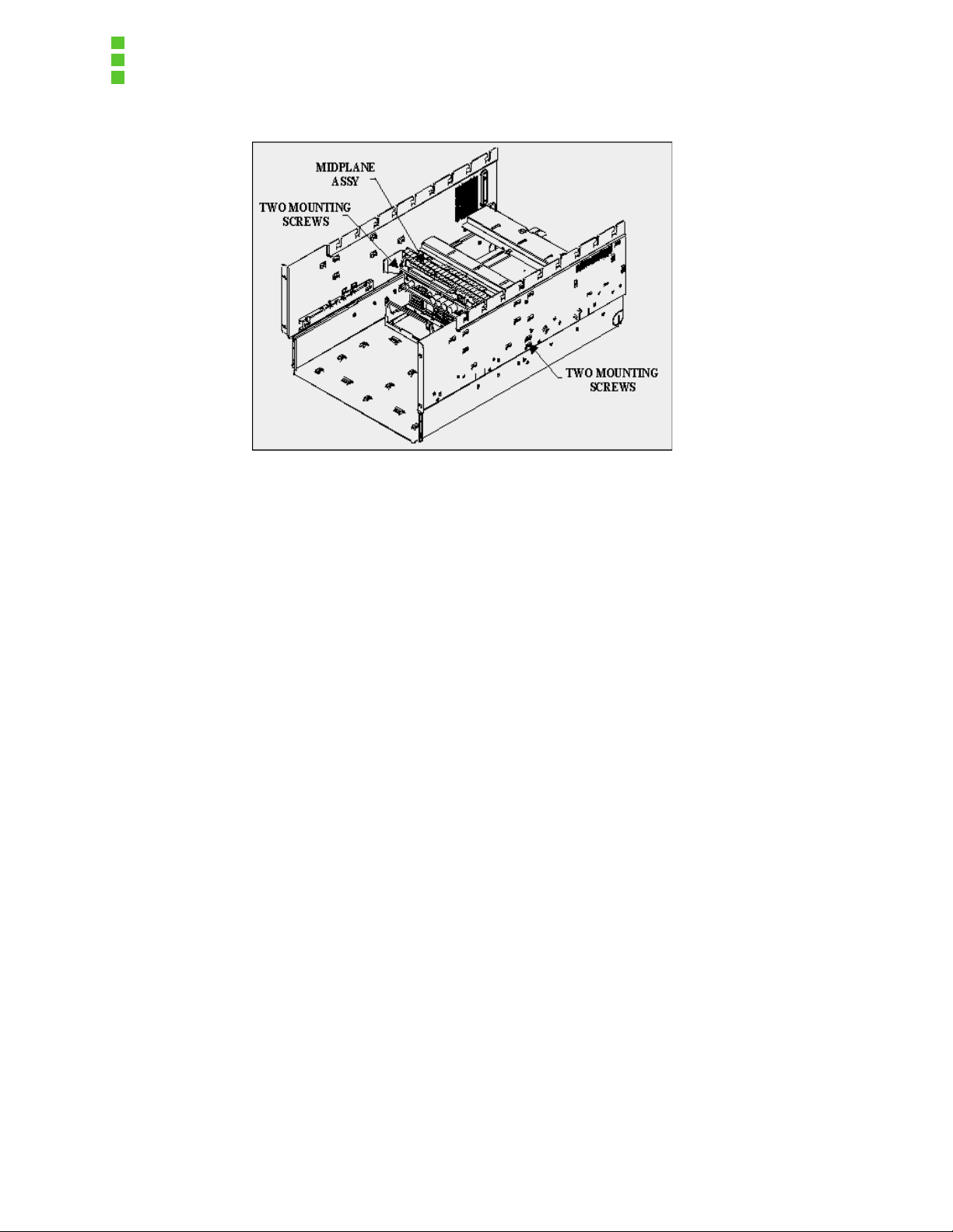

2.9 Midplane Assembly

The midplane assembly serves as an i nterconnect bet ween the power suppli es, memory boa rds,

Profusion carrier, and the I/O carrier. With the exception of limited server management and field

replaceable unit (FRU) components, the mi dplane assembly s erves merely as an interconnect ion

device, routing the signa ls between the boards , whi le maintaining the signal integr i ty requi re d for

the 100-MHz buses.

Figure 2-10: Midplane Assembly

The midplane assembly is inst alled into the OCPRF100 MP server system chass is by rotating the

assembly about two ali gnment s tru ctures. T he assembly i s secur ed b y a tot a l of fo ur scr ews, t wo

screws are located on each side of the system. All four screws must be removed to extract the

midplane assembly. The tab on the midplane assembly is used to manage the cables between

the I/O baseboard and the peripheral blind-mat e board.

13

Page 21

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Figure 2-11: Midplane Assembly Installed in System

2.10 I/O Carrier

The I/O carrier is the i nterf ace that con nects the I/O port of t he Profu sio n chi p set to the foll owing :

• Ten hot-swappable PCI slots (four of which support 66-MHz transactions).

• Legacy connector (video, keyboard, serial, parallel, USB, and Intelligent Chassis Man-

agement Bus (ICMB) ports).

• Dual LVDS.

• Internal IDE buses, floppy disk, disk drives, and SCSI connectors for peripheral support.

The PCI hot-plug (PHP) I/O carrier, legacy connector, LVDS connectors, ICMB board, and

enhanced PCI hot-plug board are assembled onto the I/O carrier tray. The PCI hot-plug base

shield is assembled and mounted over the PHP I/O board, and secured by six screws. The PHP

slot dividers snap onto the PHP base shield.

14

Page 22

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Figure 2-12: I/O Carrier Tray

The I/O carrier tray features tabs on the base of the tray that engage into slots on the horizontal

members in the chassis. Lower the tray from the top of the system and slide the tray toward the

center of the chassis using the two insert/extract handles located on the back of the tray. Secure

the I/O carrier tray to the chassis with the four screws located on the sides and back of the chassis.

Figure 2-13: Installing the I/O Carrier Tray

15

Page 23

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

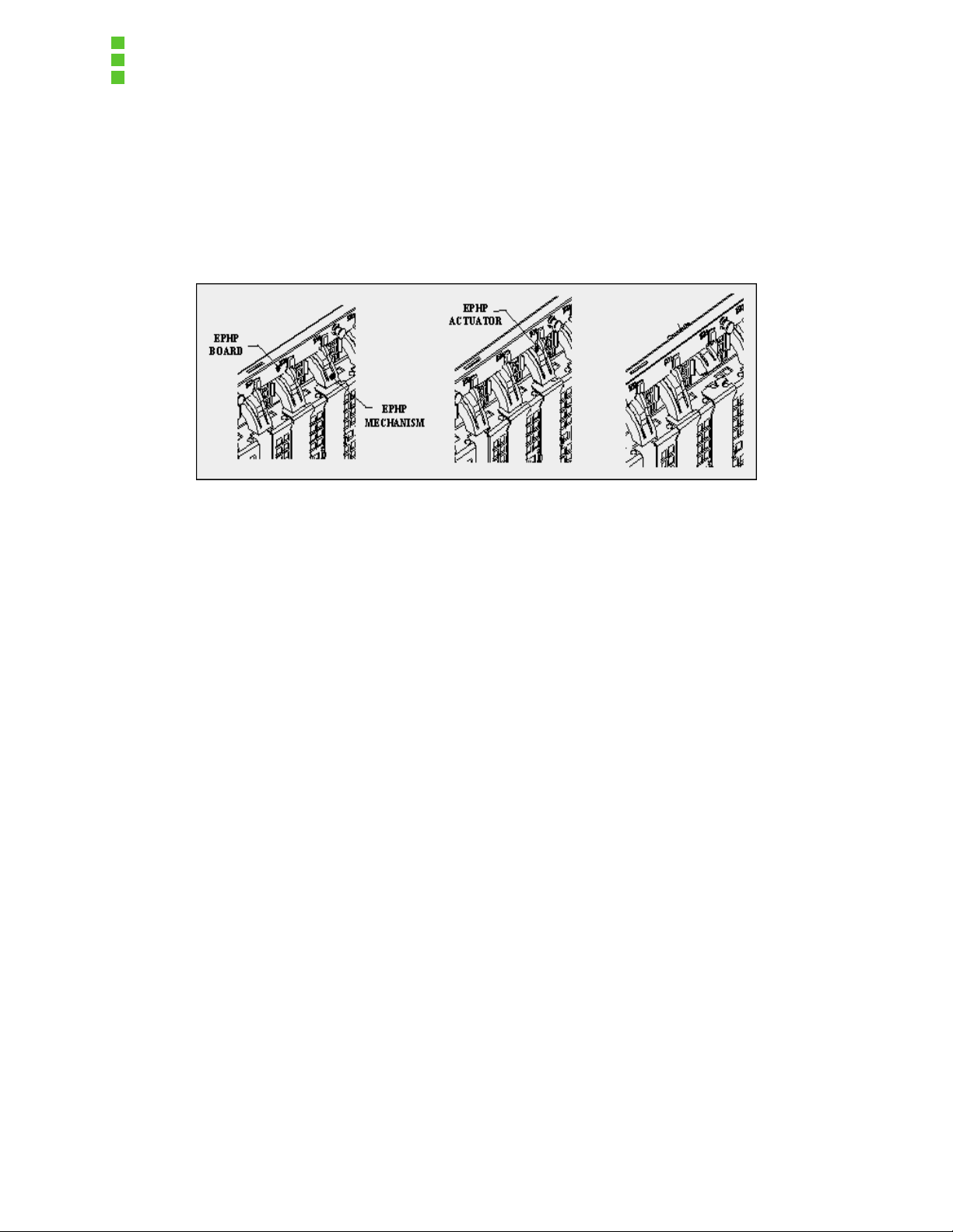

The PHP mechanism is a rotating part that actuates a switch located on the PHP board. There

are four light emitting diodes (LEDs) per sl ot--tw o can be viewed fr om the rear of the system and

two from inside the system. Once the LED shows which slot is powered down, the PHP mechanism can be depressed on the PHP actuator and the mechanism can be rotated out of place to

remove the PCI card. Once the new PCI card is installed, rotate the PHP mechanism back into

place to activate the switch and secure the PCI card.

Figure 2-14: PHP Mechanism

2.11 Power Supply

The OCPRF100 MP server system power supply operates at 208 - 220 Vac, or 100 - 115 Vac is

rated at 750 watts, and is designed to be hot-swappable, with a 2+1 redundancy factor. Each

power supply has indicators showing correct operation, failure, and predictive failure. A power

supply displaying the predicti ve fail ure LED still will oper ate corect ly, but needs to be sent out for

repair as quickly as p ossible. The predictiv e failure feature is designed t o warn the operat or of an

impending power supply failure.

2.12 OCPRF100 MP Server System Chassis

The system chassis is the rack-mount chassis used in the system. The system chassis is

designed to house all of the components listed above within a 7Ux 32” (+/-) deep space, and

mount in a 19-inch rack. The chassis itsel f is 28” deep with the extra 4” to account for cable management. The chassis was engineered to provide easy access to per form maintenance,

upgrades, add memory, and add or remove PCI cards.

The functional server weighs between 120 and 140 pounds, depending on internal configurations. The chassis is designed to provide adequa te thermal cooling of all devices within an ambient temperature of 10° to 40°C, while maintaining noise levels below 57 dB. If the ambient

temperature exceeds 30°C, the fans in the fan bay will sw itch to high speed, cooling the system

to operational values. Server management will log that a thermal excursion has occurred. Several internal heat sensors will monitor the temper ature at key point s inside the server. Should any

of these sensors indicate that the temperature has exceeded a critical thermal set-point, server

management will log the event, and the server will be shut down gracefull y, according to user

setup.

16

Page 24

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

3. System Overview

This chapter describes the features of the OCPRF100 MP server system chass is.

System Features

Table 3-1 provides a list and brief description of the features of the OCPRF100 MP server system, which utilizes the OPRF100 board set.

Table 3-1: OCPRF100 MP Server System Feature List

Feature Description

Upgradeability

PCI hot plug The chassis with the OPRF100 board set supports 10 64-bit PCI hot-plug

Compact, high-density system The system size is a 7U (12.25-inch) rack-mount server.

Redundant power The system supports three 750-W power supplies in a redundant (2 + 1)

Redundant cooling Six system fans in a redundant (5+1) configuration cool the upper system

Modular peripheral bay The peripheral bay supports one floppy disk drive, one 5.25-inch half-

Front panel liquid cr ys t al displ ay

(LCD)

Intelligent Management Platform Initiative (IPMI) compliant

The system can be upgraded to future processors within the Pentium

Xeon™ processor fa mily.

slots (four at 66 MHz, six at 33 MHz).

configuration.

(CPU and I/O). Three internal power supply fans cool the lower system

(memory, peripheral ba y, and p ower sup plies ) in a red undan t confi guratio n

when the power supply configuration is redundant (2+1).

height device, and two 3.5-inch by 1.0- or 1.6-inch hot-swappable LVDS

SCSI hard drives.

A two line LCD provides the system status.

Intelligent Platform Management Bus (IPMB) for intrachassis communication is provided. Emergency management port (EMP) is used for remote

management.

®

III

3.1 Introduction

The scalable architecture of the OCPRF100 MP server syste m supports symmetrical multiprocessing (SMP) and a variety of operating systems (OS). The server provides 10 PCI card slots.

The Profusion carrier contains connectors for installing up to eight Pentium III Xeon processors

packaged in single-edge contact cartridges (SECC). Each of the two memory carriers supports

17

Page 25

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

up to 16 GB of error correcti on code (ECC) PC-100 comp atible regi stered DIMMs. The I/O c arrier

contains four 66-MHz and six 33-MHz 64-bit hot-swap PCI slots, I/O ports, and various controllers.

Figure 3-1: OCPRF100 MP Server System Chassis with Peripheral Bay shows an isometr ic view

of the chassis with the peripheral bay installed.

Figure 3-1: OCPRF100 MP Server System Chassis with Peripheral Bay

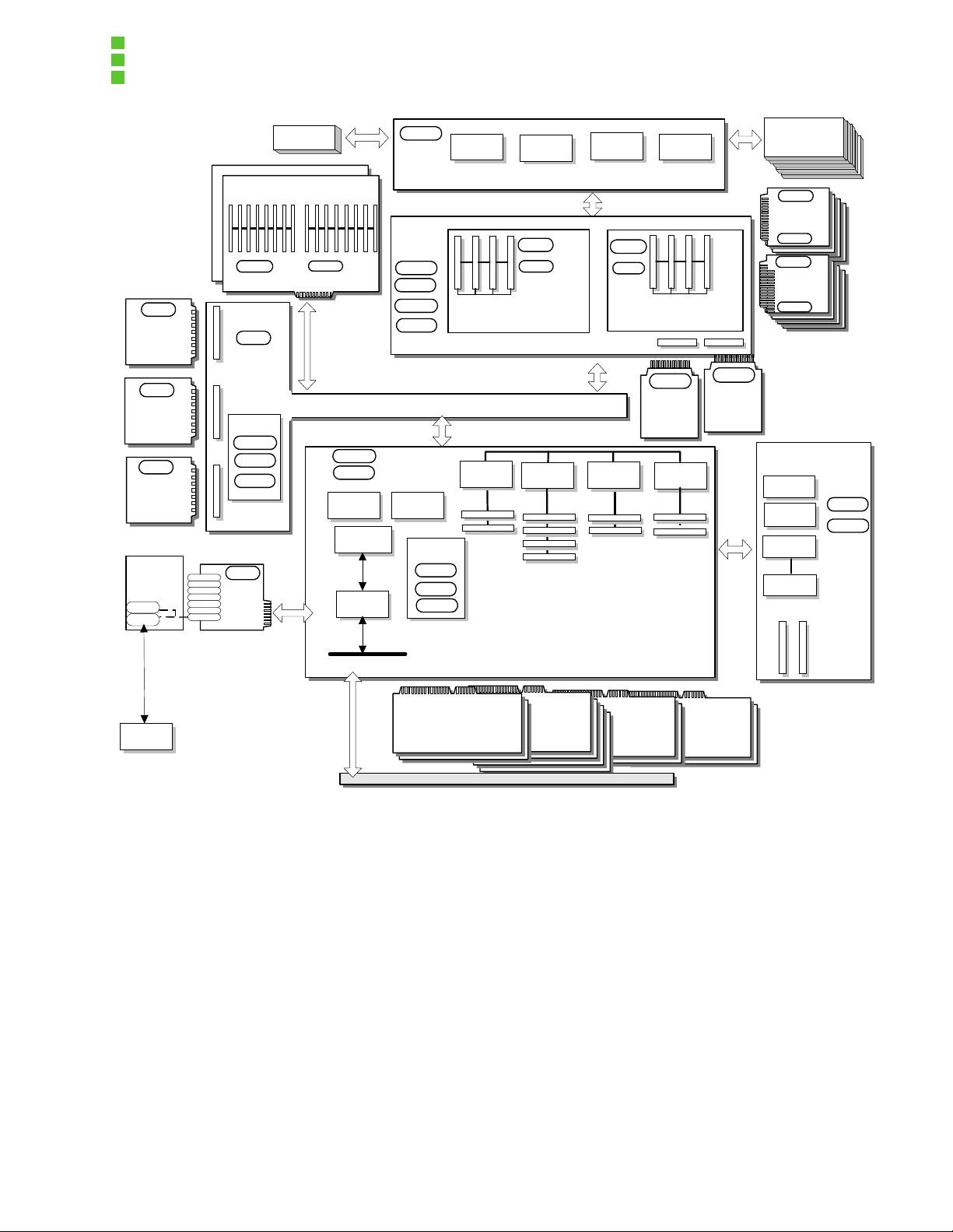

Figure 3-2: OPRF100 Board Set/System Board Locations withi n Server Chassis displays t he layout of the OPRF100 board set with respect to location within the chassis. The Profusion carrier

and I/O carrier are mounted hor izont ally, with the Profusion carrier toward the front of the ch assis

and the I/O carrier immediat ely behind at the r ear of th e chassis . The midplan e di stri butes power

and signal connections to al l boards. T he midplane resi des between the Pr ofusion car rier and the

I/O carrier, and interconnects these carriers with the memory carriers and system power supplies. The front panel resides in front of the Profusion c arrier in the same plane and provides the

user interface, system management, and cooling syst em power and control.

18

Page 26

Profusion Carrier

Front Panel

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

I/O Riser Board

I/O Carrier

Power Supplies

Memory Carriers

Midplane

Figure 3-2: OPRF100 Board Set/System Board Locations within Server Chassis

The peripheral bay mounted at the lower front of the chassis sup ports a 3.5-inch floppy drive, a

half-height 5.25-inch device (e.g., CD-ROM) and two 3.5-inch by 1.0- or 1.6-inch hot-swap hard

drives. SCSI drives in the hot-swap hard drive bays can be hot-swapped without shutting down

the server.

The chassis supports up to three hot-swap, redundant power supplies in a 2+1 configuration.

These supplies provide redundant and hot-swappable cooling to the memor y carri ers an d per ipherals when the power supplies are i n a redundant conf iguration. A cover plate for the un occupied

power supply location is supplied for sys tems without redundancy, and should be used to provide

adequate cooling and EMI shielding.

The system design provides a hot-swap, redundant (5+1) cooling system for the Profusion and I/

O carriers. Basic controls and indicators are located on the front panel.

The front bezel can be customized for integrators to meet their industrial design requirements.

The front bezel contains openings to provide adequate cooling for the chassis components and

access to the peripherals.

Figure 3-3: OCPRF100 MP Server System Chassis Bloc k Diagram shows a block diagram of t he

server system.

19

Page 27

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

FRU

Hot Swap

Power

Supply

FRU

Hot Swap

Power

Supply

FRU

Hot Swap

Power

Supply

Intelligent

Chassis

Management

Bus PBA

icmb

icmb

Intelligent

Chassis

Mgt. Bus

kbd

mouse

serial

serial

parallel

video

icmb

Temp

FRU

Power

Distribution

Volt

Temp

Status

FRU

I/O riser

card

LCD

Memory Carrier

(16 DIMMs)

Midplane

IPMB,

I2C

FRU

I2C,

PIIX4E SMBus

Volt

Temp

BMC flash

BMC

SMIC

Profusion*

Carrier

BMC RAM

ISA Bus

FRU

FRU

Temp

Volt

Status

SEEPROM

LEDs

Slot Type-2

Slot Type-2

IPMB, I2C, PIIX4E SMBus

PB64

BMC

SDR

SEL

FRU

Slot Type-2

Processor

Mezzanine

33MHz

PCI

FPC

Front Panel

Temp

FRU

Slot Type-2

Board

PB64

I/O Carrier

IPMB, I2C

33MHz

PCI

FPC flash

IPMB, I2C

Temp

FRU

Processor

Mezzanine

Board

PB64

66MHz

PCI

FPC RAM

Slot Type-2

Slot Type-2

FRU

Cache

Coherency

Board

(optional)

PB64

All slots are

64-bit &

Hot- Plug

Slot Type-2

66MHz

PCI

Slot Type-2

FRU

Cache

Coherency

Board

(optional)

IPMB

FAN

FAN

FAN

FAN

FAN

Temp

Pentium®III

Xeon™

Processor

FRU

Temp

Pentium®III

Xeon™

Processor

FRU

LVDS Disk Backplane

HSC flash

HSC RAM

HSC

SCSI I/F

Drive Slots

Temp

FRU

external

64b PCI

Add In Card

PCI Hot-Plug LED/Switch Board

64b PCI

Add In Card

Add In Card

Figure 3-3: OCPRF100 MP Server System Chassis Block Diagram

3.2 External Chassis Features

3.2.1 Front View of Chassis

The front bezel of the server has two main user-accessible areas:

Front panel liquid crystal display (LCD), switches and indicato rs.

Replaceable media bays—floppy drive and 5.25-inch half-height bay.

20

64b PCI

64b PCI

Add In Card

Page 28

OCPRF100 MP Server System Technical Product Specification

A B C D E F G H

Revision 1.0

I J K L M N

O P Q

Figure 3-4: Front View of Chassis with No Bezel

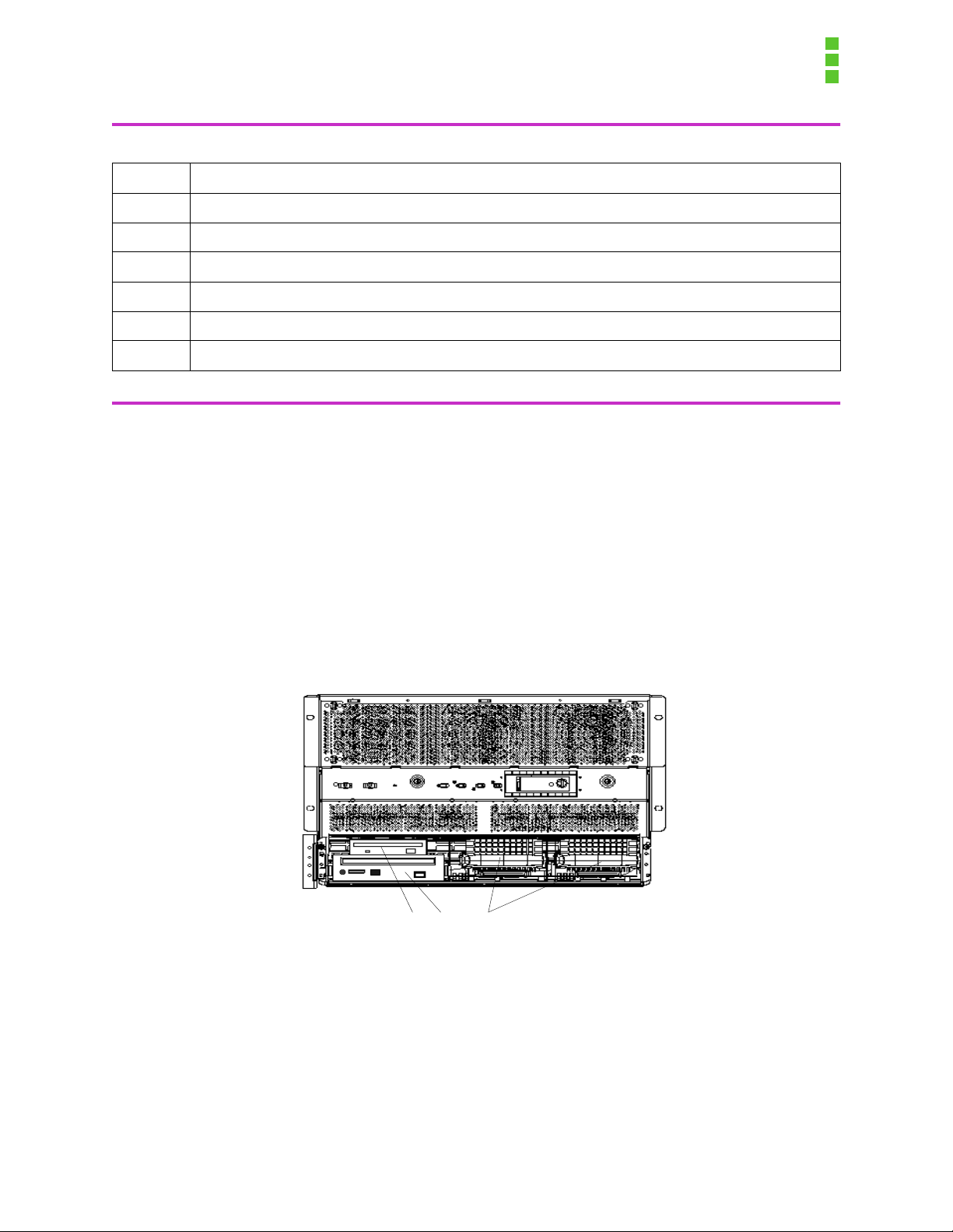

Table 3-2: System Features – Front

Item Feature Description

Front Panel Controls and Indicators

A Power switch When pressed, turns the DC power inside the server on or off.

B Reset switch When pressed, resets the server and causes the power-on self-test

(POST) to run.

C NMI switch When pressed, causes a nonmaskable interrupt (NMI). This switch is

recessed behind the front panel to prevent inadvertent activation. (The

switch must be pressed with a narrow tool.)

D Power (LED) (green) When continuously lit, indicates the presence of DC power in the server.

The light emitting diode (LED) goes out when the power is turned off or

when the power source i s disrupted. Wh en flashin g, indicate s the syst em is

in advanced configuration and power interface (ACPI) sleep mode.

E Power fault LED (yellow) When continuously lit, indi cates a power suppl y failu re. When fla shing , indi-

cates a 240 VA overload shutdown and power control failure.

21

Page 29

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Table 3-2: System Features – Front

F Fan fault LED (yellow) When lit, indicates either a fan failure, or that a predictive fan failure has

been detected in the server.

G Drive fault LED (yellow) When continuously lit, indicates an asserted fault status on one or more

hard disk drives in th e hot-swap bay. When flas hi ng, in dic ate s drive rebuild

in progress.

H Front panel LCD Displays information about processor type and failure codes.

(Items I through L on are control buttons for the CD-ROM, and the location may vary from manufacturer to manu-

facturer.)

3.5-inch Floppy Diskette Drive Descriptions

M Activity LED When lit, indicates the drive is in use.

N Ejector button When pressed, ejects the diskette.

Status LEDs for SCSI Drives in Hot-swap Bays

O Drive power LED

(green)

P Drive activity LED

(green)

Q Drive fault LED (yellow) When continuously lit, indicates an asserted fault status on one or more

When continuously lit, indicates the presence of the drive and that drive is

powered on.

When flashing, indicates drive activity.

hard disk drives in the hot-swap bay. When flashing, indicates that drive

rebuild is in progress.

22

Page 30

3.2.2 Rear View of Chassis

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

A

E

F

G

H

CB

D

I

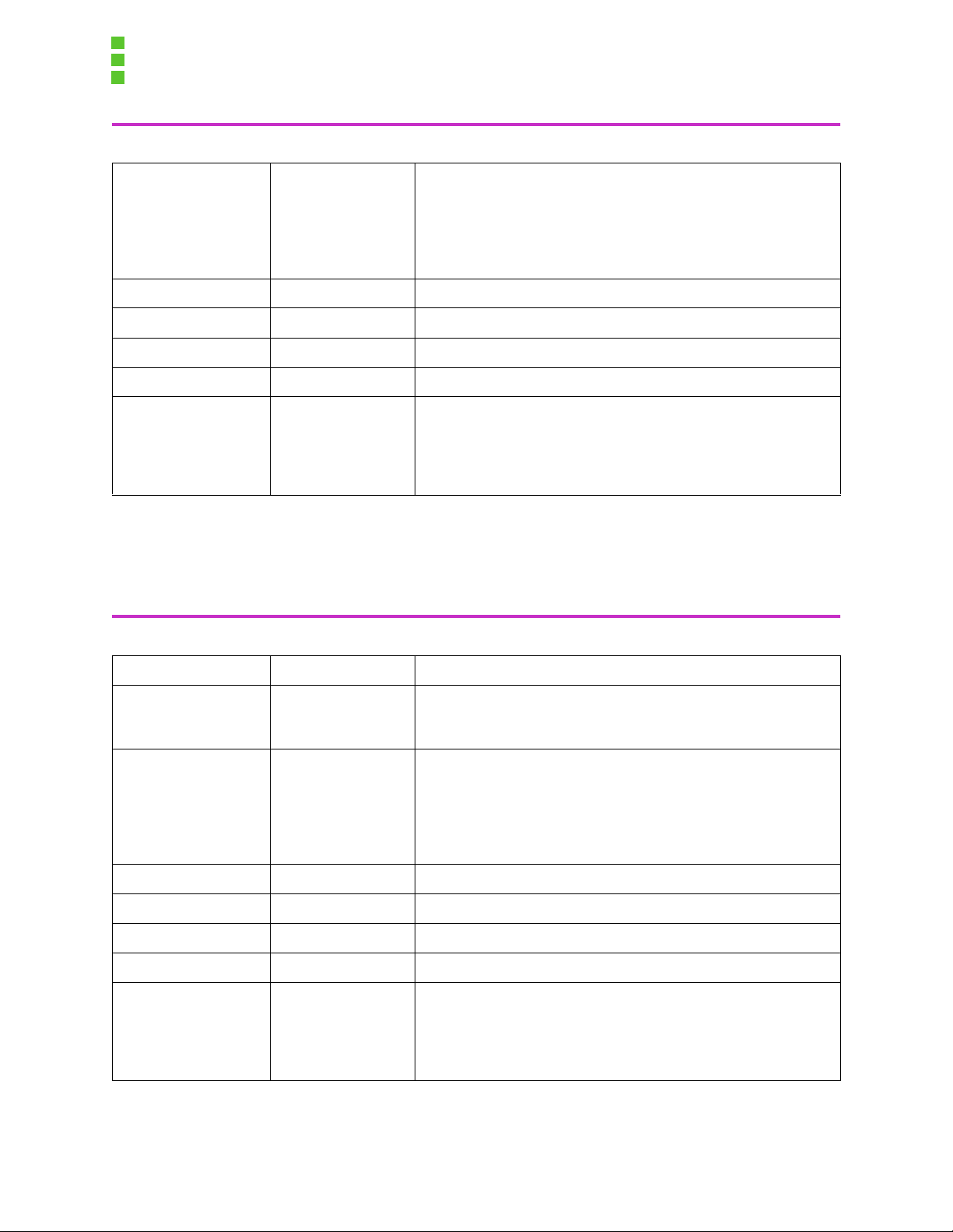

Table 3-3: System Features – Rear

Item Description

A PCI add-in board slots.

B External LVDS connector.

C ICMB connectors in/out.

D I/O riser board.

E AC input power connector.

F Three power supplies.

Figure 3-5: Rear View of Chassis

23

Page 31

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Table 3-3: System Features – Rear

G PWR LED (green) – power condition – refer to Chapter Power Supply for details.

H FAIL LED (yellow) – failure condition – refer to Chapter Power Supply for details.

I PR_FL LED (yellow) – power supply fan predictive failure – refer to Chapter Power Supply for details.

3.2.3 Riser Board External I/O Connectors

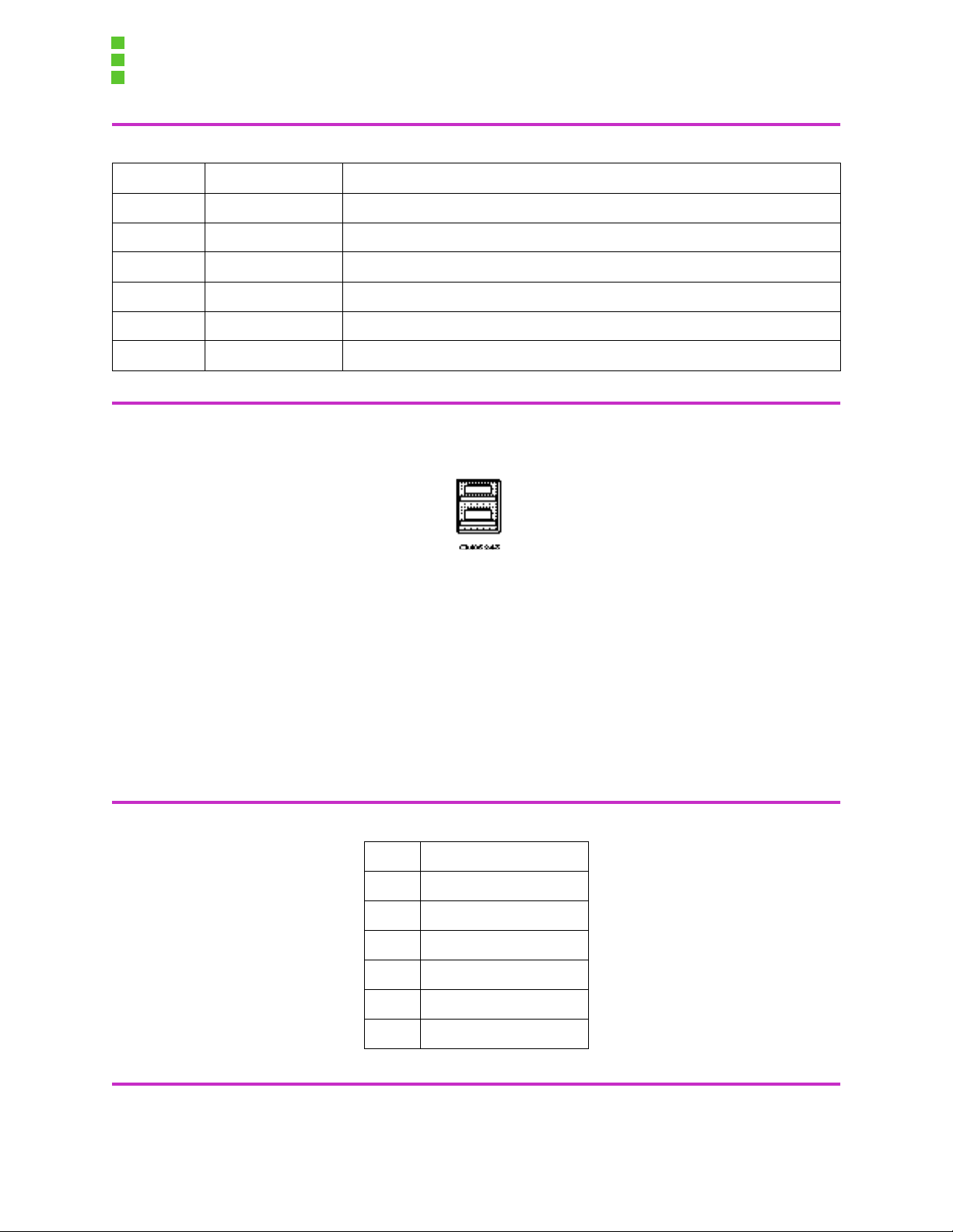

Figure 3-6: Riser Board External I/O Connectors

Table 3-4: Riser Board External I/O Connectors

Item Description

A. Serial port 1 (COM1), 9-pin RS-232 connector.

B. Parallel port, 25-pin bidirectional connector.

24

Page 32

OCPRF100 MP Server System Technical Product Specification

Table 3-4: Riser Board External I/O Connectors

C. USB ports 0 (upper) and 1 (lower).

D. Super VGA compatible, 15-pin video connector.

E. Serial port 2 (COM2), 9-pin RS-232 connector.

F. PS/2-compatible keyboard port.

G. PS/2-compatible mouse port.

H. ICMB port, SEMCONN* 6-pin connector.

I. ICMB port, SEMCONN 6-pin connector.

3.2.4 Peripheral Bay

An optional peripheral bay provides the foll owing:

Revision 1.0

• One 3.5-inch floppy drive bay

• One 5.25-inch user-accessible drive bay for removable media

• Two 3.5-inch by 1.0- or 1.6-inch hot-swap bays for SCSI SCA hard disk drives

A B C

Figure 3-7: Chassis Drive Bays

25

Page 33

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Table 3-5: I/O External Connectors

Item Bay Description

A 3.5-inch bay 3.5-inch floppy drive.

B 5.25-inch half-height bay 5.25-inch half-height peripheral drive.

C 3.5-inch by 1.0- or 1.6-inch bays Two hot-swap capable hard drives.

3.2.5 3.5-inch User-accessible Drive Bay

The system ships from the factory witho ut the peripheral bay installed.

3.2.6 5.25-inch User-accessible Drive Bay

The system ships from the factory witho ut the peripheral bay installed.

Note: Installation of hard disk drives in the 5.25-inch user-accessible bay is not recommended

due to cooling and EMI constraints.

3.2.7 3.5-inch SCSI Hot-swap Drive Bays

Two 3.5-inch hot-swap capable bays support eit her 1.0- or 1.6-inch high SCA SCSI hard disk

drives. These bays are accessible following removal of the lower bezel section. The wide LVDS

SCSI hot-swap backplane provides industry st andard 80-pin SCA-2 connectors for two drives.

Two wide/fast-20 SCSI III SCA type hard disk drives can be install ed in these bays. The wide

LVDS SCSI hot-swap backplane is designed to accept drives that consume up to 28 watts of

power and run at a maximum ambient temperature of 50°C (112°F).

Extruded aluminum drive carriers with integral heat sinks that accommodate 3.5-inch wide by

either 1.0- or 1.6-inch high driv es a re required as part of the hot-swap implementation. The carrier is attached to the drive with four fast eners, and is retai ned in the chassis by a locki ng handle.

The LEDs below each drive display individual drive status. There are three LEDs for each drive:

a power on (green) LED; an activity (green) LED; and a fault (yellow) LED. A fault LED on the

front panel board also indicates a fault on these drives.

Note: Because all hard drives have different cooling, power and vibration characteristics, Intel

will not validate hard drive types in the sys tem chassis. Refer to the OCPRF100 MP Server Sys-

tem Validation Summary document for a list of these drives.

26

Page 34

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

3.3 Internal Chassis Features

3.3.1 Power System

Three 750-W supplies in a standard configuration provide the modular power system for the system.

The power system may be configured with three power supplies (2+1) for power redun-

dancy, or with two supplies in a nonredundant configuration.

a row at the rear bottom of the chassis.

A single AC power cord provides power to the daisy-

chained supplies.

When the server is configured with three power supplies, the user can hot swap a failed supply

without affecting system functionality.

The midplane provides power distribution of the internal power system with minimal active cir-

cuitry.

The power distri bution circui try report s quantity and l ocation of the i nstall ed power supplies

through I

2

C* server management.

Two 750-W, 208-Vac supplies are capable of handling power requirements for the OPRF100

board set and peripherals.

For the OPRF100 board set, this includes eight Pentium II I Xeon pro-

cessors, 32 GB of memory and two 1.6-inch hard drives.

The power supplies are mounted in

The Profusion carrier provides he aders f or two processor mezz anine boar ds, each pr oviding f our

slots for Pentium III Xeon processors. Each mezzanine board has six integrated VRM 8.3 compatible voltage converters. The converter input is +12 Vdc from the power supply. Each Pentium

III Xeon processor core has its own converter. One converter provides power for a pair of Pentium III Xeon processor L2 caches.

The total power requ ir ement for t he OPRF100 board s et exceeds the 24 0 VA energy hazard limit

that defines an operator accessible area. As a result, only qualified technical individuals should

access the processor, memory, and non-hot-plug I/O carrier areas while the syst em is energized .

Refer to Chapter Power Supply Power Suppl y of this document for detailed power specifications.

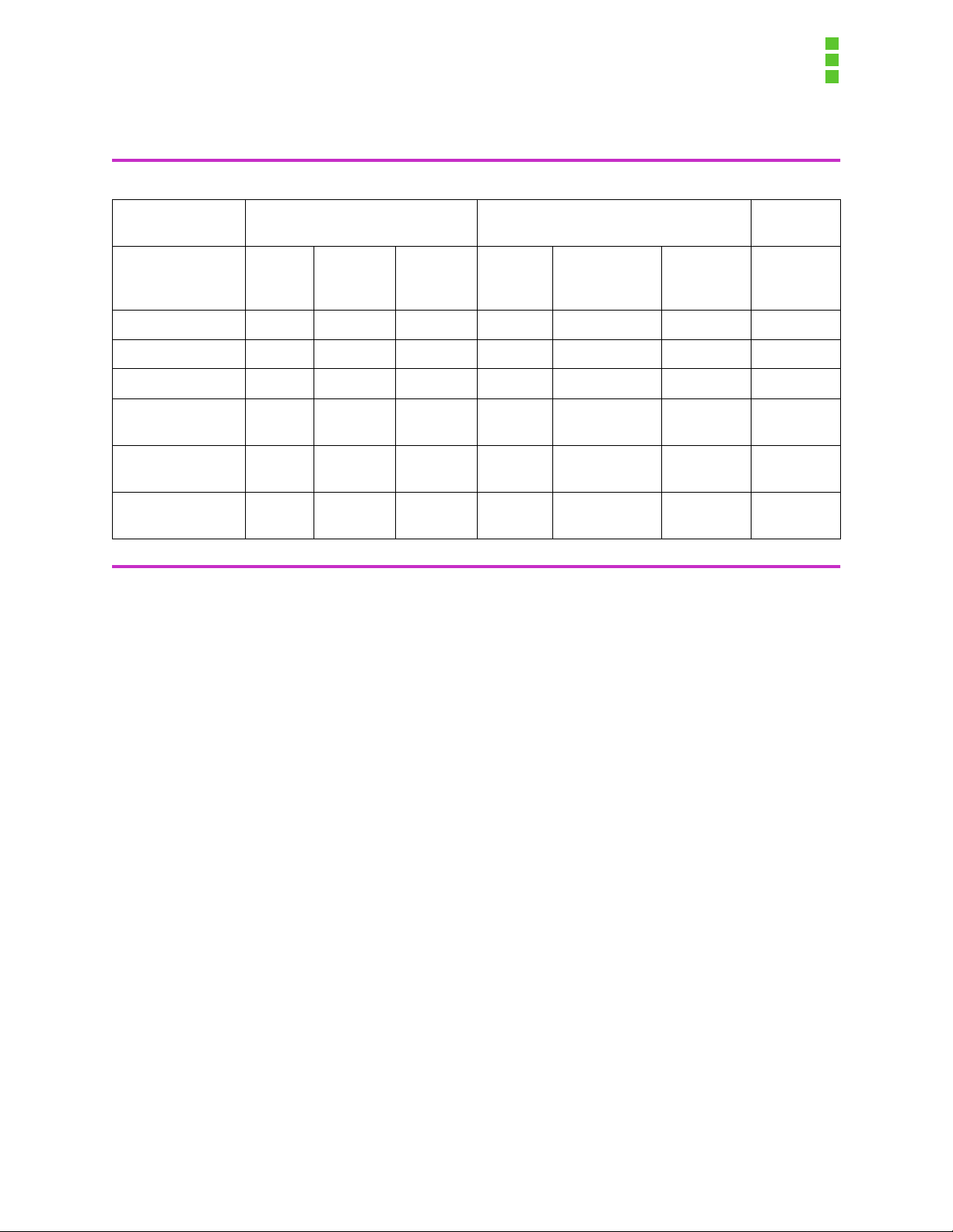

Table 3-6: System Power Budget – Current (A) and Power (W)

OCPRF100 MP Server

System Power Budget

Board Spec Units +3.3 V +5 V +12 V -12 V +5

Units +3.3 V +5 V +12 V -12 V +5

VSB

VSB

Power

Power

I/O Carrier Min. Load Adc 0.20 0.70 0.00 0.20 0.65 9.81

Max. Load Adc 7.99 45.20 5.00 1.20 0.75 330.52

Max. Step Load Adc 2.00 12.17 4.50 0.25 0.10

27

Page 35

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Table 3-6: System Power Budget – Current (A) and Power (W)

Profusion® Min. Load Adc 4.60 0.75 0.25 0.000 0.00 21.93

Carrier w/ Max. Load Adc 12.00 1.50 46.00 0.000 0.00 599.10

Mezzanines Max. Step Load Adc 2. 00 0.75 18.00

Front Panel Min. Load Adc 0.00 0.05 2.00 0.001 0.10 24.76

Max. Load Adc 0.00 0.23 5.40 0.010 0.25 67.32

Plugs into Max. Step Load Adc 0.18 0.10 0.001 0.15

Profusion Carrier

Memory Carrier 1 Min. Load Adc 1.20 0.00 0.00 0.000 0. 00 3.96

Max. Load Adc 23.00 0.00 0.00 0.000 0.00 75.90

Max. Step Load Adc 8.00

Memory Carrier 2 Min. Load Adc 0.00 0.00 0.00 0.000 0. 00 0.00

(Note: 2) Max. Load Adc 23.00 0.00 0.00 0.000 0.00 75.90

Max. Step Load Adc 8.00

Peripherals Min. Load Adc 0.00 0.70 0.25 0.000 0.00 6.50

(SCSI Backplane) Max. Load Adc 0.00 4.50 5.99 0.000 0. 00 94.38

Max. Step Load Adc 0.90 5.40

Midplane Min. Load Adc

Max. Load Adc 0.01 0.01 0.01 0.20

Total min. load Adc 6.00 2.20 2.50 0.20 0.75 66.96

Total max. step load Adc 20.00 14.00 28.00 0.25 0.25

Max. step di/dt A/uS 0.50 1.00 0.60 0.10 0.10

Total max.

load

Total load

power:

1243.32 W 217.8 257.2 748.80 14.52 5 1243.3

Adc 66.00 51.44 62.40 1.21 1.00

28

2

Page 36

OCPRF100 MP Server System Technical Product Specification

Table 3-6: System Power Budget – Current (A) and Power (W)

Total power (includes 2% distribution loss) 1268.1

Notes: 1. There is no 240 VA protection circuit in the OCPRF100 MP server system.

2. Minimum load for second memory carrier is zero; assumes no carrier is installed.

3.3.2 Cooling Syst em

3.3.2.1 Description

There are two independent cooling subsystems:

The upper system, encompassing the front p anel, Profusion carrier, and I/O carrier.

Revision 1.0

9

The lower systems, encompassing the memory carrie rs, peripheral bay, and power supplies.

Air flows in through the bezel and exhausts out the rear of the chassis.

Cooling system redundancy to the upper system is provided by the 5+1 redundant fans at the

front top of the system. All systems come with redundant cool ing for the upper area in standard

factory configuration with six upper system fans. Each fan provides tachometer sign al output to

the front panel t o indicate a fan f ailure. There may be time limit restrict ions on th e service t ime for

fan and PCI hot-plug card replacement.

Cooling system redundancy of the lower system is provided by the 2+1 system power supplies.

Each power supply fan provides t achometer si gnal output. A power supply f an failure is indicat ed

at the front panel as a predictive power supply failure. There may be time restrictions on the service time for power supply hot swap replacement.

3.3.2.2 Redundancy and Ambient Temperature Control

3.3.2.2.1 System Fans

The front panel provides either of two fan input voltages to the system fans. Under normal ambient room conditions (less than 30°C), the front panel supplies 8.4 Vdc to the system fans. When

a system fan fails or when the room ambient temperature exc eeds 30°C, the fan input voltage is

increased to 12 Vdc. Following a room temperature excursion a bove 30°C, the fan voltage does

not change back to 8.4 Vdc unti l the room temperatur e drops below 28°C a nd all syst em fans are

operational.

3.3.2.2.2 Power Supply Fans

The power supply fans are controlled independently by each supply. The ambient temperature

sensed at the inlet to each supply is used as the input to a cont rol cir cuit, which conti nuously var -

29

Page 37

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

ies the fan input voltag e. At 28°C ambient temperature, the fan input volt age is 8.0 ± 0.5 Vdc, and

at 35°C, the fan input voltage is 13.5 Vdc.

3.3.2.3 Cooling Summary

The system fans are sized to provide cooling for up to eight Pentium III Xeon processors. The

power supply fans are sized to cool both fully populated SDRAM board sets, two hot-swap hard

drives, and for maintaining power supply functi on under a full load condit ion . The coolin g system

is designed using a worst case analysis with no margin under a single fan failure (system or

power supply fan) condition. The environmental conditions are summarized in Section Specifications. Figure 3-8: OCPRF100 MP Server System Cooling s ummarizes the c ooling provide d to the

system components when system and power supply fans are operating with 12 Vdc input. The

lower fan speed settings were chosen to meet acoustic and thermal requi rements.

70 CFM (12 Vdc Input)

70 CFM (12 Vdc Input)

70 CFM (12 Vdc Input)

150 CFM

(Maximum w/ all

power supply

fans functioning)

System Fan System Fan System Fan

CFM/

HDA

Profusion*

Carrier

Pentium (R)

III Xeon (TM)

Pentium III

Xeon

Processor

System Fan System Fan System Fan

(16 DIMMs)

Memory Carrier

Memory Module

(16 DIMMs)

12

Hot-Swap Hard Drive

Backplane

Carrier

PB64

PB64

Midplane

I/O

64b PCI Add-in Card

PB64

PB64

750 W Power Supply

750 W Power Supply

750 W Power Supply

64b PCI Add-in Card

64b PCI Add-in Card

64b PCI Add-in Card

PS Fan

PS Fan

PS Fan

210 CFM (12

50 CFM (13.5 Vdc fan

input voltage)

50 CFM (13.5 Vdc fan

input voltage)

50 CFM (13.5 Vdc fan

input voltage)

Vdc)

30

Figure 3-8: OCPRF100 MP Server System Cooling

Page 38

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

3.3.3 PCI Hot-plug

3.3.3.1 Description

PCI hot plug (PHP) is the concept of removing or inserting a standard PCI adapter card from a

system without stopping the software or powering down the system as a whole.

“Hot Replace” means the user can replace a PCI card with an identical card. The re placement

card will use the same PCI resources assigned to the previous card. OS support is required for

this function .

“Hot Add” means the user can add a PCI card to a previousl y unoccupied slot. The system BIOS

needs to reserve PCI resource space for the added adapt er card upon boot.

“Hot Upgrade” means to replace an existing adapter card with a new version of the card and/or

driver. A hot upgrade is not actually a unique operation. It is implemented as a hot removal followed by a hot addition.

3.3.3.2 Hardware Components

Intel has licensed the hardware technology and methods for the implementation of PHP, which

conform to the PCI Hot-plug Specification. The basic components are:

• Power cycling and reset generation hardware that complies wit h the PCI Local Bus Spec-

ification, Rev. 2.1.

• Bus isolation switches to physically disconnect the PHP capable card from the PCI bus

(these switches are located on the I/O carrier between each PHP PCI card).

• Indicators (LEDs), located on the PHP LED/switch board, provide service personnel with

positive slot identificat ion (these LEDs are vi sible when viewed fr om above the I/O carrier,

and can be seen from the rear of the system through holes in the chassis).

• Electromechanical hardware to prevent accidental insertion/removal from a live sl ot (a

PHP switch is provided for each slot; when disengaged this switch immediately removes

power from that slot. Normal slot power down should be through the control utility

• Protection hardware to isolate the live components of the system from the card being

inserted/removed (a mechanical barrier prevents access to the I/O carrier and Profusion

carrier components, and is present between PCI cards; each PHP PCI connector is limited to 240 VA).

• A controller element which c ontrols th e above hardwar e and provides an inter face for sys tem softwar e .

3.3.3.3 Software Components

The main software components for a PHP system are:

Hot-plug User Interface

• Provides user with access to the hot-plug control panel

31

Page 39

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

• Receives user input and sends requests to the service layer

• Displays the status of the PCI slot

• Provides user with access to PHP functions that may be available through multiple inter-

faces

Hot-plug Service

• Provides communication between the user interface a nd the hot-pl ug controller driver and

is responsible for configuring, loading, and unloading the adapter driver component

• Puts the system into a quiescent state through the hot-plug adapter card by making standard system calls

• Provides communication to the hot-plug control ler

• Reports status to the hot-plug user interface

Hot-plug Driver

• Communicates a hot-plug request from the system’s service layer

• Provides a software bridge to the PCI hot-plug hardware

• Drives the hot-plug controller

BIOS

• Supplies initialization of the hot-plug hardware components

• Provides DIMM ID monitoring and presence detection

• Provides Advanced Configuration and Power Interfac e (ACPI) table generation

Adapter Drivers

• For Windows NT* 4.0, changes need to be made to standard miniport drivers.

• For SCO* UnixWare* Version 7.01, the driver must be DDI-8 compliant.

• For Novell* NetWare* Version 5.0, the driver must comply with the NWPA 2.32 or ODI

3.31 specifications.

3.3.3.4 PCI Hot Plug Mechanical Implementation

. The mechanical retention solution includes the following items:

• LED PC board

• Cable between LED board and the I/O carrier baseboard

• Rocker mechanism

• Plastic card guide/retention mechanism to secure the rear of each installed PCI card

32

Page 40

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

• A 240 VA protective shield on the I/O baseboard and the plastic dividers between PCI

slots

The LED PC board contains both the green and amber LEDs, as well as the switch that controls

the PCI slot power. These items will no longer reside on the I/O carrier baseboar d. This LED

board is mounted in the I/O tray directly abov e where the PCI cards were previously sc rewed into

the tray ledge. The LEDs can be seen from both inside and outside of the chassis. Each switch

hangs down off of the LED board so that it can be activate d by the rocker mechanism as it is

folded into the chassis. See Figure 3-9: Rocker Mechanism.

Figure 3-9: Rocker Mechanism

The rocker mechanism activates the slot power switch as it enters the I/ O tray. The rocker can be

released only from within the chassis. This is to prevent unintentional power down of PCI slots

when the system is powered up and the chassis has not yet been pulled out of the rack. The

rocker also acts as a retenti on mechanism for t he PCI card. An additional rete ntion mechani sm at

the back edge of the PCI card is currently being developed.

The opposite end of the PCI card is held in place by a plastic, snap-in, locking card guide. The

guide, installed on the center support bracket, has a built in retention mechanism that secures

the top-rear edge of the PCI card. (See Figure 3-10.)

33

Page 41

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

Figure 3-10: PCI Card Retention Mechanism

Revised non-hot plug, hot plug, and t op cover s are re quir ed to ac commodate t he ad diti onal hard ware used in this enhanced solution.

3.4 Server Management

The server system management architecture features several management controllers, which

autonomously monitor server status and provide the interface to server management control

functions. The controllers communicat e via an I

Platform Management Bus (IPMB).