Page 1

INTELLECT

DOUBLE DENSITY

DISKETTE OPERATING SYSTEM

HARDWARE

REFERENCE

MANUAL

Copyright © 1977

Intel

Corporation

Intel Corporation, 3065 Bowers

Avenue,

Santa Clara, California 95051

Order Number:

9800422-01

Page 2

Additional

copies

of

this manual

or

other Intel literature

may be

obtained from:

Literature

Department

Intel

Corporation

3065

Bowers Avenue

Santa

Clara,

CA

95051

The

information

in

this document

is

subject

to

change without notice.

Intel

Corporation makes

no

warranty

of any

kind with regard

to

this material, including,

but not

limited

to, the

implied

warranties

of

merchantability

and fitness for a

particular purpose.

Intel

Corporation assumes

no

responsibility

for any

errors

that

may

appear

in

this document. Intel Corporation makes

no

commitment

to

update

nor to

keep current

the

information contained

in

this document.

Intel Corporation assumes

no

responsibility

for the use of any

circuitry

other

than circuitry embodied

in

an

Intel

product.

No

other circuit patent licenses

are

implied.

Intel

software products

are

copyrighted

by and

shall remain

the

property

of

Intel Corporation. Use, dupli-

cation

or

disclosure

is

subject

to

restrictions stated

in

Intel's software license,

or as

defined

in

ASPR

7-104.9(a)(9).

No

part

of

this document

may be

copied

or

reproduced

in any

form

or by any

means

without

the

prior

written

consent

of

Intel

Corporation.

The

following

are

trademarks

of

Intel Corporation

and its

affiliates

and may be

used

to

identify Intel

products:

BXP

CREDIT

i

ICE

iCS

'm

iMMX

Insite

Intel

lntel

Intclevision

Intellec

Imellink

iOSP

iPDS

iRMX

iSBC

iSBX

iSXM

Librar>

Manager

MCS

Mcgachassis

Micromainframe

Micromap

Multibus

Multichannel

Multimodulc

Plug-A-Bubble

PROMPT

RMX/80

System

2000

UP1

11

A946/583/4K

Jay

Page 3

PREFACE

This

reference

manual

is the

primary source

of

information

for the

hardware

within

the

INTELLEC

Double Density Diskette Operating System.

It

explains

how

the

Diskette System

is

installed,

how it

communicates

with

the

INTELLEC

Microcomputer

Development System,

and how it

functions

internally.

Refer

to the

ISIS-II

System

User's

Guide (order number 98-306)

for

complete

instructions

on how to

operate

the

Diskette System.

For

information

on the

V

J

host system,

refer

to the

INTELLEC Microcomputer Development System Hard-

ware

Reference

Manual

and to the

INTELLEC

Microcomputer Development

System Operator's Manual.

Hi

Page 4

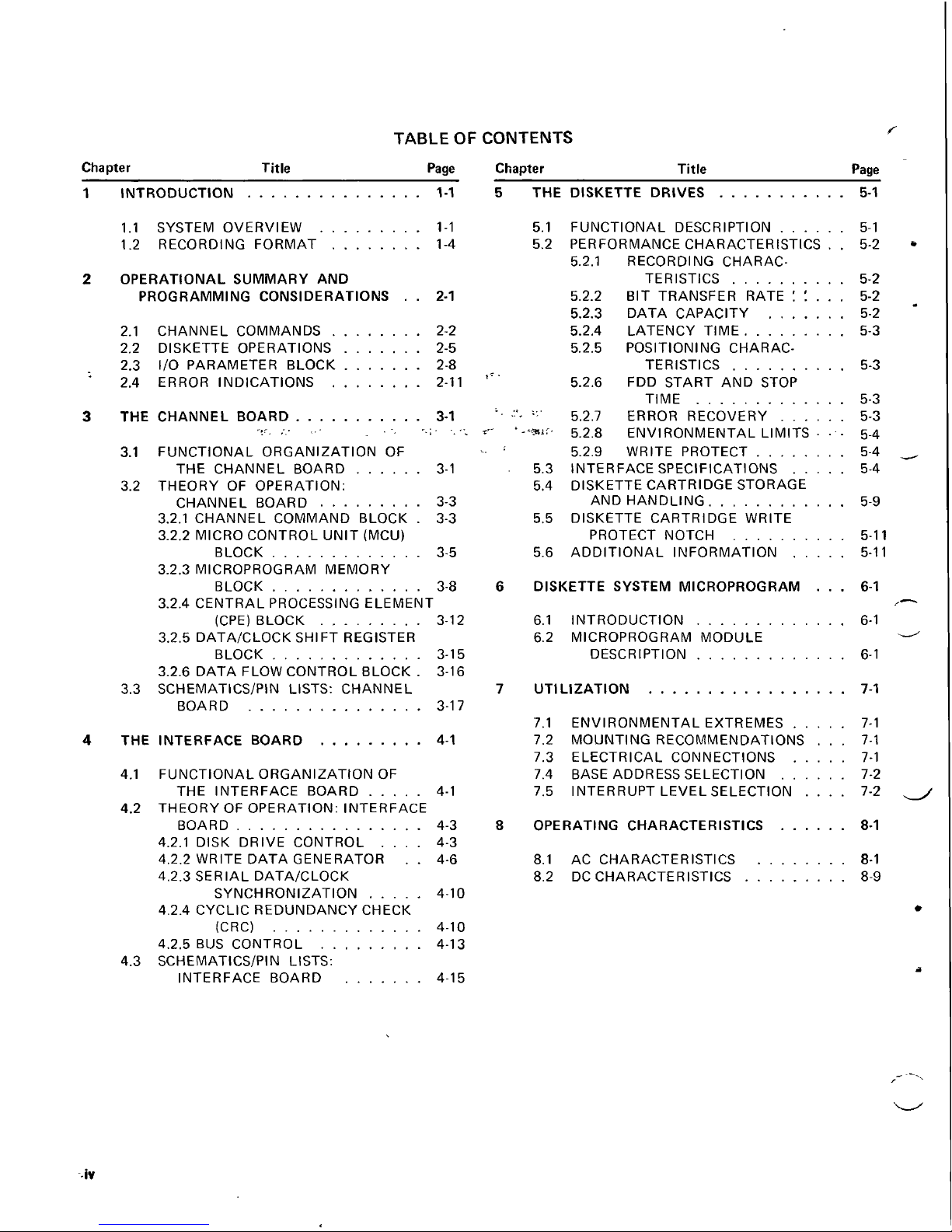

Chapter

Title

TABLE

OF

CONTENTS

Page

Chapter

Title

Page

INTRODUCTION

1-1

1.1

SYSTEM OVERVIEW

1-1

1.2

RECORDING FORMAT

1-4

OPERATIONAL

SUMMARY

AND

PROGRAMMING CONSIDERATIONS

2-1

2.1

CHANNEL COMMANDS

2-2

2.2

DISKETTE OPERATIONS

2-5

2.3 I/O

PARAMETER BLOCK

2-8

2.4

ERROR

INDICATIONS

2-11

THE

CHANNEL

BOARD

3-1

3.1

FUNCTIONAL ORGANIZATION

OF

THE

CHANNEL

BOARD

3-1

3.2

THEORY

OF

OPERATION:

CHANNEL BOARD

3-3

3.2.1 CHANNEL

COMMAND

BLOCK

. 3-3

3.2.2 MICRO CONTROL

UNIT

(MCU)

BLOCK

3-5

3.2.3 MICROPROGRAM MEMORY

BLOCK

3-8

3.2.4 CENTRAL

PROCESSING

ELEMENT

(CPE)

BLOCK

3-12

3.2.5 DATA/CLOCK

SHI

FT

REGISTER

BLOCK

3-15

3.2.6 DATA FLOW CONTROL BLOCK . 3-16

3.3

SCHEMATICS/PIN

LISTS:

CHANNEL

BOARD

3-17

THE

INTERFACE

BOARD

4-1

4.1

FUNCTIONAL ORGANIZATION

OF

THE

INTERFACE

BOARD

4-1

4.2

THEORY

OF

OPERATION: INTERFACE

BOARD

4-3

4.2.1 DISK DRIVE CONTROL

....

4-3

4.2.2 WRITE

DATA

GENERATOR

..

4-6

4.2.3 SERIAL DATA/CLOCK

SYNCHRONIZATION

4-10

4.2.4

CYCLIC

REDUNDANCY

CHECK

(CRC)

4-10

4.2.5

BUS

CONTROL

4-13

4.3

SCHEMATICS/PIN LISTS:

INTERFACE

BOARD

4-15

THE

DISKETTE DRIVES

5-1

5.1

FUNCTIONAL DESCRIPTION

5-1

5.2

PERFORMANCE CHARACTERISTICS

.. 5-2

5.2.1 RECORDING CHARACTERISTICS

5-2

5.2.2

BIT

TRANSFER RATE

:'....

5-2

5.2.3

DATA

CAPACITY

5-2

5.2.4 LATENCY TIME

5-3

5.2.5 POSITIONING CHARACTERISTICS

5-3

5.2.6

FDD

START

AND

STOP

TIME

5-3

'-

''•'

5.2.7

ERROR RECOVERY

5-3

-**«'•

5.2.8

ENVIRONMENTAL LIMITS

•-•

5-4

5.2.9 WRITE PROTECT

5-4

5.3

INTERFACE SPECIFICATIONS

5-4

5.4

DISKETTE CARTRIDGE STORAGE

AND

HANDLING

5-9

5.5

DISKETTE CARTRIDGE WRITE

PROTECT

NOTCH

5-11

5.6

ADDITIONAL INFORMATION

5-11

DISKETTE SYSTEM MICROPROGRAM

6-1

6.1

INTRODUCTION

6-1

6.2

MICROPROGRAM

MODULE

DESCRIPTION

6-1

7

UTILIZATION

7-1

7.1

ENVIRONMENTAL EXTREMES

7-1

7.2

MOUNTING

RECOMMENDATIONS

...

7-1

7.3

ELECTRICAL CONNECTIONS

7-1

7.4

BASE ADDRESS SELECTION

7-2

7.5

INTERRUPT LEVEL SELECTION

....

7-2

8

OPERATING CHARACTERISTICS

8-1

8.1 AC

CHARACTERISTICS

8-1

8.2 DC

CHARACTERISTICS

8-9

-IV

Page 5

LIST

OF

ILLUSTRATIONS

Chapter

Title

Page

1

INTRODUCTION

1-1

1-1

DISKETTE SYSTEM BLOCK DIAGRAM

1-2

1-2

PHYSICAL DATA FORMAT

1-6

1-3

BYTE REPRESENTATION

1-7

1-4

DATA

BYTES

1-7

1-5

DATA

BIT 1-8

1-6

BIT

CELL

1-8

1-7

TRACK FORMAT

1-9

1-8

INDEX ADDRESS MARK 1-10

1-9

ID

ADDRESS MARK 1-10

1-10

DATA

ADDRESS MARK 1-11

1-11

DELETED

DATA

ADDRESS MARK 1-11

2

OPERATIONAL

SUMMARY

AND

PROGRAMMING CONSIDERATIONS

2-1

2-1

SECTOR

FORMAT

2-7

2-2

'DATA'

ADDRESS MARK

2-7

2-3

'DELETED

DATA'

ADDRESS MARK

2-7

2-4

I/O

PARAMETER BLOCK

(IOPB)

FORMAT

2-9

3

CHANNEL BOARD

3-1

3-1

CHANNEL BOARD: FUNCTIONAL BLOCK DIAGRAM

3-2

3-2

3001 MICROPROGRAM CONTROL

UNIT:

FUNCTIONAL BLOCK

DIAGRAM

3-6

3-3

3002

CENTRAL

PROCESSING

ELEMENT: FUNCTIONAL BLOCK

DIAGRAM 3-14

3-4

SCHEMATIC DRAWING: CHANNEL BOARD 3-21

4

INTERFACE BOARD

4-1

4-1

INTERFACE BOARD: FUNCTIONAL BLOCK DIAGRAM

4-2

4-2

HEAD MOVEMENT CONTROL TIMING

4-5

4-3

READ

INITIATE

TIMING

4-6

4-4

M2FM

DATA ENCODING

4-7

4-5

PRECOMPENSATION

TIMING

4-8

4-6

WRITE DATA TIMING

4-9

4-7

PHASE LOCKED OSCILLATOR 4-11

4-8

READ SYNCHRONIZATION TIMING 4-12

4-9 BUS

CONTROL TIMING 4-14

4-10

CLK1/

AND

CLK2/

TIMING 4-15

4-11

SCHEMATIC DRAWING: INTERFACE BOARD 4-22

5

DISKETTE DRIVES

5-1

5-1

FDD/FDCC INTERFACE LINES

5-6

5-2

FDD

DRIVER/RECEIVER CIRCUITS

5-7

5-3

WRITE DATA TIMING

5-8

5-4

READ

DATA

TIMING 5-10

5-5

FLEXIBLE DISK CARTRIDGE

5-11

Page 6

LIST

OF

ILLUSTRATIONS

(Continued)

Chapter

Title

Page

6

DISKETTE SYSTEM MICROPROGRAM

6-1

6-1

INITIALIZATION

6-2

6-2

MAINLINE

6-3

6-3

LOAD

MA

LOWER

6-4

6-4

LOAD

MA

UPPER

AND

START

I/O 6-5

6-5

READ RESULT BYTE

6-6

'

6-6

IOPB LOADER/OP DECODE

6-7

6-7

I/O

FINISH

6-8

6-8

SEEK

6-9

6-9

FORMAT 6-10

6-10 RECALIBRATE 6-12

6-11

VERIFY/READ 6-13

6-12 WRITE DELETED/WRITE 6-15

6-13 ADDRESS PARAMETER CHECKER 6-16

6-14 READ NEXT MEMORY WORD 6-17

6-15 WRITE

DATA

FIELD

6-18

6-16 WRITE CURRENT CHECK 6-19

""

6-17

TIME-OUT

6-20

6-18 ADDRESS

MARK

DETECT

6-21

6-19 HEAD

STEPPER

6-22

6-20 READ DISK BYTE 6-23

6-21

PROCESS

ADDRESS

FIELD

6-24

6-22 WRITE ADDRESS

FIELD

6-25

7

UTILIZATION

7-1

7-1

CONNECTORS

ON

THE

CHANNEL

AND

INTERFACE

BOARDS

7-3

8

OPERATING CHARACTERISTICS

8-1

'8-1

SLAVE COMMAND

TIMING - FDCC

8-2

8-2 BUS

EXCHANGE

TIMING

8-3

8-3 ' MASTER COMMAND

TIMING

8-4

-8-4

STEP/SETTLING

TIMINGS

8-6

8-5

READ

TIMING

8-7

xB-6

WRITE

TIMING

8-7

:

3-7

INDEX

TIMING

8-8

WRITE

FAULT

RESET

TIMING

8-8

VI

Page 7

LIST

OF

TABLES

Chapter

Title

Page

1

INTRODUCTION

1-1

DISKETTE DRIVE PERFORMANCE SPECIFICATIONS

1-3

2

OPERATIONAL SUMMARY

AND

PROGRAMMING CONSIDERATIONS

2-1

INTERRUPT CONTROL BITS

2-11

3 THE

CHANNEL BOARD

3-1

AGO

INPUT

SELECTION

3-7

3-2

MICROINSTRUCTION

BIT

ASSIGNMENTS

3-9

3-3

CONTROL

PULSES

AND

LEVELS

GENERATED

BY

MICROPROGRAM

3-10

3-4

I-BUS

SELECTION

BY

MASK

FIELD

BITS

3-12

3-5

K-BUS

INPUT

SELECTION

3-13

3-6

PIN

LIST:

P1 BUS

CONNECTOR

3-17

3-7

PIN

LIST:

P2

CONTROLLER CONNECTOR

3-19

4 THE

INTERFACE BOARD

4-1

PIN

LIST:

P1 BUS

CONNECTOR

4-16

4-2

PIN

LIST:

P2

CONTROLLER CONNECTOR

4-18

4-3

J1

DRIVE CONNECTOR

4-19

8

OPERATING CHARACTERISTICS

8-1

DISKETTE OPERATING SYSTEM/INTELLEC

BUS AC

CHARACTERISTICS

8-1

8-2

DISKETTE OPERATING SYSTEM/DRIVE INTERFACE

AC

CHARACTERISTICS

...

8-5

8-3

DISKETTE OPERATING SYSTEM

DC

CHARACTERISTICS (INTELLEC BUS)

8-9

8-4

DISKETTE OPERATING SYSTEM

DC

CHARACTERISTICS (DRIVE/DISPLAY

INTERFACE)

8-12

VII

Page 8

-•*:-. ' *

w.

Jl

"»•'

Page 9

CHAPTER

1

INTRODUCTION

The

INTELLEC

Double

Density Diskette

Operating

System provides a bulk

storage

capability

for

Intel's

INTELLEC

Microcomputer

Development System.

The

Diskette System includes

an

intelligent controller

and up to

four

diskette

drives.

Each drive provides

4,100,096

user-accessible

data bits

of

storage

with a data transfer rate

of

500,000

bits/

second.

The

controller

has

been implemented

with

Intel's powerful

Series

3000

Bipolar

Computing

Elements.

The

controller

provides

an

interface

to the

INTELLEC

System bus,

as

well

as

supporting

the

four

diskette

drives.

The

Diskette System records

all

data

in the

Intel soft-sectored

format,

described

in

Section

1.2.

1.1

SYSTEM OVERVIEW

r

4

'-

f

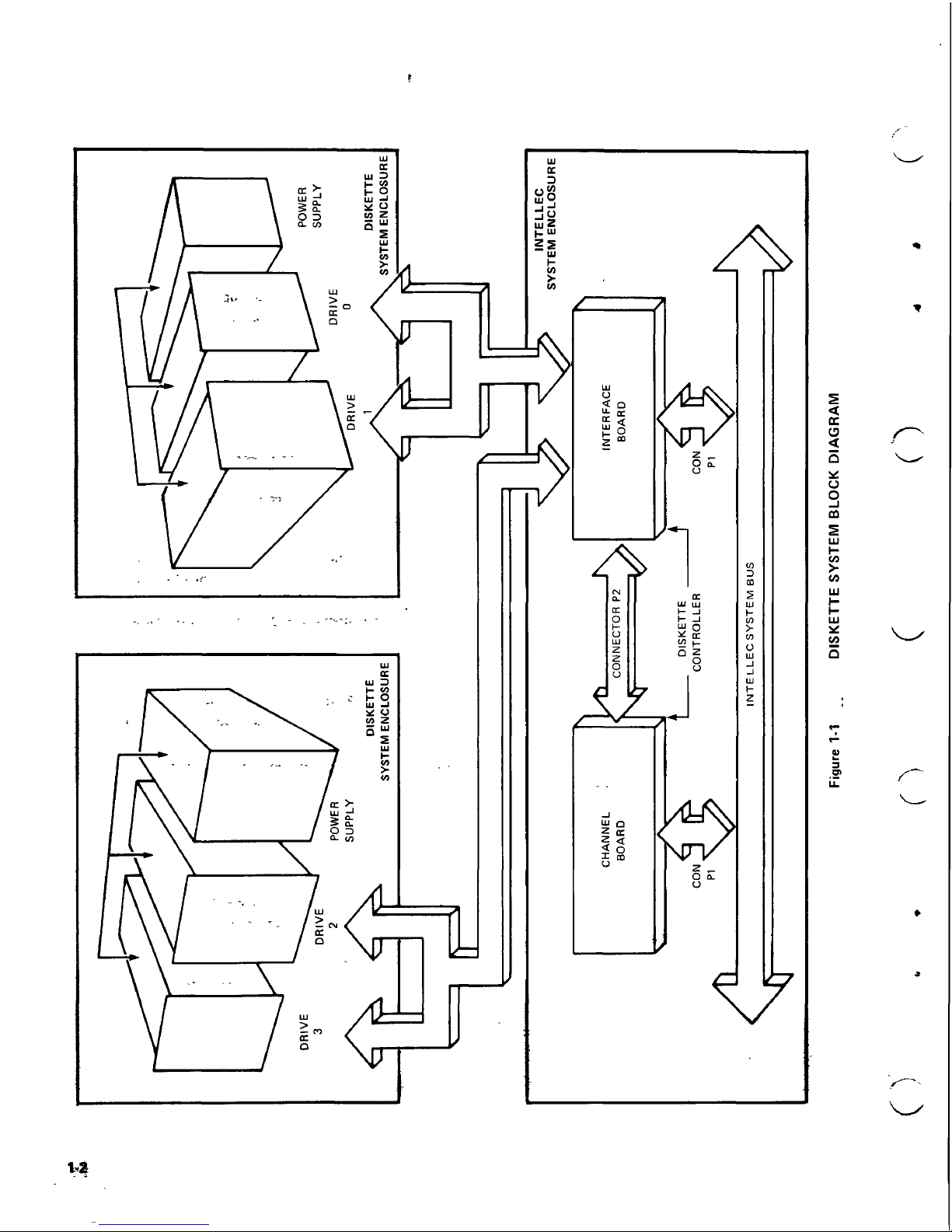

In

addition

to two or

four

diskette drives,

their

enclosure(s)

(two drives

per

enclosure)

and

power supplies,

the

Diskette System

consists

of the

Channel Board

and the

Interface Board. These

two

printed

circuit

boards

reside

in

the

INTELLEC

System cabinet

and

constitute

the

diskette controller. Each

of the

system components

is

shown

in

\

t

-9

.

,3

.

.,

...

...~

.~,.~

3,

g.-,

-

^

\

J

1,

i

*

5

The

Channel Board

is

the

primary

control

module

within

the

Diskette System.

The

Channel Board

receives,

decodes

and

responds

to

channel commands

from a Central

Processor

Unit

(CPU)

in the

INTELLEC

System.

The

Channel

Board

can

access

INTELLEC

System

memory

to

determine

the

particular

diskette

operations

to be

performed

and

to

fetch

the

parameters required

for the

successful

completion

of the

specified operations.

The

Channel Board

also

monitors

Diskette System status

and

error

conditions,

and

organizes

these indications

into

'result

type'

and

'result

byte'

words

that

can be

read

by a CPU in the

INTELLEC

System.

*

«•'

-i

,

The

control

functions

of the

Channel

and

Interface Boards

are

provided

by an

8-bit

microprogrammed processor,

implemented

with

Intel's

Series

3000

Bipolar

Computing

Elements.

The

8-bit

controller

includes

four

3002

Central

Processing

Elements (2-bit

slice

per

CPE), a 3001 Microprogram

Control

Unit

and

512

x 32

bits

of

3604

programmable-

read-only-memory

(PROM)

which

stores

the

microprogram.

The

processing

and

control

capabilities

of the

Diskette

System

are

achieved

by

execution

of the

microprogram.

,

r

The

Interface Board provides

the

diskette controller

with a means

of

communicating

with

the

diskette drives,

as

well

as

with

the

INTELLEC

System bus.

Under

control

of the

microprogram

executed

from

the

Channel

Board,

the

Interface Board

generates

those

signals

which

cause

the

read/write head

on the

selected drive

to be

loaded

(i.e.,

to

come

in

contact

with

the

diskette

platter),

then

cause

the

head

to

move

to the

proper track.

The

Interface

Board accepts

the

data being

read

off the

diskette, interprets certain synchronizing

bit

patterns, checks

the

validity

of the

data using a cyclic

redundancy

check (CRC)

polynomial,

and

passes

the

data

to the

Channel Board.

During

write

operations,

the

Interface Board

outputs

the

data

and

clock bits

to the

selected drive

at the

proper

times.

It

also

generates

CRC

characters

which

are

appended

to the

data; this allows

the

data

to be

verified when

it is

subsequently

read.

j

i * S

1-1

Page 10

cc

(D

o

3

00

s

UJ

CO

CO

LLJ

f-

UJ

V)

Q

0)

3

O)

1-2

Page 11

When

the

diskette

controller

requires

access

to

INTELLEC

System

memory,

the

Interface Board requests

and

maintains

master

control

of the

system bus,

and

generates

the

appropriate memory command.

When

a CPU in the

INTELLEC

System

issues a channel command

to the

Diskette System,

the

Interface Board

acknowledges

the

command

as

required

by

INTELLEC System

bus

protocol.

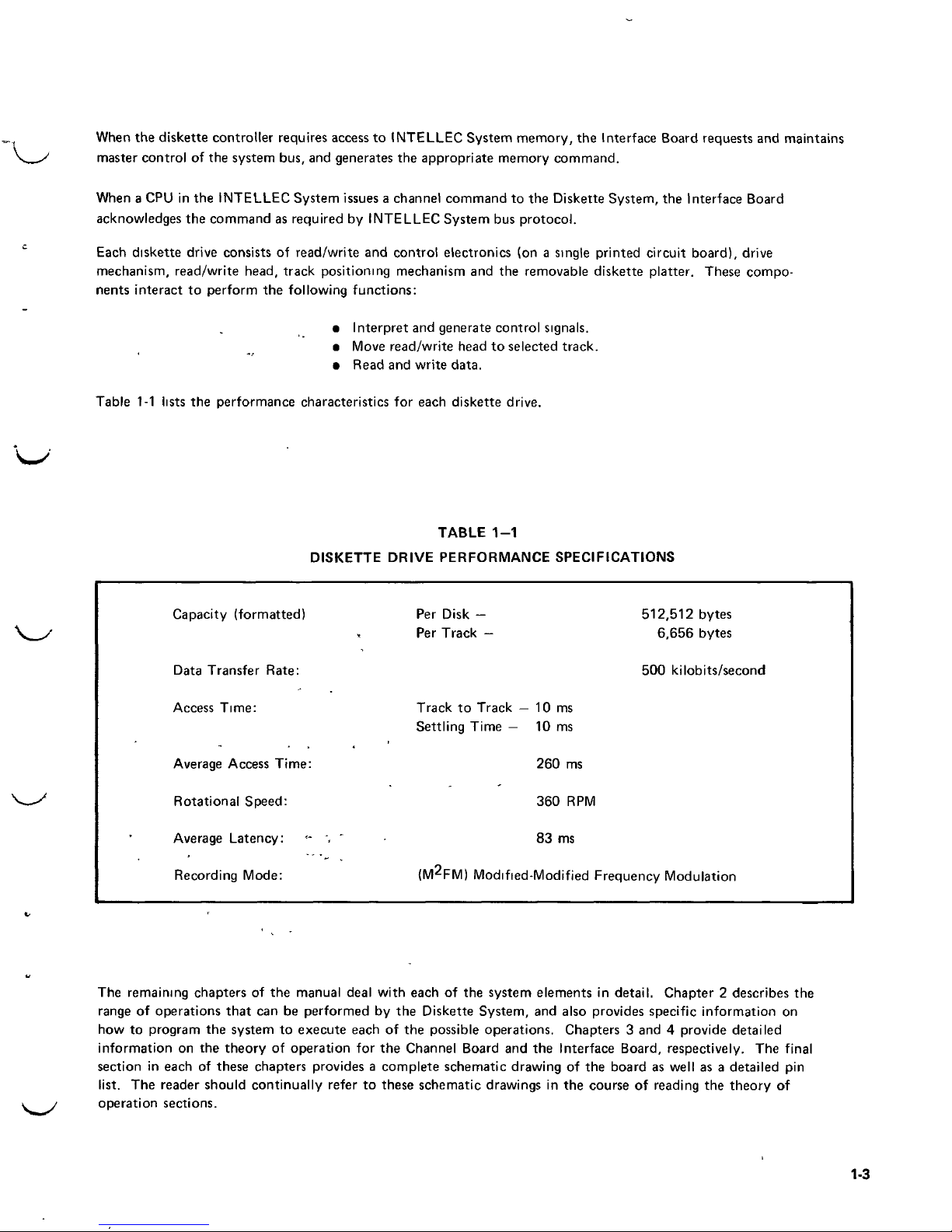

Each

diskette drive consists

of

read/write

and

control

electronics

(on a

single

printed

circuit

board), drive

mechanism,

read/write head, track positioning mechanism

and the

removable

diskette platter.

These

compo-

nents

interact

to

perform

the

following

functions:

•

Interpret

and

generate

control

signals.

•

Move read/write head

to

selected

track.

*

"r

•

Read

and

write

data.

Table

1-1

lists

the

performance

characteristics

for

each

diskette drive.

TABLE

1-1

DISKETTE DRIVE PERFORMANCE SPECIFICATIONS

Capacity

(formatted)

Data

Transfer Rate:

Access

Time:

Average

Access

Time:

Rotational Speed:

Average

Latency:

Recording

Mode:

Per

Disk

-

Per

Track

-

Track

to

Track

-

Settling Time

—

512,512 bytes

6,656

bytes

500

kilobits/second

10

ms

10 ms

260 ms

360 RPM

83 ms

(M^FM)

Modified-Modified

Frequency Modulation

The

remaining chapters

of the

manual deal

with

each

of the

system

elements

in

detail. Chapter 2 describes

the

range

of

operations

that

can be

performed

by the

Diskette System,

and

also

provides specific information

on

how to

program

the

system

to

execute

each

of the

possible operations. Chapters

3 and 4

provide detailed

information

on the

theory

of

operation

for the

Channel Board

and the

Interface

Board,

respectively.

The

final

section

in

each

of

these

chapters provides a complete schematic drawing

of the

board

as

well

as a

detailed

pin

list.

The

reader should continually refer

to

these schematic drawings

in the

course

of

reading

the

theory

of

operation sections.

1-3

Page 12

NOTE:

To

avoid

any

confusion when referring

to the

schematics

for the

Channel

and

Interface

Boards,

or

when

reading

the

corresponding

circuit

descriptions,

the

following

notation,

concerning

the

active level

of a

signal,

will

apply:

Whenever a signal

is

active-low,

its

mnemonic

is

followed

by a

slash;

for

example

MRDC/

means

that

the

level

on

that

line

will

be low

when

the

memory

read

command

is

true (active).

If the

signal

is

subsequently inverted, thus making

it

active-high,

the

slash

is

omitted;

for

example,

MRDC

means

that

the

level

on

that

line will

be

high when

the

memory command

is

true.

Chapter 5 lists

the

manufacturer's

information

on the

diskette

drives.

Chapter 6 provides

the

major state

flow

charts

for the

microprogram

which

is

executed

by the

Series

3000

Bipolar

Microcomputer

Set (on the

Channel

Board),

and

which

essentially controls operation

of the

Diskette System. Chapter 7 provides basic

information

on the

installation

and use of the

Diskette System.

Finally,

Chapter 8 summarizes

the AC and DC

operating

characteristics

for the

Diskette System.

Before proceeding

to

Chapter

2,

however,

we

first provide a comprehensive review

of the

Intel

soft-sectored

recording

format

which

is

used

by the

Diskette Operating System.

1.2

RECORDING FORMAT

This section summarizes

the

specifications

for the

soft-sectored recording

format

used

by the

Diskette Operating

System.

->«•;- !«-»

Physical

Data

Format:

The

physical data

format

is the

format

that

the

diskette

controller

circuitry

must interact

with.

The

elements

of the

physical data

format

are the

hard index hole, index mark, sector

address

marks, sector

headers,

and

data

sectors.

The

index mark

and

sector

address

marks

are

recorded

with

unique

clock patterns requiring

the

con-

troller

circuitry

to

accumulate

the

unique

clock

patterns

for

index

and

sector

address

mark

identification.

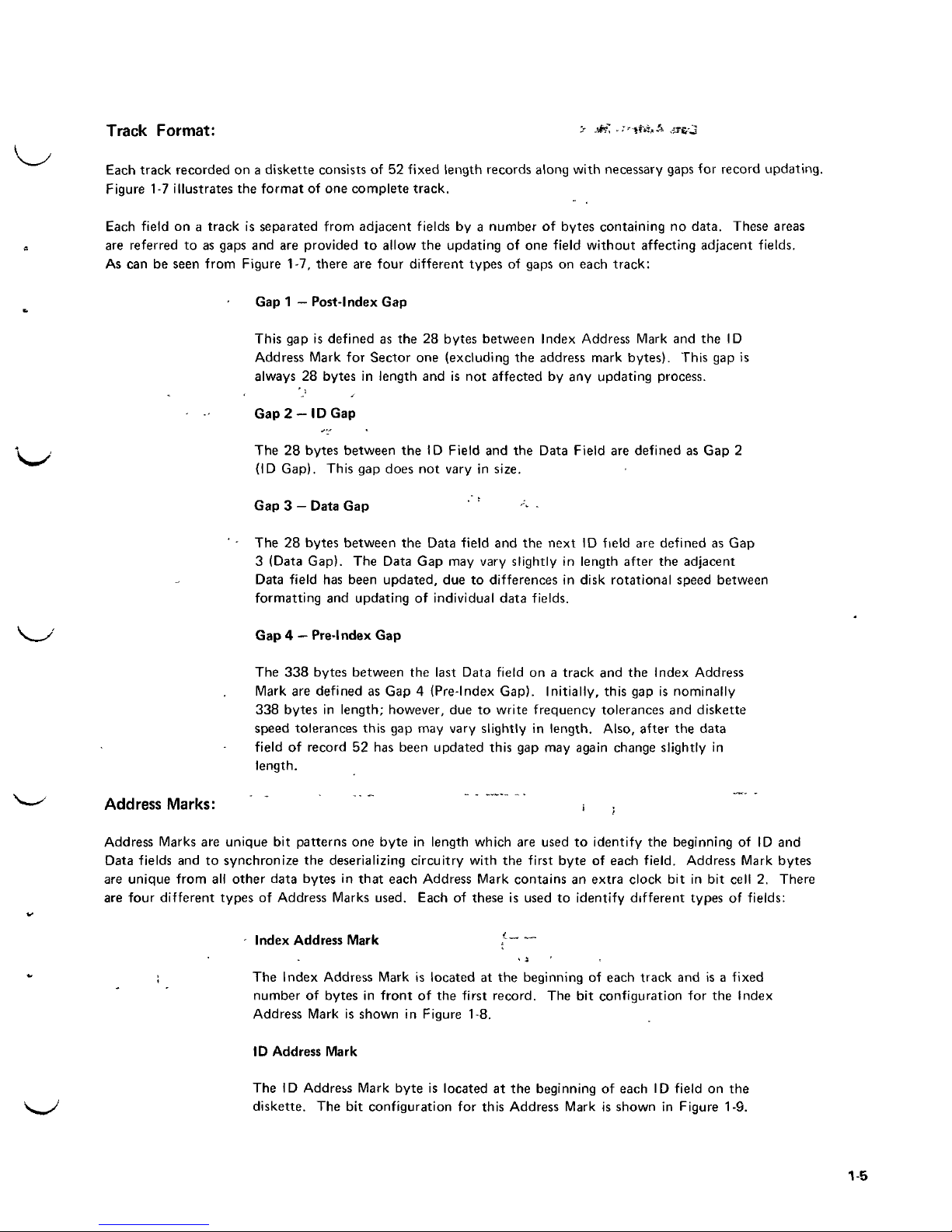

Figure

1-2

illustrates

the

general physical data

format.

J

.<

*• ;-.Y

A

'byte',

when referring

to

serial

data (being

written

to or

read

from

the

diskette drive),

is

defined

as

eight

(8)

consecutive

bit

cells.

The

most

significant

bit

cell

is

defined

as bit

cell

0 and the

least

significant

bit

cell

is

defined

as bit

cell

7.

When reference

is

made

to a

specific data

bit

(i.e., data

bit 3), it is

with

respect

to the

corresponding

bit

cell (bit cell

3).

During a write

operation

bit

cell

0 of

each

byte

is

transferred

to the

drive

first

with

bit

cell 7 being

transferred

last.

Correspondingly,

the

most significant

byte

of

data

is

transferred

to the

diskette first

and the

least

signifi-

cant

byte

is

transferred last.

When data

is

being read back

from

the

drive,

bit

cell

0 of

each

byte

will

be

transferred first

with

bit

cell

7

last.

As

with

reading,

the

most significant

byte

will

be

transferred first

from

the

drive

to the

user.

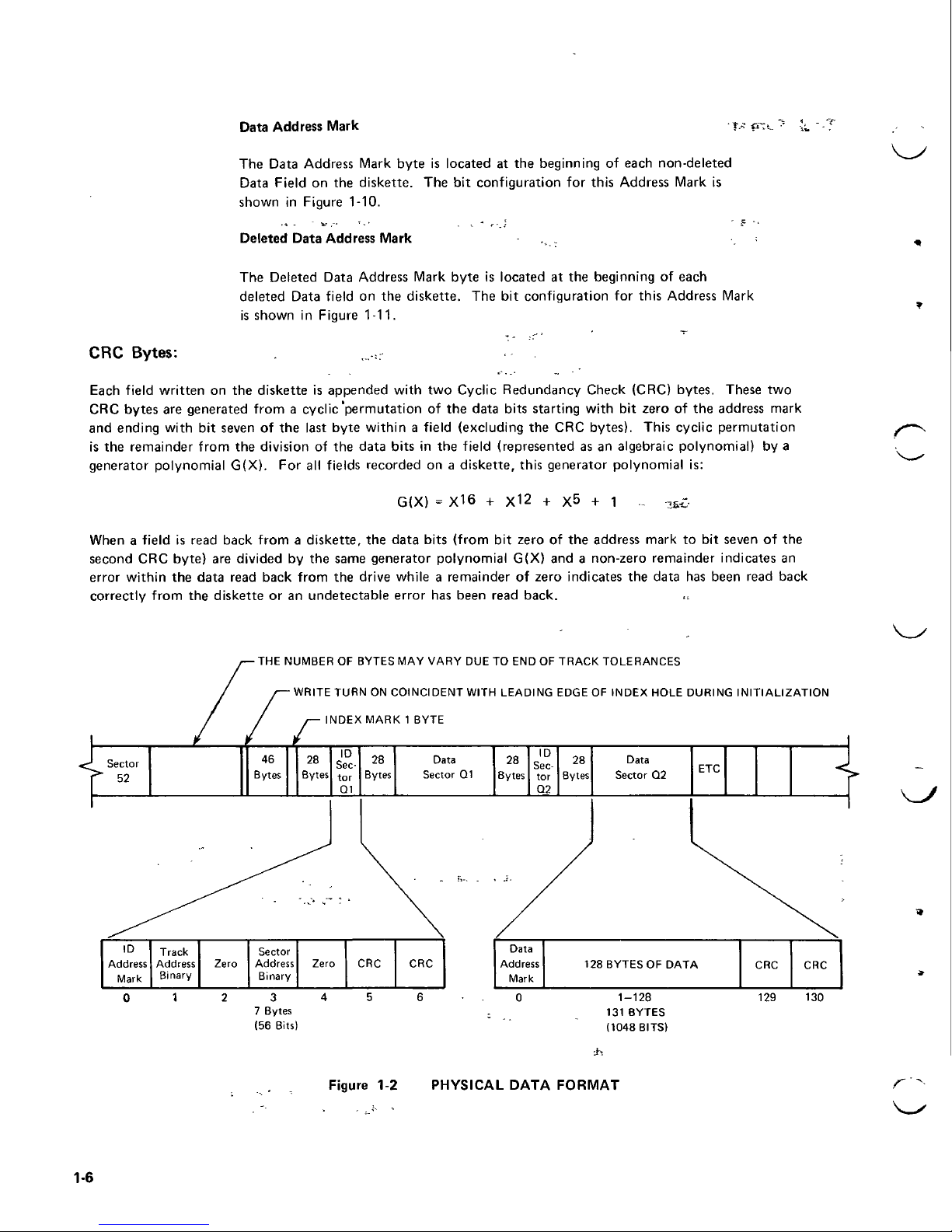

Figure

1-3

illustrates

the

relationship

of the

bits

within a byte

and

Figure

1-4

illustrates

the

relationship

of the

bytes

for

read

and

write

data.

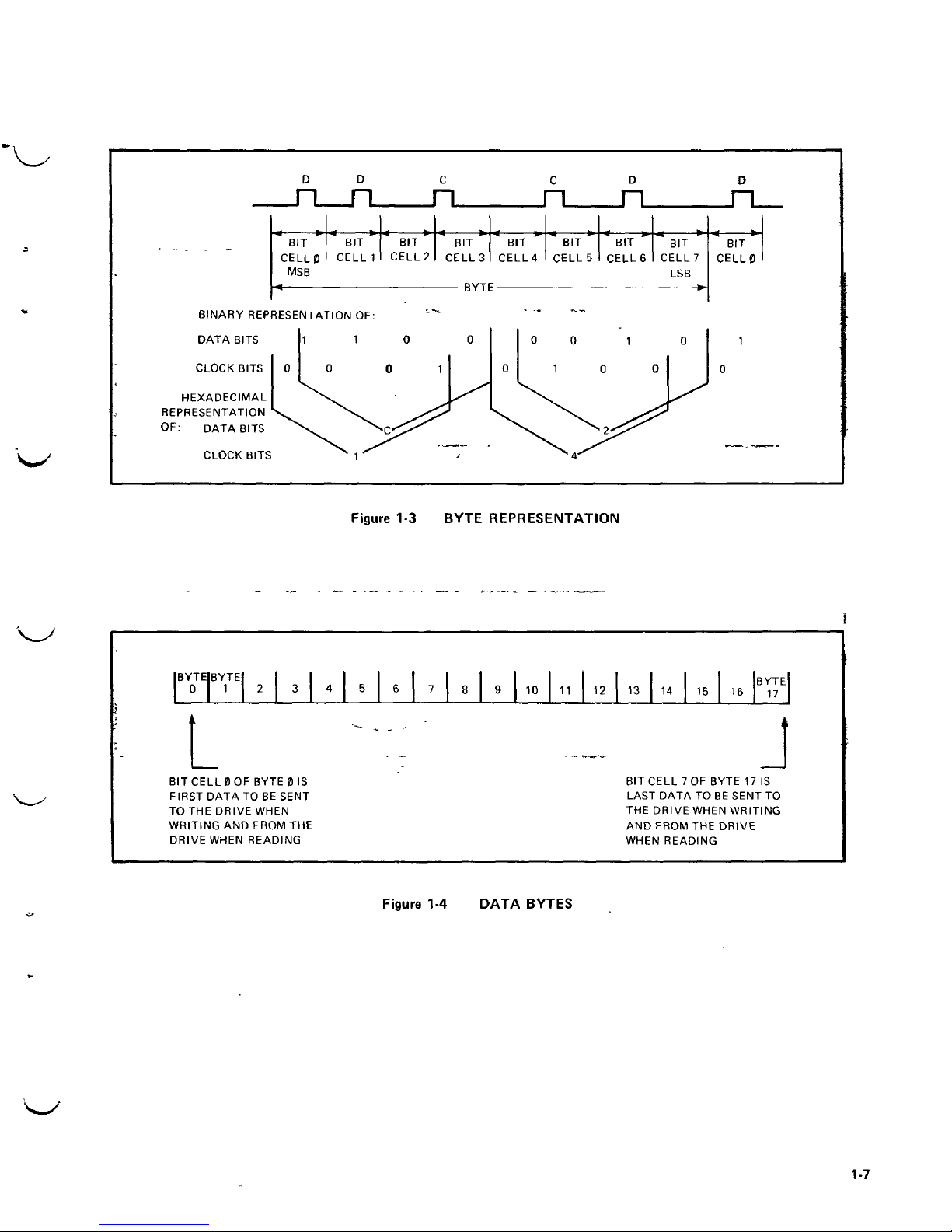

Data

is

recorded

on the

diskette using

modified

modified

(M^)

frequency

modulation

as the

recording mode. Data

written

on and

read back

from

the

disc takes

the

form

shown

in

Figure

1-5.

Clock bits

are

written

only

if

there

is

no

data

bit in the bit

cell

and

there

was no

data

bit or

clock

bit

written

in the

previous

bit

cell.

By

definition,

a

Bit

Cell

is the

period

(2 us)

consisting

of a

clock

bit

time

(1 us) and a

data

bit

time

(1

us). Figure

1-6

illustrates

a

Bit

Cell.

1-4

Page 13

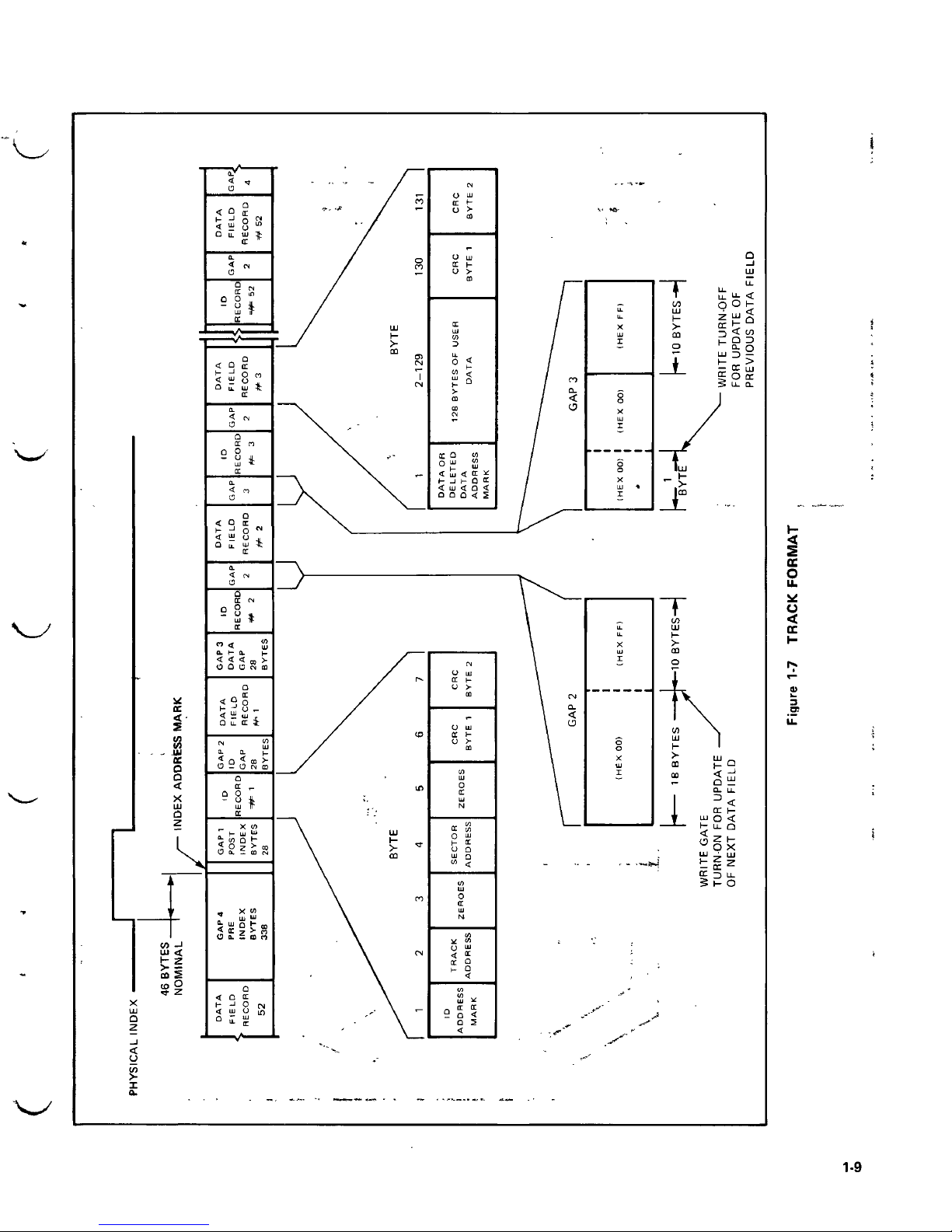

Track

Format:

>

•*' • •*••-»**«**

w3

Each

track recorded

on a

diskette consists

of 52

fixed length records along

with

necessary

gaps

for

record updating.

Figure

1-7

illustrates

the

format

of one

complete track.

Each

field

on a

track

is

separated

from adjacent

fields

by a

number

of

bytes containing

no

data.

These

areas

c

are

referred

to as

gaps

and are

provided

to

allow

the

updating

of one

field

without

affecting adjacent fields.

As

can be

seen

from

Figure 1-7, there

are

four

different types

of

gaps

on

each

track:

Gap 1 —

Post-Index

Gap

This

gap is

defined

as the 28

bytes

between Index

Address

Mark

and the ID

Address

Mark

for

Sector

one

(excluding

the

address

mark bytes). This

gap is

always

28

bytes

in

length

and is not

affected

by any

updating

process.

'

-r j/

Gap

2-ID

Gap

^..r

t

t

,

The 28

bytes between

the ID

Field

and the

Data Field

are

defined

as Gap 2

(ID

Gap). This

gap

does

not

vary

in

size.

Gap

3 -

Data

Gap

' - The 28

bytes between

the

Data

field

and the

next

ID

field

are

defined

as Gap

3

(Data Gap).

The

Data

Gap may

vary

slightly

in

length after

the

adjacent

Data

field

has

been updated,

due to

differences

in

disk rotational

speed

between

formatting

and

updating

of

individual

data

fields.

V / Gap 4 — Pre-lndex

Gap

The 338

bytes between

the

last

Data field

on a

track

and the

Index

Address

Mark

are

defined

as Gap 4

(Pre-lndex

Gap).

Initially,

this

gap is

nominally

338

bytes

in

length; however,

due to

write frequency

tolerances

and

diskette

speed

tolerances this

gap may

vary slightly

in

length.

Also,

after

the

data

field

of

record

52 has

been

updated this

gap may

again

change

slightly

in

length.

NS

---^

Address

Marks:

\

,

Address

Marks

are

unique

bit

patterns

one

byte

in

length which

are

used

to

identify

the

beginning

of ID and

Data

fields

and to

synchronize

the

deserializing

circuitry

with

the

first byte

of

each

field.

Address

Mark bytes

are

unique

from

all

other data bytes

in

that

each

Address

Mark contains

an

extra clock

bit in bit

cell

2.

There

are

four

different types

of

Address

Marks

used.

Each

of

these

is

used

to

identify

different types

of

fields:

%**

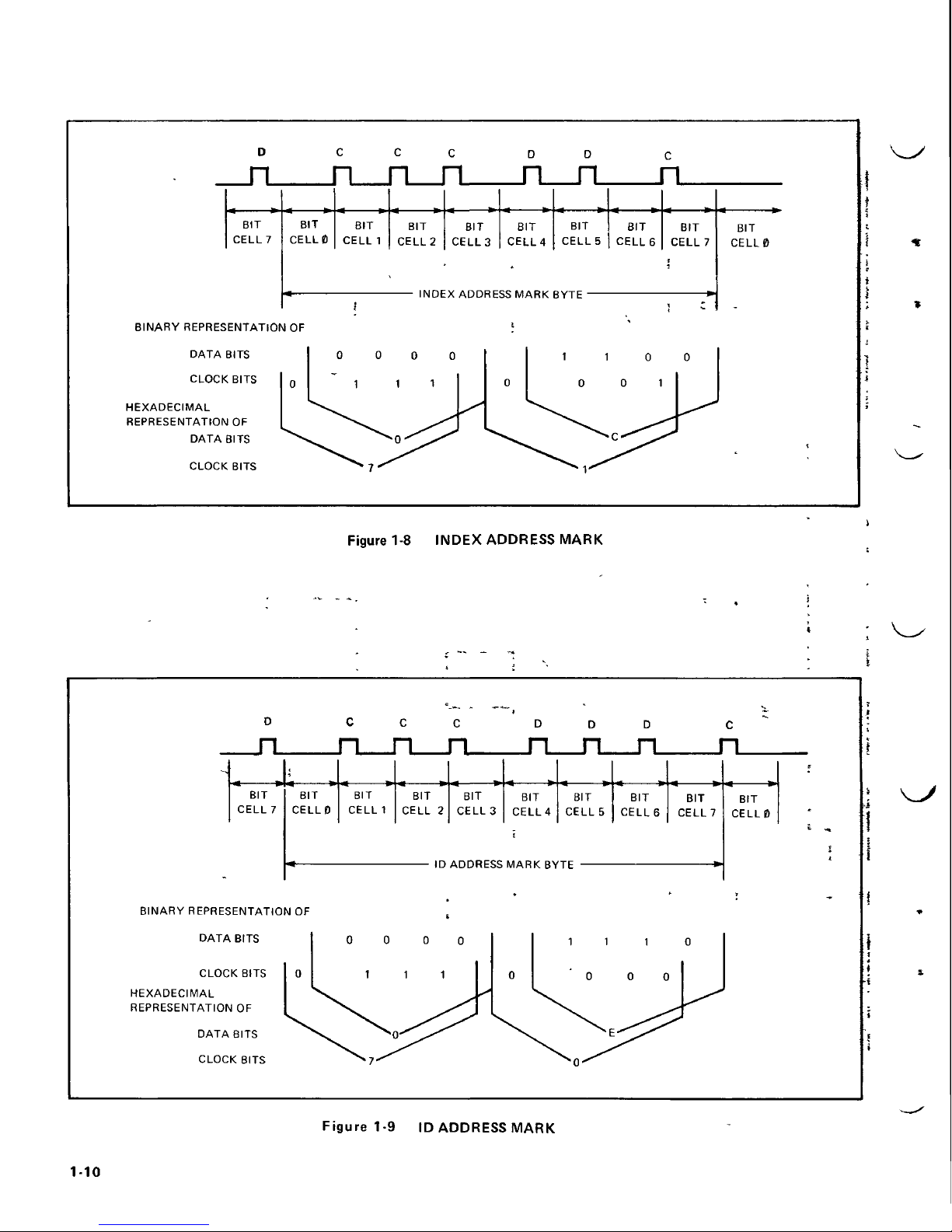

Index

Address

Mark

'r—"

>

i

;

The

Index Address Mark

is

located

at the

beginning

of

each track

and is a

fixed

number

of

bytes

in

front

of the

first record.

The bit

configuration

for the

Index

Address

Mark

is

shown

in

Figure 1-8.

ID

Address

Mark

The ID

Address

Mark byte

is

located

at the

beginning

of

each

ID

field

on the

diskette.

The bit

configuration

for

this

Address

Mark

is

shown

in

Figure 1-9.

1-5

Page 14

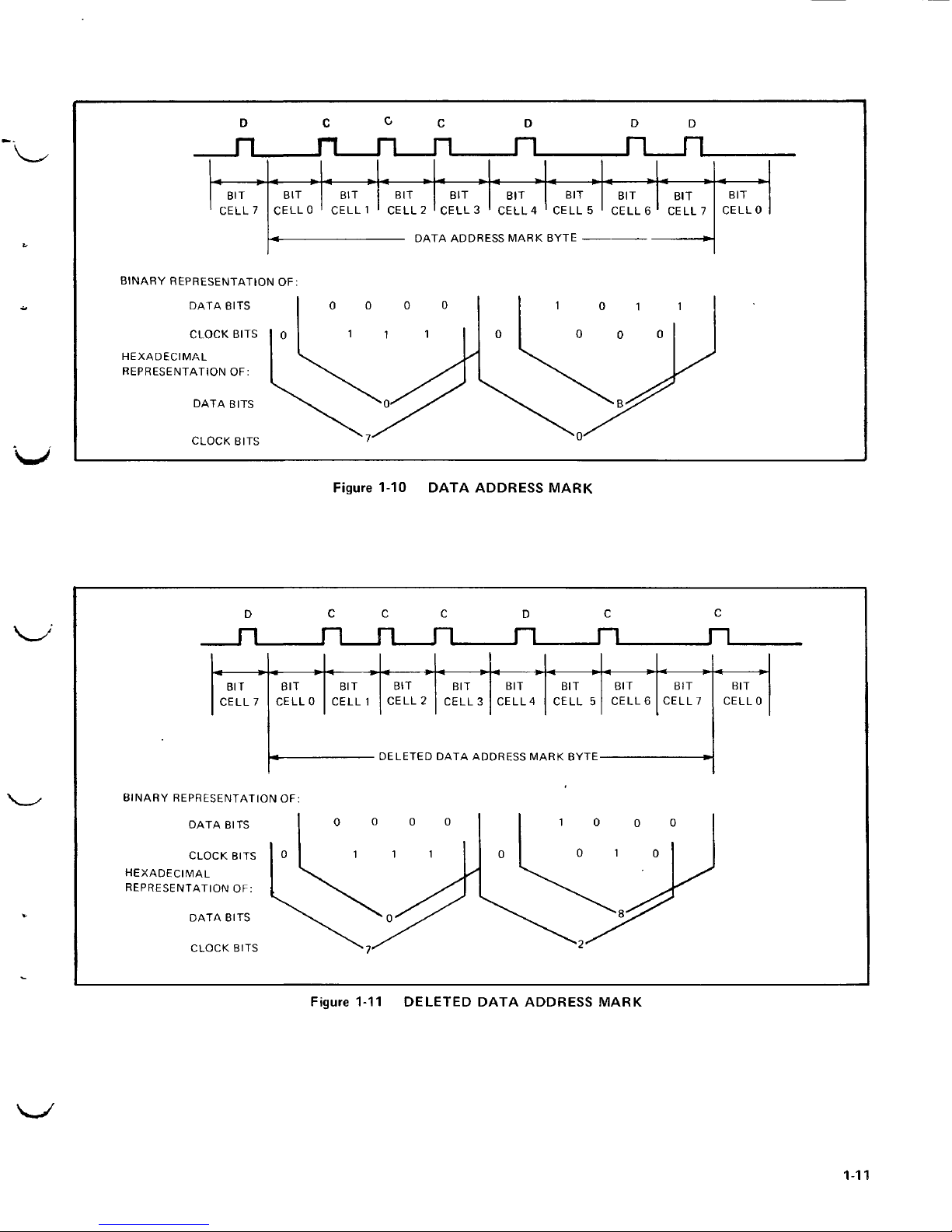

Data

Address

Mark

The

Data Address Mark byte

is

located

at the

beginning

of

each

non-deleted

Data

Field

on the

diskette.

The bit

configuration

for

this Address Mark

is

shown

in

Figure 1-10.

'•*

- ~ V

,-' *

" " •_ * r

-_

<

Deleted Data

Address

Mark

.

CRC

Bytes:

The

Deleted Data

Address

Mark byte

is

located

at the

beginning

of

each

deleted

Data field

on the

diskette.

The bit

configuration

for

this

Address

Mark

is

shown

in

Figure

1-11.

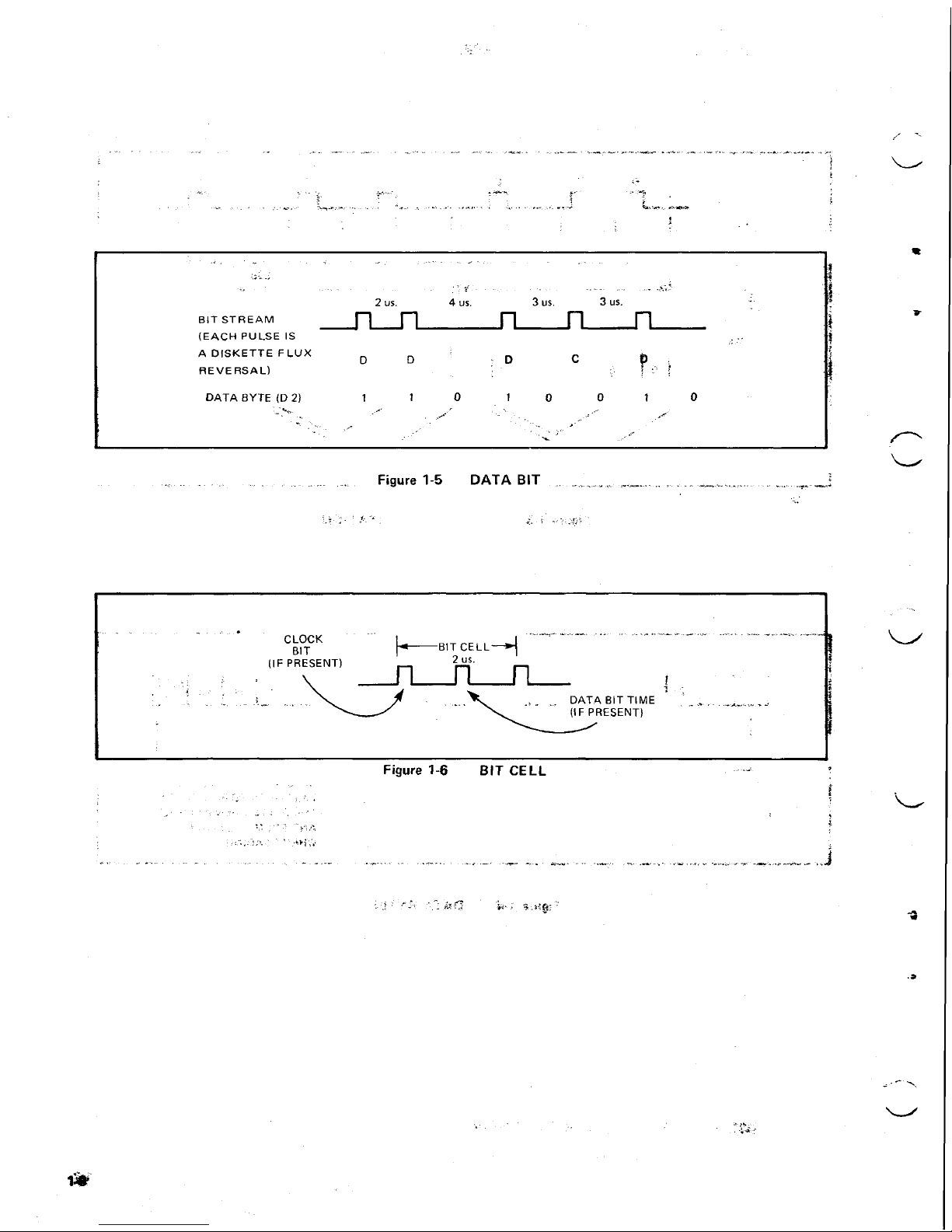

Each

field

written

on the

diskette

is

appended

with

two

Cyclic Redundancy Check (CRC) bytes.

These

two

CRC

bytes

are

generated

from a cyclic'permutation

of the

data bits starting

with

bit

zero

of the

address

mark

and

ending

with

bit

seven

of the

last

byte

within a field (excluding

the CRC

bytes). This cyclic permutation

is

the

remainder

from

the

division

of the

data bits

in the

field (represented

as an

algebraic

polynomial)

by a

generator

polynomial G(X).

For all

fields recorded

on a

diskette, this generator polynomial

is:

t~*

I

\y

\

\/1R

i

V 1

*?

i

V R

i

-1

—

b(X) - XID +

X1^ + X° + 1

75.x,-

When a field

is

read

back

from a diskette,

the

data

bits

(from

bit

zero

of the

address

mark

to bit

seven

of the

second

CRC

byte)

are

divided

by the

same

generator polynomial G(X)

and a

non-zero remainder indicates

an

error

within

the

data

read

back

from

the

drive while a remainder

of

zero indicates

the

data

has

been

read

back

correctly

from

the

diskette

or an

undetectable error

has

been

read

back.

THE

NUMBER

OF

BYTES

MAY

VARY

DUE TO END OF

TRACK TOLERANCES

/—

WRITE

TURN

ON

COINCIDENT

WITH

LEADING

EDGE

OF

INDEX HOLE

DURING

INITIALIZATION

/

'

Sector

r

*

/

/

IINUtA

MAKrx \ BY 1 t

/ /

46

Bytes

28

Bytes

ID

Sec-

tor

Q1

28

Bytes

Data

Sector

Q1

28

Bytes

ID

Sec-

tor

Q2

28

Bytes

Data

Sector

Q2

ETC

J

ID

Address

Mark

Track

Address

Binary

Zero

Sector

Address

Binary

Zero

CRC

CRC

0123456

7

Bytes

(56

Bits)

Data

Address

Mark

128

BYTES

OF

DATA

CRC

CRC

0

1-128

129 130

131

BYTES

(1048 BITS)

'f;

Figure

1-2

PHYSICAL

DATA

FORMAT

1-6

Page 15

c

n.

D

n

BIT

CELLO

MSB

BIT

CELL

1

BIT

CELL

2

BIT

CELLS

nw-rr

BIT

CELL4

BIT

CELL

5

BIT

CELL

6

BIT

CELL

7

LSB

BIT

CELLD

BINARY REPRESENTATION

OF:

DATA

BITS

CLOCK BITS

HEXADECIMAL

REPRESENTATION

OF:

DATA

BITS

CLOCK

BITS

Figure

1-3

BYTE REPRESENTATION

I

BYTE

0

BYTE

1

2

3

4

5

6

7

| 8

9

10

11

12

13

I 14

15

16

BYTE

17

BIT

CELL

OOF

BYTE

0 IS

FIRST

DATA

TO BE

SENT

TO

THE

DRIVE WHEN

WRITING

AND

FROM

THE

DRIVE

WHEN READING

BIT

CELL 7 OF

BYTE

17 IS

LAST DATA

TO BE

SENT

TO

THE

DRIVE WHEN WRITING

AND

FROM

THE

DRIVE

WHEN

READING

Figure

1-4

DATA

BYTES

1-7

Page 16

•.;:_^

2 us.

BITSTREAM

p~|

p~|

(EACH

PULSE

IS

A

DISKETTE FLUX

REVERSAL)

DATA

BYTE

(D 2) 1 1

..'*•'->

.-••'

""".'-•••.. , X

. - '

"

.. ^ -

4 us. 3 us. 3 us.

n

n n

D C D

010010

"

.,

.

-•

'

-•

V-,*'

Figure

1-5

DATA

BIT

CLOCK

BIT

(IF

PRESENT)

-BITCELL—*•]

2

us.

J1

TL

DATA

BIT

TIME

(IF

PRESENT)

Figure

1-6 BIT

CELL

1-8

Page 17

MARK

UI

cc

a

Q

X

01

Q

46

BYTES

NOMINAL

X

UJ

Q

a/

<

O

<

u

D

LL

UJ

a.

< N

O

< Q cc

t m °

^

-

U

Q

u.

UJ

I

<

O

D

OC

n

Q

0

- U JJ

a.

<

O

< Q

oc

K

-1 0

N

< * U

„

Q

u.

UJ

«

CC

Q.

<

O

Q

DC

Q

g

—

U

UJ

CC

"

<

a.

(-

a.

i-

< < <

oo

>

O

Q O Si a

a

u.

oc

o.

a.

(_

< Q <

a)

>

0 2 0 8

m

Q

oc

D

0

- u

UJ

CC

X CO

r

»-

uj uj

°:

(0 D

K

< O z >

en

0 tt. £

CD

S

<

1^ D V

«

< X -r

> n

(3

a. = m

n

Q

< Q

DC

1-

-J

O

<

uj

u

LU

I-

CQ

o

n

CM

CN

-

CN

O

ui

OC

H

(J

>-

CO

U

ui

CC

H

u

>

CO

cc

UJ

D

u.

°

*

H

°

m

CO

CN

CC

Q

</)

o

£

[S

< S <

cc

^

1-

-1

1-

Q CC

<

UJ

< Q <

Q

Q Q <

5

m

r-.

t£>

in

•"3-

„

CM

•-

CN

U

IU

CC

1-

u

>

m

CJ

UJ

CC

H-

u

>

CO

en

UJ

O

a.

N

rr

<"

CC

CO

O

ui

1-

CC

0 Q

UI

Q

<f>

<

en

UJ

O

cc

UI

N

^

en

ej

uj

tt

Q

L_

Q

en

UJ

*

9 S <

Q

2

X

UJ

I

O

o

o

o

X

UJ

X

cc

O

u.

*

O

<

oc

cu

>_

3

a;

O

oo

I

a.

1-9

Page 18

D

D

_n_

BIT

CELL?

BIT

CELLO

n

i

BIT

CELL

1

n

BIT

CELL2

\

•

i M nr

n

n n

BIT

CELLS

BIT

CELL4

».

.X

ADDRESS

MARK

BIT

CELL

5

BIT

CELL

6

n

BIT

CELL?

B T TE

^

BIT

CELLO

BINARY

REPRESENTATION

OF

DATA

BITS

CLOCK BITS

HEXADECIMAL

REPRESENTATION

OF

DATA

BITS

CLOCK BITS

0000

1100

Figure

1-8

INDEX

ADDRESS MARK

BIT

CELL?

-5

BIT

CELLO

BIT

CELL

1

BIT

CELL

2

BIT

CELL

3

A

rvrvD

ccc*

BIT

CELL4

BIT

CELL

5

BIT

CELL

6

BIT

CELL?

1 U AAL/LMll-OO

IVIMMIS.

L> 1 1

L.

^

BIT

CELLO

BINARY

REPRESENTATION

OF

DATA

BITS

CLOCK

BITS

HEXADECIMAL

REPRESENTATION

OF

DATA BITS

CLOCK

BITS

0000

1110

Figure

1-9 ID

ADDRESS

MARK

1-10

Page 19

D

D

D

_TL

BIT

CELL?

BIT

CELLO

n

i

BIT

CELL

1

BIT

CELL

2

rv

AH

n

n n n

BIT

CELLS

"A

ADORE

BIT

CELL4

SS

MARK

BIT

CELL

5

RYTE

BIT

CELL

6

BIT

CELL?

BIT

CELLO

BINARY

REPRESENTATION

OF

DATA BITS

CLOCK BITS

HEXADECIMAL

REPRESENTATION

OF:

DATA

BITS

CLOCK BITS

1011

Figure

1-10

DATA

ADDRESS

MARK

D

C C

n

TL

C

n

D

n

C

n

C

J~L

BIT

CELL

7

BIT

CELLO

BIT

CELL

1

—

BIT

CELL

2

BIT

CELL

3

BIT

CELL4

BIT

CELL

5

DELETED

DATA

ADDRESS

MARK BYTE-

BIT

CELL6

BIT

CELL?

BIT

CELLO

BINARY

REPRESENTATION

OF

DATA BITS

CLOCK BITS

HEXADECIMAL

REPRESENTATION

OF:

DATA BITS

CLOCK

BITS

1000

Figure

1-11

DELETED

DATA

ADDRESS

MARK

1-11

Page 20

LL-L

>iaviA!

ssaaoov

viva

0313130

LI-I

0 0 0

L

0000

sna

M3O13

sii9

viva

:

dO

NOIlVlN3S3Hd3y

1VIAII330VX3H

S1I9

X3013

sim

viva

dO

NOIlVlN3S3Hd3d

AHVNI9

01133

119

£ii33

119

91133

119

•31A9

XdVIAI

SS3HQaV

VIVO

031313C

9

H130

119

t-1130

119

€1130

119

2

1130

119

*•

L

1133

119

01133

119

^1130

119

LJ

3

LJ

0

LJ

a

LJ

3

U

LT

3 3

>iaVIAI

SS3HOOV

VIVO

OL-L

3jnB

!d

L

L 0 L

S1I9

»3O13

sim

viva

•dO

NOIlVlN3S3Hd3d

1VIAII330VX3H

S1I9

>I3013

siig

viva

dO

NOIlVlN3S3dd3y

AHVNI9

01133

119

Z.1133

119

91133

119

n_i-Aa

9

1133

119

»HVIAISS'

1^1133

119

gaaav

vj

£

1133

119

LJ

U U U

21130

118

I

1133

119

LJ

01133

119

Z.1133

119

U

a

a

a

Page 21

CHAPTER

2

OPERATIONAL

SUMMARY

AND

PROGRAMMING

CONSIDERATIONS

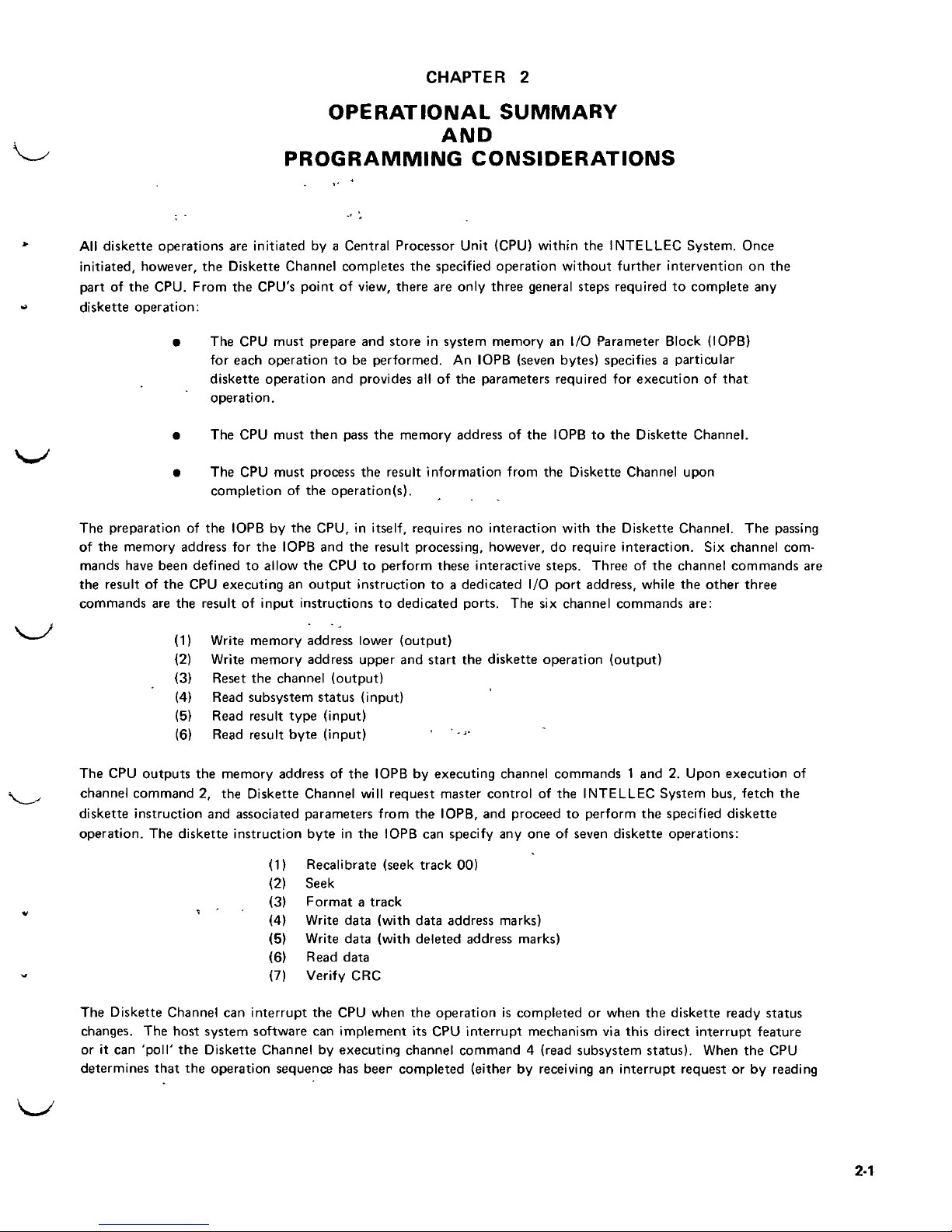

All

diskette operations

are

initiated

by a

Central

Processor

Unit

(CPU)

within

the

INTELLEC

System. Once

initiated,

however,

the

Diskette Channel completes

the

specified operation

without

further

intervention

on the

part

of the

CPU. From

the

CPU's

point

of

view, there

are

only

three general

steps

required

to

complete

any

diskette operation:

• The CPU

must prepare

and

store

in

system memory

an I/O

Parameter Block (IOPB)

for

each

operation

to be

performed.

An

IOPB

(seven

bytes)

specifies a particular

diskette operation

and

provides

all of the

parameters required

for

execution

of

that

operation.

• The CPU

must

then

pass

the

memory

address

of the

IOPB

to the

Diskette Channel.

• The CPU

must

process

the

result

information

from

the

Diskette Channel

upon

completion

of the

operation(s).

The

preparation

of the

IOPB

by the

CPU,

in

itself, requires

no

interaction

with

the

Diskette Channel.

The

passing

of the

memory

address

for the

IOPB

and the

result processing, however,

do

require interaction.

Six

channel com-

mands

have

been defined

to

allow

the CPU to

perform these interactive

steps.

Three

of the

channel commands

are

the

result

of the CPU

executing

an

output

instruction

to a

dedicated

I/O

port

address,

while

the

other three

commands

are the

result

of

input

instructions

to

dedicated ports.

The six

channel commands are:

(1)

Write memory

address

lower

(output)

(2)

Write memory

address

upper

and

start

the

diskette operation

(output)

(3)

Reset

the

channel

(output)

(4)

Read

subsystem status

(input)

(5)

Read

result

type

(input)

(6)

Read

result

byte

(input)

••-->•

The CPU

outputs

the

memory

address

of the

IOPB

by

executing channel commands

1 and 2.

Upon

execution

of

channel command

2, the

Diskette Channel

will

request master

control

of the

INTELLEC System bus, fetch

the

diskette

instruction

and

associated

parameters

from

the

IOPB,

and

proceed

to

perform

the

specified diskette

operation.

The

diskette

instruction

byte

in the

IOPB

can

specify

any one of

seven

diskette operations:

(1)

Recalibrate

(seek

track

00)

(2)

Seek

(3)

Format a track

(4)

Write data

(with

data

address

marks)

(5)

Write data

(with

deleted

address

marks)

(6)

Read

data

(7)

Verify

CRC

The

Diskette Channel

can

interrupt

the CPU

when

the

operation

is

completed

or

when

the

diskette ready status

changes.

The

host

system software

can

implement

its CPU

interrupt

mechanism

via

this

direct

interrupt

feature

or it can

'poll'

the

Diskette Channel

by

executing channel command 4 (read

subsystem status). When

the CPU

determines

that

the

operation sequence

has

beer completed (either

by

receiving

an

interrupt

request

or by

reading

2-1

Page 22

FORMAT

TRACK

"

:•*-.--

K- - -

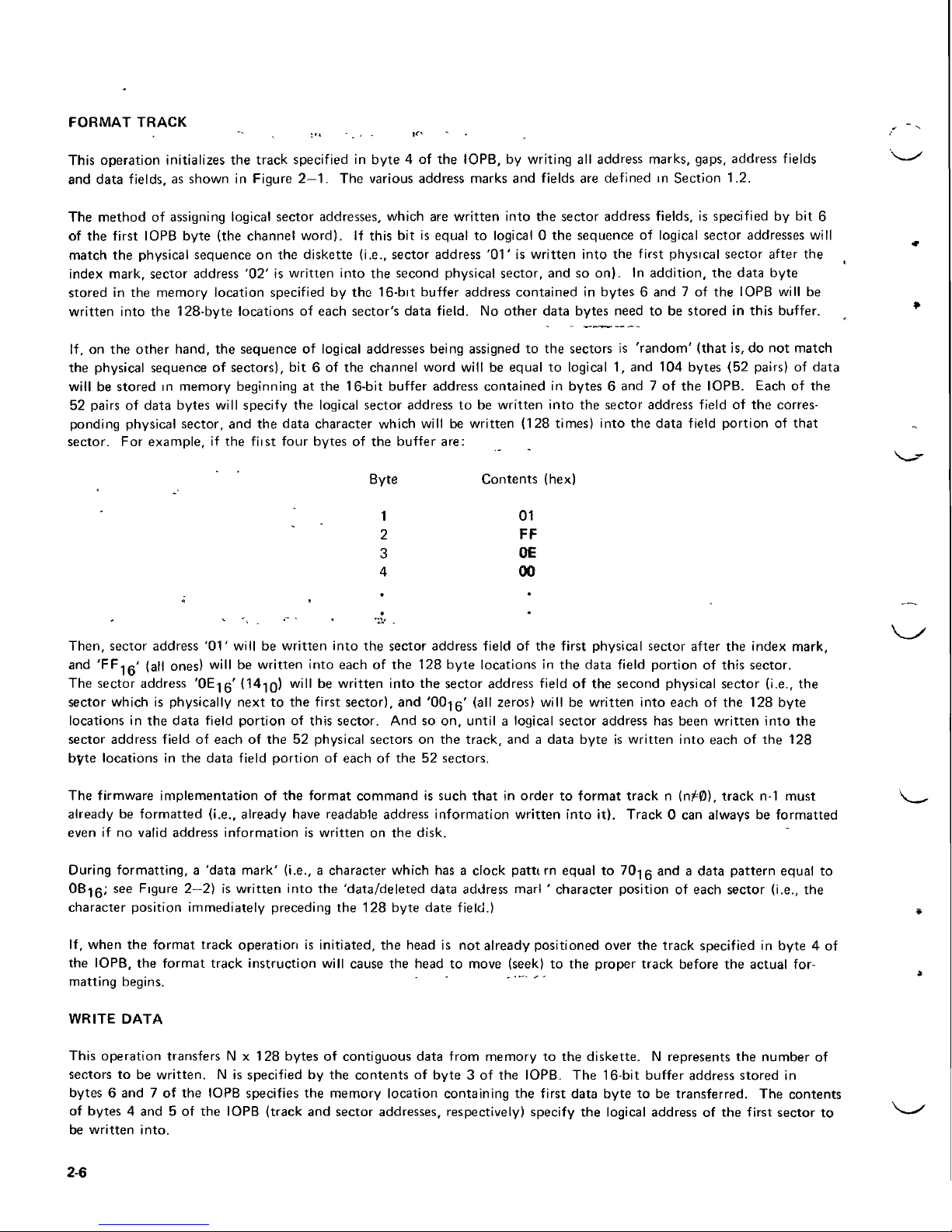

This

operation initializes

the

track

specified

in

byte

4 of the

IOPB,

by

writing

all

address

marks,

gaps,

address

fields

and

data fields,

as

shown

in

Figure

2—1.

The

various address marks

and

fields

are

defined

in

Section 1.2.

The

method

of

assigning logical sector

addresses,

which

are

written

into

the

sector

address

fields,

is

specified

by bit 6

of the

first IOPB

byte

(the channel word).

If

this

bit is

equal

to

logical

0 the

sequence

of

logical sector

addresses

will

match

the

physical sequence

on the

diskette (i.e., sector

address

'01'

is

written

into

the

first physical sector after

the

index

mark,

sector

address

'02'

is

written

into

the

second physical sector,

and so

on).

In

addition,

the

data

byte

stored

in the

memory location specified

by the

16-bit

buffer

address

contained

in

bytes

6 and 7 of the

IOPB

will

be

written

into

the

128-byte

locations

of

each sector's data

field.

No

other

data bytes need

to be

stored

in

this

buffer.

If, on the

other

hand,

the

sequence

of

logical

addresses

being

assigned

to the

sectors

is

'random'

(that

is, do not

match

the

physical sequence

of

sectors),

bit 6 of the

channel

word

will

be

equal

to

logical

1, and 104

bytes

(52

pairs)

of

data

will

be

stored

in

memory beginning

at the

16-bit

buffer

address contained

in

bytes

6 and 7 of the

IOPB. Each

of the

52

pairs

of

data bytes

will

specify

the

logical sector

address

to be

written

into

the

sector

address

field

of the

corres-

ponding

physical sector,

and the

data character

which

will

be

written

(128 times)

into

the

data

field

portion

of

that

sector.

For

example,

if the

fiist

four

bytes

of the

buffer are:

Byte Contents (hex)

1

01

2

FF

3

oe

4

00

Then,

sector

address

'01'

will

be

written

into

the

sector address

field

of the

first

physical sector after

the

index

mark,

and

'FF-jg'

(all ones)

will

be

written

into

each

of the 128

byte

locations

in the

data field

portion

of

this sector.

The

sector

address

'OE-jg'

(14-^Q)

W|

'H

be

written

into

the

sector

address

field

of the

second physical sector (i.e.,

the

sector

which

is

physically next

to the

first

sector),

and

'00-|g'

(all

zeros)

will

be

written

into

each

of the 128

byte

locations

in the

data

field

portion

of

this sector.

And so on,

until a logical sector

address

has

been

written

into

the

sector

address

field

of

each

of the 52

physical

sectors

on the

track,

and a

data byte

is

written

into

each

of the 128

byte

locations

in the

data field

portion

of

each

of the 52

sectors.

The

firmware

implementation

of the

format

command

is

such

that

in

order

to

format

track n (n^0),

track

n-1

must

already

be

formatted (i.e., already

have

readable

address

information

written

into

it). Track

0 can

always

be

formatted

even

if no

valid

address

information

is

written

on the

disk.

During

formatting, a 'data

mark'

(i.e., a character

which

has a

clock

pattern

equal

to

70-|g

and a

data

pattern

equal

to

OB-|g;

see

Figure

2—2)

is

written

into

the

'data/deleted

data

address

marl ' character

position

of

each sector (i.e.,

the

character

position immediately preceding

the 128

byte

date field.)

If,

when

the

format

track operation

is

initiated,

the

head

is not

already positioned over

the

track specified

in

byte

4 of

the

IOPB,

the

format

track

instruction

will

cause

the

head

to

move

(seek)

to the

proper

track

before

the

actual for-

matting

begins.

"

"

"

WRITE

DATA

This operation transfers

N x 1 28

bytes

of

contiguous data

from

memory

to the

diskette. N represents

the

number

of

sectors

to be

written.

N is

specified

by the

contents

of

byte

3 of the

IOPB.

The

16-bit

buffer

address

stored

in

bytes

6 and 7 of the

IOPB specifies

the

memory

location

containing

the

first data

byte

to be

transferred.

The

contents

of

bytes

4 and 5 of the

IOPB (track

and

sector

addresses,

respectively) specify

the

logical address

of the

first

sector

to

be

written

into.

2-6

Page 23

executed

sequentially

('read

result

type'

first),

and

should

be

executed

only

in

response

to an

interrupt

request

from

the

Diskette Channel; execution

at

other times could produce erroneous result data.

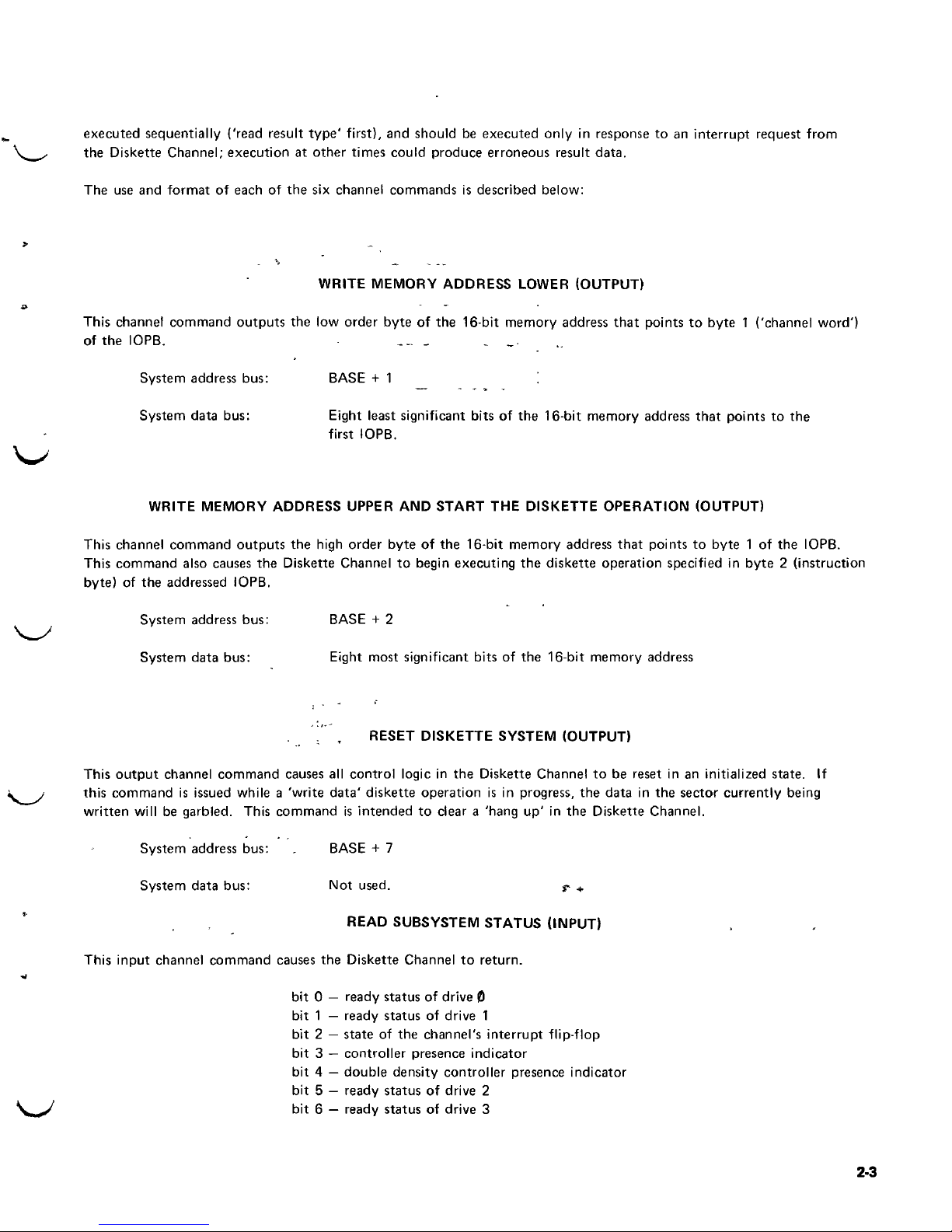

The use and

format

of

each

of the six

channel commands

is

described below:

WRITE

MEMORY

ADDRESS LOWER

(OUTPUT)

-

- .

This channel command

outputs

the low

order

byte

of the

16-bit

memory

address

that

points

to

byte 1 ('channel

word')

of

the

IOPB.

,.. _ _

_.

System

address

bus: BASE

+ 1

\

System data bus: Eight

least

significant

bits

of the

16-bit

memory

address

that

points

to the

first

IOPB.

WRITE

MEMORY

ADDRESS UPPER

AND

START

THE

DISKETTE

OPERATION

(OUTPUT)

This channel command

outputs

the

high order

byte

of the

16-bit

memory

address

that

points

to

byte

1 of the

IOPB.

This command

also

causes

the

Diskette Channel

to

begin executing

the

diskette operation specified

in

byte 2 (instruction

byte)

of the

addressed

IOPB.

System

address

bus: BASE

+ 2

System data bus: Eight most significant bits

of the

16-bit

memory

address

.

.

,

RESET

DISKETTE

SYSTEM

(OUTPUT)

This

output

channel command

causes

all

control

logic

in the

Diskette Channel

to be

reset

in an

initialized state.

If

this command

is

issued

while a 'write

data'

diskette operation

is in

progress,

the

data

in the

sector

currently

being

written

will

be

garbled. This command

is

intended

to

clear a 'hang

up'

in the

Diskette Channel.

System

address

bus: , BASE

+ 7

System

data bus:

Not

used.

$•

+

READ

SUBSYSTEM

STATUS

(INPUT)

This

input

channel command

causes

the

Diskette Channel

to

return.

bit

0 -

ready status

of

drive

0

bit 1 —

ready

status

of

drive

1

bit 2 —

state

of the

channel's

interrupt

flip-flop

bit 3 —

controller

presence

indicator

bit 4 —

double density controller

presence

indicator

bit 5 —

ready status

of

drive

2

bit 6 —

ready status

of

drive

3

2-3

Page 24

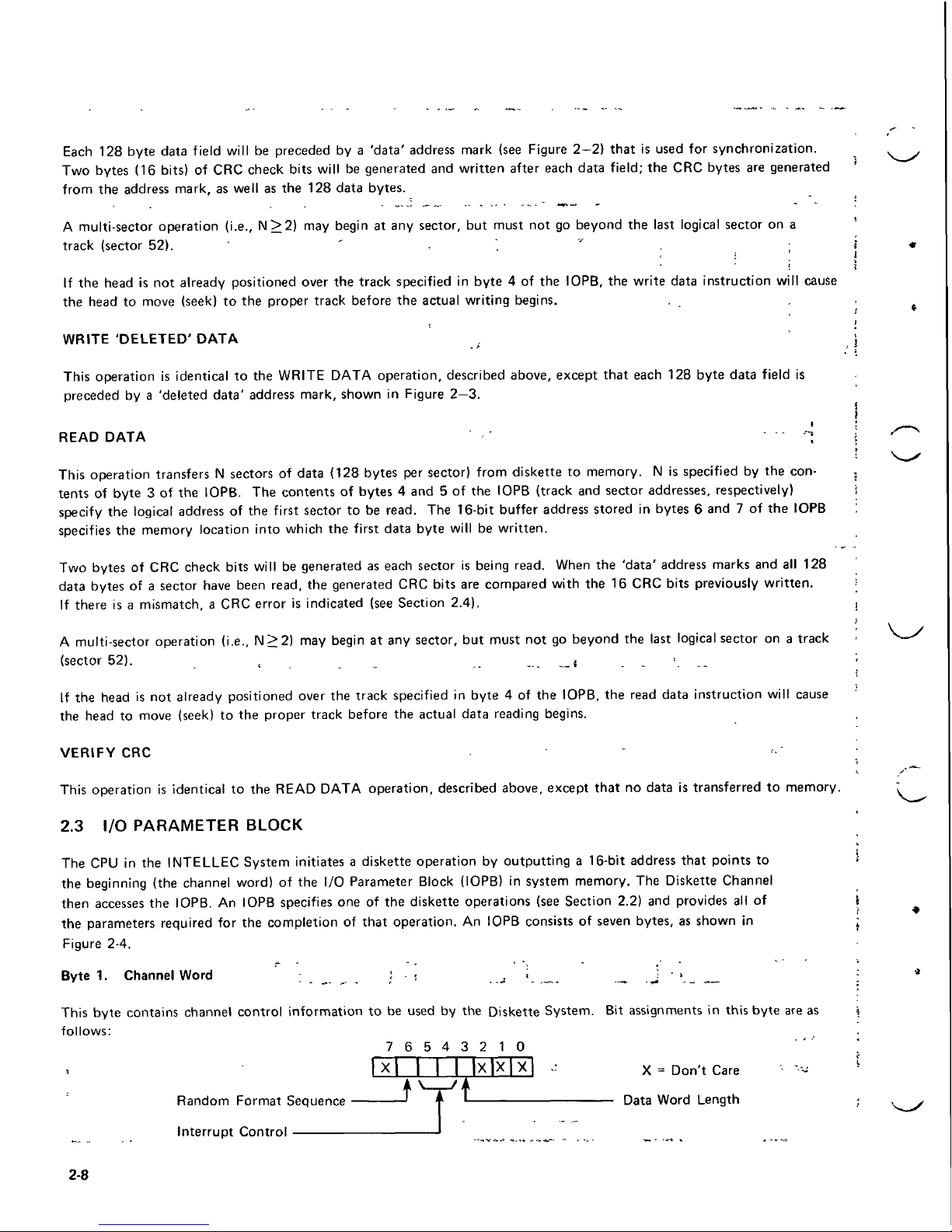

Each

128

byte data field

will

be

preceded

by a

'data'

address

mark (see Figure 2-2)

that

is

used

for

synchronization.

^^

Two

bytes

(16

bits)

of CRC

check bits

will

be

generated

and

written

after each data

field;

the CRC

bytes

are

generated

from

the

address

mark,

as

well

as the 128

data bytes.

A

multi-sector operation (i.e.,

N>2)

may

begin

at any

sector,

but

must

not go

beyond

the

last logical sector

on a

track (sector 52).

"

"

. ;

I

«

1

1

If the

head

is not

already

positioned

over

the

track

specified

in

byte

4 of the

IOPB,

the

write

data

instruction

will

cause

the

head

to

move

(seek)

to the

proper track before

the

actual

writing

begins.

. ,

/

*

}

WRITE

'DELETED'DATA

i

.

j-

/

5

This operation

is

identical

to the

WRITE

DATA

operation, described above, except

that

each

128

byte

data

field

is

preceded

by a

'deleted

data'

address

mark,

shown

in

Figure

2—3.

.

a

_^

READ

DATA

1

j

^^

This operation

transfers N sectors

of

data (128 bytes

per

sector)

from

diskette

to

memory.

N is

specified

by the

con-

?

tents

of

byte

3 of the

IOPB.

The

contents

of

bytes

4 and 5 of the

IOPB

(track

and

sector addresses, respectively)

j

specify

the

logical

address

of the

first

sector

to be

read.

The

16-bit

buffer

address

stored

in

bytes

6 and 7 of the

IOPB

:

specifies

the

memory location

into

which

the

first data

byte

will

be

written.

Two

bytes

of CRC

check bits

will

be

generated

as

each

sector

is

being read. When

the

'data'

address

marks

and all 128

data bytes

of a

sector

have

been read,

the

generated

CRC

bits

are

compared

with

the 16 CRC

bits

previously

written.

;

If

there

is a

mismatch,

a CRC

error

is

indicated (see Section 2.4).

s

A

multi-sector operation (i.e.,

N>2)

may

begin

at any

sector,

but

must

not go

beyond

the

last logical sector

on a

track

-

—

(sector

52).

(

_

{

_.'._.

If the

head

is not

already

positioned

over

the

track specified

in

byte

4 of the

IOPB,

the

read

data

instruction

will

cause

the

head

to

move

(seek)

to the

proper track before

the

actual data reading begins.

VERIFY

CRC

This operation

is

identical

to the

READ

DATA

operation,

described above, except

that

no

data

is

transferred

to

memory.

:

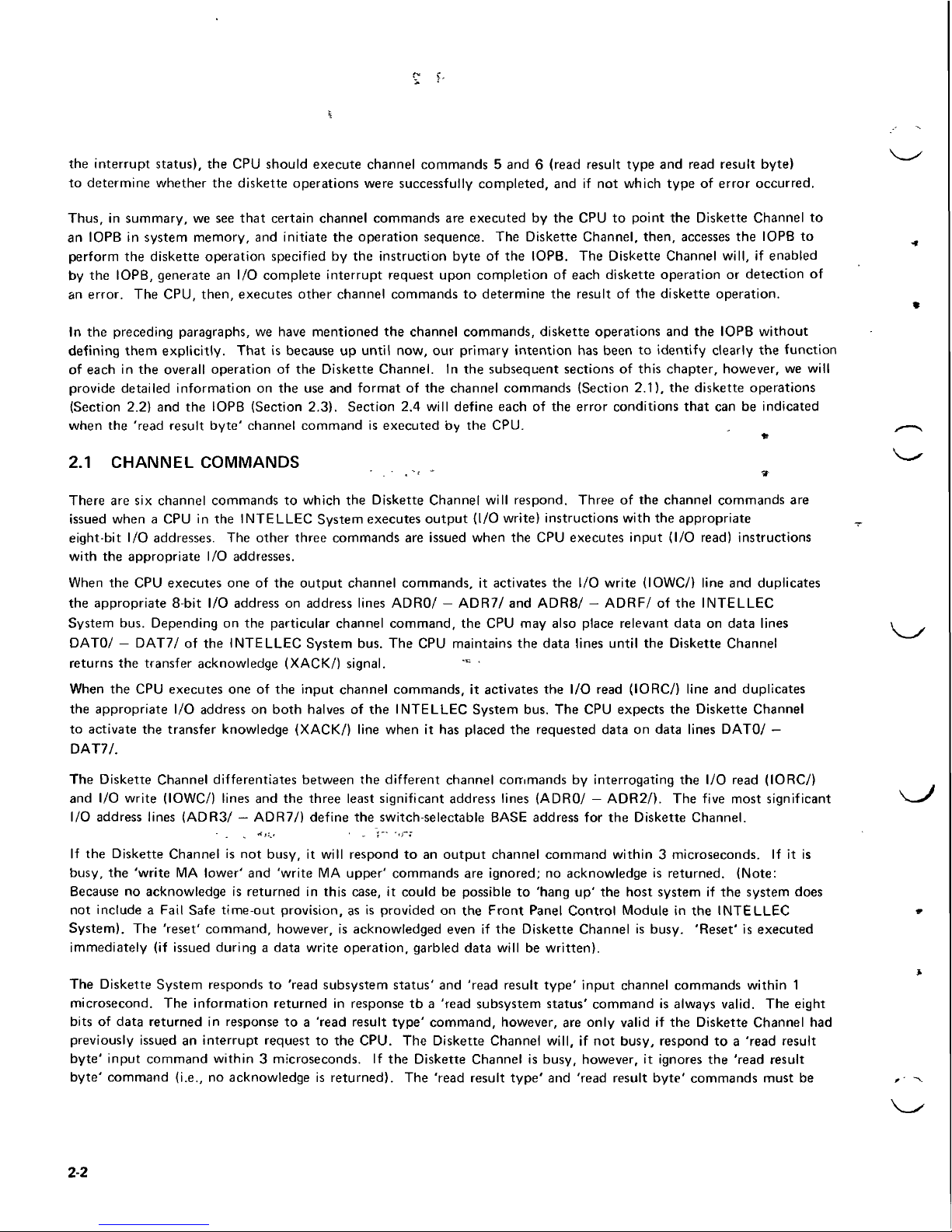

2.3 I/O

PARAMETER

BLOCK

The CPU in the

INTELLEC

System initiates a diskette

operation

by

outputting a 16-bit

address

that

points

to *

the

beginning (the channel word)

of the I/O

Parameter

Block (IOPB)

in

system

memory.

The

Diskette Channel

then

accesses

the

IOPB.

An

IOPB

specifies

one of the

diskette operations (see Section 2.2)

and

provides

all of I

^

the

parameters required

for the

completion

of

that

operation.

An

IOPB consists

of

seven

bytes,

as

shown

in

;

Figure

2-4.

Byte

1.

Channel Word

\

-

*,

^

<

_

J

'»____

;

*

This

byte

contains channel

control

information

to be

used

by the

Diskette

System.

Bit

assignments

in

this

byte

are as

\

follows:

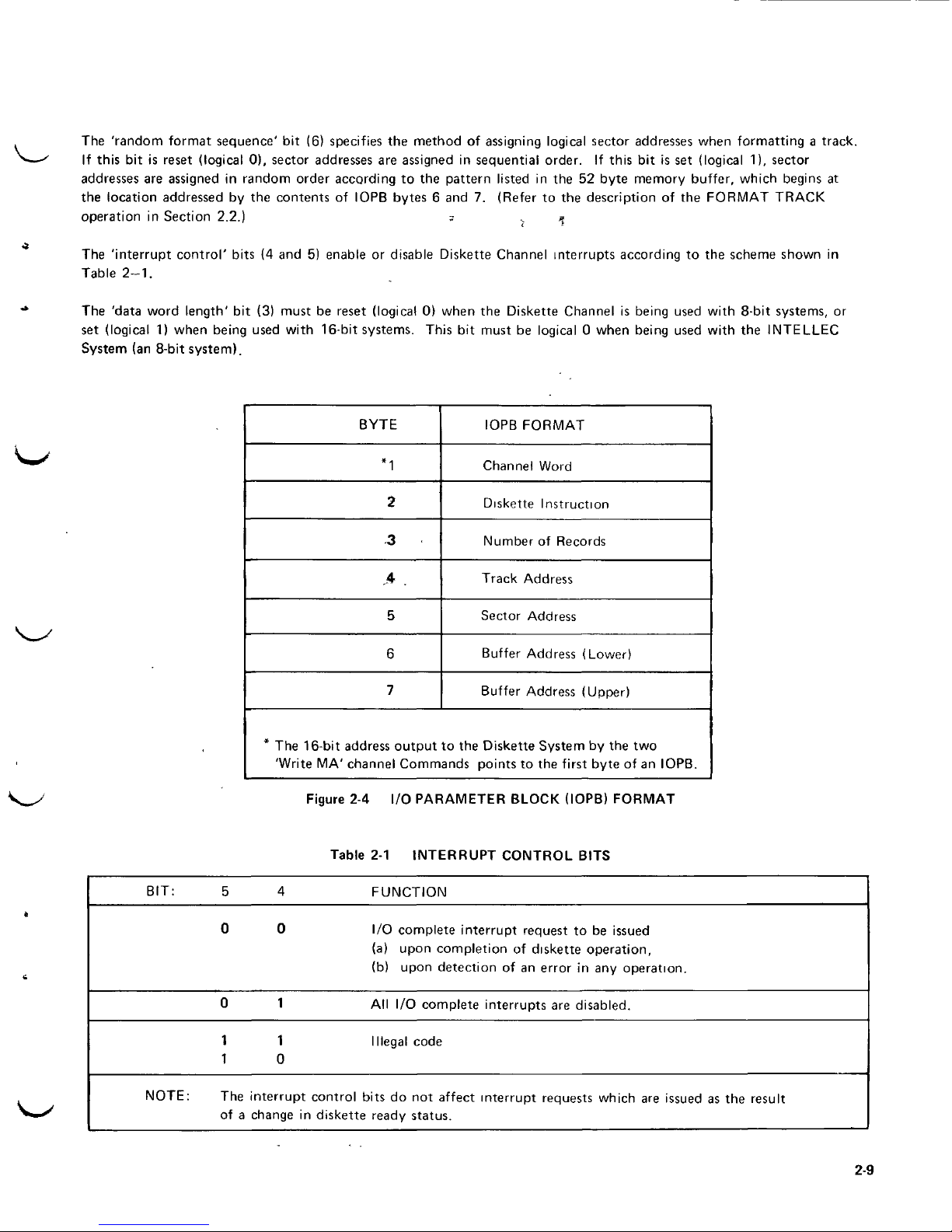

76543210

|X|

| | |

|X|X|X|

.:

x

=

Don't

Care

Random Format Sequence

Interrupt

Control

2-8

Data Word

Length

Page 25

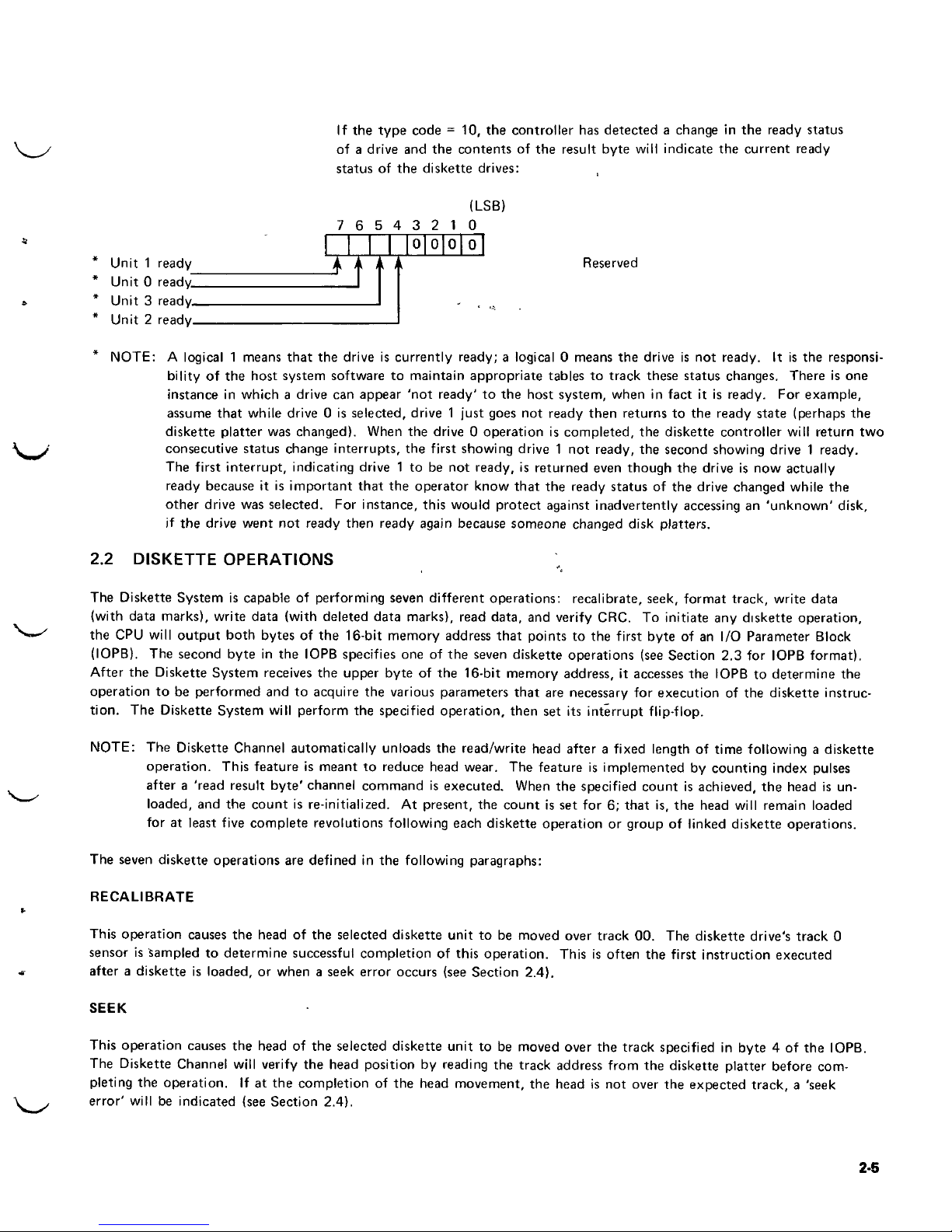

If the

type

code

= 10, the

controller

has

detected a change

in the

ready status

of a

drive

and the

contents

of the

result byte

will

indicate

the

current ready

status

of the

diskette

drives:

(LSB)

76543210

Unit 1 ready

T

t( A a Reserved

Unit 0 ready

Unit 3 ready

Unit 2 ready

0

0

o[o

*

NOTE: A logical 1 means

that

the

drive

is

currently ready; a logical 0 means

the

drive

is not

ready.

It is the

responsi-

bility

of the

host system software

to

maintain appropriate tables

to

track

these

status

changes.

There

is one

instance

in

which a drive

can

appear

'not

ready'

to the

host

system,

when

in

fact

it is

ready.

For

example,

assume

that

while

drive

0 is

selected, drive 1 just

goes

not

ready then returns

to the

ready state

(perhaps

the

diskette platter

was

changed).

When

the

drive 0 operation

is

completed,

the

diskette controller

will

return

two

V J consecutive status change interrupts,

the

first

showing drive

1 not

ready,

the

second showing drive 1 ready.

The

first

interrupt,

indicating drive

1 to be not

ready,

is

returned

even

though

the

drive

is now

actually

ready

because

it is

important

that

the

operator

know

that

the

ready status

of the

drive changed while

the

other drive

was

selected.

For

instance, this

would

protect

against

inadvertently

accessing

an

'unknown'

disk,

if the

drive

went

not

ready

then

ready again because someone changed disk platters.

2.2

DISKETTE OPERATIONS

The

Diskette System

is

capable

of

performing

seven

different operations: recalibrate,

seek,

format track, write data

(with

data marks), write data

(with

deleted data marks), read data,

and

verify CRC.

To

initiate

any

diskette operation,

^—-'

the CPU

will

output

both

bytes

of the

16-bit

memory

address

that

points

to the

first byte

of an I/O

Parameter

Block

(IOPB).

The

second byte

in the

IOPB

specifies

one of the

seven

diskette operations (see Section

2.3 for

IOPB format).

After

the

Diskette System

receives

the

upper byte

of the

16-bit memory

address,

it

accesses

the

IOPB

to

determine

the

operation

to be

performed

and to

acquire

the

various

parameters

that

are

necessary

for

execution

of the

diskette instruc-

tion.

The

Diskette System

will

perform

the

specified operation, then

set its

interrupt

flip-flop.

NOTE:

The

Diskette Channel automatically unloads

the

read/write head after a fixed length

of

time

following a diskette

operation. This feature

is

meant

to

reduce head wear.

The

feature

is

implemented

by

counting

index

pulses

after a 'read

result

byte'

channel command

is

executed. When

the

specified

count

is

achieved,

the

head

is un-

loaded,

and the

count

is

re-initialized.

At

present,

the

count

is set for 6;

that

is, the

head

will

remain loaded

for at

least

five complete revolutions following

each

diskette operation

or

group

of

linked diskette operations.

The

seven

diskette operations

are

defined

in the

following paragraphs:

RECALIBRATE

?-

This operation

causes

the

head

of the

selected

diskette

unit

to be

moved over track

00. The

diskette drive's track

0

sensor

is

sampled

to

determine

successful

completion

of

this operation. This

is

often

the

first

instruction

executed

*

after a diskette

is

loaded,

or

when a seek

error occurs (see Section 2.4).

SEEK

This operation

causes

the

head

of the

selected

diskette

unit

to be

moved over

the

track specified

in

byte

4 of the

IOPB.

The

Diskette Channel

will

verify

the

head

position

by

reading

the

track

address

from

the

diskette platter before com-

pleting

the

operation.

If at the

completion

of the

head movement,

the

head

is not

over

the

expected track, a 'seek

\.

error'

will

be

indicated (see Section 2.4).

2-5

Page 26

cperations.

hese

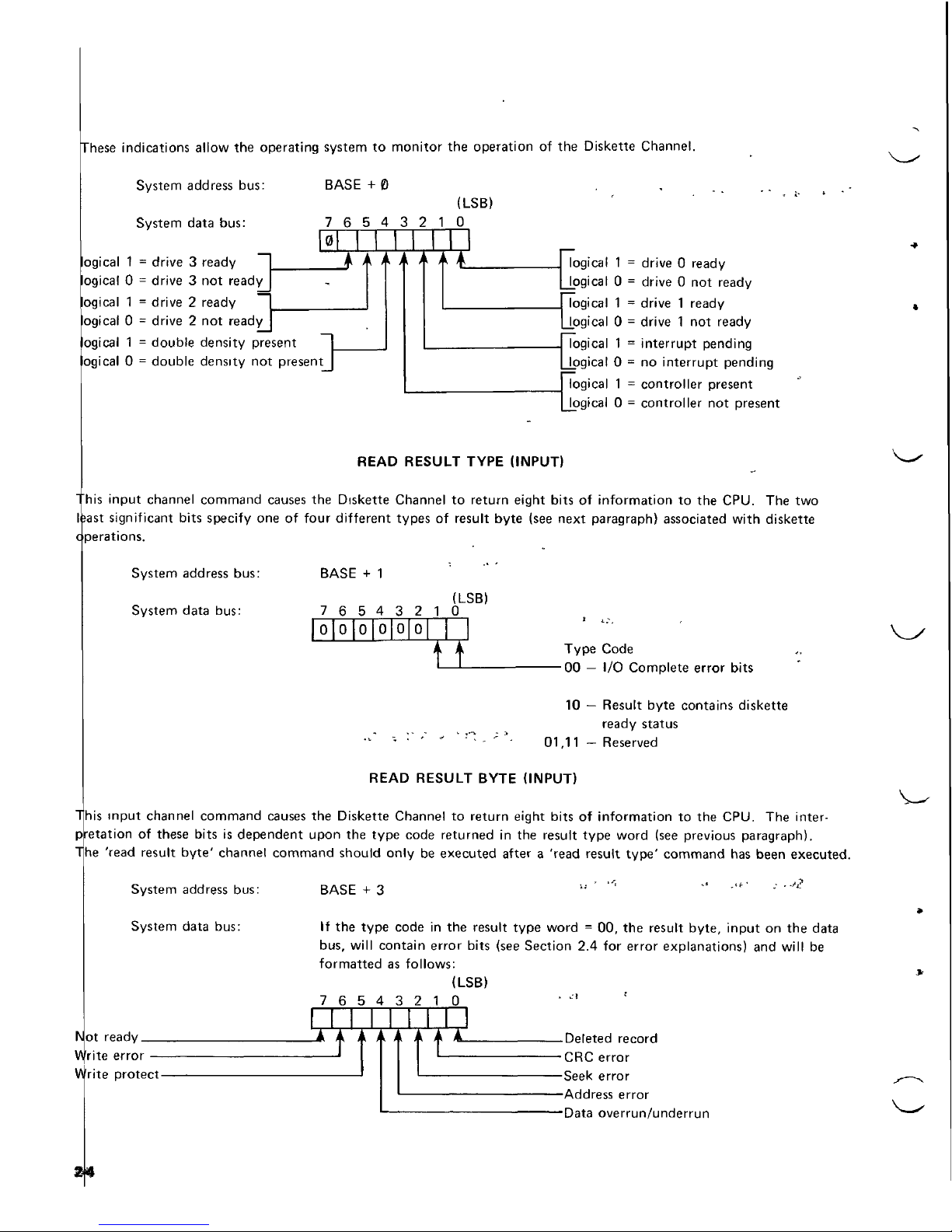

indications allow

the

operating system

to

monitor

the

operation

of the

Diskette Channel.

System

address

bus: BASE

+ 0

System data bus:

ogical

1 =

drive 3 ready

ogical

0 =

drive

3 not

ready

ogical

1 =

drive 2 ready

ogical

0 =

drive

2 not

ready

ogical

1 =

double

density present

ogical

0 =

double density

not

present

sent

t

presen

7

0

-

n

J

6

I

c

>

k

4

>

t

k

/•

>

J

k.

f

>

(LSB)

!

1 0

I

I

k A >f

logical

1 =

drive 0 ready

Jpgical

0 =

drive

0 not

ready

logical

1 =

drive 1 ready

Jpgical

0 =

drive

1 not

ready

logical

1 =

interrupt

pending

Jpgical

0 = no

interrupt

pending

logical 1 =

controller present

logical

0 =

controller

not

present

READ RESULT TYPE

(INPUT)

his

input

channel command

causes

the

Diskette Channel

to

return

eight

bits

of

information

to the

CPU.

The two

ast

significant

bits

specify

one of

four

different

types

of

result

byte

(see

next

paragraph) associated

with

diskette

BASE

+ 1

(LSB)

76543210

0

0 0

000

I

•t

System

address

bus:

System data bus:

Type

Code

00

- I/O

Complete error

bits

10 —

Result

byte

contains diskette

ready status

-"

' r ' " '•'"-'

*•

01,11 - Reserved

READ RESULT

BYTE

(INPUT)

his

input

channel command

causes

the

Diskette Channel

to

return

eight bits

of

information

to the

CPU.

The

inter-

etation

of

these

bits

is

dependent

upon

the

type

code returned

in the

result type

word

(see previous paragraph).

he

'read

result

byte'

channel

command

should

only

be

executed

after a 'read

result

type'

command

has

been

executed.

System

address

bus: BASE

+ 3

VJ

'

**

"

tf

System data bus:

If the

type

code

in the

result

type

word

- 00, the

result

byte,

input

on the

data

bus,

will

contain error bits (see Section

2.4 for

error explanations)

and

will

be

formatted

as

follows:

(LSB)

76543210

'

""'

nt

rpariy

A

>ktki

^>k

i

k A i

I

Deleted record

CRC

error

Seek

error

Address

error

Data overrun/underrun

Page 27

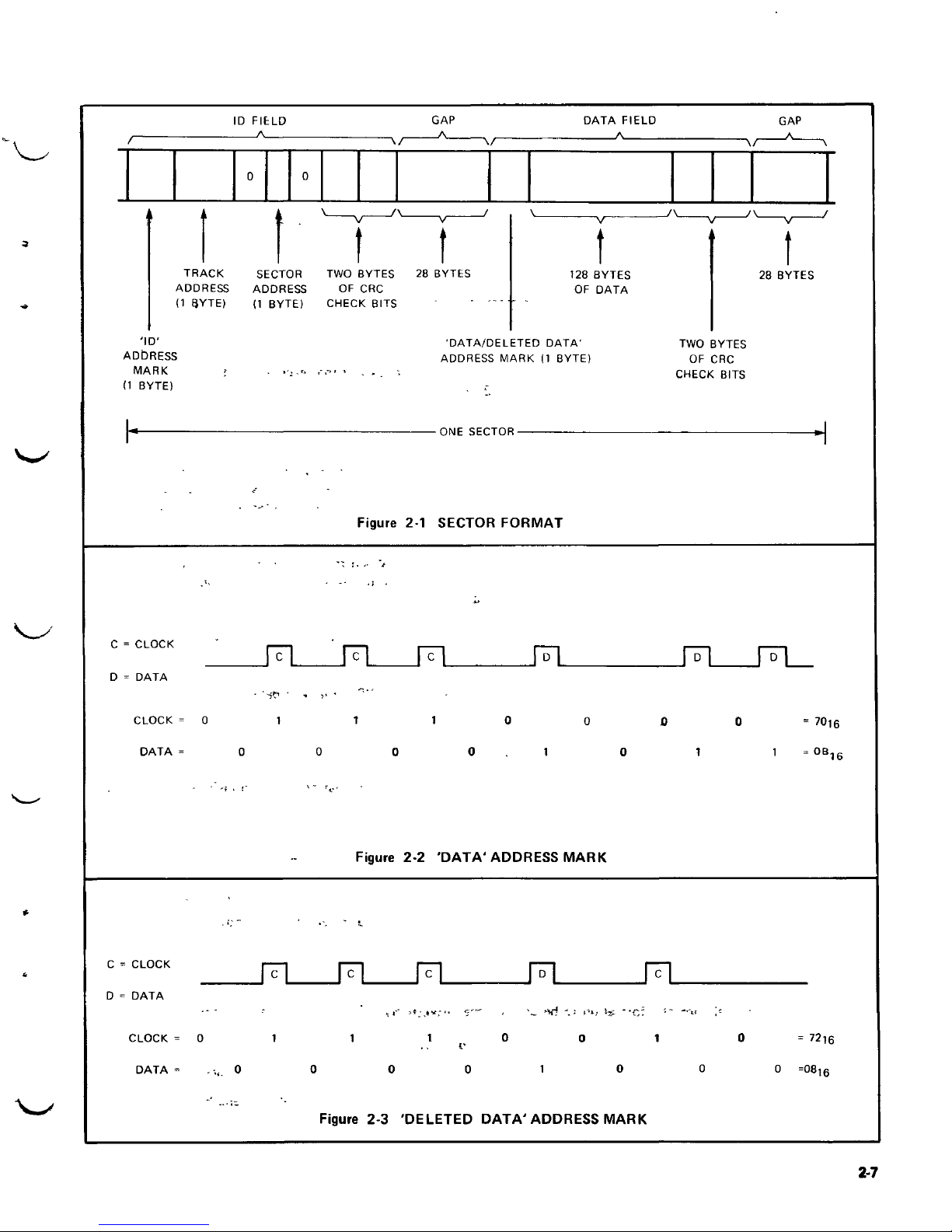

ID

FltLD

A

GAP

DATA

FIELD

A

GAP

V V

t t

TRACK

ADDRESS

(1

BYTE)

SECTOR

ADDRESS

(1

BYTE)

TWO

BYTES

OF CRC

CHECK

BITS

28

BYTES

'ID

1

ADDRESS

MARK

(1

BYTE)

t

128

BYTES

OF

DATA

'DATA/DELETED

DATA'

ADDRESS

MARK

(1

BYTE)

28

BYTES

TWO

BYTES

OF CRC

CHECK

BITS

ONE

SECTOR

Figure

2-1

SECTOR FORMAT

C = CLOCK

D =

DATA

FL__FT__Fl

D

D

CLOCK

= 0

DATA

=

Figure

2-2

'DATA'ADDRESS

MARK

=

70!

6

=

OB

16

C = CLOCK

D =

DATA

CLOCK

= 0

DATA

-

F1__FL__R

Fl

0

t 0

72

16

000

=08

16

Figure

2-3

'DELETED

DATA'ADDRESS

MARK

2-7

Page 28

the

interrupt

status),

the CPU

should execute channel commands

5 and 6

(read result

type

and

read result byte)

to

determine whether

the

diskette operations were successfully completed,

and if not

which

type

of

error occurred.

Thus,

in

summary,

we see

that

certain channel commands

are

executed

by the CPU to

point

the

Diskette Channel

to

an

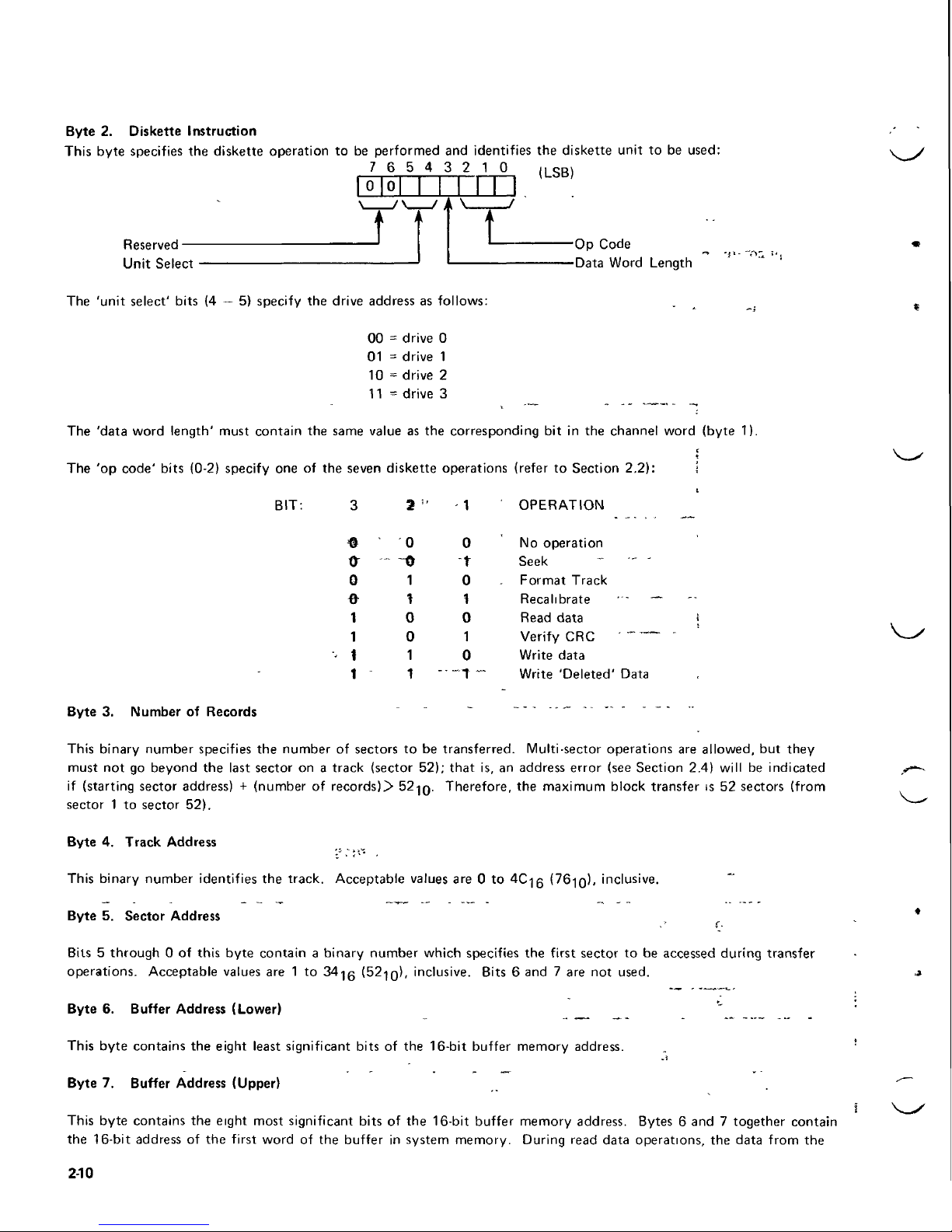

IOPB