Page 1

Intel® Core™ i7 Processor with

Intel® QM57 Express Chipset

Development Kit User Guide

December 2009

Revision 001

323094

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR

IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO

LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR

USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel

products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear

facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property

rights that relate to the presented subject matter. The furnishing of documents and other materials and information does

not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or

other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or

“undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or

incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each

processor family, not across different processor families. See http://www.intel.com/products/processor_number for

details.

The Intel® CoreTM 2 Duo processor and Mobile Intel® GME965 Express Chipset may contain design defects or errors

known as errata which may cause the product to deviate from published specifications. Current characterized errata are

available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product

order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be

obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, Dialogic, FlashFile, i960, InstantIP, Intel,

Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel.

Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel

SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus,

OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside

are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2009, Intel Corporation. All Rights Reserved.

2 323094 Dev Kit Manual

Page 3

Contents

1 About This Manual .............................................................................................. 7

1.1 Content Overview .................................................................................... 7

1.2 Text Conventions .................................................................................... 7

1.3 Glossary of Terms and Acronyms............................................................... 9

1.4 Related Documents ................................................................................ 14

1.5 Development kit Technical Support .......................................................... 14

1.5.1 Online Support......................................................................... 14

1.5.2 Additional Technical Support ...................................................... 14

2 Getting Started ................................................................................................ 15

2.1 Development Kit Contents ...................................................................... 15

2.2 Additional Required Hardware Not Included In This Kit ............................... 16

2.3 Additional Required Software Not Included In This Kit ................................ 16

2.4 Workspace Preparation .......................................................................... 16

2.5 System Setup ....................................................................................... 17

2.6 System Power-Up .................................................................................. 18

2.7 System Power-Down .............................................................................. 18

2.8 System BIOS ........................................................................................ 18

2.8.1 Configuring the BIOS ................................................................ 18

2.8.2 Programming BIOS Using a Bootable USB Device ......................... 19

2.9 Instructions to flash BIOS on SPI ............................................................ 20

3 Development Board Features ............................................................................. 21

3.1 Block Diagram ...................................................................................... 21

3.2 Mechanical Form Factor .......................................................................... 21

3.3 Development Board Features Table .......................................................... 21

3.4 Driver Key Features ............................................................................... 23

3.5 BIOS Key Features ................................................................................ 24

3.6 System Thermal Management ................................................................. 24

3.7 System Features and Operation .............................................................. 24

3.7.1 Processor ................................................................................ 25

3.7.2 Chipset ................................................................................... 29

3.7.3 Displays .................................................................................. 35

3.7.4 Debugging Interfaces ............................................................... 38

3.7.5 Power Management .................................................................. 38

3.7.6 Power Measurement Support ..................................................... 38

3.7.7 Power Supply Usage and Recommendation .................................. 43

4 Development Board Physical Hardware Reference ................................................ 44

4.1 Primary Features ................................................................................... 44

4.2 Connectors ........................................................................................... 47

4.2.1 Back Panel Connectors .............................................................. 48

4.3 Configuration Settings............................................................................ 48

4.4 Power On and Reset Push Buttons ........................................................... 51

4.5 LEDs .................................................................................................... 52

4.6 Other Headers ...................................................................................... 53

Dev Kit Manual 3 323094

Page 4

4.6.1 H8 Programming Header ........................................................... 53

4.6.2 Expansion Slots and Sockets ..................................................... 53

5 Daughter and Plug-in Cards ............................................................................... 63

5.1 PCIe* Add-in Card ................................................................................. 63

5.2 PCI Expansion Card ............................................................................... 63

5.3 Port 80-83 Add-in Card .......................................................................... 64

6 Heatsink Installation Instructions ....................................................................... 66

Figures

Figure 1. System Block Diagram ........................................................................ 21

Figure 2. VID Override Circuit ............................................................................ 26

Figure 3. Block Diagram of On-board LAN Implementations ................................... 30

Figure 4. BCLK Frequency Select Circuit .............................................................. 34

Figure 5. Platform Clocking Circuit ...................................................................... 35

Figure 6. Intel® Core™ i7 Processor Based Low-Power Platform Display Interfaces .. 37

Figure 7. Component Locations – Top View .......................................................... 44

Figure 8. Component Locations – Bottom View ..................................................... 45

Figure 9. Back Panel Connector Locations ............................................................ 48

Figure 10. PCIe* Add-in Card............................................................................. 63

Figure 11. PCI Expansion Card ........................................................................... 64

Figure 12. Port 80-83 Interposer Card ................................................................ 64

Figure 13. Block Diagram of Port 80-83 Add-in Card ............................................. 65

Figure 14. Disassembled Fan/heatsink Assembly .................................................. 66

Figure 15. Bottom View of the CRB with Backplate in Place .................................... 67

Figure 16. Top View of Board With Pins Installed, Through the Board, And

Into the Backplate (Backplate not visible) ..................................................... 68

Figure 17. Applying Thermal Grease to the Top of Processor Package .................... 69

Figure 18. Squeeze Activation Arm Downward, Toward the Board ......................... 70

Figure 19. Installing Fan/heatsink (Slide the fan/heatsink away from

compression assembly handle) .................................................................... 71

Figure 20. Fan/heatsink Power Plugged Into Board .............................................. 72

Figure 21. Completed Intel® Core™ i7 Processor CRB With Fan/heatsink

Assembly Installed .................................................................................... 73

Tables

Table 1. Text Conventions ................................................................................... 8

Table 2. Terms ................................................................................................... 9

Table 3. Acronyms ........................................................................................... 11

Table 4. Related Documents .............................................................................. 14

Table 5. Development Kit Feature Set Summary .................................................. 22

Table 6. Supported DIMM Module Configurations .................................................. 27

Table 7. Hardware Straps for processor PCI Express* Interface Usage .................... 28

Table 8. PCI Express* Ports ............................................................................... 30

Table 9. Selection of I/O Voltage for the Intel® High Definition Audio ...................... 31

Table 10. SATA Ports ........................................................................................ 31

Table 11. USB Port Mapping .............................................................................. 32

Table 12. Jumper Setting for SPI Programming .................................................... 33

Table 13. Power Management States .................................................................. 38

4 323094 Dev Kit Manual

Page 5

Table 14. Digital Multimeter ............................................................................... 39

Table 15. Power Measurement Resistor for Power Rails ......................................... 39

Table 16. Component Location .......................................................................... 45

Table 17. Connectors on the motherboard ........................................................... 47

Table 18. Back Panel Connectors ........................................................................ 48

Table 19. Configuration Jumper/Switches Settings ............................................... 48

Table 20. Power-on and Reset Push Buttons ........................................................ 52

Table 21. Development lit LEDs .......................................................................... 52

Table 22. H8 Programming jumpers ................................................................... 53

Table 23. Expansion Slots and Sockets ............................................................... 54

Table 24. Fan Connector (J4C1) ......................................................................... 54

Table 25. Front Panel Connector......................................................................... 54

Table 26. eDP Support Connector ....................................................................... 55

Table 27. SATA Port 0 „Direct Connect‟ Connector Pinout (J8J1) ............................. 55

Table 28. SATA Ports 1 and 2/eSATA Ports 3 and 4 Pinout (J7G2, J7G1, J6J1, J7J1) . 56

Table 29. SATA Power Connector (J6H1) ............................................................. 56

Table 30. SPI Programming Header (J8E1) .......................................................... 56

Table 31. HAD Header for MDC Interposer (J9E4) ................................................. 57

Table 32.HAD Header for MDC Interposer (J9E7) .................................................. 57

Table 33. HAD Header for External HDMI Support (J8F1) ...................................... 58

Table 34. LED Header (J8G3) ............................................................................. 58

Table 35. Descriptor Security Override (J8F4) ...................................................... 59

Table 36. Controller Link Header (J8G2) .............................................................. 59

Table 37. TPM Header/Port 80 Add-in-Card Header (J9A1) .................................... 60

Table 38. LPC Hot Docking (J9E5) ...................................................................... 60

Table 39. LPC Side Band Header (J9G2) .............................................................. 61

Table 40. Jumper settings for Port 80-80 card ..................................................... 65

Dev Kit Manual 5 323094

Page 6

Document

Number

Revision

Number

Description

Revision Date

323094

001

Public release.

December 2009

Revision History

§

6 323094 Dev Kit Manual

Page 7

1 About This Manual

This manual describes the use of the Intel® Core™ i7 Processor with Intel® QM57 Express

Chipset Development kit (Development kit). This manual has been written for OEMs, system

evaluators, and embedded system developers. This manual assumes basic familiarity in the

fundamental concepts involved with installing and configuring hardware for a personal

computer system. This document defines all jumpers, headers, LED functions, their locations

on the development kit, and other subsystem features and POST codes. This manual assumes

basic familiarity in the fundamental concepts involved with installing and configuring hardware

for a personal computer system.

For the latest information about the Dev Kit and platform design collateral, please visit:

http://tigris.intel.com/scripts-edk/viewer/UI_CLCatalog.asp?edkId=8381

1.1 Content Overview

This manual is arranged into the following sections:

About This Manual contains a description of conventions used in this manual. The last few

sections explain how to obtain literature and contact customer support.

Getting Started describes the contents of the development kit. This section explains the basics

steps necessary to get the board running. This section also includes information on how to

update the BIOS.

Development Board Features describes details on the hardware features of the development

board. It explains the Power Management and Testability features.

Development Board Physical Hardware Reference provides a list of major board components

and connectors. It gives a description of jumper settings and functions. The chapter also

explains the use of the programming headers.

Daughter and Plug-in Cards contains information on add-in cards available from Intel that can

be used with the development board.

1.2 Text Conventions

Throughout this document:

Intel

Intel

®

Core™ i7-620M Processor, Intel® Core™ i7-610E Processor, Intel® Core™ i7620LE Processor, Intel® Core™ i7-620UE Processor, Intel® Core™ i5-520M Processor,

and Intel® Core™ i5-520E Processor, Intel® Celeron® P4500 processor, and Intel®

Celeron® P4505 processor may be referred to as the Processor or CPU.

®

QM57 Series Chipset may be referred to as the Chipset or PCH.

The notations listed in Table 1 may be used throughout this manual.

Dev Kit Manual 7 323094

Page 8

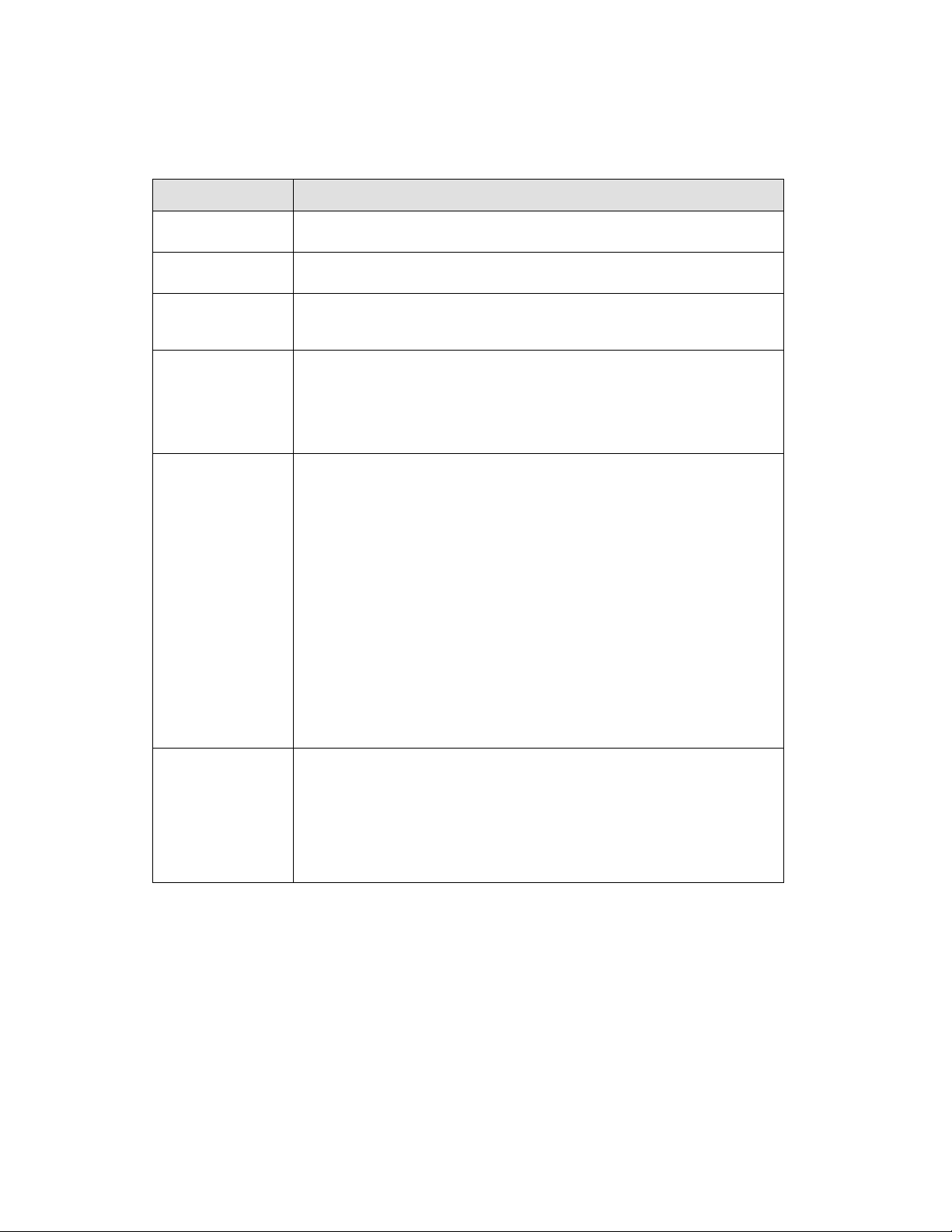

Notation

Definition

#

The pound symbol (#) appended to a signal name indicates that the signal

is active low. (e.g., PRSNT1#)

Variables

Variables are shown in italics. Variables must be replaced with correct

values.

INSTRUCTIONS

Instruction mnemonics are shown in uppercase. When you are

programming, instructions are not case-sensitive. You may use either

uppercase or lowercase.

Numbers

Hexadecimal numbers are represented by a string of hexadecimal digits

followed by the character H. A zero prefix is added to numbers that begin

with A through F. (For example, FF is shown as 0FFH.) Decimal and binary

numbers are represented by their customary notations. (That is, 255 is a

decimal number and 1111 is a binary number. In some cases, the letter B

is added for clarity.)

Units of Measure

A

GByte

KByte

K

mA

MByte

MHz

ms

mW

ns

pF

W

V

µA

µF

µs

µW

The following abbreviations are used to represent units of measure:

amps, amperes

gigabytes

kilobytes

kilo-ohms

milliamps, mill amperes

megabytes

megahertz

milliseconds

milliwatts

nanoseconds

picofarads

watts

volts

microamps, microamperes

microfarads

microseconds

microwatts

SIGNAL NAMES

Signal names are shown in uppercase. When several signals share a

common name, an individual signal is represented by the signal name

followed by a number, while the group is represented by the signal name

followed by a variable (n). For example, the lower chip-select signals are

named CS0#, CS1#, CS2#, and so on; they are collectively called CSn#.

A pound symbol (#) appended to a signal name identifies an active-low

signal. Port pins are represented by the port abbreviation, a period, and

the pin number (e.g., P1.0).

Table 1. Text Conventions

8 323094 Dev Kit Manual

Page 9

Term/Acronym

Definition

Aggressor

A network that transmits a coupled signal to another network.

Anti-etch

Any plane-split, void or cutout in a VCC or GND plane.

Bus Agent

A component or group of components that, when combined, represent a

single load on the AGTL+ bus.

Crosstalk

The reception on a victim network of a signal imposed by aggressor

network(s) through inductive and capacitive coupling between the

networks.

Backward Crosstalk - Coupling that creates a signal in a victim network

that travels in the opposite direction as the aggressor‟s signal.

Forward Crosstalk - Coupling that creates a signal in a victim network that

travels in the same direction as the aggressor‟s signal.

Even Mode Crosstalk - Coupling from a signal or multiple aggressors when

all the aggressors switch in the same direction that the victim is

switching.

Odd Mode Crosstalk - Coupling from a signal or multiple aggressors when

all the aggressors switch in the opposite direction that the victim is

switching.

Duck Bay 3

PCI Express* interposer card that provides Express-card support

Flight Time

Flight time is a term in the timing equation that includes the signal

propagation delay, any effects the system has on the TCO (time from

clock-in to data-out) of the driver, plus any adjustments to the signal at

the receiver needed to ensure the setup time of the receiver. More

precisely, flight time is defined as:

The time difference between a signal at the input pin of a receiving agent

crossing the switching voltage (adjusted to meet the receiver

manufacturer‟s conditions required for AC timing specifications; i.e.,

ringback, etc.) and the output pin of the driving agent crossing the

switching voltage when the driver is driving a test load used to specify the

driver‟s AC timings.

Maximum and Minimum Flight Time - Flight time variations are caused by

many different parameters. The more obvious causes include variation of

the board dielectric constant, changes in load condition, crosstalk, power

noise, variation in termination resistance, and differences in I/O buffer

performance as a function of temperature, voltage, and manufacturing

process. Some less obvious causes include effects of Simultaneous

Switching Output (SSO) and packaging effects.

Maximum flight time is the largest acceptable flight time a network will

experience under all conditions.

Minimum flight time is the smallest acceptable flight time a network will

experience under all conditions.

Infrared Data

Assoc.

The Infrared Data Association (IrDA) has outlined a specification for serial

communication between two devices via a bi-directional infrared data

Table 2. Terms

1.3 Glossary of Terms and Acronyms

Table 2 defines conventions and terminology used throughout this document.

Dev Kit Manual 9 323094

Page 10

Term/Acronym

Definition

port. The Development kit has such a port and it is located on the rear of

the platform between the two USB connectors.

IMVP6.5

The Intel® Mobile Voltage Positioning specification for the Intel® Core™ i5

Processor. It is a DC-DC converter module that supplies the required

voltage and current to a single processor.

Inter-Symbol

Interference

Inter-symbol interference is the effect of a previous signal (or transition)

on the interconnect delay. For example, when a signal is transmitted

down a line and the reflections due to the transition have not completely

dissipated, the following data transition launched onto the bus is affected.

ISI is dependent upon frequency, time delay of the line, and the reflection

coefficient at the driver and receiver. ISI may impact both timing and

signal integrity.

Mott Canyon IV

This Add-in Card enables Intel® High Definition Audio functionality

Network

The network is the trace of a Printed Circuit Board (PCB) that completes

an electrical connection between two or more components.

Overshoot

The maximum voltage observed for a signal at the device pad, measured

with respect to VCC.

Pad

The electrical contact point of a semiconductor die to the package

substrate. A pad is only observable in simulations.

Pin

The contact point of a component package to the traces on a substrate,

such as the motherboard. Signal quality and timings may be measured at

the pin.

Power-Good

“Power-Good,” “PWRGOOD,” or “CPUPWRGOOD” (an active high signal)

indicates that all of the system power supplies and clocks are stable.

PWRGOOD should go active at a predetermined time after system

voltages are stable and should go inactive as soon as any of these

voltages fail their specifications.

Ringback

The voltage to which a signal changes after reaching its maximum

absolute value. Ringback may be caused by reflections, driver oscillations,

or other transmission line phenomena.

System Bus

The System Bus is the microprocessor bus of the processor.

Setup Window

The time between the beginning of Setup to Clock (TSU_MIN) and the

arrival of a valid clock edge. This window may be different for each type

of bus agent in the system.

Simultaneous

Switching Output

Simultaneous Switching Output (SSO) effects are differences in electrical

timing parameters and degradation in signal quality caused by multiple

signal outputs simultaneously switching voltage levels in the opposite

direction from a single signal or in the same direction. These are called

odd mode and even mode switching, respectively. This simultaneous

switching of multiple outputs creates higher current swings that may

cause additional propagation delay (“push-out”) or a decrease in

propagation delay (“pull-in”). These SSO effects may impact the setup

and/or hold times and are not always taken into account by simulations.

System timing budgets should include margin for SSO effects.

Stub

The branch from the bus trunk terminating at the pad of an agent.

Trunk

The main connection, excluding interconnect branches, from one end.

System

Management Bus

A two-wire interface through which various system components may

communicate.

10 323094 Dev Kit Manual

Page 11

Term/Acronym

Definition

Undershoot

The minimum voltage extending below VSS observed for a signal at the

device pad.

VCC (CPU core)

VCC (CPU core) is the core power for the processor. The system bus is

terminated to VCC (CPU core).

Victim

A network that receives a coupled crosstalk signal from another network

is called the victim network.

Acronym

Definition

AC

Audio Codec

ACPI

Advanced Configuration and Power Interface

ADD2

Advanced Digital Display 2

ADD2N

Advanced Digital Display 2 Normal

AIC

Add-In Card

AMC

Audio/Modem Codec.

AMT

Advanced Management Technology

ASF

Alert Standard Format

AMI

American Megatrends Inc. (BIOS developer)

ATA

Advanced Technology Attachment (disk drive interface)

ATX

Advance Technology Extended (motherboard form factor)

BGA

Ball Grid Array

BIOS

Basic Input/Output System

CK-SSCD

Spread Spectrum Differential Clock

CMC

Common Mode Choke

CMOS

Complementary Metal-Oxide-Semiconductor

CPU

Central Processing Unit (processor)

CRB

Customer Reference Board

DDR

Double Data Rate

DMI

Direct Memory Interface

DPST

Display Power Saving Technology

ECC

Error Correcting Code

EEPROM

Electrically Erasable Programmable Read-Only Memory

EHCI

Enhanced Host Controller Interface

EMA

Extended Media Access

Table 3 defines the acronyms used throughout this document.

Table 3. Acronyms

Dev Kit Manual 11 323094

Page 12

Acronym

Definition

EMI

Electro Magnetic Interference

ESD

Electrostatic Discharge

EV

Engineering Validation

EVMC

Electrical Validation Margining Card

ERB

Early Engineering Reference Board

FCBGA

Flip Chip Ball Grid Array

FDD

Floppy Disk Drive

FIFO

First In First Out - describes a type of buffer

FIR

Fast Infrared

FS

Full-speed. Refers to USB

FSB

Front Side Bus

FWH

Firmware Hub

GMCH

Graphics Memory Controller Hub

GPIO

General Purpose IO

HDA

Intel® High Definition Audio

HDMI

High Definition Media Interface

HS

High-speed. Refers to USB

ICH

I/O Controller Hub

IDE

Integrated Drive Electronics

IMVP

Intel Mobile Voltage Positioning

IP/IPv6

Internet Protocol/Internet Protocol version 6

IrDA

Infrared Data Association

ISI

Inter-Symbol Interference

KBC

Keyboard Controller

LAI

Logic Analyzer Interface

LAN

Local Area Network

LED

Light Emitting Diode

LOM

LAN on Motherboard

LPC

Low Pin Count (often used in reference to LPC bus)

LS

Low-speed. Refers to USB

LVDS

Low Voltage Differential Signaling

MC

Modem Codec

MDC

Mobile Daughter Card

ME

Manageability Engine

MHz

Mega-Hertz

12 323094 Dev Kit Manual

Page 13

Acronym

Definition

OS

Operating System

OEM

Original Equipment Manufacturer

PCB

Printed Circuit Board

PCIe

PCI Express*

PCH

Platform Controller Hub

PCM

Pulse Code Modulation

PEG

PCI Express* Graphics

PGA

Pin Grid Array

PLC

Platform LAN Connect

PLL

Phase Locked Loop

POST

Power On Self Test

RAID

Redundant Array of Inexpensive Disks

RTC

Real Time Clock

SATA

Serial ATA

SIO

Super Input/Output

SKU

Stock Keeping Unit

SMC

System Management Controller

SMBus

System Management Bus

SO-DIMM

Small Outline Dual In-line Memory Module

SPD

Serial Presence Detect

SPI

Serial Peripheral Interface

SPWG

Standard Panels Working Group - http://www.spwg.org/

SSO

Simultaneous Switching Output

STR

Suspend To RAM

TCO

Total Cost of Ownership

TCP

Transmission Control Protocol

TPM

Trusted Platform Module

TDM

Time Division Multiplexed

TDR

Time Domain Reflectometry

UDP

User Datagram Protocol

UHCI

Universal Host Controller Interface

USB

Universal Serial Bus

VGA

Video Graphics Adapter

VID

Voltage Identification

VREG or VR

Voltage Regulator

Dev Kit Manual 13 323094

Page 14

Acronym

Definition

XDP

eXtended Debug Port

Document Title

Document No

Calpella Platform Design Guide For

Arrandale and Intel(r) Series 5 Chipset

398905

Calpella+ECC Platform Design Guide

Addendum

411043

Arrandale Processor External Design

Specification – Volumes One and Two

403777 and 403778

Mobile Intel® 5 Series Chipset and Intel®

3400 Series Chipset External Design

Specification

401376

Calpella+ECC] Platform - Fort Sumter CRB

OrCAD Schematic – Rev. 1.1

409593

[Calpella+ECC] Platform -Fort Sumter CRB

PDF Schematic – Rev. 1.11

409572

[Calpella] Platform, Eaglemont-2 Add-inCard – User Guide – Rev. 1.0

414150

[Calpella] Platform, Thimble Peak 2 Add In

Card – Schematics / Diagrams – Rev. 1.0

417149

1.4 Related Documents

Table 4 provides a summary of publicly available documents related to this development kit.

For additional documentation, please contact your Intel Representative.

Table 4. Related Documents

1.5 Development kit Technical Support

1.5.1 Online Support

Intel‟s web site (http://www.intel.com/) provides up-to-date technical information and product

support. This information is available 24 hours per day, 7 days per week, providing technical

information whenever you need it.

1.5.2 Additional Technical Support

If you require additional technical support, please contact your Intel Representative or local

distributor.

14 323094 Dev Kit Manual

Page 15

2 Getting Started

The development kit‟s motherboard is populated with the Intel® Core™ i7 Processor, the Intel®

QM57 Express Chipset and other system board components and peripheral connectors. This

section identifies the development kit‟s key components, features and specifications. It also

details basic development board setup and operation.

2.1 Development Kit Contents

The following hardware, software and documentation is included in the development kit. Check

for damage that may have occurred during shipment. Contact your sales representative if any

items are missing or damaged.

Letter to the Customer

Development kit User‟s Manual (this document)

Software CD-ROM, which includes (see the readme.txt file for a complete list of CD-

ROM contents):

o System BIOS

o BIOS installation utilities

o Chipset drivers

o Intel Embedded Graphics Drivers

o Intel

Pre-assembled development system, which includes:

o Development board

o Plexiglass stand with Acrylic pad

o Mounting screws and standoffs (installed)

o Intel

o Processor thermal solution and CPU back plate

o Intel

o QM57 heatsink (installed)

o One Type 2032, 3 V lithium coin cell battery

o One 1GB DDR3 SO-DIMM

o One Port 80 display card

o One Power Supply

o One 80 G SATA Hard Disk Drive

o One SATA DVD-ROM Drive

o SATA Cabling (Data and power)

One PCI Extension Card (codename Thimble Peak 2)

®

Active Management Technology (AMT) software installation kit

®

Core™ i5 Processor (installed)

®

QM57 Express Chipset (installed)

One 2x8 PCIe Add-in card (codename NOWATA)

Current drivers required for this development kit are available at http://platformsw.intel.com.

Dev Kit Manual 15 323094

Page 16

2.2 Additional Required Hardware Not Included In

This Kit

The following additional hardware may be necessary to successfully set up and operate the

system:

VGA Monitor: Any standard VGA or multi-resolution monitor may be used. The setup

instructions in this chapter assume the use of a standard VGA monitor, TV, or flat

panel monitor.

Keyboard: The kit can support either a PS/2 or USB style keyboard.

Mouse: The kit can support either a PS/2 or USB style mouse.

Hard Disk Drives (HDDs) and Optical Disc Drives (ODD): Up to six SATA drives

and two IDE devices (master and slave) may be connected to the kit. An optical disc

drive may be used to load the OS. All these storage devices may be attached to the

board simultaneously.

Video Adapter: Integrated video is output from the VGA connector on the back panel

of the kit. Alternately, an on board HDMI connector, On board DP connector or LVDS

displays can be used for desired display options. Check the BIOS and the graphics

driver, where appropriate, for the proper video output settings.

Network Adapter: A Gigabit network interface is provided on the kit. The network

interface will not be operational until after all the necessary drivers have been

installed. A standard PCI/PCI Express* adapter may be used in conjunction with, or in

place of, the onboard network adapter.

Note: You must supply appropriate network cables to utilize the LAN connector or any other installed

network cards.

Other Devices and Adapters: The system functions much like a standard desktop

computer motherboard. Most PC-compatible peripherals can be attached and

configured to work with the motherboard.

2.3 Additional Required Software Not Included In

This Kit

The following additional software may be necessary to operate this system:

Operating System: The user must supply any needed operating system installation files and

licenses.

Application Software: The user must supply any needed application software.

2.4 Workspace Preparation

Caution: The development kit is shipped as an open system (not in a chassis) to provide flexibility in

changing hardware configurations and peripherals in a lab environment. Because the board is

not in a protective chassis, the user is required to take the following safety precautions in

handling and operating the board.

16 323094 Dev Kit Manual

Page 17

1. The power supply cord is the main disconnect device to main power (AC power). The

socket outlet should be installed near the equipment and should be readily accessible.

2. To avoid shock, ensure that the power cord is connected to a properly wired and

grounded receptacle.

3. Ensure that any equipment to which this product will be attached is also connected to

properly wired and grounded receptacles.

4. Use a flame retardant work surface and take note of closest fire extinguisher and

emergency exits.

5. Ensure a static-free work environment before removing any components from their

anti-static packaging. Wear an ESD wrist strap when handling the development board

or other kit components. The system is susceptible to electrostatic discharge (ESD)

damage, and such damage may cause product failure, physical harm, and/or

unpredictable operation.

2.5 System Setup

Please follow the steps outlined below to ensure the successful setup and operation of your

development kit system.

These steps should already be completed in the kit:

1. One (or more) DDR3 DIMMs in memory sockets, populating J4V1 and/or J4W1.

2. The processor in socket U7J2 is locked in place (make sure to align the chip to the pin

1 marking)

3. The (default) configuration jumpers are as shown in Table 19.

4. RTC battery is populated in BT5G1.

5. The cable from the ATX power supply is inserted into J4J1.

6. The hard disk drive (HDD) is attached with the supplied cable SATA.

7. The optical driver (ODD) is a attached with the supplied SATA cable.

The following steps need to be completed by the user:

1. Connect either a PS/2 keyboard in J1A1 (bottom) or a USB keyboard in one of the

USB connectors.

2. Connect either a PS/2 mouse in J1A1 (top) or a USB mouse in one of the USB

connectors.

3. If using external graphics, plug a PCI graphics card in PCI-E x1 slot J6C2 or a PCI

Express Graphics card in the PCI-E x16 slot J5C1 and connect a monitor to the card

4. Connect an Ethernet cable (optional), one end of the cable to the motherboard, the

other end to a live Ethernet hub.

5. Connect the monitor to the VGA connector. Also take care to plug the monitor‟s power

cable into the wall.

6. Install the heatsink/fan for the processor at U7J2, and the fan-power cable must be

plugged into J4C1. Fan/heatsink installation is discussed in Appendix B Heatsink.

Installation Instructions.

Dev Kit Manual 17 323094

Page 18

2.6 System Power-Up

Having completed the steps outlined above, you are now absolutely ready to power up the

development kit:

1. Press the power button located at SW1E1.

2. As the system boots, press F2 to enter the BIOS setup screen.

3. Check time, date, and configuration settings. The default settings should be sufficient

for most users with the exception of Intel SpeedStep Technology. This feature is

disabled by default and can be enabled in setup.

4. Press F4 to save and exit the BIOS setup.

5. The system reboots and is ready for use.

Install operating system and necessary drivers:

Depending on the operating system chosen, drivers for components included in this

development kit can be found in http://platformsw.intel.com. Please note that not all drivers

are supported across all operating systems.

2.7 System Power-Down

Powering down the board:

There are three options for powering down the development kit. Those three options are:

Use OS-controlled shutdown through the OS menu (e.g., Microsoft Windows XP*: Start

Shut Down)

Press the power button on the motherboard at SW1E1 to begin power-down.

If the system hangs, it is possible to asynchronously shut the system down by holding

the power button down continuously for 4 seconds.

Note: Intel does not recommend powering down the board by removing power at the ATX power

supply by either unplugging the power supply from the AC source/wall or by unplugging the

DC power at the board.

2.8 System BIOS

A version of the AMI* BIOS is pre-loaded on the development kit board.

2.8.1 Configuring the BIOS

The default BIOS settings may need to be modified to enable or disable various features of the

development board. The BIOS settings are configured through a menu-driven user interface

which is accessible during the Power On Self Test (POST). Press the F2 key or Delete key

during POST to enter the BIOS interface.

For AMI* BIOS POST codes, visit: www.ami.com,

For BIOS updates please contact your Intel Sales Representative or visit:

https://platformsw.intel.com.

18 323094 Dev Kit Manual

Page 19

2.8.2 Programming BIOS Using a Bootable USB Device

The flash chips which store the BIOS and BIOS extensions on the development board are

connected to the SPI bus and are soldered down with solder. One method of programming

these devices is through software utilities as described below. The software files and utilities

needed to program the BIOS are contained on the included CD-ROM.

1. Follow these steps to program the system BIOS using a bootable USB Device.

2. Prepare the workspace as outlined in Section 2.4.

3. Setup the system as outlined in Section 2.5.

4. Unplug the hard disk drive (HDD) SATA cable from the board at connector J6J3 so that

the board will boot from the bootable USB key.

5. Copy the following files and utilities to a Bootable USB Device, preferably a USB flash

memory stick.

BIOS Image Files:

spifull.bin

BIOS Programming Software Utilities:

fpt.exe (DOS SPI Flash Utility)

fparts.txt (helper file)

MAC Address Programming Software Utility:

eeupdate.exe

BIOS collateral can be obtained from https://platformsw.intel.com.

6. Record the 12 digit MAC Address of the board from the sticker near the CPU.

7. Insert the Bootable USB Key into one of the USB Ports on the motherboard.

8. Switch on the power supply (to “1”).

9. Press the Power (PWR) Button on the development board.

10. Wait for the system to boot from the USB Key to a DOS prompt.

11. From the DOS prompt (C:>), Run the following:

a. fpt –f spifull.bin

b. Make sure there are no warnings or errors

12. From DOS, run the following to reprogram the MAC address:

a. eeupdate /nic=1 /mac=xxxxxxxxxxxx where: xxxxxxxxxxxx is the MAC Address

from the sticker

b. Make sure there are no warnings or errors

13. From DOS, Run the following to update the Keyboard and System Controller flash:

a. kscupdate ksc.bin

b. Make sure there are no warnings or errors

14. Power the system down by pressing the PWR button.

15. Clear the CMOS by performing the following:

a. Shunt the CMOS CLR jumper (J5F2 – near the on-board battery)

b. Press the PWR button on the board. The board will not power on, but a couple of

LEDs will flash.

c. Switch the power supply off to power down the board

d. Remove the CMOS CLR jumper (J5F2).

16. Unplug the bootable USB Key.

Verify Correct BIOS Installation:

1. Switch the power supply back on

2. Press the PWR button on the board to power-up the system.

Dev Kit Manual 19 323094

Page 20

3. Boot to BIOS Configuration screen by pressing F2 at the BIOS splash screen.

4. In the BIOS Main screen, check that the “Project Version” lists the correct version of

the BIOS.

5. Press the PWR key on the board to power the system back down, or you may simply

exit the BIOS menu and continue booting into the operating system.

BIOS update is now complete:

The system is now ready for normal operation.

2.9 Instructions to flash BIOS on SPI

The Intel® Core™ i7 Processor with Intel® QM57 Express Chipset Development kit requires the

use of a two-partition SPI image for SPI-0 and SPI-1 respectively. The Descriptors sit on SPI-0

while the BIOS on SPI-1.

1. Remove all the power supplies to the board.

2. Connect the Dediprog* SF100 at J8E1.

3. Set jumpers J8D1 and J8D2 at 1-2.

4. Set jumper J8D3 and J9E2 at 1-2 for SPI-0 and flash the .bin image corresponding to

SPI-0.

5. Set the jumper J8D3 at 2-3 and J9E2 at 1-2 for SPI-1 and flash the .bin image

corresponding to SPI-1.

6. Set the jumper J9E2 at 2-3 for SPI-1 and flash the .bin image corresponding to SPI-2.

7. Once the programming is successful on the SPI, set J8D1 and J8D2 at 1-X and J8D3 at

1-X and 3-X.

8. Remove the Dediprog connector.

9. Set the SPI.

20 323094 Dev Kit Manual

Page 21

D

I

M

M

TPM

SIO

SMC/

KBC

LPC

LPC

LPC Hot

Dock

Serial

14 USB ports

SATA PORT 0

SATA PORT 2

SATA PORT 4

USB 2.0/1.0

XDP

CRT VGA

LVD

CRT VGA

Infrared

Dual Channel DDR3

800/1067/1333/ 1.5V

DMI X 4

PS/2 ports

Scan

matrix

SATA PORT 1

SATA PORT 3

SATA PORT5

FDI

Legacy Block

HDA

header

PCIe x1 Slot1

PCIe x1 Slot2

PCIe x1 Slot3

PCIe x1 Slot4

PCIe x1 Slot5

High Definition Audio Bus

C Link

PEG x16 /eDP

PCIe* Graphics

(GEN1/GEN2)

(eDP)

Digital Display

Interface

PCI

SPI Bus

Intel® 82577

e-SATA

SATA Cable

e-SATA

SATA

SATA Cable

PCI Edge

PCI expansion card

SPI Flash

SPI Flash SPI Flash

IMVP6.5

Docking

Connector

PCI-e (port 7)

PCI-e (port 8)

PCI-e (port 6)

X16 CON

(DP/HDMI)

ADD2-N(SDVO)

Docking

Connector

SMBUS

LVDS

D

I

M

M

Intel®

Core™

i7

Intel®

QM57

Express

Chipset

3 Development Board Features

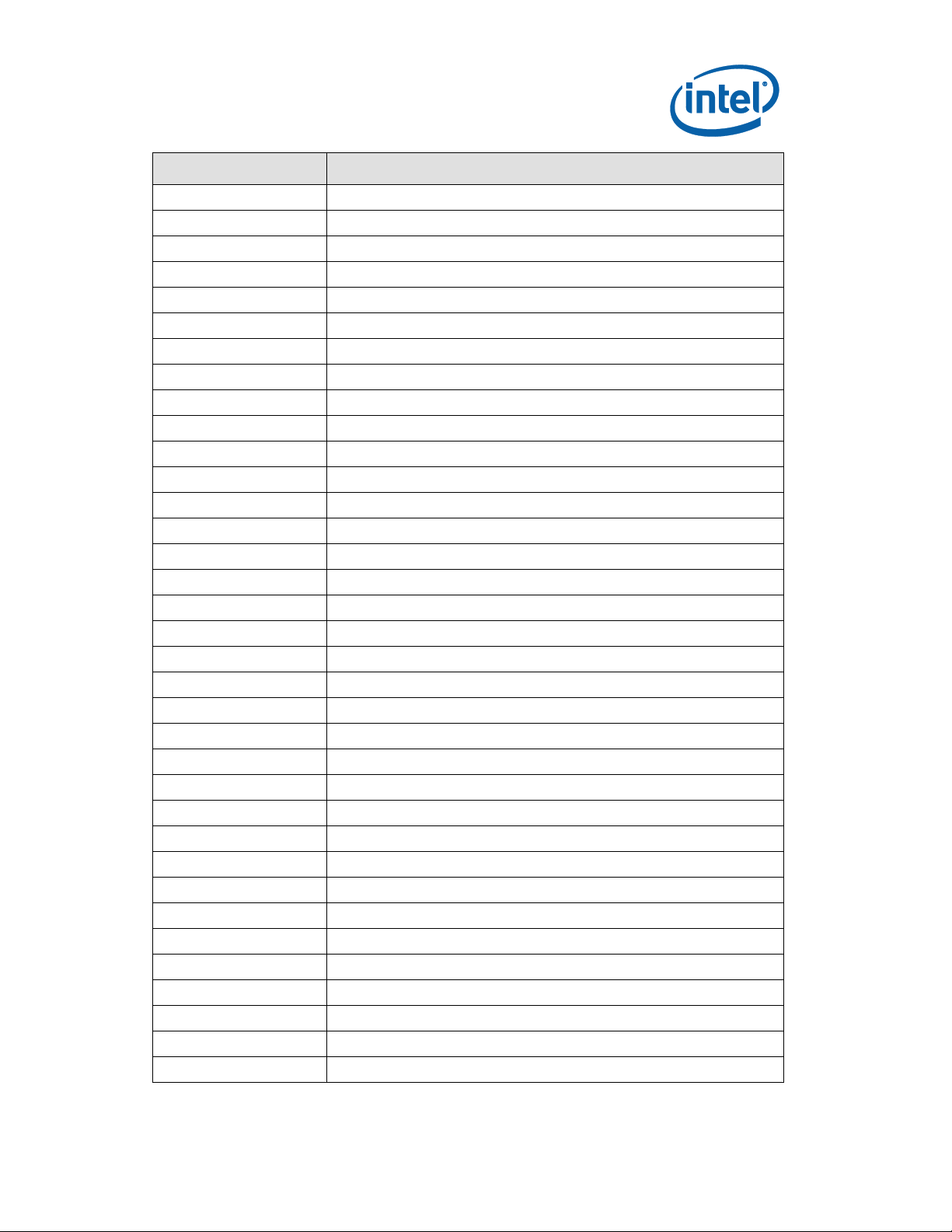

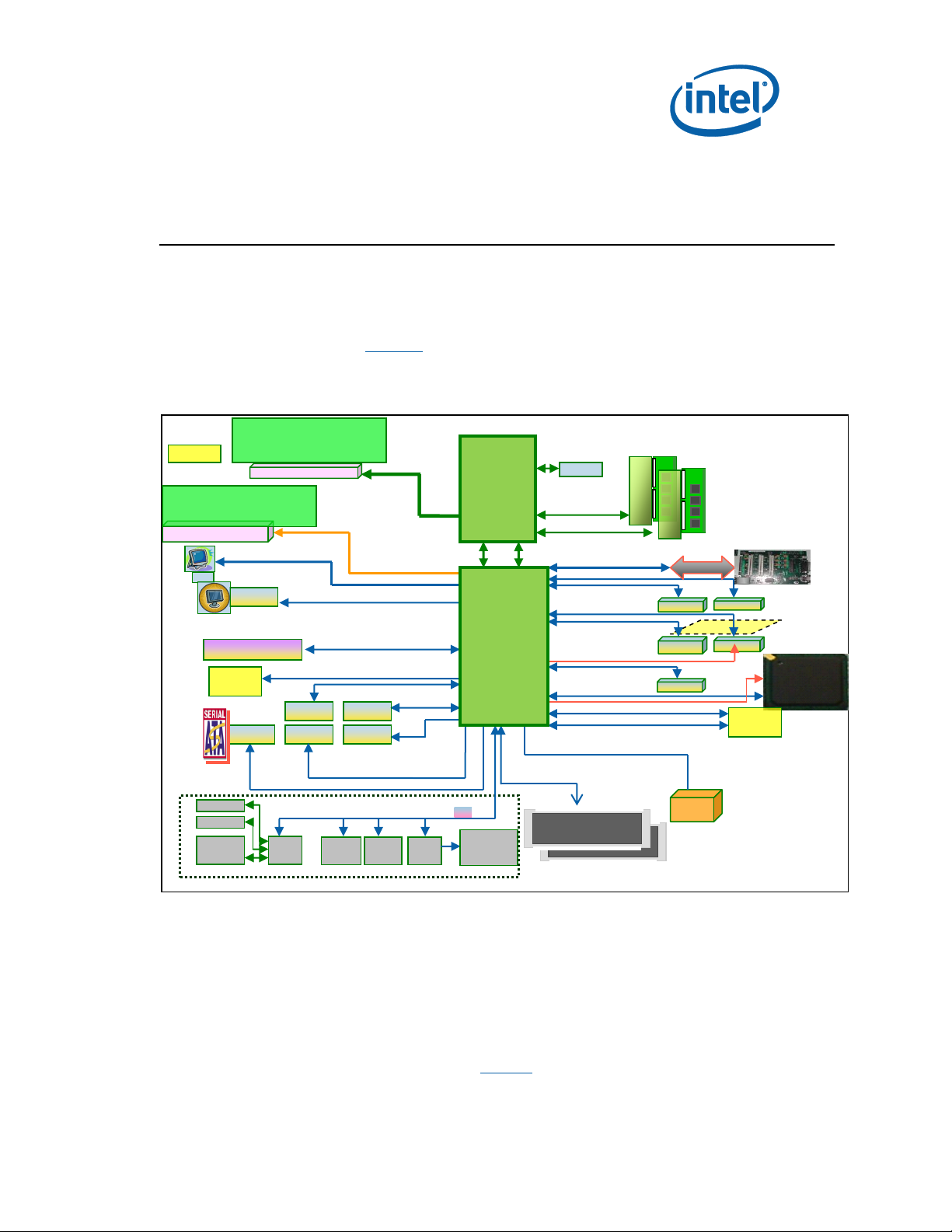

3.1 Block Diagram

The block diagram of the Intel® Core™ i7 Processor with Intel® QM57 Express Chipset

Development kit is shown in Figure 1.

Figure 1. System Block Diagram

3.2 Mechanical Form Factor

The development kit conforms to the ATX 2.2 form factor.

3.3 Development Board Features Table

Development kit features are summarized in Table 5.

Dev Kit Manual 21 323094

Page 22

Description

Comments

Processor

Intel® Core™ i5

Soldered to board

Chipset

Intel® 5 Series Chipset

1071 pin BGA footprint

Memory

Two DDR3 DIMM slots

Maximum 8GB of DDR Memory (RAM) of

ECC and non-ECC using 2Gb1 technology

Supports DDR3 frequency of up to

1066MT/s

Notes:

4Gb (x16 width only) technology support is

under investigation

External

Graphics

PCIe* Slot

One x16 PCIe slot supported.

2x8 PCIe* supported through Nowata Add-

in card.

eDP supported through PCI graphics add-in

card

Video

24-bit dual channel LVDS

Interface

Connectors and cables from previous

development kits can be used.

Display Ports

3 – Display port Lanes on Chipset. 1 On-

Board DP Connector. Other 2 ports can be

supported through PCI graphics add-in card.

CRT

On Board right-angled CRT Connector

Similar to the earlier platforms

HDMI

1 On-Board HDMI Connector (Optional

Routing through Display Port D of Chipset).

Three additional HDMI ports are available

through the Eaglemont 2 external card.

PCI

Three 5V PCI slots supported

through PCI extension card.

PCI revision 2.3 compliant (33MHz)

No PCI slots on motherboard, only one

goldfinger on board.

PCI

Express*

8 PCIe lanes

PCI Express 2.0 base revision compliance

Five lanes to x1 PCIe ports

One lane to LAN

Two Lanes to Docking

On-Board

LAN

Intel® 82577 Gigabit Ethernet PHY

BIOS (SPI)

2x SPI flash devices

Support for multi vendor SPI

Support multi package (SOIC-8 and

SOIC-16)

ATA/

Storage

6 SATA Ports

2 Cable Connector and 1 Direct Connect

Connector. 2 eSATA connectors and 1 to

docking. RAID 0/1 support.

Table 5. Development Kit Feature Set Summary

22 323094 Dev Kit Manual

Page 23

Description

Comments

Intel® High

Definition

Audio MDC

Header

Support via interposer Mott

Canyon 4 daughter card (support

via sideband cable)

Soft Audio/Soft Modem

USB

14 USB 2.0/1.1 Ports

1 Quad USB connector

1 dual USB connector on RJ45

8 ports available as FPIOs

Optional routing to docking for USB lane 4

Over Current protection provided in Pairs.

Floater OC7# used as SMC_WAKE_SCI#

LPC

One LPC slot

Includes sideband headers

SMC/KBC

H8S/2117 micro-controller

Two PS/2 ports

One scan matrix keyboard

connector

ACPI compliant

Clocks

CK-505 system

Supports Buffer Through Mode only.

RTC

Battery-backed Real Time Clock

Processor

Voltage

Regulator

IMVP-6.5 for Processor core

IMVP 6.5 Compliant CPU Core and Graphics

Core VRs, Manual Override Option for VIDs

available on both VR Controllers.

Power

Supply

ATX Power Supply

Debug

Interfaces

Processor and Chipset XDP

Port 80 display

On board Processor Chipset XDP Ports

Port 80 Through Add-in card. Four seven-

segment displays

Intel® AMT

support

Intel® Active Management

Technology 6.0

Power

Management

ACPI Compliant

Supported C states: C0, C1, C1E, C3, C6,

C7

Form Factor

ATX 2.2 like form factor

10 layer board – 12” x 11.2”

3.4 Driver Key Features

The driver CD included in the kit contains all software drivers necessary for basic system

functionality for various operating systems. The CD contains the production drivers that were

released in conjunction with the launch of this platform. However, it is possible that these

drivers have been updated since then. Please check for updated drivers at

http://platformsw.intel.com.

Dev Kit Manual 23 323094

Page 24

Note: Software in the kit is provided free by the vendor and is only licensed for evaluation purposes.

Refer to the documentation in your evaluation kit for further details on any terms and

conditions that may be applicable to the granted licenses. Customers using the tools that work

with Microsoft* products must license those products. Any targets created by those tools

should also have appropriate licenses. Software included in the kit is subject to change.

3.5 BIOS Key Features

This development kit ships with AMI* BIOS pre-boot firmware from AMI* preinstalled. AMI*

BIOS provides an industry-standard BIOS on which to run most standard operating systems,

including Windows* XP/XP Embedded, Linux*, and others.

The following features of AMI* BIOS are enabled in the development board:

DDR3 detection, configuration, and initialization

Intel

POST codes displayed to port 80h

PCI/PCI Express* device enumeration and configuration

Integrated video configuration and initialization

Super I/O configuration

Active Management Technology

Intel

®

QM57 Chipset configuration

®

Matrix Storage Manger RAID 0/1 Support

3.6 System Thermal Management

The objective of thermal management is to ensure that the temperature of each component is

maintained within specified functional limits. The functional temperature limit is the range

within which the electrical circuits can be expected to meet their specified performance

requirements. Operation outside the functional limit can degrade system performance and

cause reliability problems.

The development kit is shipped with a heatsink thermal solution for installation on the

Processor. This thermal solution has been tested in an open-air environment at room

temperature and is sufficient for development purposes. The designer must ensure that

adequate thermal management is provided for if the system is used in other environments or

enclosures.

3.7 System Features and Operation

The following section provides a detailed view of the system features and operation of the

development kit. They are divided into the two sections based upon component: the first

section describes the processor‟s features and the following section describes the chipset‟s

features.

24 323094 Dev Kit Manual

Page 25

3.7.1 Processor

The development kit uses the board design, which supports Intel® Core™ i7 processor in a

BGA package (U3E1). This processor is a 2-die package made up of the dual core processor,

graphics processor and integrate memory controller.

3.7.1.1 Processor Voltage Regulators

The development kit implements an onboard IMVP-6.5 regulator for the processor core supply,

which supports PSI (Power Status Indicator). The maximum current that can be supported by

the Core VR is 60 amps.

3.7.1.2 Processor Power Management

The Processor supports C0, C1 C1E, C3, and C6 states. On this platform all the power

management handshake happens over the DMI interface. None of the „Power State‟ status

signals can be observed on the board directly. Some important Power management pins on

the Processor are listed below.

RESET_OBS# This indicates the final handoff which gets the CPU out of RESET. It is

the final signal to go active in the reset sequence.

VCCPWRGOOD_0/1 Input from the indicating that the system rails and clocks are

stable. The Processor is now ready to be brought out of reset.

VTTPWRGOOD Indicates to the Processor that the 1.1VTT rail is stable.

PSI# An output of the Processor indicating to the VR Controller that it can enter a

low current drive mode to improve its efficiency.

IMON This is a Voltage input to the Processor providing information on the CPU

current consumption.

DPRSLPVR (VID7) An output from the Processor to the IMVP Core VR indicating that

the CPU is in a very low power state.

The only way to detect the entry to/exit from the C1/C3 C-States is to read the DMI

transmissions.

3.7.1.3 Manual VID support for CPU VR

The development kit supports manual VID operation for Processor VR. A jumper J2B1<pins

15-16> is provided to enable “VID override” to the CPU VCC Core VR. The intent of this “VID

override” circuit is for ease of debug and testing. The VID0-VID6 signals of CPU have been

brought out from VID0-VID6 pins on the processor package.

Dev Kit Manual 25 323094

Page 26

Figure 2. VID Override Circuit

3.7.1.4 Graphics Core VR

The development kit implements an onboard IMVP-6.5 compliant VR Controller for the

Graphics core supply. The maximum current that can be supported by the core VR is 21 amps.

3.7.1.5 Manual VID Support for Graphics VR

The development kit supports manual VID operation for Graphics VR. A jumper J2C1<pins 12> is provided to enable “GFX VID override” to the Graphics Core VR. The intent of this “VID

override” circuit is for ease of debug and testing. The implementation is similar to the CPU VR

VID over-ride.

3.7.1.6 Memory Support

The development kit supports dual channel DRR3 interface. There are two DDR3 DIMM sockets

(J4V1 and J4V2) on the motherboard. The memory controller supports four ranks of memory

up to 1066MT/s. The maximum amount of memory supported is 8GB of DDR3 memory.

Minimum capacity supported is 512 MB. The on-board thermal sensor is provided for the

DIMMs.

3.7.1.6.1 Compatible DDR3 DIMM Modules

Raw Card A – single rank x8 unbuffered non-ECC

Raw Card B – dual rank x8 unbuffered non-ECC

Raw Card C – single rank x16 unbuffered non-ECC

26 323094 Dev Kit Manual

Page 27

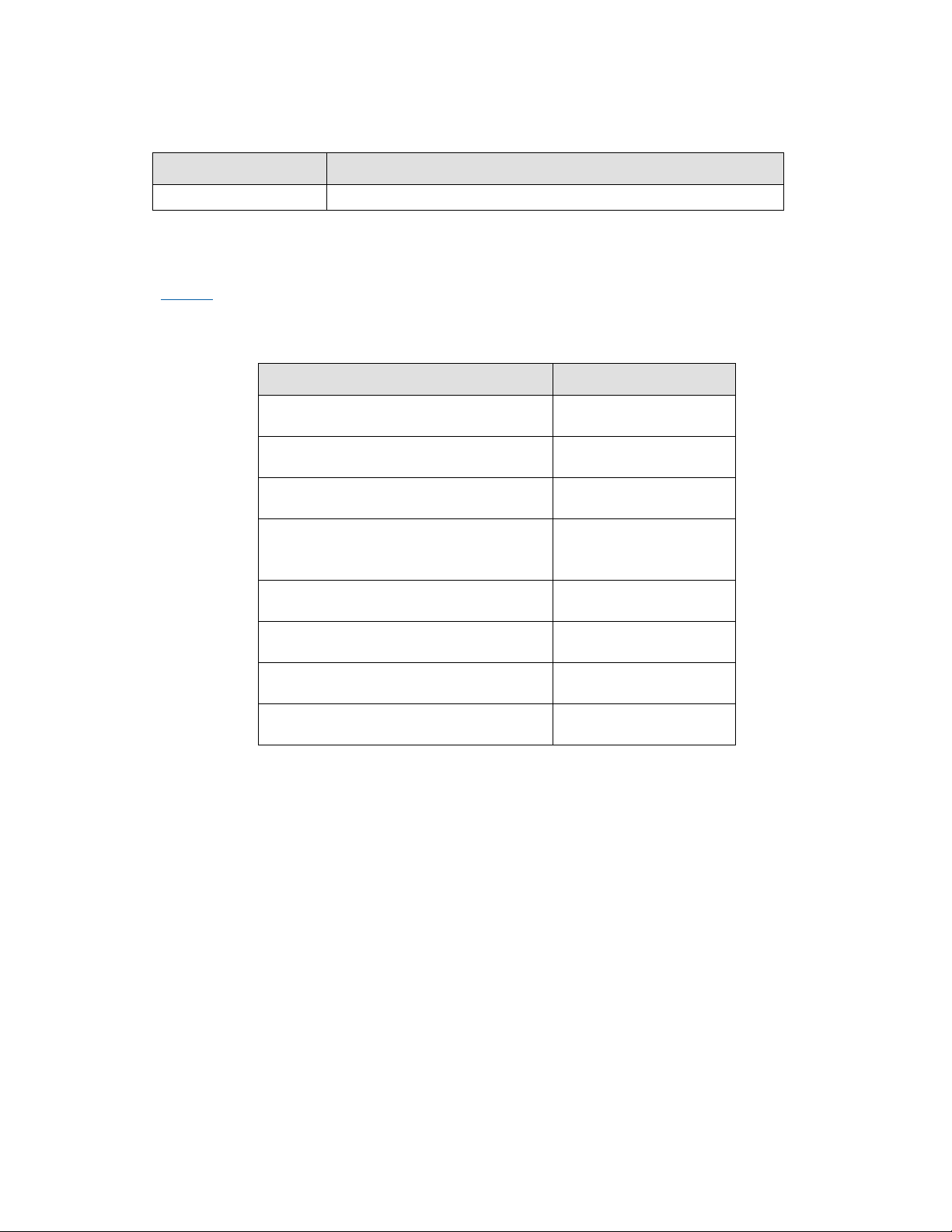

Raw

Card

Version

DIMM

Capacity

DRAM

Device

Technology

DRAM

Organization

# of

DRAM

Devices

# of

Physical

Device

Ranks

# of

Row/Col

Address

Bits

# of

Banks

Inside

DRAM

Page

Size

A

512 MB

512 Mb

64 M x 8

8 1 13/10

8

8K

1 GB

1 Gb

128 M x 8

8 1 14/10

8

8K

2 GB

2 Gb

256M x 8

8 1 15/10

8

8K

B

1 GB

512 Mb

64 M x 8

16 2 13/10

8

8K

2 GB

1 Gb

128 M x 8

16 2 14/10

8

8K

4 GB

2 Gb

256M x 8

16 2 15/10

8

8K

C

256 MB

512 Mb

32M x 16

4 1 12/10

8

8K

512 MB

1 Gb

64 M x 8

4 1 13/10

8

8K

1 GB

2 Gb

128 M x 16

4 1 14/10

8

8K

2 GB

4 Gb1

256M x 16

4 1 15/10

8

8K

D

512 MB

512 Mb

64 M x 8

9 1 13/10

8

8K

1 GB

1 Gb

128 M x 8

9 1 14/10

8

8K

2 GB

2 Gb

256M x 8

9 1 15/10

8

8K

E

1 GB

512 Mb

64 M x 8

18 2 13/10

8

8K

2 GB

1 Gb

128 M x 8

18 2 14/10

8

8K

4 GB

2 Gb

256M x 8

18 2 15/10

8

8K

F

512 MB

512 Mb

32M x 16

8 2 12/10

8

8K

1 GB

1 Gb

64 M x 16

8 2 13/10

8

8K

2 GB

2 Gb

128 M x 16

8 2 14/10

8

8K

4 GB

4 Gb1

256M x 16

8 2 15/10

8

8K

Raw Card D – single rank x8 unbuffered ECC

Raw Card E – dual rank x8 unbuffered ECC

Raw Card F - dual rank x16 unbuffered non-ECC

Table 6. Supported DIMM Module Configurations

Note: 1. 4 Gb technology support is under investigation pending availability of DRAM silicon.

3.7.1.7 Processor PCI Express* Support (PCI Express Graphics)

The processor supports a PCI Express* port, which can be used for PCI Express Graphics

(PEG) or for PCI Express IO. The development kit supports external graphics through this

processor PEG slot, and supports Lane-Reversal of the PEG lanes. However, the motherboard

uses non-reversed routing.

The processor has the capability of using the PCI Express interface in two ways:

1 x16 PCI Express IO (or PEG)

Dev Kit Manual 27 323094

Page 28

STRAP

1

0

CFG0

Single PCI Express*

(default)

PCI Express Bifurcation Enabled

J1D4: IN (1-2)

CFG4

No Display Port connected to

eDP (default)

An External Display Port is

connected

J1D1: IN (1-2)

2 x 8 PCI Express IO (or PEG)

The 2 x 8 slots are supported through the Nowata Add-In Card. Embedded Display Port (eDP)

is supported through the Eaglemont 2 add-in card.

The usage model of the processor‟s PCI Express interface needs to be configured through the

following hardware straps:

Table 7. Hardware Straps for processor PCI Express* Interface Usage

3.7.1.8 Embedded Display Port

Embedded Display Port (eDP) is a feature on Intel® Core™ Processor.

Note: When eDP is enabled, we can only have 1x8 PEG card. eDP lanes are multiplexed over PEG

12:15 lanes from the processor.

1. Insert the PCI graphics add-in-card in the PEG slot (J5C1), not the DDI slot.

2. To enable eDP, you need to “short” the Jumper pins of J1D1 (1-2) on motherboard.

3. Connect the side-band signals on J6D1 on motherboard, via a cable to J3C1 on the PCI

graphics.

4. For the Sideband signals, we have 2 options

5. Connect J6D1 (on motherboard) to J3C1 (on PCI graphics) through a 10-pin cable.

6. Use the BLI connector from LVDS Connector provided to connect it directly at the eDP

Panel.

3.7.1.9 DMI Interface

The Development kit Supports x4 DMI bi-directional lanes between the Processor and Chipset.

The transmissions happen over DMI protocol. Max speed supported is 2.5GT/s. This protocol is

different from the ones on earlier platforms, and has some instructions added.

3.7.1.10 Intel

The development kit supports Intel® FDI, a new interface. On this platform, the GPU is in the

processor and display interfaces are supported through the chipset. The Intel® FDI is a

dedicated link to transmit the display related pixel information over unidirectional 2x4 lane

interfaces. The synchronization signals are directed from chipset to processor.

28 323094 Dev Kit Manual

®

Flexible Display Interface (Intel® FDI)

Page 29

3.7.1.11 Processor Thermals

The processor temperature is communicated to the chipset over the PECI, a single wire

interface. Some important signals are:

1. CATERR# Indicates that the system has experienced a catastrophic error and

cannot continue to operate.

2. PROCHOT# PROCHOT# will go active when the Processor temperature monitoring

sensor detects that the Processor has exceeded the thermal specifications.

3. THERMTRIP# Assertion indicates that the Processor junction temperature has

reached a level beyond which permanent silicon damage may occur.

3.7.1.12 Processor Active Cooling

The development kit supports PWM-based FAN speed control. Fan circuitry is controlled by the

signal CPU_PWM_FAN signal from the EC. A 4-pin header J4C1 is provided to support FAN

speed output measurement for the CPU.

3.7.2 Chipset

The chipset on the development kit is the Intel® 5 Series Chipset. It provides the interface

optimized for the Processor, DMI and a highly integrated I/O hub that provides the interface to

peripherals. The following sections describe the motherboard implementation of the Chipset

features which are listed as below:

8x PCI Express* 2.0 specification ports running at 2.5GT/s

1x PCI Gold-finger slot (for PCI expansion slots)

On-board LAN

6x SATA ports

Support for CRT, LVDS, HDMI, DP and eDP (embedded DP) displays

14xUSB connectors

LPC interface

Serial IrDA port

Support for two SPI flash devices

Subsystem features described in this section refer to socket and connector locations on

motherboard. Socket and connector locations are labeled with a letter-number combination

(for example, the first memory DIMM connector is located at J4V1). Please refer to the

silkscreen labeling on motherboard for socket locations.

3.7.2.1 Chipset PCI Express* Support

The development kit supports five on board PCIe* (x1) slots. The Chipset has a total of 8 PCIe

Base Specification, Rev 2.0 ports running at 2.5GT/s. Of those IO ports 5 have been routed to

x1 connectors on board, 2 to Docking and one to LAN.

Dev Kit Manual 29 323094

Page 30

PCI-E* Port

Default Destination

Optional Destination

1

PCI-E Slot 1 (J6C2)

-

2

PCI-E Slot 2 (J6D2)

(in-line with Slot 1)

3

PCI-E Slot 3 (J7C1)

-

4

PCI-E Slot 4 (J7D2)

-

5

PCI-E Slot 5 (J6C1)

-

6

LAN (EU7M1)

-

7

DOCKING (J9C2)

PCIe SLOT6 (J8C1)

8

DOCKING (J9C2)

-

Intel® QM57

Express

Chipset

GbE LAN

Card

Table 8. PCI Express* Ports

3.7.2.2 PCI Slots

The development kit does not have any PCI slots on the motherboard. Three 5V PCI slots are

supported via PCI Extension Card.

3.7.2.2.1 PCI Gold-Fingers

A gold-finger connector (S9B1) is also supplied on the motherboard, which allows an external

PCI expansion board to connect to motherboard. The PCI expansion board has three

additional PCI slots allowing the user greater expansion. See section Daughter and Plug-in

Cards for more information on the PCI expansion board add-in card.

3.7.2.3 On-Board LAN

The development kit supports 10/100/1000 Mbps Ethernet on board via the Intel® 82577 GbE

PHY. It has a PCI-E and SM-BUS link to the Chipset. Data Transfer happens over PCI-E lanes.

Communication between the LAN Controller and the LAN Connected Device is done through

SMBus whenever the system is in a low power state (Sx). LAN is also supported over

DOCKING.

A block Diagram of the implementation is given in Figure 3.

Figure 3. Block Diagram of On-board LAN Implementations

30 323094 Dev Kit Manual

Page 31

I/O Voltage for the High

Definition Audio

STUFF

NO STUFF

3.3V (Default)

R8R11, R8R9

R8R10, R8E1

SATA Port

Connection Type

Connector

Port 0

Direct Connect

J8J1

Port 1 and Port 2

Cable Connect

J7G2 and J7G1

Port 3 and Port 4

eSATA

J6J1 and J7J1

3.7.2.4 Soft Audio/ Soft Modem

Intel® High Definition Audio functionality (Intel® HD Audio) is enabled through the Mott

Canyon 4 daughter card. The Chipset supports four Intel HD Audio CODECs. All four are routed

to MDC header through resistor stuffing options. By default CODEC 0 and 1 will be connected

to the MDC card. An on-board header is provided at J9E7 and J9E4 for this purpose. No direct

connection is provided for the Intel® High Definition Audio Card on the motherboard; the Mott

Canyon 4 card is required to enable the Intel HD Audio functionality. See Section 5 for more

information on the Mott Canyon 4 card.

The motherboard supports low voltage (LV) high definition I/O CODEC. Resistor stuffing

options are used to select between 3.3V I/O and 1.5VI/O.

Table 9. Selection of I/O Voltage for the Intel® High Definition Audio

3.7.2.5 SATA Storage

Table 10. SATA Ports

These connectors mentioned in Table 10 are for the serial data signals. The motherboard has a

power connector J8J1 to power the serial ATA hard disk drive. A green LED at CR7G1

indicates activity on SATA channel.

The motherboard shares the power connector for both SATA 1 and 2. Due to this only one of

the serial ATA channel (Port1 by default) supports the hot swapping capability. Hot swap on

Port 1 can be used only when the Port 2 is not used. A Y-Power cable needs to be connected

first to the device on Port 1 before connecting the signal cable. When hot swap is not desired,

both Port 1 and Port 2 can be used. A jumper J7H1 is provided to enable hot plug/removal on

port-1.

The eSATA drives should be externally powered. Hence, there is no power supply support for

them on the motherboard.

3.7.2.6 USB Connectors

The Chipset provides a total of 14 USB 2.0/1.1 ports.

Dev Kit Manual 31 323094

Four ports (0, 1, 2, and 3) are routed to a four-stacked USB connector (J3A3) at the

back panel.

Two USB ports (8 and 9) are routed to a RJ45 + Dual USB Connector (J4A1) on the

back of the chassis.

Page 32

USB Port

Panel

Connector

Port 0

Back Panel I/O Connector

J3A3 (4 stacked USB Connector)

Port 1

Back Panel I/O Connector

J3A3 (4 stacked USB Connector)

Port 2

Back Panel I/O Connector

J3A3 (4 stacked USB Connector)

Port 3

Back Panel I/O Connector

J3A3 (4 stacked USB Connector)

Port 4

FPIO

J8H1 (2x5 Connector)

Port 5

FPIO

J8H1 (2x5 Connector)

Port 6

FPIO

J7H3 (2x5 Connector)

Port 7

FPIO

J7H3 (2x5 Connector)

Port 8

Back Panel

J4A1

Port 9

Back Panel

J4A1 (Rework Required: Stuff R8F3 and

R8F5; No Stuff R8F2 and R8F4)

Port 10

FPIO

J7H4 (2x5 Connector)

Port 11

FPIO

J7H4 (2x5 Connector)

Port 12

FPIO

J7H2 (2x5 Connector)

Port 13

FPIO

J7H2 (2x5 Connector)

IO headers are provided for the other 8 USB lanes.

Over current protection has been provided for ports in pairs. Ports (0,1), (1,2)…(12,13) share

the OC Indicators.

Table 11. USB Port Mapping

3.7.2.7 LPC Super I/O (SIO)/ LPC Slot

A SMSC SIO1007 serves as the SIO on the motherboard and is located at U9A1. Shunting the

jumper at J8C3 to the 2-3 positions can disable the SIO by holding it in reset. This allows

other SIO solutions to be tested in the LPC slot at J8F2. A sideband header is provided at

J9G2 for this purpose. This sideband header also has signals for LPC power management.

3.7.2.8 Serial IrDA

The SMSC SIO incorporates a serial port, and IrDA (Infrared), as well as general purpose IOs

(GPIO). The Serial Port connector is provided at J1A2, and the IrDA transceiver is located at

U6A2. The IrDA transceiver on the motherboard supports SIR (slow IR), FIR (Fast IR) and

CIR (Consumer IR). The option to select between these is supported through software and

GPIO pin (IR_MODE) on the SIO.

3.7.2.9 System Management Controller (SMC)/ Keyboard

Controller (KBC)

A Renesas* H8S/2117 (U9H1) serves as both SMC and KBC for the platform. The SMC/KBC

controller supports two PS/2 ports, battery monitoring and charging, wake/runtime SCI

32 323094 Dev Kit Manual

Page 33

MODE

J8D1

J8D3

J8D2

Normal

Operation

1-X

1-X

3-X

1-X

Programming

SPI0

1-2

1-2

3-X

1-2

Programming

SPI1

1-2

1-X

2-3

1-2

events, CPU thermal monitoring/Fan control, GMCH thermal throttling support, LPC docking

support and power sequencing control.

The two PS/2 ports on motherboard are for legacy keyboard and mouse. The keyboard plugs

into the bottom jack and the mouse plugs into the top jack at J1A1. Scan matrix keyboards

can be supported via an optional connector at J9E3.

There is a LPC Slot (J8F2) and LPC Sideband connector (J9G2) on board to connect external

EC for validation purposes. On-board EC has to be disabled by shorting pin 1 and 2 of

connector J9F2 and an external EC has to take care of board power sequencing and thermal

management.

If the intention is just to read thermal information from the Chipset by external EC/Fan

controller, only Chipset SM-Bus signals (SML1_CLK and SML1_DATA) from the LPC sideband

connector can be used without connecting the EC on LPC slot.

For more information on the embedded controller please refer to Intel® Management Engine

(Intel® ME) and Embedded Controller Interaction for Intel® Core™ i7 Processor Based LowPower Platform.

3.7.2.10 SPI

The Serial Peripheral Interface (SPI) on Intel® QM57 Express Chipset can be used to support

two compatible flash devices (U8C1 and U8D1), storing Unified BIOS Code. The SOIC-8

package (U8D2 and U8C2) would support 16 Mb SPI flashes, while the SOIC-16 (U8C1 and

U8D1) package will support 32Mb or higher SPI flash. One can opt to use SPI sockets, if they

wish to. Socket KOZ has been taken into account in the Layout. A Dediprog Header (J8E1) has

been provided for SPI Programming.

Note: Out of the SOIC-8 and SOIC-16 footprints supported on the board only one of these can be

used at a time and on the board. Footprint is arranged one over the other. By default, U8C1

(16Mb on CS#0) and U8D1 (16Mb on CS#1) will be stuffed.

Table 12. Jumper Setting for SPI Programming

3.7.2.11 Clocks

The development kit system clocks are provided by the CK505 (EU6V1) clock synthesizer.

The BCLK frequency can be set using the BSEL Jumpers J6G1, J6F2, J6F3. Unlike previous

platforms it always needs to be 133MHz.

Dev Kit Manual 33 323094

Page 34

CPUSTP# is not supported as the requirement is to have this clock always running during

buffered mode.

Figure 4. BCLK Frequency Select Circuit

The clocks on the motherboard are provided by the chipset which uses four clocks from CK505

as inputs and use these as a reference to generate all the other platform clocks. A general

block diagram is shown in Figure 5.

34 323094 Dev Kit Manual

Page 35

Intel® QM57

Express

Chipset

Figure 5. Platform Clocking Circuit

3.7.2.12 Real Time Clocks (RTC)

An on-board battery at BT5G1 maintains power to the real time clock (RTC) when in a

mechanical off state. A CR2032 battery is installed on the motherboard.

Warning: There is a risk of explosion if the lithium battery is replaced by an incorrect type. Dispose

of used batteries according to the vendor's instructions.

3.7.3 Displays

The development kit supports the following displays:

1. CRT: A right angled CRT connector has been provided on board (J1A2). Optional

routing to the docking connector is supported through a CRT dock switch (U6C1).

2. LVDS: LVDS support is very similar to the one on earlier platforms. Connector is at

J7D3.

3. HDMI: A HDMI connector (J3A2) is added on-board for the first time. HDMI

connectors are also available on PCI graphics add-in-card.

4. DP: A DP connector (J5A1) has been added on board for the first time. DisplayPort

connectors are also available on PCI graphics add-in-Card.

5. eDP: eDP is available on the PCI graphics add-incard. When used for eDP, this card

needs to be inserted in the PCIe Slot (J5C1) and not in the DDI Slot (J8C2). A 2x5

header (J6D1) is provided for the side-band signals (backlight related information and

SMBUS access).

Dev Kit Manual 35 323094

Page 36

Note: A maximum of two displays can be active at a time.

Note: Display connectors DP/HDMI are on Port D of Chipset, Port B and C can be used through PCI

graphics add-in-card.

6. One DP and one HDMI Connector have been provided on board on the motherboard.

Port D of Digital Display Interface on PCH is mapped to on board DP and HDMI connectors.

DP is the default configuration. To select HDMI rework is required on the motherboards.

For HDMI:

a. No stuff – C5A1, C5A2, C5A13, C5A14, C5A5, C5A6, C5A9, C5A10

b. Stuff – C5A3, C5A4, C5A15, C5A16, C5A7, C5A8, C5A11, C5A12 with 0402 0.1 µF

capacitor

c. The same capacitors no stuffed in Step A can be used in Step B

i. R2M2 and R2M5 are the 2.2k pull-ups on SMBus. These should be changed to

4.4 k

ii.

3.7.3.1.1 Digital Display Interface Configuration Modes

1. 3x DisplayPorts

2. 3x HDMI/DVI Ports

3. 2x DP + 1x SDVO

4. 2x DP + 1x HDMI/DVI

5. 2x HDMI/DVI + 1x SDVO

6. 2x HDMI/DVI + 1x DP

7. 1x DP + 1x HDMI/DVI + 1x SDVO

36 323094 Dev Kit Manual

Page 37

Processor

Chipset

DMI

FDI

DPC

Primary Slot

GPIO

from

H8

Secondary Slot

Add-in-Card

DP

MUX

x16 PCIe Connector

x16 PCIe Connector

DPC

1x16 PCIe (0:15)

To

Docking

DPD

HDMI

LVL

TRAN

DP

VGA

Connector

LVDS

Connector

To

Back

Panel

Resistor Strapping

Default Option (Solid Line)

Optional (Dashed Line)