Intel Embedded Intel486, Intel486 Series, IntelDX4, IntelDX2, Ultra-Low Power Intel486 SX Hardware Reference Manual

...Page 1

Embedded Intel486™ Processor

Hardware Reference Manual

Release Date: July 1997

Order Number: 273025-001

The embedded Intel486™ proc essors m ay contain design defects known as errata which may

cause the prod ucts to deviate fr om published sp ecifications. Currently characterized errata are

available on request.

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or oth-

erwise, to any intellectua l proper ty rights is grante d by this docum ent. Exce pt as prov ided in Intel’s Terms and Conditions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications. Intel retains the right to make changes to specifications and product descriptions at any

time, without notice. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing

your product order.

Copies of d ocuments whi ch have a n or deri ng nu mber a nd are re ference d i n this doc umen t, or o ther Inte l lite ratur e, ma y be

obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

or visit Intel’s web site at http:\\www.intel.com

Copyright © INTEL CORPORATION, July 1997

*Third-party brands and names are the property of their respective owners.

Page 3

CONTENTS

CHAPTER 1

GUIDE TO THIS MANUAL

1.1 MANUAL CONTENTS................................................................................................... 1-1

1.2 NOTATIONAL CONVENTIONS..................................................................................... 1-3

1.3 SPECIAL TERMINOLOGY...................... .. .. ............... .. ............. .. .. ............. .... ............. .. 1-4

1.4 ELECTRONIC SUPPORT SYSTEMS.......... .. .... ............. .. ............. .. .. ............... .. .......... 1-5

1.4.1 FaxBa c k S e rv ic e .. ... ....... ....... ... ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... ....... ..1-5

1.4.2 World Wide Web ........................................................................................................1-5

1.5 TECHNI CAL SUPPORT.................... ............... .. ............. .. ............. .. ............... .. .. .......... 1-5

1.6 PRODUCT LIT ERATURE........................ .. .. ............. .... ............. .. .. ............. .. ............... .. 1-6

1.6.1 Related Documents ...................................................................................................1-6

CHAPTER 2

INTRODUCTION

2.1 PROCESSOR FEATURES.......... .... .. ............. .. .. ............. ............... .. .. ............. .. .. .......... 2-2

2.2 Intel486™ PROCESSOR PRODUCT FAMILY.............................................................. 2-4

2.2.1 Operatin g Mod es and Com patibility......................... .......... ................... .......... ...........2-5

2.2.2 Memory Management.......... ................... .......... ................... ........................... .......... .2-5

2.2.3 On-chip Cache ...........................................................................................................2-6

2.2.4 Floating-Point Unit .....................................................................................................2-6

2.2.5 Upgrade Power Down Mode......................................................................................2-7

2.3 SYSTEM COMPONENTS........ ............... .. .. ............. .. .. ............... .. ............. .. .. ............. .. 2-7

2.4 SYSTEM ARCHITECTURE. .. ............. .. ............... .. .. ............. .. .. ............... .. ............. .. .. ... 2-7

2.4.1 Single Processor System...........................................................................................2-8

2.4.2 Loosely Coupled M ulti-Processor System ..................................... ........................... .2-9

2.4.3 External Cache ........................................................................................................2-10

2.5 SYSTEMS APPLICATIONS........................................... .. ............ .. ....................... .. ..... 2-11

2.5.1 Embedded Personal Computers.................. ........................... .. ........................... ....2-12

2.5.2 Embedded Control lers ......... ................... .......... ................... ........................... .........2-12

iii

Page 4

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

CHAPTER 3

INTERNAL ARCHITECTURE

3.1 INSTRUCTION PIPELINING...... ............. .. .. ............... .. ............. .. .. ............... .. ............. .. 3-6

3.2 BUS INTERFACE UNIT................................................................................................. 3-7

3.2.1 Data Transfers ...........................................................................................................3-8

3.2.2 Write Bu f fe rs ............. .. ........ ....... .. ........ .. ....... ........ .. ........ .. ....... ... ....... ....... ... ....... .. ..... 3- 8

3.2.3 Locke d C y cl es...... ... ....... .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... ....... ..3-9

3.2.4 I/O Transfers..............................................................................................................3-9

3.3 CACHE UNIT............................................................................................................... 3-10

3.3.1 Cache Structure .......................................................................................................3-10

3.3.2 Cache Updatin g.... .......... ................... .......... ........................... ................... .......... ....3-12

3.3.3 Cache Replacement ................................................................................................3-12

3.3.4 Cache Configuration ................................................................................................3-12

3.4 INSTRUCTION PREFETCH UNIT................................. .. .. ........................ ........... .. .. .. . 3-13

3.5 INSTRUCTION DECODE UNIT................................................................................... 3-14

3.6 CONTROL UNIT.......................................................................................................... 3-14

3.7 INTEGER (DATAPATH) UNIT. .................................................................................... 3-14

3.8 FLOATING-POINT UNIT ............................................................................................. 3-15

3.8.1 IntelDX2™ and Intel DX4™ Processor On-Chip Flo ati ng-Point Unit. .. .. .......... .........3-15

3.9 SEGME N T A T IO N U NIT........... ....... .. ........ .. ....... ........ .. ........ .. ....... ........ .. ....... ... ....... .... 3-1 5

3.10 PAGIN G U N IT ... ....... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ... ...... 3 -1 6

CHAPTER 4

BUS OPERATION

4.1 DATA TRANSFER MECHANISM.................................................................................. 4-1

4.1.1 Memory and I/O Spaces.............................. ........................... .. ........................... ......4-1

4.1.1.1 Memory and I/O Space Organization........ ........................... .................. ........... ....4-2

4.1.2 Dynamic Data Bus Sizing ..........................................................................................4-3

4.1.3 Interfacing with 8-, 16-, and 32-Bit Memories ............................................................4-5

4.1.4 Dynam i c B u s Sizing Du ri n g C a ch e Li ne F ills ..... ........ ....... .. ........ .. ....... ........ .. ....... ... ..4- 9

4.1.5 Opera n d A lig n ment.......... ... ....... ....... ... ....... .. ........ .. ........ ....... .. ........ .. ....... ........ .. ..... 4 -1 0

4.2 BUS ARBITRATION LOGIC........................................................................................ 4-12

4.3 BUS FUNCTIONAL DESCRIPTION ............................................................................ 4-15

4.3.1 Non-Cacheabl e Non-Burst Single Cycle...................................... .. .................... .. .. ..4-16

4.3.1.1 No Wait States ....................................................................................................4-16

4.3.1.2 Inserting Wait States...........................................................................................4-17

4.3.2 Multiple and Burst Cycle Bus Transfers ...................................................................4-17

4.3.2.1 Burst Cycle s .. .. ....... ... ....... ....... ... ....... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ...4-1 8

4.3.2.2 Terminat ing Multiple and Burst Cyc le Tr ansfers ......... ................... .. ...................4-19

4.3.2.3 Non-Cacheable, Non-Burst, Multiple Cycle Transfers.........................................4-19

4.3.2.4 Non-Cacheable Burst Cycles.................. .................. ........... ........................... .. ..4-20

4.3.3 Cacheable Cycl es............................ ................... .......... ........................... .......... ......4-21

4.3.3.1 Byte Enables during a Cache Line Fill................ .......... ................... ...................4-22

iv

Page 5

CONTENTS

4.3.3.2 Non-Burst Cacheable Cycles..............................................................................4-23

4.3.3.3 Burst Cacheable Cycles......................................................................................4-24

4.3.3.4 Effect of Changing KEN# during a Cache Line Fill.......... .......... ..........................4-25

4.3.4 Burst M o de D et a ils...... ... ....... ... ....... ....... ... ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ...4-2 6

4.3.4.1 Adding Wait States to Burst Cycles ....................................................................4-26

4.3.4.2 Burst and Cache Line Fill Order..........................................................................4-27

4.3.4.3 Interrupted Burst Cycles......................................................................................4-28

4.3.5 8- and 16-Bit Cycles...... ................... ................... .......... ........................... .. ..............4-29

4.3.6 Locke d C y cl es...... ... ....... .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... .......4-3 1

4.3.7 Pseudo-Locked Cycles........ ................... .................. ........... ........................... .........4-32

4.3.7.1 Floating-Point Read and Write Cycle s............................... ................... .......... ....4-33

4.3.8 Invalidate Cycles......................................................................................................4-33

4.3.8.1 Rate of Invalidate Cycles ....................................................................................4-35

4.3.8.2 Running Invalidate Cycles Concurrently with Line Fills.......................................4-35

4.3.9 Bus Ho ld .... ........ .. ....... ... ....... ....... ... ....... ... ....... .. ........ ....... .. ........ .. ....... ........ .. ....... ...4-3 8

4.3.10 Inter ru p t A ck n o wledge .......... ....... ........ .. ....... ... ....... ........ .. ....... ... ....... .. ........ ....... .. ...4 -4 0

4.3.11 Special Bus Cycles ..................................................................................................4-41

4.3.11 .1 HALT In d ic a tio n C yc le...... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ... ....... ....... ...4-4 1

4.3.11.2 Shutdown Indication Cycle..................................................................................4-41

4.3.11.3 Stop Grant Indication Cycle ................................................................................4-41

4.3.12 Bus Cyc le R e st a rt ............... .. ....... ... ....... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ...4-4 3

4.3.13 Bus Sta te s....... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ........ ....... .. ........ .. ....... ... ....... ..... 4 -4 5

4.3.14 Floating-Point Error Handli ng for the IntelDX2™ and IntelDX4™ Processors.........4-46

4.3.14.1 Floating-Point Exceptions ...................................................................................4-46

4.3.15 IntelDX2™ and IntelDX4™ Processors Floating-Point Error Handling

in AT-Compatible Systems.......................................................................................4-47

4.4 ENHANCED BUS MODE OPERATION (WRITE-BACK MODE)

FOR THE WRITE-BACK ENHANCED IntelDX4™ PROCESSOR4-50

4.4.1 Summary of Bus Differences ...................................................................................4-50

4.4.2 Burst C yc le s....... ....... .. ........ .. ....... ........ .. ....... ... ....... ... ....... ....... ... ....... .. ........ ....... .. ...4 -5 0

4.4.2.1 Non-Cacheable Burst Operation........... .. ........................... .. ........................... ....4-51

4.4.2.2 Burst Cycle Signal Protocol.................................................................................4-51

4.4.3 Cache Consistency Cycles ......................................................................................4-52

4.4.3.1 Snoop Collision with a Current Cache Line Operation........................................4-54

4.4.3.2 Snoop under AHOLD.... .. ................... ........................... .. ........................... .........4-54

4.4.3.3 Snoop During Replacement Write-Back..............................................................4-59

4.4.3.4 Snoop under BOFF#............ ................... ........................... .. ........................... ....4-61

4.4.3.5 Snoop under HOLD....... ........... .......... ........................... ................... .......... .........4-64

4.4.3.6 Snoop under HOLD duri ng Re placement Write-Back...................... ...................4-66

4.4.4 Locke d C y cl es...... ... ....... .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... .......4-6 7

4.4.4.1 Snoop/Lo c k C o lli si o n. .. ........ .. ....... ... ....... ....... ... ....... ... ....... .. ........ ....... .. ........ .. ..... 4 -6 8

4.4.5 Flush O p er a tio n ... ....... ... ....... ....... ... ....... ... ....... ....... ... ....... .. ........ .. ....... ........ .. ....... ...4-6 9

4.4.6 Pseudo Locked Cycles .................... ................... .......... ........................... .. ..............4-70

4.4.6.1 Snoop under AHOLD duri ng Pseudo-Locked Cycles......... ................... .......... ....4-70

4.4.6.2 Snoop under Hold dur ing Pseudo-Locked Cycles....... .. ................... ...................4-71

4.4.6.3 Snoop under BOFF# Ove rl aying a Pseudo-Locked Cycle............. ................... ..4-72

v

Page 6

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

CHAPTER 5

MEMORY SUBSYSTEM DESIGN

5.1 INTRODUCTION ........................................................................................................... 5-1

5.2 PROCESSOR AND CACHE FEATURE OVERVIEW.................................................... 5-1

5.2.1 The Burst Cycle .........................................................................................................5-1

5.2.2 The KEN# Input .........................................................................................................5-2

5.2.3 Bus Ch ar a ct e ris tics.......... ... ....... .. ........ ....... .. ........ .. ........ ....... .. ........ .. ....... ... ....... .......5-4

5.2.4 Improving Write Cycle Latency ..................................................................................5-5

5.2.4.1 Interleaving............................................................................................................5-5

5.2.4.2 Write Posti n g........ ....... ... ....... ....... ... ....... .. ........ .. ........ ....... .. ........ .. ....... ........ .. .......5-5

5.2.5 Second-Level Cache............ ................... .......... ................... ........................... .......... .5-6

CHAPTER 6

CACHE SUBSYSTEM

6.1 INTRODUCTION ........................................................................................................... 6-1

6.2 CACHE MEMORY ......................................................................................................... 6-1

6.2.1 What is a Cache?.......................................................................................................6-1

6.2.2 Why Add an External Cache?....................................................................................6-2

6.3 CACHE TRADE-OFFS .................................................................................................. 6-2

6.3.1 Cache Size and Performance....................................................................................6-3

6.3.2 Associat ivity and Performance Issues.................................... .. ........................... ......6-5

6.3.3 Block/ Line Siz e .... ....... ... ....... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ... ....... ....... ...6-1 0

6.3.4 Repla ce m e n t P o lic y ......... ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... .......6-1 1

6.4 UPDA T IN G M A IN ME M O R Y ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... ....... .. ........ ...... 6 -1 1

6.4.1 Write-T hrough and Buffered Write- Through Systems.......... .......... ..........................6-12

6.4.2 Write-Back System ..................................................................................................6-13

6.4.3 Cache Consistency..................................................................................................6-13

6.5 NON-CACHEABLE MEMORY LOCATIONS............................................................... 6-15

6.6 CACHE AND DMA OPERATIONS.............................................................................. 6-16

6.7 CACHE FOR SINGLE VERSUS MULTIPLE PROCESSOR SYSTEMS.................. ... 6-16

6.7.1 Cache in Single Processor Systems........................................................................6-16

6.7.2 Cache in Multiple Processor Systems......................................................................6-16

6.8 AN Inte l486™ PROCESSOR SYSTEM EXAMPLE............ .. .. .. ............... .. ............. .. .. . 6-18

6.8.1 The Memory Hierarchy and Advantages of a Second-level Cache.........................6-19

vi

Page 7

CONTENTS

CHAPTER 7

PERIPHERAL SUBSYSTEM

7.1 PERIPHERAL/PROCESSOR BUS INTERFACE ..................... ............. .. .. ............... .. ... 7-1

7.1.1 Mapping Techniques..................................................................................................7-1

7.1.2 Dynam i c B u s Sizing .... ........ ....... .. ........ .. ....... ........ .. ........ .. ....... ........ .. ....... ... ....... .. ..... 7- 3

7.1.3 Address Decoding for I/O Devices.............................................................................7-5

7.1.3.1 Address Bus Interface...........................................................................................7-6

7.1.3.2 8-Bit I/O Interface ..................................................................................................7-7

7.1.3.3 16-Bit I/O Interface ..............................................................................................7-10

7.1.3.4 32-Bit I/O Interface ..............................................................................................7-14

7.2 BASIC PERIPHERAL SUBSYSTEM........................................................................... 7-17

7.2.1 Bus Control and Ready Logic..................................................................................7-20

7.2.2 Bus Control Signal Description................................................................................7-21

7.2.2.1 Processo r In te rface ... .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... .......7-2 1

7.2.2.2 Wait State Generation Signals............................................................................7-22

7.2.3 Wait State Generator Logic......................................................................................7-22

7.2.4 Address Decoder............................. ................... .......... ........................... ................7-23

7.2.5 Data Transceivers....................................................................................................7-26

7.2.6 Recovery and Bus Contention....... ................... .. ........................... .......... ................7-26

7.2.7 Write Buffers and I/O Cycles....................................................................................7-27

7.2.7.1 Write Buffers and Recovery Time .......................................................................7-27

7.2.8 Non-Cacheability of Memory-Mapped I/O Devices........ ........... .......... ................... ..7-27

7.2.9 Intel486™ Processor On-Chip Cache Consistency.................................................7-28

7.3 I/O CYCLES................................................................................................................. 7-29

7.3.1 Read C yc le T imi n g.. ....... ....... ... ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... .......7-2 9

7.3.2 Write C yc le Ti m in g s .. ....... ... ....... .. ........ ....... .. ........ .. ........ .. ....... ........ .. ....... ... ....... ..... 7 -3 1

7.4 DIFFERENCE BETWEEN THE Intel486™ DX PROCESSOR FAMILY

AND Intel386™ PROCESSORS........ ................................. .. .. .. ....................................7-33

7.5 INTERFACING TO

x

86 PERIPHERALS...................................................................... 7-34

7.5.1 Universal Peripheral Interface..................................................................................7-34

7.5.2 82C59A Interface.....................................................................................................7-35

7.5.2.1 Single Interrupt Controller ...................................................................................7-35

7.5.2.2 Cascaded Interrupt Controllers...........................................................................7-37

7.5.2.3 Handling Mor e than 64 Interrupts................. .. ........................... ..........................7-38

7.6 Intel486™ PROCESSOR LAN CONTROLLER INTERFACE...................................... 7-38

7.6.1 82596CA Coprocessor...... ........................... .................. ........... ........................... .. ..7-38

7.6.1.1 Hardware Interface..............................................................................................7-41

7.6.1.2 Processor and Coprocessor Interaction..............................................................7-44

7.6.1.3 Memory Structure................................................................................................7-46

7.6.1.4 Media Access......................................................................................................7-46

7.6.1.5 Transmit and Receive Operation ........................................................................7-47

7.6.1.6 Bus Throttle Timers.............................................................................................7-47

7.6.1.7 Design Co ns id e r at io n s ... ....... .. ........ .. ....... ........ .. ........ .. ....... ... ....... ....... ... ....... .. ...7 -4 8

7.6.1.8 82596 Co-proc essor Performance...................... ........................... .. ...................7-49

vii

Page 8

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

7.6.2 82557 High Speed LAN Control ler Interface............ .................... .. .................... .. ....7-50

7.6.2.1 82557 Overview ..................... ................... ........................... .......... ................... ..7-50

7.6.2.2 Features and Enhancements ..............................................................................7-51

7.6.2.3 PCI Bus Inte rf a ce . .. ... ....... ....... ... ....... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ...7-5 2

7.6.2.4 82557 Bus Operati ons ....... .. ................... ........................... .. ........................... .. ..7-52

7.6.2.5 Initializing the 82557 ...........................................................................................7-52

7.6.2.6 Control li ng the 82557......... .. ................... ........................... .. ........................... ....7-53

CHAPTER 8

SYSTEM BUS DESIGN

8.1 INTRODUCTION ........................................................................................................... 8-1

8.2 SYSTEM BUS INTERFACE.......................................................................................... 8-1

8.3 EISA BUS: SYSTEM DESIGN EXAMPLE..................................................................... 8-2

8.3.1 Introduction to the EISA Architecture.........................................................................8-2

8.3.2 An Example EISA Chip Set........................................................................................8-3

8.3.3 EBC Host Bus Interface.............................................................................................8-9

8.3.3.1 Clock, Control and Status Interface................................... ................... .......... ......8-9

8.3.3.2 Host Local Memory and I/O Interface .................................................................8-10

8.3.3.3 Host Bus Acquisition and Release ......................................................................8-10

8.3.3.4 Lock, Snoop, and Address Greater than 16 Mbytes...........................................8-10

8.3.4 EISA/ISA Bus Interface to the EBC .........................................................................8-11

8.3.4.1 EBC and EISA Bus Interface Signals..................................................................8-11

8.3.4.2 EBC and ISA Bus Interface Signals....................................................................8-12

8.3.5 EBC and ISP Interface.................. .......... ............ .......... .............................. .. .......... .8-13

8.3.6 EBC and EBB Data and Address Buffer Controls....................................................8-14

8.3.6.1 Functions of the ISP............................................................................................8-16

8.3.6.2 ISP-to-Ho s t In te rface. .. ........ .. ....... ... ....... ....... ... ....... ... ....... ....... ... ....... .. ........ .......8-1 7

8.3.7 ISP-to-EISA Interface...............................................................................................8-17

8.4 PCI BUS: SYSTEM DESIGN EXAMPLE..................................................................... 8-19

8.4.1 Introduction to PCI Architecture ...............................................................................8-19

8.4.2 Example PCI System Design...................................................................................8-19

8.4.3 Host CPU Interface..................................................................................................8-24

8.4.3.1 Host Bus Slave Device........................................................................................8-24

8.4.3.2 L1 Cache Support...............................................................................................8-24

8.4.3.3 Control and Status Interface ...............................................................................8-24

8.4.3.4 PCI Bus Cycles Support......................................................................................8-26

8.4.3.5 Host to PCI Cycles ..............................................................................................8-27

8.4.3.6 Exclusive Cycles .................................................................................................8-27

8.4.3.7 Status and Cont rol Interface ............................... .......... ................... ...................8-28

8.4.4 System Controll er/ISA Bridge Link Inter face..................................... .. .. .......... .........8-29

8.4.4.1 Status and Cont rol Interface ............................... .......... ................... ...................8-29

8.4.5 ISA Inte rface ............... ... ....... ... ....... .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ...8-3 0

8.4.5.1 I/O Recovery Support............... .......... ........................... ................... .......... .........8-30

8.4.5.2 SYSCLK Generation.............. .......... .. .................... .. .................... .. .................... .8-30

8.4.5.3 Data Byte Swapping (ISA Master or DMA to ISA Device)...................................8-30

8.4.5.4 Wait-St ate Generation................... .......... ........................... .......... ................... ....8-31

viii

Page 9

CONTENTS

8.4.5.5 Cycle Shor te n in g.. ....... ........ .. ....... ... ....... .. ........ ....... ... ....... .. ........ ....... .. ........ .. ..... 8 -3 1

8.4.5.6 Status and Cont rol Interface ............................... .......... ................... ...................8-32

8.4.6 DMA Controller ........................................................................................................8-33

8.4.6.1 DMA Status and Control Interface ......................................................................8-34

CHAPTER 9

PERFORMANCE CONSIDERATIONS

9.1 INTRODUCTION ........................................................................................................... 9-1

9.1.1 Memory Performance Factors....................................................................................9-1

9.2 INSTRUCTION EXECUTION PERFORMANCE . .. .. ............. .. .. ............. .. ............... .. .. ... 9-2

9.2.1 Intel 48 6 ™ P ro c e ss o r E x ec u ti on T im e s.. ....... ........ .. ........ .. ....... ... ....... ....... ... ....... .. ..... 9- 2

9.2.2 Application Programs Used in Analysis .....................................................................9-4

9.3 INTERNAL CACHE PERFORMANCE ISSUES ............................................................ 9-4

9.3.1 On-Chip Cache Organization Issues..........................................................................9-4

9.3.2 Performance Effects of the On-Chip Cache...............................................................9-5

9.3.3 Bus Cycle Mix with and without On-Chip Cache....................... .......... .. .................... .9-6

9.4 ON-CHIP WRITE BUFFERS ......................................................................................... 9-7

9.5 EXTE R N A L ME MO R Y C ON S ID E R A T I O N S ........ .. ........ .. ....... ........ .. ....... ... ....... ....... ... . 9-8

9.5.1 Intro ductio n .......... ... ....... ....... ... ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... ....... ..9-8

9.5.2 Wait States in Burst and Non-Burst Modes................................................................9-9

9.5.3 Impact of Wait States on Performance ....................................................................9-10

9.5.4 Bus Utilization and Wait States.................... .. .................... .. .................... .. ..............9-10

9.6 SECOND-LEVEL CACHE PERFORMANCE CONSIDERATIONS............................. 9-11

9.6.1 Advantages of a Second-Level Cache.....................................................................9-11

9.6.2 An Example of a Second- Level Cache .......... ........................... .......... ................... ..9-12

9.6.3 System Performance with a Second-Level Cache...................................................9-12

9.6.4 Impact of Second-Level Cache on Bus Utilization...................................................9-13

9.7 DRAM DESIGN TECHNIQUES............... .. .. ............. .. .. ............. .... ............. .. .. ............. 9-14

9.8 EXTENDED DATA OUTPUT RAM (EDO RAM).......................................................... 9-14

9.8.1 Interleaving ..............................................................................................................9-14

9.8.2 Impact of Performance for Posted Write Cycles ......................................................9-15

9.9 FLOATING-POINT PERFORMANCE.......................................................................... 9-16

9.9.1 Floating-Point Execution Sequences .......................................................................9-16

9.9.2 Performance of the Floating-Point Unit....................................................................9-17

ix

Page 10

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

CHAPTER 10

PHYSICAL DESIGN AND SYSTEM DEBUGGING

10.1 GENERAL SYSTEM GUIDELINES............................................................................. 10-1

10.2 POWER DISSIPATION AND DISTRIBUTION............................................................. 10-1

10.2.1 Power and Ground Planes............ .............................. .. .................... .. .. .......... .........10-2

10.3 HIGH-FREQUENCY DESIGN CONSIDERATIONS.................................................... 10-9

10.3.1 Transmission Line Effects........................................................................................10-9

10.3.1.1 Transmission Line Types ..................................................................................10-10

10.3.1.2 Micro-Strip Lines ...............................................................................................10-10

10.3.1.3 Strip Lines .........................................................................................................10-11

10.3.2 Impedance Mismatch........... ................. ................. ........ ......... .. ........ ......... ........ .. ..10-12

10.3.2.1 Impedance Matching.......... ........... ........................... .......... ................... ............10-18

10.3.2 .2 Daisy C h ai n in g ... ....... .. ........ .. ....... ........ .. ....... ... ....... ... ....... ....... ... ....... .. ........ ..... 1 0 -2 4

10.3.2.3 90-Degree Angles .............................................................................................10-24

10.3.2.4 Vias (Feed-Through Connections )............ .......... ........................... .. .................10-25

10.3.3 Interference............................................................................................................10-25

10.3.3.1 Electromagnetic Interference (EMI)...................................................................10-25

10.3.3.2 Minimizing Electromagnetic Interference ..........................................................10-26

10.3.3.3 Electrostatic Interference ..................................................................................10-28

10.3.4 Propagation Delay ....................................... ........................... .. ........................... ..10- 29

10.4 LATCH-UP................................................................................................................. 10-30

10.5 CLOCK CONSIDERATIONS ..................................................................................... 10-30

10.5.1 Requirements.........................................................................................................10-31

10.5.2 Routing...................................................................................................................10-31

10.6 THERMAL CHARACTERISTICS............................................................................... 10-33

10.7 DERATING CURVE AND ITS EFFECTS .................................................................. 10-36

10.8 BUILDING AND DEBUGGING THE Intel486™ PROCESSOR-BASED SYSTEM.... 10-37

10.8.1 Debugging Features of the Intel486™ Processor............................... ...................10-39

10.8.2 Breakpoint Instruction ............................................................................................10-39

10.8.3 Single-Step T ra p .. ... ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... ....... ....... ... ..... 1 0 -3 9

10.8.4 Debug Registers ....................................................................................................10-39

10.8.5 Debug Control Register (DR7)...............................................................................10-42

10.8.6 Debugging Overview......... ........................... ........................... .. ........................... ..10- 43

INDEX

x

Page 11

CONTENTS

FIGURES

Figure Page

2-1 A Typical In tel486™ Processor System .......................................................................2-8

2-2 Single-Processor System.............................................................................................2-9

2-3 Loosely Coupled M ulti-processor System............................ .. ........................... .........2-10

2-4 External Cache...........................................................................................................2-11

2-5 Embedded Personal Computer and Embedded Contr oller Example.........................2-12

3-1 IntelDX2™ and IntelD X4™ Processors Block Diagram.............. ............ .......... ...........3-2

3-2 Intel486™ SX Processor Block Diagram......................................................................3-3

3-3 Ultra-Low Power Inte l486™ SX and Ultra-Low Power Intel486 GX Processors

Block D ia g ra m . .. ........ .. ....... ... ....... ....... ... ....... .. ........ .. ........ ....... .. ........ .. ....... ........ .. .......3-4

3-4 Internal Pipelining.........................................................................................................3-7

3-5 Cache Organization....................................................................................................3-11

3-6 Segmentati on and Paging Address Format s.......................... .......... ..........................3-16

3-7 Translation Lookaside Buffer..... ........... .......... ........................... .. ........................... ....3-17

4-1 Physical Memor y and I/O Spaces ......... ........... .......... ........................... ................... ....4-2

4-2 Physical Memor y and I/O Space Organization....... ................... ................... .......... ......4-3

4-3 Intel 48 6 ™ P ro c e ss o r w it h 3 2- B it Me mo ry..... .. ... ....... ........ .. ....... ... ....... ....... ... ....... .. ..... 4- 5

4-4 Addressing 16- and 8-Bit Memories .............................................................................4-6

4-5 Logic to Generate A1, BHE# and BLE# for 16-Bit Buses.............................................4-8

4-6 Data Bus Interface to 16- and 8-Bit Memorie s..................... ................... .....................4-9

4-7 Single Master Intel486™ Processor System..............................................................4-12

4-8 Single Intel486™ Processor with DMA.......................................................................4-13

4-9 Single Intel 486™ Processor with Mult iple Secondary Masters........... ................... ....4-14

4-10 Basic 2-2 Bus Cycle ...................................................................................................4-16

4-11 Basic 3-3 Bus Cycle ...................................................................................................4-17

4-12 Non-Cacheable, Non-Burst, Multiple-Cycle Transfers................................................4-20

4-13 Non-Cacheable Burst Cycle................. .......... ........................... ................... .......... ....4-21

4-14 Non-Burst, Cacheable Cycles ....................................................................................4-23

4-15 Burst Cacheable Cycle ...............................................................................................4-24

4-16 Effect of Changing KEN# ...........................................................................................4-25

4-17 Slow Burst Cycle ........................................................................................................4-26

4-18 Burst Cycle Showing Order of Addresses ..................................................................4-27

4-19 Interrupted Burst Cycle...............................................................................................4-28

4-20 Interrupted Burst Cycle with Non-Obvious Order of Addresses .................................4-29

4-21 8-Bit Bus Size Cycle...................................................................................................4-30

4-22 Burst Write as a Result of BS8# or BS16#.................................................................4-31

4-23 Locke d B u s Cycle... ... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ... ....... ....... ... ....... ... .......4-3 2

4-24 Pseudo Lock Timing....................................... .................. ........... ........................... .. ..4-33

4-25 Fast Internal Cache Invalidation Cycle.......................................................................4-34

4-26 Typical Internal Cache Invalidation Cycle...................................................................4-35

4-27 System with Second-Level Cache..............................................................................4-36

4-28 Cache Invalidation Cycle Concurrent with Line Fill ....................................................4-37

4-29 HOLD/HLDA Cycles...................................................................................................4-38

4-30 HOLD Request Acknowledged during BOFF#......... .. .................... .. .................... .. ....4-39

4-31 Inter ru p t A ck n o wledge C ycles.... .. ....... ... ....... .. ........ ....... ... ....... .. ........ ....... .. ........ .. ..... 4 -4 0

xi

Page 12

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

FIGURES

Figure Page

4-32 Stop Grant Bus Cycle.................................................................................................4-42

4-33 Restarted Read Cycle ................................................................................................4-43

4-34 Restarted Write Cycle.................................................................................................4-44

4-35 Bus Sta te D ia g ra m .... ....... ....... ... ....... .. ........ ....... .. ........ .. ....... ... ....... ....... ... ....... ... .......4-4 5

4-36 DOS-Compatible Numerics Error Circuit....................................................................4-49

4-37 Basic Burst Read Cycle..............................................................................................4-51

4-38 Snoop Cycle Invalidating a Modified Line...................................................................4-55

4-39 Snoop Cycle Overlaying a Line-Fill Cycle ..................................................................4-57

4-40 Snoop Cycle Overlaying a Non-Burst Cycle...............................................................4-58

4-41 Snoop to the Line that is Being Replaced ..................................................................4-60

4-42 Snoop under BOFF # duri ng a Cache Line-Fill Cycl e............. ........................... .........4-62

4-43 Snoop under BOFF # to the Line that is Being Replaced............................ .. ..............4-63

4-44 Snoop under HOLD duri ng Line Fill.................. .............................. .. .......... .. ..............4-65

4-45 Snoop using HOLD duri ng a Non-Cacheable, Non-Burstable Code Prefetch............4-66

4-46 Locke d C y cl es (B a c k- to -Back ) ... .. .. ........ ....... .. ........ .. ........ ....... .. ........ .. ....... ... ....... ..... 4 -6 8

4-47 Snoop Cycle Overlaying a Locked Cycle ...................................................................4-69

4-48 Flush C yc le...... .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ... ....... ....... ... ....... .. ........ .......4-7 0

4-49 Snoop under AHOLD Overlaying Pseudo-Lo cked Cycle .......... .. ........................... .. ..4-71

4-50 Snoop under HOLD Overlaying Pseudo-Lo cked Cycle............. .. ........................... ....4-72

4-51 Snoop under BOFF # Overlaying a Pseudo-Locked Cycle.................... ................... ..4-73

5-1 Typica l B u rs t C yc le........... .. ........ .. ....... ... ....... ....... ... ....... ... ....... ....... ... ....... .. ........ ....... ..5-3

5-2 Burst Cycle: KEN# Normally Active..............................................................................5-4

5-3 Intel386™ Processor Bus Cycle Mix/Intel486™ Processor Bus Cycle Mix ..................5-5

6-1 A Fully Associative Cache Organization.......................................................................6-5

6-2 Direct Mappe d Cache O rganization............. ................... .......... ................... .......... ......6-7

6-3 Two-Way Set Associative Cache Organization............................................................6-8

6-4 Sector Buffer Cache Organization................................................................................6-9

6-5 The Cache Data Organi zation for the Intel486™ Processor’s On-Chip Cache...... .. ..6-10

6-6 Stale Data Problem in the Cache/Main Memory ........................................................6-12

6-7 Bus Watching/Snooping for Shared Memory Systems...............................................6-14

6-8 Hardware Transparency.............................................................................................6-14

6-9 Non-Cacheable Share Memory........................... .. ........................... .......... ................6-15

6-10 Intel486™ Processor System Arbitration....................................................................6-17

6-11 A Typical Intel486™ Processor System.....................................................................6-18

6-12 Intel486™ Processor System Memory Hierarchy.......................................................6-19

7-1 Mappi n g S ch e me ........ .. ........ .. ....... ........ .. ....... ... ....... ........ .. ....... ... ....... ....... ... ....... .. ..... 7- 2

7-2 Intel486™ Processor Interface to I/O Devices .............................................................7-6

7-3 Logic to Generate A1, BHE# and BLE# for 16-Bit Buses.............................................7-7

7-4 Intel486™ Processor Interface to 8-Bit Device.............................................................7-8

7-5 Bus Sw app ing 16- B it In te r fa ce............ ........ .. ....... ... ....... ... ....... ....... ... ....... .. ........ .......7-1 1

7-6 Bus Swapping and Low Addre ss Bit Ge nerating Control Logi c.................. ................7-14

7-7 32-Bit I/O Interface .....................................................................................................7-15

7-8 System Block Diagram ...............................................................................................7-17

7-9 Basic I/O Interface Block Diagram..............................................................................7-19

xii

Page 13

CONTENTS

FIGURES

Figure Page

7-10 PLD Equations f or Basi c I/O Control Logic.......... .. ........................... .................. ........7-23

7-11 I/O Address Example .................................................................................................7-24

7-12 Internal Logic and Truth Table of 74S138..................................................................7-25

7-13 I/O Read Timing Analysis.......... .. ................... ........................... .. ........................... ....7-29

7-14 I/O Read Timing s........... ........................... .......... ................... .................. ..................7-30

7-15 I/O Write Cycle Timings..............................................................................................7-31

7-16 I/O Write Cycle Timing Analysis .................................................................................7-32

7-17 Posted Write Circuit....................................................................................................7-32

7-18 Timing of a Posted Write ............................................................................................7-33

7-19 Intel486™ Processor Interface to the 82C59A...........................................................7-36

7-20 Casca d ed In te r ru p t C on t ro ller ........... .. ........ .. ....... ........ .. ....... ... ....... ... ....... ....... ... .......7-3 7

7-21 82596CA Coprocessor Block Diagram........... .................... .. .................... .. .......... .. .. ..7-40

7-22 82596CA Applic ation Example........... .. .................... .. .................... .. .................... .. ....7-41

7-23 82596-to- P rocessor Interfacing........................... .. ........................... .......... ................7-44

7-24 82596 Shared Me mory.............................. .......... ................... .......... ..........................7-45

7-25 Bus Throttle Timers ....................................................................................................7-48

7-26 596RESET, CA, and PORT# Equations.....................................................................7-49

7-27 Intel 82557 Block Diagram .........................................................................................7-52

8-1 Intel 48 6 ™ P ro c e ss o r S y st em............ .. ........ ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ..8- 4

8-2 Block Diagram of EISA Bus Controller (EBC) ..............................................................8-6

8-3 Block Diagram of Integrated System Peripheral (ISP).................................................8-8

8-4 EBB Byte Transfer.................. .. .................... .. .................... .. .......... .. .................... .. .. ..8-15

8-5 Example System Block Diagram ................................................................................8-20

8-6 System Controller Block Diagram...............................................................................8-22

8-7 ISA Bridge Block Diagram............... .............................. .. .................... .. .. .......... .........8-23

8-8 Internal DMA Controller..............................................................................................8-34

9-1 Cache Hit Rate for Various Programs ..........................................................................9-6

9-2 Intel486™ Processor Bus Cycle Mix with On-Chip Cache...........................................9-7

9-3 Effect of Wait States on Performance ........................................................................9-10

9-4 Effect of External Bus Utilization versus Wait States .................................................9-11

9-5 L2 Cache Performance Data with One Write Buffer...................................................9-13

9-6 Performance in Interleaved and Non-Interleaved Systems........................................9-15

9-7 Performance in Systems with and without Posted Writes..........................................9-16

10-1 Reduction in Impedance.............................................................................................10-3

10-2 Typical Power and Ground Trace Layout for Double-Layer Boards.................. .........10-5

10-3 Decoupli ng Capacitors........ ........................... .. ........................... ........................... .. ..10-6

10-4 Circuit without Decoupling..........................................................................................10-7

10-5 Decoupling Chip Capacitors.......................................................................................10-8

10-6 Decoupli ng Leaded Capacitors....................................... .......... ................... .......... ....10-9

10-7 Micro-Strip Lines ......................................................................................................10-11

10-8 Strip Lines ................................................................................................................10-12

10-9 Overshoot and Undershoot Effects..........................................................................10-13

10-10 Loaded Transmission Li ne.......... .. ................... ........................... .......... ...................10-13

10-11 Lattice Diagram ........................................................................................................10-16

xiii

Page 14

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

FIGURES

Figure Page

10-12 Lattice Diagram Example .........................................................................................10-17

10-13 Series Termination ...................................................................................................10-19

10-14 Parallel Termination .................................................................................................10-19

10-15 Thevenin’s Equivalent Circuit...................................................................................10-20

10-16 AC Termination ........................................................................................................10-21

10-17 Active Termination....................................................................................................10-22

10-18 Impedance Mismatch Example.......... ................... .......... ........................... ..............10-23

10-19 Use of Series Termination to Avoid Impedance Mismatch.......................................10-24

10-20 “Daisy” Ch ai n in g... ....... .. ........ ....... .. ........ .. ....... ........ .. ........ .. ....... ... ....... ....... ... ....... .. .10-2 4

10-21 Avoiding 90-Degree Angles......................................................................................10-25

10-22 Typical Lay o u t ........... ....... .. ........ .. ....... ........ .. ....... ... ....... ... ....... ....... ... ....... .. ........ ..... 1 0 -2 6

10-23 Removing Closed Loop Signal Paths.......................................................................10-28

10-24 Typical Clo c k T imin gs.. .. ... ....... ....... ... ....... ... ....... .. ........ ....... .. ........ .. ....... ........ .. ....... . 1 0-31

10-25 Clock Routin g .. ....... ... ....... ....... ... ....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... ..... 1 0 -3 2

10-26 Star Connec tion.... ....... .. ........ .. ....... ........ .. ....... ... ....... ... ....... ....... ... ....... .. ........ ....... .. .10-3 2

10-27 Typical Heat Sinks....................................................................................................10-35

10-28 Heat Sink Dimensions..............................................................................................10-36

10-29 Derating Curves for the Intel486™ Processor..........................................................10-37

10-30 Typical Intel486™ Processor-Based System ...........................................................10-38

10-31 Debug Registers.......................................................................................................10-41

xiv

Page 15

CONTENTS

TABLES

Table Page

2-1 Product Options... .. ................... .......... ................... ........................... .......... ..................2-4

3-1 Intel486™ Processor Family Functional Units..............................................................3-1

3-2 Cache Configuration Options .....................................................................................3-13

4-1 Byte Enables and Associated Data and Operand Bytes..............................................4-1

4-2 Generating A31–A0 from BE3#–BE0# and A31–A2........ .. .......... .. .. .......... .. ................4-2

4-3 Next Byte Enable Valu es for BS

4-4 Data Pins Read with Different Bus Sizes .....................................................................4-5

4-5 Generati ng A1, BHE# and BLE# fo r Addressing 16-Bit Devi ces...... ........................... .4-7

4-6 Generating A0, A1 and BHE# from the In tel 486™ Processor Byte Enables..............4-10

4-7 Transfer Bus Cy cles for Bytes, Words and Dwords.................... .......... ................... ..4-11

4-8 Burst Order (Both Read and Write Bursts).................................................................4-27

4-9 Special Bus Cycle Encoding ......................................................................................4-42

4-10 Bus Sta te D es c ri pt io n....... .. ........ .. ....... ........ .. ....... ... ....... ....... ... ....... ... ....... ....... ... .......4-4 6

4-11 Snoop Cycles under AHOLD, BOFF#, or HOLD......................... .................... .. .........4-52

4-12 Various Scenarios of a Snoop Write-Back Cycle Colliding with

an On-Going Cache Fill or Replacement Cycle..........................................................4-54

5-1 Access Length of Typical CPU Functions ....................................................................5-2

5-2 Clock Latencies for DRAM Functions...........................................................................5-6

6-1 Level-1 Cache Hit Rates ..............................................................................................6-3

7-1 Next Byte-Enable Values for the BS

7-2 Valid Data Lines for Valid Byte Enable Combinations..................................................7-5

7-3 PLD Input Signals....... .. .......... .. .................... .. .. .......... ............ .......... ............ .......... .. ....7-9

7-4 Equations .....................................................................................................................7-9

7-5 32-Bit to 8-Bit Steering .................................................................................................7-9

7-6 PLD Input Signals....... .. .......... .. .................... .. .. .......... ............ .......... ............ .......... .. ..7-12

7-7 PLD Output Signals...... .. .................... .. .................... .. .......... .. .................... .. ..............7-12

7-8 Equation .....................................................................................................................7-12

7-9 32-Bit to 16-Bit Bus Swapping Logic Truth Table.......................................................7-12

7-10 32-Bit to 32-Bit Bus Swapping Logic Truth Table.......................................................7-16

7-11 Bus Cyc le D e fin it io n s ......... ........ .. ....... ... ....... ....... ... ....... ... ....... ....... ... ....... .. ........ .. ..... 7 -2 1

7-12 82596 Signals...... ........... ........................... .......... ................... .......... ..........................7-42

7-13 82596 Bus Bandwidt h Uti li zation........... ......................................... .. .................... .. .. ..7-50

8-1 AEN

8-2 Supported PCI Bus Commands .................................................................................8-27

8-3 DMA Data Swap.........................................................................................................8-31

8-4 16-bit Master to 8-bit Slave Data Swap......................................................................8-31

9-1 Typical Instruction Mix and Execution Times for the Intel486™ Processor..................9-3

9-2 Programs Used ............................................................................................................9-6

9-3 Floating-Point Instruction Execution...........................................................................9-17

10-1 Comparison of Various Termination Techniques....... .................. ........... .................10-22

10-2 LEN

x

Decode Table...................................................................................................8-11

i

Fields...............................................................................................................10-42

x

# Cycles ...................................................................4-4

x

# Cycles.............................................................7-4

xv

Page 16

Page 17

GUIDE TO THIS

MANUAL

Chapter Contents

1.1 Manual Contents ........... .. ... ....... .. ........ .. ....... ... ....... ... ....... .. ...1- 1

1.2 Text C on v en t io n s ....... ... ....... .. ........ .. ....... ... ....... ... ....... .. ... .....1-3

1.3 Special Terminology .............................................................1-4

1

1.4 Elect ro n i c S u ppo r t S y st ems ........ ... ....... .. ........ .. ........ .. .. ........1-5

1.5 Techn i cal Supp o rt .... .. ........ .. .. ........ .. ....... ... ....... ... ....... .. ........1-5

1.6 Product Literature .................................................................1-6

Page 18

Page 19

CHAPTER 1

GUIDE TO THIS MANUAL

This manual describes the embedded Intel486™ processors. It is intended for use by hardware

designers familiar with the principles of embedded microprocessors and with the Intel486 processor archit ecture.

1.1 MANUAL CONTENTS

This manual contains 10 chapters and an index. This section summarizes the contents of the remaining chapters. The remainder of this chapter describes conventions and special terminology

used throughout the manual and provides references to related documentat ion.

Chapter 2:

“Introduction”

Chapter 3:

“Internal

Architecture”

Chapter 4:

“Bus O p erat ion”

Chapter 5:

“Memory Subsystem

Design”

Chapter 6:

“Cache Subsystem”

This chapter provides an overview of the current embedded Intel486

processor family, including product features, system components,

system architecture, and applications. This chapter also lists product

frequency, voltage and package offerings.

This chapter de s cribes the Intel486 processor internal architecture, wit h

a descripti on of the processor’s functi onal units.

This chapter describes the features of the processor bus, including bus

cycle handling, interrupt and reset signals, cache control, and floatingpoint error control.

This chapter designing a memory subsystem that supports features of

the Intel4 86 processor such as burst cycles and cache. This chapter also

discusses using write-posting and interleaving to reduce bus cycle

latency.

This chapter di scusses cache theory and the impact of caches on performance. This cha pter de tails di fferent cache con figur at ions, inc lud ing direct-mapped, set associative, and fully associative. In addition, writeback and write-through methods for updating main memory are described.

1-1

Page 20

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

Chapter 7:

“Peripheral

Subsystem”

Chapter 8:

“System Bus Design”

Chapter 9:

“Performance

Considerations”

Chapter 10:

“Physical Design and

System Debugging”

This chapter describes the connection of peripheral devices to the

Intel486 processor bus. Design techniques are discussed for interfacing

a variety of devices, including a LAN controller and an interrupt

controller.

This chapter provides an overview of s ystem bus design considerations,

includi ng implementing of the EISA and PCI s yst em buses.

This chapter focuses on the system parameters that affect performance.

External (L2) caches are also examined as a means of improving

memory system performance.

The higher clock speeds of Intel486 processor systems require design

guidelines. This chapter outlines basic design considerations, including

power and ground, thermal environment, and system debugging issues.

1-2

Page 21

GUIDE TO THIS MANUAL

1.2 TEXT CONVENTIONS

The following notations are used throughout this manual.

# The pound symbol (#) appe nded to a signal name i ndicates that the signal

is ac ti v e lo w .

Variables Variables are shown in italics. Variables must be replaced with correct

values.

New Terms New terms are shown in italics. See the Glossary for a brief definition of

commonly u sed term s.

Instructions Instruction mnemonics are shown in uppercase. When you are

programming, instructions are not case-sensitive. You may use either

upper- or lowercase.

Numbers Hexadecimal numbers are represented by a string of hexadecimal digits

followed by the character H. A zero prefix is added to numbers that begin

with A through F. (For example, FF is shown as 0FFH.) Decimal and

binary numbers are represented by their customary notations. (That is,

255 is a decimal number and 1111 1111 is a binary number. In some

cases, the letter B is adde d for clarity.)

Units of Measure The following abbreviations are used to represent units of measure:

Aamps, amperes

Gbyte gigabytes

Kbyte kilobytes

KΩ kilo-ohms

mA milliamps, milliamperes

Mbyte megabytes

MHz megahertz

ms milliseconds

mW milliwatts

ns nanoseconds

pF picofarads

Wwatts

V volts

µA micro am p s , mi cr o amperes

µF microfarads

µs microseconds

µWmicrowatts

1-3

Page 22

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

Register Bits When the text refers to more that one bit, the range of bits is represented

by the highest and lowest numbered bits, separated by a long dash

(example: A15–A8). The first bit shown (15 in the example) is the mostsignificant bit and the second bit shown (8) is the least-si gnificant bit.

Register Names Register names are shown in uppercase. If a register name contains a

lowercase italic character, it represents more than one register. For

example, PnCFG represent s three registers: P1CFG, P2CFG, a nd P3CFG.

Signal Names Signal names are shown in uppercase. When several signals share a

common name, an individual signal is represented by the signal name

followed by a number, while the group is represented by the signal name

followed by a variable (n). For exa mp l e, t h e l o w er c hi p -s el ec t s ign al s a r e

named CS0#, CS1#, CS2#, and so on; they are collectively called CSn#.

A pound symbol (#) appended to a signal name identifies an active-low

signal. Port pins are represented by the port abbreviation, a period, and

the pin number (e. g., P1.0, P1.1).

1.3 SPECIAL TERMINOLOGY

The following terms have special meanings in this manual.

Assert and Deasse rt The terms assert and deassert refer to the acts of making a signal

active and ina ctive, respectively. The active pol arity (high/low) is

defined b y the signal name. Active-low signals are designated by the

pound symbol (#) suffix; active-high signals have no suffix. To

assert RD# is to dr ive it low; to ass ert HOLD is to drive it high; to

deas sert RD # is to dr ive it hi gh ; to dea ss ert HO L D is to dr ive it lo w .

DOS I/O Address Peripherals that are compatible with PC/AT system architecture can

be mapped into DOS (or PC/AT) ad dres ses 0H–03FFH. In this

manual, the ter ms DOS address and PC/AT address are s ynonymous.

Expanded I/O Address All peripheral registers reside at I/O addresses 0F000H–0FFFFH.

PC/AT-compat ible integrated peripherals can also be mappe d into

DOS (or PC/AT) address space (0H–03FFH).

PC/AT Address In tegrated pe rip h er als tha t ar e co mpati b le wi t h P C /A T sy st em

architect ure c an be mapped into PC/AT (or DOS) addresses 0H–

03FFH. In th is manual, the terms DOS address and PC/AT addres s

are synonymous.

Set and Clear The terms set and clear refer to the value of a bit or the ac t of giving

it a value. If a bit is set, its value is “1”; setting a bi t g i v es it a “1”

value. If a bit is clear, its value is “0” ; clearing a bit give s it a “0”

value.

1-4

Page 23

GUIDE TO THIS MANUAL

1.4 ELECTRONIC SUPPORT SYSTEMS

Intel’s FaxBac k* service provides up-to-date technic al information. Intel also offers a variety of

information on th e World Wide Web. These syst ems are availabl e 24 hours a day, 7 days a week,

providing technical information whenever you need it.

1.4.1 FaxBack Service

FaxBack is an on -demand publ ishi ng s ystem t hat sends document s to yo ur fax machine. You can

get product announcements, change notifications, product literature, device characteristics, design recommendations, and quality and reliability information from FaxBack 24 hours a day, 7

days a week.

1-800-525-3019 ( US or Canada)

+44-1793-496646 (Europe)

+65-256-5350 (Singapore)

+852-2-844-4448 (Hong Kong)

+886-2-514-0815 (Tai wan)

+822-767-2594 (Korea)

+61-2-975-3922 (Australia)

1-503-264-6835 (Worldwide)

Think of the FaxBack service as a library of technical documents that you can access with your

phone. Just dia l th e tel ephone nu mber a nd resp ond to the sys tem prompt s. Aft er you s elect a d ocument, the system sends a copy to your fax machine.

1.4.2 World W i de Web

Intel offers a variety of information through the World Wide Web (http://www.intel.com/).

1.5 TECHNICAL SUPPORT

In the U.S. and Canada , te chnical support re presentative s ar e available to answe r your questions

between 5 a. m. and 5 p .m. PST. You can also fax your que stion s to u s. (Pl ease i ncl ude your voic e

telephone number and indicate whether you prefer a response by phone or by fax). Outside the

U.S. and Canada, pleas e contact your local distributor.

1-800-628-8686 U.S. and Canada

916-356-7599 U.S. and Canada

916-356-6100 (fax) U.S. and Canada

1-5

Page 24

EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

1.6 P RO DUCT LITERATURE

You can order product literature from the following Intel literature centers.

1-800-548-4725 U.S. and Canada

708-296-9333 U.S. (from overseas)

44(0)1793-431155 Europe (U.K.)

44(0)1793-421333 Germany

44(0)1793-421777 France

81(0)120-47-88-32 Japan (fax only)

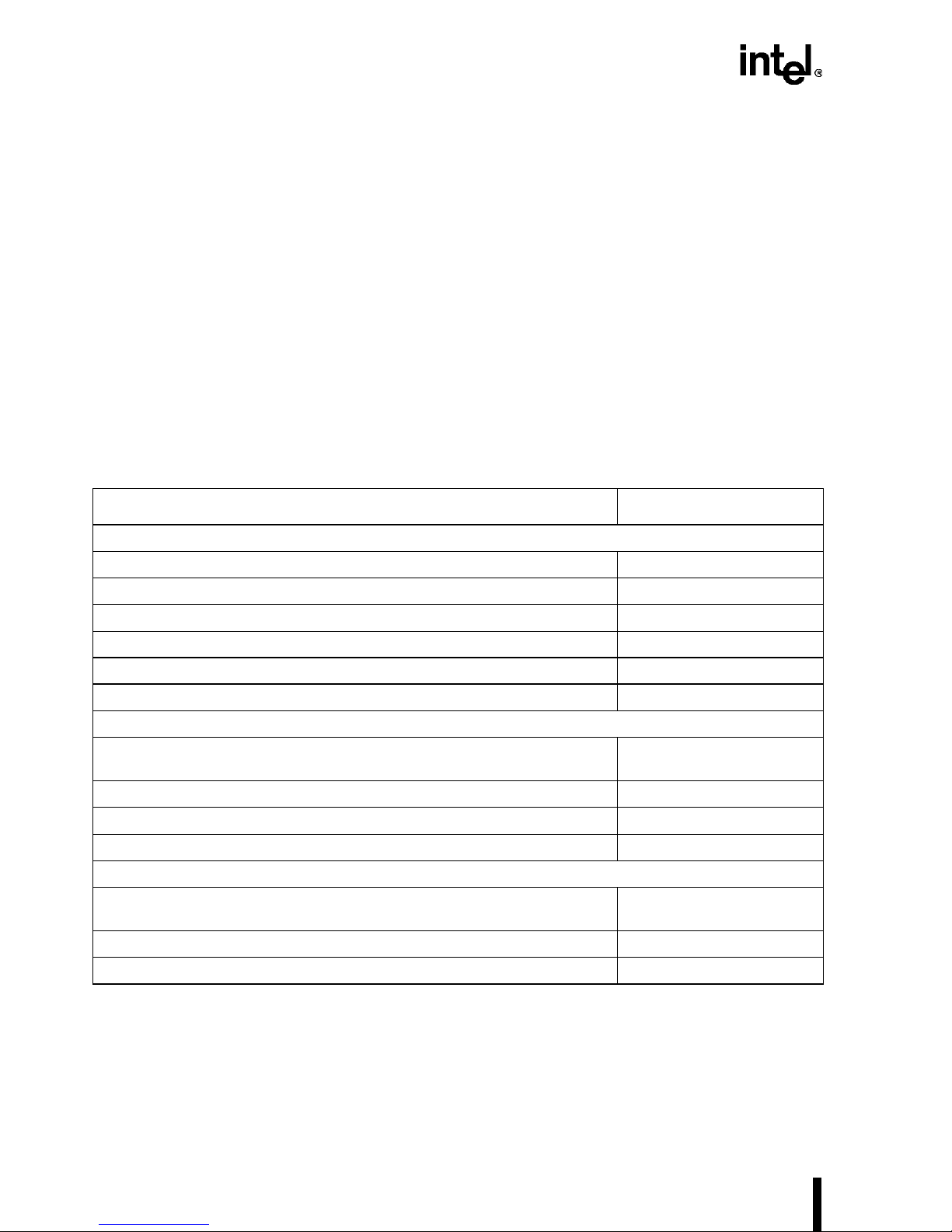

1.6.1 Related Documents

The following Intel documents contain additional information on designing systems that incorporate the Intel 486 processors.

Intel Document Name Intel Order Number

Datasheets

Embedded Intel486™ SX Processor

Embedded IntelDX2™ Processor

Embedd ed Ultra-L ow Power Inte l4 86 ™ S X Pr oc es s or

Embedded Ultra Low-Power Intel486™ GX Processor

Embedded Write-Back Enhanced IntelDX4™ Processor

MultiProcessor Specification

Intel Architecture Software Deve loper's Manual

Embedded Intel486™ Process or Family Develo per’s Manual

Ultra-Low Power Int el486™ SX Processor Evaluation Board Manual

Intel486™ Processor Family Programmer’s Reference Manual

AP-505–Picking Up the Pace: Designing the IntelDX4™ Processor into

Intel486™ Processo r-Base d Designs

Intel486™ Microp rocess or Performa nc e Brief

IntelDX4™ Processor Performance Brief

datasheet 272769-001

datasheet 272770-001

datas heet 27273 1- 0 01

datasheet 272755-001

datasheet 272771-001

Manuals

, Volu mes 1 and 2 243190-001

Application Notes/Performance Briefs

242016-005

243191-001

273021.001

272815-001

240486-003

242034-001

241254-002

242446-001

1-6

Page 25

GUIDE TO THIS MANUAL

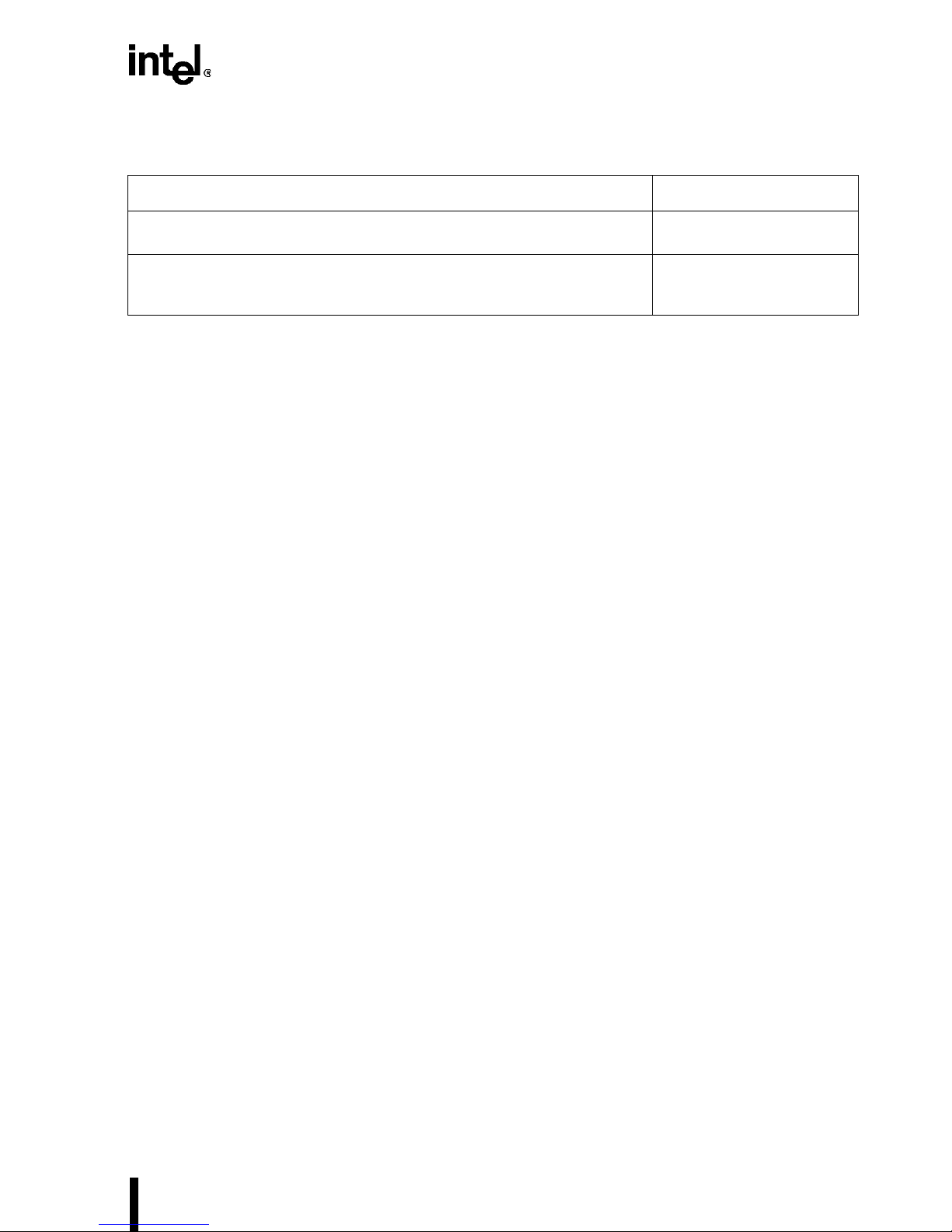

You can obtain the following resources from the Word Wide Web at the s ites listed.

Document Name Web Site

Standard 1149.1—1990, IEEE Standard Test Access Port and BoundaryScan Architecture

PCI Loc al B us Spe ci fic ation

and its supplement,

, Revi sions 2.0 and 2.1 Contact the PCI Specia l

Standard 1149.1a—1993

Contact the IEEE at

http://www.ieee.org.

Interest Group at

http://www.pcisig.com

1-7

Page 26

Page 27

Introduction

Chapter Contents

2.1 Processor Features.................................................................2-2

2.2 Intel486™ Processor Product Family................ ...................2-4

2.3 System Component s............................................ ......... ........ .2-7

2

2.4 System Architecture..............................................................2-7

2.5 Systems Applications..........................................................2-11

Page 28

Page 29

CHAPTER 2

INTRODUCTION

The Intel486™ processor family enables a range of low-cost, high-performance embedded system designs cap able of runni ng the e ntire i nstalle d base o f DOS *, Win dows*, OS/2 *, and UNIX*

applications written for the Intel architecture. This family includes the following processors:

•The IntelDX4™ processor is the fastest Intel486 processor (up to 50% faste r than an

IntelDX2™ processor). The IntelDX4 processor int egrates a 16-Kbyte unifie d ca che and

floating-poi nt hardware on-chip for improved performance.

The IntelDX4 processor is also available with a write-back on-chip cache for improved

entry-level performance.

•The IntelDX2™ processor integrates an 8-Kbyte unified cache and floating-point

hardware on-chip.

The IntelDX4 and IntelDX2 processors use Intel’s speed-multiplying technology, allowing

the p roc es sor core to op erate at fre q u en c ie s hi g h er th an th e ex t er n al m emory bus .

• Th e Int el486 SX processor offers the features of the IntelDX2 processor without floating-

point hardware and clock multiplying.

•The Ultra-Low Power Ultra-Low Power Intel486 SX and Ultra-Low Power

Intel486 GX processors provide additional power-saving features for use in batteryoperated and hand-held embedded designs . Th e Ultra-Low Power Intel486 SX processor,

like the other Intel486 processors, supports dynamic data bus sizing for 8-, 16-, or 32-bit

bus sizes, whereas the Ultra-Low Power Intel486 GX processor has a 16-bit external data

bus.

The entire Intel486 processor family incorporates energy efficient “SL Technology” for mobile

and fixed embedded comput ing . SL Tec hnol ogy ena bles syste m de signs t hat exceed th e Envi ronmental Protection Agency’s (EPA) Energy Star program guidelines without compromising performance. It also increases system design flexibility and improves battery life in all Intel486

processor-bas ed hand-held applications. S L Technology allows system de signers to di fferentiate

their power management schemes with a variety of energy efficient, battery life enhancing features.

Intel486 processors provide power management features that are transparent to application and