Intel® 875P Chipset

Platform Design Guide

For use with Intel® Pentium® 4 Processors with 512-KB L2 Cache

on 0.13 Micron Process, Intel® Pentium® 4 Processor Extreme

Edition Supporting Hyper-Threading Technology, and Intel®

Pentium® 4 Processor on 90 nm Process

February 2004

Document Number: 252527-005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

875P chipset MCH may contain design defects or errors known as errata which may cause the product to deviate from published specifica-

tions. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

1

Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a Hyper-Threading

Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See

<<http://www.intel.com/info/hyperthreading/>> for more information including details on which processors support HT Technology.

2

C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel. Imple-

I

mentations of the I

2

C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corpora-

tion.

Intel, Pentium, Intel NetBurst, Intel Xeon, Pentium II Xeon, and Pentium III Xeon are trademarks or registered trademarks of Intel Corporation or its

subsidiaries in the United States and other countries.

*Other brands and names are the property of their respective owners.

Copyright © 2003–2004 Intel Corporation

2 Intel® 875P Chipset Platform Design Guide

Contents

1 Introduction.......................................................................................................................21

1.1 Reference Documentation................................................................................... 22

1.2 Conventions and Terminology............................................................................. 23

2 System Overview ............................................................................................................. 27

2.1 Intel

2.2 Intel

2.3 Bandwidth Summary ........................................................................................... 33

2.4 System Configurations ........................................................................................ 34

3 Platform Stack-Up and Placement Overview ...................................................................35

3.1 General Design Considerations ..........................................................................35

3.2 Board Stack-Up ................................................................................................... 35

3.3 Component Quadrant Layout ..............................................................................40

3.4 Platform Component Placement ......................................................................... 43

®

82875P Memory Controller Hub (MCH) .................................................... 27

2.1.1 System Memory Interface .................................................................. 27

2.1.2 Supported Frequencies ...................................................................... 28

2.1.3 Hub Interface ......................................................................................28

2.1.4 Communications Streaming Architecture (CSA) Interface .................28

2.1.5 Accelerated Graphics Port (AGP) Interface .......................................28

®

ICH5 System Features .............................................................................. 29

2.2.1 Integrated LAN Controller...................................................................29

2.2.2 Serial ATA .......................................................................................... 30

2.2.3 USB 2.0 Support ................................................................................ 30

2.2.4 Manageability and Other Enhancements ........................................... 30

2.2.5 AC ’97 Audio and Modem Support ..................................................... 31

3.2.1 PCB Technology Considerations ....................................................... 37

3.2.2 Component Motherboard Layout (Pads and Vias) .............................38

3.3.1 Processor Quadrant Layout ............................................................... 40

3.3.2 MCH Component Quadrant Layout.................................................... 41

3.3.3 Intel

®

ICH5 Component Quadrant Layout .......................................... 42

4 Platform Clock Routing Guidelines................................................................................... 45

4.1 HOST_CLK Clock Group .................................................................................... 47

4.1.1 HOST_CLK Clock Topology...............................................................47

4.1.2 BCLK General Routing Guidelines ..................................................... 50

4.2 CLK66 and CL33 Clock Groups .......................................................................... 50

4.2.1 Length Matching ................................................................................. 50

4.2.1.1 CLK_66 and Intel

4.2.1.2 CLK_33 Length Matching ..................................................... 51

4.2.2 TCLK33 Clock Group ......................................................................... 52

4.2.2.1 Sharing 33-MHz Clocks ........................................................ 53

4.2.3 CLK66 Clock Group ...........................................................................54

4.2.4 CLK14 Clock Group ...........................................................................55

4.2.5 USB Clock Group ............................................................................... 56

4.2.6 SRC Clock Group ............................................................................... 56

4.2.6.1 SRC Clock Topology ............................................................ 56

4.2.6.2 SRC General Routing Guidelines ......................................... 58

Intel® 875P Chipset Platform Design Guide 3

®

ICH5 CLK_33 Length Matching ............. 50

4.3 Clock Driver Decoupling...................................................................................... 59

4.3.1 CK409 Power Plane Filtering ............................................................. 59

4.3.1.1 VDD Plane Filtering .............................................................. 59

4.3.1.2 VDDA Plane Filtering............................................................ 59

4.3.1.3 VDD_48 Plane Filtering ........................................................ 59

4.4 EMI Constraints................................................................................................... 60

5 Front Side Bus (FSB) ....................................................................................................... 61

5.1 General Topologies and Layout Guidelines ........................................................ 61

5.1.1 Trace Spacing Rules .......................................................................... 62

5.1.2 Signal Groups..................................................................................... 62

5.1.3 Motherboard Layout Rules for AGTL+ Signals .................................. 63

5.1.3.1 4X Routing Guidelines .......................................................... 63

5.1.3.2 2X Routing Guidelines .......................................................... 63

5.1.3.3 1X Routing Guidelines .......................................................... 64

5.1.3.4 Ground Referencing ............................................................. 64

5.1.4 Motherboard Layout Rules for Async AGTL+ Signals........................ 65

5.1.5 AGTL+ Layout Topologies ................................................................. 66

5.1.5.1 Topology 1............................................................................ 66

5.1.6 Non AGTL+ Topologies...................................................................... 66

5.1.6.1 Topology 2: THERMTRIP# and FERR# ............................... 66

5.1.6.2 Topology 3: A20M#, IGNNE#, SMI#, SLP#, STPCLK#,

LINT[1:0] ............................................................................... 67

5.1.6.3 Topology 4: IERR# ............................................................... 67

5.1.6.4 Topology 5: RESET# and BR0# ........................................... 68

5.1.6.5 Topology 6: INIT# ................................................................. 69

5.1.6.6 Topology 7: PWRGOOD ...................................................... 70

5.1.6.7 Topology 8: PROCHOT#...................................................... 70

5.1.6.8 Topology 9: TESTHI Signals ................................................ 71

5.1.6.9 Topology 10: COMP[1:0] ...................................................... 71

5.1.6.10 Topology 11: BOOTSELECT................................................ 72

5.1.6.11 Topology 12: RESERVED .................................................... 72

5.1.6.12 Topology 13: OPTIMIZED/COMPAT# or IMPSEL ............... 73

5.1.6.13 Host VREFs .......................................................................... 73

5.1.6.14 Host VID Topology ............................................................... 74

5.1.6.15 THERMDA/THERMDC ......................................................... 75

5.1.6.16 Host RCOMP ........................................................................ 75

5.1.6.17 Host SWING ......................................................................... 75

5.1.6.18 BSEL .................................................................................... 76

5.2 Trace Length Matching ....................................................................................... 77

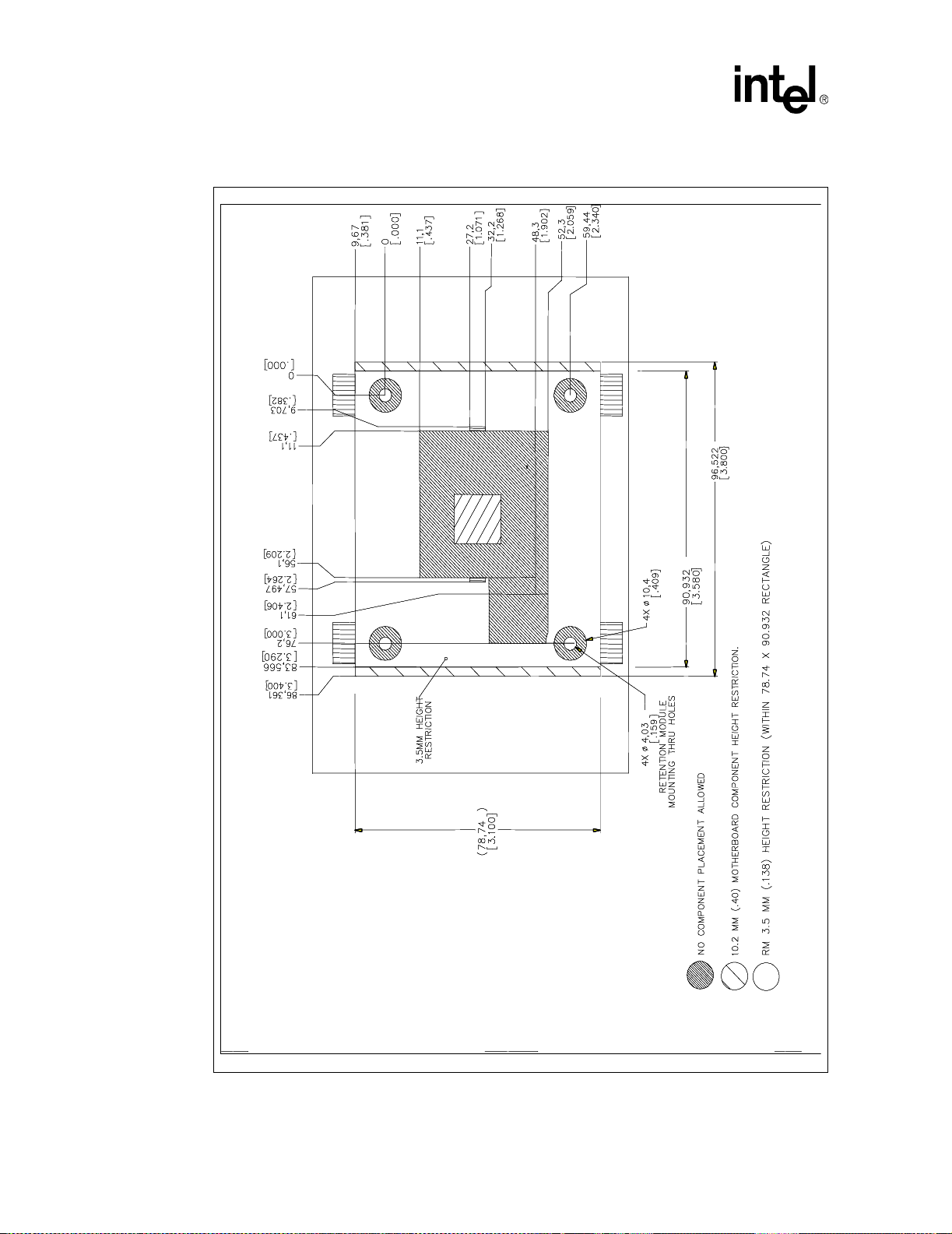

5.3 Retention Mechanism Placement and Keep-Outs .............................................. 78

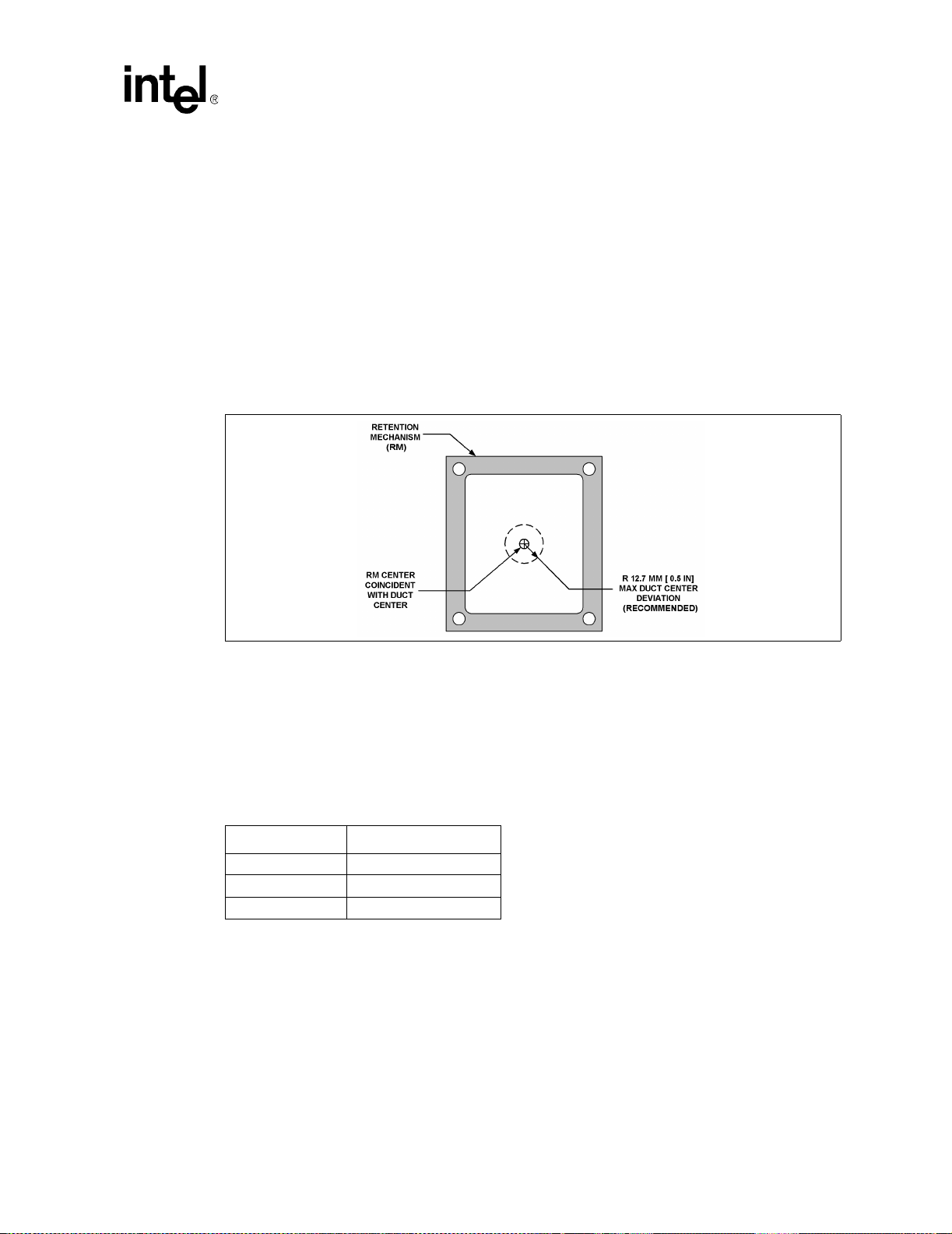

5.4 Processor Location Relative to Retention Mechanism........................................ 81

5.5 Power Header for Active Cooling Solutions ........................................................ 81

5.6 Debug Port Guidelines ........................................................................................ 82

5.6.1 Debug Tools Specifications ................................................................ 82

5.6.1.1 Logic Analyzer Interface (LAI) .............................................. 82

5.6.1.2 Mechanical Considerations .................................................. 82

5.6.1.3 Electrical Considerations ...................................................... 82

6 DDR System Memory Guidelines .................................................................................... 83

6.1 DDR Length Matching Strategy .......................................................................... 84

6.1.1 Strategy Overview .............................................................................. 84

4 Intel® 875P Chipset Platform Design Guide

6.1.2 Defining the Target Clock Reference Length ..................................... 84

6.2 Length Matching and Length Formulas...............................................................85

6.3 Package Length Compensation .......................................................................... 86

6.4 Stack-Up and Referencing Guidelines ................................................................ 86

6.4.1 Ground Stitching................................................................................. 87

6.5 DDR Design Topologies and Guidelines ............................................................. 88

6.5.1 Target Impedances ............................................................................ 88

6.5.2 Clock Signal Group Routing Guidelines

(SCMDCLK_x/SCMDCLK_x#) ........................................................... 88

6.5.3 Control Signal Group Routing Guidelines

(SCKE_x[3:0]#, SCS_x[3:0]#) ............................................................ 92

6.5.4 Address/Command Signal Group Routing Guidelines

(SMAA_x[12:0], SBA_x[1:0], SRAS_x#,

SCAS_x#, SWE_x#)........................................................................... 95

6.5.5 Data Signal Group Routing Guidelines

(SDQ_x[63:0], SDQS_x[8:0], SECC_x[7:0]).......................................97

6.6 1 DIMM per-Channel Design Exceptions .......................................................... 101

6.6.1 Ground Referencing Exceptions ...................................................... 101

6.7 Miscellaneous Signals....................................................................................... 102

6.7.1 TESTP[4:11] and TESTP[17:24] Termination .................................. 102

6.7.2 DDR VREF Overview ....................................................................... 102

6.7.2.1 DDR VREF at the MCH ...................................................... 102

6.7.3 DDR VREF at the DIMMs.................................................................103

6.8 DDR Resistive Compensation (SMRCOMP) per Channel ................................ 104

7 Hub Interface..................................................................................................................107

7.1 Hub Interface Routing Guidelines ..................................................................... 108

7.1.1 Hub Interface Signal Referencing .................................................... 108

7.1.2 Hub Interface HIVREF/HISWING Generation/Distribution ............... 109

7.1.3 Hub Interface Compensation............................................................ 110

7.1.4 Hub Interface Decoupling Guidelines ...............................................110

8 AGP8X ........................................................................................................................... 111

8.1 AGP 3.0............................................................................................................. 111

8.1.1 AGP Interface Signal Groups ........................................................... 111

8.2 AGP 8X Implementations .................................................................................. 112

8.2.1 Motherboard Layout Recommendations ..........................................112

8.2.2 AGP 8X Routing Guidelines .............................................................112

8.2.2.1 Board Constraints ............................................................... 113

8.2.3 AGP Signal Noise Decoupling Guidelines........................................114

8.2.3.1 1.5 V AGP Connector Decoupling ...................................... 114

8.2.4 Miscellaneous Signal Requirements ................................................ 115

8.2.4.1 PERR.................................................................................. 115

8.2.4.2 AGP 2.0 and AGP 3.0 Mode Detection .............................. 115

8.2.4.3 GRCOMP............................................................................ 117

8.2.4.4 AGPREF ............................................................................. 117

8.2.4.5 AGP_SWING ...................................................................... 117

9 CSA Port ........................................................................................................................119

9.1 CSA Port Routing Guidelines ............................................................................ 119

9.2 CSA Port Generation/Distribution of Reference Voltages ................................. 121

Intel® 875P Chipset Platform Design Guide 5

9.3 CSA Port Resistive Compensation ................................................................... 122

10 Intel

10.1 Source Synchronous Strobing .......................................................................... 123

10.2 IDE Interface ..................................................................................................... 125

10.3 Cable Detection for Ultra ATA/66 and Ultra ATA/100 ....................................... 126

10.4 Serial ATA Interface .......................................................................................... 130

10.5 AC ’97 ............................................................................................................... 136

10.6 CNR .................................................................................................................. 146

10.7 USB 2.0............................................................................................................. 149

9.3.1 Intel

®

ICH5 Layout/Routing Guidelines .......................................................................... 123

®

82547EI GbE Controller Layout Considerations..................... 122

10.2.1 Cabling ............................................................................................. 125

10.3.1 Combination Host-Side/Device-Side Cable Detection ..................... 126

10.3.2 Device-Side Cable Detection ........................................................... 127

10.3.3 Primary IDE Connector Requirements ............................................. 128

10.3.4 Secondary IDE Connector Requirements ........................................ 129

10.4.1 General Routing and Placement ...................................................... 130

10.4.2 Serial ATA Trace Separation............................................................ 131

10.4.3 Serial ATA Trace Length Pair Matching ........................................... 131

10.4.4 Serial ATA Trace Length Guidelines ................................................ 131

10.4.5 SATARBIAS/SATARBIAS# Connection........................................... 132

10.4.6 SATALED# Implementation ............................................................. 132

10.4.7 Serial ATA Host Connector Placement Considerations ...................133

10.5.1 AC ’97 Routing ................................................................................. 140

10.5.1.1 General Board Routing Recommendations ........................ 140

10.5.1.2 Codec Reference and Anti-Aliasing Recommendations..... 140

10.5.1.3 Codec Analog Power Decoupling Recommendations........ 140

10.5.1.4 Codec Digital Power Decoupling Recommendation ........... 141

10.5.2 Motherboard Implementation ........................................................... 141

10.5.2.1 Valid Codec Configurations ................................................ 141

10.5.3 Design Considerations for Audio Quality.......................................... 142

10.5.3.1 Audio Codec Placement ..................................................... 142

10.5.3.2 Power Plane Configurations ............................................... 142

10.5.3.3 Analog Power Delivery ....................................................... 143

10.5.3.4 Power On Audio Transitions ............................................... 143

10.5.3.5 Line Output ......................................................................... 144

10.5.3.6 Line In / Auxiliary In ............................................................ 144

10.5.3.7 Grounding Techniques ....................................................... 144

10.5.3.8 CD ATAPI Input .................................................................. 144

10.5.4 Stereo Microphone Consideration.................................................... 144

10.5.5 SPKR Pin Consideration .................................................................. 145

10.6.1 AC ’97 Audio Codec Detect Circuit and Configuration Options........ 146

10.6.1.1 CNR 1.2 AC ’97 Disable and Demotion Rules for the

Motherboard ....................................................................... 147

10.6.2 CNR Routing Summary.................................................................... 148

10.7.1 Layout Guidelines............................................................................. 149

10.7.1.1 General Routing and Placement ........................................ 149

10.7.1.2 USB 2.0 Trace Separation.................................................. 150

10.7.1.3 USBRBIAS/USBRBIAS# Connection ................................. 150

10.7.1.4 USB 2.0 Termination .......................................................... 151

10.7.1.5 USB 2.0 Trace Length Pair Matching ................................. 151

10.7.1.6 USB 2.0 Trace Length Guidelines ...................................... 151

6 Intel® 875P Chipset Platform Design Guide

10.7.2 Plane Splits, Voids, and Cut-Outs (Anti-Etch) .................................. 152

10.7.2.1 VCC Plane Splits, Voids, and Cut-Outs (Anti-Etch)............ 152

10.7.2.2 GND Plane Splits, Voids, and Cut-Outs (Anti-Etch) ........... 152

10.7.3 USB Power Line Layout Topology ................................................... 152

10.7.4 EMI Considerations ..........................................................................153

10.7.4.1 Common-Mode Chokes ...................................................... 153

10.7.5 ESD .................................................................................................. 154

10.7.6 Front Panel Solutions ....................................................................... 154

10.7.6.1 Internal USB Cables ...........................................................154

10.7.6.2 Motherboard/PCB Mating Connector.................................. 155

10.7.6.3 Front Panel Connector Card............................................... 157

10.8 Interrupt Interface .............................................................................................. 158

10.8.1 PIRQ Routing Example .................................................................... 158

10.9 SMBus 2.0/SMLink Interface............................................................................. 159

10.9.1 SMBus Design Considerations......................................................... 159

10.9.2 General Design Issues / Notes......................................................... 160

10.9.3 High-Power/Low-Power Mixed Architecture ..................................... 160

10.9.4 Calculating The Physical Segment Pull-Up Resistor........................161

10.10 PCI .................................................................................................................... 162

10.10.1 PCI Routing Summary...................................................................... 162

10.11 RTC ...................................................................................................................164

10.11.1 RTC Crystal...................................................................................... 165

10.11.2 External Capacitors .......................................................................... 166

10.11.3 RTC Layout Considerations ............................................................. 167

10.11.4 RTC External Battery Connection .................................................... 167

10.11.5 RTC External RTCRST# Circuit .......................................................168

10.11.6 SUSCLK ........................................................................................... 169

10.11.7 RTC-Well Input Strap Requirements ................................................169

10.12 Internal LAN Layout Guidelines......................................................................... 170

10.12.1 Footprint Compatibility......................................................................170

10.12.2 Intel

®

ICH5 – LAN Connect Interface Guidelines .............................172

10.12.2.1 Bus Topologies ...................................................................172

10.12.2.2 Signal Routing and Layout.................................................. 174

10.12.2.3 Crosstalk Consideration...................................................... 174

10.12.2.4 Impedances ........................................................................174

10.12.2.5 Line Termination .................................................................174

10.12.2.6 Terminating Unused LAN Connect Interface Signals .........174

10.12.3 Design and Layout Considerations for Intel

10.12.3.1 Guidelines for Intel

®

82562EZ/EX

®

82562EZ/EX .............. 175

Component Placement ....................................................... 175

10.12.3.2 Crystals and Oscillators ...................................................... 175

10.12.3.3 Intel® 82562EZ/EX Termination Resistors ......................... 175

10.12.3.4 Critical Dimensions with Discrete Magnetics Module .........176

10.12.3.5 Critical Dimensions with Integrated Magnetics Module ......177

10.12.3.6 Reducing Circuit Inductance ...............................................178

10.12.4 Intel

10.12.5 Design and Layout Considerations for Intel

®

82562EZ/EX Disable Guidelines ............................................ 180

®

Controller and Intel

82551 QM Fast Ethernet Controller ................181

®

82540EM GbE

10.12.6 General LAN Differential Pair Trace Routing Considerations .......... 181

10.12.6.1 Trace Geometry and Length ...............................................182

10.12.6.2 Signal Isolation ...................................................................182

Intel® 875P Chipset Platform Design Guide 7

10.13 Trusted Platform Module Guidelines................................................................. 185

11 Intel

12 Intel

12.1 Intel

12.2 Thermal Design Power...................................................................................... 189

12.3 Glue Chip 4 (Intel® ICH5 Glue Chip) ................................................................ 190

12.4 Discrete Glue Logic ........................................................................................... 191

12.5 Suspend-to-RAM Sequencing........................................................................... 193

12.6 Processor CMOS Considerations ..................................................................... 193

12.7 Resistor Summary............................................................................................. 194

13 Intel

13.1 SYS_RESET# Usage Model ............................................................................. 201

13.2 PWRBTN# Usage Model .................................................................................. 201

13.3 Power-Well Isolation Control Strap Requirements ............................................ 202

10.12.6.3 Magnetics Module General Power and Ground Plane

Considerations.................................................................... 183

10.12.6.4 Common Physical Layout Issues ....................................... 184

10.13.1 TPM Design Considerations............................................................. 185

10.13.2 LPC Design Considerations ............................................................. 185

10.13.3 Motherboard Placement Consideration............................................ 186

®

ICH5 General Purpose I/O ................................................................................... 187

®

ICH5 System Design Considerations ................................................................... 189

®

ICH5 Power Consumption ....................................................................... 189

12.4.1 RSMRST# Generation ..................................................................... 191

12.4.2 PWROK Generation ......................................................................... 191

12.4.3 PS_ON Generation .......................................................................... 192

12.6.1 Intel ICH5 Outputs (A20M#, SMI#, IGNNE#, CPUPWRGD,

STPCLK#, CPUSLP#, NMI, INTR, INIT#) ........................................ 193

®

ICH5 Power Management .................................................................................... 201

14 Flash BIOS Guidelines ................................................................................................... 203

14.1 Flash BIOS Vendors ......................................................................................... 203

14.2 Flash BIOS Decoupling ..................................................................................... 203

14.3 In Circuit Flash BIOS Programming .................................................................. 203

14.4 Flash BIOS INIT# Voltage Compatibility ........................................................... 204

14.5 Flash BIOS VPP Design Guidelines ................................................................. 205

15 Power Distribution Guidelines ........................................................................................ 207

15.1 Terminology and Definitions.............................................................................. 207

15.2 Customer Reference Board (CRB) Power Delivery .......................................... 208

15.2.1 VCC (Core Power to Processor) ...................................................... 210

15.2.2 VTT (Power to MCH)........................................................................ 210

15.2.3 VCCVID (Processor VID) ................................................................. 210

15.2.4 2.6 V Dual (DDR Core)..................................................................... 210

15.2.5 1.3 V (DDR Termination Voltage)..................................................... 210

15.2.6 1.5 V (VCC for MCH Core, HI, AGP, Intel

®

ICH5 HI, and AGP

Connector)........................................................................................ 211

15.2.7 5 V Dual............................................................................................ 211

15.2.8 5 V SB (Standby).............................................................................. 211

15.2.9 3.3 V SB (Standby)........................................................................... 211

15.2.10 2.6 V SB (Standby)........................................................................... 212

15.3 Component Power Delivery Guidelines ............................................................ 212

8 Intel® 875P Chipset Platform Design Guide

15.3.1 Processor Power Delivery Guidelines .............................................. 213

15.3.1.1 Processor Power Requirements ......................................... 213

15.3.1.2 Decoupling Requirements ..................................................215

15.3.1.3 Layout .................................................................................216

15.3.1.4 VRD 10.0 Switching Network.............................................. 219

15.3.1.5 Thermal Considerations...................................................... 220

15.3.1.6 Simulation ...........................................................................221

15.3.1.7 VCCVID Regulator Guidelines............................................ 223

15.3.1.8 Processor Filter Specifications for VCCA,

VCCIOPLL, and VSSA ....................................................... 224

15.3.1.9 Processor Power Sequencing ............................................ 226

15.3.2 Intel

®

Pentium® 4 Processor on 90 nm Process and Loadline A

Specifications ...................................................................................227

15.3.2.1 Loadline Requirements ....................................................... 227

15.3.2.2 Decoupling Requirements ..................................................227

15.3.2.3 VR Component Tolerance Requirements........................... 227

15.3.2.4 VR Resistor and Capacitor Changes.................................. 228

15.3.2.5 Thermal Considerations...................................................... 228

15.3.3 MCH Power Delivery Guidelines ...................................................... 229

15.3.3.1 DDR (2.6 V Power Plane) ...................................................229

15.3.3.2 VTT (MCH FSB Power Plane) ............................................ 230

15.3.3.3 Hub, CSA, AGP, and Core Interface (1.5 V Power Plane) .231

15.3.3.4 Decoupling Recommendations........................................... 233

15.3.4 MCH Filter Specifications ................................................................. 236

15.3.4.1 Plane Filter.......................................................................... 236

15.3.4.2 Analog Filters...................................................................... 236

15.3.4.3 MCH Power Sequencing Requirements ............................. 238

15.3.5 DDR DIMM Power Deliver................................................................239

15.3.5.1 2.6 V Power Delivery ..........................................................239

15.3.5.2 1.3 V VTT Power Delivery .................................................. 239

15.3.5.3 DDR DIMMs Decoupling..................................................... 240

15.3.6 Intel

®

ICH5 Power Delivery Guidelines ............................................241

15.3.6.1 Power Supply PS_ON Consideration .................................241

15.3.6.2 SLP_S4# Assertion Width .................................................. 241

15.3.6.3 3.3 V/1.5 V Power Sequencing........................................... 241

15.3.6.4 3.3 V/V5REF Sequencing ...................................................242

15.3.6.5 Intel

15.3.6.6 Intel

®

ICH5 Power Delivery ................................................242

®

ICH5 Decoupling....................................................... 246

16 EMI Design Guidelines ................................................................................................... 249

16.1 Terminology....................................................................................................... 249

16.2 Brief EMI Theory ...............................................................................................249

16.3 EMI Regulations and Certifications ...................................................................250

16.4 EMI Design Considerations ............................................................................... 250

16.4.1 Spread Spectrum Clocking (SSC) .................................................... 250

16.4.2 Differential Clocking ......................................................................... 251

16.4.3 PCI Bus Clock Control...................................................................... 252

16.4.4 EMI Test Capabilities ....................................................................... 253

17 Schematic Checklist .......................................................................................................255

17.1 Processor Interface ........................................................................................... 255

17.1.1 Processor Connector / MCH Items...................................................255

17.1.2 Processor Connector / Intel

Intel® 875P Chipset Platform Design Guide 9

®

ICH5 Items......................................... 257

17.1.3 Processor Connector Only Items ..................................................... 258

17.2 MCH Interface ................................................................................................... 261

17.2.1 MCH / FSB Items ............................................................................. 261

17.2.2 MCH / FSB Only Items ..................................................................... 262

17.2.3 MCH / DDR Channel A Items ........................................................... 263

17.2.4 MCH / DDR Channel B Items ........................................................... 264

17.2.5 MCH / AGP Items............................................................................. 266

17.2.6 MCH / AGP Only Items .................................................................... 266

17.2.7 MCH / Hub Interface Items............................................................... 267

17.2.8 MCH / CSA Items ............................................................................. 267

17.2.9 MCH / POWER Items....................................................................... 267

17.2.10 MCH / Miscellaneous Items.............................................................. 268

17.3 Clock CK409 Interface ...................................................................................... 268

17.4 AGP 4X/8X Interface ......................................................................................... 271

17.4.1 AGP Connector / MCH Items ........................................................... 271

17.4.2 AGP Connector Only Items .............................................................. 272

17.5 DDR Dual-Channel Interface ............................................................................ 273

17.5.1 DDR Channel A DIMM0 and DIMM1 / MCH Items........................... 273

17.5.2 DDR Channel-A DIMM0 and DIMM1 Only Items ............................. 274

17.5.3 DDR Channel-B DIMM0 and DIMM1 / MCH Items .......................... 275

17.5.4 DDR Channel-B DIMM0 and DIMM1 Only Items ............................. 276

17.6 Intel

®

ICH5 Interface ......................................................................................... 277

17.6.1 Intel

17.6.2 Intel

17.6.3 Intel

17.6.4 Intel

17.6.5 Intel

17.6.6 Intel

17.6.7 Intel

17.6.8 Intel

17.6.9 Intel

17.6.10 Intel

17.6.11 Intel

17.6.12 Intel

17.6.13 Intel

17.6.14 Intel

17.6.15 Intel

®

ICH5 / PCI Items..................................................................... 277

®

ICH5 / Interrupt Items ............................................................. 278

®

ICH5 / IDE Items..................................................................... 279

®

/ SATA Items .......................................................................... 280

®

ICH5 / Flash BIOS and LPC Items ......................................... 280

®

ICH5 / RTC Items ................................................................... 281

®

ICH5 / GPIO Items.................................................................. 281

®

ICH5 / SMBus and SMLink Items ........................................... 283

®

ICH5 / Miscellaneous Items.................................................... 283

®

ICH5 / Power Management Items .......................................... 284

®

ICH5 / Hub Items .................................................................... 285

®

ICH5 / LAN Items.................................................................... 285

®

ICH5 / EEPROM Items ........................................................... 286

®

ICH5 / AC ’97 Items ................................................................ 286

®

ICH5 / USB Items ................................................................... 287

17.7 Platform Power and Ground.............................................................................. 287

17.7.1 Intel

®

ICH5 / Power and Ground Items ............................................ 287

17.7.2 DDR DIMM Power Delivery.............................................................. 288

17.7.2.1 Decoupling Requirements .................................................. 288

17.7.2.2 Bulk Decoupling for DIMMs ................................................ 288

18 Layout Checklist ............................................................................................................. 289

18.1 Platform Clock ................................................................................................... 289

18.1.1 Clock Groups.................................................................................... 289

18.1.1.1 HOST_CLK Clock Group.................................................... 289

18.1.1.2 BCLK General Routing ....................................................... 290

18.1.2 CLK66 and CLK33 Clock Groups..................................................... 290

18.1.2.1 TCLK33 Clock Group ......................................................... 290

10 Intel® 875P Chipset Platform Design Guide

18.1.2.2 Sharing 33 MHz Clocks ......................................................291

18.1.2.3 CLK66 Clock Group ............................................................ 291

18.1.2.4 CLK14 Clock Group ............................................................ 292

18.1.2.5 DOTCLK and USBCLK Clock Group.................................. 292

18.1.2.6 SRC Clock Group ...............................................................293

18.1.3 Clock Driver Decoupling ...................................................................294

18.2 Front Side Bus (FSB) ........................................................................................ 294

18.2.1 AGTL + 4X Routing .......................................................................... 294

18.2.2 AGTL + 2X Routing .......................................................................... 295

18.2.3 AGTL + 1X Routing .......................................................................... 295

18.2.4 Asynchronous GTL + Signals Group................................................296

18.2.5 Power / Other Signals ...................................................................... 298

18.3 DDR System Memory........................................................................................ 299

18.3.1 Clocks – SCMDCLK_x[5:0], SCMDCLK_x[5:0]# .............................. 299

18.3.2 Control Signals – SCKE_x[3:0]#, SCS_x[3:0]# ................................ 300

18.3.3 Address/Command – SMAA_x[12:6,0], SBA_x[1:0],

SRAS_x#, SCAS_x#, SWE_x# ........................................................301

18.3.4 Data Signals – SDQ_x[63:0], SDQS_x[7:0], SDM_x[7:0]................. 302

18.3.5 DDR Reference Voltage ................................................................... 304

18.3.5.1 DDR VREF at the MCH ...................................................... 304

18.3.5.2 DDR VREF at the DIMMs ................................................... 304

18.3.6 DDR Resistive Compensation (SMRCOMP) per-Channel ............... 305

18.3.6.1 DDR SMRCOMP ................................................................305

18.3.6.2 DDR RCOMP VOH and VOL.............................................. 305

18.4 HUB Interface....................................................................................................306

18.4.1 8-Bit Hub Interface ........................................................................... 306

18.4.2 Hub Interface HIVREF/HISWING ..................................................... 306

18.4.3 Hub Interface Compensation............................................................ 307

18.4.3.1 RCOMP Resistor Values for Hub Interface ........................ 307

18.4.3.2 RCOMP Resistor Values for Intel

®

ICH5 ............................ 307

18.5 AGP 8X ............................................................................................................. 307

18.5.1 AGP 8X Routing ............................................................................... 307

18.5.1.1 Source Synchronous Signals.............................................. 307

18.5.1.2 Common Clock Signals ......................................................308

18.6 CSA Port ........................................................................................................... 309

18.6.1 CSA Port Routing ............................................................................. 309

18.6.2 CSA Port Generation/Distribution of Reference Voltage .................. 309

18.6.3 CSA Port Resistive Compensation...................................................310

18.7 Intel

18.6.3.1 RCOMP Resistor Values for MCH ......................................310

18.6.3.2 RCOMP Resistor Values for Intel

®

ICH5 ........................................................................................................ 310

Chipset Platform .................................................................310

®

82547EI

18.7.1 IDE Interface .................................................................................... 310

18.7.2 SATA Interface ................................................................................. 311

18.7.3 AC ’97............................................................................................... 312

18.7.4 USB 2.0 ............................................................................................ 313

18.7.5 PCI ................................................................................................... 314

18.7.6 RTC .................................................................................................. 314

18.7.7 LAN Connect Interface ..................................................................... 315

18.8 Flash BIOS ........................................................................................................ 316

18.8.1 Flash BIOS Decoupling .................................................................... 316

Intel® 875P Chipset Platform Design Guide 11

Figures

18.8.2 Processor/ICH5 Flash BIOS............................................................. 316

18.9 Power Distribution ............................................................................................. 317

18.9.1 Power Delivery ................................................................................. 317

18.9.2 Decoupling Requirements ................................................................ 319

18.9.3 MCH Power Delivery ........................................................................ 319

18.9.3.1 Decoupling Recommendations........................................... 319

18.9.3.2 Bulk Decoupling Requirements .......................................... 320

18.9.4 DDR DIMM Power Delivery.............................................................. 320

18.9.4.1 Decoupling Requirements .................................................. 320

18.9.4.2 Bulk Decoupling for DIMMs ................................................ 320

18.9.5 Intel

®

ICH5 Power Delivery .............................................................. 321

18.9.5.1 Decoupling Requirements .................................................. 321

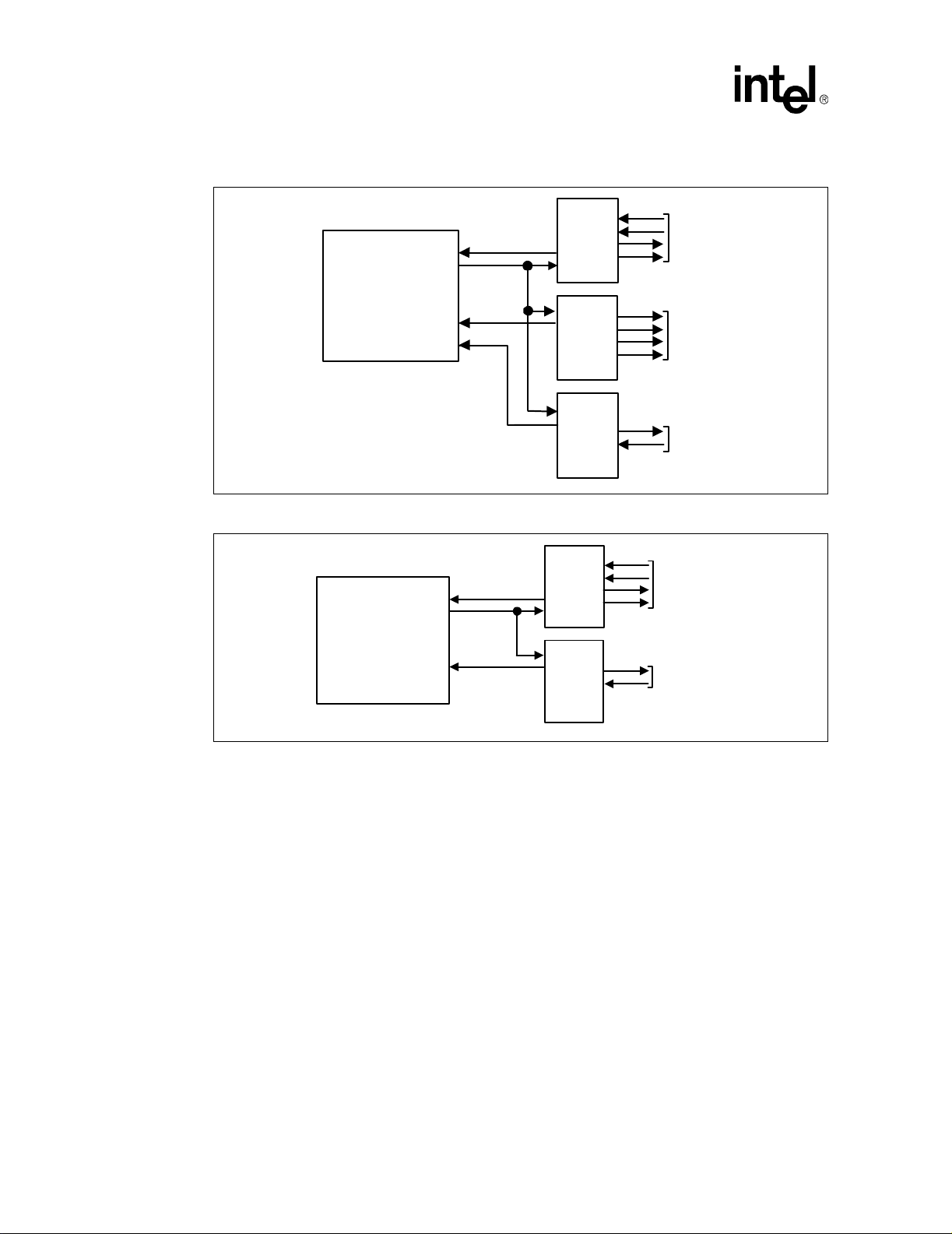

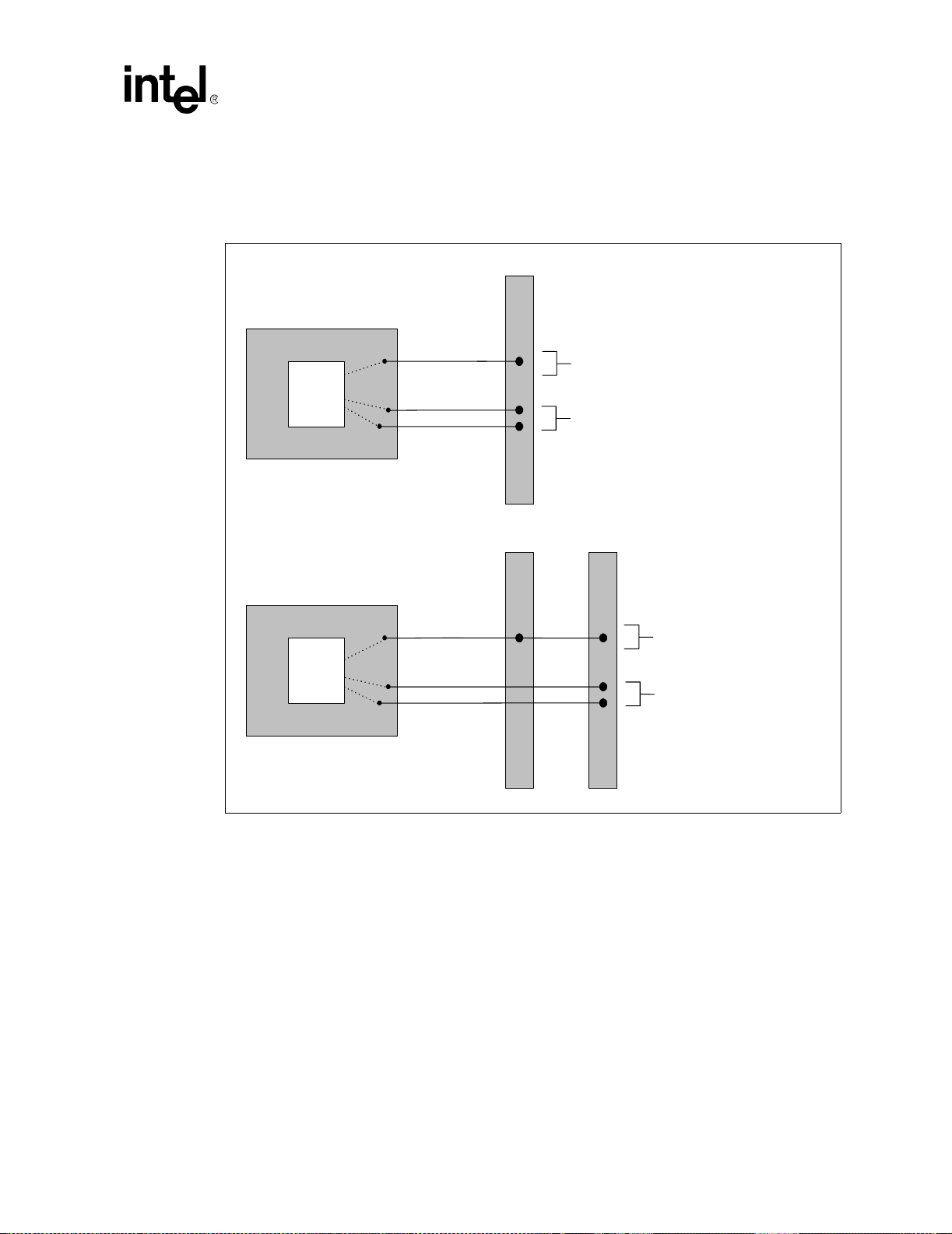

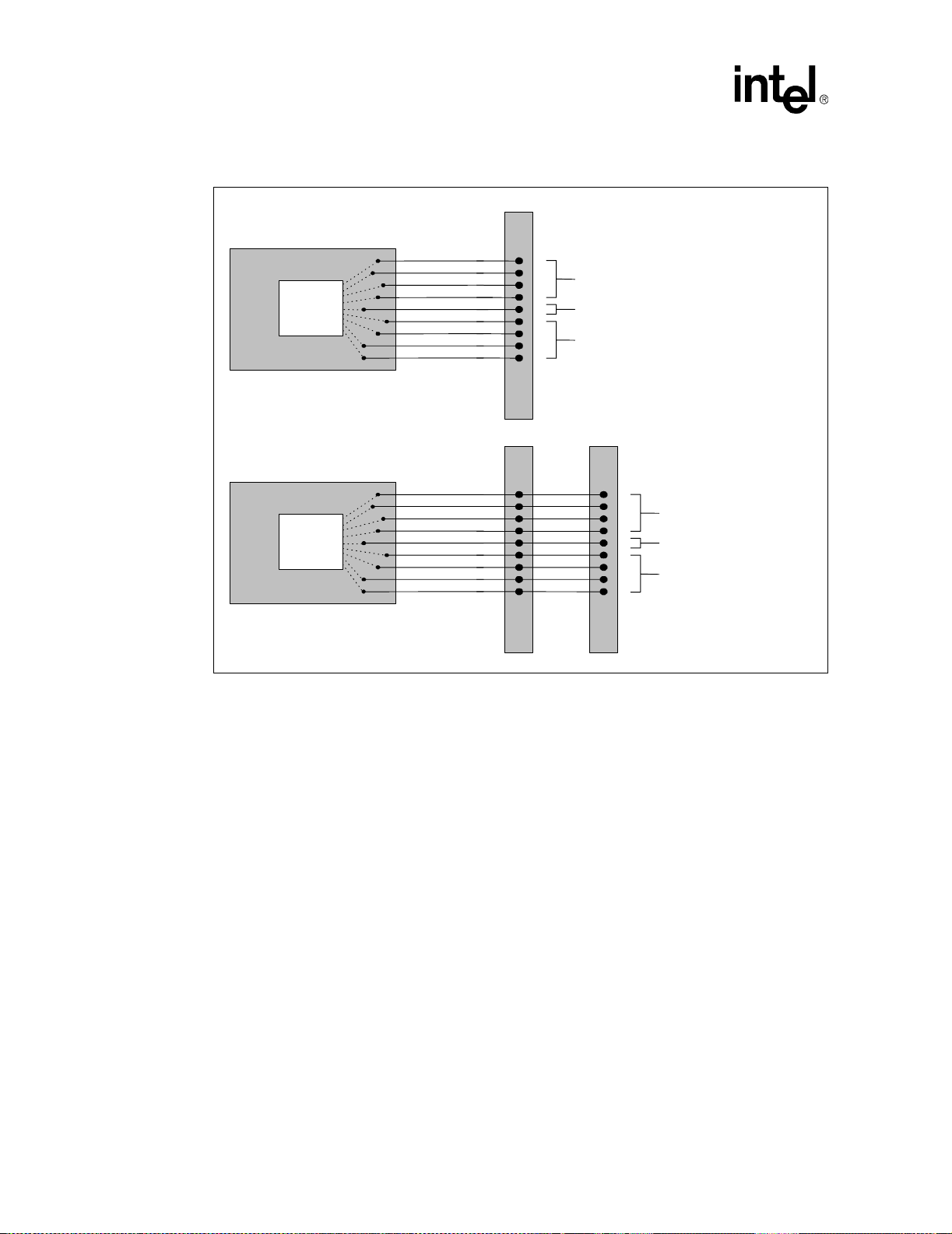

2-1 AC '97 with Audio/Modem Codec........................................................................ 31

2-2 AC '97 with Audio Codecs (4 Channel Secondary)............................................. 31

2-3 AC '97 with 2 Audio and a Modem Codec (4 Channel Secondary)..................... 32

2-4 AC '97 with Audio and Modem Codec................................................................. 32

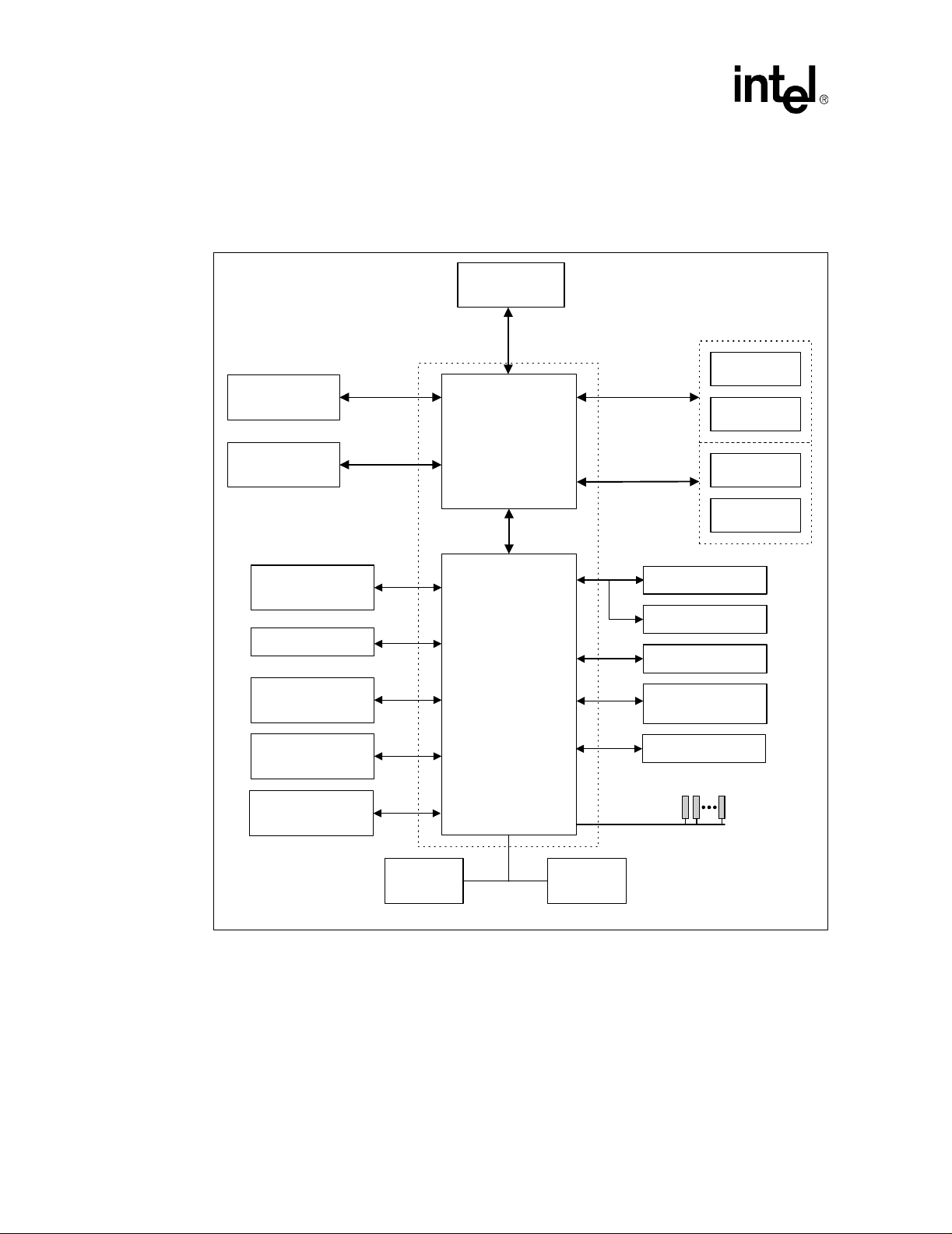

2-5 Typical System Configuration ............................................................................. 34

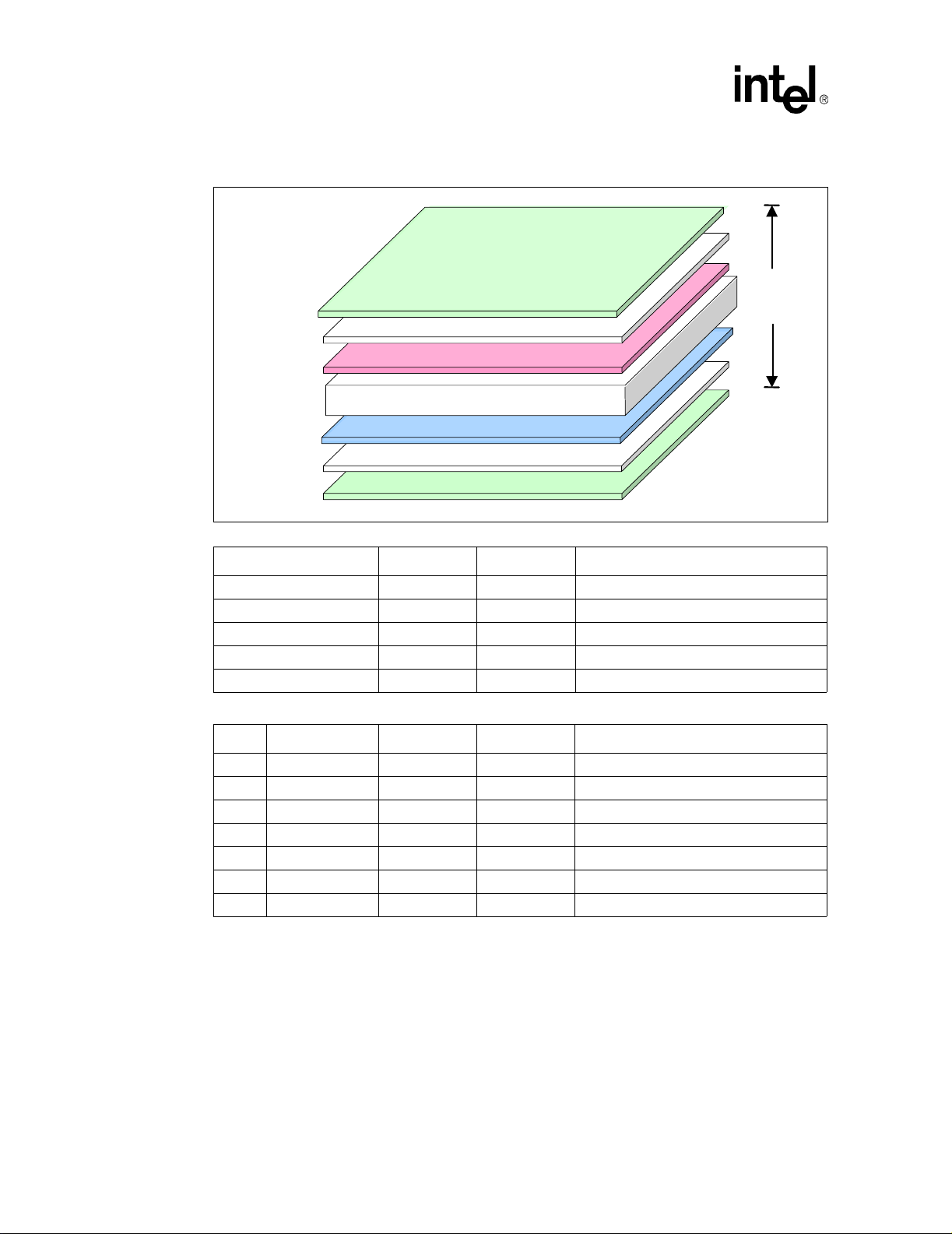

3-1 4-Layer PCB Stack-Up Example......................................................................... 36

3-2 PCB Technologies Stack-Up............................................................................... 37

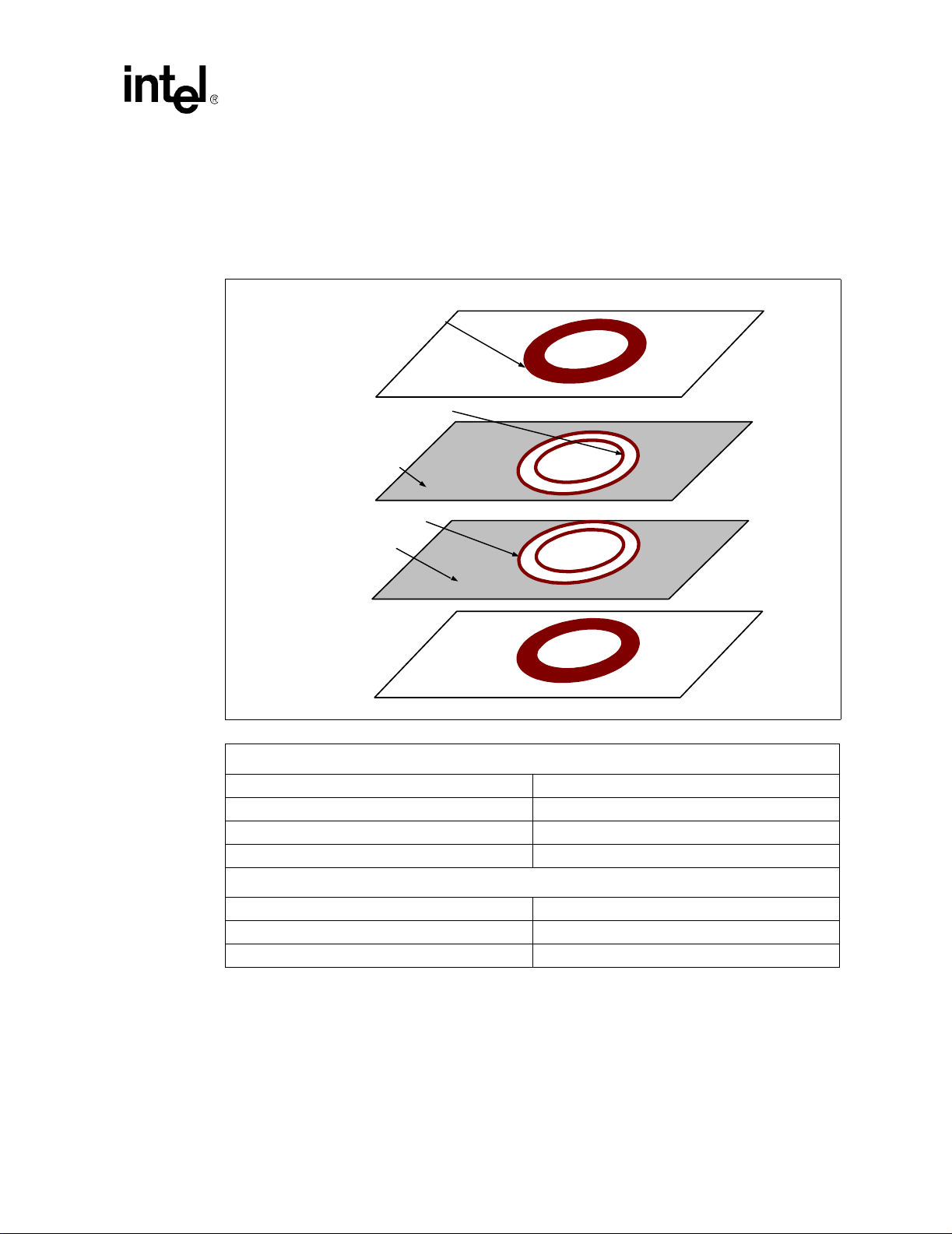

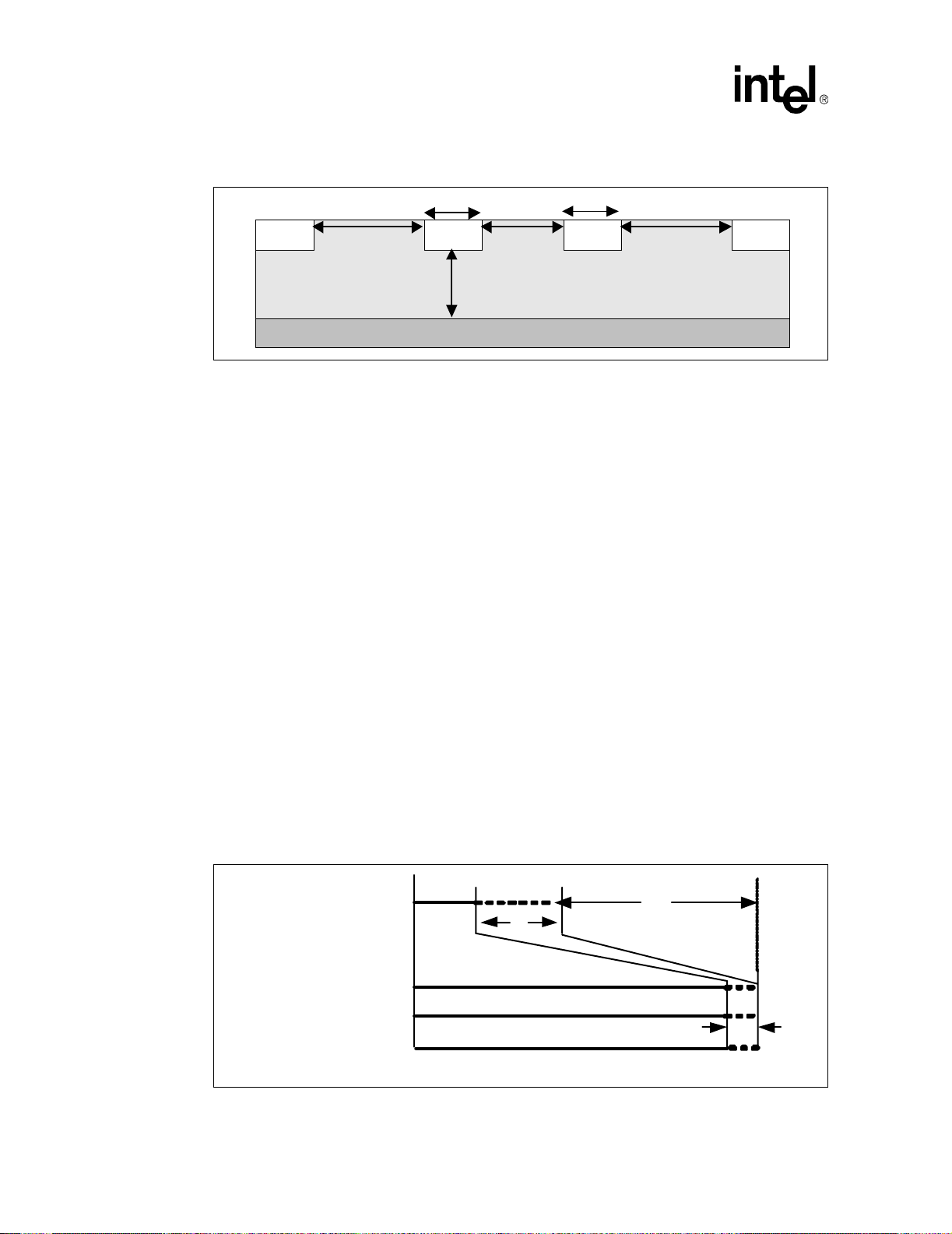

3-3 Via-Pad Layout Metal-Defined Pads .................................................................. 38

3-4 Via-Pad Layout Solder Mask-Defined Pads ........................................................ 39

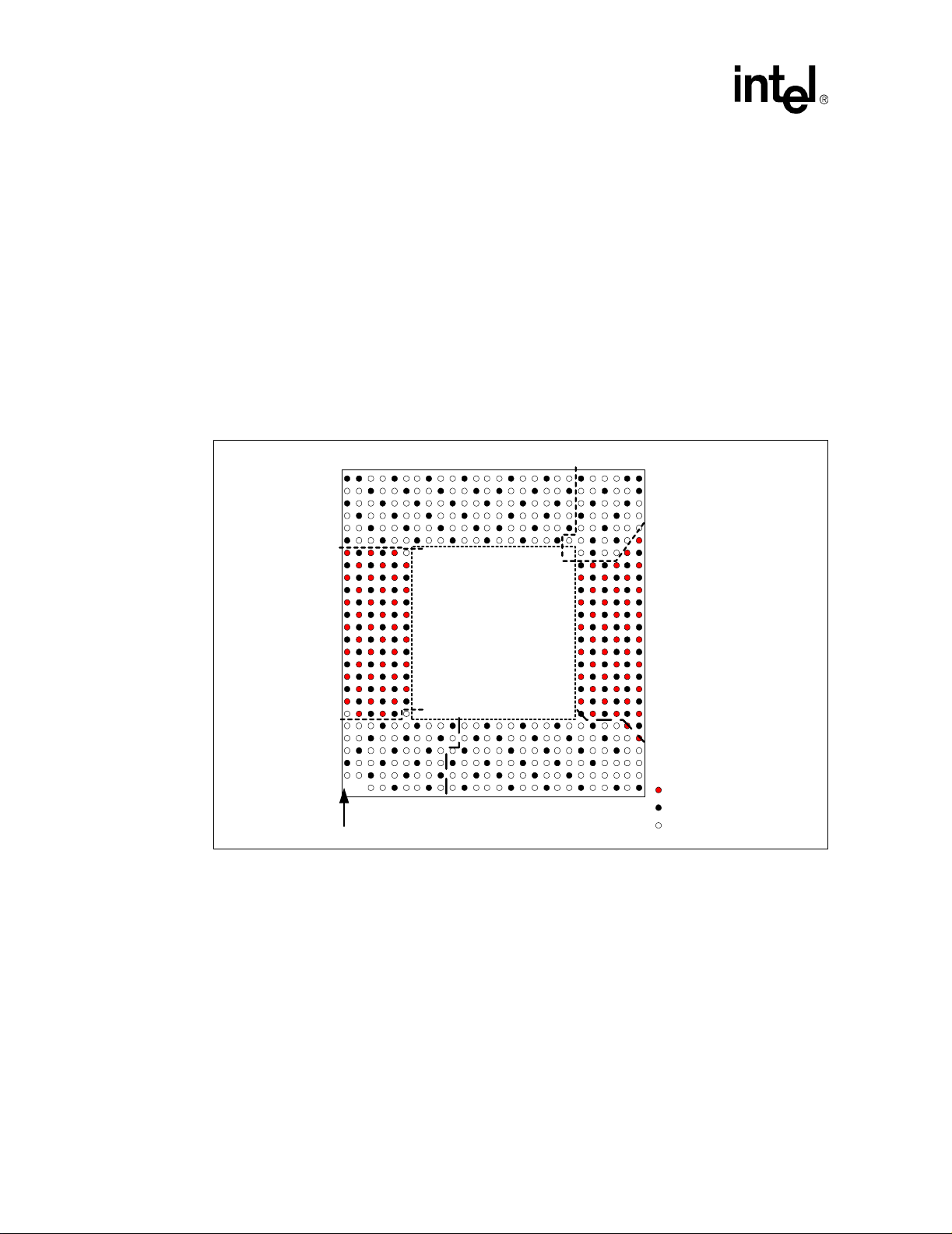

3-5 Processor Component Quadrant Layout (Top View) .......................................... 40

3-6 MCH Component Quadrant Layout (Top View) .................................................. 41

3-7 Intel

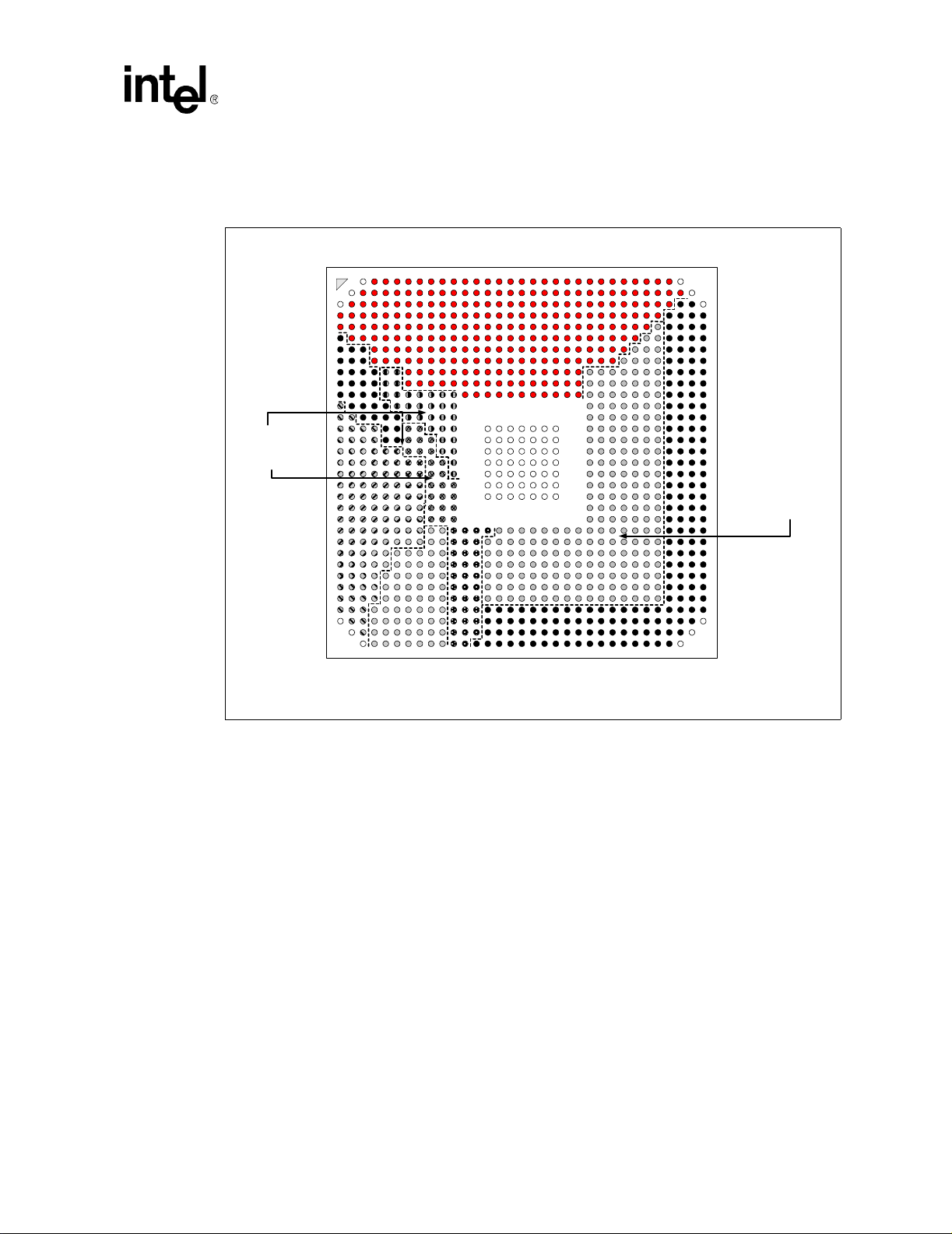

3-8 Component Placement Example Using a 4-DIMM ATX Board ........................... 43

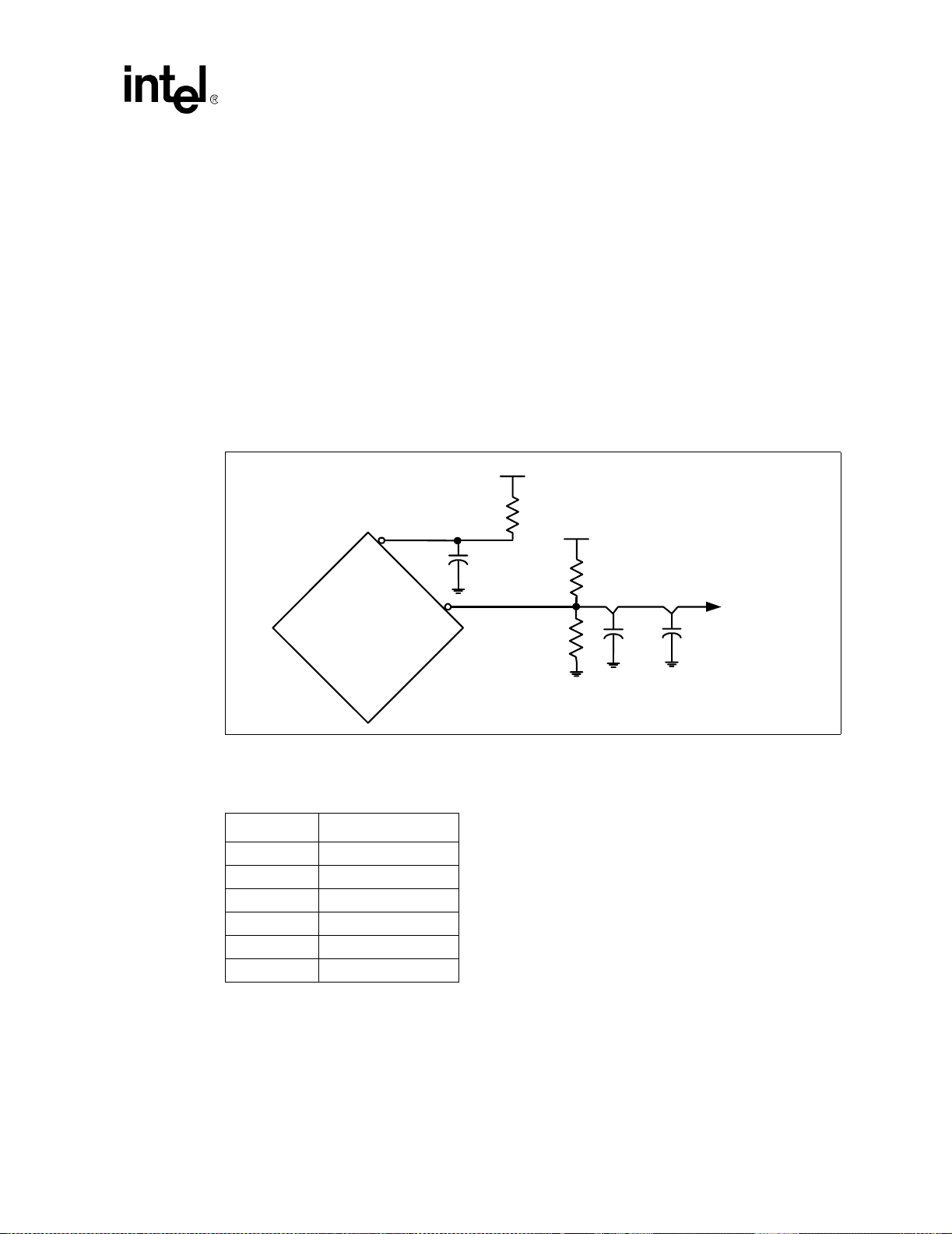

4-1 Intel

®

ICH5 Quadrant Layout (Top View) ............................................................ 42

®

875P Chipset-Based System Clocking Diagram ....................................... 46

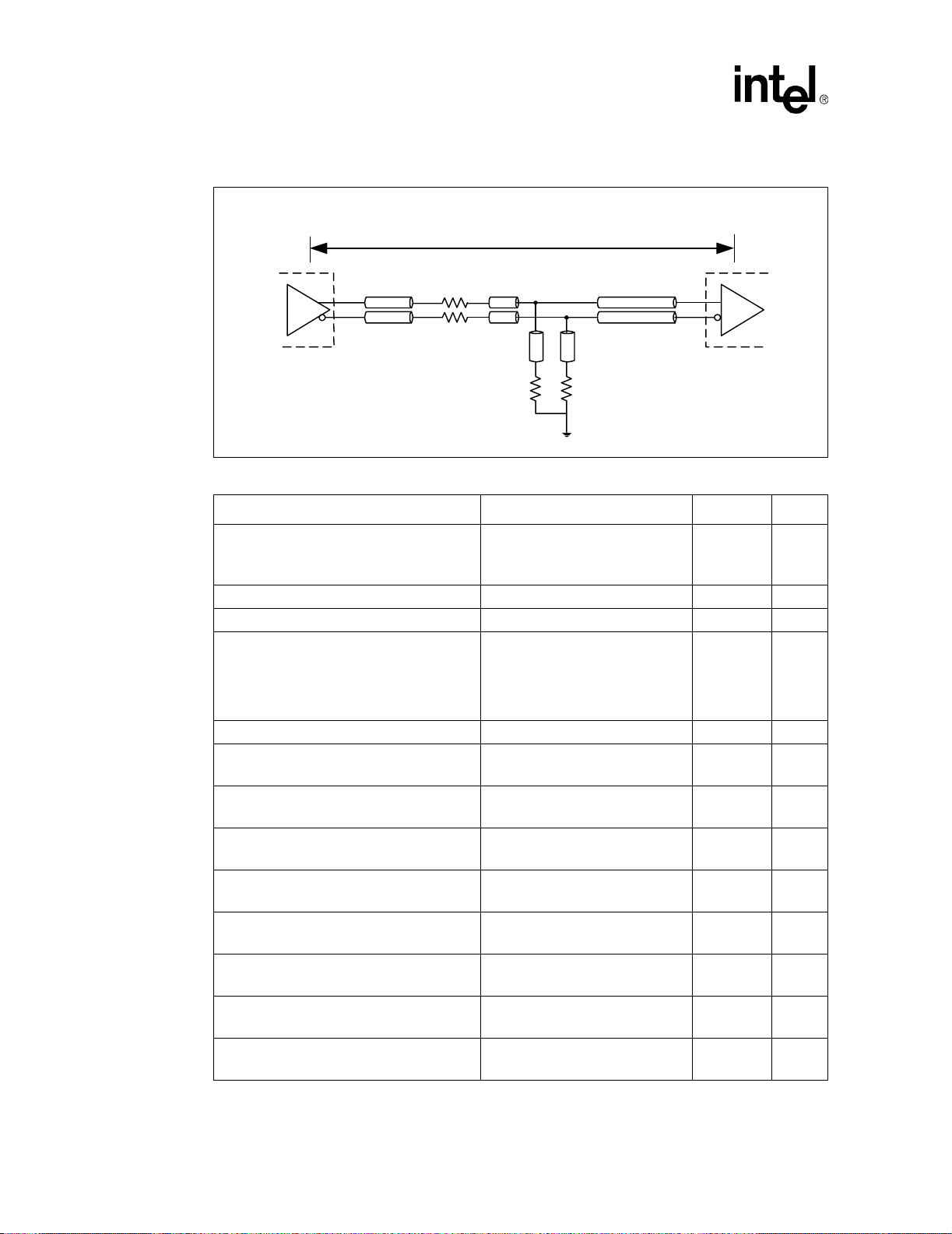

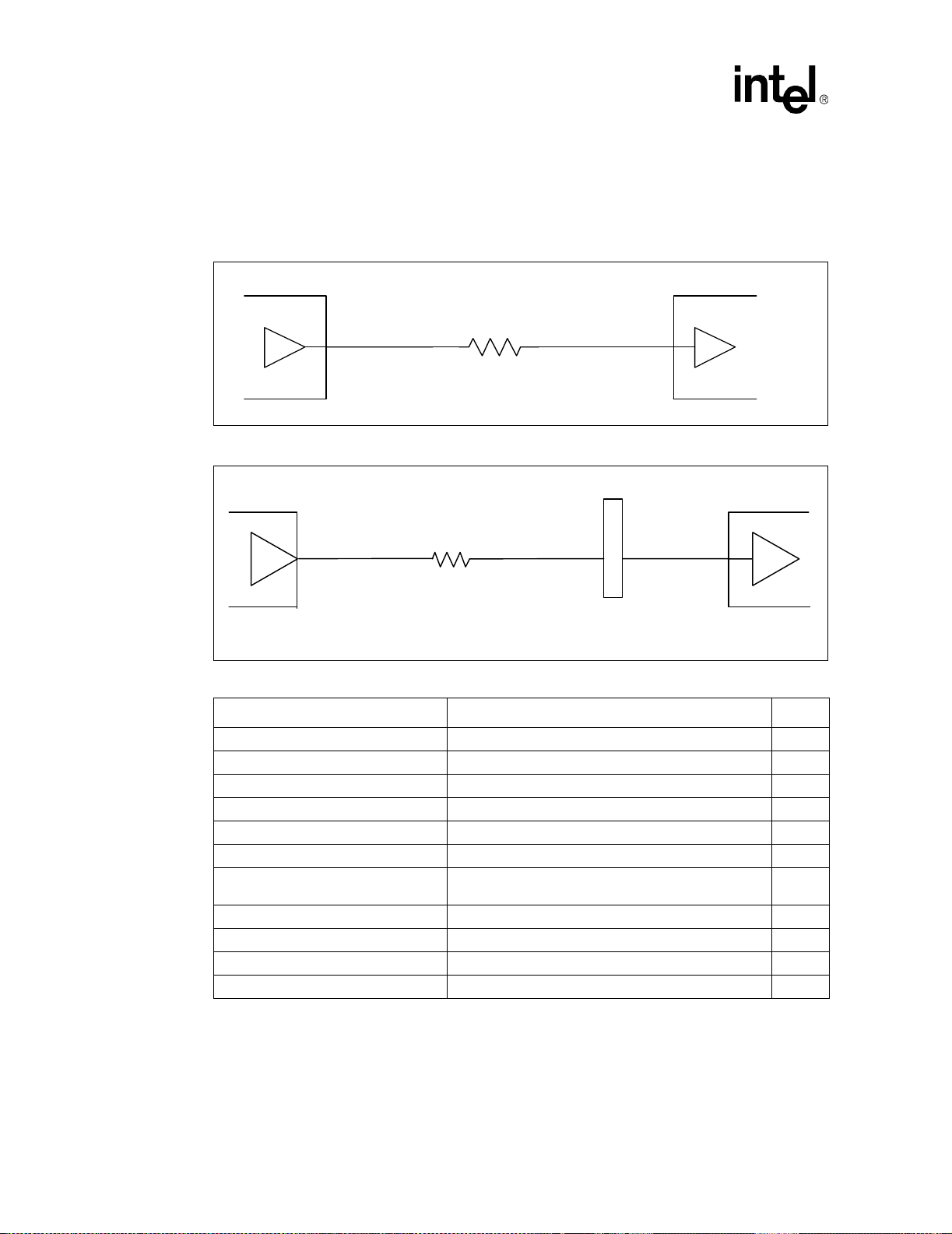

4-2 Source Shunt Termination .................................................................................. 48

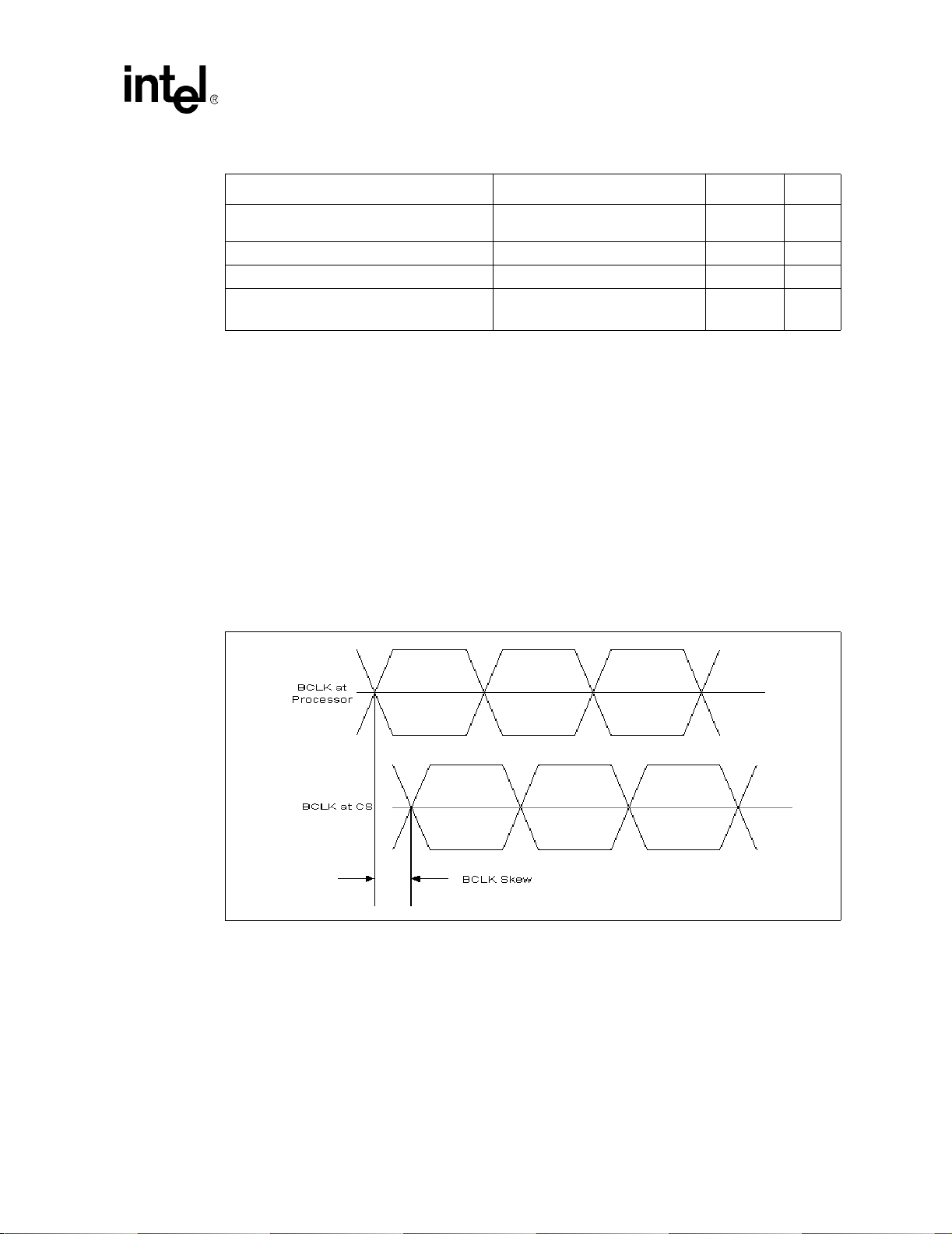

4-3 Clock Skew As Measured from Agent to Agent .................................................. 49

4-4 Trace Spacing for HOST_CLK Clocks ................................................................ 50

4-5 66 MHz/33 MHz Clock Relationships .................................................................. 50

4-6 33 MHz Clock Relationships ............................................................................... 51

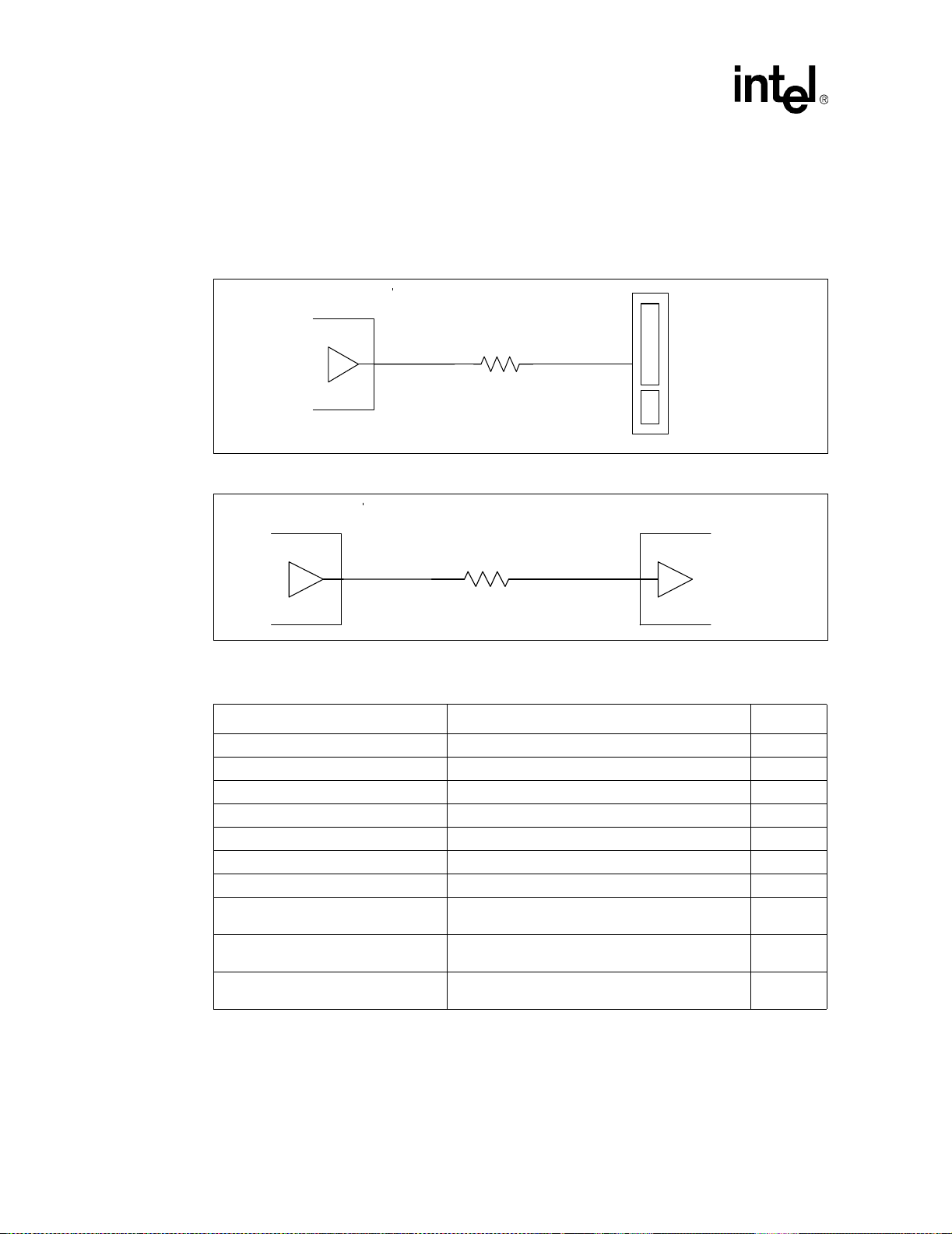

4-7 Topology for CLK33 to Down Devices ................................................................ 52

4-8 Topology for CLK33 to PCI Slot .......................................................................... 52

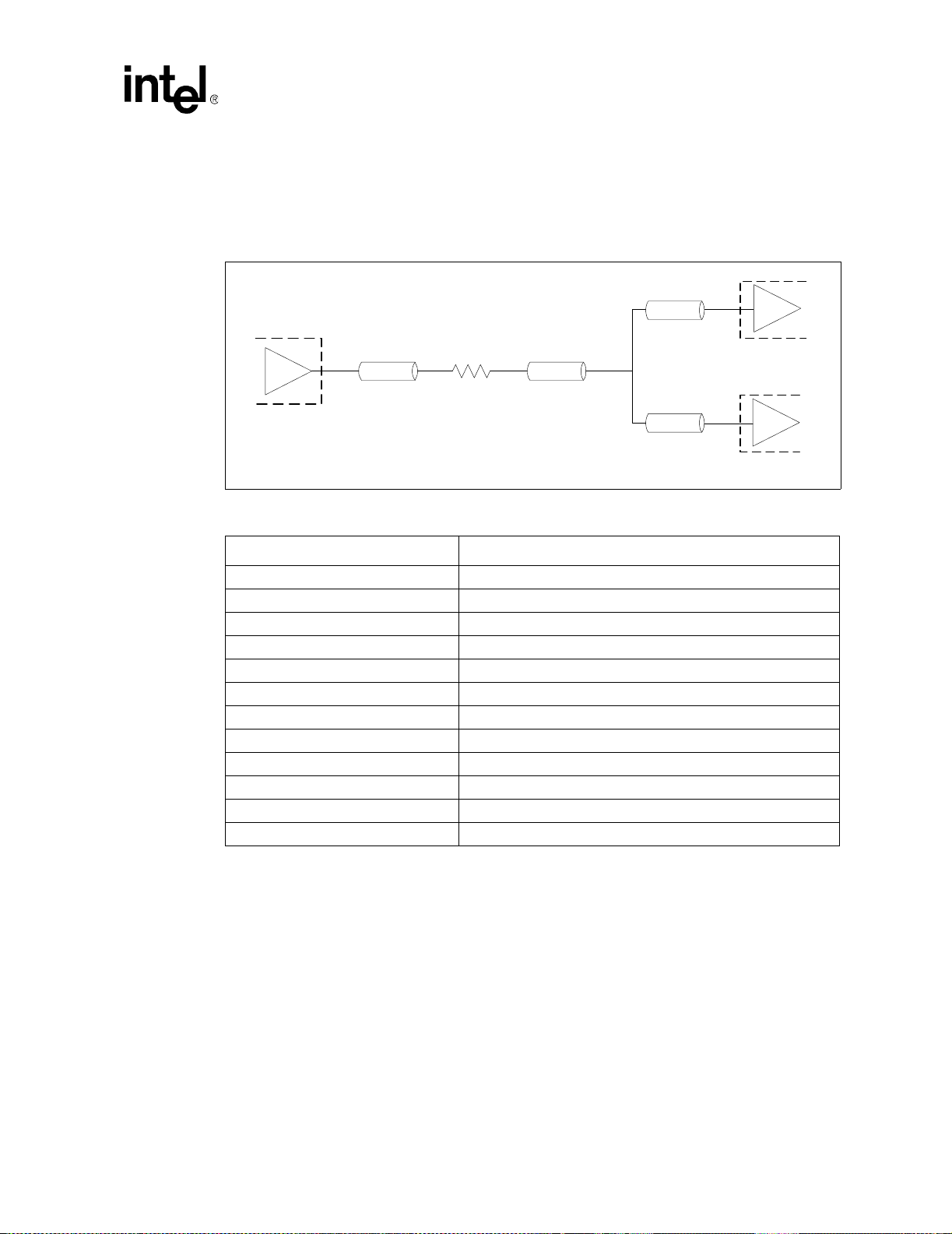

4-9 Topology for Sharing CLK33 between Two PCI Down Devices ......................... 53

4-10 Topology for CLK66 to AGP Connector .............................................................. 54

4-11 Topology for CLK66 to MCH, Intel

®

ICH5, and Intel® 82647EI GbE

Controller............................................................................................................. 54

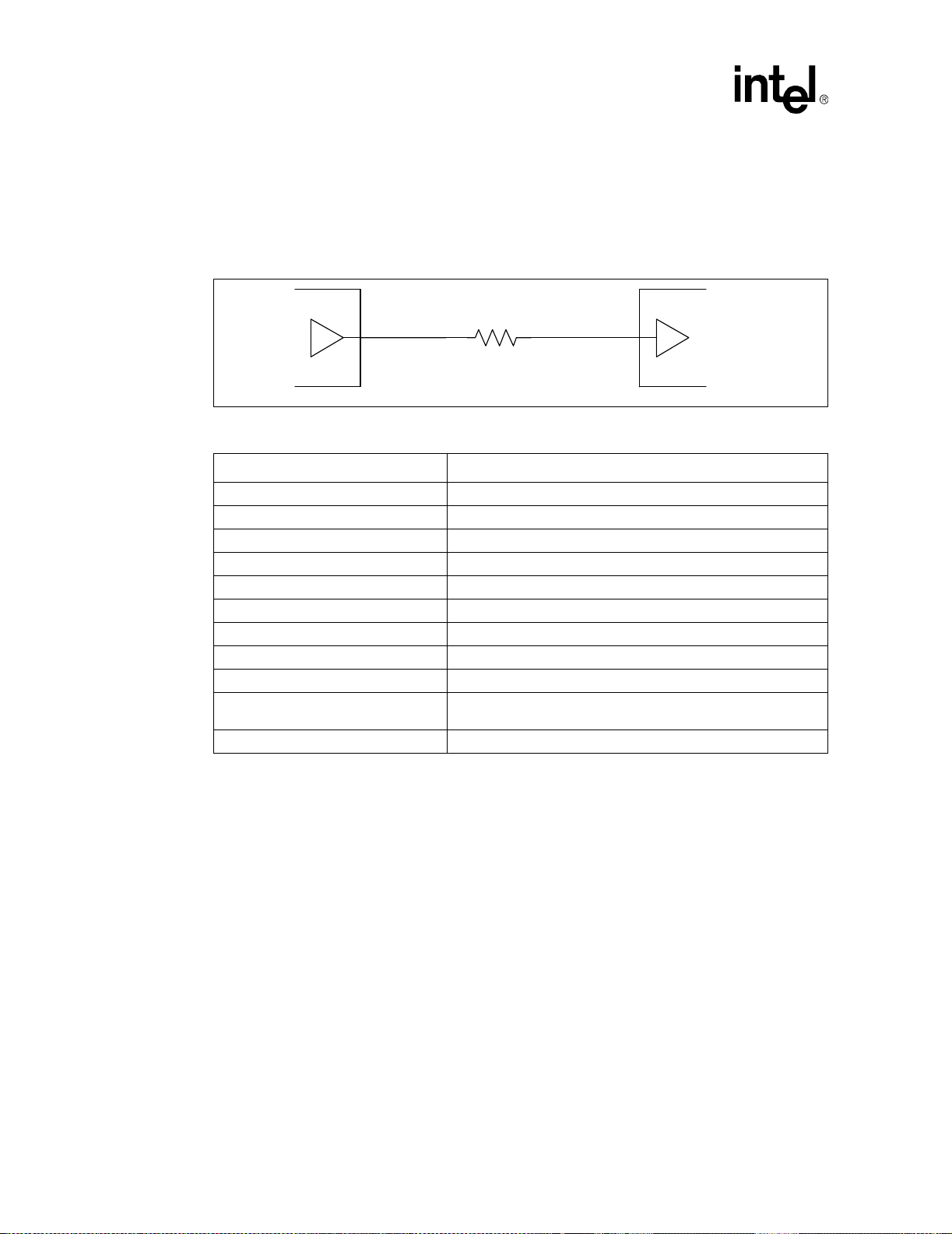

4-12 Topology for CLK14 ............................................................................................ 55

4-13 Topology for USBCLK......................................................................................... 56

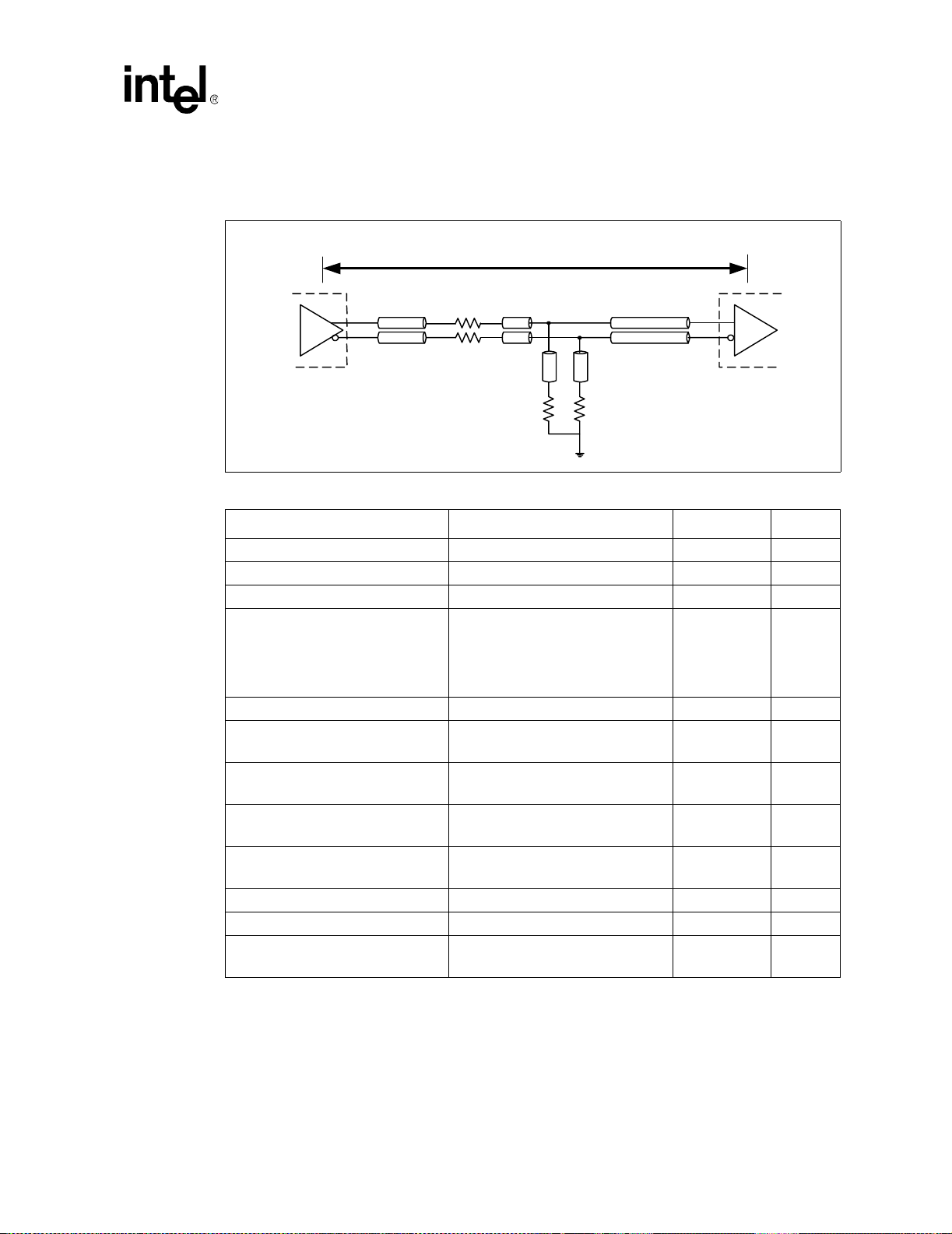

4-14 Source Shunt Termination .................................................................................. 57

4-15 Trace Spacing for SRC Clocks ........................................................................... 58

4-16 Decoupling Capacitors Placement and Connectivity .......................................... 60

5-1 Spacing Diagram................................................................................................. 62

5-2 Topology 1 .......................................................................................................... 66

5-3 Routing Illustration for FERR# and THERMTRIP# ............................................. 66

12 Intel® 875P Chipset Platform Design Guide

5-4 Routing Illustration for A20M#, IGNNE#, SMI#, SLP#, STPCLK#,

and LINT[1:0]....................................................................................................... 67

5-5 Routing Illustration for IERR................................................................................ 67

5-6 Routing Illustration for RESET# and BR0# .........................................................68

5-7 INIT# Topology.................................................................................................... 69

5-8 Voltage Translation of INIT#................................................................................ 69

5-9 Routing Illustration for PWRGOOD .....................................................................70

5-10 Routing Illustration for PROCHOT# .................................................................... 70

5-11 Routing Illustration for TESTHI and Signals ........................................................71

5-12 Routing Illustration for COMP[1:0]....................................................................... 71

5-13 VRD Feedback Switching Diagram .....................................................................72

5-14 Routing Illustration for BOOTSELECT ................................................................72

5-15 HD_VREF Circuit Topology................................................................................. 73

5-16 VID Topology....................................................................................................... 74

5-17 Host SWING Routing Example ........................................................................... 75

5-18 BSEL Topology ................................................................................................... 76

5-19 Trace Length Matching for the Front Side Bus.................................................... 77

5-20 Retention Mechanism Keep-Out Drawing 1 ........................................................ 79

5-21 Retention Mechanism Keep-Out Drawing 2 ........................................................ 80

5-22 Processor Location Recommendation for Chassis Air Guide Relative to

Retention Mechanism.......................................................................................... 81

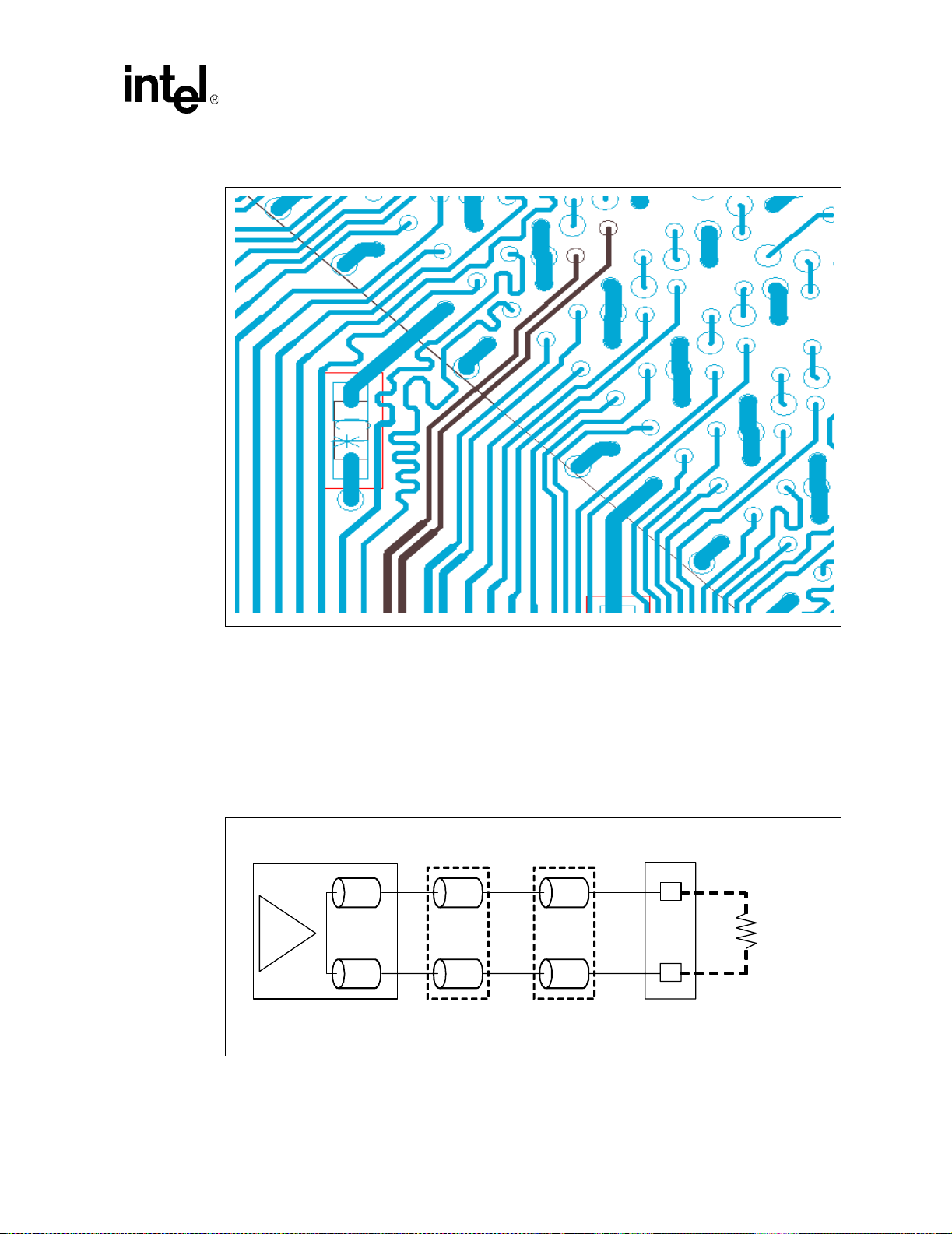

6-1 Example of Ground Flood on Layer 2 ................................................................. 87

6-2 Example of DDR Clock Neckdown at MCH......................................................... 89

6-3 DDR Differential Clock Routing Topology ........................................................... 89

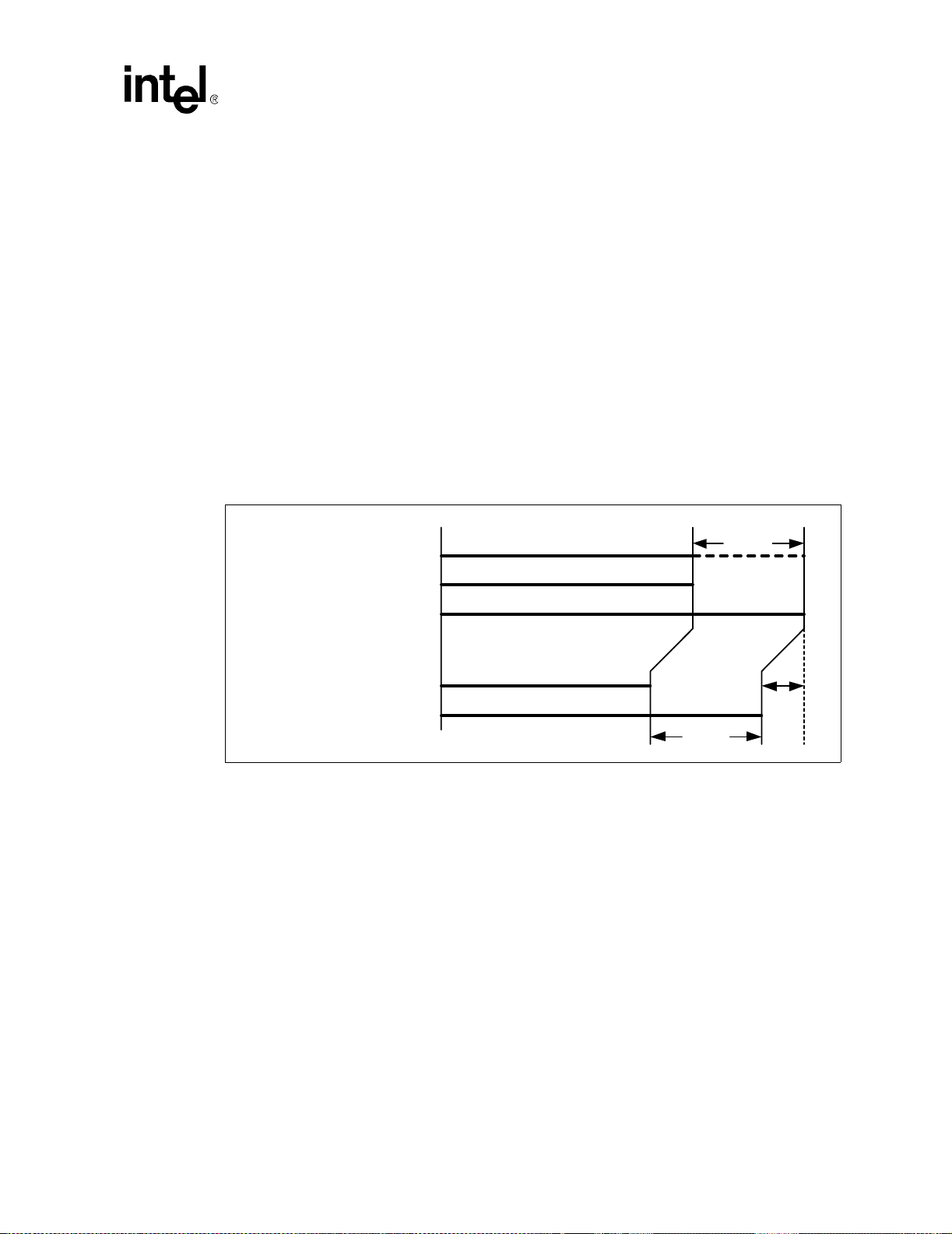

6-4 Clock-to-Clock Length Matching Requirements .................................................. 91

6-5 Control Signal Group Routing Topology.............................................................. 92

6-6 Control Signal-to-Clock Length Matching Requirements ....................................94

6-7 DDR Address/Command Routing Topology........................................................ 95

6-8 Address/Command-to-Clock Length Matching Requirements ............................ 96

6-9 Data Signal Routing Topology............................................................................. 97

6-10 SDQS-to-Clock Length Matching Requirements................................................. 99

6-11 SDQ/SECC-to-SDQS Length Matching Requirements ..................................... 100

6-12 DDR VREF Generation Example Circuit at the MCH ........................................ 102

6-13 DDR VREF Generation Example Circuit at the DIMMs..................................... 103

6-14 DDR (SMRCOMP) Resistive Compensation..................................................... 104

6-15 DDR SMRCOMP Resistor Divider Power (Flood vs. Package) ........................105

6-16 DDR RCOMP V

and VOL Circuitry ................................................................ 106

OH

7-1 Hub Interface Routing Example ........................................................................ 107

7-2 Hub Interface Signal Routing Topology............................................................. 108

7-3 Hub Interface Single HIVREF/HISWING Generation Circuit ............................. 109

7-4 Hub Interface Local HIVREF/HISWING Generation Circuit

®

(Intel

ICH5 Side)..............................................................................................110

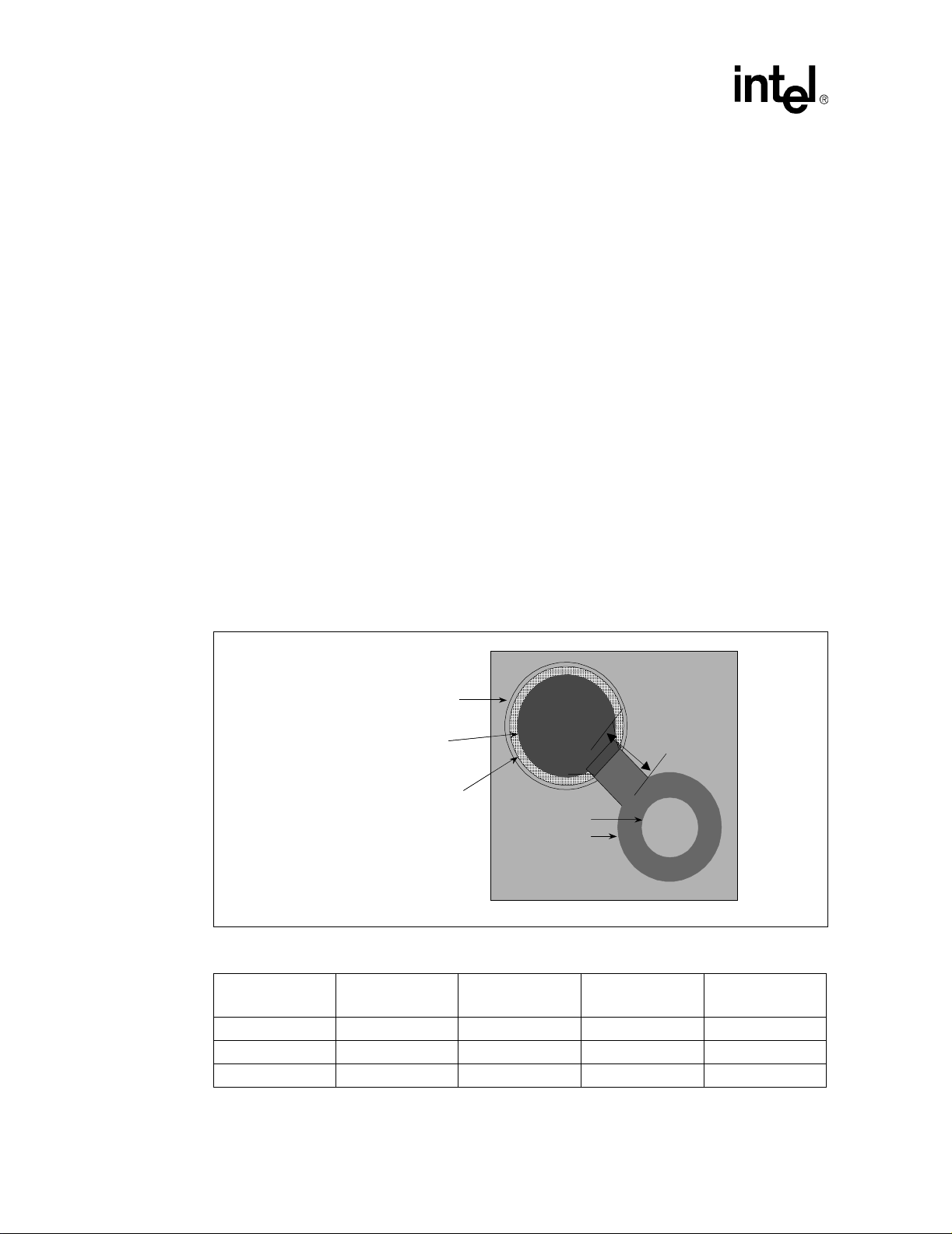

8-1 Spacing to Dielectric Height Diagram................................................................ 113

8-2 AGP Mode Detection Circuit – Option 1 ............................................................ 116

8-3 AGP Mode Detection Circuit – Option 2 ............................................................ 116

8-4 GVREF/GSWING Circuit...................................................................................117

9-1 CSA Port Signal Routing Topology ...................................................................119

9-2 CSA Port Locally Generated Reference Divider Circuits ..................................121

9-3 CSA Port RCOMP Circuits................................................................................ 122

10-1 Data Strobing Example ..................................................................................... 123

Intel® 875P Chipset Platform Design Guide 13

10-2 Correct Strobing Example (no noise) ................................................................ 124

10-3 Effect of Crosstalk on Strobe Signal ................................................................. 124

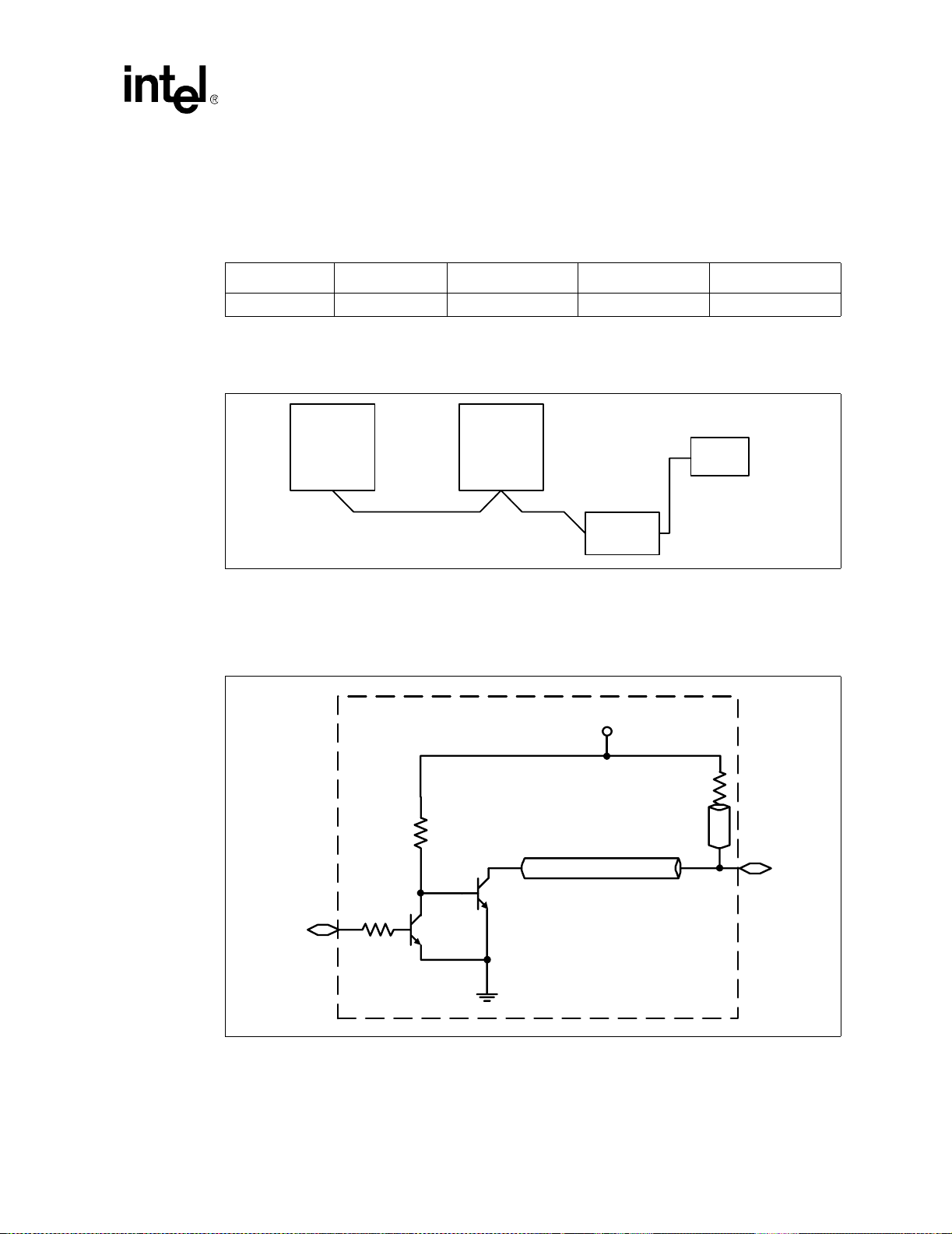

10-4 Combination Host-Side/Device-Side IDE Cable Detection ............................... 126

10-5 Device Side IDE Cable Detection ..................................................................... 127

10-6 Connection Requirements for Primary IDE Connector ..................................... 128

10-7 Connection Requirements for Secondary IDE Connector................................. 129

10-8 SATA Layout and Routing Example.................................................................. 130

10-9 Recommended Serial ATA Trace Spacing Table 10-3 ..................................... 131

10-10 SATARBIAS/SATARBIAS# Connection............................................................ 132

10-11 SATALED# Circuitry Example........................................................................... 132

10-12 SATA Cable 90º Bend Height Example ............................................................ 133

10-13 SATA Host Connector Placement Region Recommendations ......................... 133

10-14 SATA Host Connector Placement ATX Area B Example.................................. 134

10-15 Example of Poor Host Connector Placement.................................................... 135

10-16 Minimum Host Connector Placement Spacing from SATA Specification.......... 135

10-17 Intel

10-18 Intel

10-19 Intel

10-20 Intel

®

ICH5 AC '97 (Codec Connection) ........................................................... 136

®

ICH5 AC '97 – AC_BIT_CLK Topology ................................................... 137

®

ICH5 AC '97 – AC_SDOUT/AC_SYNC Topology ................................... 138

®

ICH5 AC '97 – AC_SDIN Topology ......................................................... 139

10-21 AC '97 Power Plane Configurations .................................................................. 142

10-22 AC '97 Analog Power Delivery .......................................................................... 143

10-23 Example Speaker Circuit................................................................................... 145

10-24 CNR Interface ................................................................................................... 146

10-25 Motherboard AC ’97 CNR Implementation with a Single Codec

down on Board .................................................................................................. 147

10-26 Motherboard AC ’97 CNR Implementation with No Codec down on Board ...... 148

10-27 Recommended USB Trace Spacing ................................................................. 150

10-28 USBRBIAS/USBRBIAS# Connection................................................................ 150

10-29 Good Downstream Power Connection.............................................................. 153

10-30 A Common-Mode Choke................................................................................... 153

10-31 Front Panel Header Schematic ......................................................................... 156

10-32 Motherboard Front Panel USB Support ............................................................ 157

10-33 Example PIRQ Routing ..................................................................................... 158

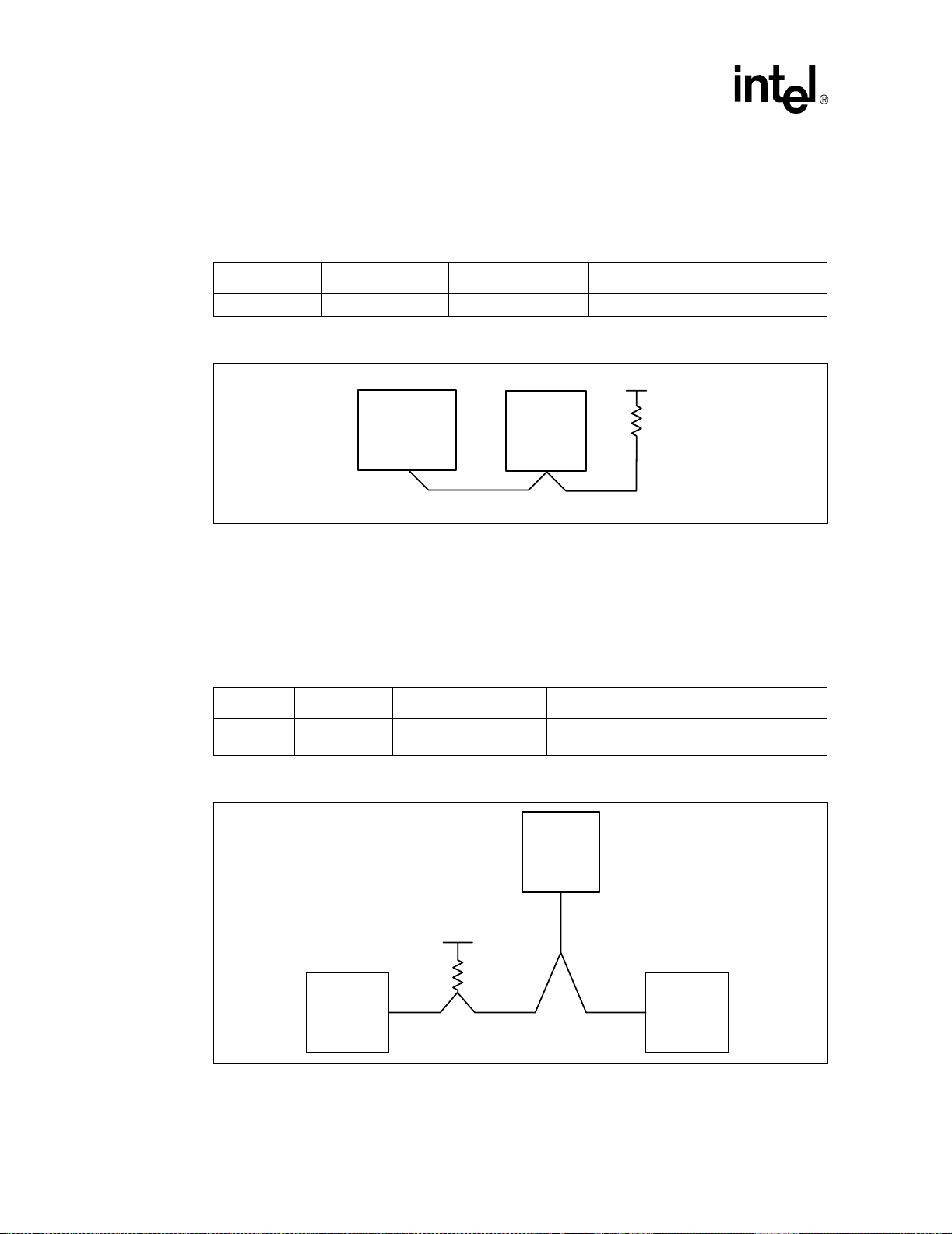

10-34 SMBUS 2.0/SMLink Interface ........................................................................... 159

10-35 High Power/Low Power Mixed VCC_SUSPEND/ VCC_CORE_

Architecture ....................................................................................................... 160

10-36 PCI Bus Layout Example .................................................................................. 162

10-37 PCI Bus Layout Example with IDSEL ............................................................... 162

10-38 RTCX1 and SUSCLK Relationship in Intel

10-39 External Circuitry for the Intel

10-40 External Circuitry for the Intel

®

ICH5 Where the Internal RTC Is Not Used...... 164

®

ICH5 RTC ........................................................ 165

10-41 A Diode Circuit to Connect RTC External Battery ............................................. 167

10-42 RTCRST# External Circuit for the Intel

10-43 Intel

®

ICH5/Platform LAN Connect Sections..................................................... 171

®

ICH5 ............................................ 164

®

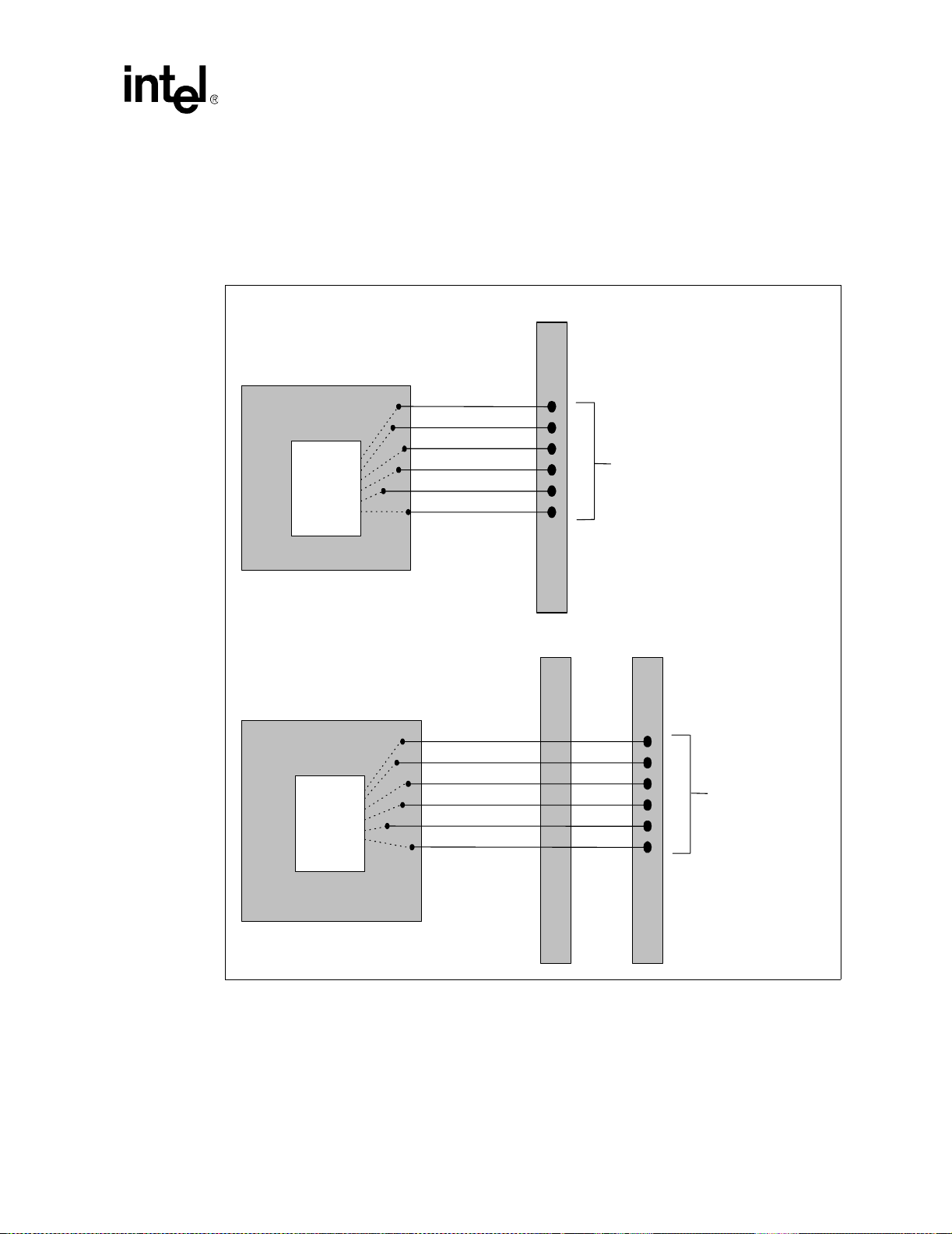

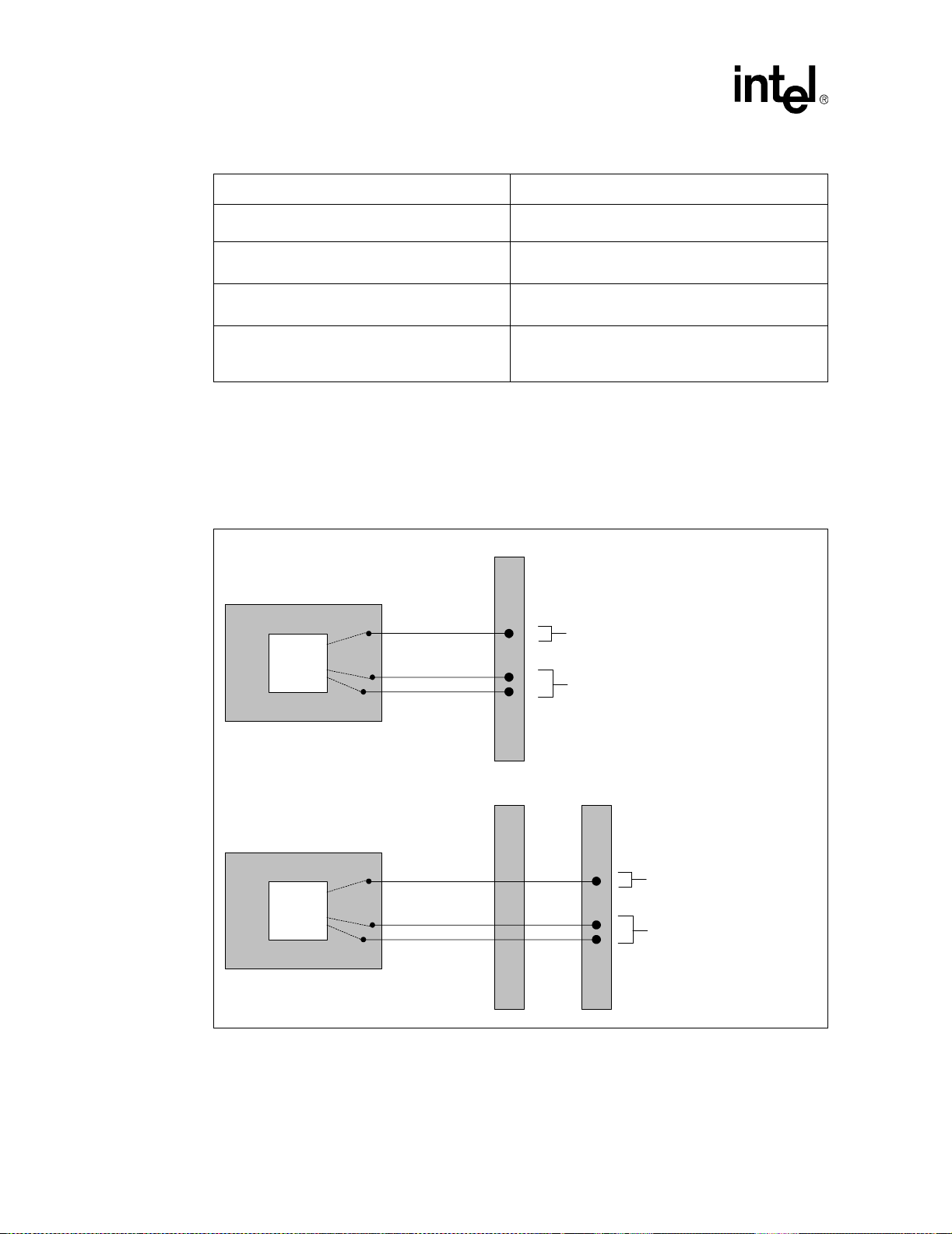

ICH5 RTC.......................................... 168

10-44 Single Solution Interconnect ............................................................................. 172

10-45 LOM/CNR Interconnect..................................................................................... 173

10-46 LAN_CLK Routing Example.............................................................................. 174

10-47 Intel

®

82562EZ/ET/EX/EM PLC Components/ Intel® 82551QM PLC

Components Termination .................................................................................. 175

10-48 Critical Dimensions for Component Placement................................................. 176

14 Intel® 875P Chipset Platform Design Guide

10-49 Critical Dimensions for Component Placement .................................................177

10-50 Termination Plane .............................................................................................179

10-51 Intel

®

82562EZ/ET/EX/EM PLC Components Disable Circuitry ....................... 180

10-52 Trace Routing.................................................................................................... 181

10-53 Ground Plane Separation.................................................................................. 183

10-54 TPM LPC Block Diagram .................................................................................. 186

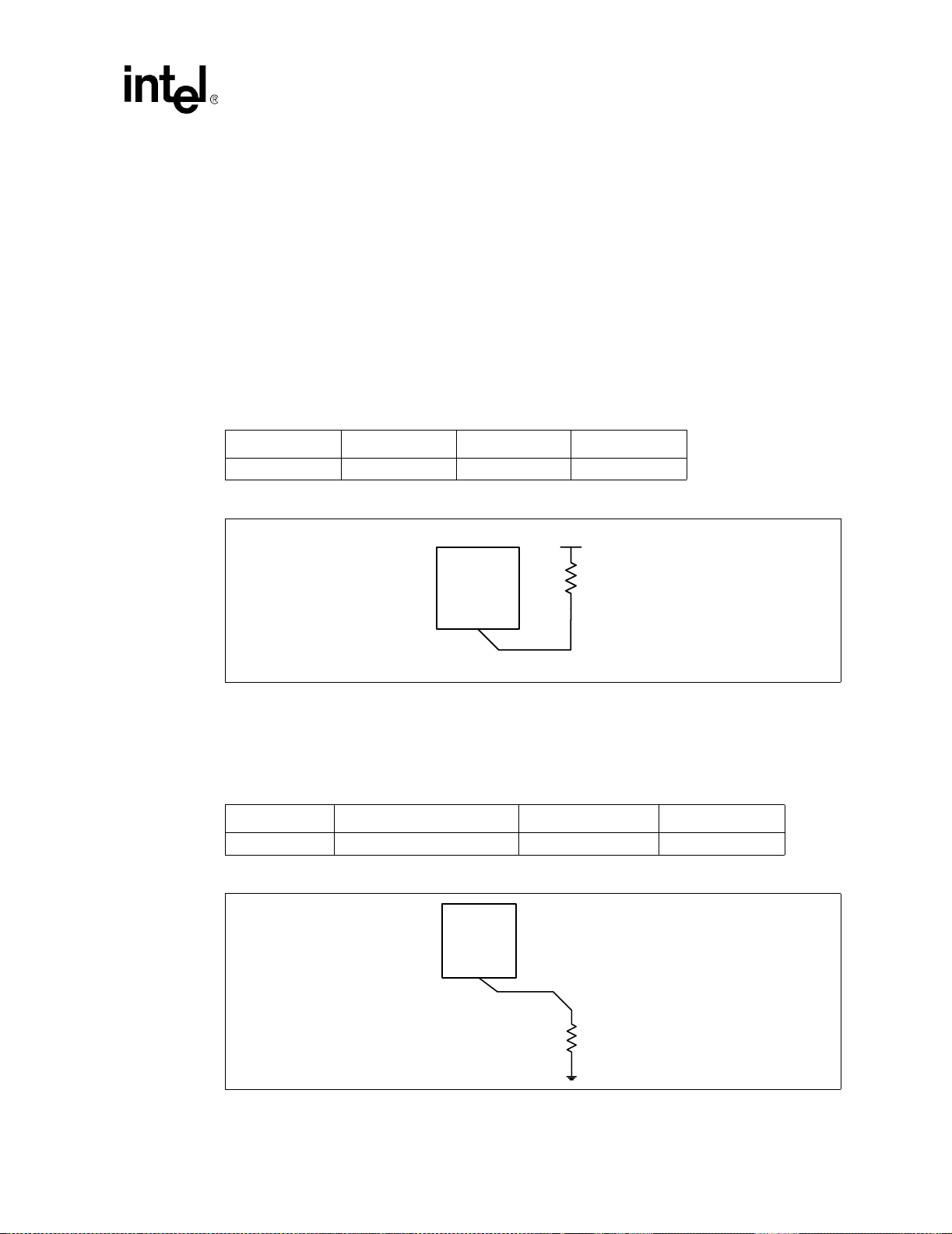

12-1 RSMRST# Generation from VCCSUS3_3 ........................................................ 191

12-2 PWROK Generation from PWR_OK Output of ATX Supply .............................191

12-3 PS_ON Generation from SLP_S3# ...................................................................192

12-4 PS_ON Generation from SLP_S3# and SKTOCC# ..........................................192

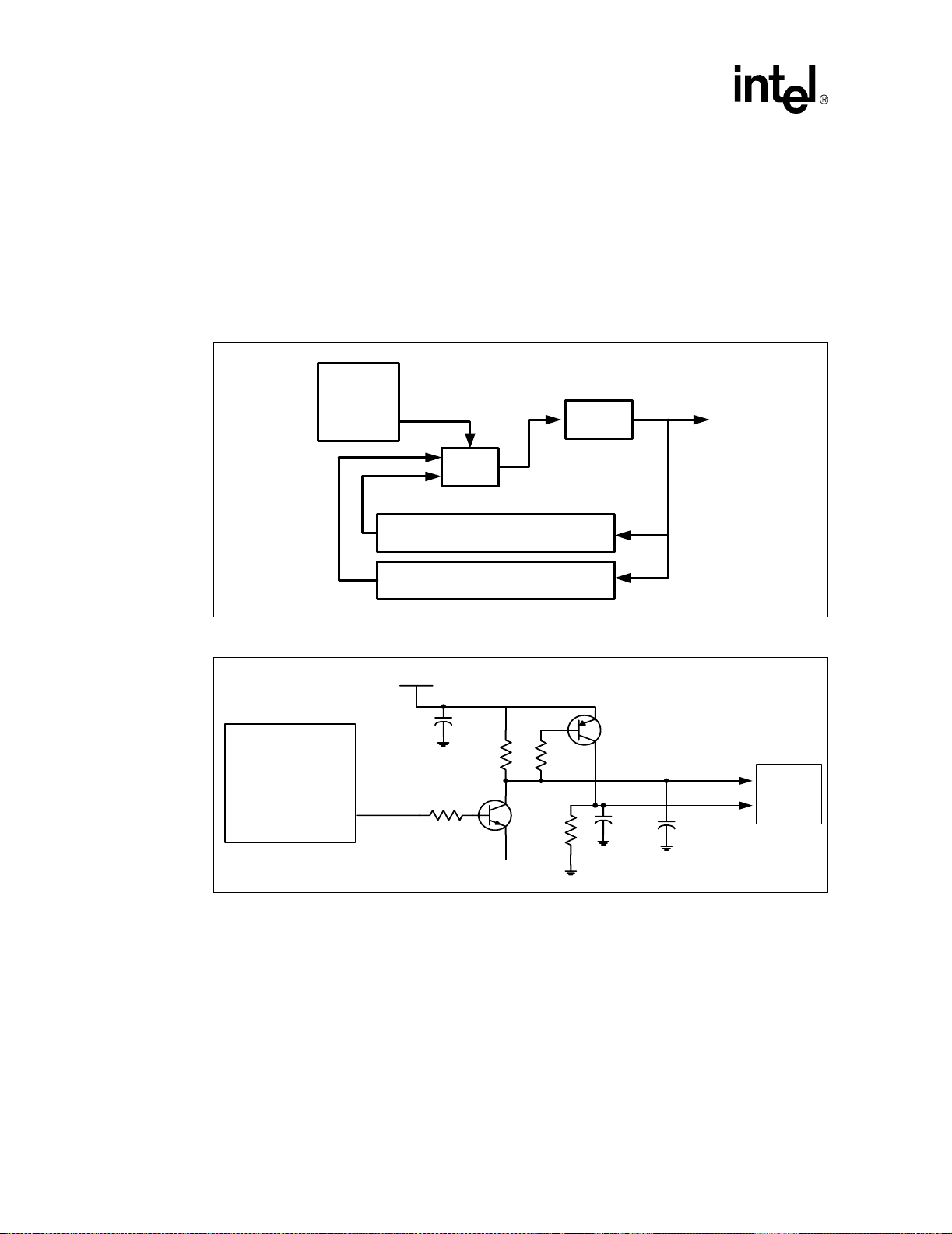

12-5 Intel ICH5 Processor CMOS Signals with Processor and Flash BIOS.............. 193

13-1 SYS_RESET# and PWRBTN# Connection ...................................................... 201

13-2 RTC Power Well Isolation Control..................................................................... 202

14-1 Flash BIOS Signal Topology Solution ...............................................................204

14-2 Flash BIOS Level Translation Circuitry ............................................................. 205

14-3 Flash BIOS VPP Circuitry.................................................................................. 205

15-1 Customer Reference Board Power Delivery Map ............................................. 209

15-2 Minimized Loop Inductance Example................................................................ 212

15-3 2 Phase VR Component Placement Example................................................... 214

15-4 Decoupling Placement ......................................................................................216

15-5 Top Layer Power Delivery Shape (VCC_CPU) ................................................. 217

15-6 Layer 2 Power Delivery Shape (VSS) ............................................................... 217

15-7 Bottom Layer Power Delivery Shape (VCC_CPU) ............................................ 218

15-8 Capacitor Orientation ........................................................................................218

15-9 Shared Ground and Power Vias........................................................................ 219

15-10 Routing of Feedback Signal .............................................................................. 220

15-11 Example VR Thermal Monitor Circuit ................................................................221

15-12 Detailed Power Distribution Model for Processor with Voltage Regulator on

System Board....................................................................................................222

15-13 VCC_VID Regulator Topology ..........................................................................223

15-14 Example of VCC_VID Routing (Layer 1) ........................................................... 223

15-15 Typical VCCIOPLL, VCCA, and VSSA Power Distribution ...............................224

15-16 AC Filter Specification ....................................................................................... 225

15-17 VCCA and VSSA Routing (Layer 1) .................................................................. 226

15-18 VCCA and VSSA Routing (Layer 4) .................................................................. 226

15-19 DDR Power Plane (Layer 1).............................................................................. 229

15-20 2.6 V DDR Power Plane (Layer 2) ....................................................................230

15-21 VTT (MCH FSB Power Plane) (Layer 1) ...........................................................230

15-22 VTT (MCH FSB Power Plane) (Layer 2) ...........................................................231

15-23 1.5 V Power Plane (Layer 1) ............................................................................. 231

15-24 1.5 V Power Plane (Layer 2) ............................................................................. 232

15-25 1.5 V Power Plane (Layer 4) ............................................................................. 232

15-26 MCH High-Frequency Decoupling Capacitor Placement .................................. 234

15-27 MCH Bulk Decoupling Capacitor Placement..................................................... 235

15-28 MCH Filter Topology for 1.5 V Core ..................................................................236

15-29 MCH Analog Filter Topologies .......................................................................... 237

15-30 Layer 1 VCCA_DDR.......................................................................................... 238

15-31 Layer 4 VCCA_DDR.......................................................................................... 238

15-32 DDR DIMMs Layer 1 Power Delivery ................................................................239

15-33 DDR DIMMS Layer 4 Power Delivery ...............................................................239

Intel® 875P Chipset Platform Design Guide 15

Tables

15-34 DDR DIMM High-Speed Decoupling ................................................................. 240

15-35 DDR DIMM VTT High-Speed Decoupling ......................................................... 240

15-36 Example 3.3 V/V5REF Sequencing Circuitry .................................................... 242

15-37 Intel

15-38 Intel

®

ICH5 Layer 1 Power Delivery .................................................................. 243

®

ICH5 Layer 2 Power Delivery .................................................................. 243

15-39 Layer 2 Close Up .............................................................................................. 244

15-40 Layer 2 Close Up .............................................................................................. 244

15-41 Intel

15-42 Intel

15-43 Intel

®

ICH5 Layer 4 Power Delivery .................................................................. 245

®

ICH5 Decoupling Capacitor Placement for VccSus1_5 .......................... 247

®

ICH5 Example Decoupling Capacitor Placement .................................... 247

16-1 Spread Spectrum Modulation Profile ................................................................ 251

16-2 impact of Spread Spectrum Clocking on Radiated Emissions .......................... 251

16-3 Cancellation of H-fields Through Inverse Currents ........................................... 252

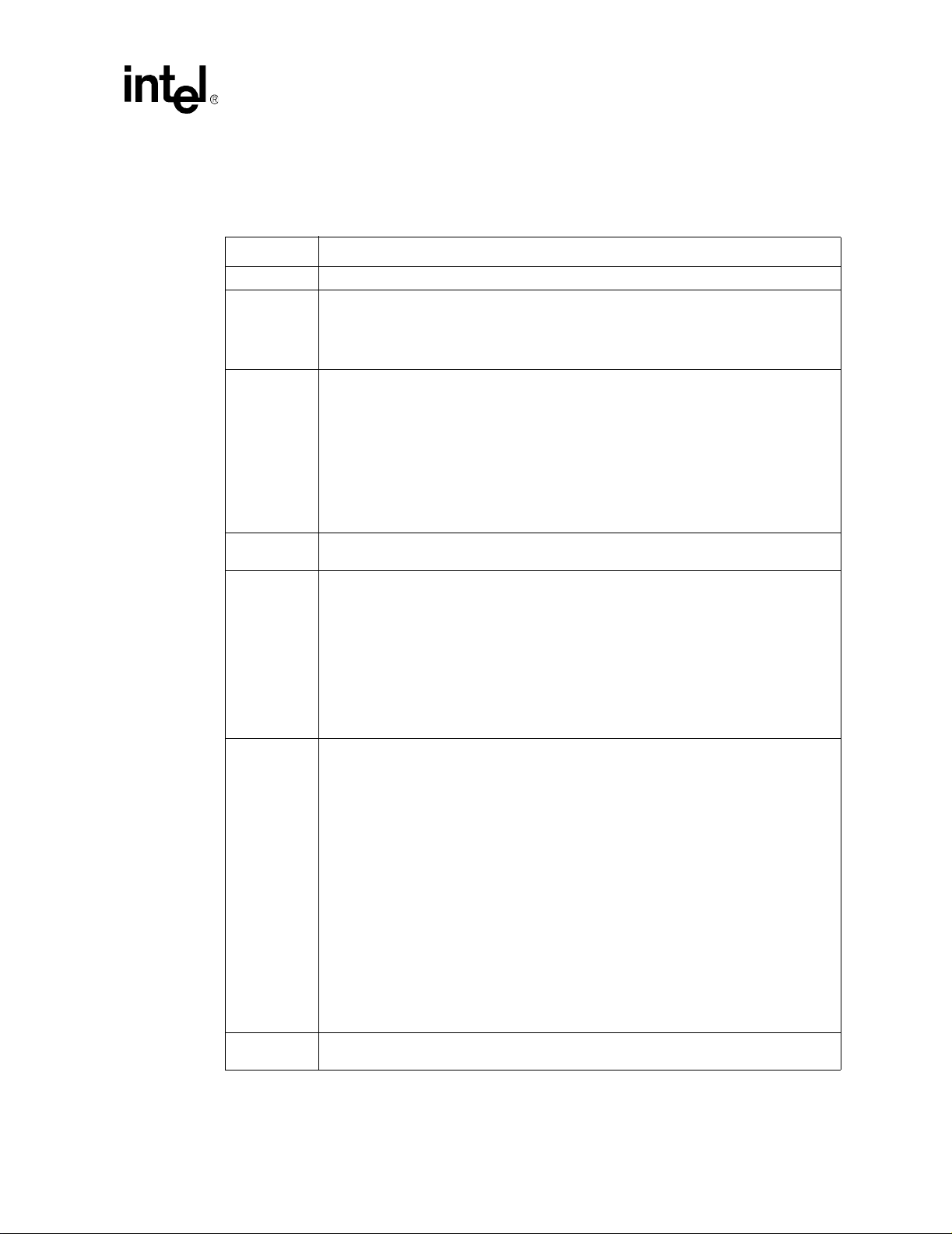

1-1 Intel® ICH5 Conventions and Terminology ......................................................... 25

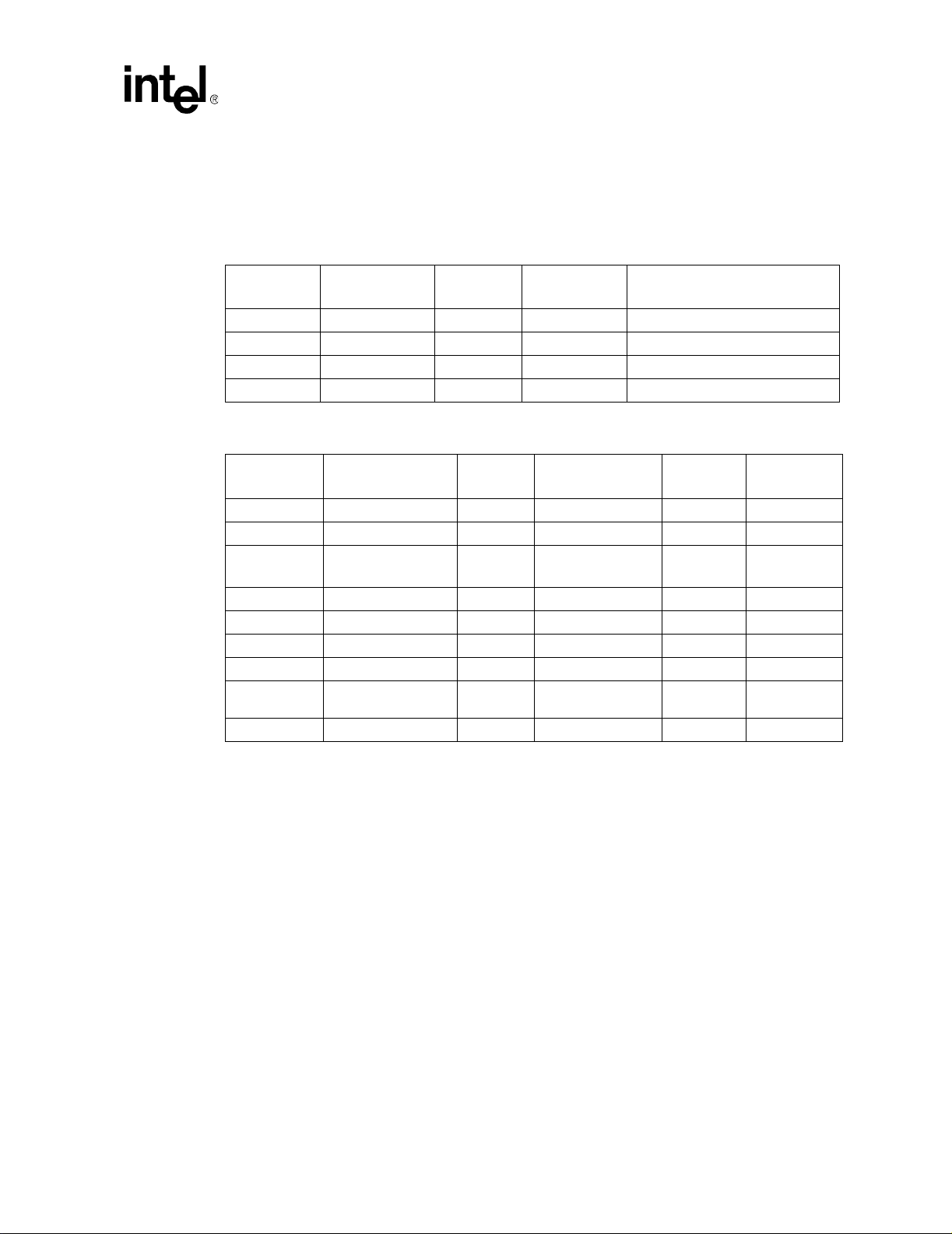

2-1 LAN Component Overview.................................................................................. 29

2-2 MCH System Bandwidth Summary..................................................................... 33

2-3 Intel

®

ICH5 System Bandwidth Summary ........................................................... 33

3-1 Via-Pad Layout Metal-Defined Pads ................................................................... 38

3-2 Via-Pad Layout Solder Mask-Defined Pads ........................................................ 39

4-1 Intel

®

875 Chipset Clock Group .......................................................................... 45

4-2 Host Clock Frequency Select on CK409 ............................................................. 47

4-3 HOST_CLK[1:0]# Routing Guidelines ................................................................. 48

4-4 CLK33 Routing Guidelines to Intel

®

ICH5, Flash BIOS, SIO, and PCI Slots ......52

4-5 CLK33 Routing Guidelines for Sharing CLK33 between Two PCI

Down Devices ..................................................................................................... 53

4-6 CLK66 Routing Guidelines for CLK66 to MCH, Intel

®

Intel

82647EI GbE Controller and AGP Connector ........................................... 54

®

ICH5,

4-7 CLK14 Routing Guidelines.................................................................................. 55

4-8 USBCLK Routing Guidelines .............................................................................. 56

4-9 SCR/SCR# Routing Guidelines........................................................................... 57

5-1 System Bus Signal Groups ................................................................................. 61

5-2 1X, 2X and 4X Signal Groups ............................................................................. 62

5-3 Address and Data, and Associated Strobe Pairs ................................................ 62

5-4 4X Routing Guidelines ........................................................................................ 63

5-5 2X Routing Guidelines ........................................................................................ 63

5-6 1X Routing Guidelines ........................................................................................ 64

5-7 Routing Guidelines for Asynchronous AGTL+ Signals........................................ 65

5-8 Layout Recommendations for FERR# and THERMTRIP# ................................. 66

5-9 Layout Recommendations for Miscellaneous Signals......................................... 67

5-10 Layout Recommendations for IERR#.................................................................. 67

5-11 Layout Recommendations for RESET# and BR0# ............................................. 68

5-12 Layout Recommendations For INIT# .................................................................. 69

5-13 Layout Recommendations for PWRGOOD ......................................................... 70

5-14 Layout Recommendations for PROCHOT# ........................................................ 70

5-15 Layout Recommendations for TESTHI Signals................................................... 71

5-16 Layout Recommendations for COMP[1:0] .......................................................... 71

16 Intel® 875P Chipset Platform Design Guide

5-17 Host VREF Resistor Values ................................................................................ 73

5-18 Host VREF Trace Lengths .................................................................................. 74

5-19 VID Topology Trace Lengths............................................................................... 74

5-20 BSEL Resistor Values .........................................................................................76

5-21 FSB Frequency Selection.................................................................................... 76

5-22 Reference Solution Fan Power Header Pinout ................................................... 81

5-23 Boxed Processor Fan Power Header Pinout....................................................... 82

6-1 MCH DDR Signal Groups.................................................................................... 83

6-2 Length Matching Formulas..................................................................................85

6-3 DDR Channel Referencing Stack-Up .................................................................. 86

6-4 Clock Signal DIMM Mapping per DIMM ..............................................................88

6-5 Clock Signal Group Routing Guidelines ..............................................................90

6-6 Control Signal-to-DIMM Mapping ........................................................................ 92

6-7 Control Signal Group Routing Guidelines ...........................................................92

6-8 Address/Command Signal Group Routing Guidelines ........................................ 95

6-9 SDQ and SECC to SDQS Mapping..................................................................... 97

6-10 Data Signal Group Routing Guidelines ...............................................................97

6-11 DDR VREF Generation Requirements at the MCH........................................... 103

6-12 DDR VREF Generation Requirements at the DIMMs ....................................... 104

6-13 DDR SMRCOMP Requirements ....................................................................... 105

6-14 DDR RCOMP V

and VOL Requirements ....................................................... 106

OH

7-1 Hub Interface Routing Parameters....................................................................108

7-2 Hub Interface HIVREF/HISWING Generation Circuit Specifications................. 109

7-3 RCOMP Resistor Values................................................................................... 110

8-1 Signal Groups.................................................................................................... 111

8-2 Associated First and Second Strobes ............................................................... 111

8-3 Motherboard Interconnect Requirements..........................................................112

9-1 CSA Port Signal Groups.................................................................................... 119

9-2 CSA Port Routing Parameters ..........................................................................120