Intel 82815E (GMCH) Intel Celeron/Intel Pentium III Processor - Low Power/Ultra Low Power (BGA2) and Intel 815E Chipset Design Guide

R

Intel®Celeron®/Intel®Pentium®III

Processor - Low Power/Ultra

®

Low Power (BGA2) and Intel

815E Chipset

Design Guide

May 2002

Document Number: 273630-001

Introduction

R

Information in this Information in this document is provided in connection with I ntel®products.

No license, express or implied, by estoppel orotherwise, to anyintellectual property rights is granted bythis document. Except as provided in I ntel’s

Terms and Conditions of Sale forsuch products, Intel assumes no liabilitywhatsoever,and Inteldisclaims anyexpress or impliedwarranty,relating

to sale and/or use of Intel products including liability orwarrantiesrelating to fitnessfor aparticular purpose, merchantability, orinfringement of any

patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving,or life sustaining applications.

Intel maymake changes tospecifications and product descriptions at any time, without notice.

Designers must notrelyon the absence or characteristics of anyfeatures or instructions marked "reserved"or "undefined." Intel reserves these for

future definition and shall haveno responsibilitywhatsoeverfor conflicts or incompatibilities arising from futurechanges to them.

The Intel® <product name> maycontain design defects or errors known as errata which may cause the product to deviate from published

specifications. Current characterized errata are available on request.

Contact your local Intel sales office or yourdistributor to obtain thelatest specifications and before placing your product order.

Copies of documents which have an ordering number andare referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Copyright © 200x ,Intel Corporation

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic,

DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP,Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4,IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo,

Intel NetBurst, Intel NetStructure, Intel Play, Intel Playlogo, Intel Pocket Concert, IntelSingleDriver, Intel SpeedStep, Intel StrataFlash, Intel

TeamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX,MMX logo, NetPort,

NetportExpress, Optimizer logo, OverDrive, Paragon, PCDads, PC Parents, Pentium, Pentium IIXeon, Pentium IIIXeon, Performance atYour

Command, ProShare, RemoteExpress, Screamline, Shiva,SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The

JourneyInside,T his Way In, TokenExpress, Trillium,Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its

subsidiaries in the United States andother countries.

*Other names and brands maybe claimed as thepropertyof others.

2 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

Revision History

Rev. No. Description Rev. Date

001 Initial Release May2002

Introduction

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 3

Introduction

Table of Contents

1 Introduction ....................................................................................................................5

1.1 Audience............................................................................................................ 5

1.2 Notation and Terminology.................................................................................. 6

1.3 Reference Documents........................................................................................8

2 General Design Considerations......................................................................................9

2.1 Nominal Board Stack-up....................................................................................9

3 Processor Host Bus Design.......................................................................................... 10

3.1 Initial Timing Analysis...................................................................................... 10

3.2 General Topology and Layout Guidelines......................................................... 13

3.3 Simulation Methodology................................................................................... 13

3.3.1 Pre-Layout Simulation....................................................................... 13

3.3.2 Post-Layout Simulation..................................................................... 14

3.4 Layout Rules for GTL+ Signals ........................................................................ 14

3.5 Layout Rules for Non-GTL+ (CMOS) Signals...................................................16

3.5.1 Additional Routing and Placement Considerations ............................16

3.6 Undershoot/Overshoot Requirements............................................................... 16

3.7 Processor Reset Requirements........................................................................ 17

3.8 Debug Port Routing Guidelines........................................................................ 18

3.9 PLL Filter Recommendations........................................................................... 19

3.9.1 Topology...........................................................................................19

3.9.2 Filter Specification ............................................................................ 21

3.10 Decoupling Guidelines for BGA2-based Processors......................................... 23

3.11 Catastrophic Thermal Protection......................................................................23

R

4 Clocking .......................................................................................................................24

4.1 General Clocking Considerations ..................................................................... 24

4.2 Single-Ended Host Bus Clocking Routing......................................................... 24

4.2.1 CLKREF Filter Implementation.......................................................... 26

4.2.2 Single-Ended Clocking BSEL[1:0] Implementation ............................ 27

4.2.3 Clock Driver Decoupling and Power Delivery .................................... 27

5 Processor Host Bus Design Checklist........................................................................... 28

5.1 Introduction......................................................................................................28

5.2 GTL+ Checklist................................................................................................ 28

5.2.1 CMOS (Non-GTL+) Checklist............................................................ 29

5.3 TAP Checklist..................................................................................................29

5.3.1 Miscellaneous Checklist....................................................................30

6 Reference Schematic................................................................................................... 31

4 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

1 Introduction

This document provides design guidelines for developing systems based on the Intel® Celeron®

Processor – Low Power or Ultra Low Power or Intel® Pentium® III - Low Power in a BGA2

packageandtheIntel

presented. Likely design errors have been listed here in a checklist format. These are

recommendations only.

These design guidelines and recommendations have been simulated and validated and strongly

recommended to meet the timing and signal quality specifications. It is recommended that

simulations be performed to meet design-specific requirements.

Note: The system bus speed supported by the design is based on the capabilities ofthe processor,

chipset, and clock driver.

® 815E chipset. Special design recommendations and concerns are

Introduction

1.1 Audience

This document is intended to be used by Intel® Celeron® or Intel® Pentium® III –

LP/ULP/815E system developers.

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 5

Introduction

1.2 Notation and Terminology

This section describes someof the terms used in this document.

Term Description

AGP AcceleratedGraphics Port

GTL+ Refers to processor bus signals that are implemented open drain GTL+ interface

signal.

Bus Agent A componentor group of compo nents that, whencombined, representasingle load on

the AGTL bus.

Crosstalk The reception o na victim network of asignal impose dby aggressor network(s) through

inductive andcapacitivecoupling betweenthenetworks.

• Backward Crosstalk–coupling that creates asignal in avictim network that travels in

the opposite direction as theaggressor signal.

• Forward Crosstalk–coupling that creates a signal in a victim network that travels in

the same direction as the aggressor signal.

• Even ModeCrosstalk–coupling from single or multipleaggressors when all the

aggressors switch in thesa m edirection that thevictim is switching.

• Odd Mode Crosstalk–coupling from single or multipleaggressors when all the

aggressorsswitchin theoppositedirection thatthe victim isswitching.

R

GMCH Graphics and MemoryController Hub. A component o f theIntel®815chipsetplatform

for use withIntel

Power

ICH2 Intel®82801BA I/O Controller Hub component.

ISI Inter-symbol interferenceis theeffect of a previo us signal(o rtra nsition)on the

interconnect dela y. For example ,when asignal is transmitted dow na line and the

reflections due tothetransition have not completelydissipated,thefollowing data

transition launched onto thebus is affected. ISI is dependent upon frequency,time

delay of the line, and the reflection coefficient at the driver and receiver. ISI can impact

both timing andsignalintegrity.

Network Length The distance between agent 0 pins and the agent pins at the far end of the bus.

Pad The electrical contact pointof a semiconductor dietothe package substrate. A padis

onlyobservablein simulation.

Pin The contact point of acomponent packageto the traces on asubstrate such as the

motherboard. Signal qualityand timings can be measured at the pin.

Ringback The voltage thata signal rings back to after achiev ingits maximumabsolute value .

Ringback maybedue to reflections, drive roscillations, or other transmission line

phenome na.

Setup Window The time between thebeginning of Setup to Clock (T

clock edge. This windowmay bedifferent for ea ch type of bus agent in the system.

®

Pentium III-Low Power an dIntel®Celeron-Ultra Low Power/Low

) and the arrival of a valid

SU_MIN

6 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

Introduction

R

Term Description

SSO Simultaneous Switching Output (SSO) Effects refers to the difference in electrical

timing parameters and degradation in signalquality causedbymultiple signal outputs

simultaneously switching voltage levels (e.g., high-to-low) in the opposite direction from

a single signal (e .g.,low-to-high) or inthesamedirection (e.g., high-to-low). These are

respectivelycalled odd-modeswitching and even-modeswitching. This simultaneous

switching of multiple outputs creates highercurrent swings that ma ycause additional

propagation delay (or “push-out”), or a decrease in propagation delay (or “pull-in”).

These SSO effects may impact the setup and/or hold times and are not always taken

into account bysimulations. Systemtimingbudgets need toinclude ma rginfor SSO

effects.

Stub The branch from the bus trunk terminatingat the pa dof an agent.

SystemBus Thesystembus isthe processorbus.

Trunk The mainconnection, ex cluding inte rconnect branches, from one end agentpad to the

other end agent pad.

Undershoot Minimum voltage observed for a signal to extend below VSSat the device pad.

Victim A network that receives a coupled crosstalk signal from another network is called the

victim network.

In this document, a ‘#’ symbol after a signal name identifies the signal as active low; that is, a

signal that is in the active state, based on the name of the signal, when dr iven to a low level. For

example, when FLUSH# is low, a flush has been requested. When NMI is high, a non-maskable

interrupt has occurred. When a signal name does not imply an active state, a # symbol indicates

that th e signal is inverted. For example, D[3:0] = ‘HLHL’ refers to a hex ‘A’, and D[3:0]# =

‘LHLH’ also refers to a hex ‘A’ (H= High logic level, L= Low logic level).

The term “BGA2-based processor(s)” refers to the Intel® Celeron® processor-Ultra Low Power

and Low Power in a BGA2 package and th e Intel® Pentium® III processor-Low Power in a

BGA2 package.

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 7

Introduction

1.3 Reference Documents

The reader of this document needs to be familiar with the material and concepts presented in th e

following documents.

R

Document Document Number /

Intel®815 Chipset Family: 82815 Graphics and Memory Controll erHub (GMCH) for

use with the Universal Socket 370 Datasheet

Intel®82802AB/82802AC Firmware Hub (FWH) Datasheet 290658

Intel®82801BA I/O Controller Hub (ICH2) and Intel®82801BAM I/O Controller Hub

(ICH2-M) Datasheet

Intel®Pentium®IIIProcessor-Low Power Datasheet 273500

Intel®Celeron®Processor-Ultra Low Power/Low Power Datasheet 273509

Intel® 815EM Chipset: 82815EM Graphics and Memory Controller Hub (GMCH2-

M)

Intel® 815EM Chipset Platform Design Guide 298241

Intel® 815E Chipset Platform Design Guide 298234

Intel® 815E Chipset Platform For Use With Universal Socket 370 Design Guide 298350

Accelerated Graphics Port Interface Specification, Revision 2.0

PCI Local Bus Specification, Revision 2.2

AC’97 2.1 Specification http://dev eloper.intel.co

82562EH HomePNA 1 Mb/s Physical Layer Interface Datasheet (Doc # 278313)

82562EH HomePNA 1 Mb/s Physical Layer Interface Brief Datasheet (Doc # 278314)

Communication Network Riser Specification, Revision 1.1 http://dev eloper.intel.co

Universal Serial Bus, Revision1.0 Specification

Location

298351

290687

290689

m/pcsupp/platform/ac97/inde

x.htm.

http://dev eloper.intel.co

m

http://dev eloper.intel.co

m

m/technology /cnr/

8 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

General Design Considerations

R

2 General Design Considerations

This section documents the example of a nominal board stack up for BGA2-based processor with

the 815E platform.

Make sure the impedance for all signal layers is 60 Ω±15%. That is, the impedance of the trace

when not subjected to fields created by changing current in neighboring traces. When calculating

flight times, it is important to consider the minimum and maximum impedance of a trace, based

on the switching of neighboring traces. The use of wider spaces between the tr aces can minimize

this trace-to-trace coupling. In addition, th ese wider spaces reduce crosstalk and settling time.

Coupling between two traces is a function of the coupled length, the distance separating th e

traces, the signal edge rate, and the degree of mutual capacitance and inductance. To minimize

the effects of trace-to-trace coupling, follow the routing guidelines documented in this section.

The routing guidelines in this design guide have been created using a PCB stack-up similar to

that in Figure 1. When this stack-up is not used, thorough simulations of every interface must be

completed. Using a thicker dielectric (prepreg) makes routing very difficult or impossible.

2.1 Nominal Board Stack-up

The BGA2-based processor/815E platform requires a board stack-up yielding a target impedance

of 60 Ω ± 15% with a 5 mil nominal trace width. Figure 1 shows an example stack-up achieving

this. It is a 6-layer printed circuit board (PCB) construction using 53%-resin FR4 material.

Figure 1. Board Construction Example for 60 ΩΩΩΩ Nominal Stack-up

Signal/Powerplane layer ½ozCu., 1ozPlating

Prepreg = 3mils

GroundLayer1ozCu.

Core = 6 mils

Signal layer 1 oz Cu.

Prepreg = 34 mils

Signal layer 1 oz Cu.

Core = 6 mils

Ground layer 1 oz Cu.

Prepreg =3 mils

Signal/Powerlayer ½ oz Cu., 1ozPlating

Dieletric Constant for FR4 = 4.2

4 mils tr ace width for outer layers gives a 50 Ω signal impedance.

5 mils tr ace width for inner layers gives a 60 Ω signal impedance

Total thickness:

62 mils

Additional guidelines on board stack-up, placement, and layout include the following.

− The board impedance (Z) is 60 Ω ± 15%.

− The dielectric process variation in the PCB fabrication is minimized.

− The ground plane is not split on the ground plane layer.

− Keep vias for decoupling capacitors as close to the capacitor pads as possible.

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 9

Processor Host Bus Design

3 Processor Host Bus Design

This section documents the layout and routing guidelines using the BGA2-based processor with

the Intel® 815E chipset platform. The solution covers system bus speeds of 100 MHz only. The

Ω

processor must also be configured to 56.2

discuss the functional aspect of any bus or the layout guideline for an add-in device.

When the guidelines listed in this document are not followed, it is very important that thorough

signal integrity and timing simulations be completed for each design. Even when the guidelines

are followed, simulate critical signals to ensure proper signal integrity and flight time. As bus

speeds increase, it is imperative that the guidelines documented are followed precisely. Simulate

any deviation from these guidelines.

3.1 Initial Timing Analy s is

To determine the available flight time window, perform an initial timing analysis. Analysis of

setup and hold conditions determine the minimum and maximum flight time bounds for the

system bus. Use the following equations to establish th e system flight time limits.

± 1% on-die termination. The document does not

R

Table 1. System Timing Equations

T

T

flight,min

flight,max

>= T

hold–Tco,min+Tskew

<= T

cycle–Tco,max–Tsu–Tskew–Tjit–Tadj

Table 2. System Timing Terms

Term Description

T

cycle

T

flight,min

T

flight,max

T

co,max

T

co,min

T

su

System cycle time, defined as th e reciprocal of the frequency.

Minimum system flight time.

Maximum system flight time.

Maximum driver delay from input clock to output data.

Minimum driver delay from input clock to output data.

Minimum setup time. Defined as the time for which the input data must be valid

prior to the input clock.

T

hold

Minimum hold time. Defined as the time for which the input data must remain

valid after the input clock.

T

skew

Clock generator skew. Defined as the maximum delay variation between output

clock signals from the system clock generator, the maximum delay variation

between clock signals due to system board variation and chipset loading variation.

T

jit

T

adj

Clock jitter. Defined as maximum edge to edge variation in a given clock signal.

Multi-bit timing adjustment factor. This term accounts for the additional delay

that occurs in the network when multiple data bits switch in the same cycle. The

adjustment factor includes such mechanisms as package and PCB crosstalk, high

inductance current return paths, and simultaneous switching noise.

Equation

10 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

Processor Host Bus Design

R

Table 3 lists the GTL+ component timings of the processors and GMCHdefined at the pins for

the Intel® 815E platform.

Note: These timings are for r eference only. Obtain the processor specifications from respective

processor datasheet and chipset values from the appropriate Intel® 815E chipset datasheet.

Table 3. Intel® Celeron® - Ultra Low Power and 82815E GMCH GTL+ Parameters for

Example Calculations

IC Parameters Intel®Celeron®-Ultra

Clock to Output maximum(T

Clock to Output minimum (T

Setup time(T

Holdtime (T

NOTES:

1. All time in nanoseconds

2. Numbers in table are for reference only. These timing parameters are subject to change. Check the

appropriatecomponent documentatio nfor validtimingparamete rvalues.

) 1.20 2.65 1,2

SU_MIN

) 1.20 0.10 1

HOLD

) 3.40 4.10 1,2

CO_MAX

) 0.20 1.05 1,2

CO_MIN

Low Power processor

core at 100 MHz

System Bus

82815E GMCH Notes

Table 4 provides an exampleGTL+ initial maximum flight time and Table 5 is an example

minimum flight time calculation for a 100 MHz, uni-processor system using the Intel®

Celeron® -Ultra Low Power processor/Intel

®

815E chipset system bus. Note that assumed values

for clock skew and clock jitter were used. Clock skew and clock jitter values are dependent on

the clock components and distribution method chosenfor a particular design and must be

budgeted into the initial timing equations as appropriate for each design.

Table4andTable5arederivedassuming:

SKEW = 0.20 ns (Note: Assumes clock driver pin-to-pin skew is reduced to 50 ps by

• CLK

tying two host clock outputs together (“ganging”) at clock driver output pins, and the PCB

clock routing skew is 150 ps. System timing budget must assume 0.175 ns of clock driver

skew and 150 ps PCB clock routing skew if outputs are not tied together and a clock driver

that meets the CK815E Clock Synthesizer/ Driver Specification is being used.)

JITTER = 0.250 ns

• CLK

See the appropriateIntel

®

815E chipset documentation, and CK815E Clock Synthesizer/Driver

Specification for details on clock skew and jitter specifications. Exact details of host clock

routing topology are provided with the platform design guideline.

Table 4. Example T

Driver Receiver Clk Period2TCO_MAX TSU_MIN ClkSKEW ClkJITTER TADJ Recommended

Processor GMCH 10.00 3.40 2.65 0.20 0.25 0.50 3.000

GMCH Processor 10.00 4.10 1.20 0.20 0.25 0.50 3.750

NOTES:

1. All times in nanoseco nds

2. BCLK period = 10.00ns @ 100MHz

FLT_MAX

Calculations For 100 MHz Bus

FLT_MAX

T

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 11

Processor Host Bus Design

R

Table 5. Example T

Driver Receiver THOLD ClkSKEW TCO_MIN Recommended

Processor GMCH 0.10 0.20 0.200 0.100

GMCH Processor 1.20 0.20 1.050 0.350

The flight times in Table 4 include margin to account for the following phenomena that Intel

observed when multiple bits are switching simultaneously. These multi-bit effects can adversely

affect the flight time and signal quality and sometimes are not accounted for durin g simulation.

Accordingly, the maximum flight times depend on the baseboard design, an d additional

adjustment factors or margins are recommended.

• SSO push-out or pull-in

• Rising or falling edge rate degradation at the receiver caused by inductance in the

current return path, requiring extrapolation that causes additional delay

• Crosstalk on the PCB and inside the package which can cause variation in the signals

Additional effects exist that may not necessarily be covered by the multi-bit adjustment factor

and need to be budgeted as appropriate to the baseboard design. These effects are included as

in th e examplecalculations in Table 4. Examples include:

T

ADJ

• The effective board propagation constant (SEFF), which is a function of:

FLT_MIN

Calculations (Frequency Independent)

FLT_MIN

T

ε

- Dielectric constant (

)ofthePCBmaterial

r

- Type oftraceconnecting the components (stripline or microstrip)

- Length of the trace an d the load of the components on the trace. Note that the board

propagation constant multiplied by the trace length is a component of the flight time,

but not necessarily equal to the flight time.

12 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

Processor Host Bus Design

R

3.2 General Topology and Layout Guidelines

Figure 2. Topology for BGA2 Designs with Single-Ended Termination (SET)

16

GMCH

BGA2-based

Processor

Z

O

Table 6. Trace Guidelines Recommedation

Description Min. Length (inches) Max. Length (inches)

GMCH to BGA2-based processor

trace

NOTES:

1. Reference a ll GTL+ bus signals to the ground pla nefor thee ntireroute.

2. Use an intragroupGTL+ spacing : line width : dielectric thickness ratio of at least 2:1:1 for microstrip

geometry. If

mils spacing, 5 mils trace width, and a 5 mils prepreg between the signal layer and the plane it references

(assuming a 6-layer board design)

3. The recomme nde dtrace widthis 5 mils, but not grea ter than 6 mils.

ε

= 4.5, this limits coupling to3.4%. Fo re xample ,intragro upGTL+ routing could use 10

r

%1560 ±Ω=

1, 2, 3

3.3 Simulation Methodology

3.3.1 Pre-Layout Simulation

Analog simulations are recommended for high-speed system bus designs. Start simulations prior

to layout. Pre-layout simulations provide a detailed picture of the working “solution space” that

meets flight time and signal qualityrequirements. By basing board layout guidelines on the

solution space, the iterations between layout and post-layout simulations can be r educed.

3.50 5.00

Intel recommends running simulations at the device pads for signal quality and at the device pins

for timing analysis. However, simulation results at the device pins may be used later to correlate

simulation performance against actual system measurements.

The BGA2-based processor and 815E I/O buffer models are available from Intel through your

Intel representative.

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 13

Processor Host Bus Design

T

3.3.2 Post-Layout Simulation

From the following layout, extract the traces and run simulations to verifythat the layout meets

timing and noise requirements. A small amount of trace “tuning” may be required, but

experience at Intel has shown that a sensitivity analysis significantlyreduces the amount of

tuning required.

Take into account the expected variation for all interconnect parameters for the post layout

simulations. Intel recommends runn ing simulations at the device pads for signal qualityand at

the device pins for timing analysis. However, simulation results at the device pins may be used

later to correlate simulation performance against actual system measurements.

3.4 Layout Rules for GTL+ Signals

Ground Reference

It is strongly recommended that GTL+ signals be routed on the signal layer n ext to the ground

layer (referenced to ground). It is important to provide an effectivesignal r eturn path with low

inductance. The best signal routing is directly adjacent to a solid GND plane with no splits or

cuts. Eliminate parallel tr aces between layers not separated bya power or ground plane. Routing

signals between two signals layers not separated by ground plan need to be implemented as

showninFigure3.

R

Figure 3. Top view of a PCB layout

0

90

Traces in layer A

races in layer B

When a signal has to go through routing layers, the recommendations are:

Note: Following these layout rules is critical for GTL+ signal integrity, particularly for

0.18 micron and smaller process technology.

• For signals going from a ground reference to a power reference, add capacitors between

ground and power near the vias to providean AC return path. Use one capacitor for every

three signal lines that change reference layers. Capacitor requirements are as follows:

C=100nF, ESR=80mΩ,ESL=0.6nH.

• For signals going from one ground reference to another, separate ground reference, add vias

between the two ground planes to provide a better return path.

14 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

Processor Host Bus Design

R

Reference Plane Splits

Splits in r eference planes disrupt signal return paths and increase overshoot/undershoot due to

significantlyincreased inductance. Eliminate routing signal across split/cut plane. When a signal

has to route across split plane, add capacitors between the split planes to ground.

Important note: It is strongly recommended NOT to route GTL+ signals across split/cut plane

or changing reference plane resulted bytraversinglayers.

Processor Breakout

It is strongly recommended that GTL+ signals do n ot traverse multiple signal layers. Intel

recommends breaking out all signals from the processor on the same layer. When r outing is

tight, break outfrom the processor on the opposite routinglayer over a ground reference and

cross over to main signal layer near the processor.

Minimizing Crosstalk

The following general rules minimize the impact of crosstalk in a high-speed GTL+ bus design:

• Maximizethe space between traces. Where possible, maintain a minimum of 10 mils

(assuming a 5 mil trace) between trace edges. It maybe necessary to use tighter spacing

when routing between component pins. When traces must be close and parallel to each

other, minimize th e distancethat they are close together and maximize the distance between

the sections when the spacing restrictions are relaxed.

• Avoid parallelism between signals on adjacent layers, when there is no AC reference plane

between th em. As a rule of thumb, route adjacent layers orthogonally.

• SinceGTL+ is a low-signal-swing technology, it is important to isolate GTL+ signals from

other signals by at least 25 mils. This avoids coupling from signals that have larger voltage

swings (e.g., 5 V PCI).

• GTL+ signals must be well isolated from system memory signals. GTL+ signal trace edges

must be at least 30 mils from system memory trace edges within 100 mils of the ball of the

Intel® 82815 GMCH.

• Select a board stack-up that minimizes th e coupling between adjacent signals. Minimize the

nominal characteristic impedance within the GTL+ specification. This can be done by

minimizing the height of the trace from its reference plane, which minimizes crosstalk.

• Route GTL+ address, data, and control signals in separate groups to minimize crosstalk

between groups. Keep at least 15 mils between each gr oup of signals.

• Minimize the dielectric used in the system. This makes the traces closer to their r eference

plane and thus reduces the crosstalk magnitude.

• Minimize the dielectric process variation used in the PCB fabrication.

• Minimize the cross-sectional area of the traces. This can be done bymeans of narrower

traces and/or by using thinner copper, but the trade-off for this smaller cross-sectional area is

higher tr ace resistivity, which can reduce the falling-edge noise margin becauseof the I*R

loss along the trace.

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 15

Processor Host Bus Design

3.5 Layout Rules for Non-GTL+ (CMOS) Signals

Table 7. Routing Guidelines for Non-GTL+ Signals

Signal Trace Width Spacing to Other Traces Trace Length

A20M# 5 mils 10 mils 1” to9”

FERR# 5 mils 10 mils 1” to 9”

FLUSH# 5 mils 10 mils 1” to 9”

IERR# 5 mils 10 mils 1” to 9”

IGNNE# 5 mils 10mils 1” to 9”

INIT# 5mils 10 mils 1” to 9”

LINT[0] (INTR) 5 mils 10 mils 1” to 9”

LINT[1] (NMI) 5 mils 10 mils 1” to 9”

PICD[1:0] 5m ils 10 mils 1” to 9”

R

PREQ# 5 mils 10m ils 1” to 9”

PWRGOOD 5 mils 10mils 1” to 9”

SLP# 5 mils 10 mils 1” to 9”

SMI# 5 mils 10 mils 1” to 9”

STPCLK 5 mils 10 mils 1” to9”

NOTE: Route these signals on any layer or combination of layers.

3.5.1 Additional Routing and Placement Considerations

• Distribute VTTwith a wide trace. A 0.050 inch minimum trace is recommended to minimize

DC losses. Route the V

trace to all components on the h ost bus. Be sure to include

TT

decoupling capacitors.

• The V

voltage need to be 1.25 V ± 3% for static conditions, and 1.25 V ± 9% for worst-

TT

case transient conditions.

• Place resistor divider pair for V

generation at the GMCHcomponent. V

REF

REF

delivered to the processor.

3.6 Undershoot/Overshoot Requirements

Overshoot (or undershoot) is the absolute value of the maximum voltage above the nominal high

voltage or below V

fast signal edge rates. The processor can be damaged by repeated overshoot events on buffers

when the charge is large enough (i.e. when the overshoot is great enough). Determining the

impact of an overshoot/undershoot condition requires knowledge ofthe magnitude, the pulse

direction an d the activityfactor (AF). Permanent damage to the pr ocessor is the likelyresult of

excessive overshoot/undershoot. Violating the overshoot/undershoot guideline also makes

satisfying the ringback specification difficult.

. The overshoot guideline limits transitions beyond VCCor VSSdue to the

SS

also is

16 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

When performing simulations to determine impact of overshoot and undershoot, ESD diodes

must be properlycharacterized. ESD protection diodes do not act as voltage clamps and do not

provide overshoot or undershoot protection. Refer to Intel® Celeron® Processor Low

Power/Ultra LowPower and Intel® Pentium® III – Low Power datasheet for detailed

undershoot/overshoot requirements.

3.7 Processor Reset Requirements

The BGA2-based processor designs must route the GTL+ reset signalfrom the chipset to the

processor as well as to the debug port connector. The A6 (RESET) signal is connected to this pin

for the Intel® Pentium® III processor (CPUID=068xh), Intel® Celeron® processor

(CPUID=068xh)

Note: The GTL+ reset signal must always terminate to VTT on th e motherboard.

Designs that do not support the debug port will not utilize the 240 Ω series resistor or the

connection of RESET# to the debug port connector.

Processor Host Bus Design

The routing rules for the GTL+ reset signal a re shown in Figure 4.

Figure 4. RESET# Routing Guidelines

VTT

L2 L0

Processor GMCH

Table 8. RESET# Routing Guidelines (see Figure 4)

Parameter Minimum (in) Maximum (in)

L0 2.0 4.1

L1 0.5 1.5

Ω

86

L1

L2 0.9 1.5

L0+L2 3.5 5.0

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 17

Processor Host Bus Design

3.8 Debug Port Routing Guidelines

The Test Access Port (TAP) interface is an implementation of the IEEE 1149.1 (“JTAG”)

standard. Due to voltage levels supported bythe TAP interface, Intel recommends that the Intel®

Celeron® Processor-LP/ULP and Intel® Pentium® III Processor-LP and the other 1.5V JTAG

specification compliant devices be last in the JTAG chain after an y devices with 3.3 V or 5 V

JTAG interfaces within th e system. A translation buffer needs to be used to reducethe TDO

output voltage of the last 3.3/5 V device down to the 1.5 V range that the processors can tolerate.

Multiple copies of TMS and TRST# must be provided, one for each voltage level.

A Debug Port an d connector may be placed at the start and end of the JTAG chain containing the

processor, with TDI tothe first component coming from theDebug Port and TDO from the last

component going to the Debug Port. There are no requirements for placing the Intel® Celeron®

Processor-ULP/LP and Intel® Pentium® III Processor-LP in the JTAG chain, except for those

that ar e dictated by voltage requirements ofthe TAP signals.

The 1.5 V connector is a mirror image of the older 2.5 V connector. Either connector will fit into

the same printed circuit board layout. Only the pin numbers change (Figure 5). Also required,

along with the newconnector, is an In-Target Probe* (ITP) that is capable of communicating

with the TAP at the appropriate logic levels.

R

Figure 5. TAP Connector Comparison

2.5 V connector,AMP 104068-3 vertical plug, top view

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30

RESET#

RESET#

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29

1.5 V connector,AMP 104078-4 vertical receptacle, topview

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30

sys_bus_TAP_conn

Caution: The Intel® Pentium® III processor (CPUID=068xh) and Intel® Celeron® processor

(CPUID=068xh) require an in-target probe (ITP) compatible with 1.5 V signal levels on the

TAP. Previous ITPs were designed to work with higher voltages and may damage the processor

when connected to any of these specified processors.

See the processor datasheet for more information regarding the debug port.

18 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

3.9 PLL Filter Recommendations

It is h igh ly critical that phase lock loop power delivery to the processor meets Intel requirements.

A low pass filter is required for power deliveryto pins PLL1 and PLL2. This serves as an

isolated, decoupled power source for the internal PLL.

3.9.1 Topology

The general desired topology for these PLLs is shown in Figure 6. Not shown are the parasitic

routing and local decoupling capacitors. Excluded from the external circuitry are parasitic

associated with each component.

The following tables contain examples of components that meet Intel recommendations when

configured in the topology of Figure6.

Table 9. Component Recommendations – Inductor

Processor Host Bus Design

Part Number Value Tolerance SRF Rated

TDK MLF2012A4R7KT 4.7 µH 10% 35M Hz 30 mA 0.56 Ω (1 Ω max.)

Murata LQG21N4R7K00T1 4.7 µH 10% 47 MHz 30 mA 0.7 Ω (±50%)

Murata LQG21C4R7N00 4.7 µH 30% 35 MHz 30 mA 0.3 Ω max.

Table 10. Component Recommendations – Capacitor

Part Number Value Tolerance ESL ESR

Kemet T495D336M016AS 33µF 20% 2.5 nH 0.225 Ω

AVX TPSD336M020S0200 33 µF 20% 2.5 nH 0.2 Ω

Table 21. Component Recommendation – Resistor

Value Tolerance Power Note

1 Ω 10% 1/16 W Resistor may beimplemented with trace resistance, in

which case a discrete R is not needed. See Figure.

To satisfydamping requirements, total series resistance in the filter (from VTTto the top plate of

the capacitor) must be at least 0.35 Ω. This resistor can be in the form of a discrete component or

routing or both. For example, if the chosen inductor has minimum DCR of 0.25 Ω,thena

routing resistance of at least 0.10 Ω is required. Be careful not to exceed the maximum resistance

rule(2Ω). For example, if using discrete R1 (1 Ω±1%), the maximum DCR of the L (tra ce plus

inductor) is less than 2.0 – 1.1 = 0.9 Ω, which precludes the use of some inductors and sets a

max. trace length.

Current

DCR (Typical)

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 19

Processor Host Bus Design

Other routing requirements:

• The capacitor (C) is close to the PLL1 and PLL2 pins, < 0.1 Ω per route. These routes do not

count towards the min imum damping R requirement.

• The PLL2 route is parallel and next to the PLL1 route (i.e., minimize loop area).

R

• The inductor (L) is close to C. Any routing resistance is inserted between V

• Anydiscrete resistor (R) is in serted between V

Figure 6. Example PLL Filter Using a Discrete Resistor

V

TT

LR

<0.1Ω route

Discrete resistor

C

<0.1Ω route

Figure 7. Example PLL Filter Using a Buried Resistor

TT

and L.

PLL1

PLL2

TT

Processor

and L.

PLL_filter_1

V

TT

Trace resistance

LR

<0.1Ω route

C

PLL1

Processor

PLL2

<0.1Ω route

PLL_filter_2

20 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

3.9.2 Filter Specification

The function of the filter is to protect the PLL from external noise thr ough low-pass attenuation.

The low-pass specification, with input at VCC

as follows:

• < 0.2 dB gain in pass band

• < 0.5 dB attenuation in pass band (see DC drop in next set of requirements)

• > 34 dB attenuation from 1 MHz to 66 MHz

• > 28 dB attenuation from 66 MHz to core frequency

The filter specification is graphically shown in Figure 8.

Processor Host Bus Design

and output measured across the capacitor, is

CORE

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 21

Processor Host Bus Design

Figure 8. Filter Specification

R

0.2dB

0dB

-0.5 dB

Forbidden

Zone

Forbidden

Zone

-28dB

-34dB

1MHz 66MHz fcorefpeak1HzDC

passband

NOTES:

1. Diagram not to scale.

2. No specification for frequencies beyond

3.

fpeak is less than 0.05 MHz .

fcore.

high frequency

band

Other requirements:

• Use shielded-type inductor to minimize magnetic pickup.

• Filter supports DC current > 30 mA.

• DC voltage drop from VCC to PLL1 is < 60 mV, which in practice implies series

R<2Ω. This alsomeans pass-band (from DC to 1 Hz) attenuation < 0.5 dB for V

V, and < 0.35 dB for V

=1.5V.

CC

filter_spec

CC

=1.1

22 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

Processor Host Bus Design

R

3.10 Decoupling Guidelines for BGA2-based Processors

The amount of bulk decoupling required on the VCCand V

planes to met the voltage tolerance

CCT

requirements for th e Intel® Celeron® Processor – Low Power or Ultra Low Power and Intel®

Pentium® III Processor – Low Power are a strong function of the power supply design. Contact

your Intel Field Sales Representative for tools to help determine h ow much bulk decoupling is

required.

For 700 MHz processors, the following decoupling is recommended. The processor core power

plane (V

) has fifteen 0.68µF 0603 ceramic capacitors (using X7R dielectric for thermal

CC

reasons) placed directly under the package using two vias for power and two vias for ground to

reduce the trace inductance. Also to minimize inductance, traces to those vias are 22 mils (in

width) from the capacitor pads to match the via-pad size (assuming 22-mil pad size). Twenty-

µ

four 2.2

die as flex solution allows. The system bus buffer power plane (V

F 0805, X5R mid-frequency decoupling capacitors placed around the die as close to the

) has twenty 0.1µFhigh-

CCT

frequency decoupling capacitors around the die.

For 500 and 400 MHz processors, the processor core power plane (V

frequency decoupling capacitors placed underneath the die an d twenty 0.1

)haseight0.1µFhigh-

CC

µ

F mid-frequency

decoupling capacitors placed around the die as close to the die as flex solution allows. The

system bus buffer power plane (V

) has twenty 0.1µF high-frequencydecoupling capacitors

CCT

around the die.

For 300 MHz processors, the processor core powe r plane (V

decoupling capacitors placed underneath the die and twenty 0.1

)haseight0.1µF high-frequency

CC

µ

F mid-frequency decoupling

capacitors placed around the die as close to the die as flex solution allows. The system bus buffer

power plane (V

) has twenty 0.1µF high-frequencydecoupling capacitors around the die.

CCT

3.11 Catastrophic Thermal Protection

The Intel® Celeron® Processor – Low Power / Ultra Low Power and Intel® Pentium® III

Processor – LowPower does not support catastrophic thermal protection or the THERMTRIP#

signal. An external thermal sensor must be used to protect the processor and the system against

excessive temperatures.

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 23

Clocking

4 Clocking

4.1 General Clocking Considerations

The host bus clock signals are critical signals for the BGA2-based processor an d 815E platform.

The signal integrity and timing of these signals needs to be carefullyevaluated and simulated.

In general, the following layout recommendation needs to be followed for the host bus clocks:

• It is recommended that system bus clocksbe routed on the signal layer next to the

ground layer (referenced toground)

• It is strongly recommended that system bus clocks do not traverse multiple signal layers.

R

• System clock routing over power plane splits need to be eliminated.

• When necessary, grounded guard band traces can be routed next to clock traces to

reduce cross talk to other signals.

4.2 Single-Ended Host Bus Clocking Routing

The BGA2-based processor and 815E platforms have support for using single-ended host bus

clock driver. When using this clocking method, the BCLK signal is used as th e single-ended

clock input to the BGA2-based processor. The CLKREF signal is used as a reference voltage and

must be connected to the appropriate filter circuit described in section 4.2.1

Figure 9 shows the topology recommended for the BGA2-based processor and 815E clock traces.

Please note that section 1, section 2 and section 3 r efer to tra ce length between the illustrated

components. Table 12 contains the r ecommended length and component values for this topology.

24 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

Figure 9 Single-Ended Clocking Topology

Clocking

Table 12 Recommended Length for Single-Ended Clocking Topology

Destination

ProcessorBCLK <0.1” <0.5” A + 5.2” N.A.

GMCH HCLK N.A. <0.5” N.A. A +8”

NOTES:

1. Length “A” has bee nsimulated upto6 inches. The length must bem a tchedbetween SDRAM MCLK lines

±100 mils.

by

2. All length specific in inches

Clock Decoupling

Several general layout guidelines need to be followed when laying out the power planes for the

CK815 clock generator, as follows:

• Isolate power planes to each of the clock groups.

• Place local decoupling as close as possible to power pins, and connect with short, wide traces

and copper.

• Connect pins to appropriate power plane with power vias (larger than signal vias).

• Bulk decoupling needs to be connected to a plane with 2 or more power vias.

• Minimize clock signal routing over plane splits.

• Donot route any signals underneath the clock generator on the component side of the board.

• An example signal via is a 14 mils finished hole with a 24 mils to 26 mils pad. An example

power via is an 18 mils finished h ole with a 33 mils to 38 mils pad. For large decoupling or

power planes with large current transients, a larger power via is recommended

Section 0 Length Section 1 Length Section 2 Length Section 3 Length

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 25

Clocking

4.2.1 CLKREF Filter Implementation

When using single-ended clocking mode, the CLKREF signal on the BGA2-based processor

serves as a reference voltage to the clock input. To provide a steady reference voltage, a filter

circuit must be implemented and attached to this pin. Figure 10 shows the recommended

CLKREF filter implementation. The CLKREF filter n eed to be placed as close as possible (less

than 1.0 inch) to the processor CLKREF pin.

Figure 10. Examples for CLKREF Divider Circuit

R

Table 13. CLKREF Component Values

R1 (Ω

Ω) ± 1% R2 (ΩΩΩΩ) ± 1% CLKREF Voltage (V)

ΩΩ

1k 1k 1.25

26 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

8

4.2.2 Single-Ended Clocking BSEL[1:0] Implementation

The BGA2-based processor and 815E platform is using single-ended clocking that only support

100 MHz system bus. In order to implement the 100 MHz system bus, BSEL0 needs to be pulled

up to 1.5 V through a 1.5 KΩ 5% resistor and BSEL1 needs to be pulled down to GND. This

strapping configures the clock generator to output 100 MHz clock to support a 100 MHz capable

processor. Figure 11 shows a diagram of this implementation.

Figure 11. BSEL[1:0] Circuit Implementation for LP CopperMine processor

Designs

Clocking

.2k

4.2.3 Clock Driver Decoupling and Power Delivery

The decoupling and power delivery requirements of the system clock driver are dependent on the

clock driver and chipset used in the system implementation. Because ofthis, no specific

information can be provided in this document. However, since proper decoupling and n oise-free

power deliveryare critical to the clock driver operation, Intel encourages system implementers to

carefully followthe chipset and clock driver vendor recommendations in these areas. An

incorrect implementation of these circuits can easily cripple clock driver recommendations in

these areas and its abilityto produce reliable clock signals and lead to system instability. Please

refer to the appropriate clock driver and chipset vendor information for more details.

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 27

Processor Host Bus Design Checklist

5 P rocessor Host Bus Design

Checklist

5.1 Introduction

This checklist highlights design considerations that n eed to be reviewed prior to manufacturing a

motherboard. This design checklist only provides the processor host bus signals design

recommendation. It is not a complete list and does not guarantee that a design functions

properly. Besides the items in the following text, refer to most recent version of the Intel® 815E

Chipset Platform For Use with Universal Socket 370 Design Guide for more detailed instruction.

This checklist is to be revised, as new information is available.

R

5.2 GTL+ Checklist

Table 14. GTL+ signals checklist

Checklist items Recommendations

A[35:3]# Connect to A[31:3]# to 815 GMCH. LeaveA[35:32]# as N/C.

BNR#, BPRI#,

D[63:0]#,

DBSY#,

DEFER#,

DRDY#, HIT#,

HITM#, LOCK#,

REQ#[4:0],

RS[2:0], TRDY#

ADS# Connect to 815 GMCH. For de bugpurpo se,pull-up toVCCT through 56

AERR#,

AP[1:0]#,

BERR#, BINIT#,

BP[3:2]#,

BPM[1:0]#,

DEP[7:0]#, RP#,

RSP#

BREQ0# 10Ωpull down toground.

RESET# Connect to8 1 5GMCH. Pull up to VCCT withan 86Ω1%resistor.Connect to

Connect to 815 GMCH.

resistor, and placed within 150 mils of 815 GMCH

Leave as N/C.

ITP with 240

Ω

series resistor near to ITP if ITP is used.

Ω

28 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

5.2.1 CMOS (Non-GTL+) Checklist

Table 15. CMOS (Non-GTL+) signals checklist

Checklist items Recommendations

A20M#, IGNNE#,

INTR,INIT#,NMI,

SMI#, STPCLK#

FERR#, SLP#, Conne cttoICH2. Pull up toVCCT with a 1.5KΩresistor.

FLUSH#, IERR#,

PREQ#

PWRGOOD Pull up to2.5V with 1.5KΩresistor.

PICD[1:0] Connect to ICH2. Pull up to VCCT with a 150Ωresistor.

Connect toICH2.

Pull up toVCCT with 1.5 KΩresistor.

Processor Host Bus Design Checklist

5.3 TAP Checklist

Table 16. TAP signals checklist

Checklist items Recommendations

TCK,TMS ConnecttoITP with47Ωseriesresistor.Pull upto VCCT with1KΩresistor

TDI, TDO Co n n ect toITP. Pullu pto VCCT with a 150Ωresistor.

TRST# Connect to ITP. Pull down with1 KΩresistor to ground.

PRDY# Connect to ITP with 240Ωseriesresistor.Pull upto VCCT with56.2

resistor.

PRDY1#,PRDY2#,

PRDY3#

Pull up to 1.5 V VCCT through 1 KΩresistor.

Ω

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 29

Processor Host Bus Design Checklist

5.3.1 Miscellaneous Checklist

Table 17. Miscellaneous signal checklist

BCLK Connect to CK815 clock generator with 33Ωserie sresistor(mayvary

depends onsimulatio n). Tie bo thhost clock outputs (to the processor and to

the chipset) at the clock gene ra to rbe forerouting outtoprocessor andGMCH.

BSEL0 Pullupto VCCT with 1.5 KΩ5% resistor (100 MHz PSB only).

BSEL1 Tie toground (100 MHz PSBonly).

CLKREF Connect to voltage divider circuitry on 2.5 V to create 1.25 V reference.

Decouple using 0.1

EDGECTRLP Pull down with 110Ωresistor 1% to ground.

PICCLK Connect to CK815E clock genera to r with33Ωserie sresistor(mayvary

depends onsimulatio n).

PLL1, PLL2 Connect to PLL lowpass filter circuit.

RTTIMPEDP Pull down with 56.2Ωresistor 1% to ground.

THERMDA,

THERMDC

CMOSREF Connect to voltage divider circuitry on 2.5 V to create 1V reference. Decouple

VID[4:0] Connect 100Ωresistorto GND.

VREF[7:0] Connect to v oltag edivider circuit toVCCT with 2/3 ratio(75Ωand 150Ω,1%

VCC_CORE Processor coresupply.Se enotes 1 and 2

VCCT 1.5 V supply.

VSS Ground.

A15, A16, A17, C14,

D8, D14, D16, E15,

G2, G5, G18, H3,

H5,J5,M4,M5,P3,

P4, AA5, AA19,

AC3, AC17, AC20,

AD15, R2

If thermalsensor isused, connecttothermal sensor. Else,leaveas NC.

using two 0.1

resistors). Decouple with four 0.1

to 815 GMCH GTLREF[A,B] with two0.1

Noconnect.

µF capacitors.

R

µF capacitor

µF capacitors near processor. Also connect

µF decoupling capacitors at GMCH.

NOTES:

1. Refer to

2. Refer to

Intel® Pentium®IIIProcessor – Low Power 700Mhz, 500Mhz and 400Mhz Processors in BGA2

Package

Processor in a BGA2 Package

for power supplyde co upling require ment.

Intel® Celeron® Processor – Low Power/Ultra Low Power 300MHz (ULP) and 400AMHz (LP)

for power supplyde co upling require ment.

30 Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide

R

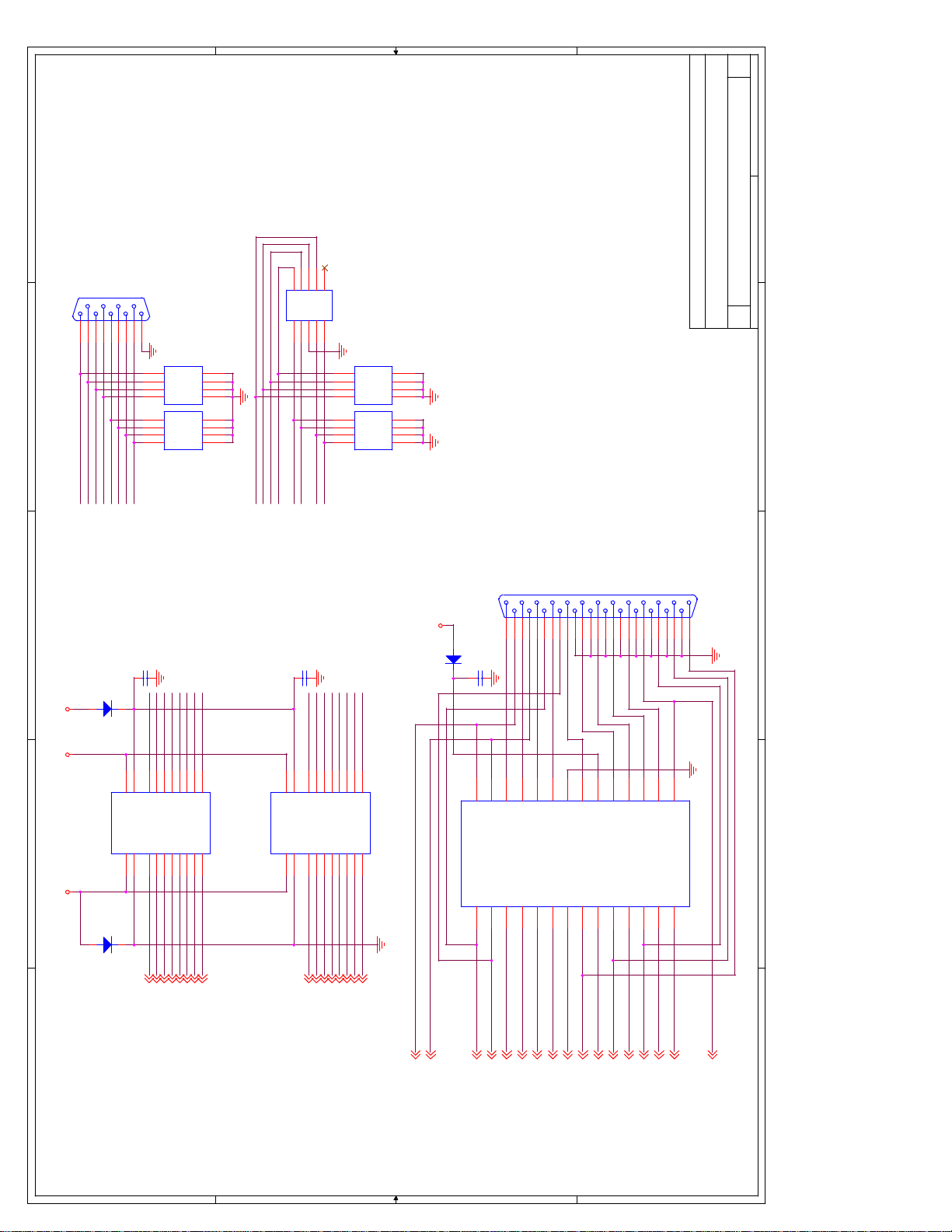

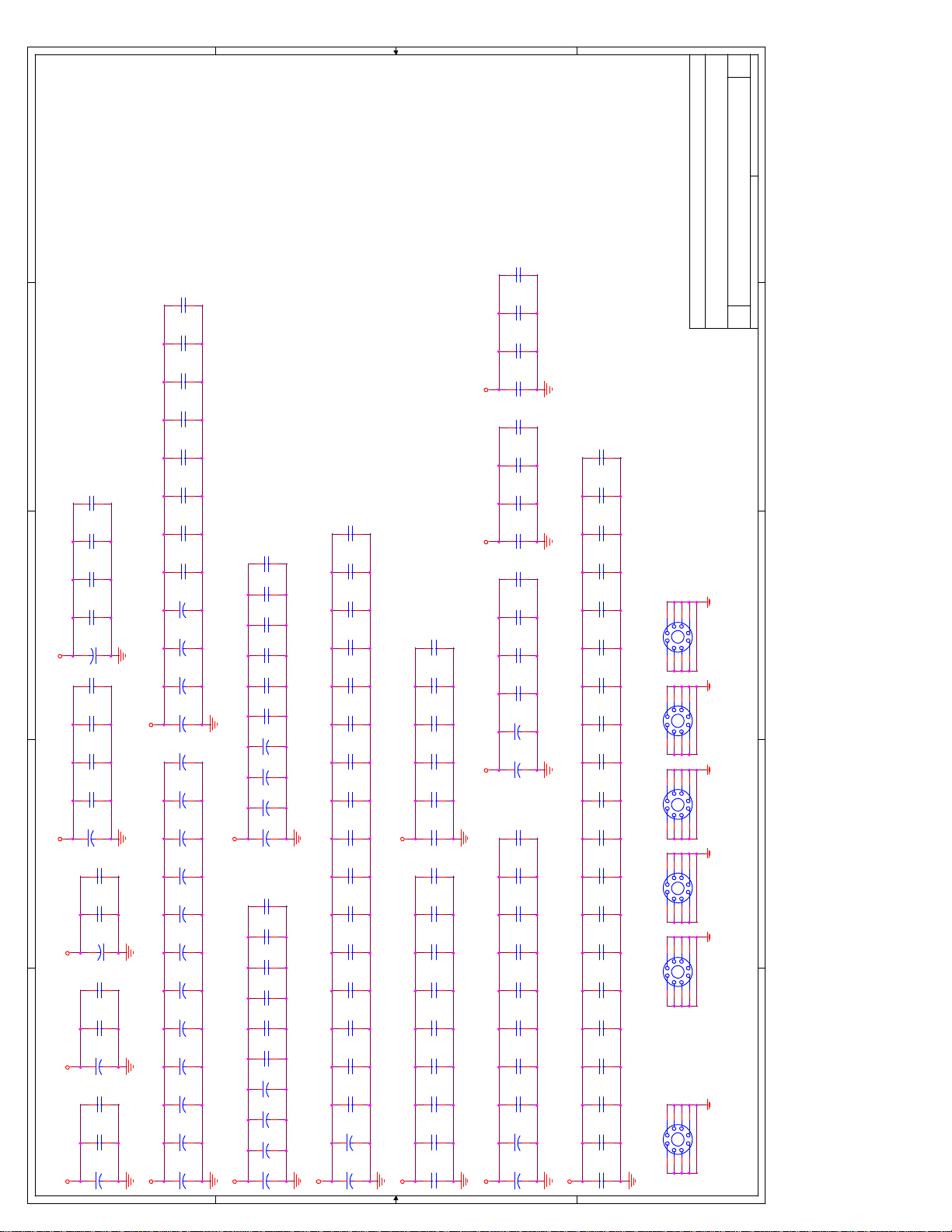

6 Reference Schematic

This section providethe reference schematic for Intel ® Celeron® Processor – Low Power or

Ultra Low Power or Intel ® Pentium® III - Low Power in a BGA2 package and th e Intel

chipset platform.

Reference Schematic

® 815E

Intel®Pentium®III and Intel Celeron®– Low Power/Ultra Low Power / 815E Design Guide 31

COVER SHEET

<Doc> 0.5

Low Power Intel® Celeron®/Pemtium® III with 815E

Title

Size Document Number Rev

of

1 34Wednesday, March 27, 2002

Date: Sheet

The Intel® Celeron(tm) processor and Intel® 815E chipset may contain design defects

or errors known as errata which may cause the product to deviate from published

specifications. Current characterized errata are available on request.

Copyright (c) Intel Corporation 2001.

THESE SCHEMATICS ARE PROVIDED "AS IS" WITH NO WARRANTIES

WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS

FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING

OUT OF PROPOSAL, SPECIFICATION OR SAMPLES.

Information in this document is provided in connection with Intel products. No license,

express or impl ied, by estoppel or otherwise, to any intellectual property rights is

granted by this document. Except as provided in Intel's Terms and Conditions of Sale

for such products, Intel assumes no liability whatsoever, and Intel disclaims any

express or implied warranty, relating to sale and/or use of Intel products including

liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products

A

** Please note these schematics are subject to change.

are not intended for use in medical, life saving or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time,

without notice.

* Third-party brands and names are the property of their respective owners.

A

REVISION 0.5

INTEL® PENTIUM® III LOW POWER & INTEL®

UNIPROCESSOR CUSTOMER REFERENCE SCHEMATICS

CELERON (TM) ULTRA-LOW POWER

PROCESSOR (BGA2) / INTEL® 815E CHIPSET

1

Title Page

Cover Sheet

5CPU Decoupling

3, 4

2

Low Power Intel® Celeron®/Pemtium® III BGA2

Clock Synthesizer 6

Block Diagram

7, 8, 91011, 12

82815E

Display Cache

System Memory

13, 141516

17, 18

19202122232425

ICH2

FWH & UDAM 100 IDE1-2

Super I/O

PCI Connectors

USB Connectors

AC97 CODEC

Serial and Parallel Ports

Audio I/O

Kybrd / Mse / F. Disk / Gme Connectors

Digital Video Out

29, 30

26

27, 283132, 33

Video Connectors

LAN on Motherboard

ATX Power & H/W Monitor

Voltage Regulators

System Configuration

34

Pullup Resistors and Unused Gates

Power Plane Decoupling Capacitors

A A

PCI CONN 4

BLOCK DIAGRAM

Title

Low Power Intel® Celeron®/Pemtium® III with 815E

Size Document Number Rev

of

2 34Wednesday, March 27, 2002

<Doc> 0.5

Date: Sheet

PCI CONN 3

PCI CONN 2

A

PCI CONN 1

Serial 2

A

Serial 1

Clock

2 DIMM

Modules

Floppy Parallel

PCI BUS

DATA

DATA

SIO

LPC Bus

Mouse

Keyboard

Game Port

CTRL

CTRL

ADDR

GTL BUS

ADDR

815E

GMCH

ICH2

FirmWare

Hub

Block Diagram

Low Power Intel® Celeron®/Pemtium® III BGA2 Processor

UltraDMA/100

USB

Jordan PHY

AC'97 Link

VRM

8.5

Memory

Display Cache

Out Device

Digital Video

IDE Primary

IDE Secondary

A A

USB Port 1-2

82562

PHY

Audio

Codec

of

3 34Wednesday, March 27, 2002

1

PROCESSOR PART 1

Title

2

G6G7G8G9G10

G11

G12

G13

G14

G15

G16

VCCT

VCCT

VCCT

VCCT

VCCT

G17H6H17J6J17K6K17L6L17M6M17N6N17P6P17R6R17T6T17U6U17V6V7V8V9

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

V10

VCCT

V11

VCCT

V12

VCCT

V13

VCCT

V14

VCCT

V15

VCCT

V16

VCCT

V17W6W7W8W9

VCCT

VCCT

VCCT

VCCT

VCCT

W10

VCCT

VCCT

W11

W12

VCCT

VCCT

W13

W14

VCCT

W15

VCCT

VCCT

W16

W17Y6Y7Y8AA6

VCCT

VCCT

VCCT

VCCT

VCCT

AA7

VCCT

AA8

VCCT

AB6

VCCT

AB7

VCCT

VCCT

AB8

VCCT

AC6

AC7

VCCT

AC8

VCCT

AD6

VCCT

AD7

VCCT

AD8

VCCT

VCCT

Low Power Intel® Celeron®/Pemtium® III with 815E

Size Document Number Rev

1

<Doc> 0.5

Date: Sheet

2

3

BGA2_1B

H8

VCC

H10

VCC

H12

VCC

H14

VCC

H16

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

J7

J9

J11

J13

L7

L9

K8

J15

K10

K12

K14

M8

L11

L13

L15

K16

M10

M12

M14

M16

P1

P8

N7

N9

P10

P12

N15

P14

N11

N13

T8

R7

R9

P16

R11

R13

R15

U7

U9

T10

T12

T14

T16

A15

A16

U11

U13

U15

A17

C14D8D14

D16

G2

G5

E15

G18

H3

H5J5M4

P3

P4

M5

AA5

AC3

AA19

AC17

AC20

AD15

R2

Intel® Celeron®/Pemtium® III Low Power PBGA

3

VCC_CORE VCCT1_5

4

N10

N12

N14

N16

N18

N19

N20P5P7P9P11

P13

P15

P19R3R4R5R8

R10

R12

R14

R16

R20T3T5T7T9

T11

T13

T15

T18

T19U8U10

U12

U14

U16

N2N3N4

VSS

VSS

VSS

VSS

VSS

VSS

U20V3V19W4W18Y3Y9

VSS

VSS

VSS

VSS

N8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y10

VSS

Y11

VSS

Y12

VSS

Y13

VSS

Y14

VSS

Y15

VSS

Y16

VSS

Y19

VSS

AA4

VSS

AA13

VSS

AA20

VSS

AB3

VSS

AB5

VSS

AB9

VSS

AB11

AB13

VSS

VSS

AB14

VSS

AB17

VSS

AC1

VSS

AC2

VSS

AC5

VSS

AC10

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AD1

VSS

AD5

AD16

VSS

VSS

AD21

VSS

4

BGA2_1A

Low Power

VSS

A2A7A8

VSS

VSS

A12

VSS

VSS

B1B5B6B7B8

A21

VSS

VSS

VSS

VSS

VSS

BGA2-495

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J4

E3E7E8

E9

C9

D2D6D7

C15

C16

C19

D9

B10

B15

B18

C11

F3F6F7F8F9

E10

E11

E13

E19

F10

F11

G3

F12

F13

H2H7H9

F14

F15

F16

F20

G19

H11

H13

H15

H20

J8

K2K7K9

J10

J12

J14

J16

J19

L5

L8

M7

L10

K11

K13

K15

K20

M9

L12

L14

L16

L19

M11

VSS

M13

VSS

M15

VSS

VSS

M20

Intel® Celeron®/Pemtium® III Low Power PBGA

5

A A

B B

C C

D D

5

1

2

3

VCCT1_5

VCC2_5VCC2_5

R1

VCCT1_5

R4

R3

R2

L1

1.5K 1%

1K 1%

1K 1%

PLL1

C4

4.7uH

1

C3

C2

VREF_CMOS

R7

C1

VREF_CLK

R6

VREF_GTL

2K 1%

BC4

0.1uF

BC3

0.1uF

BC2

0.1uF

BC1

0.1uF

PLL2

33uF 16V

0.1uF

CPU_TRDY# 7

CPU_BNR# 7

CPU_BPRI# 7

0.1uF

1K 1%

T4U4U2U3R1T1V1Y4AA3

0.1uF

1K 1%

R5

BGA2_2D

E5

VREF_GTL

BNR#

VREF

E16

BPRI#

TRDY#

VREF

VREF

E17F5F17

Place very close to Processor

VCCT1_5

CPU_LOCK# 7

CPU_DEFER# 7

LOCK#

DEFER#

VREF

VREF

U5

R8

CPU_DRDY# 7

CPU_HIT# 7

HIT#

DRDY#

VREF

VREF

Y17

Y18

1.5K

CPU_HITM# 7

CPU_ADS# 7

CPU_DBSY# 7

AB2

AC9

ADS#

HITM#

DBSY#

VREF

CMOSREF

AA9

AD18

VREF_CMOS

VCCT1_5

CPU_HCLK 6

Y21

FLUSH#

CMOSREF

CLKREF BP#2

P2 AA21

VREF_CLK

R9

1.5K

VCCT1_5

R11

VCCT1_5

Do not stuff

C5

R10

W21

W19C6M3

BP#3

BPM#0

BPM#1

BREQ#0

TESTHI

TESTLO1

TESTLO2

Y5

N5

AD17

18pF

10

AD20

86

BCLK

TESTP

TESTP

H4

R15

R14

AA17

1K

1K

R13

R12

TESTP

G4

150

150

CPU_RST# 7

ITP_RESET#

VCC2_5

AA1E6V21

AERR#

BERR#

RESET#

PICCLK

PICD0

TESTP

AA18

AB21

CPU_APICCLK6

CPU_APIC013

R18

110 1%

CPU_EDGECTRL

R17

1.5K, 1%

AD19

AB19

BINIT#

RTTIMPEDP

PICD1

PLL1

PLL2 EDGECTRLP

L2

M2 AA16

Y20

AA12

PLL2

PLL1

CPU_APIC113

R19

56.2 1%

CPU_PWGD 13

V5A6AA15

RSVD

PWRGOOD

BSEL0

BSEL1

AB15

THRMDN 16,28

VTIN2 16,28

AB16

THERMDA

THERMDC

A20M#

IGNNE#

AA10

AD10

AC13

CPU_A20M#13

CPU_IGNNE#13

VCCT1_5

ITP_PREQ#

ITP_TCK

ITP_PRDY#

AA11

W20

AB20

TCK

PREQ#

PRDY#

INIT#

INTR/LINT0

NMI/LINT1

FERR#

AB18

AC19

AC12

CPU_INIT#13,15

CPU_NMI13

CPU_INTR13

CPU_FERR#13

ITP_TDI

ITP_TDO

AD13

AC15

TDI

TDO

IERR#

SLP#

AD9

AB12

CPU_SLP#13

R29

R28

R27

R26

R25

R24

R23

R22

R21

ITP_TRST#

ITP_TMS

AD14

AA14

TMS

TRST#

SMI#

STPCLK#

AB10

AC11

CPU_SMI#13

CPU_STPCLK#13

56.2

1.5K

150

150

1K

1K

10K

1K

1K

Intel® Celeron®/Pemtium® III Low Power PBGA

VCCT1_5

VCCT1_5

RESET# GND

J1

2 1

4 3

R32 240

ITP_RESET#

R31

1.5K

R30

1.5K 1%

ITP_TDI

DBRESET# GND

TCK GND

6 5

8 7

R33 47

ITP_TMS

ITP_TCK

DBRESET#27

ITP_TDO

ITP_TRST#

POWERON TDO

DBINST# TRST#

TMS TDI

10 9

12 11

R34 47

ITP_PREQ#

ITP_PRDY#

GND BSEN#

GND PREQ0#

14 13

16 15

18 17

R35240

GND PRDY0#

GND PREQ1#

20 19

22 21

R36

GND PRDY1#

GND PREQ2#

24 23

26 25

1K

GND PRDY2#

GND PREQ3#

ITP_CLK PRDY3#

28 27

30 29

ITP_CLK6

PROCESSOR PART 2

<Doc> 0.5

Low Power Intel® Celeron®/Pemtium® III with 815E

ITP_RECEPTACLE

Title

Size Document Number Rev

of

4 34Wednesday, March 27, 2002

1

Date: Sheet

2

3

GTLREF7

R16

1.5K

VCCT1_5

R20

HD#[63:0] 7

HD#6

HD#8

HD#5

HD#3

HD#4

D#3

D#4

D#5

C10

HD#7

D#6

HD#9

HD#10

B11

C12

B13

A14

D#7

D#8

D#9

D#10

HD#1

HD#2

4

HD#0

D10

D11C7C8B9A9

D#0

D#1

D#2

HD#11

HD#12HA#15

B12

E12

D#11

HD#13

B16

D#12

HD#14

A13

D#13

Only 100Mhz PSB

supported by BGA2

HD#15

HD#18

HD#16

HD#17

D13

D15

D12

B14

D#14

D#15

D#16

D#17

D#18

processors.

BSEL[1:0]='01'

HD#22

HD#20

HD#19

HD#21

E14

C13

A19

B17

D#19

D#20

D#21

HD#23

A18

D#22

HD#24

C17

D#23

HD#25

D17

D#24

HD#26

C18

D#25

D#26

HD#27

HD#28

B19

D18

D#27

CPU_BSEL06,8

HD#29

B20

D#28

CPU_BSEL16,8

D#29

VCCT1_5

HD#31

HD#30

A20

B21

D#30

HD#32

D19

D#31

D#32

HD#34

HD#33

C21

D#33

E18

HD#35

C20

D#34

1.5K

HD#36

F19

D#35

HD#37

D20

D#36

HD#38

D21

D#37

HD#39

H18

D#38

HD#40

F18

D#39

D#40

HD#41

HD#42

J18

F21

D#41

HD#43

E20

D#42

HD#44

H19

D#43

HD#45

E21

D#44

D#45

HD#46

HD#47

J20

H21

D#46

HD#48

L18

D#47

HD#49

G20

D#48

HD#50

P18

D#49

D#50

HD#52

HD#51

G21

K18

D#51

HD#53

K21

D#52

D#53

HD#54

HD#55

M18

L21

D#54

HD#56

R19

D#55

D#56

HD#58

HD#57

K19

T20

D#57

HD#59

J21

D#58

D#59

HD#60

HD#61

L20

M19

D#60

HD#62

U18

D#61

D#62

HD#63

R18

D#63

4

BGA2_1C

AD3

VID1

AD4

VID2

AC4

VID3

VID4

AB4

Intel® Celeron®/Pemtium® III Low Power PBGA

R41

1K

R40

1K

R39

1K

R38

1K

R37

1K

5

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

L3K3J2L4L1

HA#3

5

HA#[31:3]7

HA#4

HA#5

HA#6

HA#7

K5

HA#8

K1

HA#9

J1

HA#11

HA#10

J3

K4

HA#12

G1

H1

HA#14

HA#13

E4F1F4F2E1

HA#16

HA#18

HA#17

C4D3D1E2D5D4C3

HA#19

HA#23

HA#20

HA#22

HA#21

HA#24

HA#25

B3A3B2C2A4A5B4

C1

HA#27

HA#26

HA#29

HA#28

HA#31

HA#30

C5

T2

V4

HREQ#0

HREQ#1

HREQ#[4:0]7

V2

W3

HREQ#2

HREQ#3

W5

HREQ#4

U1

RS#0

RS#[2:0]7

RS#0

AA2

RS#1

RS#1

W1

RS#2

RS#2

V20

DEP#1

DEP#0

T21

DEP#2

U21

DEP#3

R21

DEP#4

V18

P21

DEP#6

DEP#5

P20

U19

DEP#7

W2

RP#

Y1

RSP#

AB1

AP#0

Y2

AP#1

VID0

AD2

E E

D D

C C

B B

A A

of

5 34Wednesday, March 27, 2002

C21

2.2uF 6.3V

C47

2.2uF 6.3V

C63

2.2uF 6.3V

C79

C78

C77

C76

C75

C74

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

C94

C93

C92

C91

C90

0.68uF 6.3V

C99

0.68uF 6.3V

C98

0.68uF 6.3V

C97

0.68uF 6.3V

C96

0.68uF 6.3V

C95

0.68uF 6.3V

0.68uF 6.3V

0.68uF 6.3V

0.68uF 6.3V

0.68uF 6.3V

C117

C116

C115

C114

C113

0.68uF 6.3V

0.68uF 6.3V

0.68uF 6.3V

0.68uF 6.3V

0.68uF 6.3V

Low Power Intel® Celeron®/Pemtium® III with 815E

Title

1

<Doc> 0.5

Size Document Number Rev

Date: Sheet

2

1

C20

2.2uF 6.3V

C46

2.2uF 6.3V

C62

2.2uF 6.3V

C19

2.2uF 6.3V

C45

C18

2.2uF 6.3V

C44

C17

2.2uF 6.3V

C43

C16

2.2uF 6.3V

2

C42

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

C61

C60

C59

C58

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

2.2uF 6.3V

VCC_CORE

C31

10uF 6.3V

C41

10uF 6.3V

C57

10uF 6.3V

C73

C15

10uF 6.3V

10uF 6.3V

C89

10uF 6.3V

C30

10uF 6.3V

C40

10uF 6.3V

C56

10uF 6.3V

C72

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

C71

C70

C69

C68

C67

C66

C65

C64

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

C88

C87

C86

C85

C84

C83

C82

C81

C80

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

10uF 6.3V

VCCT1_5

C112

C111

C110

C109

C108

C107

C106

C105

C104

C103

C102

C101

C100

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

150uF

150uF

150uF

C127

C126

C125

C124

C123

C122

C121

C120