Page 1

Celeron™ Processor

Development Kit Manual

July 1999

Order Number: 273246-002

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Celeron™ processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled

platforms may require licenses from various entities, including Intel Corporatio n.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-

548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1999. Portions of this manual Copyright © 1999 General Software, Inc. All rights reserved.

*Third-party brands and names are the property of their respective owners.

Celeron™ Processor De velopment Kit Manual

Page 3

Contents

1 About This Manual ..................................................................................................1-1

1.1 Content Overview...............................................................................................1-1

1.2 Text Conventions ...............................................................................................1-1

1.3 Technical Support ..............................................................................................1-2

1.3.1 Electronic Support Systems ........................................ ...... ....... ...... ...1-2

1.3.1.1 Online Documents ...............................................................1-2

1.3.1.2 Intel Product Forums ...........................................................1-3

1.3.2 Telephone Technical Support ........... ...... ....... ...... ....... ...... ....... ...... ...1-3

1.4 Product Literature...............................................................................................1-3

1.5 Related Documents............................................................................................1-4

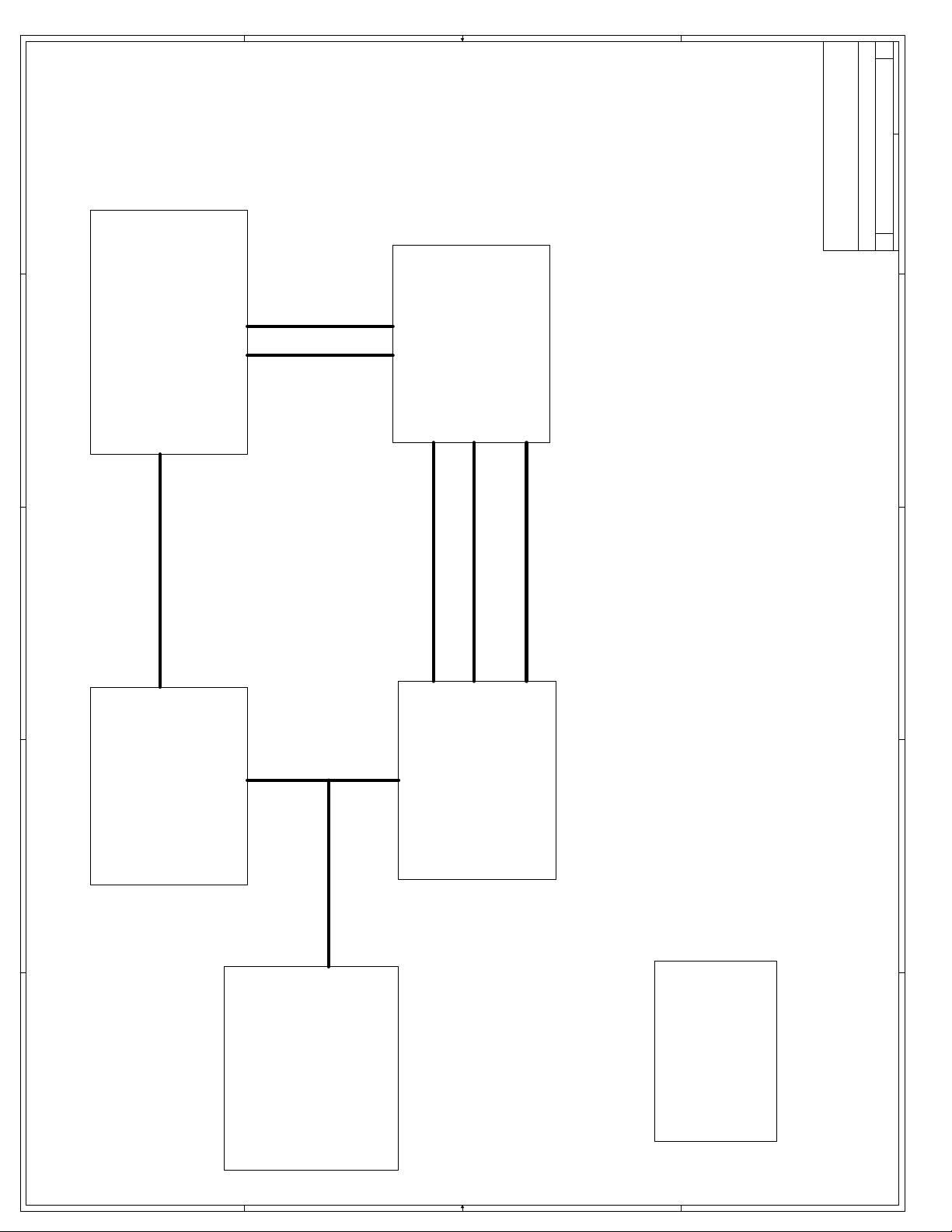

2 Getting Started ......................................................... ....................................... .........2-1

2.1 Overview ............................................................................... .............................2-1

2.1.1 Processor Assembly Features ..........................................................2-1

2.1.2 Baseboard Features..........................................................................2-2

2.2 Included Hardware .............................................................................................2-2

2.3 Software Key Features.......................................................................................2-3

2.3.1 General Software, Inc........................................................................2-3

2.3.2 QNX Software Systems, Ltd..............................................................2-4

2.4 Before You Begin ...............................................................................................2-4

2.5 Setting up the Evaluation Board.........................................................................2-5

2.6 Configuring the BIOS .........................................................................................2-7

3 Theory of Operation...............................................................................................3-1

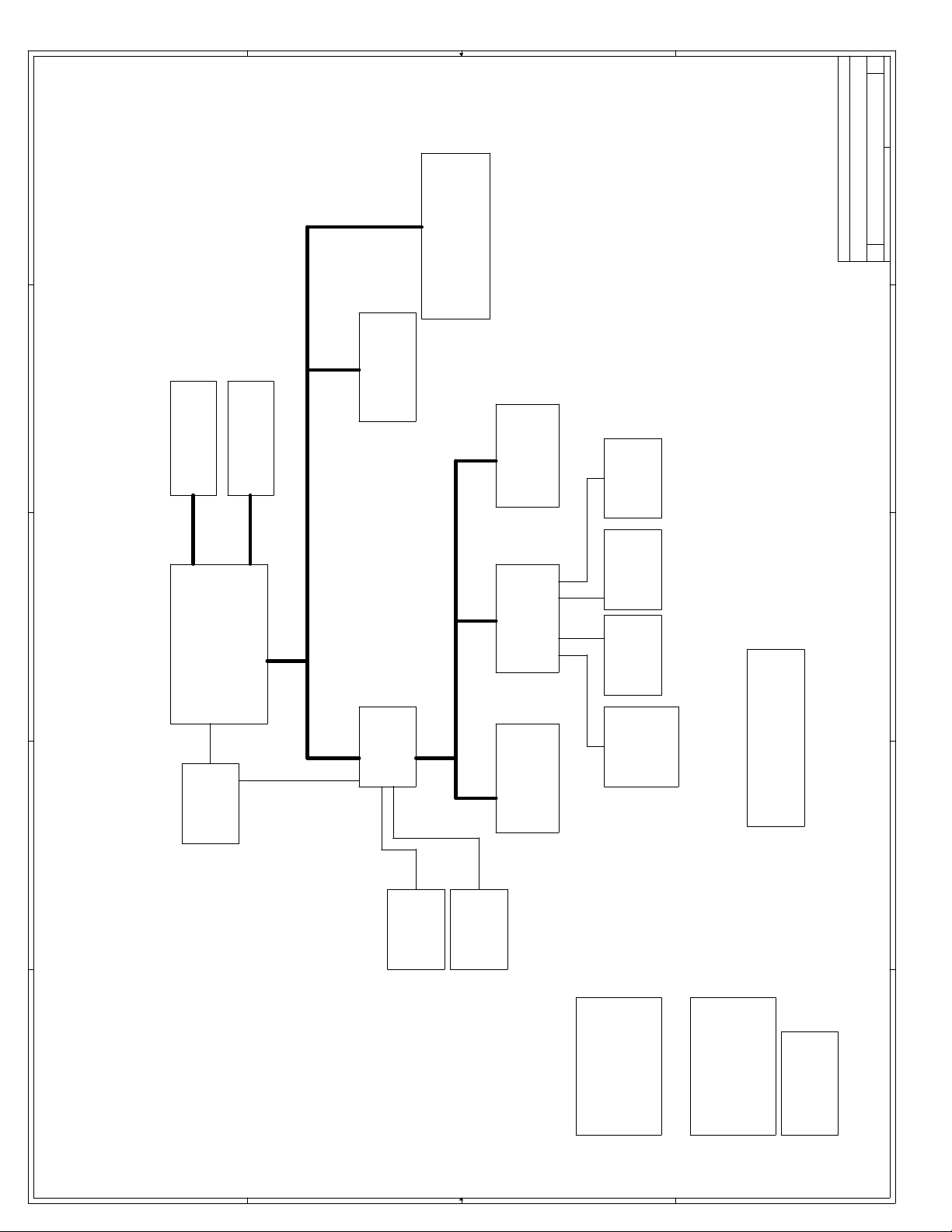

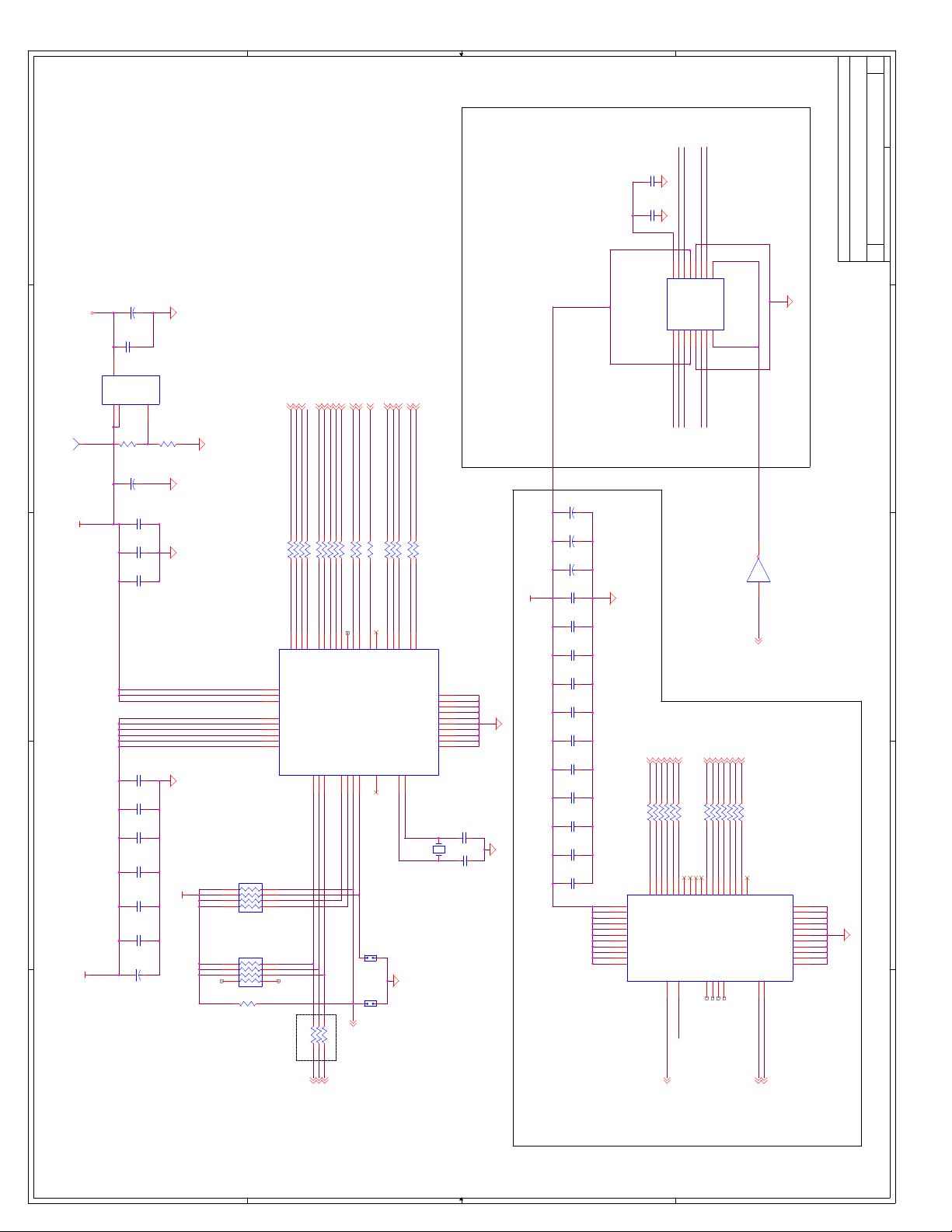

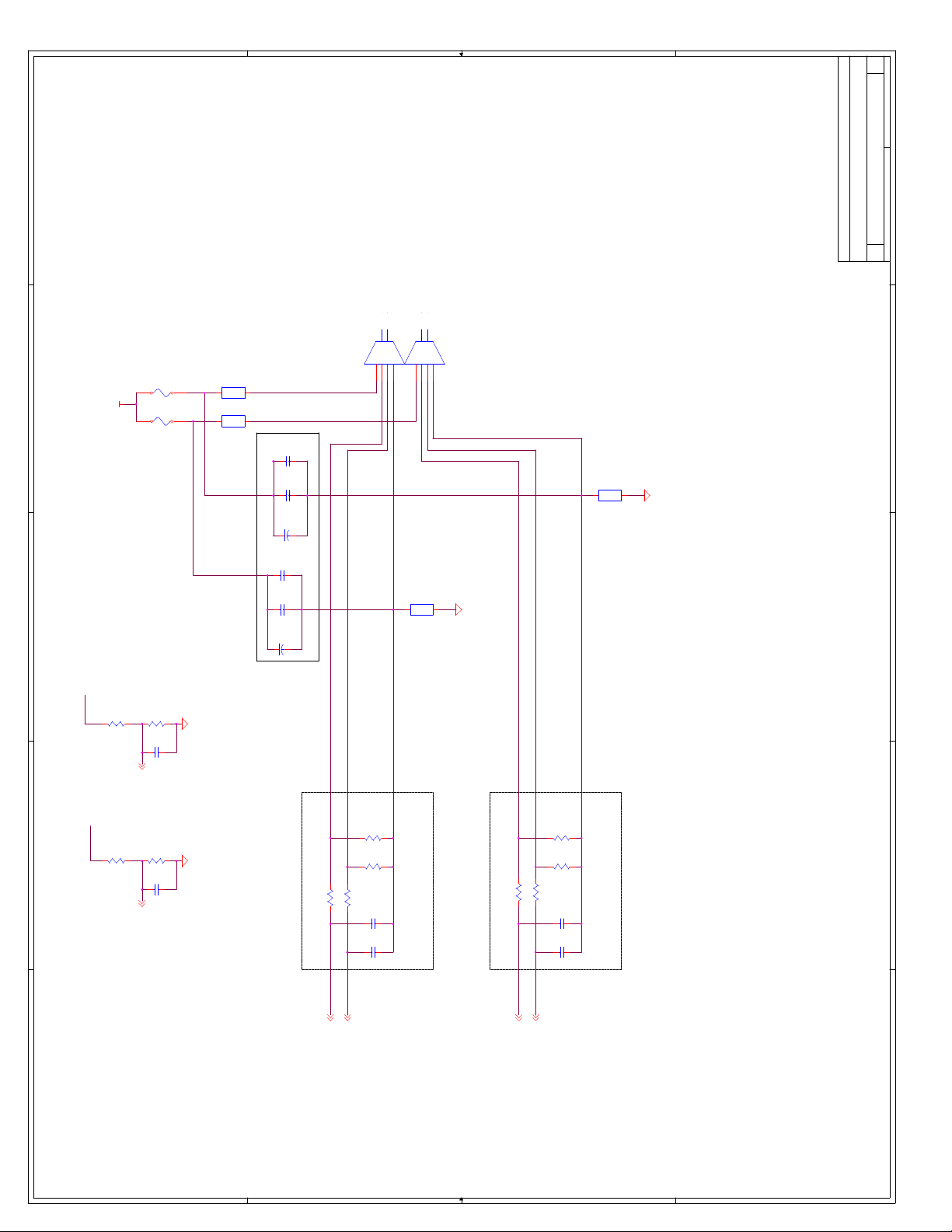

3.1 Block Diagram....................................................................................................3-1

3.2 System Operation...............................................................................................3-2

3.2.1 Celeron Processor ................................... ....... ...... ....... ...... ....... ...... ...3-2

3.2.2 82443BX Host Bridge/Controller .............................................. .........3-2

3.2.2.1 System Bus Interface...........................................................3-3

3.2.2.2 Accelerated Graphics Port (AGP) Interface.........................3-3

3.2.2.3 System Clocking..................................................................3-3

3.2.3 ITP.....................................................................................................3-3

3.2.4 82371EB PCI to ISA/IDE Xcelerator (PIIX4E)...................................3-4

3.2.5 DRAM................................................................................................3-4

3.2.6 Power ................................................................................................3-4

3.2.7 Boot ROM..........................................................................................3-4

3.2.8 RTC/NVRAM.....................................................................................3-4

3.2.9 Legacy I/O...................... ...... ...... ....... ...... ....... ...... ....... ......................3-4

3.2.10 IDE Support.......................................................................................3-5

3.2.11 Floppy Disk Support ..........................................................................3-5

3.2.12 Keyboard/Mouse ...............................................................................3-5

3.2.13 USB...................................................................................................3-5

3.2.14 RS232 Ports................... ...... ...... ....... ...... ....... ...... ....... ...... ....... ...... ...3-5

3.2.15 IEEE 1284 Parallel Port.....................................................................3-5

3.2.16 PCI Connectors.................................................................................3-5

3.2.17 ISA Connectors .................................................................................3-5

3.2.18 AGP Connector .................................................................................3-5

Celeron™ Processor Development Kit Manual

iii

Page 4

3.2.19 Post Code Debugger.........................................................................3-6

3.2.20 Cloc k Ge neration .. ...... ....... ...................................... ....... ...... ....... ......3-6

3.2.21 Interrupt Map.....................................................................................3-6

3.2.22 Memory Map .....................................................................................3-7

4 Hardware Reference .................................... ....................................... ...................4-1

4.1 Processor Assembly .......................... ...... ...... ....... ...... ....... ...... ..........................4-1

4.1.1 Thermal Management .......................................................................4-1

4.1.2 ITP Debugger Port ............................................................................4-1

4.2 Post Code Debugger..........................................................................................4-1

4.3 ISA and PCI Expansion Slots.............................................................................4-2

4.4 PCI Device Mapping ..........................................................................................4-2

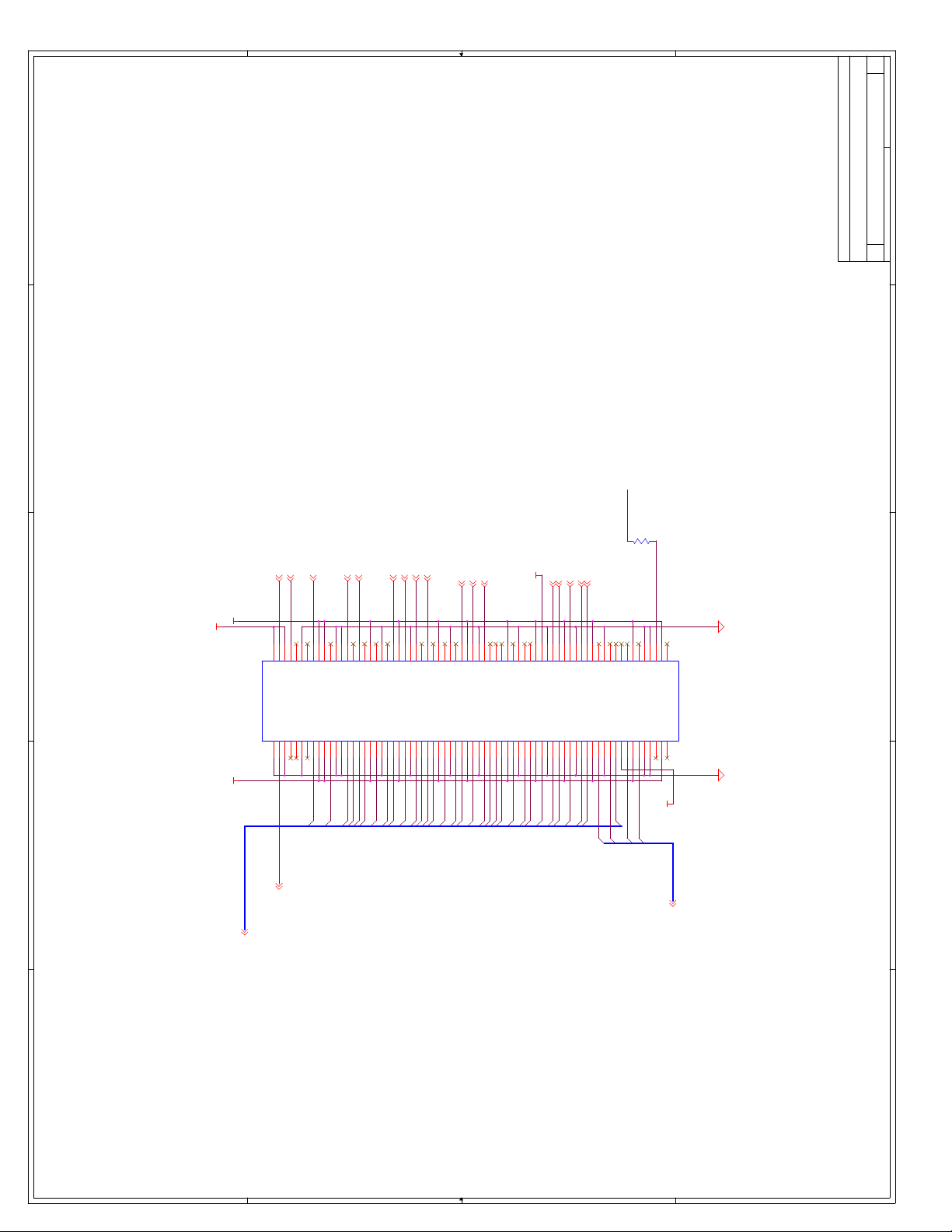

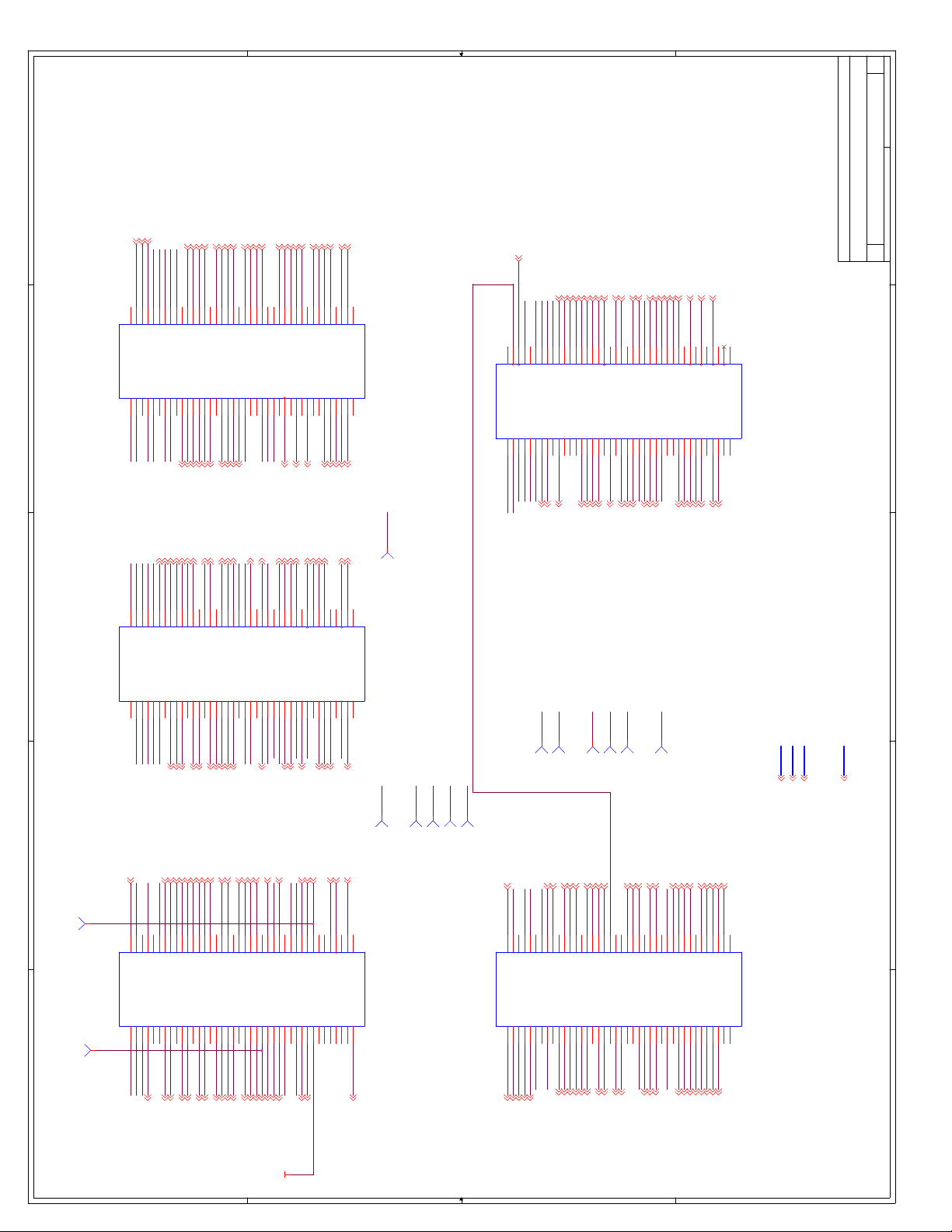

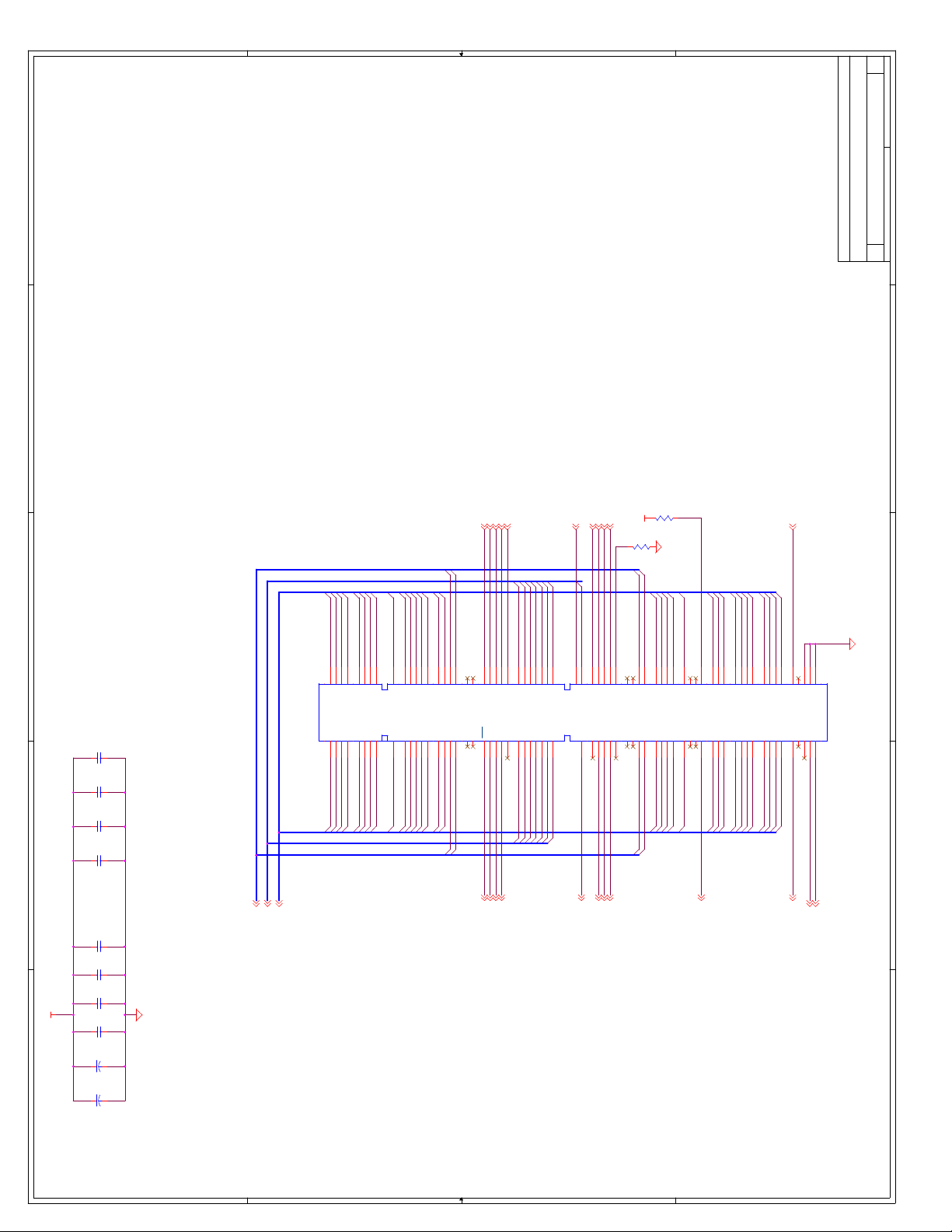

4.5 Connector Pinouts..............................................................................................4-3

4.5.1 ATX Power Connector.......................................................................4-3

4.5.2 ITP Debugger Connector ..................................................................4-4

4.5.3 Stacked USB.....................................................................................4-4

4.5.4 Mouse and Keyboard Connectors.....................................................4-5

4.5.5 Parallel Port.......................................................................................4-5

4.5.6 Serial Ports........................................................................................4-6

4.5.7 IDE Connector...................................................................................4-6

4.5.8 Floppy Drive Connector.....................................................................4-7

4.5.9 PCI Slot Connector............................................................................4-8

4.5.10 IS A Slot Conne cto r..... ....... ...... ...... ....... ....................................... ......4-9

4.6 AGP Connector.............. ....... ...... ....... ...... ...... ....... ...... ....... ...... ........................4-10

4.7 Jumpers ...... ...... ....... ...... ....................................... ...... ....... ...... ....... ...... ....... ....4-11

4.7.1 Enable Spread Spectrum Clocking (J14)........................................4-11

4.7.2 Clock Frequency Selection (J15) ....................................................4-11

4.7.3 On/Off (J20).....................................................................................4-11

4.7.4 Flash BIOS VPP Select (J21)..........................................................4-12

4.7.5 Flash BIOS Boot Block Control (J22)..............................................4-12

4.7.6 SMI# Source Control (J23)..............................................................4-12

4.7.7 CMOS RAM Clear (J24)..................................................................4-12

4.7.8 Push Button Switches .....................................................................4-12

4.8 In-Circuit BIOS Update.....................................................................................4-13

5 BIOS Quick Reference .......................................................... ................................5-1

5.1 BIOS and Pre-Boot Features.............................................................................5-1

5.2 Power-On Self-Test (POST) .................... ...... ....... ...... ....... ...... ....... ...... ....... ......5-1

5.3 Setup Screen System ........................................................................................5-3

5.3.1 Basic CMOS Configuration Screen...................................................5-3

5.3.2 Configuring Drive Assignments.........................................................5-4

5.3.2.1 Configuring Floppy Drive Types ..........................................5-4

5.3.3 Configuring IDE Drive Types.............................................................5-5

5.4 Configuring Boot Actions....................................................................................5-6

5.5 Custom Configuration Setup Screen..................................................................5-6

5.6 Shadow Configuration Setup Screen.................................................................5-7

5.7 Standard Diagnostics Routines Setup Screen ...................................................5-8

5.8 Start System BIOS Debugger Setup Screen .....................................................5-8

5.9 Start RS232 Manufacturing Link Setup Screen .................................................5-9

5.10 Manufacturing Mode ..........................................................................................5-9

iv

Celeron™ Processor De velopment Kit Manual

Page 5

5.10.1 Console Redirection ..........................................................................5-9

5.10.2 CE-Ready Windows CE Loader ......................................................5-10

5.10.3 Integrated BIOS Debugger..............................................................5-10

5.11 Embedded BIOS POST Codes........................................................................5-12

5.12 Embedded BIOS Beep Codes..........................................................................5-15

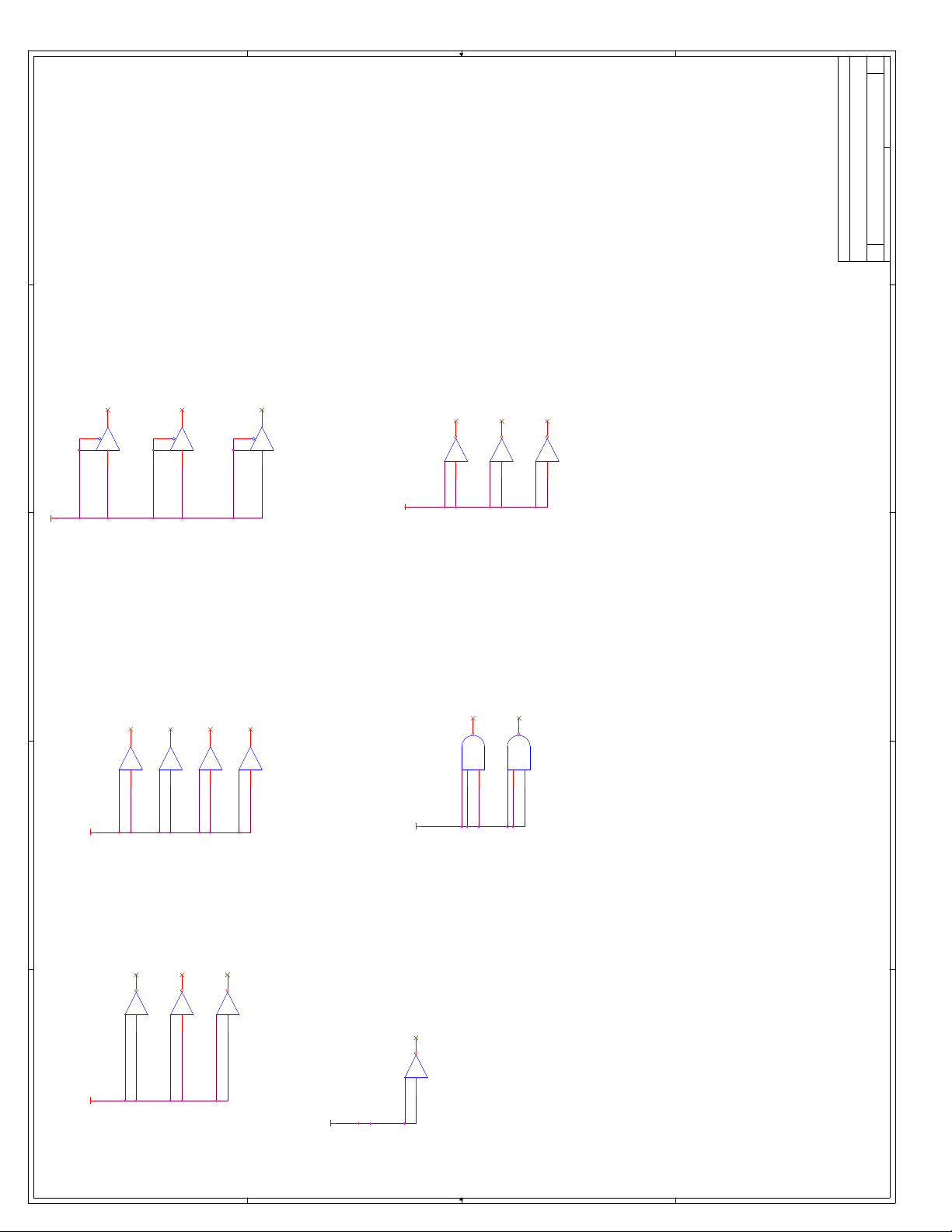

A PLD Code Listing................................................................................................... A-1

B Bill of Materials....................................................................................................... B-1

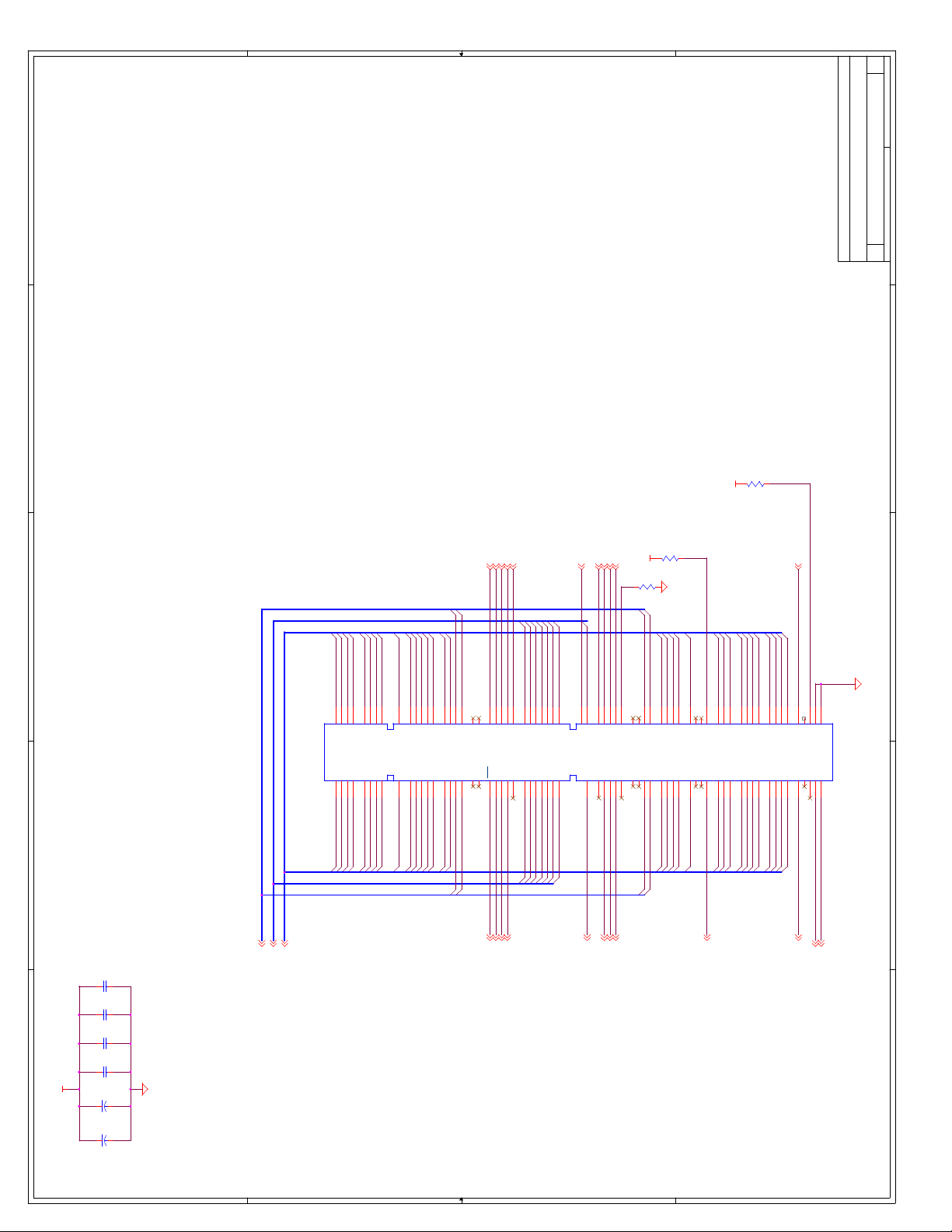

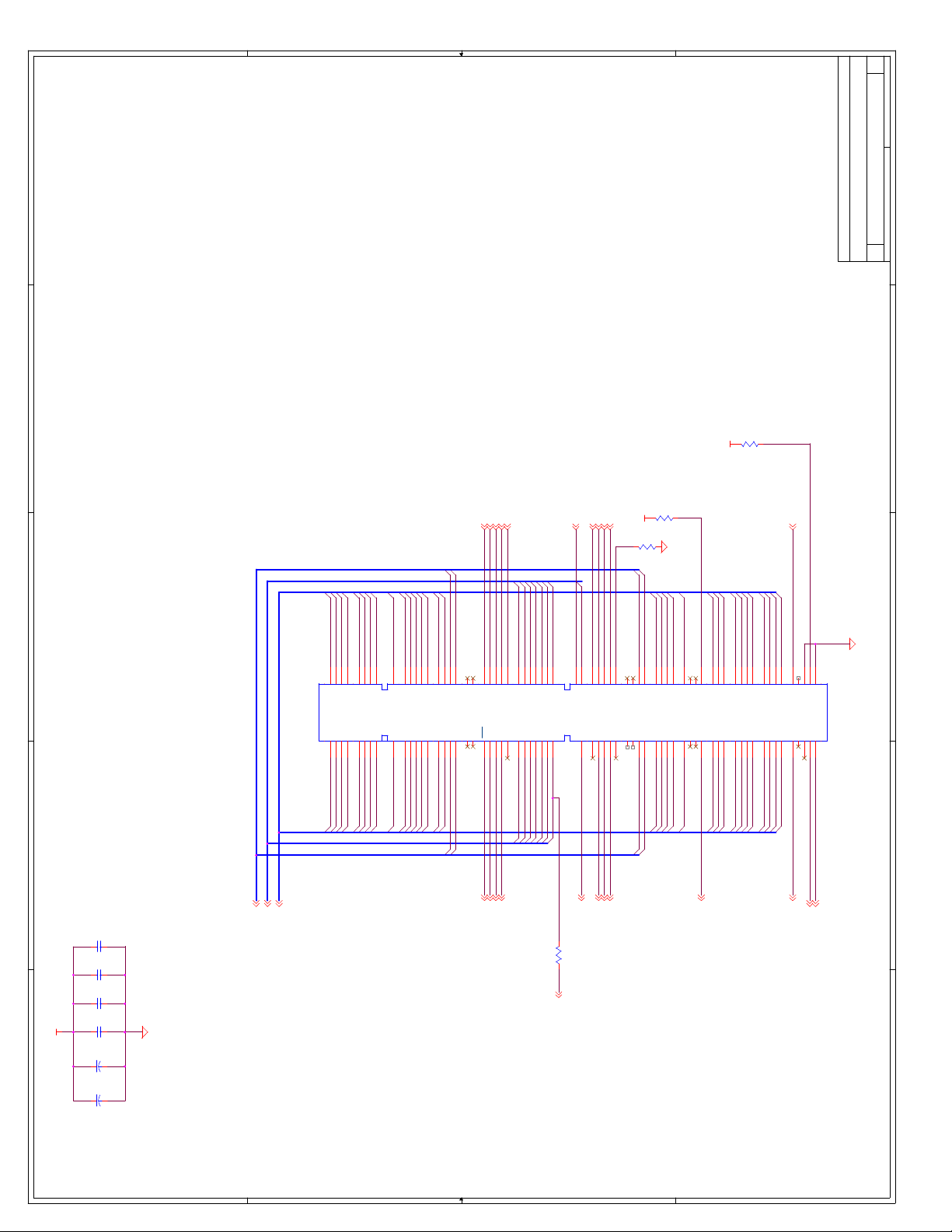

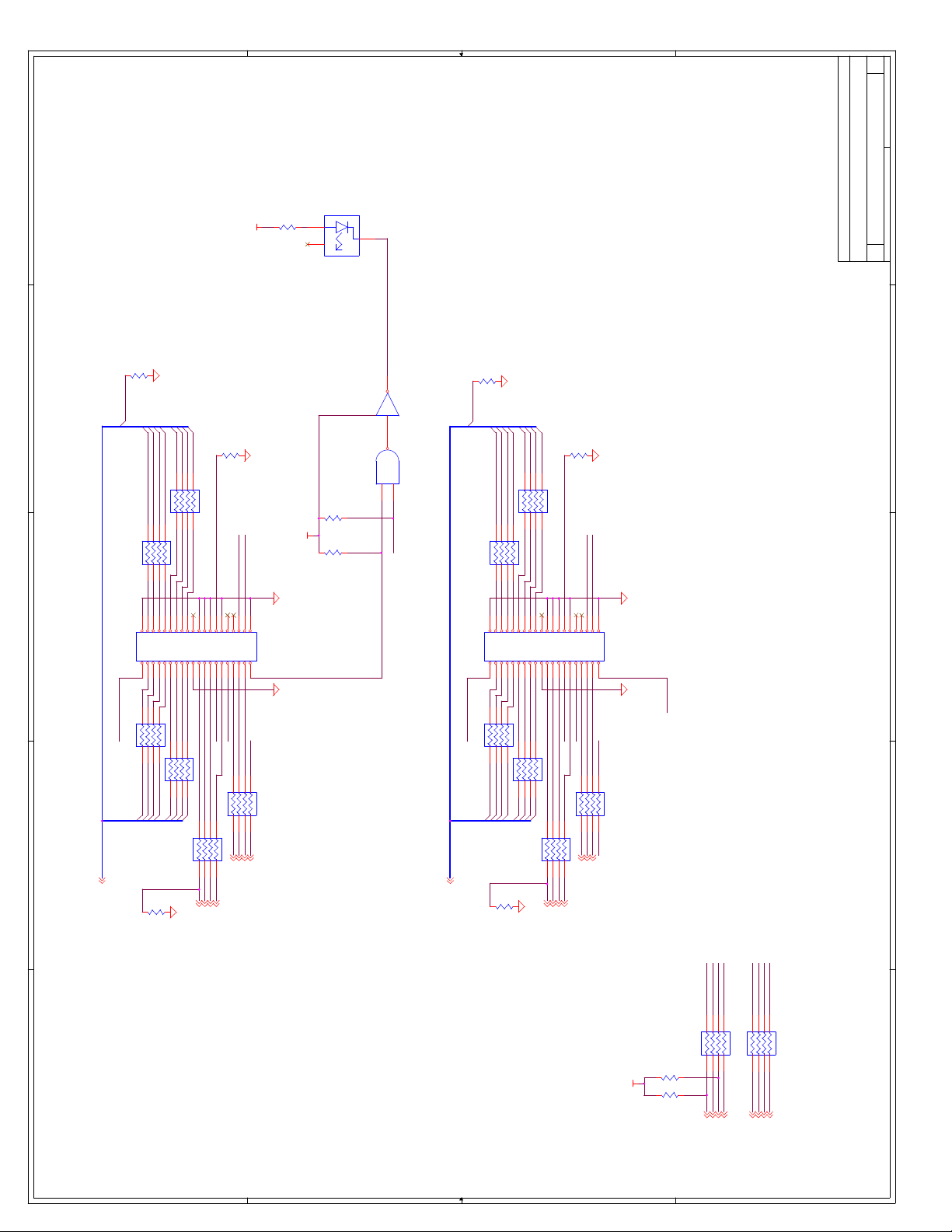

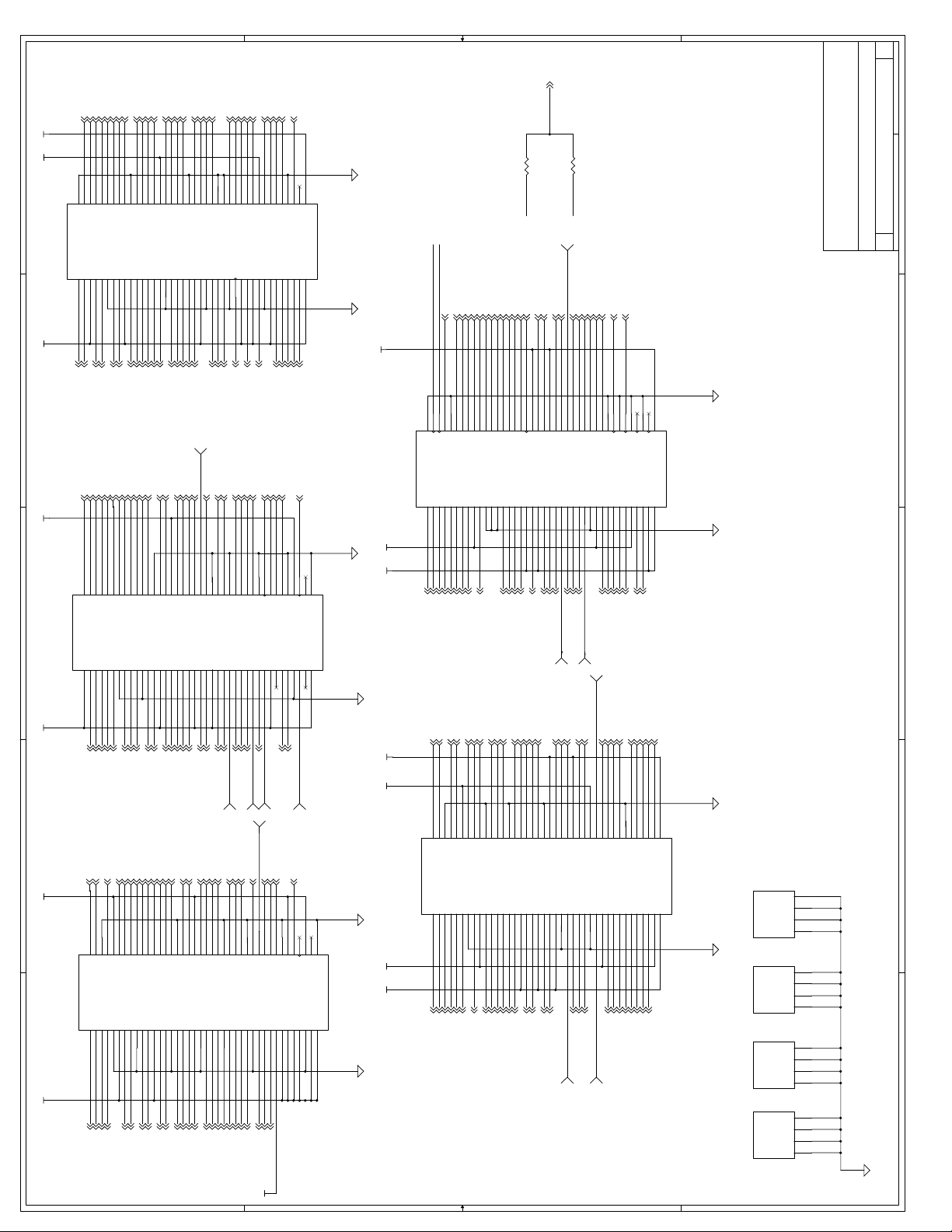

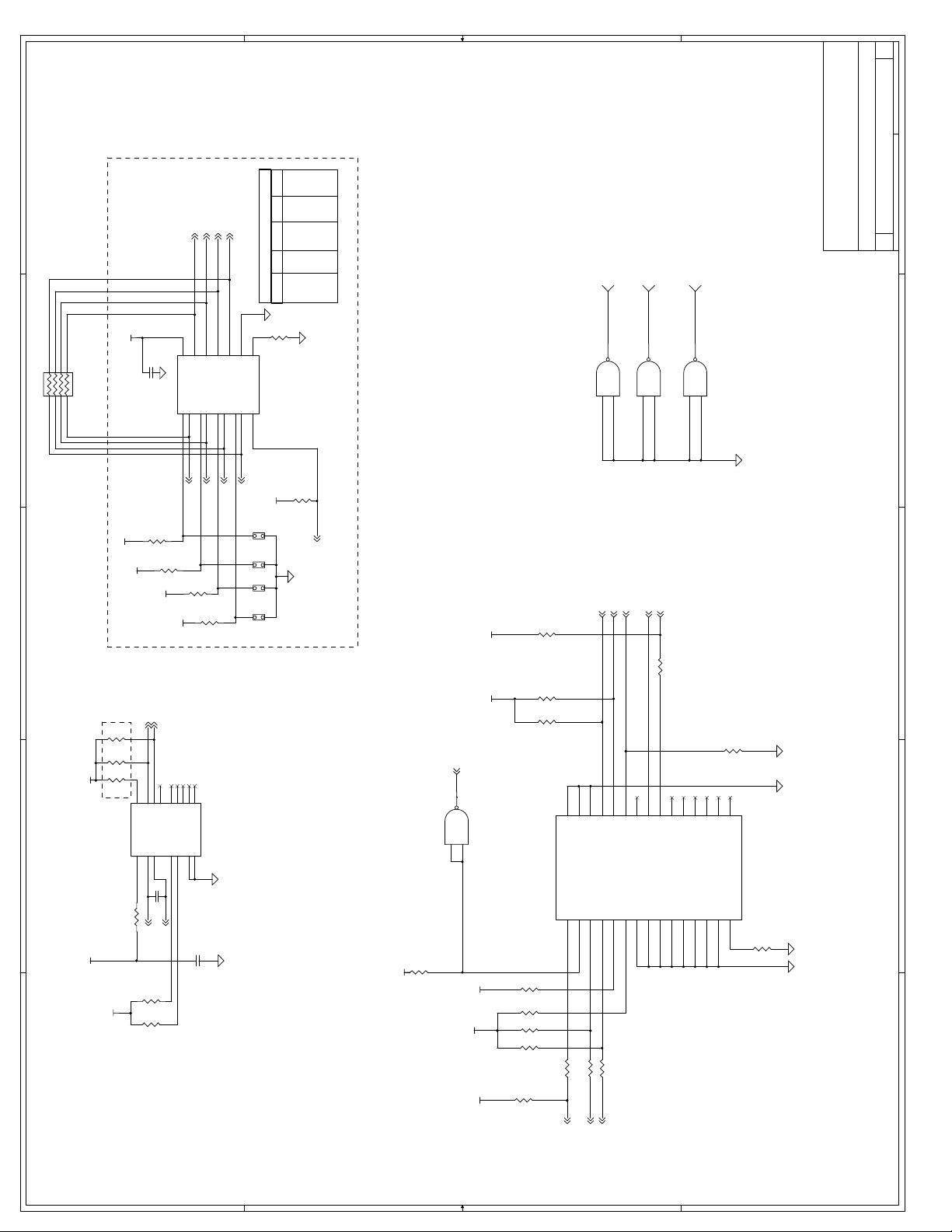

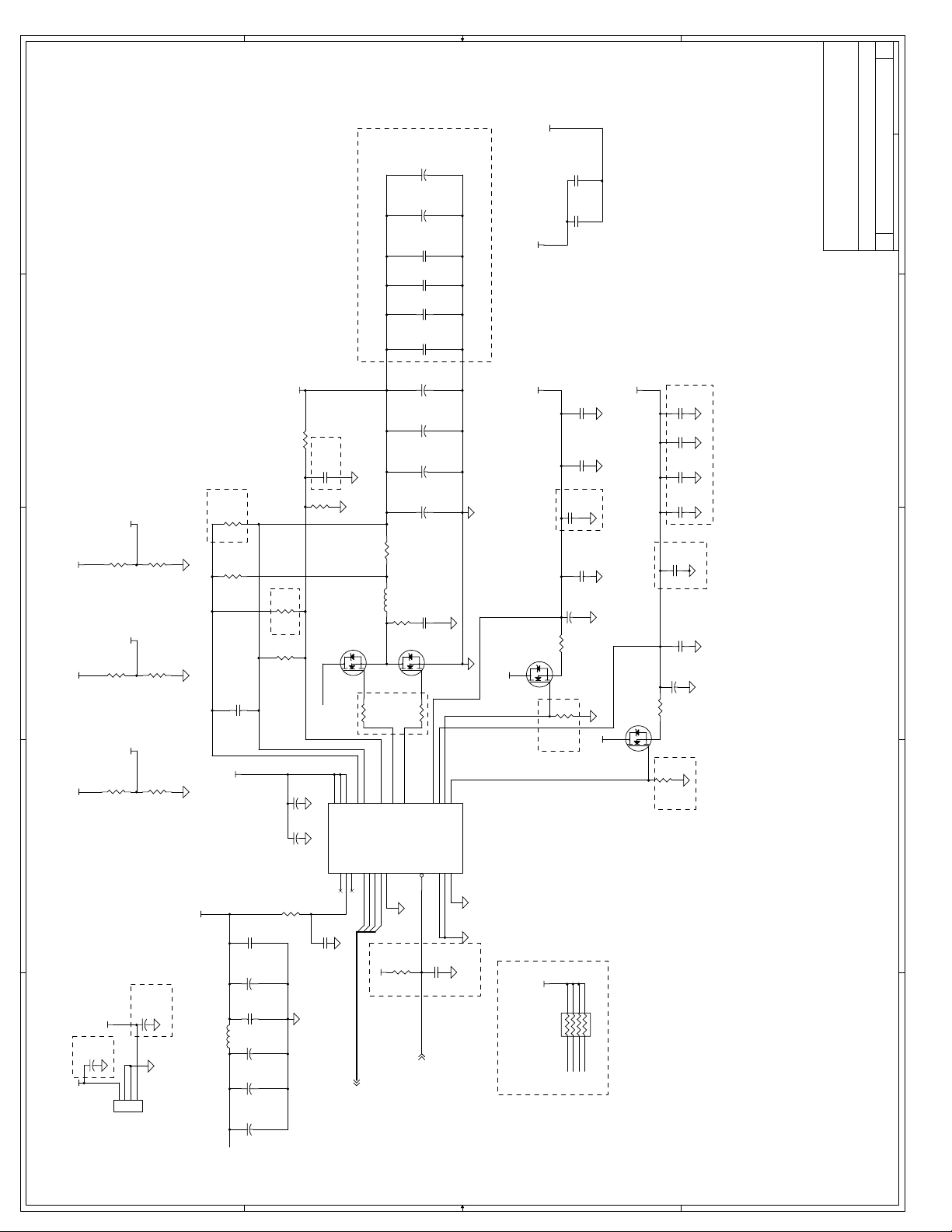

C Schematics ...............................................................................................................C-1

Index .................................................................................................................................Index-1

Figures

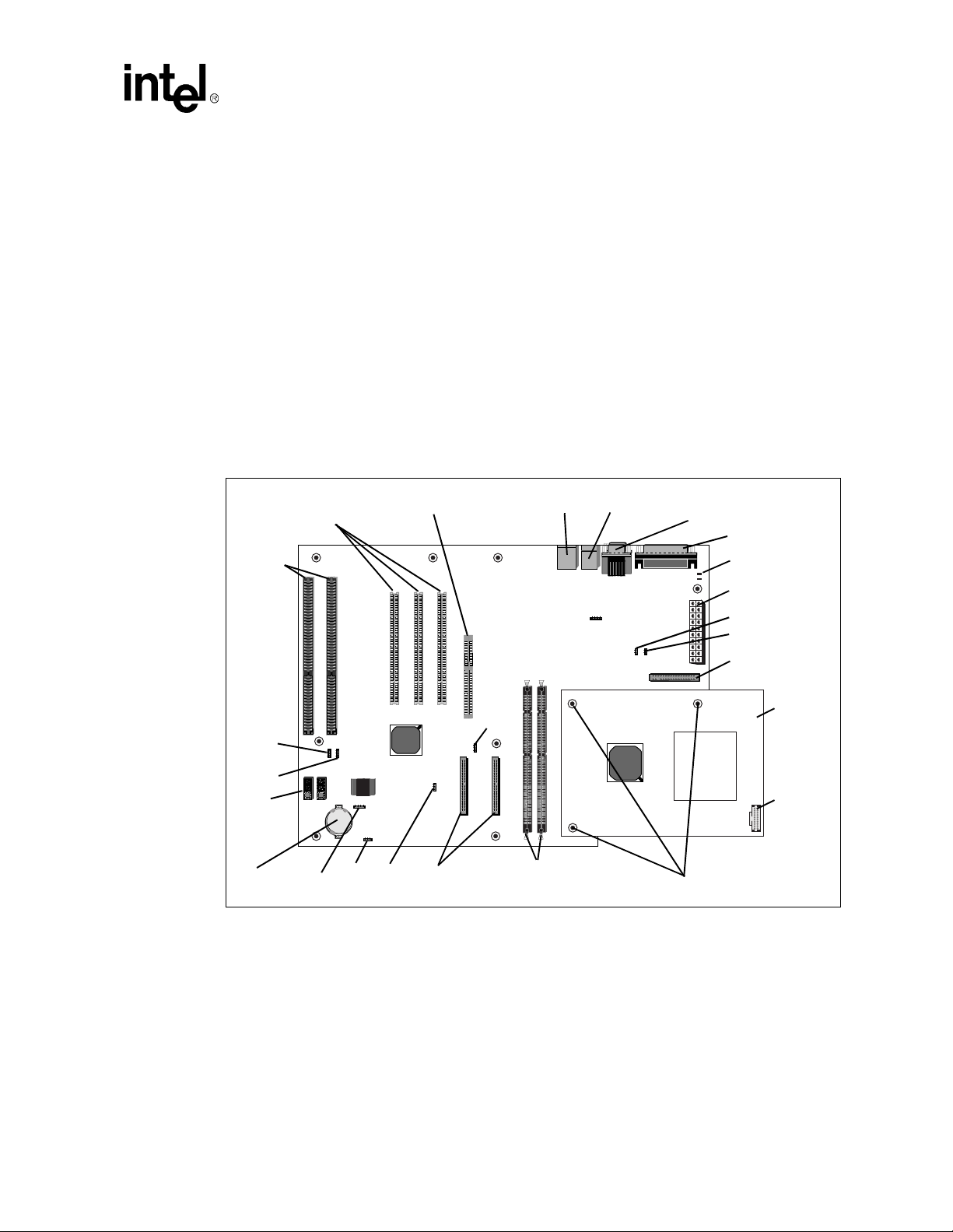

2-1 Evaluation Board Jumpers and Connectors.......................................................2-5

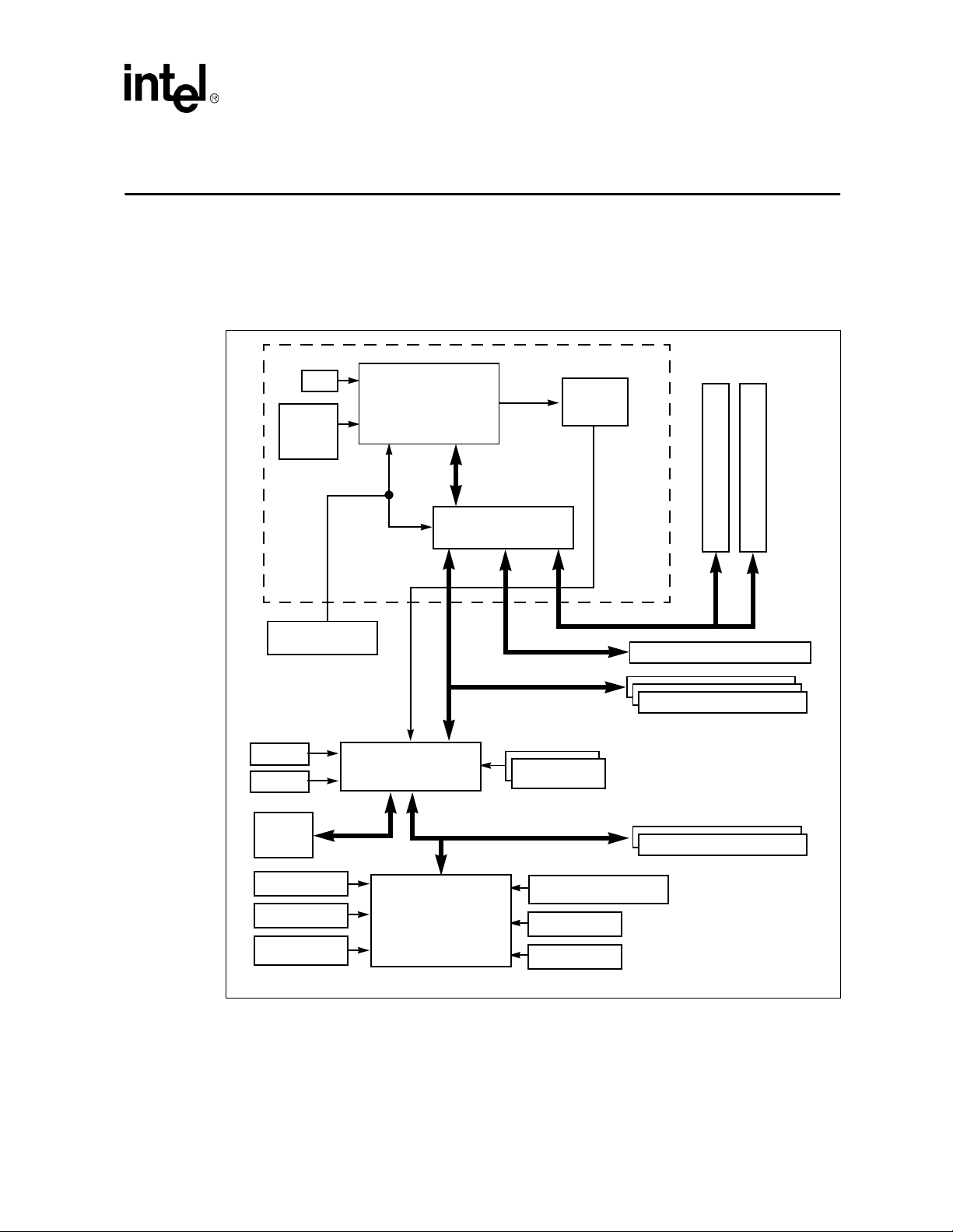

3-1 Evaluation Board Block Diagram........................................................................3-1

5-1 BIOS POST Pre-Boot Environment....................................................................5-2

5-2 Embedded BIOS Setup Screen Menu................................................................5-3

5-3 Embedded BIOS Basic Setup Screen................................................................5-4

5-4 Embedded BIOS Custom Setup Screen ............................................................5-7

5-5 Embedded BIOS Shadow Setup Screen............................................................5-7

5-6 Standard Diagnostic Routines Setup Screen.....................................................5-8

5-7 Start RS232 Manufacturing Link Setup Screen..................................................5-9

5-8 CE-Ready Boot Feature...................................................................................5-10

5-9 Integrated BIOS Debugger Running Over a Remote Terminal........................5-11

Tables

1-1 Related Documents............................................................................................1-4

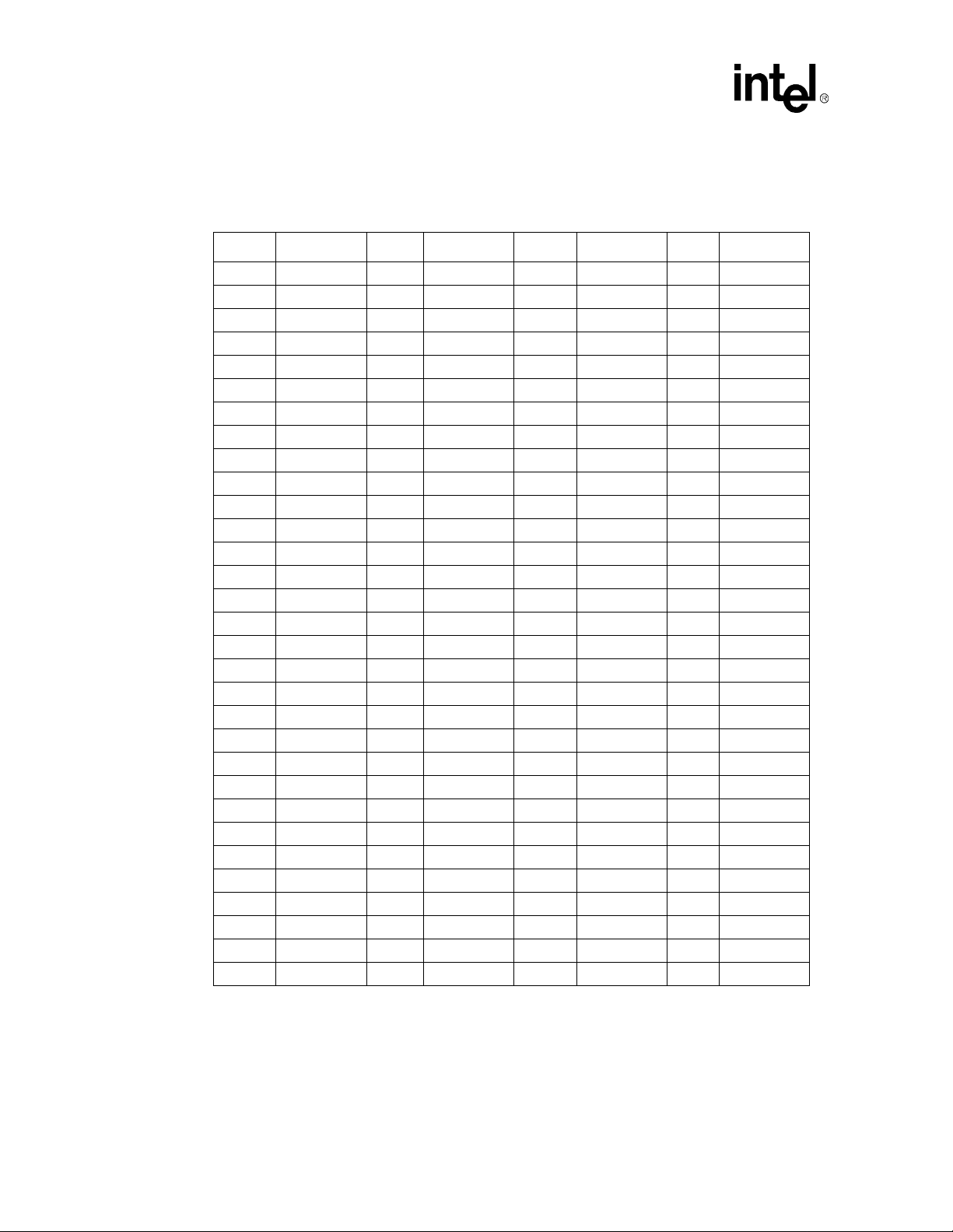

3-1 Interrupts............................................................................................................3-6

3-2 Memory Map ......................................................................................................3-7

4-1 PCI Device Mapping...........................................................................................4-2

4-2 Primary Power Connector (J11).........................................................................4-3

4-3 ITP Connector Pin Assignment (J2 on the Processor Assembly) ......................4-4

4-4 USB Connector Pinout (J2)................................................................................4-4

4-5 Keyboard and Mouse Connector Pinouts (J1 on the Baseboard)......................4-5

4-6 DB25 Parallel Port Connector Pinout (J3)..........................................................4-5

4-7 Serial Port Connector Pinout (J4).......................................................................4-6

4-8 PCI IDE1 (JP3) and IDE2 (JP4) Connector........................................................4-6

4-9 Diskette Drive Header Connector (JP1).............................................................4-7

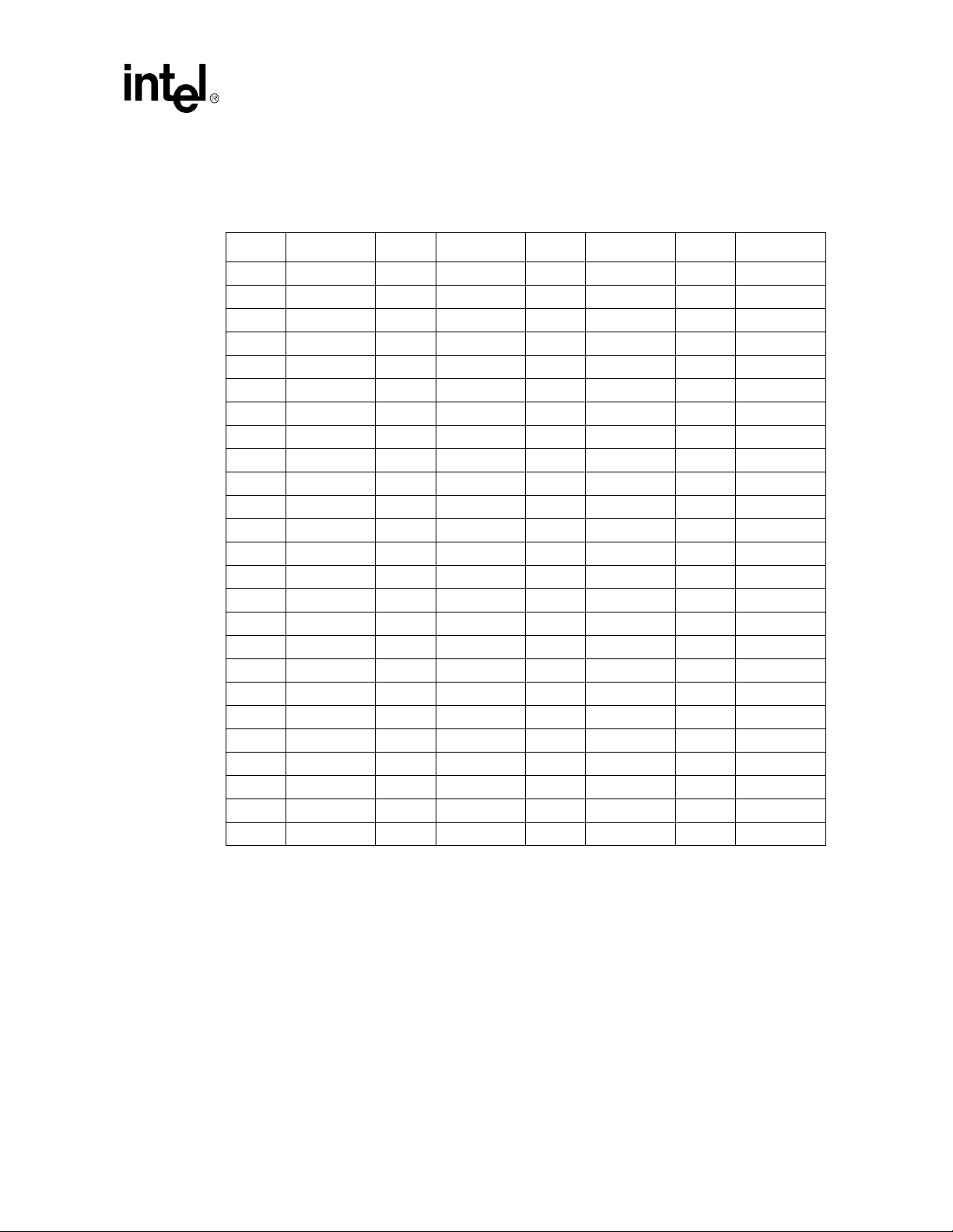

4-10 PCI Slots (J7, J8, J9)..........................................................................................4-8

4-11 ISA Slots (J5, J6)................................................................................................4-9

4-12 AGP Slot (J13) .................................................................................................4-10

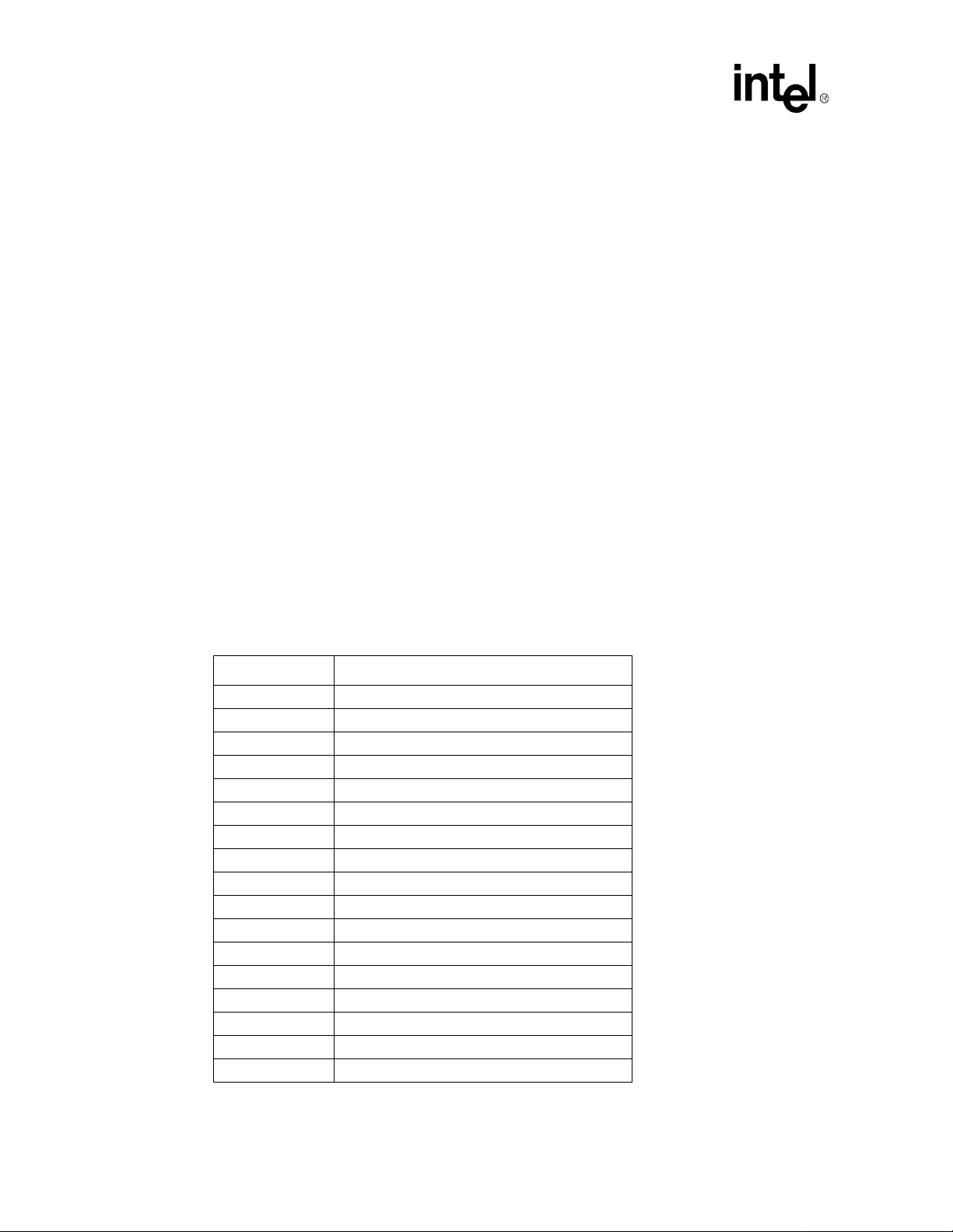

4-13 Default Jumper Settings...................................................................................4-11

5-1 IDE0-IDE3 Drive Assignments...........................................................................5-5

B-1 Baseboard Bill of Materials................................................................................ B-1

B-2 Celeron™ Processor Assembly Bill of Materials............................................... B-5

Celeron™ Processor Development Kit Manual

v

Page 6

Page 7

About This Manual

This manual tells you how to set up and us e the eval uati on board and pr oces sor ass embly i nclu ded

in your Celeron™ Processor Development Kit.

1.1 Content Overview

Chapter 1, “About This Manual” - This chapter contains a description of conventions used in this

manual. The last few sections tell you how to obtain literature and contact customer support.

Chapter 2, “Getting Started” - Provides complete instructions on how to configure the evaluation

board and processor assembly by setting jumpers, connecting peripherals, providing power, and

configuring the BIOS.

Chapter 3, “Theory of Operation” - This chapter provides information on the system design.

Chapter 4, “Hardware Reference” - This chapter provides a description of jumper settings and

functions, and pinout information for each connector.

Chapter 5, “BIOS Quick Reference” - This chapter describes how to configure the BIOS for your

system configuration. A summary of all BIOS menu options is provided.

Appendix A, “PLD Code Listing” - This appe ndix i nclud es a sample code li stin g for t he Post Code

Debugger .

1

Appendix B, “Bill of Materials” - This appendix contains the bill of materials for the evaluation

board.

Appendix C, “Schematics” - This appendix contains schematics for selected connectors and

subsystems for the evaluation board.

1.2 Text Conventions

The following notations may be used throughout this manual.

# The pound symbol (#) appended to a signal name indicates that the

signal is active low.

Variables Variables are shown in italics. Variables must be replaced with correct

values.

Instructions Instruction mnemonics are shown in uppercase. When you are

programming, instructions are not case-sensitive. You may use either

upper- or lowercase.

Celeron™ Processor Development Kit Manual

1-1

Page 8

About This Manual

Numbers Hexadecimal numbers are represented by a string of hexadecimal digits

Units of Measure The following abbreviations are used to represent units of measure:

followed by the character H. A zero prefix is added to numbers that

begin with A through F. (For example, FF is shown as 0FFH.) Decimal

and binary numbers are represented by their customary notations. (That

is, 255 is a decimal number and 1111 1111 is a binary number. In some

cases, the letter B is added for clarity.)

Aamps, amperes

Gbyte gigabytes

Kbyte kilobytes

KΩ kilo-ohms

mA milliamps, milliamperes

Mbyte megabytes

MHz megahertz

ms milliseconds

mW milliwatts

ns nanoseconds

pF picofarads

Wwatts

Vvolts

µA microamps, microamperes

µF microfarads

µs microseconds

µW microwatts

Signal Names Signal names are shown in uppercase. When several signals share a

common name, an individual signal is represented by the signal name

followed by a number, while the group is represented by the signal name

followed by a variable (n). For example, the lower chip-select signals

are named CS0#, CS1#, CS2#, and so on; they are collectively called

CSn#. A pound symbol (#) appended to a signal name identifies an

active-low signal. Port pins are represented by the port abbreviation, a

period, and the pin number (e.g., P1.0).

1.3 Technical Support

1.3.1 Electronic Support Systems

Intel’s site on the World Wide Web (http://www.intel.com/) provides up-to-date technical

information and product support. This information is available 24 hours per day, 7 days per week,

providing technical information whenever you need it.

1.3.1.1 Online Documents

Product doc umentation is pro vided online in a v ariety of web-friendly formats at:

http://developer.intel.com/design/litcentr/index .htm

1-2

Celeron™ Processor Development Kit Manual

Page 9

1.3.1.2 Intel Product Forums

Intel provides technical expertise through electronic messaging. With publicly accessible forums,

you have all of the benefits of email technical support, with the added benefit of the option of

viewing previous messages written by other participants, and providing suggestions and tips that

can help others.

Each of Intel’s technical support forums is based on a single product or product family. Questions

and replies are limited to the topic of the particular forum. Intel also provides several non-technical

support related forums.

Complete information on Intel forums is available at:

http://support.intel.com/newsgroups/index.htm

1.3.2 Telephone Technical Support

In the U.S. and Canada, technical support representatives are available to answer your questions

between 5 a.m. and 5 p.m. PST. You can also fax your questions to us. (Please include your voice

telephone number and indicat e whether you prefer a response b y phone or b y fax). Outside the U.S .

and Canada, please contact your local distributor.

About This Manual

1-800-628-8686 U.S. and Canada

916-356-7599 U.S. and Canada

916-356-6100 (fax) U.S. and Canada

1.4 Product Literature

You can order product literature from the following Intel literature centers.

1-800-548-4725 U.S. and Canada

708-296-9333 U.S. (from overseas)

44(0)1793-431155 Europe (U.K.)

44(0)1793-421333 Germany

44(0)1793-421777 France

81(0)120-47-88-32 Japan (fax only)

Celeron™ Processor Development Kit Manual

1-3

Page 10

About This Manual

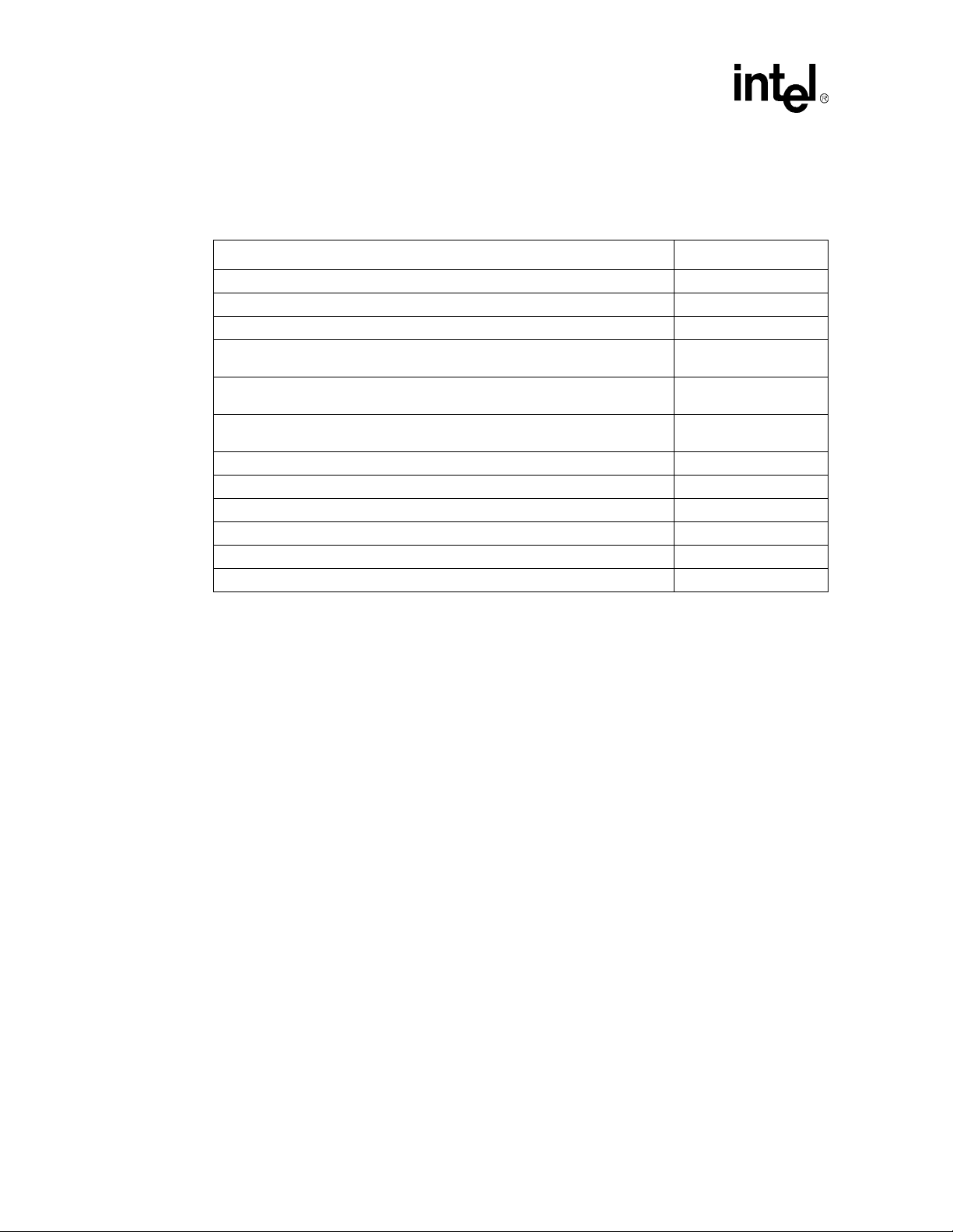

1.5 Related Documents

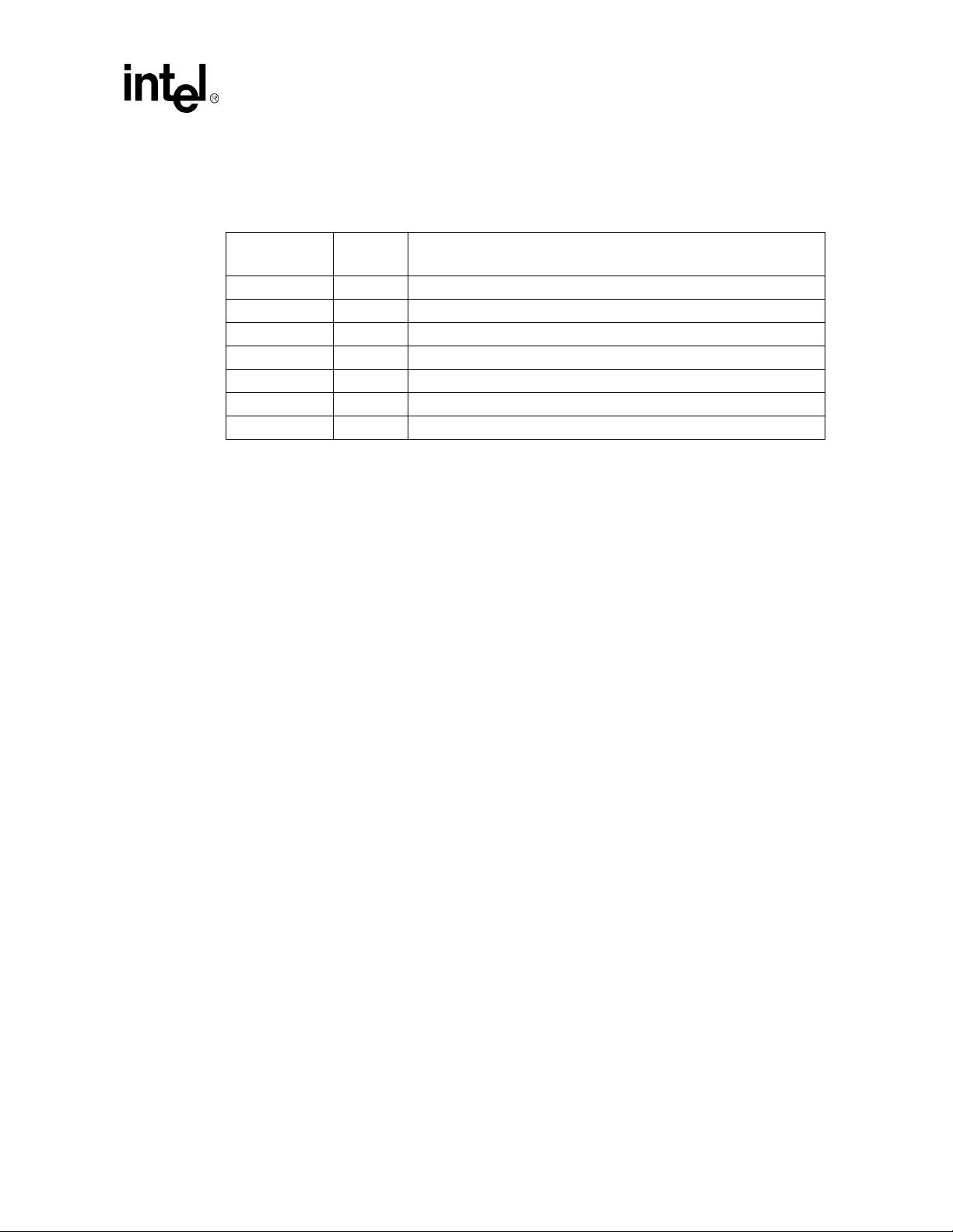

Table 1-1. Related Documents

Document Title Order Number

Intel® Celeron™ Processor

Intel® Celeron™ Processor Specification Update

P6 Family of Processors Hardware Developer’s Manual

Intel Architecture Software Developer’s Manual,

Volume 1: Basic Architecture

Intel Architecture Software Developer’s Manual,

Volume 2: Instruction Set Reference

Intel Architecture Software Developer’s Manual,

Volume 3: System Programming Guide

Intel® 440BX AGPset: 82443BX Host Bridge/Controller

Intel® 440BX AGPset: 82443BX Host Bridge/Controller Specification Update

Intel® 440BX AGPset: 82443BX Host Bridge/Controller Timing Specification

82371AB (PIIX4) and 82371EB (PIIX4E) PCI-TO-ISA/IDE Xcelerator

Intel 82371EB (PIIX4E) Specification Update

Intel 82371AB PCI ISA IDE Xcelerator (PIIX4) Timing Specification

datasheet 243658

datasheet 290633

datasheet 290562

243748

244001

243190

243191

243192

290639

273218

290635

273135

1-4

Celeron™ Processor Development Kit Manual

Page 11

Getting Started

This chapter identifies the Development Kit’s key components, features and specifications, and

tells you how to set up the board for o peratio n.

2.1 Overview

The evaluation board consists of a baseboard and a processor assembly.

• The processor assembly contains an Intel

Bridge/Controller.

• The baseboard contains the 82371EB PCI ISA IDE Xcelerator (PIIX4E) and other system

board components and peripheral connectors.

Warning: The processor assembly is attached to the baseboard at the factory. Do not remove the processor

assembly from the baseboard. Intel will not support the processor assembly or the baseboard if any

portion of the assembly is removed by the customer.

2.1.1 Processor Assembly Features

The processor assembly features are summarized below.

®

Celeron™ Processor and an 82443BX Host

2

• Celeron Processor in a PPGA package (Socket-370) with 66-MHz system bus frequencies

• Intel 440BX AGPset: 82443BX Host Bridge/Controller

• 66 MHz memory interface: A wide range of DRAM support including:

— 64-bit memory data interface plus 8 ECC bits and hardware scrubbing

— 60 ns EDO DRAM and 66 MHz SDRAM support

— 16 Mbit and 64 Mbit DRAM technologies

• Five PCI masters

— PCI Specification Rev 2.1 Compliant

• Accelerated Graphics Port (AGP) Support:

— AGP Interface Specification Revision 1.0 compliant

— AGP - 66/133 MHz, 3.3-V device support

• Integrated System Power Management support

Celeron™ Processor Development Kit Manual

2-1

Page 12

Getting Started

2.1.2 Baseboard Features

The baseboard has these features:

• Flash system BIOS ROM

— General Software system BIOS

— In-circuit BIOS upgradability

• Two SDRAM DIMM connectors

• 32-Mbyte SDRAM DIMM included

— 4 Mbyte x64, 3.3 V, 66 MHz with a CAS latency of 2

• User-accessible on-board connectors include:

— Two serial RS-232 ports; COM1, COM2

— One EPP/ECP parallel port

— PS/2 keyboard and PS/2 mouse (6-pin mini-DIN connectors)

— Two USB ports

— Two IDE bus connectors

— One floppy connector

— Three PCI expansion slots and two ISA expansion slots. There are no shared slots; all

slots are usable.

— One AGP connector

— Standard ATX power supply connector

• Miscellaneous features include:

— On board post-code debugger (Port 80)

— Reset push button

— Stand-off feet for table-top operation

2.2 Included Hardware

• Evaluation board (baseboard and processor assembly combination)

• 3.2-Gbyte hard disk drive pre-loaded with the QNX Real Time Operating System*

• 32-Mbyte SDRAM DIMM

• Attached heatsink and fan

• PCI video graphics adapter using the CHIPS* 69000 HiQVideo* Accelerator

• Mounting hardware

• IDE cable for the hard disk drive

2-2

Celeron™ Processor Development Kit Manual

Page 13

2.3 Software Key Features

The software in the kit was chosen to facilitate development of real-time applications based on the

components used in the evaluation board. The software tools included in your kit are described in

this section.

Note: Software in the kit is provided free by the vendor and is only licensed for evaluation purposes.

Customers using the tools that work with Microsoft products must have licensed those products.

Any targets created by those tools should also have appropriate licenses. Software included in the

kit is subject to change.

2.3.1 General Software, Inc.

Embedded BIOS is a full-featured BIOS for x86-based handheld, embedded, and volume

consumer electronics applications. This product offers a winning combination of superior OEM

configurability and superior embedded featu res .

Embedded BIOS leads the industry with all the on-target embedded features that OEMs making

embedded, handheld, mobile, and consumer electronics demand:

• CE Ready*, the Windows CE* launcher

• Integrated BIOS-aware debugger

• Resident Flash Disk disk emulator

• ROM disk and RAM disk emulators

• Manufacturing Mode for in-field diagnosis and software upgrades

• Power management that can operate in an APM or stand-alone environment

• PCI resource management

• Matrix keyboard support

• LCD panel driver s

• Console redirection over RS232 ports

• Flexibility to boot from man y disk servers

• OEM-configurable setup screen system

• Embedded DOS*-ROM (adap t ation kit and license )

• Total compatibility with industry standards

Getting Started

Celeron™ Processor Development Kit Manual

2-3

Page 14

Getting Started

2.3.2 QNX Software Systems, Ltd.

QNX Real Time Operating System for Intel Architecture.

• Small memory footprint of the QNX operating system with microGUI

• QNX microGUI is a full featured graphical user interface (GUI) and windowing system

• Photon Application Builder

• QNX Development kit prov ides the basic utilities to build and program Intel Flash

• Watcom C/C++ Development Suite: is a full featured development suite

• Includes compiler, assembler and debugger with full support for the QNX microGUI function

library

• Makes development of the QNX executables fast, easy and optimized

Caution: Use the shutdown button to exit from QNX. Improper shutdown may result in the loss of the file

system.

2.4 Before You Begin

Before you set up and configure your evaluation board, you may want to gather some additional

hardware and software.

VGA Monitor Y o u can use any standard VGA or multi-resolution monitor. The setup

instructions in this chapter assume that you are using a standard VGA

monitor.

Power Supply You must use an ATX-type PC power supply.

Keyboard You need a keyboard with a PS/2 style connector or adapter.

Mouse Optional. You can use a mouse with a PS/2 style connector or adapter.

Additional Drives You can connect up to four IDE drives and a floppy drive to the

evaluation board. Two devices (master and slave) can be attached to

each IDE connector. You will need to provide the cables for these

drives.

You may have all these storage devices attached to the board at the

same time.

Video Adapter You can use the Chips and Technologies video adapter supplied with

your kit, or you can use a different adapter. The evaluation board

supports AGP, PCI and ISA video cards. It is up to you to install the

correct drivers for video adapters other than the one provided.

Other Devices

and Adapters

The evaluation board behaves much like a standard desktop computer

motherboard. Most PC compatible peripherals can be attached and

configured to work with the evaluation board. For example, you may

want to install a sound card or network adapter.

2-4

Celeron™ Processor Development Kit Manual

Page 15

Getting Started

2.5 Setting up the Evaluation Board

Once you have gathered the hardware described in the las t section, fo llow the steps below to set up

your evaluation board. This manual assumes y ou are familiar with basic concepts involved with

installing and configuring hardware for a personal computer system. Refer to Figure 2-1 for

locations of connectors, jumpers, etc.

1. Make sure you are in a static-free environment before removing any components from their

anti-static packaging. The evaluation board is susceptible to electro-static discharge damage;

such damage may cause product failure or unpredictable operation.

2. Inspect the contents of your kit. Check for damage that may have occurred during shipment.

Contact your sales representative if any items are missing or damaged.

Caution: Connecting the wrong cable or reversing the cable can damage the evaluation board and may

damage the device being connected. Since the board is not in a protective chassis, use caution when

connecting cables to this product.

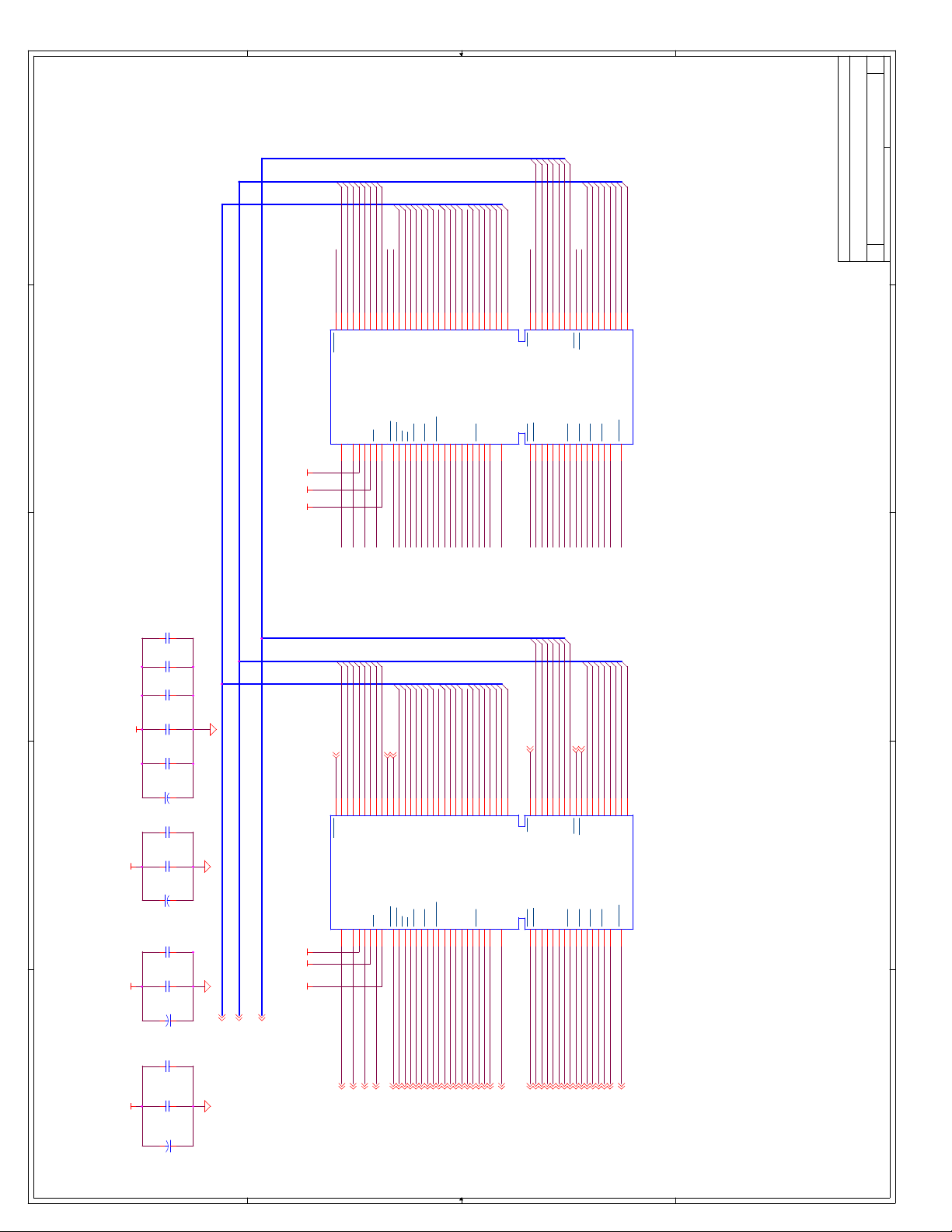

Figure 2-1. Evaluation Board Jumpers and Connectors

Connectors

ISA

Connectors

J21

J22

Post

Code

Debugger

Battery JP2

PCI AGP Connector USB Keyboard (Top) COM1 (Top)/

/Mouse COM2

J12

J5 J6

J12

J7 J8 J9

J2

J1

J12

J13

J18J17

J3

J4

J14 J15

JP1

D1

D2

J11

Parallel Port

LEDs

ATX Power

Connector

J14

J15

Floppy

Connector

J20

U12 U13

J21 J22

U11

JP2

J24

J23J24 SDRAM

IDE Connectors

J23

J20

JP2 JP3

IDE2 IDE1

DIMM Slots

Special Mounting Holes

Processor

Assembly

ITP

Debugger

Port

J2

Celeron™ Processor Development Kit Manual

2-5

Page 16

Getting Started

3. Make sure the board’s jumpers are set to the following default locations.

• J14 - Not installed

• J15 - Installed

• J20 - Jump er pins 2-3

• J21 - Jump er pins 2-3

• J22 - Jump er pins 2-3

• J23 - Jump er pins 2-3

• J24 - Jump er pins 1-2

4. Mount the hardware:

• Table-top operation: The evaluation board is shipped with standoff “feet” for use in a

table-top environment. These feet are installed on the evaluation board to raise it off the

table surface.Your kit contains two bags of mounting hardware. One bag contains eight

standoff feet, eight mounting screws, and eight washers. Another bag has three shorter

feet that must be attached slightly differently.

— To mount the eight standard feet, insert a washer onto a screw, then push the screw

through the top of the board. From below the board, thread one of the longer feet

onto the screw.

— To mount the three special feet, screw the three

screws. See Figure 2-1 for the location of the three special holes.

Warning: Do not remove the nuts from these three holes! This will detach the process or ass e mbly from the

baseboard, and Intel will no long er support the evaluation board.

• The evaluation board is not ATX compatible.

5. Connect desired storage devices to the evaluation board:

The evaluation board supports Primary and Secondary I DE interfaces that can each host one or

two devices (master/slave). When you are using multiple devices, such as a hard disk and a

CD-ROM drive, make sure the hard disk drive has a jumper in the master position and the CDROM has a jumper in the slave position. When you are using a single IDE device with the

evaluation board, be sure that the jumpers set correctly fo r sing le master operation. Fo r jumper

settings for other configurations, consult the drive’s documentation.

Note: The evaluation board BIOS only supports hard drives of 16 Gbytes or less.

• Installing the IDE hard disk drive included in your kit:

— Connect the hard drive’s IDE connector to the JP4 connector on the evaluation

board. Be sure to align Pin 1 of the cable connector with pin 1 of JP4.

— Connect the other end to the hard disk drive.

Caution: Make sure the tracer on the ribbon cable is aligned with pin 1 on both the hard disk and the IDE

connector header. Connecting the cable backwards can damage the evaluation board or the hard

disk.

shorter feet onto the existing

2-6

— Connect the hard drive to the power supply.

Note: The hard disk is already formatted and is pre-loaded with the QNX Real-Time Operating System

for Intel Architecture.

Celeron™ Processor Development Kit Manual

Page 17

Getting Started

— You may have to make changes to the system BIOS to enable this hard disk. See

Chapter 5, “BIOS Quick Reference” for more information.

• Floppy drive: A floppy disk drive connected to the evaluation board is the most direct

method for loading software.

— Insert floppy cable into JP1 (be sure to orient Pin 1 correctly).

— Connect the other end of the ribbon cable to the floppy drive.

— Connect a power cable to the floppy drive.

— You must make changes to the system BIOS to enable this floppy disk. See

Chapter 5, “BIOS Quick Reference” for more information.

6. Make sure the SDRAM DIMM is installed in the socket labeled J18.

7. Connect a PS/2 mouse and keyboard (see Figure 2-1 for connector locations).

Note: J1 (on the baseboard) is a stacked PS/2 connector. The bottom connector is for the mouse and the

top is for the keyboard.

8. Install the Chips and Technologies PCI video adapter into one of the available PCI slots.

Connect the monitor cable to the VGA port on the card.

9. Connect the power supply:

You’ll need a standard ATX PC power supply. Make sure the power supply is unplugged (or

turned off), then connect the power supply cable to the power header (J11).

Note: Some ATX power supplies do not have an on/off switch. In this case remove jumper J20 before

plugging in the ATX power connector. J20 controls an internal power supply on/off switch. When

you are ready to apply power , ins ert the ju mper on pins 2-3 . You may want to wire this header up to

a toggle switch for convenience.

Turn on the power to the monitor and evaluation board. When the power is on you should see two

power-indicator LEDs light up (located next to the ATX power connector in the upper right corner

of the board; see Figure 2-1). Check to see that the fan on the processor is operating.

2.6 Configuring the BIOS

General Software’s BIOS software is pre-loaded on the evaluation board. You will have to make

changes to the BIOS to enable hard disks, floppy disks and other supported features You can use

the Setup program to modify BIOS settings and control the special features of the system. Setup

options are configured through a menu-driven user interface. Chapter 5, “BIOS Quick Reference”

contains a description of BIOS options.

BIOS updates may periodically be posted to Intel’s Developers’ web site at

http://developer.intel.com/.

Celeron™ Processor Development Kit Manual

2-7

Page 18

Page 19

Theory of Operation

3.1 Block Diagram

Figure 3-1. Evaluation Board Block Diagram

3

Processor Assembly

ITP

VCCcore

Voltage

Regulator

Clock Generator

USB

I/O APIC

Boot

Flash

Celeron™ Processor

with 128 Kbyte

Integrated L2 Cache

PIIX4E

XD Bus

Processor

Side Bus

82443BX

Host Bridge/Controller

PCI Bus

ISA Bus

Thermal

Sensor

DRAM Bus

AGP Bus

Bus Master IDE

SMBus

72-Bit DIMM

AGP Connector

PCI Connectors

ISA Connectors

72-Bit DIMM

PS/2 Mouse

PS/2 Keyboard

Floppy Drive

SMC FDC37B78X

SuperI/O*

Celeron™ Processor Development Kit Manual

IEEE 1284 Parallel Port

COM1

COM2

3-1

Page 20

Theory of Operation

3.2 System Operation

The Celeron™ processor evaluation board is a full-featured system board and processor assembly.

The processor assembly includes either a 366-MHz or a 433-MHz Celeron processor (based on the

development kit purchased) with 128 Kbytes of integrated L2 cache and the Intel 82443 BX Host

Bridge/Controller. The evaluation board contains the Intel 82371EB PCI-to-ISA/IDE Xcelerator

(PIIX4E) and other system and I/O peripherals.

The evaluation board and pr oces sor assembly support 300-MHz, 366-MHz, and 433 MHz Cel eron

processors with 128 Kbytes of integrated L2 cache. The customer may remove the Celeron

processor from the processor socket and replace it with another supported version. Do not remove

the processor assembly. The evaluation board automatically detects which processor is installed in

the socket.

3.2.1 Celeron Processor

The Celeron processor for appli ed computing is of fered at 36 6 MHz and 433 MHz with a processo r

system bus speed of 66 MHz. The Celeron pr ocessor co nsists of a Pentium

an integrated second level cache and a 64-bit high-performance host bus. The processor has a

private second level cache bus that allows a high-performance 64-bit wide cache subsystem to be

integrated on the same die as the processor. The processor can cache up to 4 Gbytes of memory

using 128 Kbytes of L2 cache, 16 Kbytes of L1 data cache and 16 Kbytes of L2 code cache. The

private first and second level cache operate at the same frequency and voltage as the processor core

to improve performance and reduce total system power consumption.

3.2.2 82443BX Host Bridge/Controller

The Intel® 440BX AGPset supports the Pentium II processor architecture. It interfaces with the

Celeron processor system bus at 66 MHz. Along with its Host-to-PCI bridge interface, the

82443BX Host Bridge/Controller has been optimized with a 66MHz SDRAM memory controller

and data path unit. The 82443BX also features the Accelerated Graphi cs Port (AGP) interface. Th e

82443BX component includes the following functions and capabilities:

• 64-bit GTL+ based system data bus interface

• 32-bit system address bus support

• 64/72-bit main memory interface with optimized support for SDRAM

• 32-bit PCI bus interface with integrated PCI arbiter

• AGP interface with up to 133 MHz data transfer capability

• Extensive data buffering between all interfaces for high throughput and concurrent operations

®

II processor core with

3-2

Celeron™ Processor Development Kit Manual

Page 21

3.2.2.1 System Bus Interface

The 82443BX supports a maximum of 4 Gbytes of memory address space from the processor

perspective. The largest address size is 32 bits. The 82443BX provides bus control signals and

address paths for transfers between the processor bus, PCI bus, Accelerated Graphics Port and

main memory. The 82443BX supports a 4-deep-in-order queue, which provides support for

pipelining of up to four outstanding transaction requests on the system bus.

For system bus-to-PCI transfers, the addresses are either translated or directly forwarded on the

PCI bus, depending on the PCI address space being accessed. When the access is to a PCI

configuration space, the processor I/O cycle is mapped to a PCI configuration space cycle. When

the access is to a PCI I/O or memory space, the processor address is passed without modification to

the PCI bus. Certain memory address ranges are dedicated for a graphics memory address space.

When this space or a portion of it is mapped to main DRAM, the address is translated by the AGP

address remapping mech ani sm an d the request is forwarde d to t h e DRAM subsystem. A portion of

the graphics aperture can be mapped on the AGP, and the corresponding system bus cycles

accessing that range are forwarded to the AGP without any translation. The AGP address map

defines other system bus cycles that are forwarded to the AGP.

3.2.2.2 Accelerated Graphics Port (AGP) Interface

The 82443BX supports an AGP interface. The AGP interface has a maximum theoretical transfer

rate of ~532 Mbytes/s.

Theory of Operation

3.2.2.3 System Clocking

The 82443BX operates the system bus interface at 66 MHz, the PCI bus at 33 MHz and the AGP at

a transfer rate of 66/133 MHz. The 82443BX clocking scheme uses an external clock synthesizer

that produces reference clocks for the system bus and PCI interfaces. The 82443BX generates the

AGP and DRAM clock signals. Please refer to the CK97 Clock Synthesizer/Driver Specification

(order number 243867).

3.2.3 ITP

The evaluation board is pop ulated with a 2.5 V ITP debu gger port. The ITP por t provid es a path for

debugger tools like emulators, in-target probes, and logic analyzers to gain access to the Celeron

processor registers and signals without affecting high speed operation. This allows the system to

operate at full speed with the debugger attached.

Celeron™ Processor Development Kit Manual

3-3

Page 22

Theory of Operation

3.2.4 82371EB PCI to ISA/IDE Xcelerator (PIIX4E)

The 82443BX is designed to support the PIIX4E I/O bridge. The PIIX4E is a highly-integrated

multifunctional component that support s th e following:

• PCI Revision 2.1 compliant PCI-to-ISA bridge with support for 33 MHz PCI operations

• ACPI Power Management support

• Enhanced DMA controller, interrupt controller and timer functions

• Integrated IDE controller with Ultra DMA/33 support

• USB host interface with support for two USB ports

• System Management Bus (SMB) with support for DIMM Serial Presence Detect

3.2.5 DRAM

The evaluation board provides two 168-pin DIMM module connectors. The DRAM interface is a

64-bit data path that supports Synchronous DRAM (SDRAM). The DRAM interface supports

4 Mbytes to 256 Mbytes of 4-Mbit, 16-Mbit and 64-Mbit DRAM and SRAM technology (both

symmetrical and asymmetrical). Parity is not supported. One 32-Mbyte SDRAM DIMM is

included in the kit.

3.2.6 Power

The evaluation board uses an indus try standard ATX-style power supply with a 20- pin connect or . A

230-watt (minimum) supply is recommended. Note th at the ATX power connector is keyed to

prevent incorrect insertion. See “ATX Power Connector” on page 4-3 for a detailed description of

the power connector.

Make sure that the AT X power supply is not plugged into the wall when connecting or

disconnecting it from the evaluation board.

3.2.7 Boot ROM

The system boot ROM installed at U11 is a 2-Mbit 28F002BC flash device. The system is set up

for in-circuit reprogramming of the BIOS, but the flash device is also socketed. This device is

addressable on the XD bus extension of the ISA bus.

3.2.8 RTC/NVRAM

The RTC and NVRAM are contained within the 82371EB PIIX4E device. CMOS NVRAM

backup is provided by a 3-V lithium-ion battery.

3.2.9 Legacy I/O

Support for legacy I/O functions is provided by the Intel 82371EB PIIX4E and the SMC

FDC37B78X SuperI/O* device.

3-4

Celeron™ Processor Development Kit Manual

Page 23

3.2.10 IDE Support

The evaluation board supports both a primary and secondary IDE interface via two 40-pin IDE

connectors. The connector labeled IDE1 is the primary interface. IDE2 is the secondary interface.

3.2.11 Floppy Disk Support

Floppy disk support is provided by the SMC FDC37B78X SuperI/O device. One 34-pin floppy

connector is provided on the evaluation board.

3.2.12 Keyboard/Mouse

Keyboard and mouse support are provided by the SMC FDC37B8X SuperI/O device. The

keyboard and mouse connectors (J1) are PS/2 style, 6-pin stacked miniature DIN connectors. The

top connector is for the keyboard and the bottom connector is for the mouse.

3.2.13 USB

USB support is provided through the PIIX4E and can be used through connector J2.

Theory of Operation

3.2.14 RS232 Ports

Two serial I/O ports provided by the SMC FDC37B78X SuperI/O device. Two 9-pin RS232

connectors are provided on a single stacked connector (J4).

3.2.15 IEEE 1284 Parallel Port

One 25-pin IEEE 1284 parallel port connector controlled by the SMC FDC37B78X SuperI/O

device is provided (J3).

3.2.16 PCI Connectors

Three industry standard 32-bit, 5-V PCI connectors are provided on the evaluation board. The

connectors are designed to handle either a 5-V only card or a universal card. 3.3-V cards are not

supported.

3.2.17 ISA Connectors

Two 16-bit ISA connectors are provided on the evaluation board.

3.2.18 AGP Connector

AGP support is provided through the 82443BX Host Bridge/Controller. One industry standard

AGP connector (J13) is provided on the evaluation board.

Celeron™ Processor Development Kit Manual

3-5

Page 24

Theory of Operation

3.2.19 Post Code Debugger

The evaluation board has an on-board Post Code Debugger. Data from any program that does an

I/O write to 0080H is lat ched and di splayed o n the two LEDs (U12 and U1 3). During BIOS startup,

codes are posted to these LEDs to indicate what the BIOS is doing. Application programs can post

their own data to these LEDs by writing to I/O address 0080 H.

3.2.20 Clock Generation

There are three devices on the baseboard which generate and distribute the clocks used by the

entire system. These are the CY2280 clock synthesizer, CY2318NZ clock bu f fer and the CY23009

zero delay buffer. Not all of these devices are used on this version of the evaluation board.

The CY2280 generates the clocks for the Celeron processor, Host Bridge/Controller, cache, PCI,

USB and ISA bus. The processor clock runs at 66 MHz. The PCI clocks run at 33 MHz. This

device is capable of spread spectrum clocking. If spread spectrum clocking is enabled, a 0.5%

down spread will be introduced in the processor and PCI clocks.

The CY2318NZ clock buffer is used to buffer the clock signals sent to the SDRAM DIMMS. The

SDRAM interface operates at 66 MHz.

The CY2309 Zero Delay Buffer is not used by the evaluation board.

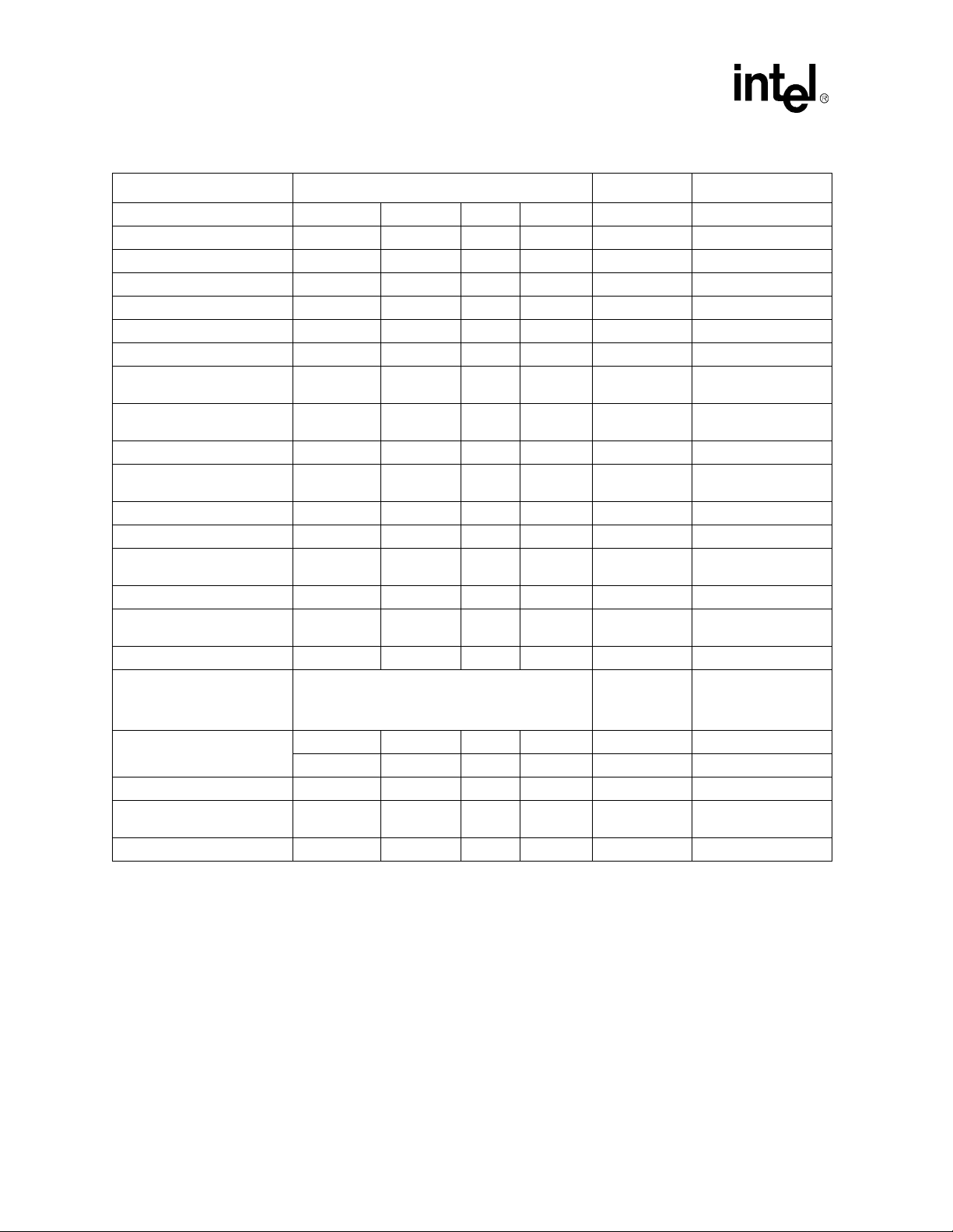

3.2.21 Interrupt Map

Table 3-1. Interrupts

IRQ System Resources

NMI I/O Channel Check

0 Reserved, Interval Timer

1 Reserved, Keyboard buffer full

2 Reserved, Cascade interrupt from slave PIC

3 Serial Port 2

4 Serial Port 1

5 Parallel Port (PNP0 option)

6 Floppy

7 Parallel Port 1

8 Real Time Clock

9 IRQ2 Redirect

10 Reserved. Not supported.

11 Reserved. Not supported.

12 Onboard Mouse Port if present, else user available

13 Reserved, Math coprocessor

14 Primary IDE if present, else user available

15 Reserved. Not supported.

3-6

Celeron™ Processor Development Kit Manual

Page 25

3.2.22 Memory Map

T able 3-2. Memory Map

Theory of Operation

Address Range

(Hex)

100000-8000000 127.25M Extended Memory

E0000-FFFFF 128K BIOS

C8000-DFFFF Available expansion BIOS area (Flash disk memory window)

A0000-C7FFF Off-board video memory and BIOS

9FC00-9FFFF 1K Extended BIOS Data (movable by QEMM, 386MAX)

80000-9FBFF 127K Extended conventional

00000-7FFFF 512K Conventional

Size Description

Celeron™ Processor Development Kit Manual

3-7

Page 26

Page 27

Hardware Reference

This section provides reference information on the system design. Included in this section is

connector pinout information, jumper settings, and other system design information.

4.1 Processor Assembly

The processor assembly cont ai ns t he Cel er on™ proces s or, the 82443BX Host Bridge/Controller, a

voltage regulator and an ITP debugger connector. The assembly connects to the baseboard via a

400-pin connector.

Warning: The processor assembly is attached to the baseboard at the factory. Do not remove the processor

assembly from the baseboard. Intel will not support the processor assembly or the baseboard if any

portion of the assembly is removed by the customer.

4.1.1 Thermal Management

The objective of thermal management is to ensure that the temperature of each component is

maintained within specified functional limits. The functional temperature limit is the range within

which the electrical circuits can be expected to meet their specified performance requirements.

Operation outside the functional limit can degrade system performance and cause reliability

problems.

4

Important: The evaluation kit contains a heatsink and fan attached to the top of the Celeron processor. This

thermal solution has been tested in an open air environment at room temperature and is sufficient

for evaluation purposes only. It is up to the designer to provide adequate thermal management for

any designs derived from the schematics provided in your kit.

4.1.2 ITP Debugger Port

The evaluation platform i s p opu l ated wit h a 2.5 V ITP debugger port . T he I T P po rt pro vi des a path

for debugger tools like emulators, in-target probes, and logic analyzers to gain access to the

Celeron processor’s registers and signals without affecting high speed operation. This allows the

system to operate at full speed with the debugger attached.

4.2 Post Code Debugger

The evaluation board has an on-board Post Code Debugger. Data from any code that does an I/O

write to 80H is latched on the two led di splays (U12/U13). During BIOS startup, code is posted to

these LEDs to indicate what the BIOS is doing. Application code can post its own data to these

LEDs by doing an I/O write to address 80H. The 22V10 PLD code used to implement this function

is included in Appendix A, “PLD Code Listing.”

Celeron™ Processor Development Kit Manual

4-1

Page 28

Hardware Reference

4.3 ISA and PCI Expansion Slots

The evaluation platform has three PCI expansion slots and two ISA slots.

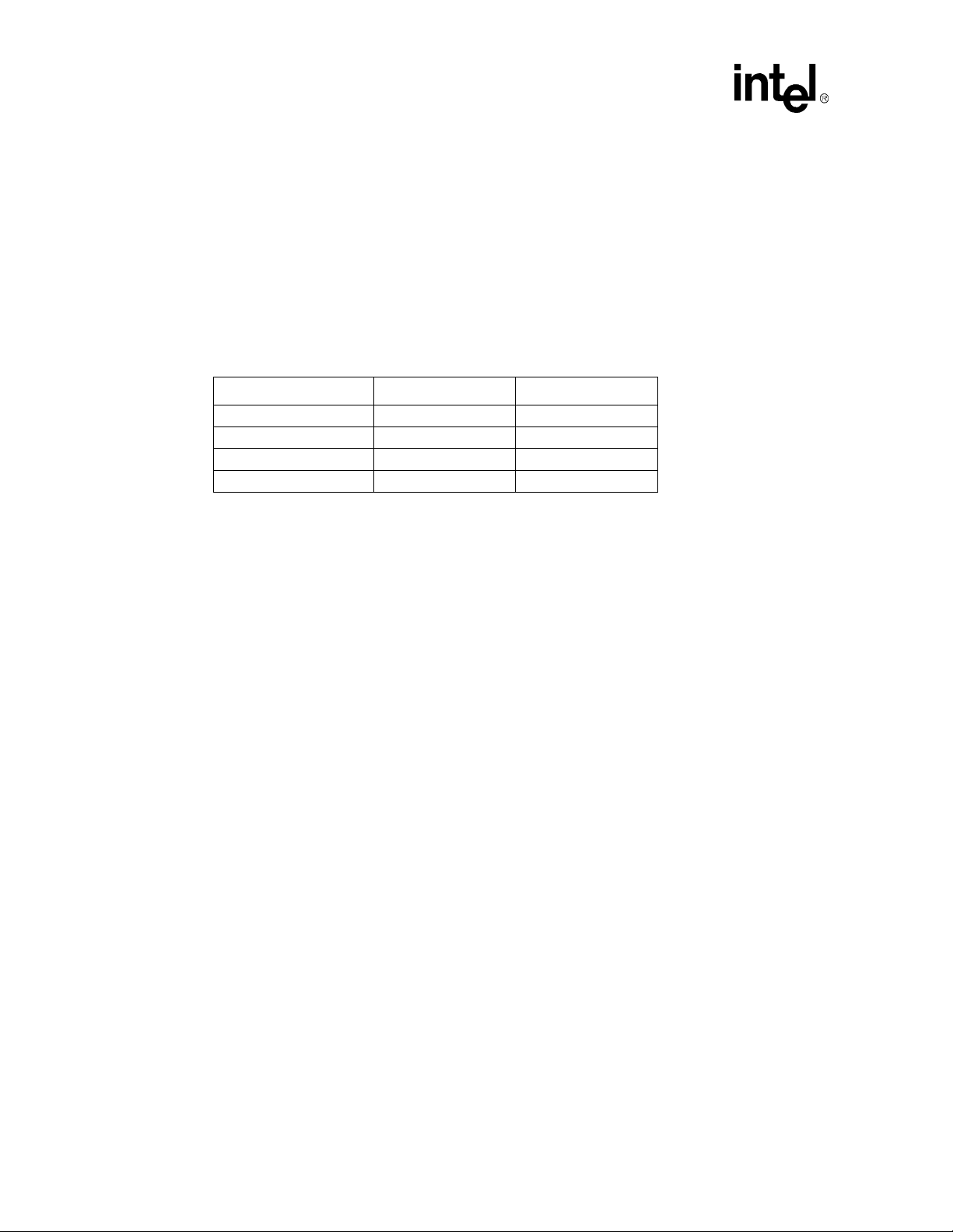

4.4 PCI Device Mapping

On the evaluation platform the PCI devices are mapped to PCI device numbers by connecting an

address line to the IDSEL signal of each PCI device. Table 4-1 s hows the mapping of PCI devices.

Table 4-1. PCI Device Mapping

Device Address Line PCI Device Number

PIIX4E AD18 7

PCI Slot 0 (J7) AD28 17

PCI Slot 1 (J8) AD29 18

PCI Slot 2 (J9) AD30 19

4-2

Celeron™ Processor Development Kit Manual

Page 29

4.5 Connector Pinouts

4.5.1 ATX Power Connector

Table 4-2 shows the signals assigned to the ATX style power connector.

Table 4-2. Primary Power Connector (J11)

Pin Name Function

1 3.3 V 3.3 V

2 3.3 V 3.3 V

3 GND Ground

4 +5V +5 V VCC

5 GND Ground

6 +5V +5 V VCC

7 GND Ground

8 PWRGD Power Good

9 5VSB Standby 5 V

10 +12 V +12 V

11 3.3 V 3.3 V

12 –12 V –12 V

13 GND Ground

14 PS_ON# Soft-off control

15 GND Ground

16 GND Ground

17 GND Ground

18 –5 V –5 Volts

19 +5 V +5 V VCC

20 +5 V +5 V VCC

Hardware Reference

Celeron™ Processor Development Kit Manual

4-3

Page 30

Hardware Reference

4.5.2 ITP Debugger Connector

Table 4-3. ITP Connector Pin Assignment (J2 on the Processor Assembly)

Pin Signal Pin Signal

1 RESET# 16 PREQ0#

2 GND 17 GND

3 DBRESET# 18 PRDY0#

4 GND 19 GND

5 TCK 20 PREQ1#

6 GND 21 GND

7 TMS 22 PRDY1#

8 TDI 23 GND

9 POWERON 24 PREQ2#

10 TDO 25 GND

11 DBINST# 26 PRDY2#

12 TRST# 27 GND

13 GND 28 PREQ3#

14 BSEN# 29 BCLK

15 GND 30 PRDY3#

4.5.3 Stacked USB

P0 is the bottom connector. P1 is on top.

Table 4-4. USB Connector Pinout (J2)

Pin P0 Signals P1 Signals

1 VCC0 VCC1

2 D0- D13 D0+ D1+

4 GND0 GND1

4-4

Celeron™ Processor Development Kit Manual

Page 31

4.5.4 Mouse and Keyboard Connectors

The keyboard port is on top. The mouse port is on the bottom.

Table 4-5. Keyboard and Mouse Connector Pinouts (J1 on the Baseboard)

Pin Signal Name

1Data

2 No Connect

3 Ground

4 +5 V (fused)

5Clock

6 No Connect

4.5.5 Parallel Port

Table 4-6. DB25 Parallel Port Connector Pinout (J3)

Hardware Reference

Pin

1 Strobe# 14 Auto Feed#

2 Data Bit 0 15 Fault#

3 Data Bit 1 16 INIT#

4 Data Bit 2 17 SLCT IN#

5 Data Bit 3 18 Ground

6 Data Bit 4 19 Ground

7 Data Bit 5 20 Ground

8 Data Bit 6 21 Ground

9 Data Bit 7 22 Ground

10 ACK# 23 Ground

11 Busy 24 Ground

12 Paper end 25 Ground

13 SLCT

Signal

Name

Pin

Signal

Name

Celeron™ Processor Development Kit Manual

4-5

Page 32

Hardware Reference

4.5.6 Serial Ports

COM1 is the top connector. COM2 is the bottom connector.

Table 4-7. Serial Port Connector Pinout (J4)

Pin Signal Name

1 DCD

2 Serial In (SIN)

3 Serial Out (SOUT)

4DTR

5GND

6DSR

7RTS

8CTS

9RI

4.5.7 IDE Connector

Table 4-8. PCI IDE1 (JP3) and IDE2 (JP4) Connector

Pin Signal Name Pin Signal Name

1 Reset IDE 2 Ground

3 Host Data 7 4 Host Data 8

5 Host Data 6 6 Host Data 9

7 Host Data 5 8 Host Data 10

9 Host Data 4 10 Host Data 11

11 Host Data 3 12 Host Data 12

13 Host Data 2 14 Host Data 13

15 Host Data 1 16 Host Data 14

17 Host Data 0 18 Host Data 15

19 Ground 20 Key

21 DRQ3 22 Ground

23 I/O Write# 24 Ground

25 I/O Read# 26 Ground

27 IOCHRDY 28 BALE

29 DACK 3# 30 Ground

31 IRQ14 32 IOCS16#

33 Addr 1 34 Ground

35 Addr 0 36 Addr 2

37 Chip Select 0# 38 Chip Select 1#

39 Activity 40 Ground

4-6

Celeron™ Processor Development Kit Manual

Page 33

4.5.8 Floppy Drive Connector

Table 4-9. Diskette Drive Header Connector (JP1)

Pin Signal Name Pin Signal Name

1 Ground 2 FDHDIN

3 Ground 4 Reserved

5 Key 6 FDEDIN

7 Ground 8 Index

9 Ground 10 Motor Enable A#

11 Ground 12 Drive Select B#

13 Ground 14 Drive Select A#

15 Ground 16 Motor Enable B#

17 Ground 18 DIR#

19 Ground 20 STEP#

21 Ground 22 Write Data#

23 Ground 24 Write Gate#

25 Ground 26 Track 00#

27 Ground 28 Write Protect#

29 Ground 30 Read Data#

31 Ground 32 Side 1 Select#

33 Ground 34 Diskette Change#

Hardware Reference

Celeron™ Processor Development Kit Manual

4-7

Page 34

Hardware Reference

4.5.9 PCI Slot Connector

Table 4-10. PCI Slots (J7, J8, J9)

Pin Signal Name Pin Signal Name Pin Signal Name Pin Signal Name

A1 VC C B1 - 12V A32 AD16 B32 AD17

A2 + 12V B2 GND A33 3.3V B33 CBE2#

A3 VCC B3 GND A34 FRAME# B34 GND

A4 VC C B4 No Connect A35 GND B35 IRDY#

A5 VCC B5 VCC A36 TRDY# B36 3.3 V

A6 PIRQ1# B6 VCC A37 GND B37 DEVSEL#

A7 PI RQ 3# B7 PIRQ2# A38 STOP# B38 GND

A8 VCC B8 PIRQ0 A39 3.3 V B39 LOCK#

A9 No Connect B9 PRSNT1B# A40 SDONE B40 PERR#

A10 VCC B10 No Connect A41 SBO# B41 3.3 V

A11 No Connect B11 PRSNT2B# A42 GND B42 SERR#

A12 GND B12 GND A43 PAR B43 3.3V

A13 GND B13 GND A44 AD15 B44 CBE1#

A14 No Connect B14 No Connect A45 3.3V B45 AD14

A15 RST# B15 GND A46 AD13 B46 GND

A16 VCC B16 PCLK3 A47 AD11 B47 AD12

A17 GNT1# B17 GND A48 GND B48 AD10

A18 GND B18 REQ# A49 AD9 B49 GND

A19 Reserved B19 VCC A50 KEY B50 KEY

A20 AD30 B20 AD31 A51 KEY B51 KEY

A21 3.3V B21 AD29 A52 CBEO# B52 AD8

A22 AD28 B22 GND A53 3.3 V B53 AD7

A23 AD26 B23 AD27 A54 AD6 B54 3.3 V

A24 GND B24 AD25 A55 AD4 B55 AD5

A25 AD24 B25 3.3 V A56 GND B56 AD3

A26 IDSEL B26 CBE3# A57 AD2 B57 GND

A27 3.3V B27 AD23 A58 AD0 B58 AD1

A28 AD22 B28 GND A59 VCC B59 VCC

A29 AD20 B29 AD21 A60 REQ64# B60 ACK64#

A30 GND B30 AD19 A61 VCC B61 VCC

A31 AD18 B31 3.3 V A62 VCC B62 VCC

4-8

Celeron™ Processor Development Kit Manual

Page 35

4.5.10 ISA Slot Connector

Table 4-11. ISA Slots (J5, J6)

Pin Signal Name Pin Signal Name Pin Signal Name Pin Signal Name

A1 IOCHK# B1 GND A26 SA5 B26 DACK2#

A2 SD7 B2 RSTSLOT A27 SA4 B27 TC

A3 SD6 B3 VCC A28 SA3 B28 BALE

A4 SD5 B4 IRQB9 A29 SA2 B29 VCC

A5 SD4 B5

A6 SD3 B6 DREQ2 A31 SA0 B31 GND

A7 SD2 B7

A8 SD1 B8 ZEROWS# C2 LA23 D2 IOCS16#

A9 SD0 B9 +12V C3 LA22 D3 IRQB10

A10 IOCHRDY B10 GND C4 LA21 D4 IRQB11

A11 AEN B11 SMEMW# C5 LA20 D5 IRQ B11

A12 SA19 B12 SMEMR# C6 LA19 D6 IRQ15

A13 SA18 B13 IOW# C7 LA18 D7 IRQ14

A14 SA17 B14 IOR# C8 LA17 D8 DACK0

A15 SA16 B15 DACK3# C9 MEMR# D9 DREQ0

A16 SA15 B16 DREQ3 C10 MEMW# D10 DACK5

A17 SA14 B17 DACK1# C11 SD8 D11 DREQ5

A18 SA13 B18 DREQ1 C12 SD9 D12 DACK6#

A19 SA12 B19 REFRESH# C13 SD10 D13 DREQ6

A20 SA11 B20 SYSCLK C14 SD11 D14 DACK7#

A21 SA10 B21 IRQA7 C15 SD12 D15 DREQ7#

A22 SA9 B22 IRQA6 C16 SD13 D16 VCC

A23 SA8 B23 IRQA5 C17 SD14 D17 MASTER#

A24 SA7 B24 IRQA4 C18 SD15 D18 GND

A25 SA6 B25 IRQA3

Hardware Reference

–5V A30 SA1 B30 OSC

–12V C1 SBHE# D1 MEMCS16#

Celeron™ Processor Development Kit Manual

4-9

Page 36

Hardware Reference

4.6 AGP Connector

Table 4-12. AGP Slot (J13)

Pin#BAPin#BA

1 OVRCNT# 12V 34 Vddq3.3 Vddq3.3

2 5.0V TYPEDET# 35 AD21 AD22

3 5.0V Reserved 36 AD19 AD20

4 USB+ USB- 37 GND GND

5 GND GND 38 AD17 AD18

6 INTB# INTA# 39 C/BE2# AD16

7 CLK RST# 40 Vddq3.3 Vddq3.3

8 REQ# GNT# 41 IRDY# FRAME#

9 VCC3.3 VCC3.3 42 3.3Vaux Reserved

10 ST0 ST1 43 GND GND

11 ST2 Reserved 44 Reserved Reserved

12 RBF# PIPE# 45 VCC3.3 VCC3.3

13 GND GND 46 DEVSEL# TRDY#

14 Reserved Reserved 47 V ddq3.3 STOP#

15 SBA0 SBA1 48 PERR# PME#

16 VCC3.3 VCC3.3 49 GND GND

17 SBA2 SBA3 50 SERR# PAR

18 SB_STB Reserved 51 C/BE1# AD15

19 GND GND 52 Vddq3.3 Vddq3.3

20 SBA4 SBA5 53 AD14 AD13

21 SBA6 SBA7 54 AD12 AD11

22 KEY KEY 55 GND GND

23 KEY KEY 56 AD10 AD9

24 KEY KEY 57 AD8 C/BE0#

25 KEY KEY 58 Vddq3.3 Vddq3.3

26 AD31 AD30 59 AD_STB0 Reserved

27 AD29 AD28 60 AD7 AD6

28 VCC3.3 VCC3.3 61 GND GND

29 AD27 AD26 62 AD5 AD4

30 AD25 AD24 63 AD3 AD2

31 GND GND 64 Vddq3.3 Vddq3.3

32 AD_STB1 Reserved 65 AD1 AD0

33 AD23 C/BE3# 66 Reserved Reserved

NOTES:

1. Reserved pins are only for future use by the AGP interface specification.

2. IDSEL# is not a pin on the AGP connector. AGP graphics components should connect the AD16 signal to

the 3. 3 volt IDSEL# function internal to the component.

3. All 3.3 volt cards leave the TYPEDET signal open. All 1.5 volt cards tie this signal hard to ground.

4-10

Celeron™ Processor Development Kit Manual

Page 37

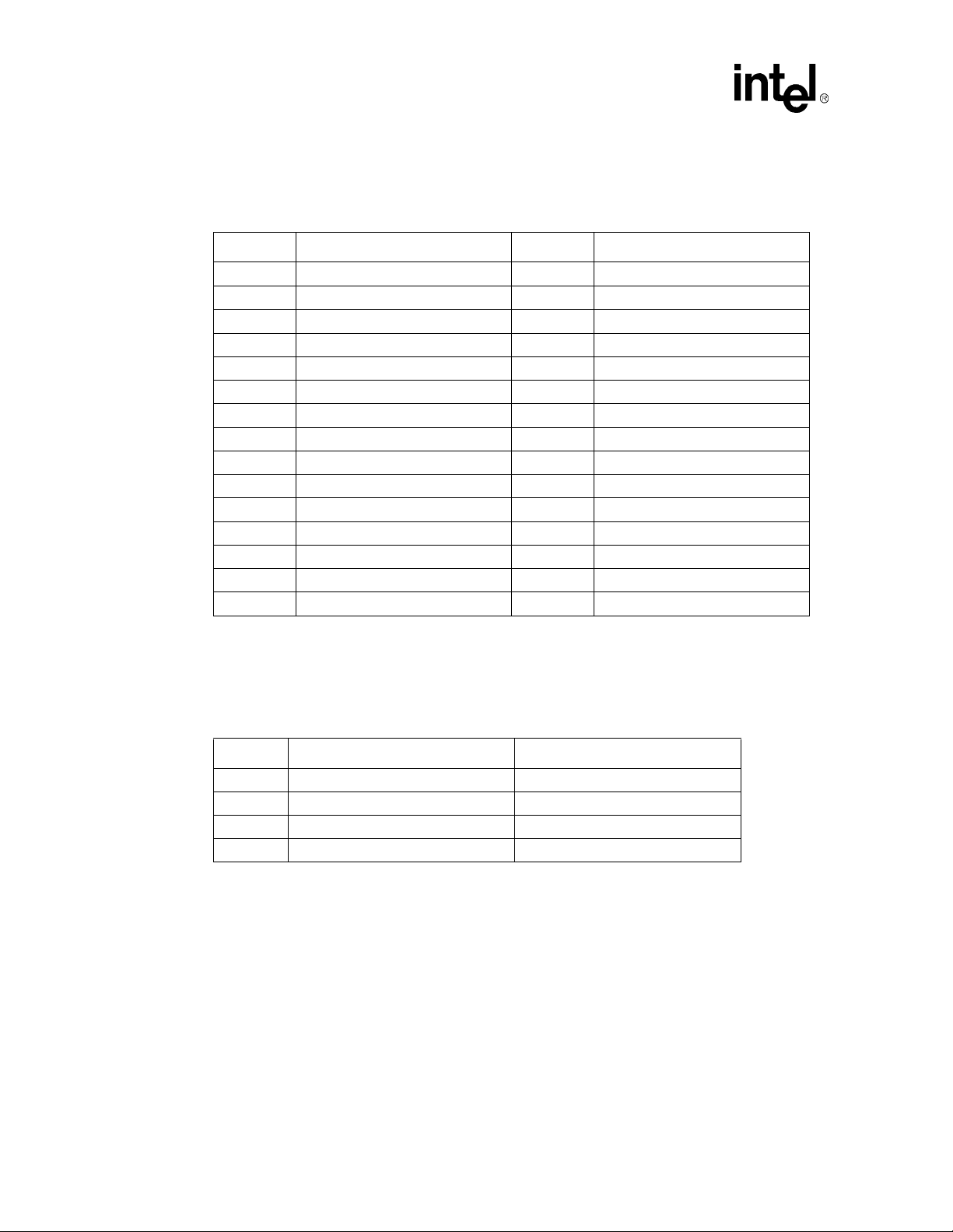

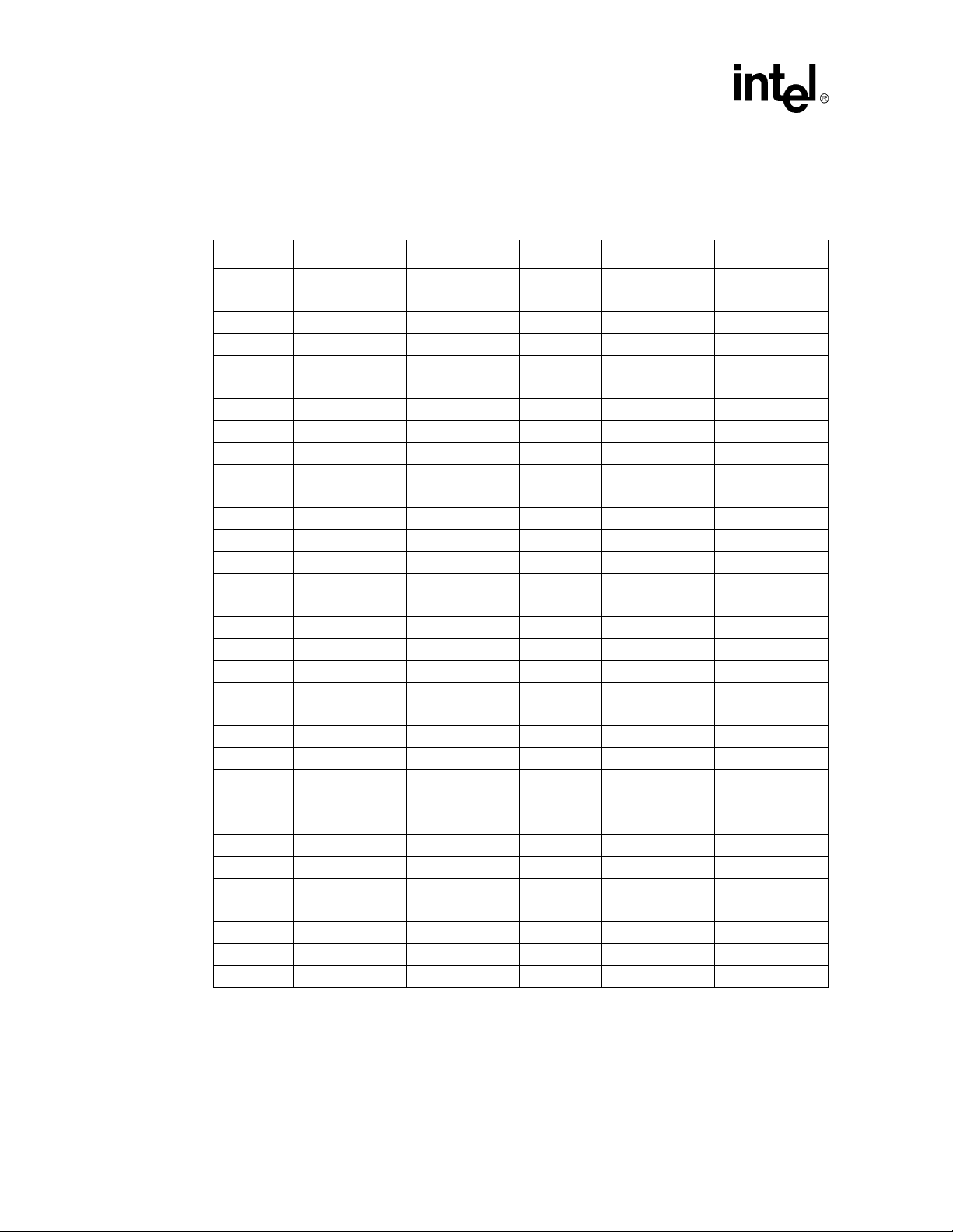

4.7 Jumpers

T a bl e 4-13 shows defau l t Ju mper set t i ngs.

Table 4-13. Default Jumper Settings

Jumper Function Settings

J14 Enable Spread Spectrum Clocking

J15 Clock Frequency Selection

J20 On/Off

J21 Flash BIOS VPP Select

J22 Flash BIOS boot block control

J23 SMI# Source

J24 CMOS RAM Clear

Hardware Reference

In – Enable Spread Spectrum

Out – Disable Spread Spectrum (Default)

In – 66 MHz Processor Clock (Default)

Out – Reserved

1–2 Reserved

2–3 On (Default)

No Jumper Installed – Off

1–2 12 V

2–3 5 V (Default)

1–2 12 V

2–3 5 V (Default)

1–2 SMI# controlled by IOAPIC

2–3 SMI# controlled by PIIX4E (Default)

1–2 Normal Operation (Default)

2–3 Clear CMOS RAM

4.7.1 Enable Spread Spectrum Clocking (J14)

This jumper is used to enable or disable spread spectrum clocking on the clock synthesizer. When

this jumper is in, a 0.5% down spread will be introduced into the PCI and processor clocks. The

default setting is no jumper installed, which di sables spread spectrum clocking.

4.7.2 Clock Frequency Selection (J15)

This jumper controls the frequency of the processor clock. When the jumper is in, 66 MHz

operation is supported. This is the only setting supported by this evaluation k it.

Caution: Leave this jumper installed. When the jumper is out, 100 MHz processor clocks will be generated.

This position is not supported and may cause damage to the processor.

4.7.3 On/Off (J20)

This jumper is used to control the state of the ATX power supply. When this jumper is removed, the

power supply will be turned off. Placing the jumper in the 2-3 position will turn the power supply

on.

The 1-2 position is reserved and should not be used.

Celeron™ Processor Development Kit Manual

4-11

Page 38

Hardware Reference

4.7.4 Flash BIOS VPP Select (J21)

This jumper controls the voltage presented to the flash BIOS VPP pin. The 2-3 position supplies

5 V and is the default for normal o perati on. T his pos iti on in hibit s pr ogramming or erasing the f lash

BIOS.

The 1-2 position supplies 12 V and should only be used if directed to do so by a utility that is used

to reprogram the BIOS.

4.7.5 Flash BIOS Boot Block Control (J22)

This jumper controls the Boot Block protection of the flash BIOS. When this jumper is in the 2-3

position, the boot block is locked and cannot be programmed. This is the default position of this

jumper.

The 1-2 position unlocks the boot block so that it can be erased and reprogrammed. This position

should only be used under the direction of a utility that is designed to reprogram the boot block of

the flash device.

4.7.6 SMI# Source Control (J23)

This jumper selects the source of the SMI# interrupt to the processor. Only the 2-3 position which

selects the PIIX4E is supported. The 1-2 position is res erved for future use.

4.7.7 CMOS RAM Clear (J24)

This jumper controls power to the battery backed-up CMOS RAM. This RAM is used to sto r e

information about the system configuration that is required by the BIOS. The 1-2 position is for

normal operation. The 2-3 position allows for the RAM to be cleared.

To clear the RAM perform the following steps:

1. Remove power from the evaluation platform by removing jumper J20

2. Move J24 to the 2-3.

3. Disconnect the power supply (J11).

4. Install J24 in the 1- 2 position.

5. Reconnect the power supply (J11).

6. Reboot the system and enter the BIOS setup screen to configure the system.

4.7.8 Push Button Switches

There are two push button switches on the evaluation board labeled S1 and S2.

• S1 is non-functional and reserved for future use.

• S2 is the reset button. Press S2 to force a hardware reset of the system.

4-12

Celeron™ Processor Development Kit Manual

Page 39

4.8 In-Circuit BIOS Update

The BIOS can be upgraded in-circuit. BIOS updates may periodically be posted to Intel’s

Developers’ site at http://www.intel.com/design/.

To r eprogram the BIOS:

1. Set Jumper J21 and Jumper J22 to the 1-2 position on the evaluation platform.

2. Download the new BIOS upgrade file from Intel’s Developers’ web site.

3. Extract the BIOS upgrade zip file onto a bootable floppy.

4. Insert the floppy disk into the floppy drive attached to the evaluation board.

5. Reboot the evaluation board so that it boots from the floppy.

6. Follow the on-screen instructions.

7. When the BIOS update program is finished, power down the board and reset the jumpers at

J21 and J22 to the 2-3 position.

Hardware Reference

Celeron™ Processor Development Kit Manual

4-13

Page 40

Page 41

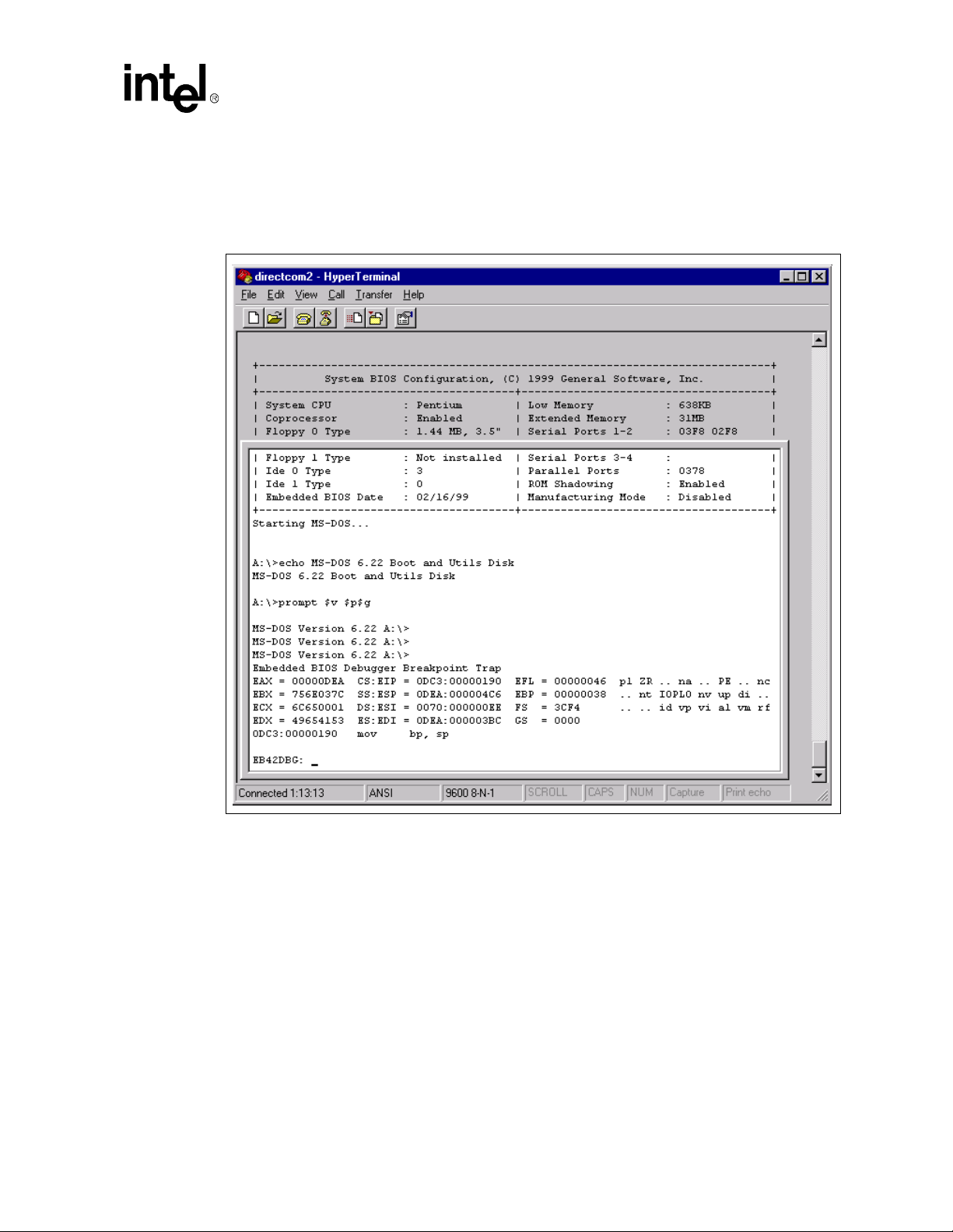

BIOS Quick Reference

5

The Celeron processor evaluation board is licensed with a single copy of Embedded BIOS and

Embedded DOS software from General Software, Inc.

demonstration purposes only and must be licensed directly from General Software, Inc. for

integration with new designs. General Software may be reached at (800) 850-5755, on the web at

http://www.gensw.com, or via email at sales@gensw.com.

BIOS updates may periodically be posted to the Intel Developers’ web site at

http://developer.intel.com/.

5.1 BIOS and Pre-Boot Features

The system’s pre-boot environment is managed with an adaptation of Embedded BIOS from

General Software. The pre-boot environment includes POST, Setup Screen System, Manufacturing

Mode, Console Redirection, Windows CE Loader (CE Ready), and Integrated BIOS Debugger. A

REFLASH tool is also available to update the BIOS image with new builds of Embedded BIOS

that may be obtained from General Software.

Before using the system, please read the following to properly configure CMOS settings, and learn

how to use the embedded features of the pre-boot firmware, Embedded BIOS.

The last two sections of this chapter provide the BIOS POST Codes and Beep codes.

5.2 Power-On Self-Test (POST)

1

This software is provided for

When the system is powered on, Embedded BIOS tests and initializes the hardware and programs

the chipset and other peri phera l comp onents. During this time, P OST p rogress codes are wri tten by

the system BIOS to I/O port 80H, allowing the user to monitor the progress with a special monitor.

“Embedded BIOS POST Codes” on page 5-12 lists the POST codes and their meanings.

During early POST, no video is available to display error messages should a critical error be

encountered; therefore, POST uses beeps on the speaker to indicate the failure of a critical system

component during this time. Consult “Embedded BIOS Beep Codes” on page 5-15 for a list of

Beep codes used by the system’s BIOS.

POST displays its progress on the system video device, which may be the video screen if a VGA

card is used, or on a terminal emulation program’s screen if output is redirected over a serial port.

1. General Software™, the GS Logo, Embedded BIOS™, BIOStart™, CE-Ready™, and Embedded DOS™ are trademarks or registered

trademarks of General Software, Inc.

Celeron™ Processor Development Kit Manual

5-1

Page 42

BIOS Quick Reference

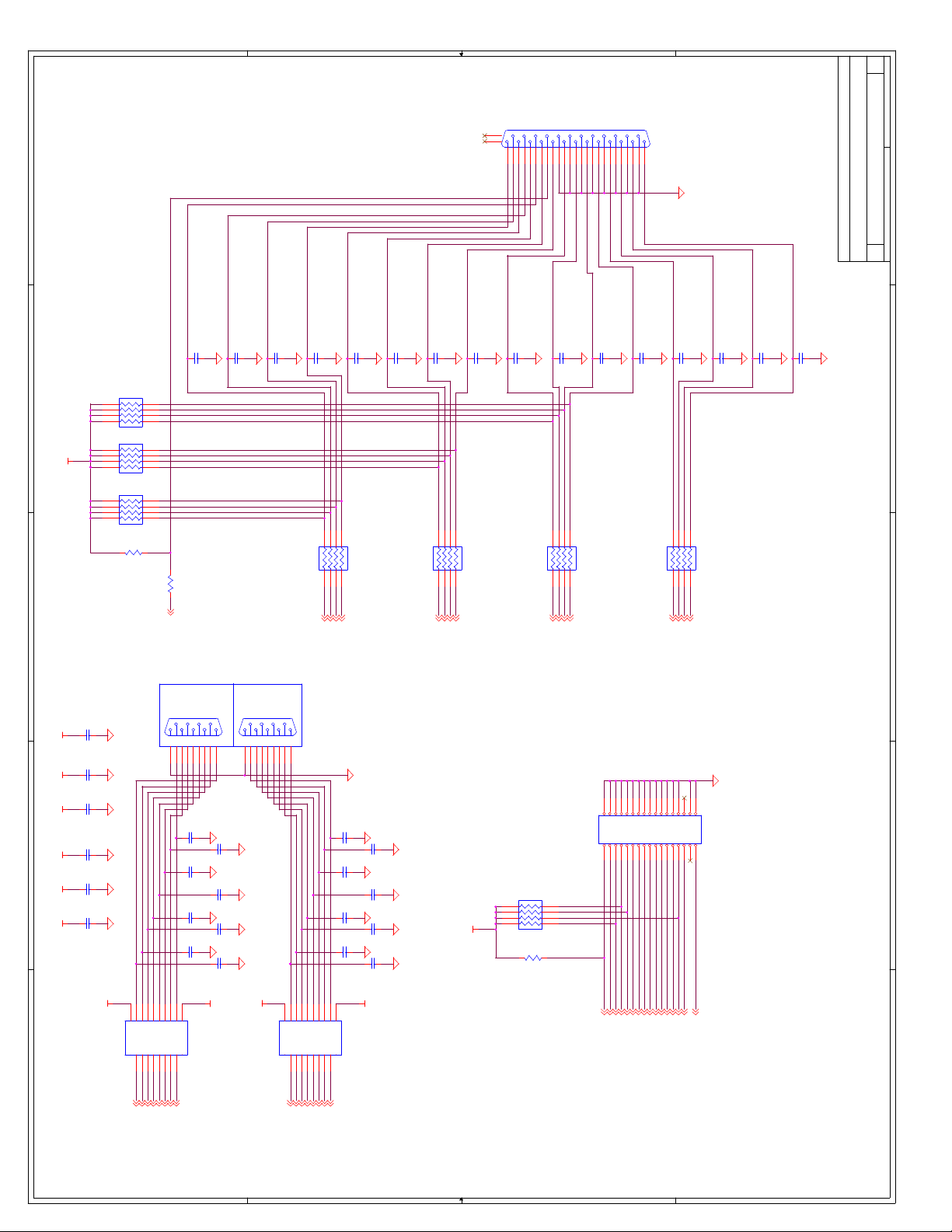

Figure 5-1. BIOS POST Pre-Boot Environment

When the system is powered on for the first time, you’ll need to configure the system through the

Setup Screen System (described later) before peripherals, such as disk dr ives, are recognized by the

BIOS. The information is written to battery-backed CMOS RAM on the board’s Real Time Clock.

Should the board’s battery fail, this information will be lost and the board will need to be

reconfigured.

OEMs can modify the look-and-feel of POST with the Embedded BIOS adaptation kit. While the

demonstration BIOS looks and feels like a desktop PC, it is possible to eliminate messages, sounds,

delays, to make the POST effectively invisible.

5-2

Celeron™ Processor Development Kit Manual

Page 43

5.3 Setup Screen System

The system is configured from within the Setup Screen System, which is a series of menus that can

be invoked from POST by pressing the <DEL> key if the main keyboard is being used, or by

pressing ^C if the console is being redirected to a terminal program.

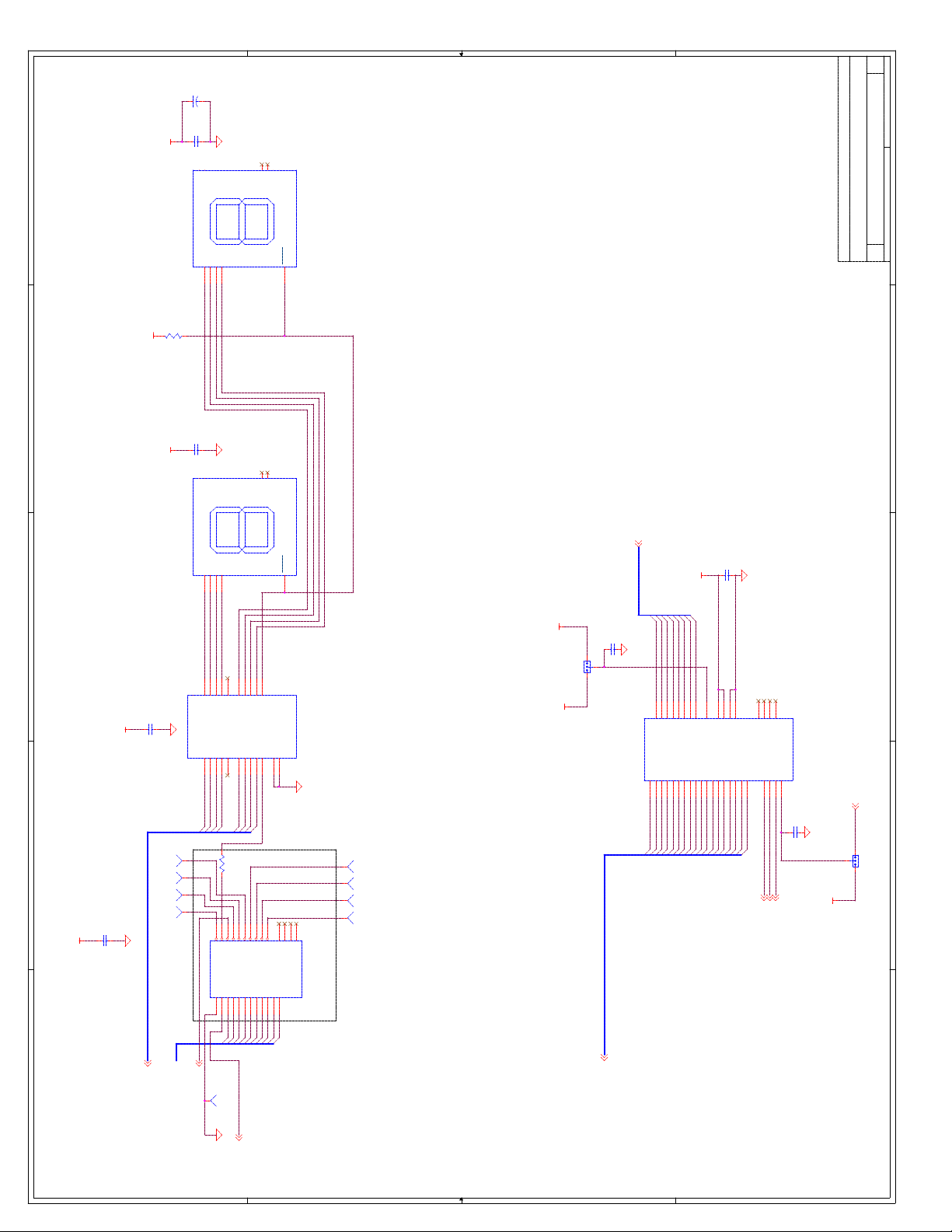

Figure 5-2. Embedded BIOS Setup Screen Menu

BIOS Quick Reference

Once in the Setup Screen System (Figure 5-2), the user can navigate with the UP and DOWN

arrow keys from the main conso le, or us e the ^E and ^X keys from the remote te rminal pro gram to

accomplish the same thing. TAB and ENTER are used to advance to the next field, and ‘+’ and ‘-’

keys cycle through values, such as those in the Basic Setup Screen, or the Diagnostics Setup

Screen.

5.3.1 Basic CMOS Configuration Screen

The system’s drive types, boot activities, and POST optimizations are configured from the Basic

Setup Screen (Figure 5-3). In order to use disk drives with your system, you must select

appropriate assignments of drive types in the left-hand column. Then, if you are using true floppy

and IDE drives (not memory disks that emulate these drives), you need to configu re the drive types

themselves in the Floppy Drive Types and IDE Drive Geometry sections. Finally, you’ll need to

configure the boot sequence in the middle of the screen. Once these selections have been made,

your system is ready to use.

Celeron™ Processor Development Kit Manual

5-3

Page 44

BIOS Quick Reference

Figure 5-3. Embedded BIOS Basic Setup Screen

5.3.2 Configuring Drive Assignments

Embedded BIOS allows the user to map a different file system to each drive letter. The BIOS

allows file systems for each floppy (Floppy0 and Floppy1), each IDE drive (Ide0, Ide1, Ide2, and

Ide3), and memory disks when configured (Flash0, ROM0, R AM0, etc. ) Figur e 5-3 shows how the

first floppy drive (Floppy0) is assigned to drive A: in the sy stem , and then how the first IDE drive

(Ide0) is assigned to drive C: in the system.

To switch two floppy disks around or two hard disks around, just map Floppy0 to B: and Floppy1

to A:, and for hard disks map Ide0 to D: and Ide1 to C:.

Caution: Take care to not skip drive A: when making floppy disk assignments, as well as drive C: when

making hard disk assignments . The first floppy should be A:, and the fir st hard dri ve s hou ld be C: .

Also, do not assig n th e s ame file system to more t h an one drive letter. Thus, Floppy0 should not be

used for both A: and B:. The BIOS permits this to allow embedded dev ices to alias drives, but

desktop operating systems may not be able to maintain cache coherency with such a mapping in

place.

A special field in this section entitled “Bo ot Method: (Windows CE/Boot Sector)” is used to

configure the CE Ready feature of the BIOS. For normal bo oting (DOS, Windows NT, etc.), select

“Boot Sector” or “Unused”.

5.3.2.1 Configuring Floppy Drive Types

If true floppy drive file systems (and not their emulators, such as ROM, RAM, or flash disks) are

mapped to drive letters, then the floppy drives themselves must be configured in this section.

Floppy0 refers to the first floppy disk drive on the drive ribbon cable (normally drive A:), and

Floppy1 refers to the second drive (drive B:).

5-4

Celeron™ Processor Development Kit Manual

Page 45

5.3.3 Configuring IDE Drive Types

If true IDE disk file systems (and not their emulators, such as ROM, RAM, or flash disks) are

mapped to drive letters, then the IDE drives themselves must be configured in this section. The

following table shows the drive assignments for Ide0-Ide3:

Table 5-1. IDE0-IDE3 Drive Assignments

File System Name Controller Mas ter/Slave

Ide0 Primary (1f0h) Master

Ide1 Primary (1f0h) Slave

Ide2 Secondary (170h) Master

Ide3 Secondary (170h) Slave

To use the primary master IDE drive in your system (the typical case), just configure Ide0 in this

section, and map Ide0 to drive C: in the Configuring Drive Assignmen ts section.

The IDE Drive Types section lets you select the type for each of the four IDE drives: None, User,

Physical, LBA, or CHS.

User This type allows the user to select the maximum cylinders, heads, and sectors

per track associated with the IDE drive. This method is now rarely used since

LBA is now in common use.

BIOS Quick Reference

Physical This type instructs the BIOS to query the drive’s geometry from the controller

on each POST. No translation on the drive’s geometry is performed, so this type

is limited to drives of 512 Mbytes or less. Com monly, this is used with

embedded ATA PC Cards.

LBA This type instructs the BIOS to query the drive’s geometry from the controller

on each POST, but then translate the geometry according to the industrystandard LBA convent ion. This support s up to 16-Gbyt e drives. Use this method

for all new drive s.

CHS This type instructs the BIOS to query the drive’s geometry from the controller

on each POST, but then translate the geometry according to the Phoenix CHS

convention. Using this type on a drive previously formatted with LBA or

Physical geometry might show data as being missing or corrupted.

Celeron™ Processor Development Kit Manual

5-5

Page 46

BIOS Quick Reference

5.4 Configuring Boot Actions

Embedded BIOS supports up to six different user-defined steps in the boot sequence. When the

entire system has been initialized, POST executes these steps in order until an operating system

successfully loads. In addition, other pre-boot features can be run before, after, or between

operating system load attempts. The following actions can be used:

Drive A: - K: Boot operating system from specified drive. If “Loader” is set to “BootRecord”

or “Unused”, then the standard boot record will be invoked, caus ing DOS,

Windows95/98, Windows NT, or other industry-standard operating systems to

load. If “Boot Method” is set to “Windows CE”, then the boot drive’s boot

record will not be used, and instead the BIOS will attempt to load and execute

the Windows CE Kernel file, NK.BIN, from the root directory of each boot

device.

Debugger Launch the Integrated BIOS Debugger. To return to the boot process from the

debugger environment, type “G” at the debugger prompt and press ENTER.

MFGMODE Initiate Manufacturing Mode, allowing the system to be configured remotely

via an RS232 connect to a host computer.