Page 1

Intel® 64 and IA-32 Architectures

Software Developer’s Manual

Volume 2A:

Instruction Set Reference, A-M

NOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual

consists of five volumes: Basic Architecture, Order Number 253665;

Instruction Set Reference A-M, Order Number 253666; Instruction Set

Reference N-Z, Order Number 253667; System Programming Guide,

Part 1, Order Number 253668; System Programming Guide, Part 2,

Order Number 253669. Refer to all five volumes when evaluating your

design needs.

Order Number: 253666-024US

August 2007

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERT Y RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH

PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED

FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Developers must not rely on the absence or characteristics of any features or instructions marked “reserved”

or “undefined.” Improper use of reserved or undefined features or instructions may cause unpre dictab le be havior or failure in developer's software code when running on an Intel processor. Intel reserves these features or instructions for future definition and shall have no responsibility whatsoever for conflicts or

incompatibilities arising from their unauthorized use.

The Intel

acterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel

Threading Technology and an HT Technology enabled chipset, BIOS and oper ating sys tem. Pe rformance will

vary depending on the specific hardware and software you use. For more information, see http://www.in-

tel.com/technology/hyperthread/index.htm; including details on which processors support HT Technology.

®

64 architecture processors ma y conta in de sign defects o r err ors kn own as err a ta. Curr ent c har -

®

processor supporting Hyper-

No computer system can provide absolute security under all conditions. Intel® Trusted Ex ecution Technology requires a computer system with Intel® Virtualization Technology, an Intel TXT-enabled processor,

chipset, BIOS, Authenti cate d Code Mo dule s and an Intel TXT-compatible measured launched environment

(MLE). The MLE could consist of a virtual machine monitor, an OS or an application. In addition, Intel TXT

requires the system to contain a TPM v1.2, as defined by the Trusted Computing Group, and specific software for some uses. For more information, see http://www.intel.com/technology/security

®

Virtualization T echnol ogy requires a computer syste m with an enabled Intel® processor , BIOS, virtual

Intel

machine monitor (VMM) and for some uses, certain platform software enabled for it. Functionality, performance or other benefits will

Technology-enabled BIOS and VMM applications are currently in development.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel

(including 32-bit operation) without an Intel

pending on your hardware and software configurations. Consult with your system vendor for more information.

vary depending on hardware and software configurations. Intel® Virtualization

®

®

64 architecture-enabled BIOS. Performance will vary de-

64 architecture. Processors will not operate

Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability

and a supporting operating system. Chec k with your PC manufacturer on whether your system delivers Execute Disable Bit functionality.

Intel, Pentium, Intel Xeon, Intel NetBurst, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo, Intel Core 2

Extreme, Intel Pentium D, Itanium, Intel SpeedStep, MMX, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and befo re plac ing

your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel

literature, may be obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call 1-800-548-4725

or visit Intel’s website a t http://www.intel.com

Copyright © 1997-2007 Intel Corporation

ii Vol. 2A

Page 3

CONTENTS

PAGE

CHAPTER 1

ABOUT THIS MANUAL

1.1 IA-32 PROCESSORS COVERED IN THIS MANUAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2 OVERVIEW OF VOLUME 2A AND 2B: INSTRUCTION SET REFERENCE . . . . . . . . . . . . . . . . . . 1-2

1.3 NOTATIONAL CONVENTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.3.1 Bit and Byte Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.3.2 Reserved Bits and Software Compatibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.3.3 Instruction Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3.4 Hexadecimal and Binary Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3.5 Segmented Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3.6 Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.3.7 A New Syntax for CPUID, CR, and MSR Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.4 RELATED LITERATURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

CHAPTER 2

INSTRUCTION FORMAT

2.1 INSTRUCTION FORMAT FOR PROTECTED MODE, REAL-ADDRESS MODE, AND

VIRTUAL-8086 MODE 2-1

2.1.1 Instruction Prefixes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1.2 Opcodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.3 ModR/M and SIB Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.1.4 Displacement and Immediate Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.1.5 Addressing-Mode Encoding of ModR/M and SIB Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.2 IA-32E MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.2.1 REX Prefixes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.2.1.1 Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.2.1.2 More on REX Prefix Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.2.1.3 Displacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.2.1.4 Direct Memory-Offset MOVs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.2.1.5 Immediates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.2.1.6 RIP-Relative Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.2.1.7 Default 64-Bit Operand Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.2.2 Additional Encodings for Control and Debug Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

CHAPTER 3

INSTRUCTION SET REFERENCE, A-M

3.1 INTERPRETING THE INSTRUCTION REFERENCE PAGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1.1 Opcode Column in the Instruction Summary Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.1.2 Instruction Column in the Opcode Summary Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.1.3 64-bit Mode Column in the Instruction Summary Table . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.1.1.4 Compatibility/Legacy Mode Column in the Instruction Summary Table. . . . . . . . . . . 3-7

Vol. 2A iii

Page 4

CONTENTS

PAGE

3.1.1.5 Description Column in the Instruction Summary Table. . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.1.1.6 Description Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.1.1.7 Operation Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.1.1.8 Intel® C/C++ Compiler Intrinsics Equivalents Section . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.1.1.9 Flags Affected Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.1.1.10 FPU Flags Affected Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.1.1.11 Protected Mode Exceptions Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.1.1.12 Real-Address Mode Exceptions Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

3.1.1.13 Virtual-8086 Mode Exceptions Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

3.1.1.14 Floating-Point Exceptions Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

3.1.1.15 SIMD Floating-Point Exceptions Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3.1.1.16 Compatibility Mode Exceptions Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3.1.1.17 64-Bit Mode Exceptions Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3.2 INSTRUCTIONS (A-M) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

AAA—ASCII Adjust After Addition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

AAD—ASCII Adjust AX Before Division. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

AAM—ASCII Adjust AX After Multiply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

AAS—ASCII Adjust AL After Subtraction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

ADC—Add with Carry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

ADD—Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

ADDPD—Add Packed Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . . 3-33

ADDPS—Add Packed Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . 3-36

ADDSD—Add Scalar Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . 3-39

ADDSS—Add Scalar Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . 3-42

ADDSUBPD—Packed Double-FP Add/Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-45

ADDSUBPS—Packed Single-FP Add/Subtract. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-49

AND—Logical AND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-53

ANDPD—Bitwise Logical AND of Packed Double-Precision Floating-Point Values . . . 3-56

ANDPS—Bitwise Logical AND of Packed Single-Precision Floating-Point Values . . . . 3-58

ANDNPD—Bitwise Logical AND NOT of Packed Double-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-60

ANDNPS—Bitwise Logical AND NOT of Packed Single-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-62

ARPL—Adjust RPL Field of Segment Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-64

BOUND—Check Array Index Against Bounds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-66

BSF—Bit Scan Forward . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-69

BSR—Bit Scan Reverse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-71

BSWAP—Byte Swap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-73

BT—Bit Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-75

BTC—Bit Test and Complement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-78

BTR—Bit Test and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-81

BTS—Bit Test and Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-84

CALL—Call Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-87

CBW/CWDE/CDQE—Convert Byte to Word/Convert Word to Doubleword/Convert Dou-

bleword to Quadword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-105

CLC—Clear Carry Flag. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-106

CLD—Clear Direction Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-107

iv

Vol. 2A

Page 5

CONTENTS

PAGE

CLFLUSH—Flush Cache Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-108

CLI — Clear Interrupt Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-110

CLTS—Clear Task-Switched Flag in CR0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-113

CMC—Complement Carry Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-115

CMOVcc—Conditional Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-116

CMP—Compare Two Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-123

CMPPD—Compare Packed Double-Precision Floating-Point Values . . . . . . . . . . . . . . . 3-126

CMPPS—Compare Packed Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . 3-131

CMPS/CMPSB/CMPSW/CMPSD/CMPSQ—Compare String Operands . . . . . . . . . . . . . . . 3-136

CMPSD—Compare Scalar Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . 3-142

CMPSS—Compare Scalar Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . 3-146

CMPXCHG—Compare and Exchange. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-150

CMPXCHG8B/CMPXCHG16B—Compare and Exchange Bytes . . . . . . . . . . . . . . . . . . . . 3-153

COMISD—Compare Scalar Ordered Double-Precision Floating-Point Values and Set

EFLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-156

COMISS—Compare Scalar Ordered Single-Precision Floating-Point Values and Set

EFLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-159

CPUID—CPU Identification. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-162

CVTDQ2PD—Convert Packed Doubleword Integers to Packed Double-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-190

CVTDQ2PS—Convert Packed Doubleword Integers to Packed Single-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-192

CVTPD2DQ—Convert Packed Double-Precision Floating-Point Values to Packed

Doubleword Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-195

CVTPD2PI—Convert Packed Double-Precision Floating-Point Values to Packed

Doubleword Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-198

CVTPD2PS—Convert Packed Double-Precision Floating-Point Values to Packed

Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-201

CVTPI2PD—Convert Packed Doubleword Integers to Packed Double-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-204

CVTPI2PS—Convert Packed Doubleword Integers to Packed Single-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-207

CVTPS2DQ—Convert Packed Single-Precision Floating-Point Values to Packed

Doubleword Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-210

CVTPS2PD—Convert Packed Single-Precision Floating-Point Values to Packed

Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-213

CVTPS2PI—Convert Packed Single-Precision Floating-Point Values to Packed

Doubleword Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-216

CVTSD2SI—Convert Scalar Double-Precision Floating-Point Value to Doubleword

Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-219

CVTSD2SS—Convert Scalar Double-Precision Floating-Point Value to Scalar

Single-Precision Floating-Point Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-222

CVTSI2SD—Convert Doubleword Integer to Scalar Double-Precision

Floating-Point Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-225

CVTSI2SS—Convert Doubleword Integer to Scalar Single-Precision

Floating-Point Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-228

CVTSS2SD—Convert Scalar Single-Precision Floating-Point Value to Scalar

Vol. 2A v

Page 6

CONTENTS

PAGE

Double-Precision Floating-Point Value. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-231

CVTSS2SI—Convert Scalar Single-Precision Floating-Point Value to

Doubleword Integer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-234

CVTTPD2PI—Convert with Truncation Packed Double-Precision Floating-Point

Values to Packed Doubleword Integers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-237

CVTTPD2DQ—Convert with Truncation Packed Double-Precision Floating-Point

Values to Packed Doubleword Integers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-240

CVTTPS2DQ—Convert with Truncation Packed Single-Precision Floating-Point

Values to Packed Doubleword Integers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-243

CVTTPS2PI—Convert with Truncation Packed Single-Precision Floating-Point

Values to Packed Doubleword Integers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-246

CVTTSD2SI—Convert with Truncation Scalar Double-Precision Floating-Point

Value to Signed Doubleword Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-249

CVTTSS2SI—Convert with Truncation Scalar Single-Precision Floating-Point

Value to Doubleword Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-252

CWD/CDQ/CQO—Convert Word to Doubleword/Convert Doubleword to Quadword3-255

DAA—Decimal Adjust AL after Addition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-257

DAS—Decimal Adjust AL after Subtraction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-259

DEC—Decrement by 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-261

DIV—Unsigned Divide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-264

DIVPD—Divide Packed Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . .3-268

DIVPS—Divide Packed Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . .3-271

DIVSD—Divide Scalar Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . 3-274

DIVSS—Divide Scalar Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . .3-277

EMMS—Empty MMX Technology State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-280

ENTER—Make Stack Frame for Procedure Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . 3-282

F2XM1—Compute 2x–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-286

FABS—Absolute Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-288

FADD/FADDP/FIADD—Add. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-290

FBLD—Load Binary Coded Decimal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-294

FBSTP—Store BCD Integer and Pop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-296

FCHS—Change Sign . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-299

FCLEX/FNCLEX—Clear Exceptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-301

FCMOVcc—Floating-Point Conditional Move. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-303

FCOMI/FCOMIP/ FUCOMI/FUCOMIP—Compare Floating Point

Values and Set EFLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-309

FCOS—Cosine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-312

FDECSTP—Decrement Stack-Top Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-314

FDIV/FDIVP/FIDIV—Divide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-316

FDIVR/FDIVRP/FIDIVR—Reverse Divide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-320

FFREE—Free Floating-Point Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-324

FICOM/FICOMP—Compare Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-325

FILD—Load Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-328

FINCSTP—Increment Stack-Top Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-330

FINIT/FNINIT—Initialize Floating-Point Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-332

FIST/FISTP—Store Integer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-334

FISTTP—Store Integer with Truncation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-338

vi

Vol. 2A

Page 7

CONTENTS

PAGE

FLD—Load Floating Point Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-341

FLD1/FLDL2T/FLDL2E/FLDPI/FLDLG2/FLDLN2/FLDZ—Load Constant . . . . . . . . . . . 3-344

FLDCW—Load x87 FPU Control Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-346

FLDENV—Load x87 FPU Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-348

FMUL/FMULP/FIMUL—Multiply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-351

FNOP—No Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-355

FPATAN—Partial Arctangent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-356

FPREM—Partial Remainder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-359

FPREM1—Partial Remainder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-362

FPTAN—Partial Tangent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-365

FRNDINT—Round to Integer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-368

FRSTOR—Restore x87 FPU State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-370

FSAVE/FNSAVE—Store x87 FPU State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-373

FSCALE—Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-377

FSIN—Sine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-379

FSINCOS—Sine and Cosine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-381

FSQRT—Square Root . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-384

FST/FSTP—Store Floating Point Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-386

FSTCW/FNSTCW—Store x87 FPU Control Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-389

FSTENV/FNSTENV—Store x87 FPU Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-392

FSTSW/FNSTSW—Store x87 FPU Status Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-395

FSUB/FSUBP/FISUB—Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-398

FSUBR/FSUBRP/FISUBR—Reverse Subtract. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-402

FTST—TEST. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-406

FUCOM/FUCOMP/FUCOMPP—Unordered Compare Floating Point Values . . . . . . . . . 3-408

FXAM—ExamineModR/M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-411

FXCH—Exchange Register Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-413

FXRSTOR—Restore x87 FPU, MMX , XMM, and MXCSR State. . . . . . . . . . . . . . . . . . . . 3-415

FXSAVE—Save x87 FPU, MMX Technology, SSE, and SSE2 State . . . . . . . . . . . . . . . . 3-418

FXTRACT—Extract Exponent and Significand . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-429

FYL2X—Compute y * log2x . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-431

FYL2XP1—Compute y * log2(x +1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-433

HADDPD—Packed Double-FP Horizontal Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-435

HADDPS—Packed Single-FP Horizontal Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-439

HLT—Halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-443

HSUBPD—Packed Double-FP Horizontal Subtract. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-445

HSUBPS—Packed Single-FP Horizontal Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-449

IDIV—Signed Divide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-453

IMUL—Signed Multiply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-457

IN—Input from Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-462

INC—Increment by 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-464

INS/INSB/INSW/INSD—Input from Port to String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-467

INT n/INTO/INT 3—Call to Interrupt Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-471

INVD—Invalidate Internal Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-486

INVLPG—Invalidate TLB Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-488

IRET/IRETD—Interrupt Return . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-490

Jcc—Jump if Condition Is Met . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-501

Vol. 2A vii

Page 8

CONTENTS

PAGE

JMP—Jump . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-508

LAHF—Load Status Flags into AH Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-518

LAR—Load Access Rights Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-520

LDDQU—Load Unaligned Integer 128 Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-524

LDMXCSR—Load MXCSR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-527

LDS/LES/LFS/LGS/LSS—Load Far Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-529

LEA—Load Effective Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-535

LEAVE—High Level Procedure Exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-538

LFENCE—Load Fence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-540

LGDT/LIDT—Load Global/Interrupt Descriptor Table Register . . . . . . . . . . . . . . . . . . . .3-541

LLDT—Load Local Descriptor Table Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-544

LMSW—Load Machine Status Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-547

LOCK—Assert LOCK# Signal Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-549

LODS/LODSB/LODSW/LODSD/LODSQ—Load String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-551

LOOP/LOOPcc—Loop According to ECX Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-555

LSL—Load Segment Limit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-558

LTR—Load Task Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-562

MASKMOVDQU—Store Selected Bytes of Double Quadword . . . . . . . . . . . . . . . . . . . . . 3-565

MASKMOVQ—Store Selected Bytes of Quadword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-568

MAXPD—Return Maximum Packed Double-Precision Floating-Point Values . . . . . . .3-571

MAXPS—Return Maximum Packed Single-Precision Floating-Point Values . . . . . . . . 3-574

MAXSD—Return Maximum Scalar Double-Precision Floating-Point Value . . . . . . . . . 3-577

MAXSS—Return Maximum Scalar Single-Precision Floating-Point Value . . . . . . . . . .3-580

MFENCE—Memory Fence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-583

MINPD—Return Minimum Packed Double-Precision Floating-Point Values. . . . . . . . . 3-584

MINPS—Return Minimum Packed Single-Precision Floating-Point Values. . . . . . . . . . 3-587

MINSD—Return Minimum Scalar Double-Precision Floating-Point Value . . . . . . . . . . .3-590

MINSS—Return Minimum Scalar Single-Precision Floating-Point Value . . . . . . . . . . . .3-593

MONITOR—Set Up Monitor Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-596

MOV—Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-599

MOV—Move to/from Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-605

MOV—Move to/from Debug Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-608

MOVAPD—Move Aligned Packed Double-Precision Floating-Point Values . . . . . . . . . 3-610

MOVAPS—Move Aligned Packed Single-Precision Floating-Point Values . . . . . . . . . . 3-613

MOVD/MOVQ—Move Doubleword/Move Quadword . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-616

MOVDDUP—Move One Double-FP and Duplicate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-620

MOVDQA—Move Aligned Double Quadword. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-623

MOVDQU—Move Unaligned Double Quadword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-625

MOVDQ2Q—Move Quadword from XMM to MMX Technology Register . . . . . . . . . . . 3-628

MOVHLPS— Move Packed Single-Precision Floating-Point Values High to Low . . . .3-630

MOVHPD—Move High Packed Double-Precision Floating-Point Value . . . . . . . . . . . . .3-632

MOVHPS—Move High Packed Single-Precision Floating-Point Values . . . . . . . . . . . . .3-635

MOVLHPS—Move Packed Single-Precision Floating-Point Values Low to High. . . . . 3-638

MOVLPD—Move Low Packed Double-Precision Floating-Point Value. . . . . . . . . . . . . . 3-640

MOVLPS—Move Low Packed Single-Precision Floating-Point Values. . . . . . . . . . . . . . 3-642

MOVMSKPD—Extract Packed Double-Precision Floating-Point Sign Mask . . . . . . . . . 3-645

MOVMSKPS—Extract Packed Single-Precision Floating-Point Sign Mask . . . . . . . . . . 3-647

viii

Vol. 2A

Page 9

CONTENTS

PAGE

MOVNTDQ—Store Double Quadword Using Non-Temporal Hint . . . . . . . . . . . . . . . . . 3-649

MOVNTI—Store Doubleword Using Non-Temporal Hint . . . . . . . . . . . . . . . . . . . . . . . . . 3-652

MOVNTPD—Store Packed Double-Precision Floating-Point Values Using

Non-Temporal Hint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-654

MOVNTPS—Store Packed Single-Precision Floating-Point Values Using

Non-Temporal Hint. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-657

MOVNTQ—Store of Quadword Using Non-Temporal Hint. . . . . . . . . . . . . . . . . . . . . . . . 3-660

MOVQ—Move Quadword . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-663

MOVQ2DQ—Move Quadword from MMX Technology to XMM Register. . . . . . . . . . . 3-666

MOVS/MOVSB/MOVSW/MOVSD/MOVSQ—Move Data from String to String. . . . . . . 3-668

MOVSD—Move Scalar Double-Precision Floating-Point Value . . . . . . . . . . . . . . . . . . . . 3-673

MOVSHDUP—Move Packed Single-FP High and Duplicate . . . . . . . . . . . . . . . . . . . . . . . 3-676

MOVSLDUP—Move Packed Single-FP Low and Duplicate . . . . . . . . . . . . . . . . . . . . . . . . 3-679

MOVSS—Move Scalar Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . 3-682

MOVSX/MOVSXD—Move with Sign-Extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-685

MOVUPD—Move Unaligned Packed Double-Precision Floating-Point Values . . . . . . 3-687

MOVUPS—Move Unaligned Packed Single-Precision Floating-Point Values . . . . . . . 3-690

MOVZX—Move with Zero-Extend. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-693

MUL—Unsigned Multiply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-695

MULPD—Multiply Packed Double-Precision Floating-Point Values. . . . . . . . . . . . . . . . 3-698

MULPS—Multiply Packed Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . 3-701

MULSD—Multiply Scalar Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . . 3-704

MULSS—Multiply Scalar Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . 3-707

MWAIT—Monitor Wait. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-710

CHAPTER 4

INSTRUCTION SET REFERENCE, N-Z

4.1 INSTRUCTIONS (N-Z). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

NEG—Two's Complement Negation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

NOP—No Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

NOT—One's Complement Negation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

OR—Logical Inclusive OR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values . . . . . . . . . . . . . .4-12

ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values . . . . . . . . . . . . . . .4-14

OUT—Output to Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

OUTS/OUTSB/OUTSW/OUTSD—Output String to Port . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-18

PABSB/PABSW/PABSD — Packed Absolute Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-23

PACKSSWB/PACKSSDW—Pack with Signed Saturation . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-27

PACKUSWB—Pack with Unsigned Saturation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-32

PADDB/PADDW/PADDD—Add Packed Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36

PADDQ—Add Packed Quadword Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-40

PADDSB/PADDSW—Add Packed Signed Integers with Signed Saturation. . . . . . . . . . .4-43

PADDUSB/PADDUSW—Add Packed Unsigned Integers with Unsigned Saturation . . .4-47

PALIGNR — Packed Align Right . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-51

PAND—Logical AND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-54

PANDN—Logical AND NOT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-57

PAUSE—Spin Loop Hint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-60

Vol. 2A ix

Page 10

CONTENTS

PAGE

PAVGB/PAVGW—Average Packed Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-61

PCMPEQB/PCMPEQW/PCMPEQD— Compare Packed Data for Equal. . . . . . . . . . . . . . . . 4-64

PCMPGTB/PCMPGTW/PCMPGTD—Compare Packed Signed Integers for Greater Than .4-

68

PEXTRW—Extract Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-73

PHADDW/PHADDD — Packed Horizontal Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-76

PHADDSW — Packed Horizontal Add and Saturate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-79

PHSUBW/PHSUBD — Packed Horizontal Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-82

PHSUBSW — Packed Horizontal Subtract and Saturate . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-85

PINSRW—Insert Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-88

PMADDUBSW — Multiply and Add Packed Signed and Unsigned Bytes. . . . . . . . . . . . . 4-91

PMADDWD—Multiply and Add Packed Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-94

PMAXSW—Maximum of Packed Signed Word Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-98

PMAXUB—Maximum of Packed Unsigned Byte Integers . . . . . . . . . . . . . . . . . . . . . . . . .4-101

PMINSW—Minimum of Packed Signed Word Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-104

PMINUB—Minimum of Packed Unsigned Byte Integers . . . . . . . . . . . . . . . . . . . . . . . . . . 4-107

PMOVMSKB—Move Byte Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-110

PMULHRSW — Packed Multiply High with Round and Scale . . . . . . . . . . . . . . . . . . . . . . 4-113

PMULHUW—Multiply Packed Unsigned Integers and Store High Result . . . . . . . . . . .4-116

PMULHW—Multiply Packed Signed Integers and Store High Result . . . . . . . . . . . . . . .4-120

PMULLW—Multiply Packed Signed Integers and Store Low Result. . . . . . . . . . . . . . . . 4-123

PMULUDQ—Multiply Packed Unsigned Doubleword Integers . . . . . . . . . . . . . . . . . . . . . 4-127

POP—Pop a Value from the Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-130

POPA/POPAD—Pop All General-Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-137

POPF/POPFD/POPFQ—Pop Stack into EFLAGS Register . . . . . . . . . . . . . . . . . . . . . . . . . 4-139

POR—Bitwise Logical OR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-143

PREFETCHh—Prefetch Data Into Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-146

PSADBW—Compute Sum of Absolute Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-148

PSHUFB — Packed Shuffle Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-152

PSHUFD—Shuffle Packed Doublewords . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-156

PSHUFHW—Shuffle Packed High Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-159

PSHUFLW—Shuffle Packed Low Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-162

PSHUFW—Shuffle Packed Words. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-165

PSIGNB/PSIGNW/PSIGND — Packed SIGN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-168

PSLLDQ—Shift Double Quadword Left Logical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-173

PSLLW/PSLLD/PSLLQ—Shift Packed Data Left Logical. . . . . . . . . . . . . . . . . . . . . . . . . . .4-175

PSRAW/PSRAD—Shift Packed Data Right Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-180

PSRLDQ—Shift Double Quadword Right Logical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-185

PSRLW/PSRLD/PSRLQ—Shift Packed Data Right Logical. . . . . . . . . . . . . . . . . . . . . . . . . 4-187

PSUBB/PSUBW/PSUBD—Subtract Packed Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-192

PSUBQ—Subtract Packed Quadword Integers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-196

PSUBSB/PSUBSW—Subtract Packed Signed Integers with Signed Saturation . . . . .4-199

PSUBUSB/PSUBUSW—Subtract Packed Unsigned Integers

with Unsigned Saturation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-203

PUNPCKHBW/PUNPCKHWD/PUNPCKHDQ/PUNPCKHQDQ— Unpack High Data . . . . 4-207

PUNPCKLBW/PUNPCKLWD/PUNPCKLDQ/PUNPCKLQDQ—

Unpack Low Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-212

x

Vol. 2A

Page 11

CONTENTS

PAGE

PUSH—Push Word, Doubleword or Quadword Onto the Stack . . . . . . . . . . . . . . . . . . . 4-217

PUSHA/PUSHAD—Push All General-Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 4-222

PUSHF/PUSHFD—Push EFLAGS Register onto the Stack . . . . . . . . . . . . . . . . . . . . . . . . 4-225

PXOR—Logical Exclusive OR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-228

RCL/RCR/ROL/ROR-—Rotate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-231

RCPPS—Compute Reciprocals of Packed Single-Precision Floating-Point Values . . 4-238

RCPSS—Compute Reciprocal of Scalar Single-Precision Floating-Point Values . . . . 4-241

RDMSR—Read from Model Specific Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-244

RDPMC—Read Performance-Monitoring Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-246

RDTSC—Read Time-Stamp Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-251

REP/REPE/REPZ/REPNE/REPNZ—Repeat String Operation Prefix . . . . . . . . . . . . . . . 4-253

RET—Return from Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-258

RSM—Resume from System Management Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-270

RSQRTPS—Compute Reciprocals of Square Roots of Packed

Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-272

RSQRTSS—Compute Reciprocal of Square Root of Scalar

Single-Precision Floating-Point Value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-275

SAHF—Store AH into Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-278

SAL/SAR/SHL/SHR—Shift . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-280

SBB—Integer Subtraction with Borrow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-287

SCAS/SCASB/SCASW/SCASD—Scan String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-291

SETcc—Set Byte on Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-296

SFENCE—Store Fence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-301

SGDT—Store Global Descriptor Table Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-302

SHLD—Double Precision Shift Left . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-305

SHRD—Double Precision Shift Right . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-308

SHUFPD—Shuffle Packed Double-Precision Floating-Point Values . . . . . . . . . . . . . . . 4-311

SHUFPS—Shuffle Packed Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . 4-314

SIDT—Store Interrupt Descriptor Table Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-317

SLDT—Store Local Descriptor Table Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-320

SMSW—Store Machine Status Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-322

SQRTPS—Compute Square Roots of Packed Single-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-328

SQRTSD—Compute Square Root of Scalar Double-Precision Floating-Point Value. 4-331

SQRTSS—Compute Square Root of Scalar Single-Precision Floating-Point Value. . 4-334

STC—Set Carry Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-337

STD—Set Direction Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-338

STI—Set Interrupt Flag. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-339

STMXCSR—Store MXCSR Register State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-342

STOS/STOSB/STOSW/STOSD/STOSQ—Store String. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-344

STR—Store Task Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-348

SUB—Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-350

SUBPD—Subtract Packed Double-Precision Floating-Point Values . . . . . . . . . . . . . . . 4-353

SUBPS—Subtract Packed Single-Precision Floating-Point Values . . . . . . . . . . . . . . . . 4-356

SUBSD—Subtract Scalar Double-Precision Floating-Point Values . . . . . . . . . . . . . . . . 4-359

SUBSS—Subtract Scalar Single-Precision Floating-Point Values. . . . . . . . . . . . . . . . . . 4-362

SWAPGS—Swap GS Base Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-365

Vol. 2A xi

Page 12

CONTENTS

PAGE

SYSCALL—Fast System Call . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-367

SYSENTER—Fast System Call . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-369

SYSEXIT—Fast Return from Fast System Call . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-373

SYSRET—Return From Fast System Call . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-377

TEST—Logical Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-379

UCOMISD—Unordered Compare Scalar Double-Precision Floating-Point Values and Set

EFLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-382

UCOMISS—Unordered Compare Scalar Single-Precision Floating-Point Values and Set

EFLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-385

UD2—Undefined Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-388

UNPCKHPD—Unpack and Interleave High Packed Double-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-389

UNPCKHPS—Unpack and Interleave High Packed Single-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-392

UNPCKLPD—Unpack and Interleave Low Packed Double-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-395

UNPCKLPS—Unpack and Interleave Low Packed Single-Precision

Floating-Point Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-398

VERR/VERW—Verify a Segment for Reading or Writing . . . . . . . . . . . . . . . . . . . . . . . . . 4-401

WAIT/FWAIT—Wait. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-404

WBINVD—Write Back and Invalidate Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-406

WRMSR—Write to Model Specific Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-408

XADD—Exchange and Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-410

XCHG—Exchange Register/Memory with Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-413

XLAT/XLATB—Table Look-up Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-416

XOR—Logical Exclusive OR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-418

XORPD—Bitwise Logical XOR for Double-Precision Floating-Point Values. . . . . . . . . 4-421

XORPS—Bitwise Logical XOR for Single-Precision Floating-Point Values. . . . . . . . . . 4-423

CHAPTER 5

VMX INSTRUCTION REFERENCE

5.1 OVERVIEW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 CONVENTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.3 VMX INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

VMCALL—Call to VM Monitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

VMCLEAR—Clear Virtual-Machine Control Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

VMLAUNCH/VMRESUME—Launch/Resume Virtual Machine . . . . . . . . . . . . . . . . . . . . . . . 5-10

VMPTRLD—Load Pointer to Virtual-Machine Control Structure. . . . . . . . . . . . . . . . . . . . 5-13

VMPTRST—Store Pointer to Virtual-Machine Control Structure . . . . . . . . . . . . . . . . . . . 5-16

VMREAD—Read Field from Virtual-Machine Control Structure . . . . . . . . . . . . . . . . . . . . 5-18

VMRESUME—Resume Virtual Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

VMWRITE—Write Field to Virtual-Machine Control Structure . . . . . . . . . . . . . . . . . . . . . . 5-22

VMXOFF—Leave VMX Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

VMXON—Enter VMX Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

Vol. 2A

xii

Page 13

CONTENTS

PAGE

CHAPTER 6

SAFER MODE EXTENSIONS REFERENCE

6.1 OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

6.2 SMX FUNCTIONALITY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

6.2.1 Detecting and Enabling SMX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

6.2.2 SMX Instruction Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

6.2.2.1 GETSEC[CAPABILITIES] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

6.2.2.2 GETSEC[ENTERACCS] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

6.2.2.3 GETSEC[EXITAC]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

6.2.2.4 GETSEC[SENTER] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

6.2.2.5 GETSEC[SEXIT] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

6.2.2.6 GETSEC[PARAMETERS] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

6.2.2.7 GETSEC[SMCTRL]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

6.2.2.8 GETSEC[WAKEUP] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

6.2.3 Measured Environment and SMX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

6.3 GETSEC LEAF FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

GETSEC[CAPABILITIES] - Report the SMX Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

GETSEC[ENTERACCS] - Execute Authenticated Chipset Code . . . . . . . . . . . . . . . . . . . . . .5-12

GETSEC[EXITAC]—Exit Authenticated Code Execution Mode . . . . . . . . . . . . . . . . . . . . . .5-23

GETSEC[SENTER]—Enter a measured environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

GETSEC[SEXIT]—Exit measured environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-39

GETSEC[PARAMETERS]—Report the SMX parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-43

GETSEC[SMCTRL]—SMX mode control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-48

GETSEC[WAKEUP]—Wake up sleeping processors in measured environment . . . . . . .5-52

APPENDIX A

OPCODE MAP

A.1 USING OPCODE TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.2 KEY TO ABBREVIATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.2.1 Codes for Addressing Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.2.2 Codes for Operand Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

A.2.3 Register Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.2.4 Opcode Look-up Examples for One, Two,

and Three-Byte OpcodesA-4

A.2.4.1 One-Byte Opcode Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.2.4.2 Two-Byte Opcode Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

A.2.4.3 Three-Byte Opcode Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

A.2.5 Superscripts Utilized in Opcode Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

A.3 ONE, TWO, AND THREE-BYTE OPCODE MAPS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

A.4 OPCODE EXTENSIONS FOR ONE-BYTE AND TWO-BYTE OPCODES . . . . . . . . . . . . . . . . . . . A-19

A.4.1 Opcode Look-up Examples Using Opcode Extensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-19

A.4.2 Opcode Extension Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-20

A.5 ESCAPE OPCODE INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-22

A.5.1 Opcode Look-up Examples for Escape Instruction Opcodes . . . . . . . . . . . . . . . . . . . . . . . .A-22

A.5.2 Escape Opcode Instruction Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-22

A.5.2.1 Escape Opcodes with D8 as First Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-23

A.5.2.2 Escape Opcodes with D9 as First Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-24

Vol. 2A xiii

Page 14

CONTENTS

PAGE

A.5.2.3 Escape Opcodes with DA as First Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-25

A.5.2.4 Escape Opcodes with DB as First Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-26

A.5.2.5 Escape Opcodes with DC as First Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-27

A.5.2.6 Escape Opcodes with DD as First Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-28

A.5.2.7 Escape Opcodes with DE as First Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-29

A.5.2.8 Escape Opcodes with DF As First Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-30

APPENDIX B

INSTRUCTION FORMATS AND ENCODINGS

B.1 MACHINE INSTRUCTION FORMAT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

B.1.1 Legacy Prefixes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

B.1.2 REX Prefixes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

B.1.3 Opcode Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

B.1.4 Special Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

B.1.4.1 Reg Field (reg) for Non-64-Bit Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

B.1.4.2 Reg Field (reg) for 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-4

B.1.4.3 Encoding of Operand Size (w) Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-5

B.1.4.4 Sign-Extend (s) Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-5

B.1.4.5 Segment Register (sreg) Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-6

B.1.4.6 Special-Purpose Register (eee) Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-6

B.1.4.7 Condition Test (tttn) Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-7

B.1.4.8 Direction (d) Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-8

B.1.5 Other Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-9

B.2 GENERAL-PURPOSE INSTRUCTION FORMATS AND ENCODINGS

FOR NON-64-BIT MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-9

B.2.1 General Purpose Instruction Formats and Encodings for 64-Bit Mode . . . . . . . . . . . . . B-24

B.3 PENTIUM

®

PROCESSOR FAMILY INSTRUCTION FORMATS AND ENCODINGS . . . . . . . . . . B-53

B.4 64-BIT MODE INSTRUCTION ENCODINGS FOR SIMD INSTRUCTION EXTENSIONS . . . . . . B-54

B.5 MMX INSTRUCTION FORMATS AND ENCODINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-54

B.5.1 Granularity Field (gg) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-54

B.5.2 MMX Technology and General-Purpose Register Fields (mmxreg and reg) . . . . . . . . . B-55

B.5.3 MMX Instruction Formats and Encodings Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-55

B.6 P6 FAMILY INSTRUCTION FORMATS AND ENCODINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-58

B.7 SSE INSTRUCTION FORMATS AND ENCODINGS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-59

B.8 SSE2 INSTRUCTION FORMATS AND ENCODINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-68

B.8.1 Granularity Field (gg) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-68

B.9 SSE3 FORMATS AND ENCODINGS TABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-85

B.10 SSSE3 FORMATS AND ENCODING TABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-87

B.11 SPECIAL ENCODINGS FOR 64-BIT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-91

B.12 FLOATING-POINT INSTRUCTION FORMATS AND ENCODINGS . . . . . . . . . . . . . . . . . . . . . . . . B-95

B.13 VMX INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-101

B.14 SMX INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-103

APPENDIX C

INTEL® C/C++ COMPILER INTRINSICS AND FUNCTIONAL EQUIVALENTS

C.1 SIMPLE INTRINSICS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-2

C.2 COMPOSITE INTRINSICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-14

Vol. 2A

xiv

Page 15

CONTENTS

PAGE

FIGURES

Figure 1-1. Bit and Byte Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Figure 1-2. Syntax for CPUID, CR, and MSR Data Presentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

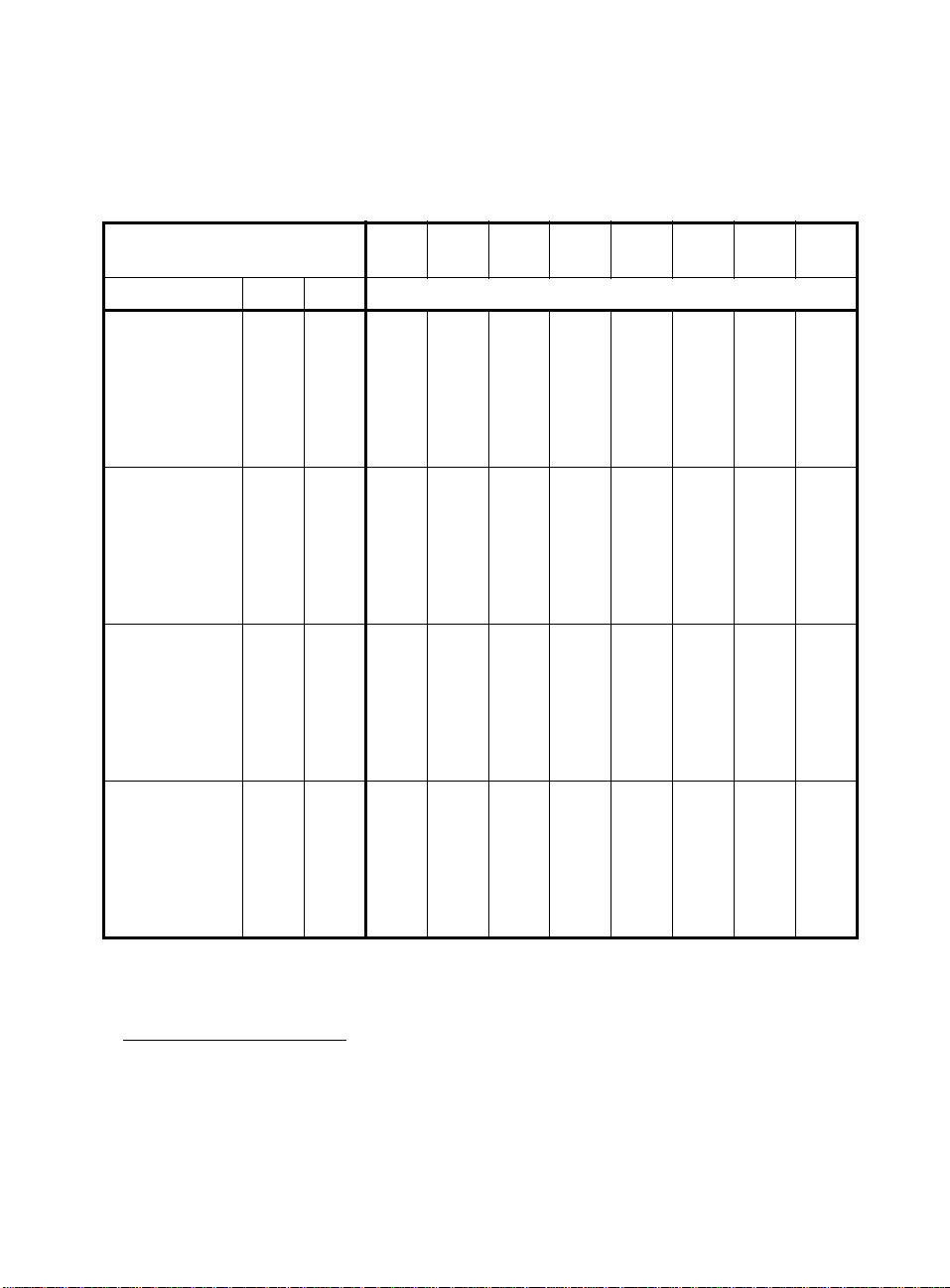

Figure 2-1. Intel 64 and IA-32 Architectures Instruction Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Figure 2-2. Table Interpretation of ModR/M Byte (C8H) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Figure 2-3. Prefix Ordering in 64-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 2-4. Memory Addressing Without an SIB Byte; REX.X Not Used . . . . . . . . . . . . . . . . . . . . .2-11

Figure 2-5. Register-Register Addressing (No Memory Operand); REX.X Not Used . . . . . . . . . .2-11

Figure 2-6. Memory Addressing With a SIB Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

Figure 2-7. Register Operand Coded in Opcode Byte; REX.X & REX.R Not Used . . . . . . . . . . . . .2-12

Figure 3-1. Bit Offset for BIT[RAX, 21] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

Figure 3-2. Memory Bit Indexing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

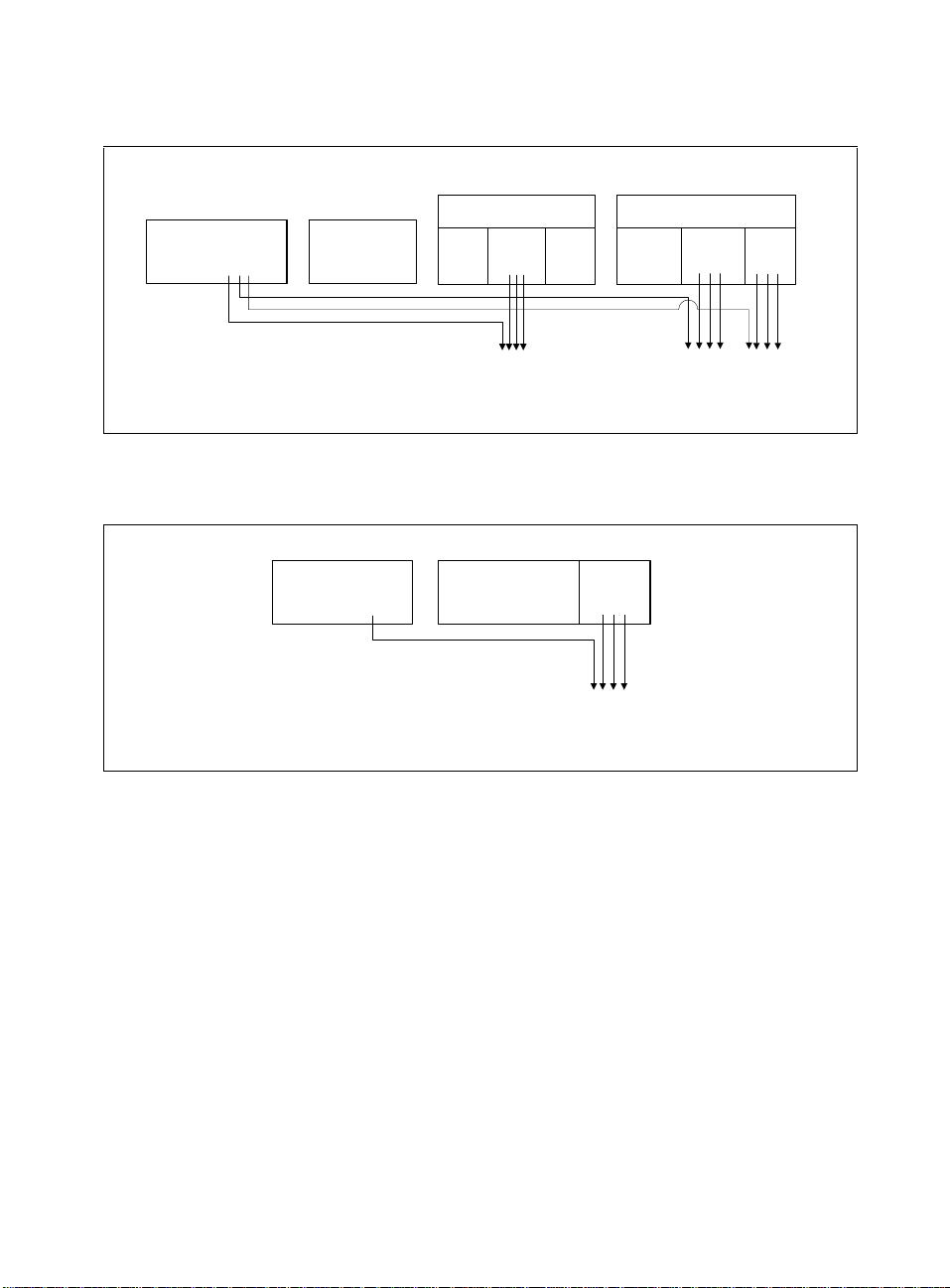

Figure 3-3. ADDSUBPD—Packed Double-FP Add/Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-45

Figure 3-4. ADDSUBPS—Packed Single-FP Add/Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-49

Figure 3-5. Version Information Returned by CPUID in EAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-170

Figure 3-6. Feature Information Returned in the ECX Register . . . . . . . . . . . . . . . . . . . . . . . . . . 3-172

Figure 3-7. Feature Information Returned in the EDX Register . . . . . . . . . . . . . . . . . . . . . . . . . . 3-174

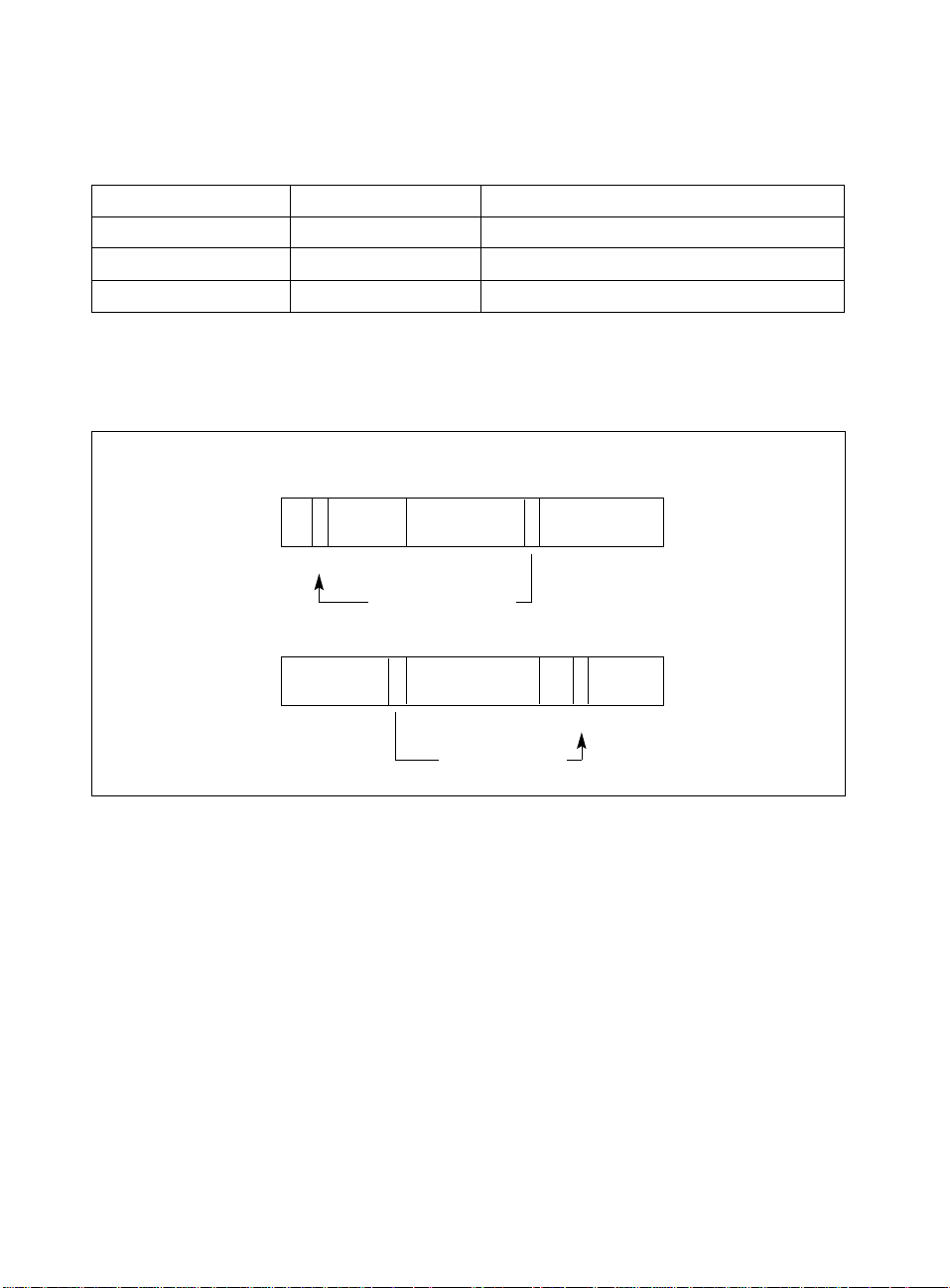

Figure 3-8. Determination of Support for the Processor Brand String . . . . . . . . . . . . . . . . . . . . 3-182

Figure 3-9. Algorithm for Extracting Maximum Processor Frequency . . . . . . . . . . . . . . . . . . . . 3-184

Figure 3-10. HADDPD—Packed Double-FP Horizontal Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-435

Figure 3-11. HADDPS—Packed Single-FP Horizontal Add . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-439

Figure 3-12. HSUBPD—Packed Double-FP Horizontal Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-445

Figure 3-13. HSUBPS—Packed Single-FP Horizontal Subtract . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-450

Figure 3-14. MOVDDUP—Move One Double-FP and Duplicate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-620

Figure 3-15. MOVSHDUP—Move Packed Single-FP High and Duplicate . . . . . . . . . . . . . . . . . . . . 3-676

Figure 3-16. MOVSLDUP—Move Packed Single-FP Low and Duplicate . . . . . . . . . . . . . . . . . . . . . 3-679

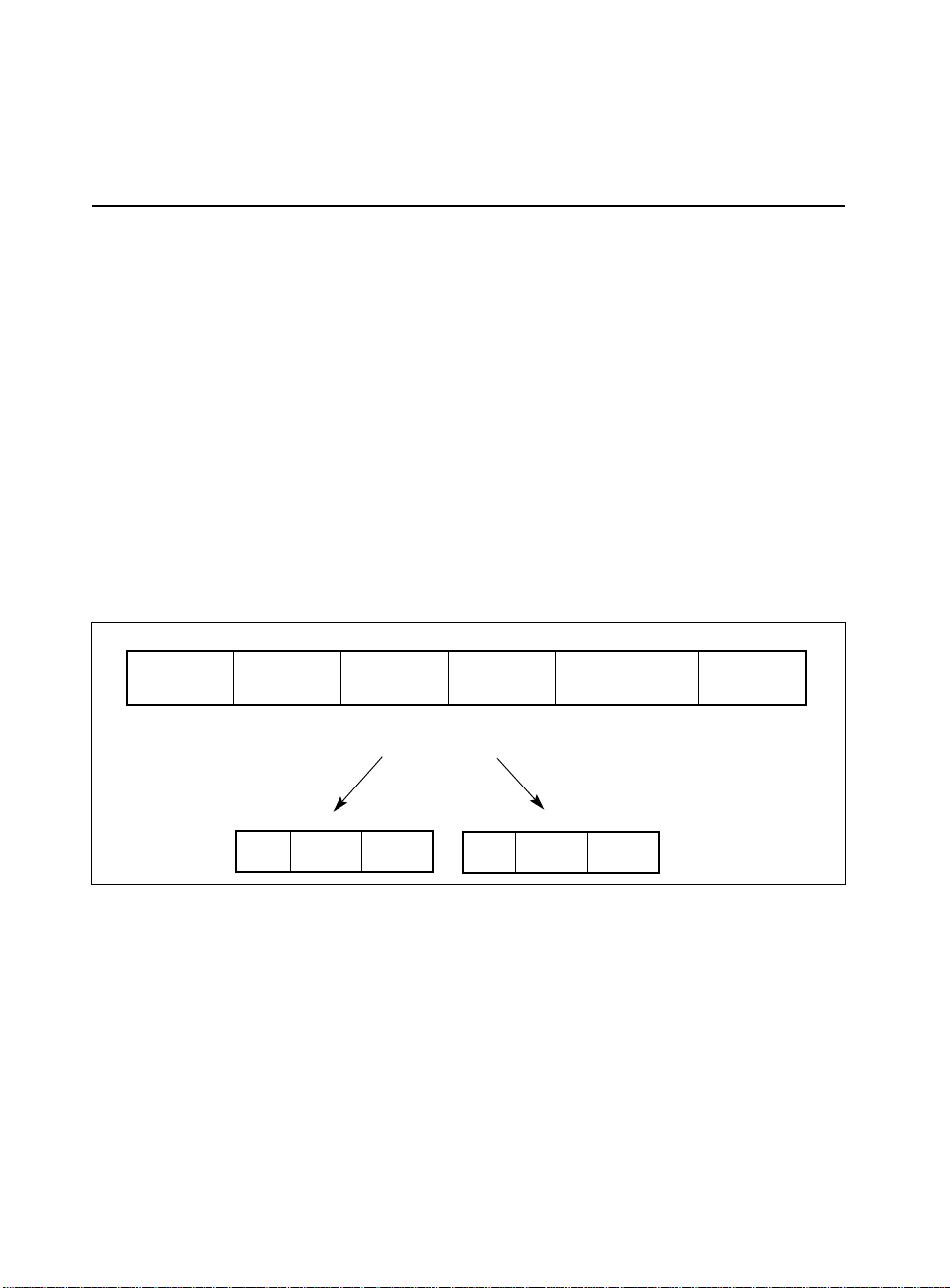

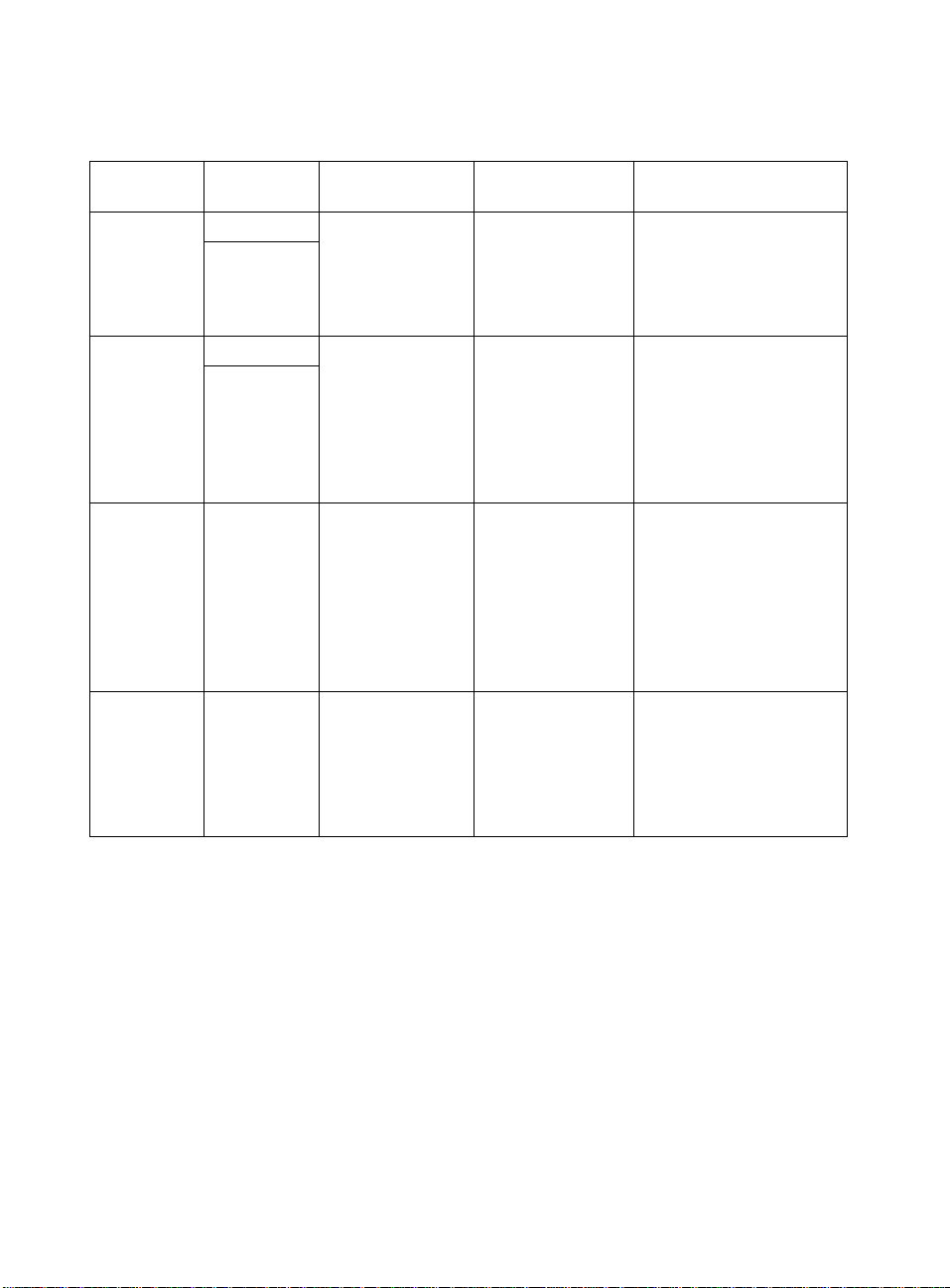

Figure 4-1. Operation of the PACKSSDW Instruction Using 64-bit Operands . . . . . . . . . . . . . . . .4-27

Figure 4-2. PMADDWD Execution Model Using 64-bit Operands . . . . . . . . . . . . . . . . . . . . . . . . . . .4-95

Figure 4-3. PMULHUW and PMULHW Instruction Operation Using 64-bit Operands . . . . . . . 4-116

Figure 4-4. PMULLU Instruction Operation Using 64-bit Operands . . . . . . . . . . . . . . . . . . . . . . . 4-123

Figure 4-5. PSADBW Instruction Operation Using 64-bit Operands. . . . . . . . . . . . . . . . . . . . . . . 4-149

Figure 4-6. PSHUB with 64-Bit Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-153

Figure 4-7. PSHUFD Instruction Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-156

Figure 4-8. PSLLW, PSLLD, and PSLLQ Instruction Operation Using 64-bit Operand . . . . . . . 4-176

Figure 4-9. PSRAW and PSRAD Instruction Operation Using a 64-bit Operand . . . . . . . . . . . . 4-181

Figure 4-10. PSRLW, PSRLD, and PSRLQ Instruction Operation Using 64-bit Operand . . . . . . 4-188

Figure 4-11. PUNPCKHBW Instruction Operation Using 64-bit Operands . . . . . . . . . . . . . . . . . . 4-208

Figure 4-12. PUNPCKLBW Instruction Operation Using 64-bit Operands . . . . . . . . . . . . . . . . . . . 4-212

Figure 4-13. SHUFPD Shuffle Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-311

Figure 4-14. SHUFPS Shuffle Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-314

Figure 4-15. UNPCKHPD Instruction High Unpack and Interleave Operation . . . . . . . . . . . . . . . 4-389

Figure 4-16. UNPCKHPS Instruction High Unpack and Interleave Operation . . . . . . . . . . . . . . . 4-392

Figure 4-17. UNPCKLPD Instruction Low Unpack and Interleave Operation . . . . . . . . . . . . . . . . 4-395

Figure 4-18. UNPCKLPS Instruction Low Unpack and Interleave Operation . . . . . . . . . . . . . . . . 4-398

Figure A-1. ModR/M Byte nnn Field (Bits 5, 4, and 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-19

Figure B-1. General Machine Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Vol. 2A xv

Page 16

CONTENTS

PAGE

TABLES

Table 2-1. 16-Bit Addressing Forms with the ModR/M Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Table 2-2. 32-Bit Addressing Forms with the ModR/M Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Table 2-3. 32-Bit Addressing Forms with the SIB Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Table 2-4. REX Prefix Fields [BITS: 0100WRXB]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Table 2-5. Special Cases of REX Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Table 2-6. Direct Memory Offset Form of MOV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Table 2-7. RIP-Relative Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Table 3-1. Register Codes Associated With +rb, +rw, +rd, +ro . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table 3-2. Range of Bit Positions Specified by Bit Offset Operands . . . . . . . . . . . . . . . . . . . . . . 3-11

Table 3-3. Intel 64 and IA-32 General Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Table 3-5. SIMD Floating-Point Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

Table 3-4. x87 FPU Floating-Point Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

Table 3-6. Decision Table for CLI Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-110

Table 3-7. Comparison Predicate for CMPPD and CMPPS Instructions. . . . . . . . . . . . . . . . . . . . 3-126

Table 3-8. Pseudo-Op and CMPPD Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-127

Table 3-9. Pseudo-Ops and CMPPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-132