现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

Version 1.2 , May 2004

Datasheet

DS-CoreControl-TDA21302

TDA21302

Authors: Edward Chang

Published by Infineon Technologies AG

http://www.infineon.com/DCDC

Power Management & Supply

CoreControl

TM

Page 1 of 25 DS-CoreControl-TDA21302

Never stop thinking.

Contents:

Features………………………………………………………………………………………………………......3

Application……………………………………………………………………………………………………...…3

Pinout Drawing and Description………………………………………………………………………………..3

General Description……………………………………………………………………………………………...5

Block Diagram…………………………………………………………………………………………………….5

Reference Schematic……………………………………………………………………………………………6

Absolute Maximum Rating.................................................................................................................... 7

Thermal Characteristic.......................................................................................................................... 7

Electrical Characteristic ........................................................................................................................ 7

Operating Condition.............................................................................................................................. 9

VRD10,x VID Table ............................................................................................................................ 10

Application Information ....................................................................................................................... 11

Voltage Control………………………………………………………………………………………..11

Current Balance……………………………………………………………………………………….12

Load Droop…………………………………………………………………………………………….12

Fault Detection………………………………………………………………………………………...12

Phase Setting and Converter Start Up……………………………………………………………...13

Current Sensing Setting………………………………………………………………………………13

DAC Offset Voltage & Droop Tuning………………………………………………………………..14

Protection and SS Function………………………………………………………………………….15

Design Procedure Suggestion ............................................................................................................ 16

Design Example.................................................................................................................................. 17

Layout Guide ...................................................................................................................................... 20

Outline Diemension……………………………………………………………………………………………..22

CoreControl

TM

Page 2 of 25 DS-CoreControl-TDA21302

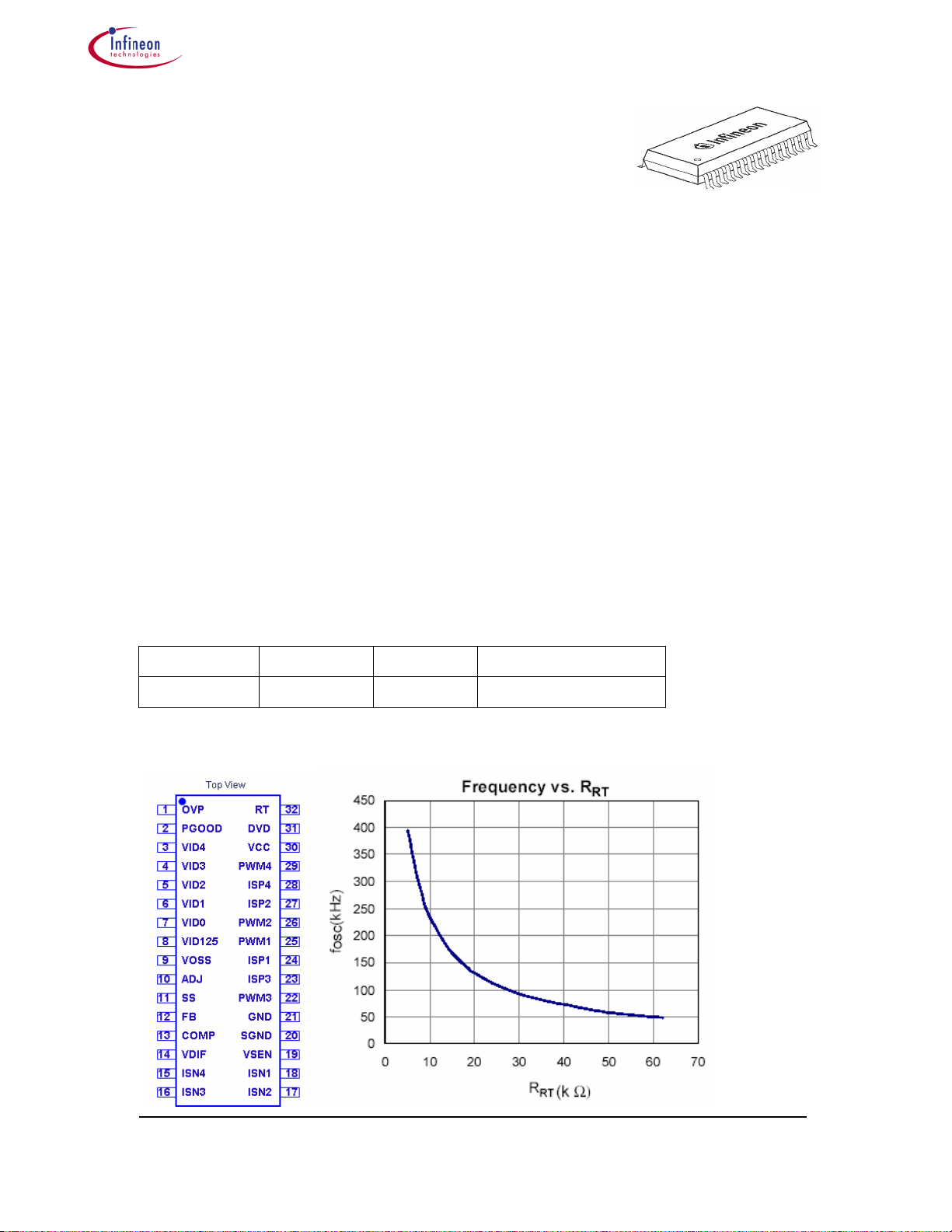

Multi-Phase PWM Controller for CPU Core

Power Supply

P-DSO-32

Features :

• Multi-Phase PWM Conversion with Automatically Phase Selection

• VRD10.X Compliant

• Active Droop Compensation For Fast Load Response

• Smooth V

• Power Stage Thermal Balance By Sync FET Rds(on) Current Sense Technique

• Hiccup Mode Over Current Protection

• Programmable Switching Frequency ( 50KHz ~ 400KHz per Phase ), Under

Voltage Lockout, and Soft-Start

• High Output Ripple Frequency times numbers of working Channels

Application :

• Intel Processor Voltage Regulator : VRM10.X

• Low Output Voltage High Output Current DC-DC Converters

• Voltage Regulator Modules

Voltage Transition during the VID On The Fly

CORE

Type Package Marking Ordering Code

TDA21302 P-DSO-32 21302 Q67042-S4229

Pinout Drawing and Description :

CoreControl

TM

Page 3 of 25 DS-CoreControl-TDA21302

CoreControl

TM

Page 4 of 25 DS-CoreControl-TDA21302

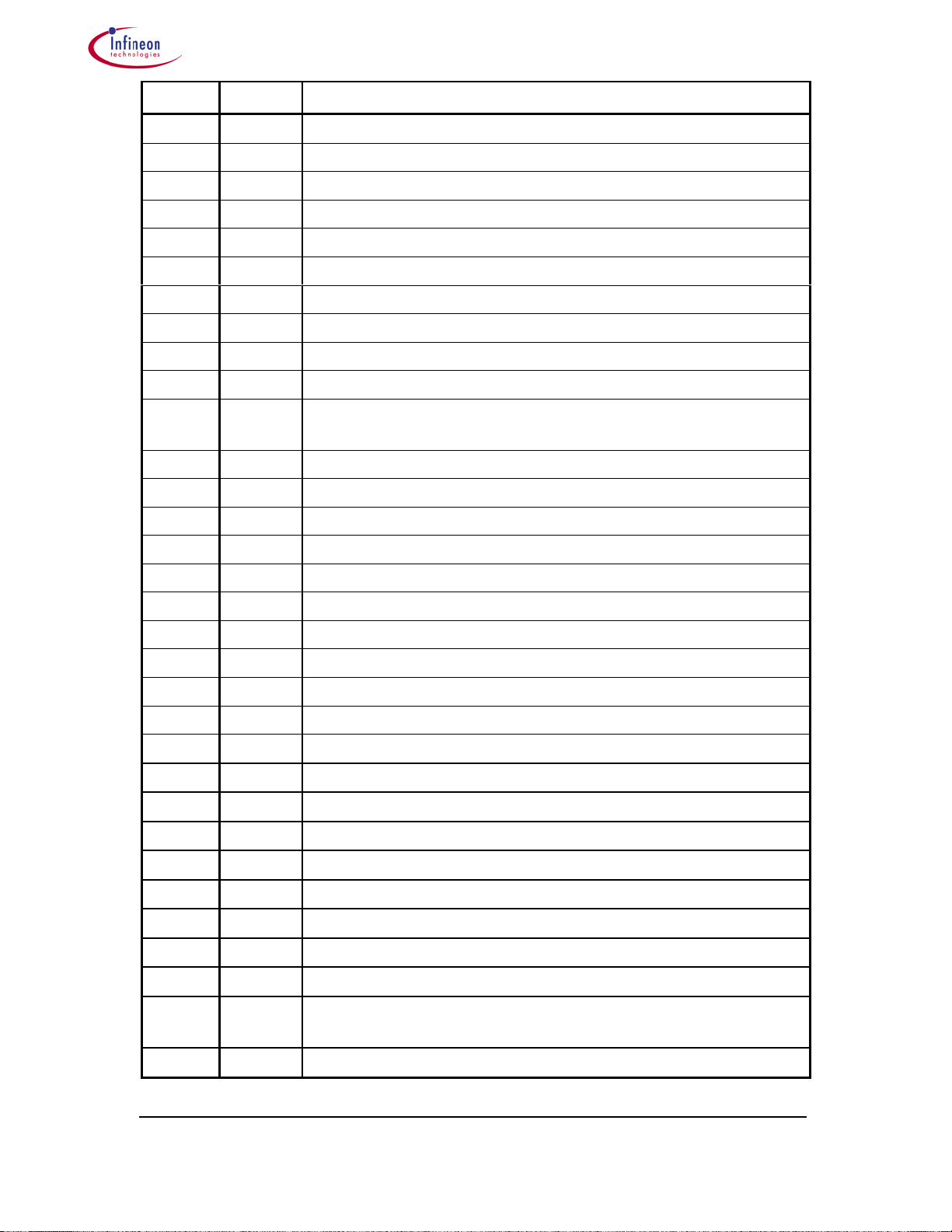

Number Name Description

1 OVP

2 PGOOD

3 VID4

4 VID3

5 VID2

6 VID1

7 VID0

8 VID125

9 VOSS

10 ADJ

11 SS

12 FB

13 COMP

14 VDIF

15 ISN4

16 ISN3

Over voltage trip output

Open drain power good signal output pin

Voltage Identification DAC Input. Internally pull up to 3V.

Voltage Identification DAC Input. Internally pull up to 3V.

Voltage Identification DAC Input. Internally pull up to 3V.

Voltage Identification DAC Input. Internally pull up to 3V.

Voltage Identification DAC Input. Internally pull up to 3V.

Voltage Identification DAC Input. Internally pull up to 3V.

Connect a resistor to GND to set the initial offset voltage.

Connect a resistor to GND to set the Droop Voltage.

Soft-Start. Connect with a capacitor to GND to set the Soft-Start Interval. Pulling down this pin

below 1V shall shut the converter down.

Internal error amplifier inverting input pin

Output of the error amplifier and input of the PWM comparator

Output pin of the differential converter output voltage sense

Differential current sense negative input pin connects to the drain pin of channel 4 Sync FET

Differential current sense negative input pin connects to the drain pin of channel 3 Sync FET

17 ISN2

18 ISN1

19 VSEN

20 SGND

21 GND

22 PWM3

23 ISP3

24 ISP1

25 PWM1

26 PWM2

27 ISP2

28 ISP4

29 PWM4

30 VCC

31 DVD

Differential current sense positive input pin connects to the drain pin of channel 2 Sync FET

Differential current sense positive input pin connects to the drain pin of channel 1 Sync FET

The positive input pin of the differential converter output voltage sense amplifier

The negative input pin of the differential converter output voltage sense amplifier

Ground pin of the IC

Channel 3 PWM output pin. Connect to high level for 2 phase operation.

Differential current sense positive input pin connects to the source pin of channel 3 Sync FET

Differential current sense positive input pin connects to the source pin of channel 1 Sync FET

Channel 1 PWM output pin

Channel 2 PWM output pin

Differential current sense positive input pin connects to the source pin of channel 2 Sync FET

Differential current sense positive input pin connects to the source pin of channel 4 Sync FET

Channel 4 PWM output pin. Connect to high level for 2 or 3 phase operation.

IC power supply pin connects to 5V

Connect the external voltage divider to program the controller under voltage lockout based on

the input voltage of the power stage voltage

32 RT

CoreControl

Connect a resistor to GND to set the channel switching frequency

TM

Page 5 of 25 DS-CoreControl-TDA21302

g

g

g

g

A

General Description

TDA21302 is a multi-phase DC-DC buck converter controller integrated all control functions for the next generation GHz CPU

voltage regulator. TDA21302 automatically controls 2 to 4 interleaved buck switching power stage operation. The multi-phase

architecture is able to provide high output current with lower power dissipation on the switching devices and minimizing the

input ripple current and output ripple voltage. The equivalent high operation frequency optimizes the voltage regulator design

for better transient response and thermal performance.

TDA21302 utilizes the Sync FET Rds(on) in every channel as the current sense element. The differential current sense in

every channel results precious channel current information to the controller for good droop adjustment, channel current

balance, channel switching devices thermal balance and over current protection.

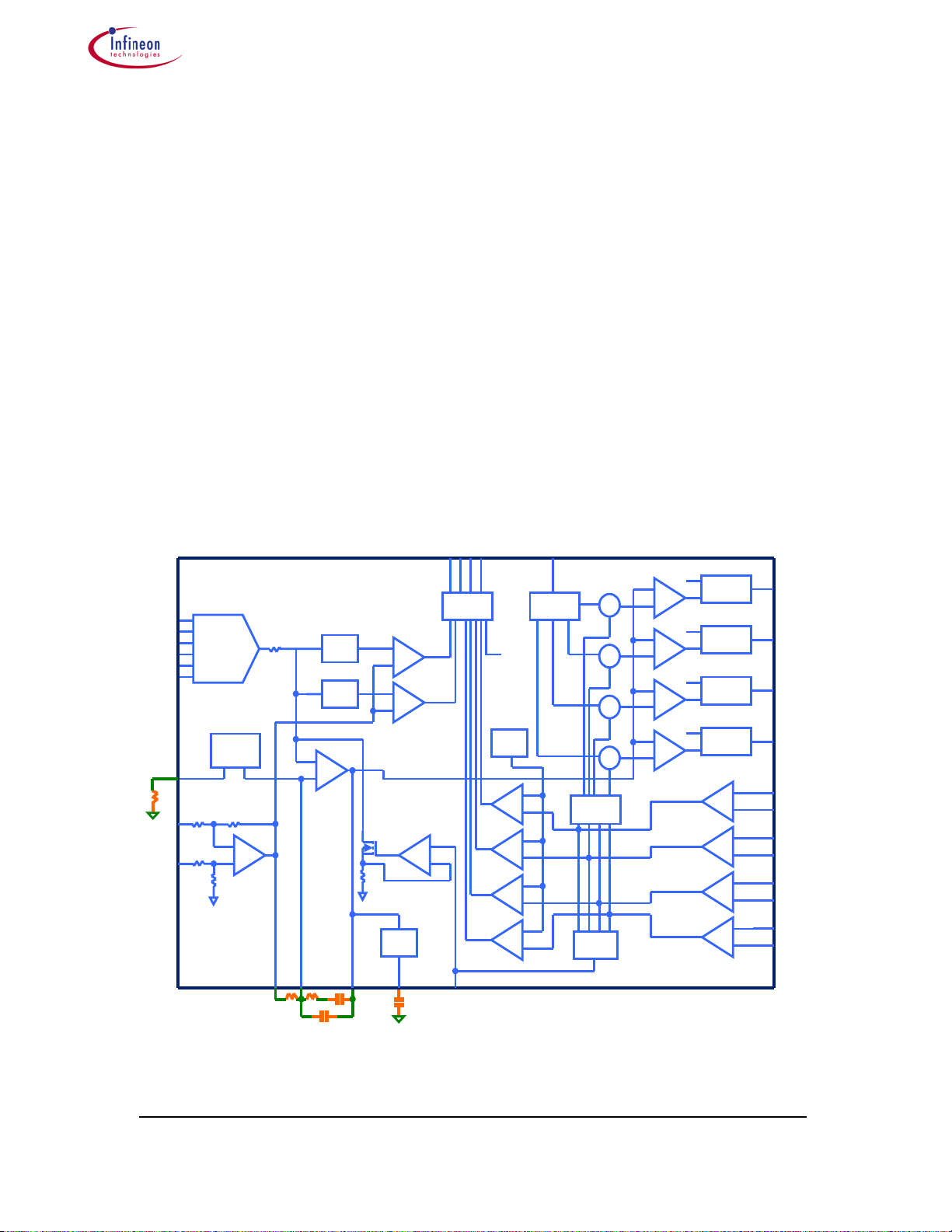

Block Diagram

VOSS

SGND

VSEN

VID0

VID1

VID2

VID3

VID4

VID DAC

& Step

Offset

Settin

VCC PGOOD

INH

+

+

+

+

I

I

I

I

RT DVD

Oscillatior

& Sawtooth

+

+

+

+

Current

Correction

SUM/M

INH

I

I

I

I

PWM Logic

PWM CMP

INH

PWM Logic

PWM CMP

INH

PWM Logic

PWM CMP

INH

PWM Logic

PWM CMP

+

+

+

+

+

+

+

+

+

I

+

I

+

I

+

I

PWM1

PWM2

PWM3

PWM4

ISN1

ISP1

ISN2

ISP2

ISN3

ISP3

ISN4

ISP4

OVP

Power On

Reset

OVP

Settin

PG

Settin

I

+

I

+

+

I

+

I

OCP

Settin

+

I

Soft

Start

VDIF COMP FB

SS

DJ

CoreControl

TM

Page 6 of 25 DS-CoreControl-TDA21302

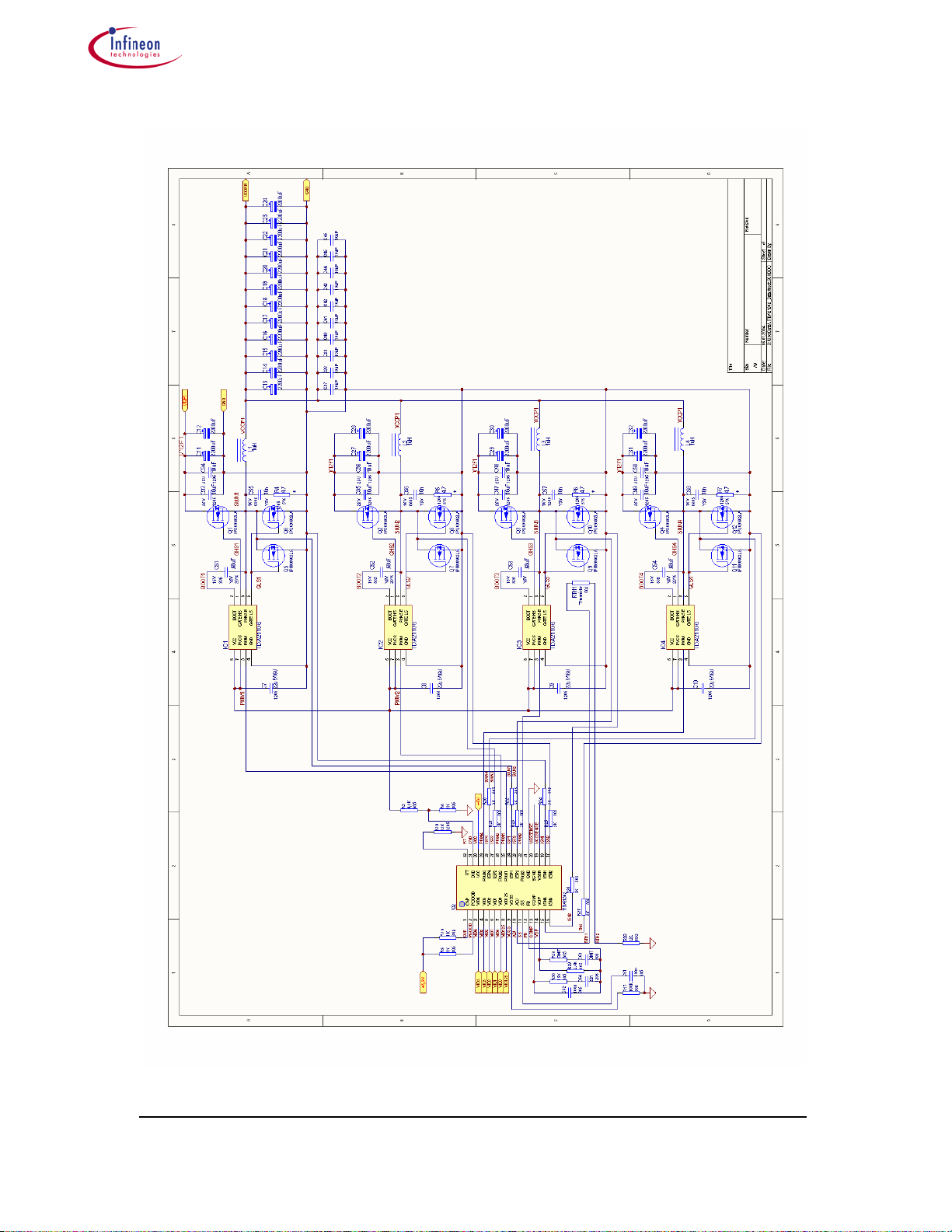

Reference Schmatic

CoreControl

TM

Page 7 of 25 DS-CoreControl-TDA21302

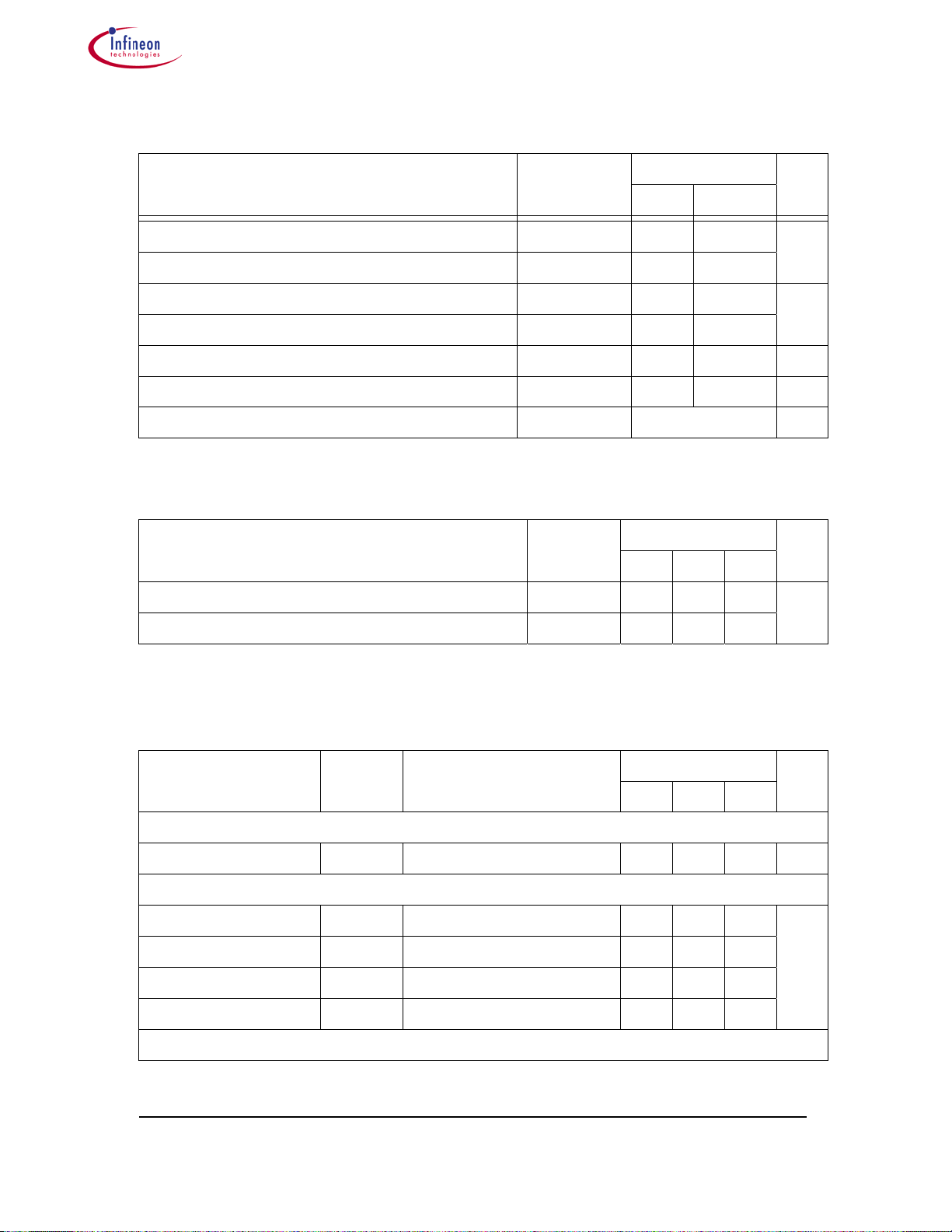

Absolute Maximum Ratings

At Tj = 25 °C, unless otherwise specified

Parameter

Symbol

Voltage supplied to ‘VCC’ pin; DC VCC -0.3 7

Input, Output or I/O Pin -0.3 Vcc+0.3

Junction temperature TJ 0 125

Value

Min. Max.

Unit

V

°C

Storage temperature TS -65 150

ESD Rating; Human Body Model 2 KV

ESD Rating; Machine M Model 200 V

IEC climatic category; DIN EN 60068-1 55/150/56 -

Thermal Characteristic

Parameter

Symbol

Thermal resistance, junction-soldering point

Values

Unit

Min. Typ. Max.

K/W

Thermal resistance, junction-ambient 50

Electrical Characteristic

At Vcc=5V, Tj = 25 °C, unless otherwise specified

Parameter

Supply Characteristic

Bias supply current ICC PWM1,2,3,4 Open 12 16 mA

Power On Reset Characteristic

POR Threshold

Hysteresis V

V

Threshold V

DVD

V

Hysteresis V

DVD

Oscillator

Symbol

V

CCRTH

CCHYS

DVDTP

DVDHYS

Conditions

Values

Min. Typ. Max.

VCC rising threshold 4,0 4,2 4,5

Unit

V

0,2 0,5

Low to High Enable 1,9 2 2,1

V

falling threshold 0,1

VCC

CoreControl

TM

Page 8 of 25 DS-CoreControl-TDA21302

Oscillator Frequency

Accuracy

Oscillator Frequency

f

OSC

f

OSC_ADJ

R

= 12 K

RT

170 200 230

KHz

50 400

Adjustable Range

Ramp Amplitude

V

R

OSC

RT

= 12 K

1,9 V

Ramp Valley VRV 0,7 1,0 V

Maximum Duty Cycle Every Phase 62 66 75 %

RT Pin Voltage VRT

R

= 12 K

RT

0,55 0,6 0,65 V

Reference and DAC

DACOUT Voltage

Accuracy

DAC (VID0~VID125)

Input Low

DAC (VID0~VID125)

V

DAC

V

DAC

V

DAC

R

= 12 K

RT

1V

< 1V

VRV 0,8 V

-1 +1 %

-10 +10 mV

0,4 V

Input High

DAC ( VID0~VID125)

I

BIAS_DAC

60 120 180 uV

Bias Current

VOSS Pin Voltage V

VOSS

R

VOSS

= 100 K

0,95 1,0 1,05 V

Error Amplifier

Open Loop Gain

85 dB

Gain Bandwidth GBW 10 MHz

Slew Rate SR COMP = 10 pF 3 V/uS

Differential Sense Amplifier

Input Impedance

Z

IMP

16

K

Gain Bandwidth GBW 10 MHz

Slew Rate SR COMP = 10 pF 3 V/uS

Differential Current Sense GM Amplifier

ISP1, 2, 3, 4 Full

I

ISPFSS

60 uA

Scale Source Current

ISP1, 2, 3, 4 Current

for OCP

CoreControl

TM

I

ISPOCP

100

Page 9 of 25 DS-CoreControl-TDA21302

uA

At Vcc=5V, Tj = 25 °C, unless otherwise specified

Protection

SS Current Iss Vss = 1V 8 13 18 uA

Over Voltage Trip

( V

/ DACOUT )

SENSE

OVP Voltage V

V

OVT

I

OVP

Power Good

Power Good Rising

Threshold

( V

/ DACOUT )

SENSE

Power Good Low

V

PG

V

I

PGL

Voltage

Operating Conditions

At Tj = 25 °C, unless otherwise specified

130 140 150 %

= 10mA 2,2 3,28 4,0 V

OVP

V

Rising

SENSE

= 4mA 0,2 V

PG

92

Values

%

Parameter

Voltage supplied to

‘VCC’ pins

Symbol

V

4,5 5,0 5,5 V

VCC

Conditions

Min. Typ. Max.

Unit

Ambient temperature TA 0 70 °C

Junction temperature TJ 0 125 °C

CoreControl

TM

Page 10 of 25 DS-CoreControl-TDA21302

VRD10,X VID Table

Pin Names Pin Names

VID125 VID4 VID3 VID2 VID1 VID0 Vcore VID125 VID4 VID3 VID2 VID1 VID0 Vcore

0 0 1 0 1 0 0,8375 0 1 1 0 1 0 1,2125

1 0 1 0 0 1 0,8500 1 1 1 0 0 1 1,2250

0 0 1 0 0 1 0,8625 0 1 1 0 0 1 1,2375

1 0 1 0 0 0 0,8750 1 1 1 0 0 0 1,2500

0 0 1 0 0 0 0,8875 0 1 1 0 0 0 1,2625

1 0 0 1 1 1 0,9000 1 1 0 1 1 1 1,2750

0 0 0 1 1 1 0,9125 0 1 0 1 1 1 1,2875

1 0 0 1 1 0 0,9250 1 1 0 1 1 0 1,3000

0 0 0 1 1 0 0,9375 0 1 0 1 1 0 1,3125

1 0 0 1 0 1 0,9500 1 1 0 1 0 1 1,3250

0 0 0 1 0 1 0,9625 0 1 0 1 0 1 1,3375

1 0 0 1 0 0 0,9750 1 1 0 1 0 0 1,3500

0 0 0 1 0 0 0,9875 0 1 0 1 0 0 1,3625

1 0 0 0 1 1 1,0000 1 1 0 0 1 1 1,3750

0 0 0 0 1 1 1,0125 0 1 0 0 1 1 1,3875

1 0 0 0 1 0 1,0250 1 1 0 0 1 0 1,4000

0 0 0 0 1 0 1,0375 0 1 0 0 1 0 1,4125

1 0 0 0 0 1 1,0500 1 1 0 0 0 1 1,4250

0 0 0 0 0 1 1,0625 0 1 0 0 0 1 1,4375

1 0 0 0 0 0 1,0750 1 1 0 0 0 0 1,4500

0 0 0 0 0 0 1,0875 0 1 0 0 0 0 1,4625

1 1 1 1 1 1 OFF 1 0 1 1 1 1 1,4750

0 1 1 1 1 1 OFF 0 0 1 1 1 1 1,4875

1 1 1 1 1 0 1,1000 1 0 1 1 1 0 1,5000

0 1 1 1 1 0 1,1125 0 0 1 1 1 0 1,5125

1 1 1 1 0 1 1,1250 1 0 1 1 0 1 1,5250

0 1 1 1 0 1 1,1375 0 0 1 1 0 1 1,5375

1 1 1 1 0 0 1,1500 1 0 1 1 0 0 1,5500

0 1 1 1 0 0 1,1625 0 0 1 1 0 0 1,5625

1 1 1 0 1 1 1,1750 1 0 1 0 1 1 1,5750

0 1 1 0 1 1 1,1875 0 0 1 0 1 1 1,5875

1 1 1 0 1 0 1,2000 1 0 1 0 1 0 1,6000

Note : “ 1 “ is open and “ 0 “ is connecting to ground.

CoreControl

TM

Page 11 of 25 DS-CoreControl-TDA21302

Application Information :

TDA21302 is a multi-phase DC/DC controller that precisely regulates CPU core voltage and balances

the current of different power channels. The converter consisting of TDA21302 and its companion

drivers, TDA21106 and TDA21102, provides high quality CPU power and all the protection functions to

meet the requirement of the latest VRMs.

Voltage Control

The TDA21302 senses the CPU V

on the PCB trace at heavy load condition. VSEN & SGND are the differential input pins for V

their output, VDIF, is the input of the PGOOD & OVP sense. The internal highly accurate VID DAC

provides the reference voltage for VRD10,X compliance. Control loop consists of error amplifier, pulse

width modulator, external driver ICs and power components. Like conventional voltage mode controller,

the output voltage is locked at the V

signal Vc of the pulse width modulator. The PWM signals of different channels are generated by

comparison of EA output and split-phase saw-tooth wave. Power stage transforms V

PWM signal on-time ratio.

by an precise instrumental amplifier to minimize the voltage drop

CORE

CORE

of the error amplifier and the error signal is used as the control

REF

to output by

IN

and

VID0

VID1

VID2

VID3

VID4

VID125

VOSS

SGND

VSEN

VID DAC

& Step

Offset

Setting

I

+

OVP Setting

PG

Setting

+

I

OVP

+

I

+

I

PWM Comparator

+

I

Soft

Start

VCC PGOOD

DVD

Power On

Reset

INH

CoreControl

TM

VDIF FB

COMP

Page 12 of 25 DS-CoreControl-TDA21302

SS

ADJ

Current Balance

TDA21302 senses the current of the Sync FET in each phase when it is conducting for channel balance

and droop tuning. The differential sensing GM amplifier converts the voltage on the sense components

which can be sense resistors or the Rds(on) of the Sync FET to current signal into internal balance

circuit. The current balance circuit sums and averages the current signals and then generates the

balancing signals injected to pulse signal modulator. If some of the channel current is higher than

average, the balancing signal shall decrease the pulse width to keep the current balance.

Oscillatior &

Sawtooth

COMP

RT

+

+

+

+

Current

Correction

SUM/M

+

+

+

+

+

I

+

I

+

I

+

I

INH

PWM Logic

PWM CMP

INH

PWM Logic

PWM CMP

INH

PWM Logic

PWM CMP

INH

PWM Logic

PWM CMP

PWM1

PWM2

PWM3

PWM4

+

I

+

I

+

I

+

I

ISN1

ISP1

ISN2

ISP2

ISN3

ISP3

ISN4

ISP4

Load Droop

The sensed channel current signals regulated the reference of DAC to form a output voltage droop

proportional to the load current. The droop or so-called “ Active Voltage Positioning “ can reduce the

output voltage ripple during the load transient and the size of the LC filters.

Fault Detection

The chip detects V

for over voltage and power good detection. The “ hiccup mode “ operation of

CORE

over-current protection is adopted to reduce the short circuit current. The inrush current at the start up is

suppressed by the soft start circuit through clamping the pulse width and output voltage.

CoreControl

TM

Page 13 of 25 DS-CoreControl-TDA21302

A

A

∆

∆

AAV

V

Phase Setting and Converter Start Up

The TDA21302 interfaces with companion MOSFET drivers, TDA21106 ( Single Channel ) and

TDA21102 ( Dual Channel ), for correct converter initialization. The tri-state PWM output pins sense the

interface voltage at IC POR period ( both VCC and DVD trip ). The channel is enabled if the voltage at

the pin is 1,2V less than VCC. Please tie the PWM outputs to VCC and the current sense pins to GND

or leave them floating if the channel is unused. For 3 Phase application, connect PWM4 high.

Current Sensing Setting

TDA21302 senses the current of the Sync FET in each phase when it is conducting for channel balance

and droop tuning. The differential sensing GM amplifier converts the voltage on the sense components

which can be sense resistors or the Rds(on) of the Sync FET to current signal into internal balance

circuit.

IX1

Current

Balance

Droop

OCP

IX1

2I

X1

I

X1

Sample

& Hold

I

BP

I

BP

ISP1

ISN1

R

SP1

I

I

1

LL1

R

R

SN1

DS(on)1

Differential Current

GM Amplifier

Basic Theory

BP SN1 , BP X1 SP1 L1_VALLEY DS(on)1

VI R V(I+I)R I R

+−

=× = × − ×

V V and R R I I

+−

SN1 SP1 X1 L1_VALLEY

==⇒∴=×∵

I

I

E

PPE

KK

I

I

I

I

vvaalllleeyy

I

I

G

G

LS

IR

×

I=

The sensing circuit gets by local feedback. R

GM amplifier input bias current. I

X

R

SP

is sampled and held just before low side MOSFET turns off.

X

SP

Therefore,

R

DS(on)1

R

SP1

OOFFV

T×

I=

∆

L

= RSN to cancel the voltage drop caused by

CoreControl

TM

Page 14 of 25 DS-CoreControl-TDA21302

L (S/H) S O OFF IN O

IR VT V - V

I = , I =I - , T = 3,3 for F = 300 KHz

X (S/H) L (S/H) L (AVG) OFF OSC

∴×

I=I -

X (S/H) L (AVG)

××

R2LV

SP IN

V - V

IN O

××

O

V3,3

IN

V

2L R

uS

R

S

SP

uS

×

DAC Offset Voltage & Droop Setting

The DAC offset voltage is set by compensation network & external resistor at VOSS pin by .

1V R

×

R4

VOSS

The S/H current signals from power channel are injected to ADJ pin to establish the droop voltage. V

= R

X ∑2IX. The DAC output voltage decreased by V

ADJ

to generate the V

ADJ

load droop.

CORE

ADJ

f1

CoreControl

TM

Page 15 of 25 DS-CoreControl-TDA21302

Protection and SS Function

For OVP, the TDA21302 detects the VCORE by VDIF pin voltage that is the output of the differential

amplifier. This is to eliminate the delay caused by the compensation network for faster and more

accurate detection. The trip point of OVP is 140% of the normal V

are pulled low to turn on the Sync FET and to turn off the control FET while OVP is detected. The OVP

latch can only be reset by either VCC or DVD. The PGOOD trip point is set at the 92% of the normal

V

voltage level. The open drain PGOOD pin shall be pulled low while V

CORE

During the VID on the fly condition, there is nothing able to change the status of the PGOOD.

Soft-start circuit generates a ramp by charging an external capacitor with a 13uA constant current

source after the POR of IC is active. The pulse width of PWM signal and V

ramp to reduce the inrush current and protect the power devices.

Over-current protection trip point is internally set at around 100uA for each channel. OCP is triggered if

one channel S/H current signal. Controller forces PWM output latched at high impedance to turn off both

control and Sync FETs in the power stage and initial the hiccup mode protection. The SS pin voltage is

pulled low with a 13uA current after it is less than 90% VCC. The converter restarts after SS pin voltage

is lower than 0,2V. Three times of OCP disable the converter and only release the latch by POR acts.

voltage level. The PWM outputs

CORE

is lower than this point.

CORE

are clamped by rising

CORE

CH1 : V

CH2 : Short Circuit Current

CH3 : V

CH4 : V

ADJ

CORE

SS

CoreControl

TM

Page 16 of 25 DS-CoreControl-TDA21302

Design Process Suggestion :

Voltage Loop Setting

• Pole and Zero of output filter : Output inductor value, the capacitance and ESR value of the

output capacitors

• Compensation Network : Error amplifier compensation & sawtooth wave amplitude.

• Kelvin sense for V

Current Loop Setting

• GM amplifier S/H current setting : Current sensing components ( Rds(on) ), the value of the

resistors connecting to ISPx & ISNx. Do keep ISPx current < 60uA at full load condition for

better load line linearity.

• Over current protection trip point : This has been set internally and please keep ISPx < 100uA

at OCP condition for better accuracy.

VRM Load Line Setting

• Droop amplitude : External ADJ pin resistor.

• No load offset : Additional resistor in compensation network.

• DAC offset voltage seeting : VOSS pin & compensation network resistor.

PCB Layout

• Kelvin sense for current sense GM amplifier input.

• Refer to layout guide for other item.

CORE

CoreControl

TM

Page 17 of 25 DS-CoreControl-TDA21302

Design Example :

Given

Apply for four phase converter

= 12V

V

IN

V

= 1,35V

CORE

= 100A

I

LOAD

V

= 100 mV at full load

DROOP

OCP set at 35A for each channel ( S/H )

Rds(on) = 3 m for Sync FET at 25°C ( 2 X IPU06N03LA in parallel )

= 0,6uH

L

OUT

= 17,600 uH with 1 m ESR

C

OUT

1. Compensation Setting

•

Modulator Gain, Pole and Zero :

From the following formula ;

Modulator Gain = ( 12,46 dB )

Where V

: ramp amplitude of the sawtooth waveform

RAMP

LC Filter Pole = = 1,549 KHz and

ESR Zero = = 9,0429 KHz

2ESRC

• EA Compensation Network :

Select RF1 = 2,4 K , RF2 = 24 K , CC2 = 6,6 nF, C

scheme shown in Figure 5.

V

RAMP

V

π

×12LC

1

π

××OUT

=

1,9V

V12

×

2,4

=

3

IN

2

= 33 pF and Use type 2 compensation

C1

CoreControl

TM

Page 18 of 25 DS-CoreControl-TDA21302

Amp

V

DAC

lifier

+(1/SCC2)

Error

R

R

F1

VDIF

From the following formulas :

F

= = 1 KHz , FP = = 200 KHz

Z

π

Middle Band Gain = = 10 ( 20 dB )

The asymptotic bode plot of EA compensation and PWM loop gain is shown as below.

2R C

R

F2

1

F2 C1

××

R

C

C2

COMP FB

C

C1

π

2R

F2

F1

R

F2

Z

=

R

C1

1

C1 C2

CC

F2

××

C1 C2

C+C

(S

1

+

(SSC

+

×

)

F2C2

RC

C2C1

CC

+

)

CCR

C2C1F2

CoreControl

TM

Page 19 of 25 DS-CoreControl-TDA21302

×

2. Droop & DAC Offset Setting

For each channel the load current is 100A / 4 = 25A and the ripple current, IL , is given as

= 6,65 A

3,33 S 1

The load current, IL, at S/H is 25A - = 21,675 A.

1,35V 1,35V

××−

u

0,6uH 12V

∆I

2

Using the following formula to select the appropriate I

for the S/H of GM amplifier :

X(MAX)

I

X(MAX) =

R 21,675A

×DS(ON)

R

SP

The suggested I

uA. V

= 100 mV = 43,35 uA X 2 X 4 X R

DROOP

is in the range of 50 uA ± 5uA, select RSP = RSN = 1,5 K, then I

X

, therefore R

ADJ

= 287 .

ADJ

would be 43,35

X(MAX)

The R

junction temperature, the R

of MOSFET varies with temperature rise. When the Sync FETs are working at 100°C

DS(ON)

of MOSFET at 100°C is given as 7,3 m. So the R

DS(ON)

ADJ

at 100°C is

given as :

R

ADJ_100°C

X ( R

DS(ON)_25°C

/ R

DS(ON)_100°C

) = 236

3. Over Current Protection Setting

OCP trip point is internally set at around 100 uA of IX for each channel. As above selected RSP = RSN =

1,5 K, the OCP trip point is found using :

(OCP)

Ix = 100uA

RI 3mI

×Ω×

DS(ON) L(TRIP) L(TRIP)

SP

R1,5K

==

Ω

4. Soft-start Capacitor Selection

CSS = 100 nF is the suitable value for most application.

××⇒

It= VC C=

SS SS SS SS SS

SS SS SS

I = 13 uA , V = 2V , t = 10 mS

SS

C = 65 nF

SS SS

It

V

SS

CoreControl

TM

Page 20 of 25 DS-CoreControl-TDA21302

Layout Guide :

Place the high-power switching components first, and separate them from the sensitive nodes.

1. Most Critical Path :

The current sense circuit is the most sensitive part of the converter. The current sense resistor

tied to ISP1,2,3,4 and ISN1,2,3,4 should be located not more than 0,5 inch from the IC and

away from the noise switching nodes. The PCB trace of sense nodes should be parallel and as

short as possible. Kelvin connection of the sense component, additional current sense resistor

or the R

of MOSFETs, ensures the accurate and stable current sensing signals.

DS(ON)

DPAK or

2

D

PAK

2. Switching Ripple Path :

• The best connection of the input capacitors is to place at the drain of the high side MOSFET

and the source of the low side MOSFET.

• Low side MOSFET to the output capacitor.

• The return path of input and output capacitor.

• Separate the power and signal GND.

• The PHASE node, the conjunction of the high / low side MOSFETs and inductor, is the

nosiy node. Keep them away from the sensitive small-signal node.

• Reducing the parasitic impedance and inductance is done by minimizing the length of the

traces, offering enough copper area and avoiding the vias.

CoreControl

TM

IPAK

Page 21 of 25 DS-CoreControl-TDA21302

3. MOSFET drivers :

• Both of the decoupling capacitors for VCC and PVCC should be placed as close to the driver IC

as possible.

• The bootstrap capacitor should be placed close to the

• The traces of

GATE

and PHASE should be routed in parallel and to keep it short and wide.

HS

BOOT pin.

The width of the trances should be no less than 40mils.

• High current loops from the input capacitor, high side MOSFET, output inductors and output

capacitors back to the input capacitor negative terminal should be kept the distance minimized.

• The conjunction of high side MOSFET, low side MOSFET and output inductor should be kept as

close as possible.

4. Other Path :

• The components from the compensation network, high frequency bypass capacitors and the

setting resistors should be placed near controller IC and away from the noisy power path.

• The thermal compensation thermistor should be placed at the hottest point which is

normally the MOSFETs located at the inner part of the power stage.

CoreControl

TM

Page 22 of 25 DS-CoreControl-TDA21302

Outline Dimension :

CoreControl

TM

Page 23 of 25 DS-CoreControl-TDA21302

@

Revision History

Datasheet DS-CoreControl-TDA21302

Actual Release: V1.2 Date: 10.04.2004 Previous Release: V1.1 Date: 10.01.04

Page of

actual Rel.

17 17

10 10

Page of

prev. Rel.

Subjects changed since last release

C

= 6,6 nF, C

C1

= 33 pF => C

C2

= 6,6 nF, C

C2

= 33 pF

C1

VID table correction VID4 1Æ 0 from 1,0375V to 1,0875v

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in

Germany or the Infineon Technologies Companies and Representatives worldwide: see the address list

on the last page or our webpage at

http://www.infineon.com/DCDC

OptiMOS

We listen to Your Comments

Any information within this dokument that you feel is wrong, unclear or missing at all?

Your feedback will help us to continously improve the quality of this dokument.

Please send your proposal (including a reference to this dokument) to:

mcdoku.comment

Edition 2004-01-10

Published by Infineon Technologies AG,

St.-Martin-Strasse 53,

D-81541 München

© Infineon Technologies AG 2004.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts

stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please conta ct your nearest Infineon Technologies Office in Germany

or our Infineon Technologies Representatives worldwide (see address list).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest

Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies,

if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or

effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or

maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be

endangered.

and OptiMOS II are trademarks of Infineon Technologies AG.

infineon.com

CoreControl

TM

Page 24 of 25 DS-CoreControl-TDA21302

Infineon Technologies AG sales offices worldwide – partly represented by Siemens AG

A

Siemens AG Österreich

Erdberger Lände 26

A-1031 Wien

T (+43)1-17 07-3 56 11

Fax (+43)1-17 07-5 59 73

AUS

Siemens Ltd.

885 Mountain Highway

Bayswater,Victoria 3153

T (+61)3-97 21 21 11

Fax (+61)3-97 21 72 75

B

Siemens Electronic Components

Benelux

Charleroisesteenweg 116/

Chaussée de Charleroi 116

B-1060 Brussel/Bruxelles

T (+32)2-5 36 69 05

Fax (+32)2-5 36 28 57

Email:components@siemens.nl

BR

Siemens Ltda.

Semiconductores

Avenida Mutinga,3800-Pirituba

05110-901 São Paulo-SP

T (+55)11-39 08 25 64

Fax (+55)11-39 08 27 28

CDN

Infineon Technologies Corporation

320 March Road,Suite 604

Canada,Ontario K2K 2E2

T (+1)6 13-5 91 63 86

Fax (+1)6 13-5 91 63 89

CH

Siemens Schweiz AG

Bauelemente

Freilagerstrasse 40

CH-8047 Zürich

T (+41)1-4 953065

Fax (+41)1-4 955050

D

Infineon Technologies AG

Völklinger Str.2

D-40219 Düsseldorf

T (+49)2 11-3 99 29 30

Fax (+49)2 11-3 99 14 81

Infineon Technologies AG

Werner-von-Siemens-Platz 1

D-30880 Laatzen (Hannover)

T (+49)5 11-8 77 22 22

Fax (+49)5 11-8 77 15 20

Infineon Technologies AG

Von-der-Tann-Straße 30

D-90439 Nürnberg

T (+49)9 11-6 54 76 99

Fax (+49)9 11-6 54 76 24

Infineon Technologies AG

Weissacher Straße 11

D-70499 Stuttgart

T (+49)7 11-1 37 33 14

Fax (+49)7 11-1 37 24 48

D

Infineon Technologies AG

Halbleiter Distribution

Richard-Strauss-Straße 76

D-81679 München

T (+49)89-92 21 40 86

Fax (+49)89-92 21 20 71

DK

Siemens A/S

Borupvang 3

DK-2750 Ballerup

T (+45)44 77-44 77

Fax (+45)44 77-40 17

E

Siemens S.A.

Dpto.Componentes

Ronda de Europa,5

E-28760 Tres Cantos-Madrid

T (+34)91-5 14 71 51

Fax (+34)91-5 14 70 13

F

Infineon Technologies France,

39/47,Bd.Ornano

F-93527 Saint-Denis CEDEX2

T (+33)1-49 22 31 00

Fax (+33)1-49 22 28 01

FIN

Siemens Components

Scandinavia

P.O .Bo x 6 0

FIN-02601 Espoo (Helsinki)

T (+3 58)10-5 11 51 51

Fax (+3 58)10-5 11 24 95

Email:

scs@components.siemens.se

GB

Infineon Technologies

Siemens House

Oldbury

GB-Bracknell,Berkshire

RG12 8FZ

T (+44)13 44-39 66 18

Fax (+44)13 44-39 66 32

H

Simacomp Kft.

Lajos u.103

H-1036 Budapest

T (+36)1-4 57 16 90

Fax (+36)1-4 57 16 92

HK

Infineon Technologies

Hong Kong Ltd.

Suite 302,Level 3,

Festival Walk,

80 Tat Chee Avenue,

Yam Yat Tsuen,

Kowloon Tong

Hong Kong

T (+8 52)28 32 05 00

Fax (+8 52)28 27 97 62

I

Siemens S..A.

Semiconductor Sales

Via Piero e Alberto Pirelli,10

I-20126 Milano

T (+39)02-66 76 -1

Fax (+39)02-66 76 43 95

IND

Siemens Ltd.

Components Division

No.84 Keonics Electronic City

Hosur Road

Bangalore 561 229

T (+91)80-8 52 11 22

Fax (+91)80-8 52 11 80

Siemens Ltd.

CMP Div,5th Floor

4A Ring Road,IP Estate

New Delhi 110 002

T (+91)11-3 31 99 12

Fax (+91)11-3 31 96 04

Siemens Ltd.

CMP Div,4th Floor

130,Pandurang Budhkar Marg,

Worli

Mumbai 400 018

T (+91)22-4 96 21 99

Fax (+91)22-4 96 22 01

IRL

Siemens Ltd.

Electronic Components Division

8,Raglan Road

IRL-Dublin 4

T (+3 53)1-2 16 23 42

Fax (+3 53)1-2 16 23 49

IL

Nisko Ltd.

2A,Habarzel St.

P.O.Box 58151

61580 Tel Aviv –Isreal

T (+9 72)3 -7 65 73 00

Fax (+9 72)3 -7 65 73 33

J

Siemens Components K.K.

Talanawa Park Tower 12F &17F

3-20-14,Higashi-Gotanda,

Shinagawa-ku

Tokyo

T (+81)3-54 49 64 11

Fax (+81)3 -54 49 64 01

MAL

Infineon Technologies AG

Sdn Bhd

Bayan Lepas Free Industrial Zone1

11900 Penang

T (+60)4 -6 44 99 75

Fax (+60)4 -6 41 48 72

N

Siemens Components

Scandinavia

Østre Aker vei 24

Postboks 10,Veitvet

N-0518 Oslo

T (+47)22-63 30 00

Fax (+47)22-68 49 13

Email:

scs@components.siemens.se

NL

Siemens Electronic Components

Benelux

Postbus 16068

NL-2500 BB Den Haag

T (+31)70-3 33 20 65

Fax (+31)70-3 33 28 15

Email:components@siemens.nl

NZ

Siemens Auckland

300 Great South Road

Greenland

Auckland

T (+64)9-5 20 30 33

Fax (+64)9-5 20 15 56

P

Siemens S.A.

an Componentes Electronicos

R.Irmaos Siemens,1

Alfragide

P-2720-093 Amadora

T (+351)1-4 17 85 90

Fax (+351)1-4 17 80 83

PK

Siemens Pakistan Engineering

Co.Ltd.

PO Box 1129,Islamabad 44000

23 West Jinnah Ave

Islamabad

T (+92)51-21 22 00

Fax (+92)51-21 16 10

PL

Siemens SP.z.o.o.

ul.Zupnicza 11

PL-03-821 Warszawa

T (+48)22-8 70 91 50

Fax (+48)22-8 70 91 59

ROK

Siemens Ltd.

Asia Tower,10th Floor

726 Yeoksam-dong,Kang-nam Ku

CPO Box 3001

Seoul 135-080

T (+82)2-5 27 77 00

Fax (+82)2-5 27 77 79

RUS

INTECH electronics

ul.Smolnaya,24/1203

RUS-125 445 Moskva

T (+7)0 95 -4 51 97 37

Fax (+7)0 95 -4 51 86 08

S

Siemens Components Scandinavia

Österögatan 1,Box 46

S-164 93 Kista

T (+46)8-7 03 35 00

Fax (+46)8-7 03 35 01

Email:

scs@components.siemens.se

ROC

Infineon Technologies

Taiwan.Ltd.

12F-1, No.3-2 Yuan Qu. St., Nan

Kang Software Park, Taipei, 115

T (+8 86)2-2655 7500

Fax (+8 86)2-2655 7501

SGP

Infineon Technologies Asia

Pacific,Pte.Ltd.

168 Kallang Way

Singapore 349 253

T (+65)8 40 06 10

Fax (+65)7 42 62 39

USA

Infineon Technologies Corporation

1730 North First Street

San Jose,CA 95112

T (+1)4 08-5 01 60 00

Fax (+1)4 08-5 01 24 24

Siemens Components,Inc.

Optoelectronics Division

19000 Homestead Road

Cupertino,CA 95014

T (+1)4 08-2 57 79 10

Fax (+1)4 08-7 25 34 39

Siemens Components,Inc.

Special Products Division

186 Wood Avenue South

Iselin,NJ 08830-2770

T (+1)7 32-9 06 43 00

Fax (+1)7 32-6 32 28 30

VRC

Infineon Technologies

Hong Kong Ltd.

Beijing Office

Room 2106,Building A

Vantone New World Plaza

No.2 Fu Cheng Men Wai Da Jie

Jie

100037 Beijing

T (+86)10 -68 57 90 -06,-07

Fax (+86)10 -68 57 90 08

Infineon Technologies

Hong Kong Ltd.

Chengdu Office

Room14J1,Jinyang Mansion

58 Tidu Street

Chengdu,

Sichuan Province 610 016

T (+86)28-6 61 54 46 /79 51

Fax (+86)28 -6 61 01 59

Infineon Technologies

Hong Kong Ltd.

Shanghai Office

Room1101,Lucky Target Square

No.500 Chengdu Road North

Shanghai 200003

T (+86)21-63 6126 18 /19

Fax (+86)21-63 61 11 67

Infineon Technologies

Hong Kong Ltd.

Shenzhen Office

Room 1502,Block A

Tian An International Building

Renim South Road

Shenzhen 518 005

T (+86)7 55 -2 28 91 04

Fax (+86)7 55-2 28 02 17

ZA

Siemens Ltd.

Components Division

P.O.B.3438

Halfway House 1685

T (+27)11-6 52 -27 02

Fax (+27)11-6 52 20 42

CoreControl

TM

Page 25 of 25 DS-CoreControl-TDA21302

Loading...

Loading...