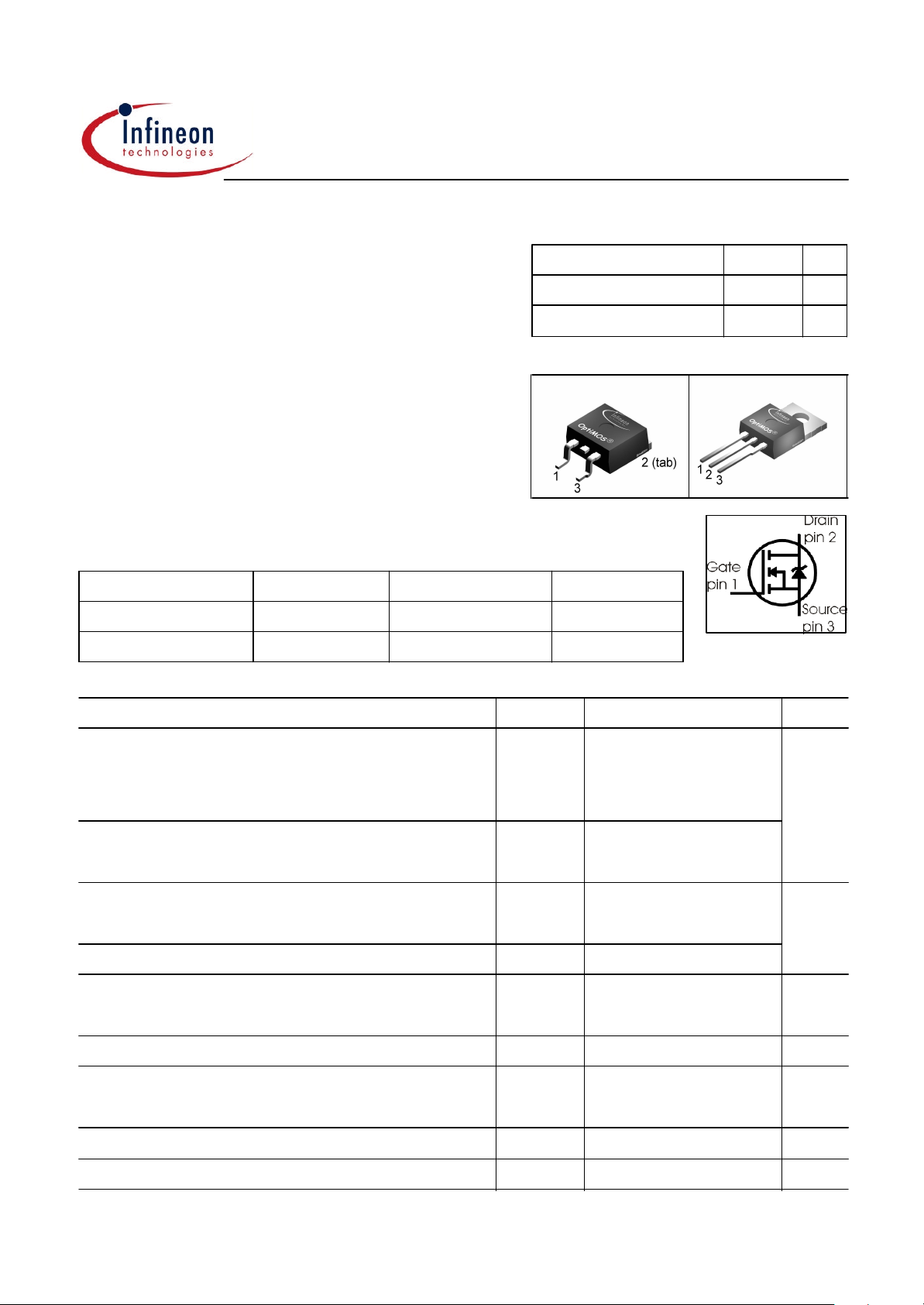

SPP80N08S2L-07

SPB80N08S2L-07

OptiMOS Power-Transistor

j

stg

Feature

• N-Channel

• Enhancement mode

• Logic Level

• 175°C operating temperature

• Avalanche rated

• dv/dt rated

Product Summary

V

DS

R

DS(on)

I

D

P- TO263 -3-2 P- TO220 -3-1

max. SMD version 6.8 mΩ

75 V

80 A

Type Package Ordering Code

SPP80N08S2L-07 P- TO220 -3-1 Q67060-S6015

SPB80N08S2L-07 P- TO263 -3-2 Q67060-S6016

Marking

2N08L07

2N08L07

Maximum Ratings, at Tj = 25 °C, unless otherwise specified

Parameter Symbol Value Unit

Continuous drain current

TC=25°C

1)

I

D

80

A

80

Pulsed drain current

TC=25°C

Avalanche energy, single pulse

ID=80 A , VDD=25V, RGS=25Ω

Repetitive avalanche energy, limited by T

Reverse diode dv/dt

IS=80A, VDS=60V, di/dt=200A/µs, T

jmax

=175°C

jmax

I

D puls

E

AS

2)

E

AR

dv/dt 6 kV/µs

320

810 mJ

30

Gate source voltage V

Power dissipation

TC=25°C

Operating and storage temperature T

IEC climatic category; DIN IEC 68-1

Page 1

P

GS

tot

, T

±20

300 W

-55... +175

55/175/56

V

°C

2003-05-09

SPP80N08S2L-07

SPB80N08S2L-07

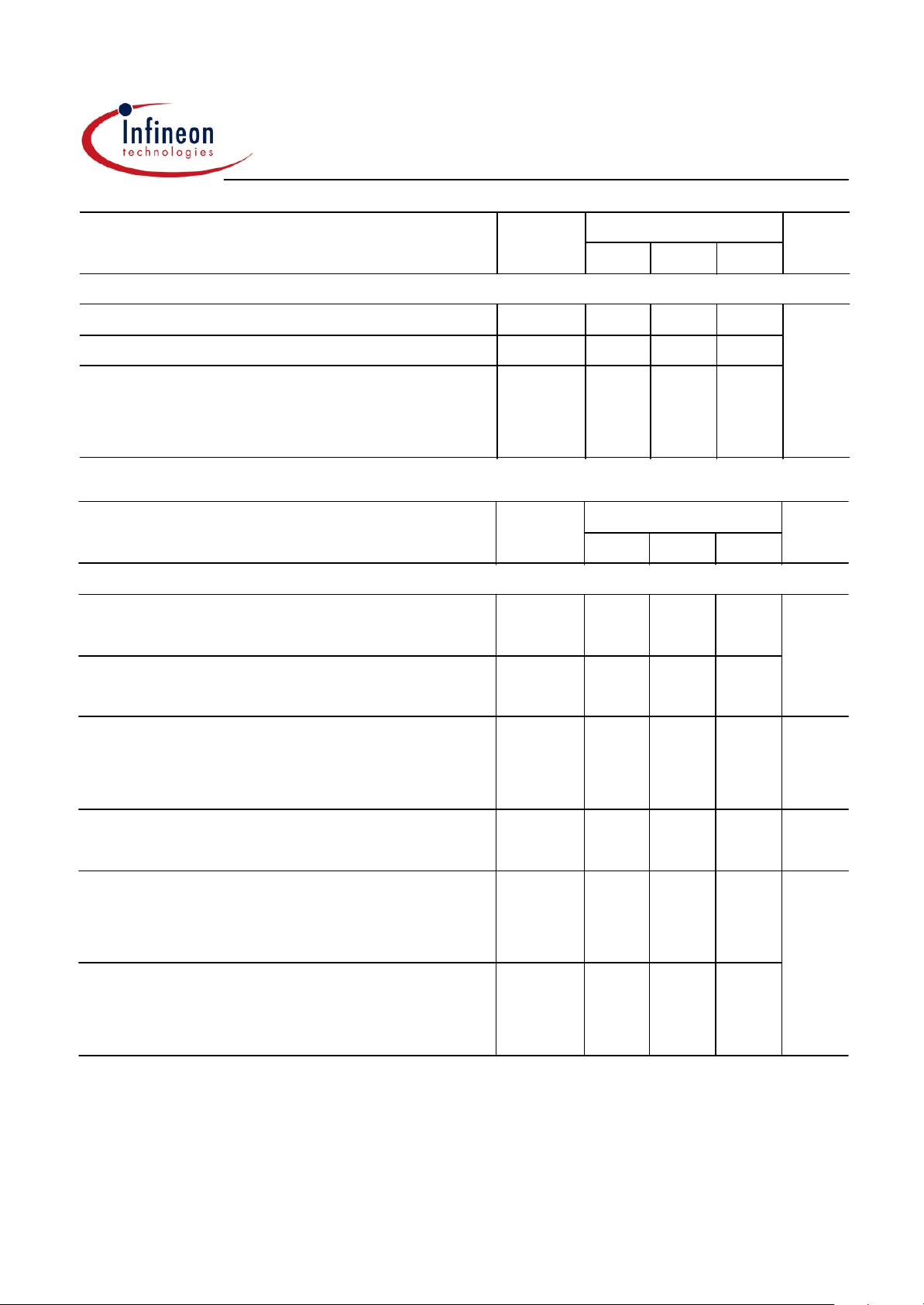

Thermal Characteristics

Parameter Symbol Values Unit

min. typ. max.

Characteristics

Thermal resistance, junction - case

Thermal resistance, junction - ambient, leaded

SMD version, device on PCB:

@ min. footprint

@ 6 cm2 cooling area

3)

R

R

R

thJC

thJA

thJA

- 0.3 0.5 K/W

- - 62

-

-

-

-

62

40

Electrical Characteristics, at Tj = 25 °C, unless otherwise specified

Parameter Symbol Values Unit

min. typ. max.

Static Characteristics

Drain-source breakdown voltage

VGS=0V, ID=1mA

Gate threshold voltage, VGS = V

ID=250µA

Zero gate voltage drain current

VDS=75V, VGS=0V, Tj=25°C

DS

V

(BR)DSS

V

GS(th)

I

DSS

75 - - V

1.2 1.6 2

-

0.01

1

µA

VDS=75V, VGS=0V, Tj=125°C

Gate-source leakage current

VGS=20V, VDS=0V

Drain-source on-state resistance

VGS=4.5V, ID=67A

VGS=4.5V, ID=67A, SMD version

Drain-source on-state resistance

VGS=10V, ID=67A

VGS=10V, ID=67A, SMD version

1

Current limited by bondwire ; with an R

information see app.-note ANPS071E available at www.infineon.com/optimos

2

Defined by design. Not subject to production test.

3

Device on 40mm*40mm*1.5mm epoxy PCB FR4 with 6cm² (one layer, 70 µm thick) copper area for drain

connection. PCB is vertical without blown air.

4

Diagrams are related to straight lead versions

2)

I

GSS

R

DS(on)

4)

= 0.5K/W the chip is able to carry ID= 135A at 25°C, for detailed

thJC

R

DS(on)

-

1

100

- 1 100 nA

-

-

-

-

6.5

6.2

5.3

5

9

8.7

7.1

6.8

mΩ

Page 2

2003-05-09

SPP80N08S2L-07

SPB80N08S2L-07

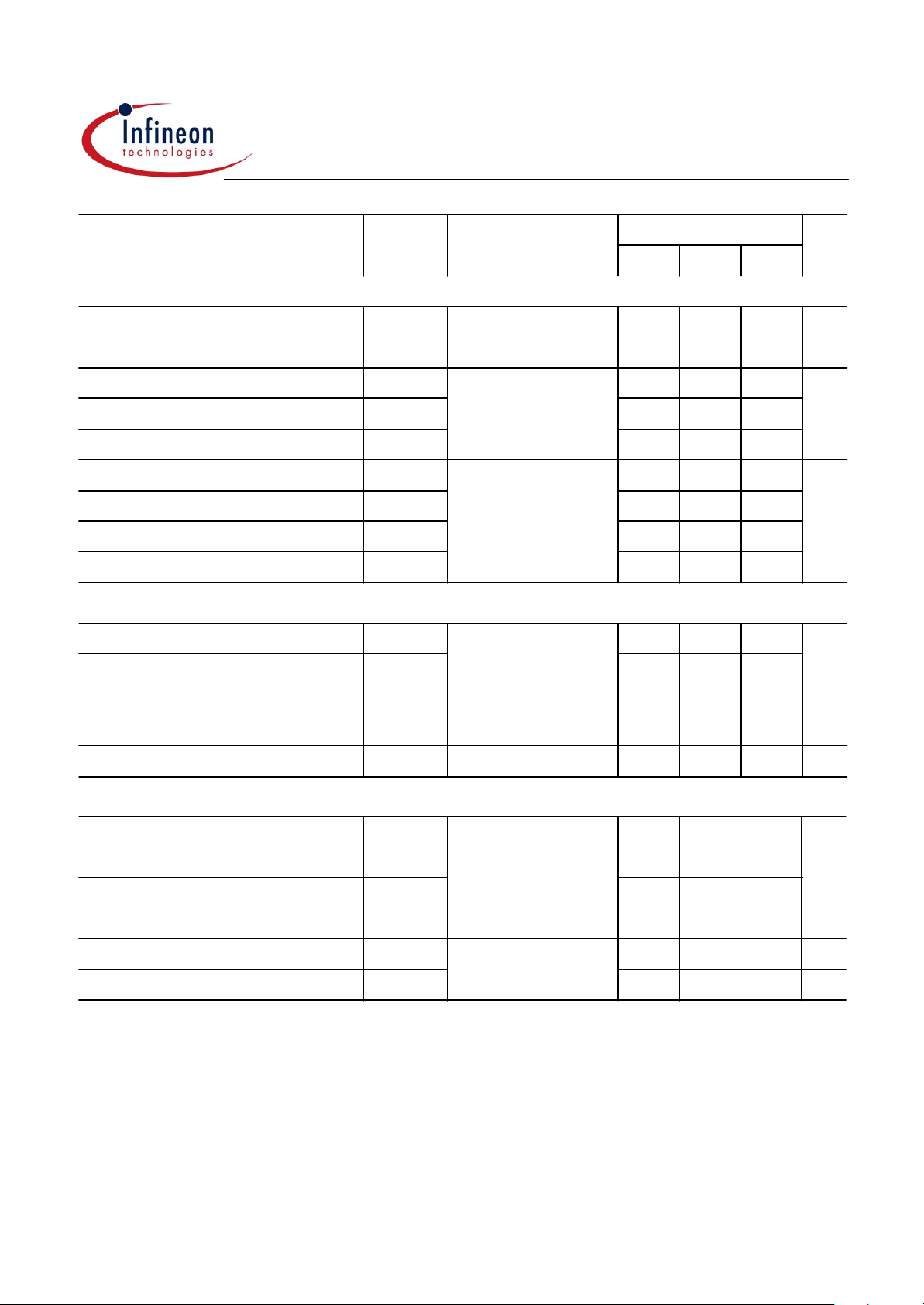

Electrical Characteristics

Parameter Symbol Conditions Values Unit

min. typ. max.

Dynamic Characteristics

Transconductance g

Input capacitance C

Output capacitance C

Reverse transfer capacitance C

Turn-on delay time t

Rise time t

Turn-off delay time t

Fall time t

Gate Charge Characteristics

Gate to source charge Q

Gate to drain charge Q

Gate charge total Q

Gate plateau voltage V

fs

iss

oss

rss

d(on)

r

d(off)

f

gs

gd

g

(plateau)

VDS≥2*ID*R

ID=80A

VGS=0V, VDS=25V,

f=1MHz

DS(on)max

,

74 148 - S

- 5130 6820 pF

- 993 1320

- 415 620

VDD=40V, VGS=10V,

ID=80A,

RG=1.1Ω

- 25 38 ns

- 81 122

- 76 114

- 78 117

VDD=60V, ID=80A - 18 23 nC

- 66 83

VDD=60V, ID=80A,

VGS=0 to 10V

VDD=60V, ID=80A - 3.3 - V

- 186 233

Reverse Diode

Inverse diode continuous

I

forward current

Inv. diode direct current, pulsed

I

Inverse diode forward voltage V

Reverse recovery time t

Reverse recovery charge Q

S

SM

SD

rr

rr

TC=25°C - - 80 A

- - 320

VGS=0V, IF=80A - 0.9 1.3 V

VR=40V, I

diF/dt=100A/µs

Page 3

F=lS

,

- 81 100 ns

- 197 250 nC

2003-05-09

SPP80N08S2L-07

SPB80N08S2L-07

1 Power dissipation

P

= f (TC)

tot

2 Drain current

ID = f (TC)

parameter: VGS≥ 4 V

SPP80N08S2L-07

320

W

240

tot

200

P

160

120

80

40

0

0 20 40 60 80 100 120 140 160°C190

parameter: VGS≥ 10 V

SPP80N08S2L-07

90

A

70

60

D

I

50

40

30

20

10

0

0 20 40 60 80 100 120 140 160°C 190

T

C

T

C

3 Safe operating area

ID = f ( VDS )

parameter : D = 0.01 , TC = 25 °C

3

SPP80N08S2L-07

10

A

D

I

DS(on)

=

10

/

DS

V

0

10

2

10

D

I

R

1

10

0

10

-1

10

4 Max. transient thermal impedance

Z

= f (tp)

thJC

parameter : D = tp/T

1

SPP80N08S2L-07

10

K/W

t

= 3.7µs

p

0

10

10 µs

thJC

-1

10

100 µs

1 ms

1

V

V

DS

10

2

Z

D = 0.50

0.20

0.10

0.05

0.02

0.01

-3

10

-2

t

0

s

10

p

10

10

10

-2

-3

-4

10

single pulse

-7

10

-6

-5

10

-4

10

10

Page 4

2003-05-09

SPP80N08S2L-07

SPB80N08S2L-07

5 Typ. output characteristic

6 Typ. drain-source on resistance

ID = f (VDS); Tj=25°C

parameter: tp = 80 µs

SPP80N08S2L-07

190

Ptot = 300W

A

g

h

160

140

120

D

I

100

80

60

40

20

0

0 0.5 1 1.5 2 2.5 3 3.5 4

i

VGS [V]

f

e

d

c

b

a

a 2.8

b 3.0

c 3.3

d 3.5

e 3.8

f 4.0

g 4.3

h 4.5

i 10.0

V

V

DS

R

parameter: V

DS(on)

24

= f (ID)

GS

SPP80N08S2L-07

m Ω

c

20

18

16

DS(on)

R

14

12

10

8

6

4

VGS [V] =

c

2

5

0

d

3.3

3.5

3.8

0 20 40 60 80 100 120 140

d

e

f

g

4.0

h

4.3

4.5

10.0

e

i

f

g

h

i

A

180

I

D

7 Typ. transfer characteristics

ID= f ( VGS ); VDS≥ 2 x ID x R

DS(on)max

parameter: tp = 80 µs

160

A

120

D

100

I

80

60

40

20

0

0 0.5 1 1.5 2 2.5 3 3.5

V

DS

V

4.5

8 Typ. forward transconductance

gfs = f(ID); Tj=25°C

parameter: g

170

S

140

120

fs

g

100

80

60

40

20

0

0 20 40 60 80 100 120 A 160

fs

I

D

Page 5

2003-05-09

SPP80N08S2L-07

SPB80N08S2L-07

9 Drain-source on-state resistance

10 Typ. gate threshold voltage

R

DS(on)

= f (Tj)

parameter : ID = 67 A, VGS = 10 V

SPP80N08S2L-07

28

mΩ

24

22

20

DS(on)

18

R

16

14

12

10

8

6

4

2

0

-60 -20 20 60 100 140

98%

typ

°C

V

parameter: VGS = V

GS(th)

2.5

= f (Tj)

DS

V

GS(th)

V

1.5

1.25mA

250µA

1

0.5

200

T

j

0

-60 -20 20 60 100

°C

180

T

j

11 Typ. capacitances

C = f (VDS)

parameter: VGS=0V, f=1 MHz

5

10

pF

4

10

C

C

3

10

2

10

0 5 10 15 20 V 30

iss

C

oss

C

rss

V

DS

12 Forward character. of reverse diode

IF = f (VSD)

parameter: Tj , tp = 80 µs

3

SPP80N08S2L-07

10

A

2

10

F

I

1

10

Tj = 25 °C typ

Tj = 175 °C typ

Tj = 25 °C (98%)

Tj = 175 °C (98%)

0

10

0 0.4 0.8 1.2 1.6 2 2.4

V

V

SD

3

Page 6

2003-05-09

SPP80N08S2L-07

SPB80N08S2L-07

13 Typ. avalanche energy

14 Typ. gate charge

EAS = f (Tj)

par.: ID = 80 A , VDD = 25 V, RGS = 25 Ω

850

mJ

700

600

AS

E

500

400

300

200

100

0

25 45 65 85 105 125 145 °C 185

T

V

GS

= f (Q

Gate

)

parameter: ID = 80 A pulsed

SPP80N08S2L-07

16

V

12

GS

10

V

8

6

4

2

0

0 40 80 120 160 200 240

j

V0,2

DS max

0,8 V

DS max

nC

Q

300

Gate

15 Drain-source breakdown voltage

V

(BR)DSS

= f (Tj)

parameter: ID=10 mA

SPP80N08S2L-07

92

V

88

86

84

(BR)DSS

V

82

80

78

76

74

72

70

68

-60 -20 20 60 100 140

°C

200

T

j

Page 7

2003-05-09

SPP80N08S2L-07

SPB80N08S2L-07

Published by

Infineon Technologies AG ,

Bereichs Kommunikation

St.-Martin-Strasse 53,

D-81541 München

© Infineon Technologies AG 1999

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement,

regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or our Infineon Technologies Reprensatives worldwide (see address list).

Warnings

Due to technical requirements components may contain dangerous substances.

For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express

written approval of Infineon Technologies, if a failure of such components can reasonably be expected to

cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device

or system Life support devices or systems are intended to be implanted in the human body, or to support

and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health

of the user or other persons may be endangered.

Further information

Please notice that the part number is BSPP80N08S2L-07 and BSPB80N08S2L-07, for simplicity the device is referred

to by the term SPP80N08S2L-07 and SPB80N08S2L-07 throughout this documentation.

Page 8

2003-05-09

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Loading...

Loading...