SPD30N08S2L-21

j

j

g

OptiMOS

â

Power-Transistor

Feature

• N-Channel

• Enhancement mode

• Logic Level

• 175°C operating temperature

• Avalanche rated

• dv/dt rated

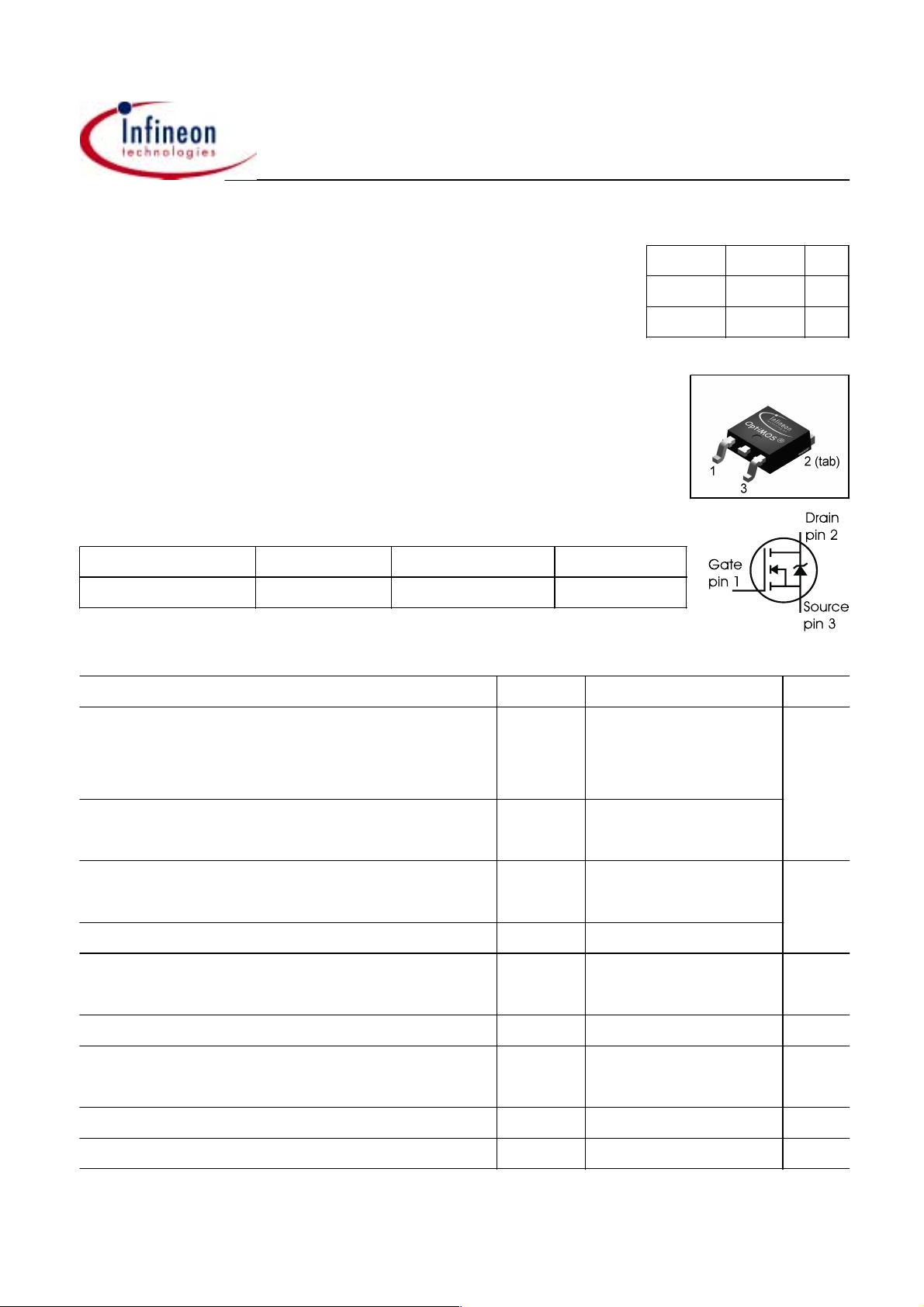

Type Package Ordering Code

SPD30N08S2L-21 P- TO252 -3-11 Q67060-S7414

Marking

2N08L21

Product Summary

V

DS

R

DS(on)

I

D

P- TO252 -3-11

75 V

20.5 mΩ

30 A

Maximum Ratings, at Tj = 25 °C, unless otherwise specified

Parameter

Continuous drain current

T

=25°C

C

T

=100°C

C

1)

Pulsed drain current

T

=25°C

C

Avalanche energy, single pulse

I

=30 A , VDD=25V, RGS=25Ω

D

Repetitive avalanche energy, limited by T

max

Reverse diode dv/dt

I

=30A, VDS=60V, di/dt=200A/µs, T

S

jmax

=175°C

Gate source voltage V

Power dissipation

T

=25°C

C

Operating and storage temperature T

Symbol Value Unit

I

D

30

30

I

D puls

E

AS

2)

E

AR

dv/dt

GS

P

tot

T

,

st

120

240 mJ

14

6 kV/µs

±20

136 W

-55... +175

IEC climatic category; DIN IEC 68-1 55/175/56

A

V

°C

Page 1

2002-06-17

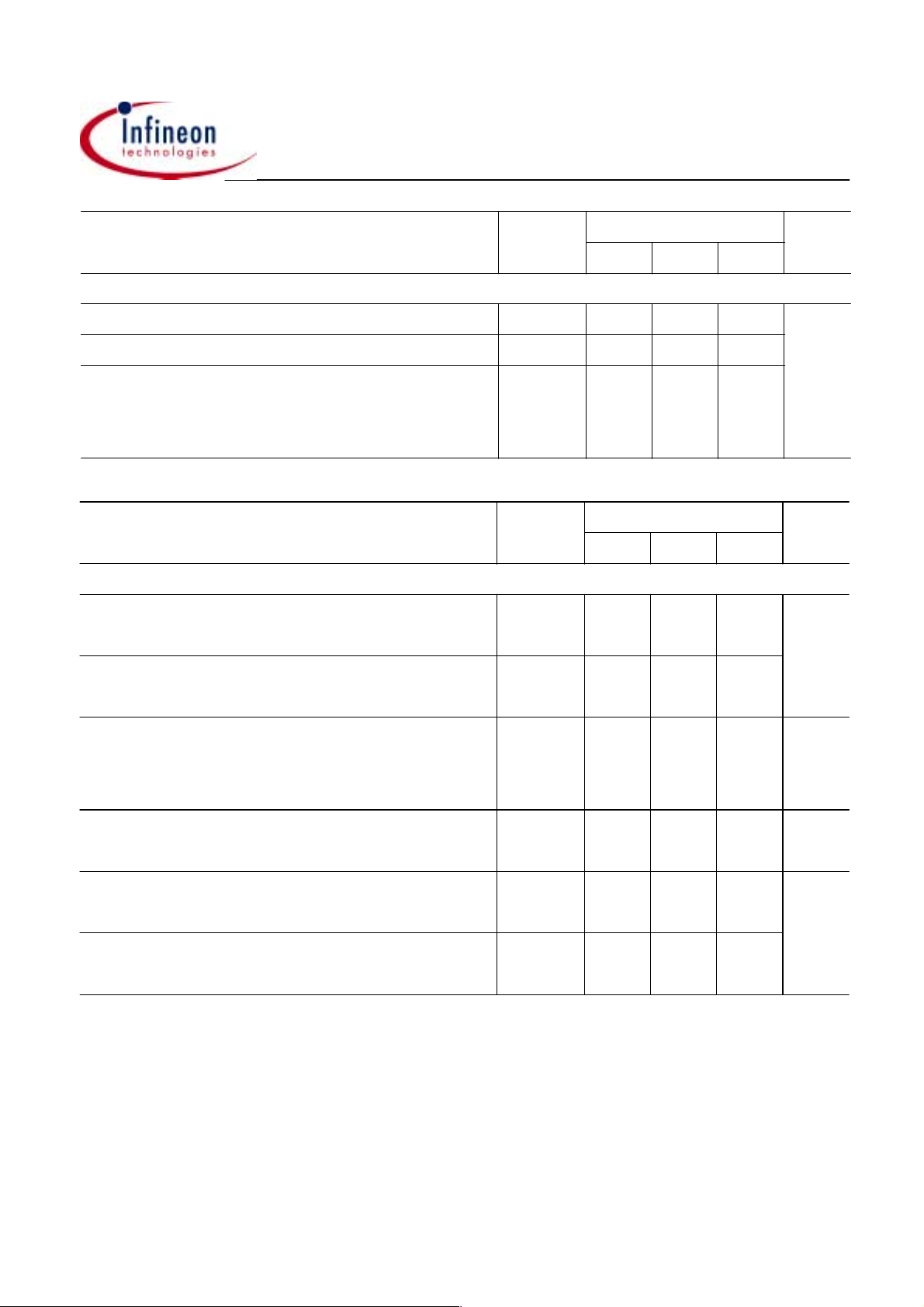

Thermal Characteristics

A

SPD30N08S2L-21

Parameter

Symbol Values Unit

min. typ. max.

Characteristics

Thermal resistance, junction - case R

Thermal resistance, junction - ambient, leaded R

SMD version, device on PCB:

@ min. footprint

@ 6 cm

2

cooling area

3)

R

thJC

thJ

thJA

- 0.7 1.1 K/W

- - 100

-

-

Electrical Characteristics, at Tj = 25 °C, unless otherwise specified

Parameter

Symbol Values Unit

min. typ. max.

Static Characteristics

Drain-source breakdown voltage

VGS=0V, ID=1mA

Gate threshold voltage, VGS = V

I

=80µA

D

Zero gate voltage drain current

VDS=75V, VGS=0V, Tj=25°C

DS

V

(BR)DSS

V

GS(th)

I

DSS

75 - - V

1.2 1.6 2

-

-

-

0.01

75

50

1

µA

=75V, VGS=0V, Tj=125°C

V

DS

Gate-source leakage current

VGS=20V, VDS=0V

Drain-source on-state resistance

VGS=4.5V, ID=25A

Drain-source on-state resistance

VGS=10V, ID=25A

1

Current limited by bondwire ; with an R

information see app.-note ANPS071E available at www.infineon.com/optimos

2

Defined by design. Not subject to production test.

3

Device on 40mm*40mm*1.5mm epoxy PCB FR4 with 6cm² (one layer, 70 µm thick) copper area for drain

connection. PCB is vertical without blown air.

= 1.1K/W the chip is able to carry ID= 54A at 25°C, for detailed

thJC

I

GSS

R

DS(on)

R

DS(on)

-

- 1 100 nA

- 19.1 26

- 15.3 20.5

1

100

mΩ

Page 2

2002-06-17

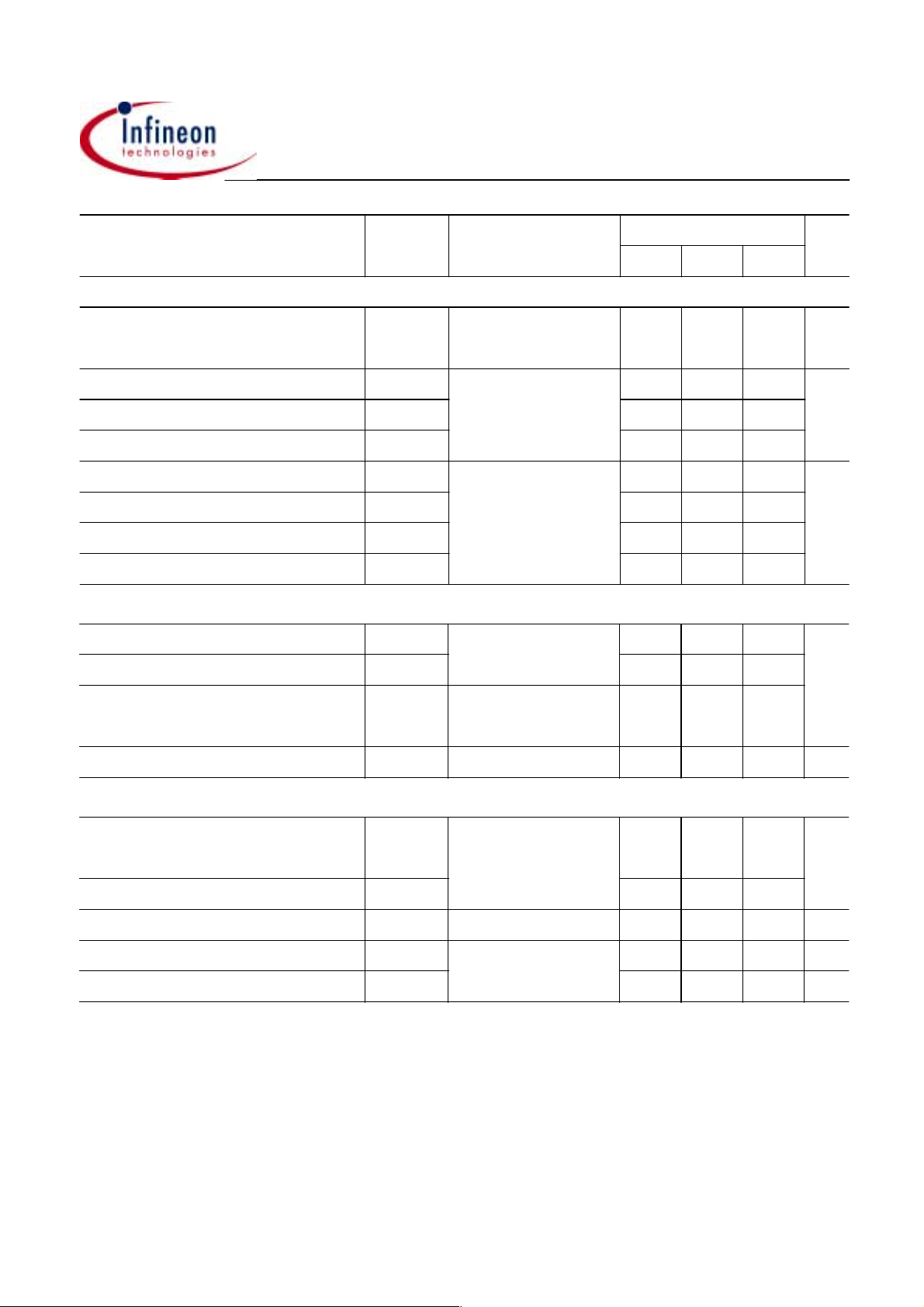

Electrical Characteristics

SPD30N08S2L-21

Parameter

Dynamic Characteristics

Transconductance g

Input capacitance C

Output capacitance C

Reverse transfer capacitance C

Turn-on delay time t

Rise time t

Turn-off delay time t

Fall time t

Gate Charge Characteristics

Gate to source charge

Q

Gate to drain charge Q

Gate charge total Q

Symbol Conditions Values Unit

min. typ. max.

fs

iss

oss

rss

d(on)

r

d(off)

f

gs

gd

g

VDS≥2*ID*R

I

=30A

D

VGS=0V, VDS=25V,

f=1MHz

VDD=40V, VGS=4.5V,

=30A,

I

D

R

=3.9Ω

G

VDD=60V, ID=30A - 5.1 6.8 nC

VDD=60V, ID=30A,

=0 to 10V

V

GS

DS(on)max

,

23 45 - S

- 1600 2130 pF

- 320 425

- 130 200

- 11 16 ns

- 15 24

- 21 30

- 15 23

- 21 32

- 54 72

Gate plateau voltage V

Reverse Diode

Inverse diode continuous

I

forward current

Inv. diode direct current, pulsed I

Inverse diode forward voltage V

Reverse recovery time t

Reverse recovery charge Q

(plateau)

S

SM

SD

rr

rr

VDD=60V, ID=30A - 3.4 - V

TC=25°C - - 30 A

- - 120

VGS=0V, IF=30A - 0.9 1.3 V

VR=40V, I

di

/dt=100A/µs

F

lS,

=

F

- 52 65 ns

- 122 153 nC

Page 3

2002-06-17

Loading...

Loading...