Page 1

ICE Module

ICE Module Carrier Board Design Guide

Page i

Page 2

Date Version Changes

2008-09 1.00 Initial release

ICE Module

Revision

Page ii

Page 3

ICE Module

COPYRIGHT NOTICE

The information in this document is subject to change without prior notice in order to

improve reliability, design and function and does not represent a commitment on the

part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or

consequential damages arising out of the use or inability to use the product or

documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are

Copyright

reserved. No part of this manual may be reproduced by any mechanical, electronic, or

other means in any form without prior written permission of the manufacturer.

TRADEMARKS

All registered trademarks and product names mentioned herein are used for

identification purposes only and may be trademarks and/or registered trademarks of

their respective owners.

Page iii

Page 4

ICE Module

Table of Contents

1 INTRODUCTION.....................................................................................................1

1.1 INTRODUCTION .....................................................................................................2

1.2 ACRONYMS AND ABBREVIATIONS DEFINITION .....................................................2

1.3 REFERENCE DOCUMENTS......................................................................................4

2 ICE MODULE OVERVIEW...................................................................................5

2.1 CHAPTER OVERVIEW.............................................................................................6

2.2 ICE SPECIFICATIONS.............................................................................................7

2.2.1 ICE-9152-R10...............................................................................................8

2.2.2 ICE-9102-1GZ-R10.....................................................................................10

2.2.3 ICE-9102-1G512-R10.................................................................................12

2.2.4 ICE-ATOM-R10..........................................................................................14

2.2.5 ICE-GM45A-R10 ........................................................................................16

2.2.6 ICE-DB-9S-R10 ..........................................................................................17

2.3 PERFORMANCE....................................................................................................19

3 PIN ASSIGNMENTS..............................................................................................20

3.1 CHAPTER OVERVIEW...........................................................................................21

3.2 TYPE 1, TYPE 2, TYPE 3, TYPE 4 AND TYPE 5 .....................................................22

3.3 SIGNAL TABLE TERMINOLOGY ...........................................................................23

3.4 CONNECTOR PINOUT ROW A AND ROW B...........................................................24

3.5 CONNECTOR PINOUT ROWS C AND D..................................................................26

4 SIGNAL DESCRIPTION AND ROUTING GUIDELINE.................................29

4.1 PEG (PCI EXPRESS GRAPHIC)............................................................................30

4.1.1 Signal Description ......................................................................................30

4.1.2 PEG Connector...........................................................................................32

4.1.3 SDVO ..........................................................................................................33

4.1.4 PEG_ENABLE#..........................................................................................34

4.1.5 PCI Express Test Points and Probing ........................................................34

4.1.6 PCI Express Routing Guideline..................................................................35

4.1.6.1 Impedance Consideration.....................................................................35

4.1.6.2 AC Coupling Capacitors......................................................................36

4.1.6.3 Routing Notices ...................................................................................37

Page iv

Page 5

ICE Module

4.2 PCI EXPRESS ......................................................................................................38

4.2.1 Signal Description ......................................................................................39

4.2.2 PCI Express Slot X1....................................................................................40

4.2.3 Express Card Connector.............................................................................40

4.2.4 PCIe Mini Card...........................................................................................43

4.2.5 PCI Express Clock Buffer...........................................................................46

4.2.5.1 PCI Express Routing Guideline...........................................................46

4.3 PCI .....................................................................................................................47

4.3.1 Signal Description ......................................................................................47

4.3.2 PCI Connector............................................................................................48

4.3.3 PCI IRQ Assignment...................................................................................48

4.3.4 PCI Clock Buffer.........................................................................................50

4.3.5 PCI Routing Guideline................................................................................50

4.4 SATA (SERIAL ATA INTERFACE) ......................................................................51

4.4.1 Signal Description ......................................................................................51

4.4.2 SATA Connector..........................................................................................52

4.4.3 SATA LED#.................................................................................................53

4.4.4 SATA Routing Guideline.............................................................................53

4.5 UNIVERSAL SERIAL BUS (USB)..........................................................................54

4.5.1 Signal Description ......................................................................................54

4.5.2 USB Keyed Connector Protocol .................................................................55

4.5.3 ESD/EMI.....................................................................................................57

4.5.4 Over Current Protection.............................................................................58

4.5.5 Reference Schematics..................................................................................58

4.5.6 USB Routing Guideline...............................................................................60

4.5.6.1 Impedance............................................................................................60

4.5.6.2 General Routing and Placement...........................................................60

4.6 LVDS .................................................................................................................61

4.6.1 Signal Description ......................................................................................61

4.6.2 LVDS Cable Consideration.........................................................................62

4.6.3 Backlight and LCD Power Timing Control.................................................62

4.6.4 LVDS Routing Guideline.............................................................................64

4.6.4.1 Impedance............................................................................................64

4.6.4.2 Implement............................................................................................64

4.7 AUDIO CODEC INTERFACE(AC’97/HDA) ...........................................................65

4.7.1 Signal Description ......................................................................................65

4.8 REFERENCE CIRCUIT...........................................................................................65

Page v

Page 6

4.8.1 Audio Routing Guideline.............................................................................65

4.8.1.1 Analog Power Delivery........................................................................65

4.8.1.2 Digital and Analog Signals Isolation...................................................66

4.8.1.3 EMI Consideration...............................................................................66

4.9 IDE.....................................................................................................................66

4.9.1 Signal Description ......................................................................................66

4.9.2 IDE Connector............................................................................................67

4.9.3 CF Connector..............................................................................................68

4.10 TV-OUT............................................................................................................69

4.10.1 Signal Description ....................................................................................69

4.10.2 TV -Out Routing Guideline ........................................................................69

4.10.2.1 Signal Termination.............................................................................69

4.10.2.2 Video Filter........................................................................................69

4.10.2.3 ESD Protection...................................................................................70

ICE Module

4.10.2.4 Reference Schematic..........................................................................70

4.11 LAN (LOCAL AREA NETWORK)........................................................................71

4.11.1 Signal Description.....................................................................................71

4.11.2 Giga LAN Connector.................................................................................72

4.11.3 LAN Link Activity and Speed LED............................................................72

4.11.4 LAN Routing Guideline.............................................................................73

4.11.4.1 Impedance..........................................................................................73

4.11.4.2 LAN Ground Plane Separation..........................................................74

4.12 LPC (LOW PIN COUNT INTERFACE)..................................................................74

4.12.1 Signal Description ....................................................................................74

4.12.2 Clock and Reset Buffer..............................................................................75

4.12.3 LPC SuperIO for Legacy IO Support........................................................76

4.12.3.1 Keyboard/Mouse................................................................................76

4.12.3.2 RS-232/Floppy/LPT/IR......................................................................77

4.13 VGA.................................................................................................................79

4.13.1 Signal Description ....................................................................................79

4.13.2 VGA Connector.........................................................................................80

4.13.3 VGA DAC Filter........................................................................................80

4.13.4 Routing Guide Line...................................................................................80

4.13.4.1 HSYNC and VSYNC Signals............................................................80

4.13.4.2 ESD....................................................................................................80

4.13.4.3 DDC Interface....................................................................................80

4.13.5 VGA Reference Design .............................................................................81

Page vi

Page 7

ICE Module

4.14 MISCELLANEOUS ..............................................................................................82

4.14.1 Signal Description ....................................................................................82

4.14.2 Speaker/FAN Control/RTC Reference.......................................................84

4.14.2.1 Speaker Out........................................................................................84

4.14.2.2 FAN Control.......................................................................................84

4.14.2.3 RTC....................................................................................................85

5 PCB STACK AND POWER DELIVER DESIGN............................................86

5.1 CHAPTER OVERVIEW...........................................................................................87

5.2 MICROSTRIP OR STRIPLINE..................................................................................87

5.3 PCB STACKUP EXAMPLE....................................................................................87

5.3.1 Four-Layer Stack-up...................................................................................88

5.3.2 Six-Layer Stack-up......................................................................................88

5.4 ATX POWER DELIVERY GUIDELINES ..................................................................90

5.4.1 ATX Power Status (S0,S3,S4,S5,G3)...........................................................91

5.4.2 ATX Power Diagram...................................................................................92

6.3.3 ATX Power On Timing................................................................................92

5.5 AT POWER DELIVERY GUIDELINE......................................................................93

5.5.1 AT Power Diagram.....................................................................................93

5.5.2 AT Power On Timing..................................................................................94

6 MECHANICAL DESIGN GUIDELINES............................................................95

6.1 CHAPTER OVERVIEW...........................................................................................96

6.2 COM MODULE AND CARRIER BOARD CONNECTOR............................................96

6.2.1 Module Connector ......................................................................................96

6.2.2 Carrier Board Connector ...........................................................................97

6.3 CONNECTOR FOOTPRINT.....................................................................................98

6.4 COM EXPRESS FORM FACTORS..........................................................................99

6.5 HEAT SPREAD....................................................................................................100

6.6 DESIGN NOTES..................................................................................................103

6.6.1 Component Height — Module Back and Carrier Board Top....................103

6.6.2 Air Follow Issue........................................................................................105

6.6.3 Grounding Issue........................................................................................105

6.7 OTHERS KITS SPECIFICATION............................................................................105

6.7.1 Heat Sink...................................................................................................105

A ICE MODULE DESIGN SCHEMATIC CHECK LIST ..................................107

B APPLICA TION NOTES......................................................................................116

Page vii

Page 8

B.1 TERMINOLOGY .................................................................................................117

B.2 UPDATING BIOS VERSION ...............................................................................117

B.2.1 Using AFUWIN.........................................................................................118

6.7.2 Using DOS Command...............................................................................121

A.1 RTC OVERVIEW...............................................................................................123

A.1.1 How to Calculate the Battery Life............................................................123

B REFERENCE CARRIER BOARD SCHEMATIC...........................................124

ICE Module

Page viii

Page 9

ICE Module

List of Figures

Figure 2-1: ICE Module Application..............................................................................................6

Figure 2-2: ICE-9152-R10...............................................................................................................8

Figure 2-3: ICE-9102-1GZ-R10.....................................................................................................10

Figure 2-4: ICE-9102-1G512-R10.................................................................................................12

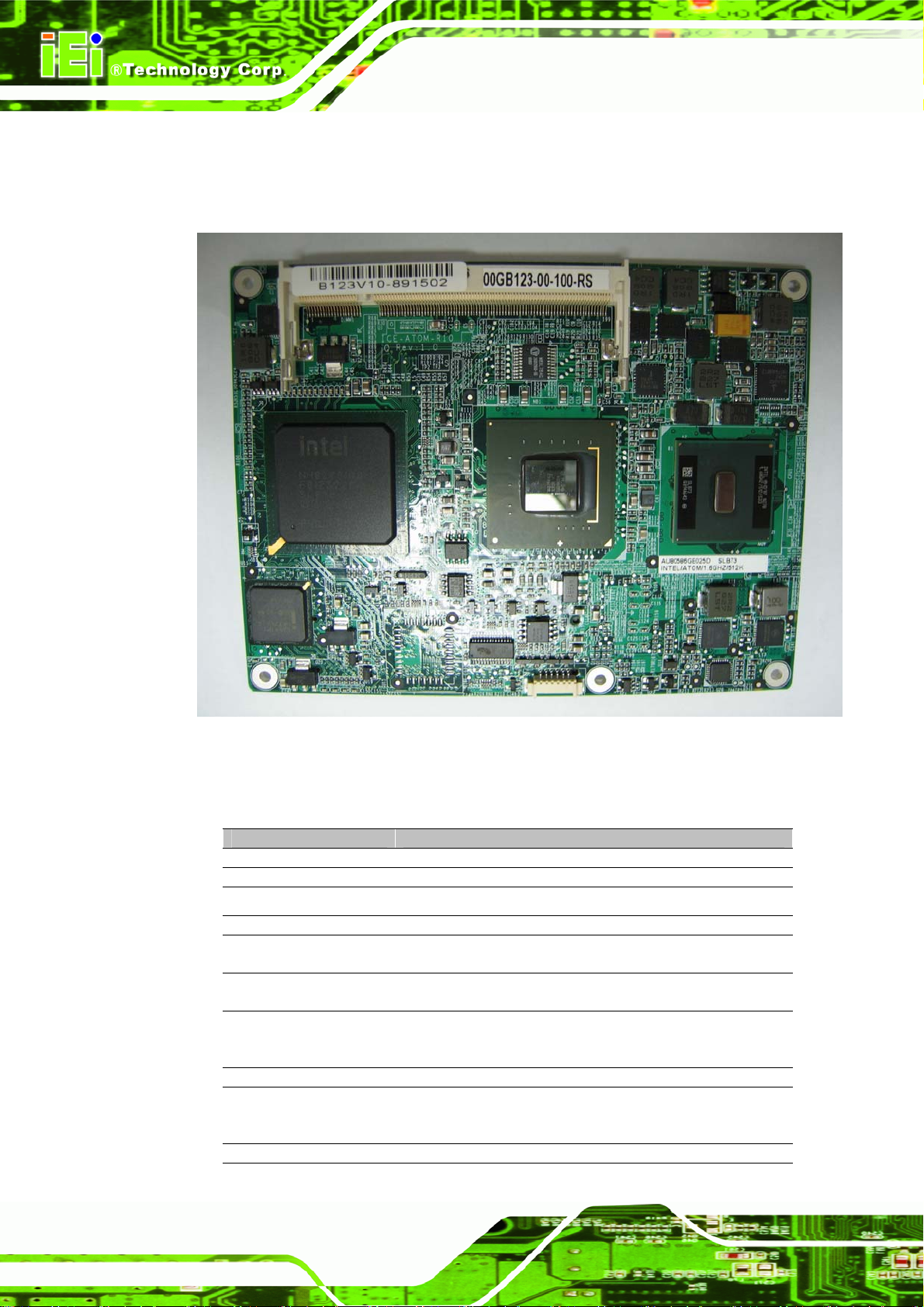

Figure 2-5: ICE-ATOM-R10...........................................................................................................14

Figure 2-6: ICE-DB-9S-R10 ..........................................................................................................17

Figure 3-1: COM Express Type 2 Module Diagram...................................................................21

Figure 4-1: PCI Express x16 Slot Example ................................................................................32

Figure 4-2: Intel Recommend Test Structure for PCI Express Data Eye Measurement........35

Figure 4-3: PEG Lane Connection Topology Example.............................................................37

Figure 4-4: PEG Layout Trace Example .....................................................................................38

Figure 4-5: PCI Express x1 Slot Example ..................................................................................40

Figure 4-6: Express Card Slot Example...................................................................................41

Figure 4-7: Express Card 54&34 Type (Refer to www.expresscard.org)..............................42

Figure 4-8: Express Card 54 & 34 Plug Way (Refer to www.expresscard.org)....................43

Figure 4-9: Express Card Slot Example .....................................................................................44

Figure 4-10: Mini Card Bottom Side Dimensions (Refer to www.pcisig.com)........................45

Figure 4-11: Mini Card Top Side Dimensions (Refer to www.pcisig.com)..............................45

Figure 4-12: Mini Card Connector (Refer to www.pcisig.com) ................................................46

Figure 4-13: PCI Express Clock Buffer Example.......................................................................46

Figure 4-14: PCI Slot Connection Example................................................................................48

Figure 4-15: PCI Slot Routing Example...................................................................................49

Figure 4-16: PCI Clock Buffer Example......................................................................................50

Figure 4-17: SATA 7-pin Connector Example.........................................................................52

Figure 4-18: SATA LED Connection Example.........................................................................53

Figure 4-19: Keyed Connector Protocol (Refer to USB2.0 Spec.)...........................................55

Figure 4-20: USB Connector........................................................................................................56

Figure 4-21: RailClamp SRV05-4 Low Capacitance TVS Diode Array for ESD ......................57

Figure 4-22: 90 ohm Common Mode Choke at 100MHz for EMI ..............................................57

Figure 4-23: MIC2026 Block Diagram(Please refer the datasheet from MICREL ).................58

Figure 4-24: USB Reference Design...........................................................................................59

Figure 4-25: LVDS Power Control...............................................................................................62

Figure 4-26: Backlight Control Circuit........................................................................................63

Page ix

Page 10

Figure 4-27: LCD Power Sequence Example(Refer to AUO G150XG01).................................63

Figure 4-28: Audio Analog Power Example...............................................................................66

Figure 4-29: IDE Reference Design.............................................................................................67

Figure 4-30: CF Connector ..........................................................................................................68

Figure 4-31: CompactFlash® Reference Design.......................................................................68

Figure 4-32: TV Out Schematic Reference.................................................................................70

Figure 4-33: Giga Lan Connection Exampel (including Transformer)....................................72

Figure 4-34: Clock Buffer.............................................................................................................75

Figure 4-35: Windbond W83627EHG Reference Design...........................................................76

Figure 4-36: Keyboard/Mouse Reference Schematic................................................................77

Figure 4-37: RS-232 Reference Schematic ................................................................................77

Figure 4-38: LPT Reference Schematic......................................................................................78

Figure 4-39: Floppy Reference Schematic.................................................................................78

Figure 4-40: IR Reference Schematic.........................................................................................79

ICE Module

Figure 4-41: VGA Connector D-SUB15.......................................................................................80

Figure 4-42: VGA Reference Design...........................................................................................81

Figure 4-43: Speaker Out Reference Schematic .......................................................................84

Figure 4-44: FAN Reference Schematic .....................................................................................84

Figure 4-45: RTC Reference Schematic .....................................................................................85

Figure 5-1: Four Layers Stack.....................................................................................................88

Figure 5-2: Six Layers Stack........................................................................................................89

Figure 5-3: ATX Power Delivery Block Diagram........................................................................92

Figure 5-4: ATX Power On Sequence.........................................................................................92

Figure 5-5: AT Power Delivery Block Diagram..........................................................................93

Figure 5-6: AT Power On Sequence............................................................................................94

Figure 6-1: Module Connector Picture .......................................................................................97

Figure 6-2: Carrier Board Connector..........................................................................................97

Figure 6-3: Single Connector Physical Dimensions.................................................................98

Figure 6-4: Dual Connector Footprint and Alignment ..............................................................98

Figure 6-5: Compact, Basic and Extended Form Factor ....................................................... 100

Figure 6-6: Overall Height for Heat-Spreader in Basic and Extended Modules.................. 101

Figure 6-7: Basic Module Heat-Spreader ................................................................................ 102

Figure 6-8: Basic Module Heat-Spreader Footprint ............................................................... 102

Figure 6-9: IEI Heat Spread Module......................................................................................... 103

Figure 6-10: Component Clearances Underneath Module.................................................... 104

Figure 6-11: IEI Heat Sink Module Dimensions...................................................................... 105

Figure 6-12: IEI Heat Sink Module Picture .............................................................................. 106

Page x

Page 11

ICE Module

Figure 6-13: BIOS Main Menu (BIOS Version: MR10) ............................................................ 118

Figure 6-14: AFUWIN – Open BIOS File................................................................................... 118

Figure 6-15: Locate BIOS File................................................................................................... 119

Figure 6-16: Check Program All Block.................................................................................... 119

Figure 6-17: AFUWIN – Flash ................................................................................................... 120

Figure 6-18: BIOS Main Menu – Updated BIOS Version (MR11)........................................... 120

Figure 6-19: USB Flash Drive and BIOS Updating Files........................................................ 121

Figure 6-20: BIOS Updating File Directory.............................................................................. 121

Figure 6-21: GO Command....................................................................................................... 122

Figure 6-22: BIOS Updating Complete (DOS)......................................................................... 122

Figure 6-23: BIOS Main Menu – Updated BIOS Version (MR11)........................................... 123

Page xi

Page 12

ICE Module

List of Tables

Table 1-1: Conventions and Terminology....................................................................................2

Table 1-2: Reference Documents..................................................................................................4

Table 2-1: IEI ICE Modules.............................................................................................................7

Table 2-2: ICE-9152-R10 Specification .........................................................................................8

Table 2-3: ICE-9102-1GZ-R10 Specification...............................................................................10

Table 2-4: ICE-9102-1G512-R10 Specification...........................................................................12

Table 2-5: ICE-ATOM-R10 Specification.....................................................................................14

Table 2-6: ICE-GM45A-R10 Specification...................................................................................16

Table 2-7: ICE-DB-9S-R10 Specification ....................................................................................17

Table 3-1 ........................................................................................................................................22

Table 3-2: Conventions and Terminology..................................................................................23

Table 3-3: Module Type 2 Connector Pinout Rows (A and B)..................................................24

Table 3-4: Module Type 2 Connector Pinout Rows (C and D)..................................................26

Table 4-1: PCI Express Signal Descriptions..............................................................................30

Table 4-2: PEG & S DVO Pin Assignment..................................................................................33

Table 4-3: Intel® SDVO Support Device List..............................................................................33

Table 4-4: PCI Express Impedance Consideration....................................................................35

Table 4-5: PCI Express Signal Descriptions..............................................................................39

Table 4-6: Express Card Pin Definition ......................................................................................41

Table 4-7: Mini Card Pin-out .....................................................................................................44

Table 4-8: PCI Signal Description...............................................................................................47

Table 4-9: PCI Slot Routing Table...............................................................................................49

Table 4-10: PCI Impedance Consideration.................................................................................51

Table 4-11: Serial ATA Signal Descriptions...............................................................................52

Table 4-12: SATA Impedance Consideration.............................................................................53

Table 4-13: USB Signal Description............................................................................................54

Table 4-14: USB Connector Signal Description ........................................................................56

Table 4-15: LVDS Signals Description........................................................................................61

Table 4-16: LVDS Impedance Consideration.............................................................................64

Table 4-17: Audio Signals Description.......................................................................................65

Table 4-18: IDE signals description............................................................................................66

Table 4-19: TV-Out Signal Descriptions.....................................................................................69

Table 4-20: Ethernet signals description...................................................................................71

Page xii

Page 13

ICE Module

Table 4-21: LAN Impedance Consideration ...............................................................................73

Table 4-22: LPC Interface Signal Descriptions..........................................................................75

Table 4-23: VGA signals description..........................................................................................79

Table 4-24: Miscellaneous pin assignment................................................................................82

Table 5-1: Signal Tables Terminology Descriptions.................................................................91

Table 5-2: Power State Behavior.................................................................................................91

Table 5-3: ATX Power On Sequence Timing..............................................................................93

Table 5-4: AT Power On Sequence Timing ................................................................................94

Page xiii

Page 14

ICE Module

Chapter

1

1 Introduction

Page 1

Page 15

1.1 Introduction

This design guide describes the design concept of the IEI COM Express module and

how to teach customers to develop their own COM Express baseboard. IEI COM

Express module is compatible with all baseboards compliant with COM Express

specification.

1.2 Acronyms and Abbreviations Definition

Table 1-1 defines the acronyms, conventions, and terminology that are used

throughout the design guide.

Table 1-1: Conventions and Terminology

Terminology Description

AC97 Audio Codec 97’

ICE Module

HDA High Definition Audio

SATA Serial AT Attachment: serial-interface standard for hard disks

IDE (ATA) Integrated Drive Electronics (Advanced Technology Attachment)

SDVO Serial Digital Video Out is a proprietary technology introduced by Intel®

to add additional video signaling interfaces to a system

EMI Electromagnetic Interference

ESD Electrostatic Discharge

PCIe x1, x2, x4, x16 x1 refers to one PCI Express Lane of basic bandwidth; x2 to two PCI

Express Lanes; etc.. Also referred to as x1, x2, x4, x16 link.

PCI Express (PCIe) Peripheral Component Interface Express – next-generation high speed

Serialized I/O bus

ExpressCard A PCMCIA standard built on the latest USB 2.0 and PCI Express buses

GBE Gigabit Ethernet

CRT Cathode Ray Tube

DDR Double Data Rate SDRAM memory technology

DVI Digital Visual Interface is the interface specified by the DDWG (Digital

Display working Group) DVI Spec. Rev. 1.0

DDC Display Data Channel is an I2C bus interface between a display and a

graphics adapter.

Page 2

Page 16

ICE Module

I2C Inter-IC (a two wire serial bus created by Philips)

LCD Liquid Crystal Display

LFP Local Flat Panel

LVDS Low Voltage Differential Signaling: A high speed, low power data

transmission standard used for display connections to LCD panels.

NTSC National Television Standards Committee

PAL Phase Alternate Line

PCI Peripheral Component Interface

RTC Real Time Clock

SMBus System Management Bus.

COM Computer On Module

STD Suspend To Disk

STR Suspend To RAM

ULV Ultra-Low Voltage

USB Universal Serial Bus

PCI

N.C. Not connected

N.A. Not available

T.B.D. To be determined

Page 3

Page 17

ICE Module

1.3 Reference Documents

Table 1-2 lists all the reference documents of this design guide.

Table 1-2: Reference Documents

Document Location

PICMGR COM Express Module™ Base Specification

I2C Bus Interface

PCI Local Bus Specification, Revision 2.3

Serial ATA Specification, Revision 1.0a

PC104

SMBus

Universal Serial Bus (USB) Specification, Revision 2.0

IrDA

Ethernet(IEEE 802.3)

RS-232

Advanced Configuration and Power Management (ACPI)

Specification 1.0b & 2.0

Advanced Power Management (APM) Specification 1.2

PCI Express Base Specification, Revision 2.0

ExpressCard Standard Release 1.0

http://www.picmg.org/

http://www.semiconductors.philips.com/

http://www.pcisig.com/

http://www.serialata.org/

http://www.pc104.org/technology/pc104_tech.html

http://www.smbus.org/specs/

http://www.usb.org/home

http://www.irda.org/

http://www.ieee.org/portal/site

http://www.eia.org/

http://www.teleport.com/~acpi/

http://www.microsoft.com/hwdev/busbios/amp_12.

htm

http://www.pcisig.com/specifications

http://www.expresscard.org/

High Definition Audio Specification, Rev. 1.0

Extended Display Identification Data Standard Version 1.3

(EDID™)

Enhanced Display Data Channel Specifi cation Version 1.1

(DDC)

Audio Codec ‘97 Component Specification, Version 2.3

http://www.intel.com/standards/hdaudio/

http://www.vesa.org/

http://www.vesa.org/

http://www.intel.com/design/chipsets/audio/

Page 4

Page 18

ICE Module

Chapter

2

2 ICE Module Overview

Page 5

Page 19

2.1 Chapter Overview

ICE modules have various options for users to choose. IEI provides high-end,

mid-range and low-end CPU modules. Using the ICE module can overcome the

problems that may be caused by designing a compatible and stable module. IEI also

provides the service of deigning COM Express baseboard.

ICE Module

Figure 2-1: ICE Module Application

Page 6

Page 20

ICE Module

2.2 ICE Specifications

IEI provides many kinds of ICE modules for customers, including BGA type and socket

type.

Table 2-1 lists the IEI ICE modules and the specifications.

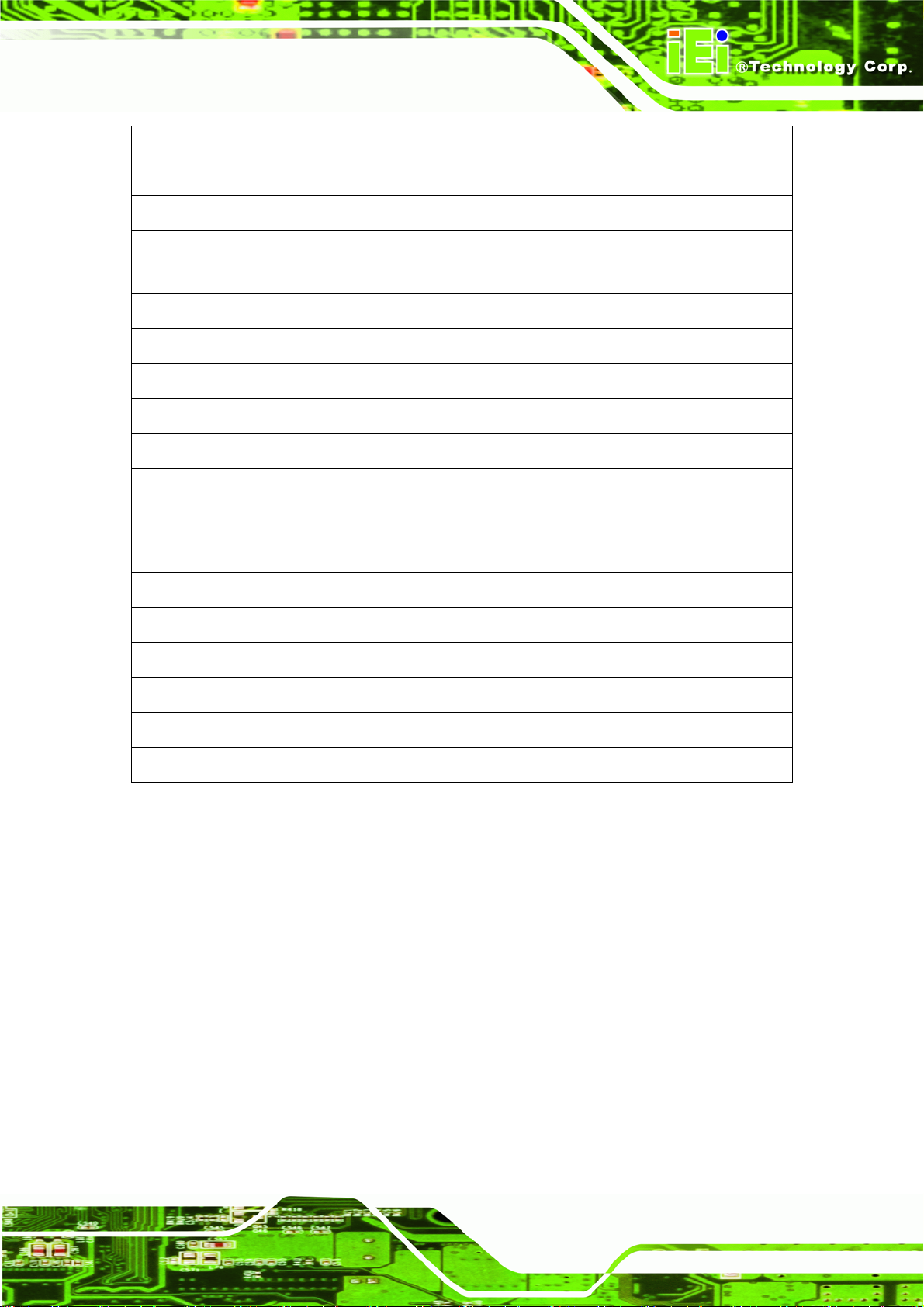

Table 2-1: IEI ICE Modules

ICE 910/915 Series Description

ICE-9152-R10

ICE-9102-1GZ-R10

ICE-9102-1G512-R10

ICE Atom Series Description

ICE-ATOM-R10

ICE GM45 Series Description

ICE-GM45A-R10

COM Express Basic Type 2 Module, Socket 479

Intel® Pentium M CPU, VGA/LVDS, LAN, CF, SATA,

USB 2.0 and Audio

COM Express Basic Type 2 Module with Intel®

Celeron® M 1G zero cache CPU, VGA/LVDS, LAN,

CF, SATA, USB 2.0 and Audio

COM Express Basic Type 2 Module with Intel®

Celeron® M 1G 512KB cache CPU, VGA/LVDS,

LAN, CF, SATA, USB 2.0 and Audio

COM Express Basic Type 2 Module with Intel®

Diamondville-SC Processor at FSB 533MHz, Intel®

945GSE/ICH7M Basic Mobile Platform supports

COM Express Module with Intel® GM45/Penryn

processor DDR2, GbE, LVDS/CRT/HDTV-out,

SATAII, USB2.0

Carrier Board Description

ICE-DB-9S-R10 Base Board for COM Express Type 2 modules

Others Description

Page 7

Page 21

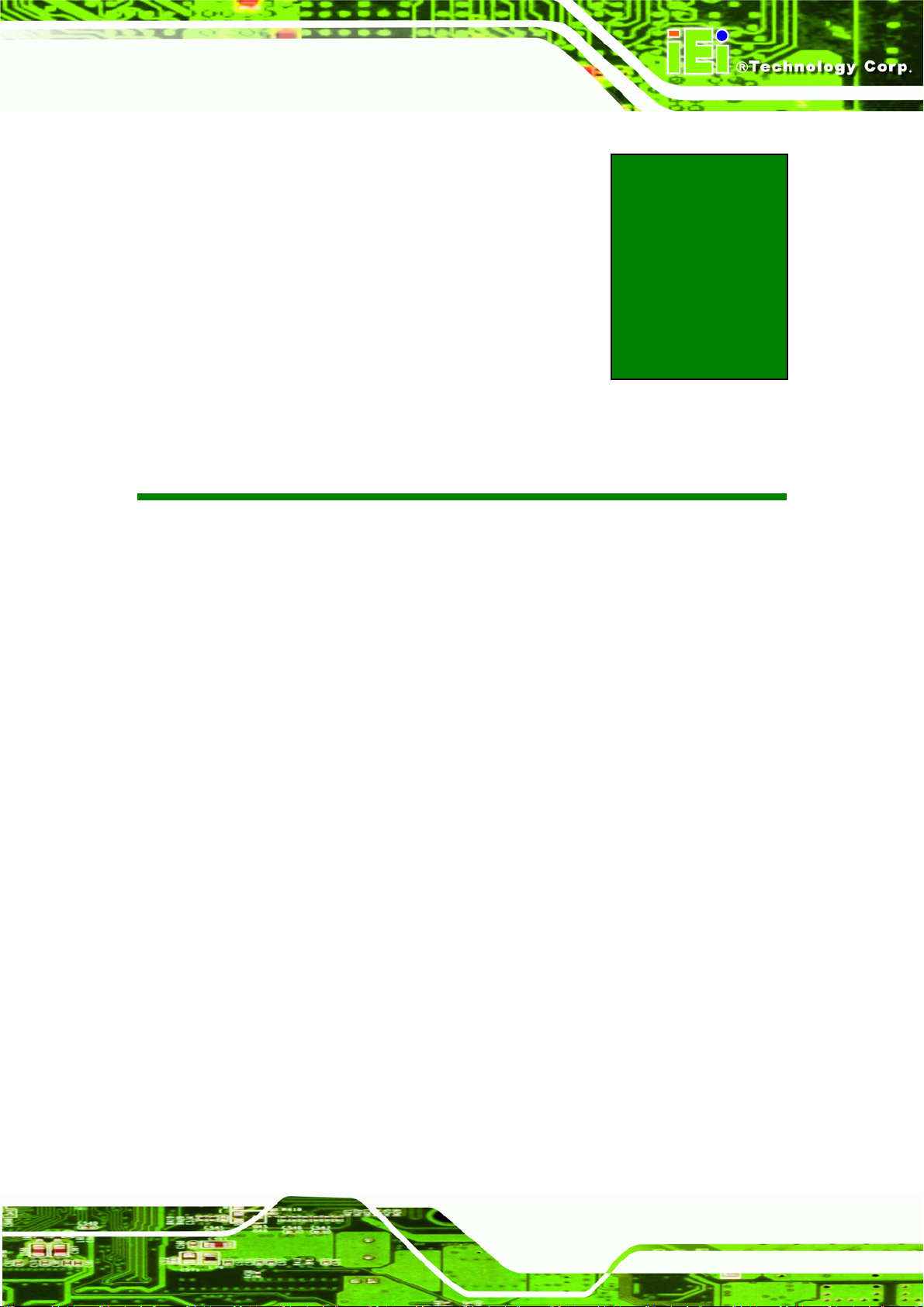

2.2.1 ICE-9152-R10

The ICE-9152 is shown in Figure 2-2 and the specifications are list in Table 2-2.

ICE Module

Figure 2-2: ICE-9152-R10

Table 2-2: ICE-9152-R10 Specification

Item Description

CPU Socket 479 Intel® Pentium® M, Celeron® M processor

with a 533/400MHz FSB

System Memory One 200-pin 533/400MHz DDR2 SDRAM SO-DIMM

supported (system max. 2GB)

System Chipset

BIOS AMI Flash BIOS

WatchDog Timer

Expansion Interface

MIO

USB 8 x USB 2.0 (Signal to Base Board)

Intel® 915GME + ICH6M

255 levels timer interval, from 1 to 255 sec or min

setup by software, jumperless selection, generates

system reset

1 x PCIe x16 signal to Base Board

4 x PCIe x1 signal to Base Board

4 x PCI , 32 bit / 33 MHz PCI bus Singal to Base Base

Board

2 x SATA (Signal to Base Board)

1 x IDE channel (Signal to Base Board)

Page 8

Page 22

ICE Module

Audio

Ethernet

CRT Display mode

LCD Display mode

Dimensions (L x W) 125 mm x 95 mm

Power Supply Voltage ATX / AT supported

Operating

Temperature

Operating Humidity 0% ~ 90% relative humidity, non-condensing

AC’97 Audio Signal to Base Board (Audio Codec on

Base Board)

One Intel® 82541PI GbE Chipset (co-layout Intel®

82551ER 10/100Mbps Ethernet chipset)

Signal to Base Board

VGA Integrated in Intel 915GME Signal (Signal to Base

Board)

18/24-bit Dual channel LVDS Signal (to Base Board)

0 ~ 60˚ C (32 ~ 140˚ F)

Page 9

Page 23

2.2.2 ICE-9102-1GZ-R10

The ICE-9102-1GZ is shown in Figure 2-3 and the specifications are listed in Table

2-3.

ICE Module

Figure 2-3: ICE-9102-1GZ-R10

Table 2-3: ICE-9102-1GZ-R10 Specification

Item Description

CPU On board Intel® Celeron® M 1GHz zero cache

processor

System Memory One 200-pin 400MHz DDR2 SDRAM SO-DIMM

supported (system max. 2GB)

System Chipset

BIOS AMI Flash BIOS

WatchDog Timer

Expansion Interface

MIO

USB 8 x USB 2.0 (Signal to Base Board)

Audio

Ethernet

Intel® 910GMLE + ICH6-M

Software programmable supports 1 ~255 sec. System

reset

2 x SATA (Signal to Base Board)

1 x IDE channel (Signal to Base Board)

4 x PCIe x1 Signal to Base Board

4 x PCI , 32 bit / 33 MHz PCI bus Signal to Base Board

AC’97 Audio Signal to Base Board (Audio Codec on

Base Board)

One Intel® 82541PI GbE Chipset (co-layout Intel®

82551ER 10/100Mbps Ethernet chipset)

Page 10

Page 24

ICE Module

Singal to Base Board

CRT Display mode

LCD Display mode

Dimensions (L x W) 125 mm x 95 mm

Power Supply Voltage ATX / AT supported

Operating

Temperature

Operating Humidity 0% ~ 90% relative humidity, non-condensing

VGA Integrated in Intel 910GMLE Signal (Signal to

Base Board)

18/24-bit Dual channel LVDS Signal (Signal to Base

Board)

0 ~ 60˚ C (32 ~ 140˚ F)

Page 11

Page 25

A

2.2.3 ICE-9102-1G512-R10

The ICE-9152-1G512 is shown in Figure 2-4 and the specifications are listed in Table

2-4.

ICE Module

Figure 2-4: ICE-9102-1G512-R10

Table 2-4: ICE-9102-1G512-R10 Specification

Item Description

CPU On board Intel® Celeron® M 1GHz 512KB cache

processor

System Memory One 200-pin 400MHz DDR2 SDRAM SO-DIMM

supported (system max. 2GB)

Intel® 910GMLE + ICH6-M

Software programmable supports 1 ~255 sec. System

reset

2 x SATA (Signal to Base Board)

1 x IDE channel (Signal to Base Board)

4 x PCIe x1 Signal to Base Board

4 x PCI , 32 bit / 33 MHz PCI bus Signal to Base Board

C’97 Audio Signal to Base Board (Audio Codec on

Page 12

System Chipset

BIOS AMI Flash BIOS

WatchDog Timer

Expansion Interface

MIO

USB 8 x USB 2.0 (Signal to Base Board)

Audio

Page 26

ICE Module

Base Board)

One Intel® 82541PI GbE Chipset (co-layout Intel®

Ethernet

CRT Display mode

LCD Display mode

Dimensions (L x W) 125 mm x 95 mm

Power Supply Voltage ATX / AT supported

Operating

Temperature

Operating Humidity 0% ~ 90% relative humidity, non-condensing

82551ER 10/100Mbps Ethernet chipset)

Signal to Base Board

VGA Integrated in Intel 910GMLE Signal (Signal to

Base Board)

18/24-bit Dual channel LVDS Signal (Signal to Base

Board)

0 ~ 60˚ C (32 ~ 140˚ F)

Page 13

Page 27

A

2.2.4 ICE-ATOM-R10

The ICE-ATOM is shown in Figure 2-5 and the specifications are listed in Table 2-5.

ICE Module

Figure 2-5: ICE-ATOM-R10

Table 2-5: ICE-ATOM-R10 Specification

Item Description

CPU Intel Diamondville-SC support at FSB 533Mhz

System Memory 1x DDR2 SO-DIMM 400/533MHz support up to 2GB

System Chipset

BIOS AMI BIOS

WatchDog Timer

Audio

MIO

USB 8 USB ports, USB 2.0 (Signal to Base Board)

Ethernet

Display

Intel 945GSE + ICH7M

Sofware Programmable support 1~255 sec. System

reset

HD Audio Signal to Base Board (Audio Codec on Base

Board)

2 x SATA II (Signal to Base Board)

1 x IDE channel (Signal to Base Board)

1 x Intel® 82541PI GbE Chipset (co-layout Intel®

82551ER 10/100Mbps Ethernet chipset) (Signal to

Base Board)

nalog CRT(VGA) Integrated in Intel® 945GSE (Signal

Page 14

Page 28

ICE Module

to Base Board)

18-bits Dual Channel LVDS Signal (Signal to Base

Board)

HDTV-out (Signal to Base Board)

1 x SDVO Interface (Only SDVO Port_B)

Dimensions (L x W) 125 mm x 95 mm

Power Supply Voltage AT/ATX support

Operating

Temperature

Operating Humidity 0% ~ 90% relative humidity, non-condensing system

0 ~ 60° C (32 ~ 140° F)

Page 15

Page 29

2.2.5 ICE-GM45A-R10

The ICE-GM45A is shown in Error! Reference source not found. and the specifications

ICE Module

are listed in

Table 2-6: ICE-GM45A-R10 Specification

Item Description

CPU Socket P Intel® mobile Core™ 2 Duo(Penryn), Intel®

System Memory 2 x 200-pins 1066/800MHz DDR2 SDRAM SO-DIMM

System Chipset

BIOS AMI BIOS

WatchDog Timer

Audio

MIO

Expansion

USB 8 x USB 2.0 (Signal to Base Board)

Ethernet 1 x Intel 82574L GbE chipset (Signal to Base Board)

Display

Dimensions (L x W) 125 mm x 95 mm

Power Supply Voltage ATX/AT supported

Operating

Temperature

Operating Humidity 0% ~ 90% relative humidity, non-condensing system

Table 2-6.

Celeron® M

Supported

Intel® GM45 + Intel® ICH9M

Software programmable supports 1 ~255 sec. System

reset

HD Audio Signal to Base Board (Audio Codec on Base

Board)

4 x SATA II (Signal to Base Board)

1 x IDE channel (Signal to Base Board)

1 x PCIe x16 signal to Base Board

4 x PCIe x1 signal to Base Board

4 x PCI, 32 bit / 33 MHz PCI bus to Base Board

Analog CRT(VGA) Integrated in Intel® GM45 (Signal to

Base Board)

18/24-bits Dual-Channel LVDS (Signal to Base Board)

HDTV-out (Signal to Base Board)

0 ~ 60° C (32 ~ 140° F)

Page 16

Page 30

ICE Module

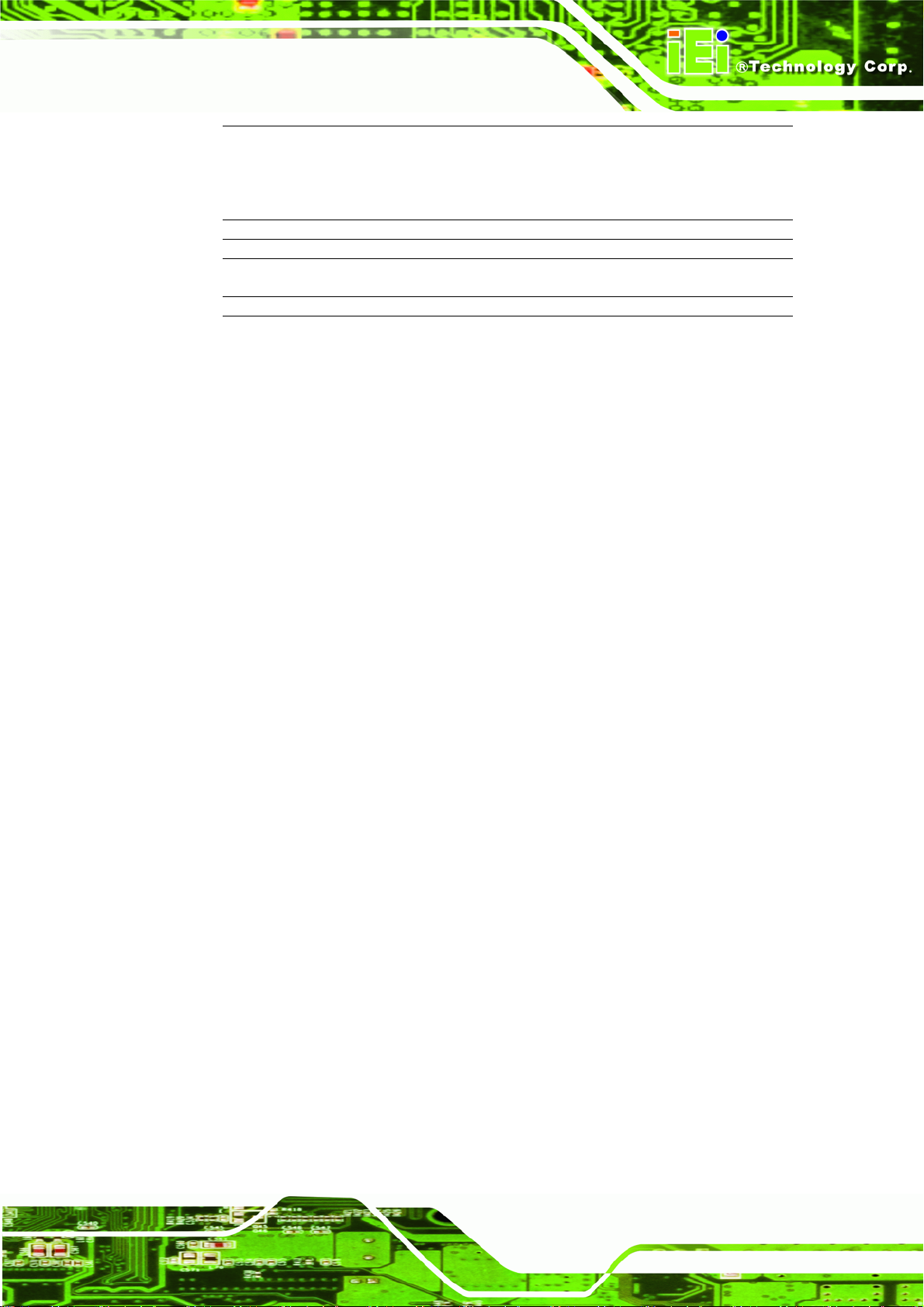

2.2.6 ICE-DB-9S-R10

The ICE-DB-9S is a full function carrier board for customers to apply or test the COM

Express module. The carrier board can be used for any combination, including

software and hardware. Using the carrier board to develop and test the ICE module

also can achieve a quicker time to market. The ICE-DB-9S is shown in

the specifications are listed in

Table 2-7.

Figure 2-6 and

Figure 2-6: ICE-DB-9S-R10

Table 2-7: ICE-DB-9S-R10 Specification

Item Description

CPU module interface Supports COM Express Compact/Basic/Extended

modules using connector pin out Type 2

Realtek ALC888 7.1 channels HD audio codec

Audio

MIO

Front Audio by pin-header(Line in, Line out, Mic in)

SPDIF by pin-header

CD-IN by pin-header

1 x PCIe by 16 Slot

4 x PCIe by 1 Slot

3 x PCI Slot

1 x PCIe Mini card Slot

1 x Express Card Slot

1 x Mini PCI Card Slot

Page 17

Page 31

1 x ISA

1 x IDE

2/4 x SATA/SATA II

1 x CF type II Slot

6 x USB 2.0

1 x LPT

1 x FDD

5 x RS-232

1 x RS-232/422/485

2 x USB 2.0 to PCIe Mini card Slot & Express Card Slot

Ethernet 1 x RJ-45 GbE connector

VGA DB15 connector

Display

Dimensions (L x W) 304.8 mm x 190.5 mm ( 12" x 7.5" )

Power Supply Voltage ATX / AT support

Operating

Temperature

Operating Humidity 0% ~ 90% relative humidity, non-condensing system

1 x 18/24 bit dual channel LVDS Connector

1 x Inverter connector

1 x TV-out interface

0 ~ 60° C (32 ~ 140° F)

ICE Module

Page 18

Page 32

ICE Module

2.3 Performance

Page 19

Page 33

ICE Module

Chapter

3

3 Pin Assignments

Page 20

Page 34

ICE Module

3.1 Chapter Overview

This chapter describes pin assignments and I/O characteristics for COM Express

modules. The carrier board uses two 220-pin 0.5 mm fine pitch board-to-board

connectors. There are five different pin-out types currently defined by the COM

Express Specification. The preferred choice of the embedded computer industry is the

Type 2 pin-out and therefore the leading manufacturers have chosen to produce COM

Express Type 2 modules. This pin-out offers the best balance between older

technology such as PCI and Parallel ATA while providing the latest technologies

including PCI Express, Serial ATA and PCI Express graphics.

Figure 3-1: COM Express Type 2 Module Diagram

Page 21

Page 35

3.2 Type 1, Type 2, Type 3, Type 4 and Type 5

The differences among the Module Types are summarized in Table 3-1.

Module Type 1 supports a single connector with two rows of pins

(220 pins total).

Module Types 2-5 support two connectors with four rows of pins

(440 pins total).

Connector placement and most mounting holes have transparency between Form

Factors.

Table 3-1

Module Type Rows PCIe Lanes (max) PCI IDE LAN (Max)

ICE Module

1

2 (Default)

3

4

5

AB 6 X X 1

AB, CD 22 V V 1

AB, CD 22 X V 3

AB, CD 32 V X 1

AB, CD 32 X X 3

Page 22

Page 36

ICE Module

3.3 Signal Table Terminology

The following section describes the signals found on COM Express Type 2 connectors.

Most of the signals listed in the following sections also apply to other COM Express

module types. The pinout for connector rows A and B remains the same regardless of

the module type but the pinout for connector rows D and C are dependent on the

module type. Refer to the COM Express specification for information about the

different pin-outs of the module types other than Type 2.

Table 3-2 below describes the terminology used in this section for the Signal

Description tables. The “#” symbol at the end of the signal name indicates that the

active or asserted state occurs when the signal is at a low voltage level. When “#” is

not present, the signal is asserted when at a high voltage level.

Table 3-2: Conventions and Terminology

Term Description

I/O Bi-directional signal

I Input signal

O Output signal

I/F Interface

GND Ground

PWR Power

OD Open drain output

PD Pull down

PU Pull up

+V12 +12V ±5% Volts Normal Power

+V5SB +5V ±5% Standby Power

+3.3VSB +3.3V ±5% Standby Power

+V3.3 +3.3V ±5% Volts Normal Power

+V5 +5V ±5% Volts Normal Power

# Active-Low Signals

‘+’ and ‘-‘ Differential Pairs

PM Power Management

GBE Giga Bits Ethernet

Page 23

Page 37

ICE Module

3.4 Connector Pinout Row A and Row B

Table 3-3: Module Type 2 Connector Pinout Rows (A and B)

Pin Signal I/F I/O Pin Signal I/F I/O

A1 GND GND - B1 GND GND -

A2 GBE0_MDI3- GBE I/O B2 GBE0_ACT# GBE O 3.3V

A3 GBE0_MDI3+ GBE I/O B3 LPC_FRAME# LPC O 3.3V

A4 GBE0_LINK100# GBE O 3.3V B4 LPC_AD0 LPC I/O 3.3V

A5 GBE0_LINK1000# GBE O 3.3V B5 LPC_AD1 LPC I/O 3.3V

A6 GBE0_MDI2- GBE I/O B6 LPC_AD2 LPC I/O 3.3V

A7 GBE0_MDI2+ GBE I/O B7 LPC_AD3 LPC I/O 3.3V

A8 GBE0_LINK# GBE O 3.3V B8 LPC_DRQ0# LPC I 3.3V

A9 GBE0_MDI1- GBE I/O B9 LPC_DRQ1# LPC I 3.3V

A10 GBE0_MDI1+ GBE I/O B10 LPC_CLK LPC O 3.3V

A11 GND GND - B11 GND GND -

A12 GBE0_MDI0- GBE I/O B12 PWRBTN# PM I

A13 GBE0_MDI0+ GBE I/O B13 SMB_CK SMB -

A14 GBE0_CTREF GBE B14 SMB_DAT SMB -

A15 SUS_S3# PM O B15 SMB_ALERT# SMB I

A16 SATA0_TX+ SATA O B16 SATA1_TX+ SATA O

A17 SATA0_TX- SATA O B17 SATA1_TX- SATA O

A18 SUS_S4# PM O B18 SUS_STAT# PM O

A19 SATA0_RX+ SATA I B19 SATA1_RX+ SATA I

A20 SATA0_RX- SATA I B20 SATA1_RX- SATA I

A21 GND GND - B21 GND GND -

A22 SATA2_TX+ SATA O B22 SATA3_TX+ SATA O

A23 SATA2_TX- SATA O B23 SATA3_TX- SATA O

A24 SUS_S5# PM O B24 PWR_OK PM I

A25 SATA2_RX+ SATA I B25 SATA3_RX+ SATA I

A26 SATA2_RX- SATA I B26 SATA3_RX- SATA I

A27 BATLOW# PM I B27 WDT - -

A28 ATA_ACT# SATA O 3.3V B28 AC_SDIN2 HDA I 3.3V

A29 AC_SYNC HDA O 3.3V B29 AC_SDIN1 HDA I 3.3V

A30 AC_RST# HDA O 3.3V B30 AC_SDIN0 HDA I 3.3V

A31 GND GND - B31 GND GND -

A32 AC_BITCLK HDA O 3.3V B32 SPKR - -

A33 AC_SDOUT HAD O 3.3V B33 I2C_CK I2C -

A34 BIOS_DISABLE# - - B34 I2C_DAT I2C -

A35 THRMTRIP# PM O B35 THRM# PM I

A36 USB6- USB I/O B36 USB7- USB I/O

A37 USB6+ USB I/O B37 USB7+ USB I/O

A38 USB_6_7_OC# USB I 3.3V B38 USB_4_5_OC# USB I 3.3V

A39 USB4- USB I/O B39 USB5- USB I/O

A40 USB4+ USB I/O B40 USB5+ USB I/O

A41 GND GND - B41 GND GND -

A42 USB2- USB I/O B42 USB3- USB I/O

A43 USB2+ USB I/O B43 USB3+ USB I/O

A44 USB_2_3_OC# USB I 3.3V B44 USB_0_1_OC# USB I 3.3V

A45 USB0- USB I/O B45 USB1- USB I/O

A46 USB0+ USB I/O B46 USB1+ USB I/O

A47 VCC_RTC PWR -- B47 EXCD1_PERST# PCIE -

A48 EXCD0_PERST# PCIE - B48 EXCD1_CPPE# PCIE -

A49 EXCD0_CPPE# PCIE - B49 SYS_RESET# PM I

A50 LPC_SERIRQ LPC I/O

3.3V

B50 CB_RESET# PM O

Page 24

Page 38

ICE Module

A51 GND GND - B51 GND GND -

A52 PCIE_TX5+ PCIE O B52 PCIE_RX5+ PCIE I

A53 PCIE_TX5- PCIE O B53 PCIE_RX5- PCIE I

A54 GPI0 - - B54 GPO1 - -

A55 PCIE_TX4+ PCIE O B55 PCIE_RX4+ PCIE I

A56 PCIE_TX4- PCIE O B56 PCIE_RX4- PCIE I

A57 GND GND - B57 GPO2 --

A58 PCIE_TX3+ PCIE O B58 PCIE_RX3+ PCIE I

A59 PCIE_TX3- PCIE O B59 PCIE_RX3- PCIE I

A60 GND GND - B60 GND GND -

A61 PCIE_TX2+ PCIE O B61 PCIE_RX2+ PCIE I

A62 PCIE_TX2- PCIE O B62 PCIE_RX2- PCIE I

A63 GPI1 - - B63 GPO3 - -

A64 PCIE_TX1+ PCIE O B64 PCIE_RX1+ PCIE I

A65 PCIE_TX1- PCIE O B65 PCIE_RX1- PCIE I

A66 GND GND - B66 WAKE0# PCIE I

A67 GPI2 - - B67 WAKE1# PM I

A68 PCIE_TX0+ PCIE O B68 PCIE_RX0+ PCIE I

A69 PCIE_TX0- PCIE O B69 PCIE_RX0- PCIE I

A70 GND GND - B70 GND GND -

A71 LVDS_A 0+ LV DS O B71 LVDS _B0+ LV DS O

A72 LVDS_A 0- LVDS O B72 LVDS_B 0- LVDS O

A73 LVDS_A 1+ LV DS O B73 LVDS _B1+ LV DS O

A74 LVDS_A 1- LVDS O B74 LVDS_B 1- LVDS O

A75 LVDS_A 2+ LV DS O B75 LVDS _B2+ LV DS O

A76 LVDS_A 2- LVDS O B76 LVDS_B 2- LVDS O

A77 LVDS_VDD_EN LVDS O 3.3V B77 LVDS_B 3+ LVDS O

A78 LVDS_A 3+ LV DS O B78 LVDS _B3- LV DS O

A79 LVDS_A 3- LVDS O B79 LVDS_BKLT_EN LVDS O 3.3V

A80 GND GND - B80 GND GND -

A81 LVDS_A _CK+ LVDS O B81 LV DS_ B_CK+ LVDS O

A82 LVDS_A _CK- LV DS O B82 LVDS_B_ CK- LVD S O

A83 LVDS_I2C_CK LVDS O 3.3V B83 LVDS_BKLT_CTRL LVDS O 3.3V

A84 LVDS_I2C_DAT LVDS IO 3.3V B84 5VSB PWR -

A85 GPI3 - - B85 5VSB PWR -

A86 KBD_RST# KB/MS B86 5VSB PWR -

A87 KBD_A20GATE B87 5VSB PWR -

A88 PCIE0_CK_REF+ B88 RSVD - -

A89 PCIE0_CK_REF- B89 VGA_RED VGA

A90 GND B90 GND GND -

A91 RSVD - - B91 VGA_GRN VGA

A92 RSVD - - B92 VGA_BLU VGA

A93 GPO0 B93 VGA_HSYNC VGA

A94 RSVD - - B94 VGA_VSYNC VGA

A95 RSVD - - B95 VGA_I2C_CK VGA

A96 GND GND B96 VGA_I2C_DAT VGA

A97 +V12 PWR - B97 TV_DAC_A TV

A98 +V12 PWR - B98 TV_DAC_B TV

A99 +V12 PWR - B99 TV_DAC_C TV

A100 GND GND B100 GND GND -

A101 +V12 PWR - B101 +V12 PWR -

A102 +V12 PWR - B102 +V12 PWR -

A103 +V12 PWR - B103 +V12 PWR -

A104 +V12 PWR - B104 +V12 PWR -

A105 +V12 PWR - B105 +V12 PWR -

A106 +V12 PWR - B106 +V12 PWR -

Page 25

Page 39

A107 +V12 PWR - B107 +V12 PWR -

A108 +V12 PWR - B108 +V12 PWR -

A109 +V12 PWR - B109 +V12 PWR -

A110 GND GND - B110 GND GND -

ICE Module

3.5 Connector Pinout Rows C and D

Table 3-4: Module Type 2 Connector Pinout Rows (C and D)

Pin Signal I/F I/O Pin Signal I/F I/O

C1 GND GND - D1 GND GND -

C2 IDE_D7 IDE IO 3.3V D2 IDE_D5 IDE IO 3.3V

C3 IDE_D6 IDE IO 3.3V D3 IDE_D10 IDE IO 3.3V

C4 IDE_D3 IDE IO 3.3V D4 IDE_D11 IDE IO 3.3V

C5 IDE_D15 IDE IO 3.3V D5 IDE_D12 IDE IO 3.3V

C6 IDE_D8 IDE IO 3.3V D6 IDE_D4 IDE IO 3.3V

C7 IDE_D9 IDE IO 3.3V D7 IDE_D0 IDE IO 3.3V

C8 IDE_D2 IDE IO 3.3V D8 IDE_REQ IDE I 3.3V

C9 IDE_D13 IDE IO 3.3V D9 IDE_IOW# IDE O 3.3V

C10 IDE_D1 IDE IO 3.3V D10 IDE_ACK# IDE O 3.3V

C11 GND GND - D11 GND GND -

C12 IDE_D14 IDE IO 3.3V D12 IDE_IRQ IDE I 3.3V

C13 IDE_IORDY IDE I 3.3V D13 IDE_A0 IDE O 3.3V

C14 IDE_IOR# IDE O 3.3V D14 IDE_A1 IDE O 3.3V

C15 PCI_PME# PCI IO 3.3V D15 IDE_A2 IDE O 3.3V

C16 PCI_GNT2# PCI O 3.3V D16 IDE_CS1# IDE O 3.3V

C17 PCI_REQ2# PCI I 3.3V D17 IDE_CS3# IDE O 3.3V

C18 PCI_GNT1# PCI O 3.3V D18 IDE_RESET# IDE IO 3.3V

C19 PCI_REQ1# PCI I 3.3V D19 PCI_GNT3# PCI O 3.3V

C20 PCI_GNT0# PCI O 3.3V D20 PCI_REQ3# PCI I 3.3V

C21 GND GND - D21 GND GND -

C22 PCI_REQ0# PCI I 3.3V D22 PCI_AD1 PCI IO 3.3V

C23 PCI_RESET# PCI O 3.3V D23 PCI_AD3 PCI IO 3.3V

C24 PCI_AD0 PCI IO 3.3V D24 PCI_AD5 PCI IO 3.3V

C25 PCI_AD2 PCI IO 3.3V D25 PCI_AD7 PCI IO 3.3V

C26 PCI_AD4 PCI IO 3.3V D26 PCI_C/BE0# PCI IO 3.3V

C27 PCI_AD6 PCI IO 3.3V D27 PCI_AD9 PCI IO 3.3V

C28 PCI_AD8 PCI IO 3.3V D28 PCI_AD11 PCI IO 3.3V

C29 PCI_AD10 PCI IO 3.3V D29 PCI_AD13 PCI IO 3.3V

C30 PCI_AD12 PCI IO 3.3V D30 PCI_AD15 PCI IO 3.3V

C31 GND GND - D31 GND GND -

C32 PCI_AD14 PCI IO 3.3V D32 PCI_PAR PCI IO 3.3V

C33 PCI_C/BE1# PCI IO 3.3V D33 PCI_SERR# PCI IO 3.3V

C34 PCI_PERR# PCI IO 3.3V D34 PCI_STOP# PCI IO 3.3V

C35 PCI_LOCK# PCI IO 3.3V D35 PCI_TRDY# PCI IO 3.3V

C36 PCI_DEVSEL# PCI IO 3.3V D36 PCI_FRAME# PCI IO 3.3V

C37 PCI_IRDY# PCI IO 3.3V D37 PCI_AD16 PCI IO 3.3V

C38 PCI_C/BE2# PCI IO 3.3V D38 PCI_AD18 PCI IO 3.3V

C39 PCI_AD17 PCI IO 3.3V D39 PCI_AD20 PCI IO 3.3V

C40 PCI_AD19 PCI IO 3.3V D40 PCI_AD22 PCI IO 3.3V

C41 GND GND - D41 GND GND -

C42 PCI_AD21 PCI IO 3.3V D42 PCI_AD24 PCI IO 3.3V

C43 PCI_AD23 PCI IO 3.3V D43 PCI_AD26 PCI IO 3.3V

C44 PCI_C/BE3# PCI IO 3.3V D44 PCI_AD28 PCI IO 3.3V

C45 PCI_AD25 PCI IO 3.3V D45 PCI_AD30 PCI IO 3.3V

Page 26

Page 40

ICE Module

C46 PCI_AD27 PCI IO 3.3V D46 PCI_IRQC# PCI I 3.3V

C47 PCI_AD29 PCI IO 3.3V D47 PCI_IRQD# PCI I 3.3V

C48 PCI_AD31 PCI IO 3.3V D48 PCI_CLKRUN# PCI I/O 3.3V

C49 PCI_IRQA# PCI I 3.3V D49 PCI_M66EN PCI I 3.3V

C50 PCI_IRQB# PCI I 3.3V D50 PCI_CLK PCI OI 3.3V

C51 GND GND - D51 GND GND -

C52 PEG_RX0+ PEG I D52 PEG_TX0+ PEG O

C53 PEG_RX0- PEG I D53 PEG_TX0- PEG O

C54 TYPE0# D54 PEG_LANE_RV#

C55 PEG_RX1+ PEG I D55 PEG_TX1+ PEG O

C56 PEG_RX1- PEG I D56 PEG_TX1- PEG O

C57 TYPE1# D57 TYPE2#

C58 PEG_RX2+ PEG I D58 PEG_TX2+ PEG O

C59 PEG_RX2- PEG I D59 PEG_TX2- PEG O

C60 GND GND - D60 GND GND -

C61 PEG_RX3+ PEG I D61 PEG_TX3+ PEG O

C62 PEG_RX3- PEG I D62 PEG_TX3- PEG O

C63 RSVD - - D63 RSVD - -

C64 RSVD - - D64 RSVD - -

C65 PEG_RX4+ PEG I D65 PEG_TX4+ PEG O

C66 PEG_RX4- PEG I D66 PEG_TX4- PEG O

C67 FAN_PWMOUT - O D67 GND GND -

C68 PEG_RX5+ PEG I D68 PEG_TX5+ PEG O

C69 PEG_RX5- PEG I D69 PEG_TX5- PEG O

C70 GND GND - D70 GND GND -

C71 PEG_RX6+ PEG I D71 PEG_TX6+ PEG O

C72 PEG_RX6- PEG I D72 PEG_TX6- PEG O

C73 SDVO_DATA D73 SVDO_CLK

C74 PEG_RX7+ PEG I D74 PEG_TX7+ PEG O

C75 PEG_RX7- PEG I D75 PEG_TX7- PEG O

C76 GND GND - D76 GND GND -

C77 FAN_TACHOIN - I D77 IDE_CBLID# IDE I 3.3V

C78 PEG_RX8+ PEG I D78 PEG_TX8+ PEG O

C79 PEG_RX8- PEG I D79 PEG_TX8- PEG O

C80 GND GND - D80 GND GND -

C81 PEG_RX9+ PEG I D81 PEG_TX9+ PEG O

C82 PEG_RX9- PEG I D82 PEG_TX9- PEG O

C83 RSVD D83 RSVD

C84 GND GND - D84 GND GND -

C85 PEG_RX10+ PEG I D85 PEG_TX10+ PEG O

C86 PEG_RX10- PEG I D86 PEG_TX10- PEG O

C87 GND GND - D87 GND GND -

C88 PEG_RX11+ PEG I D88 PEG_TX11+ PEG O

C89 PEG_RX11- PEG I D89 PEG_TX11- PEG O

C90 GND GND - D90 GND GND -

C91 PEG_RX12+ PEG I D91 PEG_TX12+ PEG O

C92 PEG_RX12- PEG I D92 PEG_TX12- PEG O

C93 GND GND - D93 GND GND -

C94 PEG_RX13+ PEG I D94 PEG_TX13+ PEG O

C95 PEG_RX13- PEG I D95 PEG_TX13- PEG O

C96 GND GND - D96 GND GND -

C97 RSVD - - D97 PEG_ENABLE#

C98 PEG_RX14+ PEG I D98 PEG_TX14+ PEG O

C99 PEG_RX14- PEG I D99 PEG_TX14- PEG O

C100 GND GND - D100 GND GND -

C101 PEG_RX15+ PEG I D101 PEG_TX15+ PEG O

Page 27

Page 41

C102 PEG_RX15- PEG I D102 PEG_TX15- PEG O

C103 GND GND - D103 GND GND -

C104 +V12 PWR - D104 +V12 PWR -

C105 +V12 PWR - D105 +V12 PWR -

C106 +V12 PWR - D106 +V12 PWR -

C107 +V12 PWR - D107 +V12 PWR -

C108 +V12 PWR - D108 +V12 PWR -

C109 +V12 PWR - D109 +V12 PWR -

C110 GND GND - D110 GND GND -

ICE Module

Page 28

Page 42

ICE Module

Chapter

4

4 Signal Description and

Routing Guideline

Page 29

Page 43

4.1 PEG (PCI Express Graphic)

The PEG Port can utilize COM Express PCIe lanes 16-32 and is suitable to drive a x16

link for an external high-performance PCI Express Graphics card, if implemented on

the COM Express module. It supports a theoretical bandwidth of up to 4 GB/s – twice

the peak bandwidth achievable with AGP 8x. Each lane of the PEG Port consists of a

receiver and transmit differential signal pair designated 'PEG_RX0' (+ and -) to

'PEG_RX15' (+ and -) and correspondingly from 'PEG_TX0' (+ and -) to 'PEG_TX15'

(+ and -). The corresponding signals can be found on the Module connector rows C

and D. The pins of the PEG Port are shared with other functionality like SDVO or DVO

depends of the used chipset. SDVO and PEG are defined on COM Express

specification as “may be used”. Please be sure, your functionality will be supported by

your module vendor.

4.1.1 Signal Description

ICE Module

Table 4-1: PCI Express Signal Descriptions

Pin Signal I/O Description

C52

C53

D52

D53

C55

C56

D55

D56

C58

C59

D58

D59

C61

C62

D61

D62

C65

C66

D65

D66

C68

C69

D68

D69

C71

C72

D71

D72

C74

C75

D74 PEG_TX7+ O PEG Port 7. Transmit Output differential pair.

PEG_RX0+

PEG_RX0PEG_TX0+

PEG_TX0PEG_RX1+

PEG_RX1PEG_TX1+

PEG_TX1PEG_RX2+

PEG_RX2PEG_TX2+

PEG_TX2PEG_RX3+

PEG_RX3PEG_TX3+

PEG_TX3PEG_RX4+

PEG_RX4PEG_TX4+

PEG_TX4PEG_RX5+

PEG_RX5PEG_TX5+

PEG_TX5PEG_RX6+

PEG_RX6PEG_TX6+

PEG_TX6PEG_RX7+

PEG_RX7-

I PEG Port 0. Receive Input differential pair.

O PEG Port 0. Transmit Output differential pair.

I PEG Port 1. Receive Input differential pair.

O PEG Port 1. Transmit Output differential pair.

I PEG Port 2. Receive Input differential pair.

O PEG Port 2. Transmit Output differential pair.

I PEG Port 3. Receive Input differential pair.

O PEG Port 3. Transmit Output differential pair.

I PEG Port 4. Receive Input differential pair.

O PEG Port 4. Transmit Output differential pair.

I PEG Port 5. Receive Input differential pair.

O PEG Port 5. Transmit Output differential pair.

I PEG Port 6. Receive Input differential pair.

O PEG Port 6. Transmit Output differential pair.

I PEG Port 7. Receive Input differential pair.

Page 30

Page 44

ICE Module

D75 PEG_TX7C78

C79

D78

D79

C81

C82

D81

D82

C85

C86

D85

D86

C88

C89

D88

D89

C91

C92

D91

D92

C94

C95

D94

D95

C98

C99

D98

D99

C101

C102

D101

D102

A88

A98

D73 SDVO_I2C_CLK O 2.5V

C73 SDVO_I2C_DAT

D54 PEG_LANE_RV# I 3.3V

D97 PEG_ENABLE# I 3.3V

PEG_RX8+

PEG_RX8PEG_TX8+

PEG_TX8PEG_RX9+

PEG_RX9PEG_TX9+

PEG_TX9PEG_RX10+

PEG_RX10PEG_TX10+

PEG_TX10PEG_RX11+

PEG_RX11PEG_TX11+

PEG_TX11PEG_RX12+

PEG_RX12PEG_TX12+

PEG_TX12PEG_RX13+

PEG_RX13PEG_TX13+

PEG_TX13PEG_RX14+

PEG_RX14PEG_TX14+

PEG_TX14PEG_RX15+

PEG_RX15PEG_TX15+

PEG_TX15PCIE_CLK_REF

+

PCIE_CLK_REF-

A

I PEG Port 8,. Receive Input differential pair.

O PEG Port 8. Transmit Output differential pair.

I PEG Port 9,. Receive Input differential pair.

O PEG Port 9. Transmit Output differential pair.

I PEG Port 10.. Receive Input differential pair.

O PEG Port 10.Transmit Output differential pair.

I PEG Port 11. Receive Input differential pair.

O PEG Port 11. Transmit Output differential pair.

I PEG Port 12. Receive Input differential pair.

O PEG Port 12. Transmit Output differential pair.

I PEG Port 13,. Receive Input differential pair.

O PEG Port 13. Transmit Output differential pair.

I PEG Port 14.. Receive Input differential pair.

O PEG Port 14. Transmit Output differential pair.

I PEG Port 15. Receive Input differential pair.

O PEG Port 15. Transmit Output differential pair.

O PCIe Reference Clock for all COM Express

CMOS

I/O 2.5V

OD CMOS

CMOS

CMOS

PCIe lanes, and for PEG lanes

I2C based control signal (clock) for SDVO

device.

I2C based control signal (data) for SDVO device

PCI Express Graphics lane reversal input strap.

Pull low on the carrier board to reverse lane

order.

PEG enable function. Strap to enable PCI

Express x16 external graphics interface. Pull low

to disable internal graphics and enable the x16

interface.

PS: IEI Bios auto detect the SDVO or

PCIEX16, please reserve for future use

Page 31

Page 45

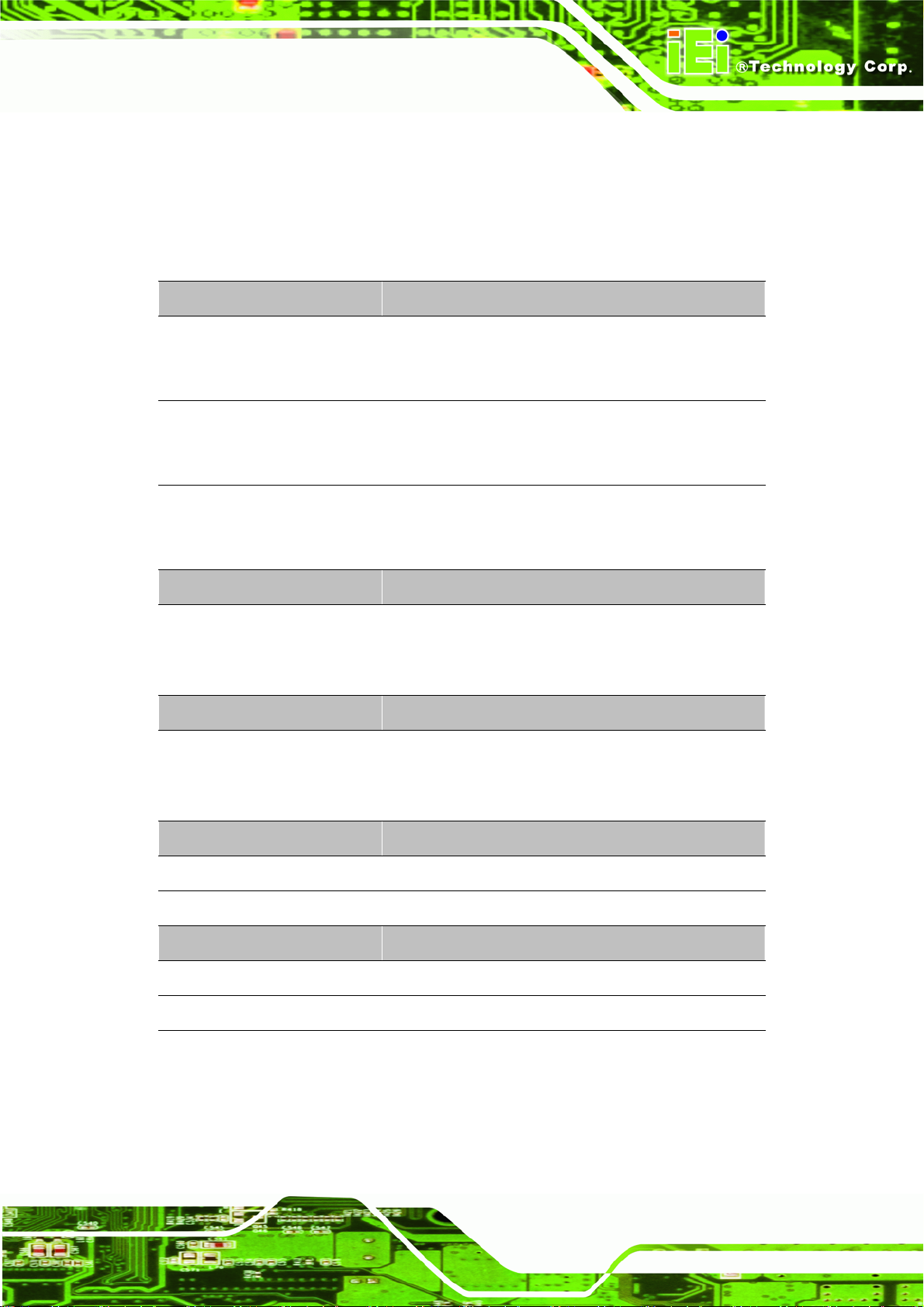

4.1.2 PEG Connector

Figure 4-1 illustrates the pinout definition for the standard PCI Express x16

connectors.

ICE Module

+V3.3_DU AL

SMB_CK3,4,5, 10,11,17, 20

SMB_DAT3,4,5, 10,11,17, 20

PCIE_WAKE_U P#3,5,10,16

PEG_TX0+3

PEG_TX0-3

SDVO_I2C_CK3

PEG_TX1+3

PEG_TX1-3

PEG_TX2+3

PEG_TX2-3

PEG_TX3+3

PEG_TX3-3

SDVO_I2C_D AT3

PEG_TX4+3

PEG_TX4-3

PEG_TX5+3

PEG_TX5-3

PEG_TX6+3

PEG_TX6-3

PEG_TX7+3

PEG_TX7-3

PEG_TX8+3

PEG_TX8-3

PEG_TX9+3

PEG_TX9-3

PEG_TX10+3

PEG_TX10-3

PEG_TX11+3

PEG_TX11-3

PEG_TX12+3

PEG_TX12-3

PEG_TX13+3

PEG_TX13-3

PEG_TX14+3

PEG_TX14-3

PEG_TX15+3

PEG_TX15-3

+V12 +V3.3

PCIEX16_1

TP43

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

B1

B2

B3

B4

B5

B6

B7

B8

B9

+12V03

+12V04

RSVD05

GND35

SMBCLK

SMBDATA

GND36

3_3V03

JTAG1

3_3VAUX

WAKE#

RSVD06

GND37

HSOP0

HSON0

GND38

PRSNT2#01

GND39

HSOP1

HSON1

GND40

GND41

HSOP2

HSON2

GND42

GND43

HSOP3

HSON3

GND44

RSVD07

PRSNT2#02

GND45

HSOP4

HSON4

GND46

GND47

HSOP5

HSON5

GND48

GND49

HSOP6

HSON6

GND50

GND51

HSOP7

HSON7

GND52

PRSNT2#03

GND53

HSOP8

HSON8

GND54

GND55

HSOP9

HSON9

GND56

GND57

HSOP10

HSON10

GND58

GND59

HSOP11

HSON11

GND60

GND61

HSOP12

HSON12

GND62

GND63

HSOP13

HSON13

GND64

GND65

HSOP14

HSON14

GND66

GND67

HSOP15

HSON15

GND68

PRSNT2#04

RSVD08

NC1

PCIE_X16

NC2

NC1

NC2

PRSNT1#

+12V01

+12V02

GND01

JTAG2

JTAG3

JTAG4

JTAG5

3_3V01

3_3V02

PWRGD

GND02

REFCLK+

REFCLK-

GND03

HSIP0

HSIN0

GND04

RSVD01

GND05

HSIP1

HSIN1

GND06

GND07

HSIP2

HSIN2

GND08

GND09

HSIP3

HSIN3

GND10

RSVD02

RSVD03

GND11

HSIP4

HSIN4

GND12

GND13

HSIP5

HSIN5

GND14

GND15

HSIP6

HSIN6

GND16

GND17

HSIP7

HSIN7

GND18

RSVD04

GND19

HSIP8

HSIN8

GND20

GND21

HSIP9

HSIN9

GND22

GND23

HSIP10

HSIN10

GND24

GND25

HSIP11

HSIN11

GND26

GND27

HSIP12

HSIN12

GND28

GND29

HSIP13

HSIN13

GND30

GND31

HSIP14

HSIN14

GND32

GND33

HSIP15

HSIN15

GND34

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

+V12+V3.3

CB_RESET# 3,5, 10,11,14, 20

CLK100M_PCIEx16_SLOT+ 4

R1710_4 12

R2230_4 12

R2240_4 12

R2250_4 12

R2260_4 12

R2270_4 12

R2280_4 12

R3760_4 12

R3780_4 12

R3790_4 12

R3800_4 12

R3810_4 12

R3820_4 12

R3830_4 12

R3840_4 12

R3850_4 12

R3860_4 12

R3870_4 12

R3880_4 12

R3890_4 12

R3900_4 12

R3910_4 12

R3920_4 12

R3930_4 12

R3940_4 12

R3950_4 12

R3960_4 12

R3970_4 12

R3990_4 12

R4000_4 12

R4010_4 12

CLK100M_PCIEx16_SLOT- 4

PEG_RX0+ 3

PEG_RX0- 3

PEG_RX1+ 3

PEG_RX1- 3

PEG_RX2+ 3

PEG_RX2- 3

PEG_RX3+ 3

PEG_RX3- 3

PEG_RX4+ 3

PEG_RX4- 3

PEG_RX5+ 3

PEG_RX5- 3

PEG_RX6+ 3

PEG_RX6- 3

PEG_RX7+ 3

PEG_RX7- 3

PEG_RX8+ 3

PEG_RX8- 3

PEG_RX9+ 3

PEG_RX9- 3

PEG_RX10+ 3

PEG_RX10- 3

PEG_RX11+ 3

PEG_RX11- 3

PEG_RX12+ 3

PEG_RX12- 3

PEG_RX13+ 3

PEG_RX13- 3

PEG_RX14+ 3

PEG_RX14- 3

PEG_RX15+ 3

PEG_RX15- 3

1

TP61

1

TP62

1

TP63

1

TP68

1

TP71

1R3770_4 12

TP72

1

TP73

1

TP74

1

TP75

1

TP76

1

TP77

1

TP78

1

TP79

1

TP81

1

TP82

1

TP83

1

TP84

1

TP85

1

TP86

1

TP87

Figure 4-1: PCI Express x16 Slot Example

Page 32

Page 46

ICE Module

4.1.3 SDVO

The Serial Digital Video Out (SDVO) display ports are multiplexed over a subset of the

External Graphics Interface using PCI Express. Users can choose a manufacturer

approved by Intel® to convert the SDVO port to TV, LVDS, DVI or CRT connection. IEI

also provides cables and SDVO card for customer to use. Due to the fact that SDVO is

an Intel® defined interface, the number of supported SDVO devices is limited to

devices that are supported by the Intel® Graphics Video BIOS and Graphics Driver

software.

The COM Express Module graphics controller configures the PEG lines for SDVO

operation if it detects that COM Express signals SDVO_I2C_CLK and

SDVO_I2C_DATA are pulled high to 2.5V, and if the PEG_ENABLE# line is left

floating. IEI BIOS auto detects the SDVO or PCIEX16, please reserve for future use.

Table 4-2: PEG & S DVO Pin Assignment

Pin Signal SDVO Description

C52

C53

C55

C56

C58

C59

C68

C69

D52

D53

D55

D56

D58

D59

D61

D62

D65

D66

D68

D69

D71

D72

D74

D75

PEG_RX0+

PEG_RX0PEG_RX1+

PEG_RX1PEG_RX2+

PEG_RX2PEG_RX5+

PEG_RX5PEG_TX0+

PEG_TX0PEG_TX1+

PEG_TX1PEG_TX2+

PEG_TX2PEG_TX3+

PEG_TX3PEG_TX4+

PEG_TX4PEG_TX5+

PEG_TX5PEG_TX6+

PEG_TX6PEG_TX7+

PEG_TX7-

SDVO_TVCLKIN+

SDVO_TVCLKINSDVOB_INT+

SDVOB_INT-

SDVO_FLDSTALL+

SDVO_FLDSTALL-

SDVOB_INT+

SDVOB_INT-

SDVOB_RED+

SDVOB_REDSDVOB_GREEN+

SDVOB_GREENSDVOB_BLUE+

SDVOB_BLUESDVOB_CLK+

SDVOB_CLKSDVOC_RED+

SDVOC_REDSDVOC_GREEN+

SDVOC_GREENSDVOC_BLUE+

SDVOC_BLUESDVOC_CLK+

SDVOC_CLK-

SDVO TVOUT Synchronization Clock

differential pair.

SDVOB Input Interrupt differential pair.

SDVO Field Stall differential pair.

SDVOC Input Interrupt differential pair.

SDVO Channel B Red differential pair.

SDVO Channel B Green differential pair.

SDVO Channel B Blue differential pair.

SDVO Channel B Clock differential pair.

SDVO Channel C Red differential pair.

SDVO Channel C Green differential pair.

SDVO Channel C Blue differential pair.

SDVO Channel C Clock differential pair.

Table 4-3: Intel® SDVO Support Device List

Device Vander Application Link

Page 33

Page 47

CH7021A Chrontel SDTV / HDTV Transmitter http://www.chrontel.com

CH7308A Chrontel LVDS Transmitter http://www.chrontel.com

CH7307C Chrontel DVI Transmitter http://www.chrontel.com

CH7312 Chrontel DVI Transmitter http://www.chrontel.com

CX25905 Conexant DVI-D / TV / CRT Transmitter http://www.conexant.com

SiL1362/1364 Silicon Image DVI Transmitter http://www.siliconimage.com

SiL 1390 Silicon Image HDMI Transmitter http://www.siliconimage.com

ICE Module

4.1.4 PEG_ENABLE#

PEG_ENABLE# is defined on the COM Express connector as a method to configure

the COM Express PCIe lanes 16 through 32 on the C-D connector as a PCI Express

Graphics port, for use with an external graphics device. The usual effect of pulling

PEG_ENABLE# low is to disable the on-Module graphics engine. For some Modules,

it is possible to configure the Module such that the internal graphics engine remains

active, even when the external PEG interface is being used for a Carrier Board

graphics device. This is Module dependent. Check with your vendor. ICE Modules

implement the auto-detect function. So, please reserve this pin for future use.

4.1.5 PCI Express Test Points and Probing

IEI follows the suggestion provided by Intel® to preserve 0-Ω on the baseboard.

Additional test structures were not included in the simulation sweeps that this

guideline is based on. The inclusion of test points and probing structures has the

ability to impact the loss and jitter budgets of a PCI Express interconnect. This is not to

say that they cannot be tolerated. In general, test points and probe structures should

not introduce stubs on the differential pairs or cause significant deviation from the

recommendations given throughout this chapter. Existing vias, pads or pins should be

used wherever possible to accommodate such structures. Careful consideration must

be taken whenever additional probing structures are used.

Page 34