Integrated Device Technology Inc IDT7M1002S45GB, IDT7M1002S40GB, IDT7M1002S35G, IDT7M1002S30G Datasheet

Integrated Device Technology, Inc.

16K x 32 CMOS

DUAL-PORT STATIC RAM

MODULE

IDT7M1002

FEATURES

• High-density 512K CMOS Dual-Port RAM module

• Fast access times

—Commercial: 30, 35ns

—Military: 40, 45ns

• Fully asynchronous read/write operation from either port

• Easy to expand data bus width to 64 bits or more using

the Master/Slave function

• Separate byte read/write signals for byte control

• On-chip port arbitration logic

•

INT

flag for port-to-port communication

• Full on-chip hardware support of semaphore signaling

between ports

• Surface mounted fine pitch (25 mil) LCC packages allow

through-hole module to fit into 121 pin PGA footprint

• Single 5V (±10%) power supply

• Inputs/outputs directly TTL-compatible

DESCRIPTION

The IDT7M1002 is a 16K x 32 high-speed CMOS Dual-Port

Static RAM Module constructed on a co-fired ceramic substrate using four 16K x 8 (IDT7006) Dual-Port Static RAMs in

surface-mounted LCC packages. The IDT7M1002 module is

designed to be used as stand-alone 512K Dual-Port RAM or

as a combination Master/Slave Dual-Port RAM for 64-bit or

more word width systems. Using the IDT Master/Slave approach in such system applications results in full-speed, errorfree operation without the need for additional discrete logic.

The module provides two independent ports with separate

control, address, and I/O pins that permit independent and

asynchronous access for reads or writes to any location in

memory. System performance is enhanced by facilitating

port-to-port communication via additional control signals

and

INT

.

The IDT7M1002 module is packaged in a ceramic 121 pin

PGA (Pin Grid Array)1.35 inches on a side. Maximum access

times as fast as 30ns are available over the commercial

temperature range and 40ns over the military temperature

range.

All IDT military modules are constructed with semiconductor components manufactured in compliance with the latest

revision of MIL-STD-883, Class B making them ideally suited

to applications demanding the highest level of performance

and reliability.

SEM

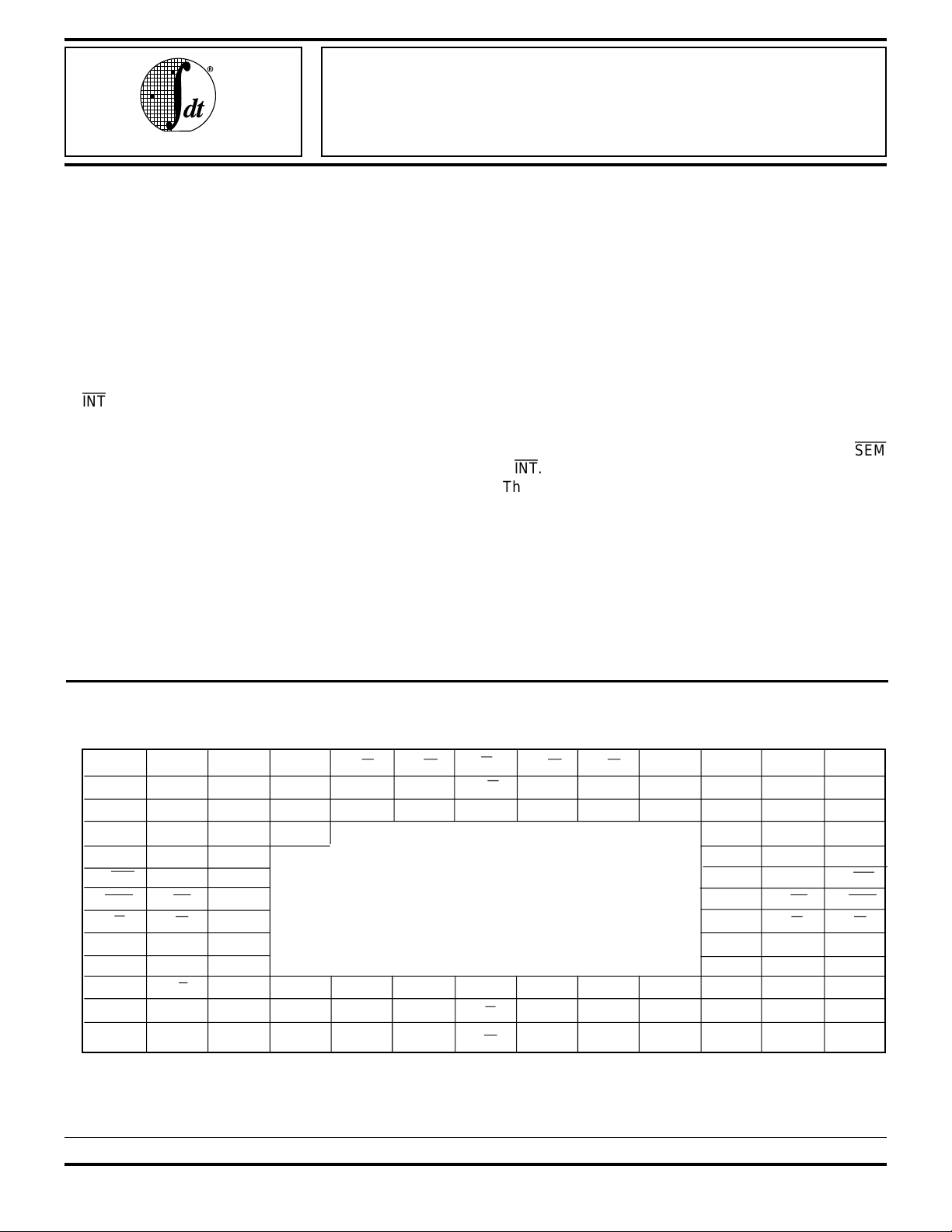

PIN CONFIGURATION

1234 56 78

L_CS L_OE R_OE R_CS

L_I/O(23) L_R/W(4) R_I/O(27) R_I/O(23)R_I/O(25)R_I/O(29)R_I/O(31)R_A(0)L_A(0)L_I/O(31)L_I/O(29)L_I/O(27)L_I/O(25)B

L_SEM

L_BUSY

H

L_R/W

L_I/O(15) L_I/O(14) L_A(8) R_I/O(15)R_I/O(14)R_A(8)I

L_I/O(13) L_I/O(12) L_A(9) R_I/O(13)R_A(9) R_I/O(12)J

L_I/O(11) GND L_A(10) R_I/O(11)VCC GNDR_A(10)R_A(11)R_A(12)GNDL_A(12)L_A(11)K

L_I/O(10) L_I/O(8) L_I/O(6) R_I/O(10)R_I/O(6) R_I/O(8)

L_I/O(9) L_I/O(7) L_I/O(5) R_I/O(9)R_I/O(5) R_I/O(7)

The IDT logo is a registered trademark of Integrated Device Technology Inc.

L_I/O(16) L_A(6) R_A(6) R_I/O(16)F

L_INT R_INT R_BUSY

(1)

L_R/W(2)

M/S

GND GNDG

L_A(7) R_A(7)

PGA

TOP VIEW

R_R/W (4)

R_R/W (3)

MILITARY AND COMMERCIAL TEMPERATURE RANGES DECEMBER 1995

©1996 Integrated Device Technology, Inc. DSC-2795/5

7.02 1

910

R_I/O(28) R_I/O(24)R_I/O(26)R_I/O(30)L_R/W(3)L_I/O(30)L_I/O(28)L_I/O(26)L_I/O(24)A

R_A(4) R_I/O(19)R_I/O(20)GNDL_A(4)L_I/O(20)L_I/O(19)D

R_A(5) R_I/O(17)R_I/O(18)L_A(5)L_I/O(18)L_I/O(17)E

R_I/O(4)R_I/O(2)R_A(13)L_A(13)L_I/O(2)L_I/O(4)L

R_I/O(3)R_I/O(1)R_I/O(0)L_I/O(0)L_I/O(1)L_I/O(3)M

11 12 13

GND R_I/O(21)R_I/O(22)R_A(3)R_A(2)R_A(1)GNDL_A(1)L_A(2)L_A(3)VCCL_I/O(22)L_I/O(21)C

R_SEM

R_R/W (2) R_R/W (1)

2795 drw 01

IDT7M1002

16K x 32 CMOS DUAL-PORT STATIC RAM MODULE MILITARY AND COMMERCIAL TEMPERATURE RANGES

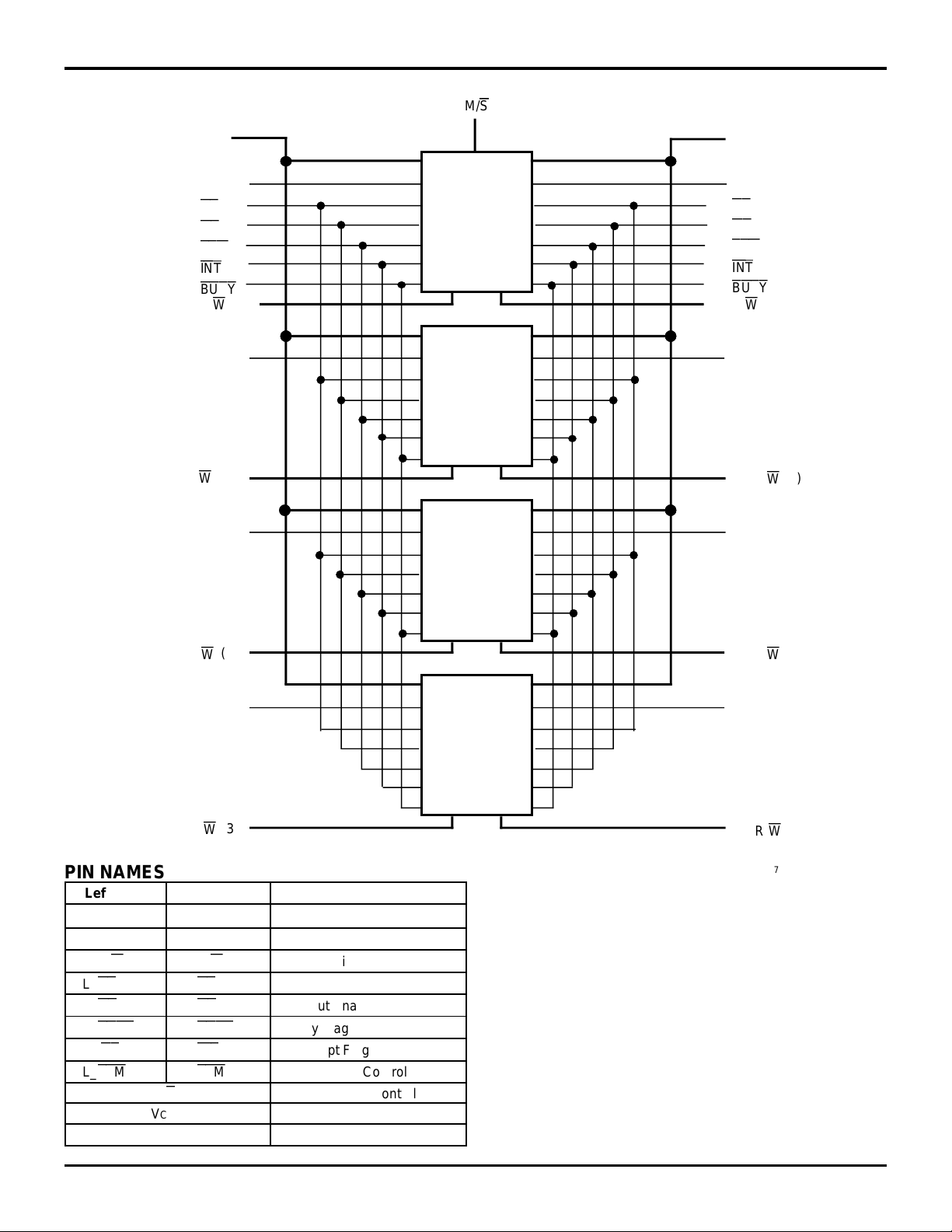

FUNCTIONAL BLOCK DIAGRAM

L_A(0–13)

L_I/O(0–7)

L_

CS

L_

OE

L_

SEM

L_

INT

L_

BUSY

(0)

L_

R/

W

L_I/O(8–15)

R/

(1)

W

L_

L_I/O(16–23)

M/S

IDT7006

16K x 8

(ARBITRATION

LOGIC)

IDT7006

16K x 8

(ARBITRATION

LOGIC)

IDT7006

16K x 8

R_A(0–13)

R_I/O(0–7)

R_

CS

R_

OE

R_

SEM

R_

INT

R_

BUSY

R/

W

(0)

R_

R_I/O(8–15)

R_

R/

R_I/O(16–23)

(1)

W

R/

(2)

W

L_

L_I/O(24–31)

L_ R_

(3)

R/

W

PIN NAMES

Left Port Right Port Description

L_A (0–13) R_A (0–13) Address Inputs

L_I/O (0–31) R_I/O (0–31) Data Inputs/Outputs

L_R/W (1–4) R_R/W (1–4) Read/Write Enables

L_

L_

L_

L_I

L_

CS

OE

BUSY

NT

SEM

R_

M/

CS

R_

OE

R_

BUSY

R_

INT

R_

SEM

S

Chip Select

Output Enable

Busy Flag

Interrupt Flag

Semaphore Control

Master/Slave Control

VCC Power

GND Ground

(ARBITRATION

LOGIC)

IDT7006

16K x 8

(ARBITRATION

LOGIC)

2795 tbl 01

R/

(2)

W

R_

R_I/O(24–31)

(3)

R/

W

2795 drw 02

7.02 2

IDT7M1002

16K x 32 CMOS DUAL-PORT STATIC RAM MODULE MILITARY AND COMMERCIAL TEMPERATURE RANGES

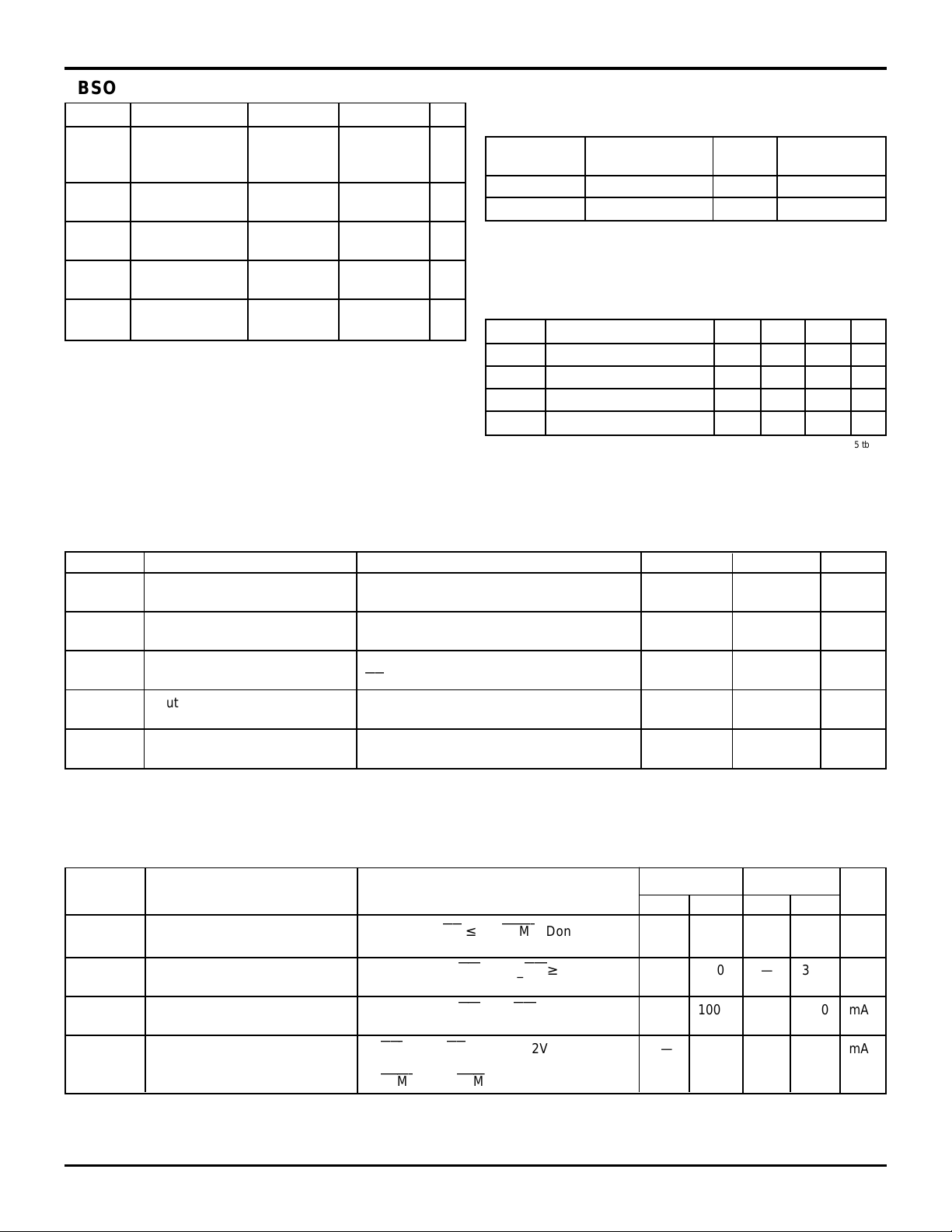

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Rating Commerical Military Unit

TERM Terminal Voltage –0.5 to +7.0 –0.5 to +7.0 V

V

with Respect to

GND

A Operating 0 to +70 –55 to +125 °C

T

Temperature

BIAS Temperature –55 to +125 –65 to +135 °C

T

Under Bias

STG Storage –55 to +125 –65 to +150 °C

T

Temperature

OUT DC Output 50 50 mA

I

Current

NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any other conditions above those

indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may

affect reliability.

2795 tbl 02

DC ELECTRICAL CHARACTERISTICS

(VCC = 5V ± 10%, TA = –55°C to +125°C or 0°C to +70°C)

RECOMMENDED OPERATING

TEMPERATURE AND SUPPLY VOLTAGE

Ambient

Grade Temperature GND VCC

Military –55°C to +125°C 0V 5.0V ± 10%

Commercial 0°C to +70°C 0V 5.0V ± 10%

2795 tbl 03

RECOMMENDED DC

OPERATING CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

VCC Supply Voltage 4.5 5.0 5.5 V

GND Supply Voltage 0 0 0 V

VIH Input High Voltage 2.2 — 6.0 V

IL Input Low Voltage –0.5

V

NOTE:

1. VIL ≥ –3.0V for pulse width less than 20ns

(1)

— 0.8 V

2795 tbl 04

Symbol Parameter Test Conditions Min. Max. Units

LI| Input Leakage VCC = Max. — 40 µA

|I

(Address & Control) VIN = GND to VCC

|ILI| Input Leakage VCC = Max. — 10 µA

(Data) VIN = GND to VCC

|ILO| Output Leakage VCC = Max. — 10 µA

(Data)

CS

≥ VIH, VOUT = GND to VCC

VOL Output Low VCC = Min. IOL = 4mA — 0.4 V

Voltage

OH Output High VCC = Min, IOH = –4mA 2.4 — V

V

Voltage

DC ELECTRICAL CHARACTERISTICS

(VCC = 5V ± 10%, TA = –55°C to +125°C or 0°C to +70°C)

Commercial Military

Symbol Parameter Test Conditions Min. Max. Min. Max. Units

I

CC2 Dynamic Operating Current VCC = Max.,

(Both Ports Active) Outputs Open, f = fMAX

ISB Standby Supply Current VCC = Max., L_

(Both Ports Inactive) Outputs Open, f = fMAX

ISB1 Standby Suppy Current VCC = Max., L_

(One Port Inactive) Outputs Open, f = fMAX

ISB2 Full Standby Supply Current L_

(Both Ports Inactive) V

CS

IN > VCC – 0.2V or < 0.2V

L_

SEM

CS

≤ VIL,

SEM

= Don’t Care — 1360 — 1600 mA

CS

and R_

CS

≥ VIH — 280 — 340 mA

CS

or R_

CS

≥ VIH — 1000 — 1160 mA

and R_CS ≥ VCC – 0.2V — 60 — 120 mA

and R_

SEM

≥ V

CC – 0.2V

2795 tbl 05

2795 tbl 06

7.02 3

IDT7M1002

16K x 32 CMOS DUAL-PORT STATIC RAM MODULE MILITARY AND COMMERCIAL TEMPERATURE RANGES

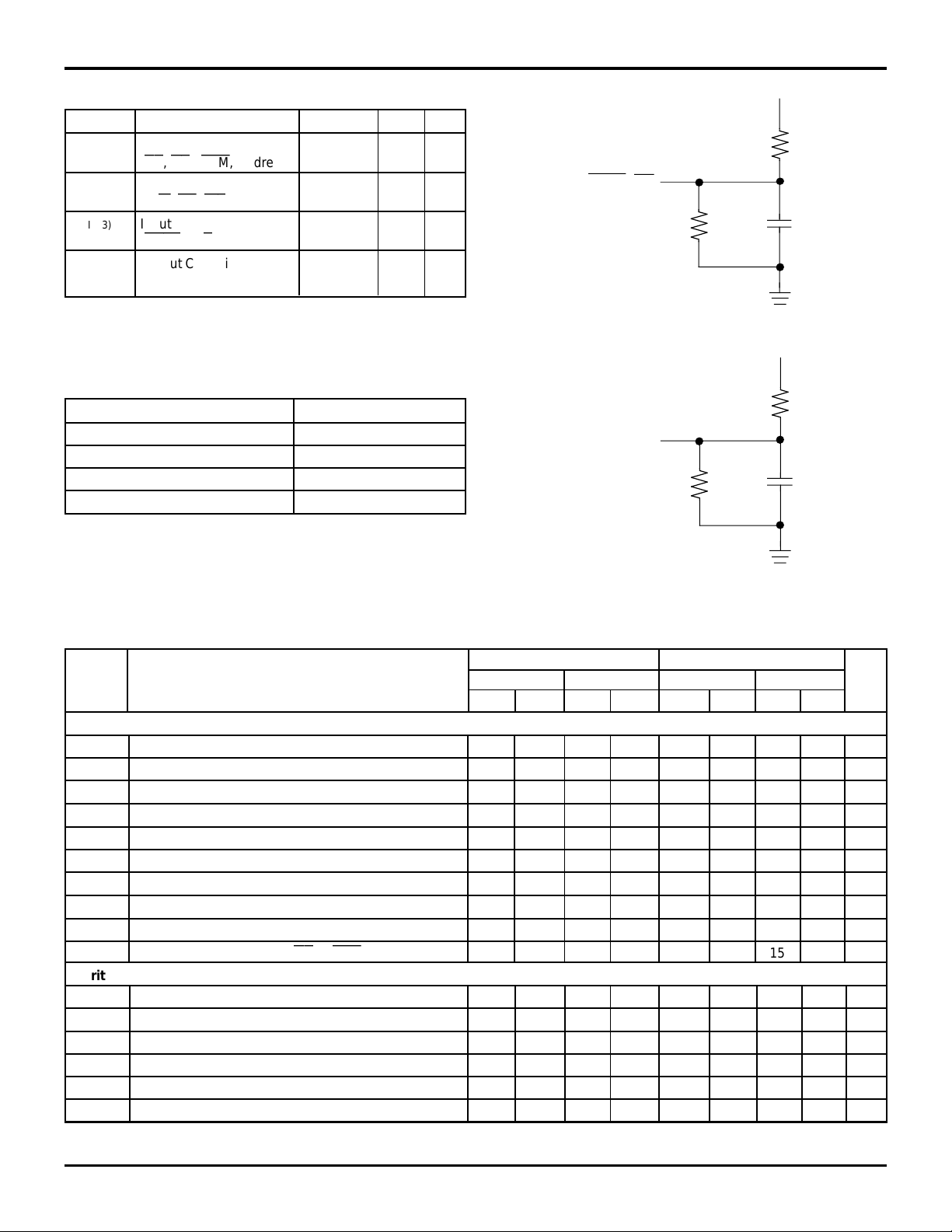

CAPACITANCE

(1)

(TA = +25°C, f = 1.0MHz)

+5V

Symbol Parameter Condition Max. Unit

IN (1) Input Capacitance VIN = 0V 40 pF

C

(CS, OE,

IN(2) Input Capacitance VIN = 0V 12 pF

C

(R/W,

IN(3) Input Capacitance VIN = 0V 45 pF

C

(

BUSY

OUT Output Capacitance VOUT = 0V 12 pF

C

SEM

I/O, INT

, M/S)

, Address)

)

BUSY, INT

255Ω

480Ω

30pF*

(I/O)

*Including scope and jig capacitances.

Figure 1. Output Load

2795 drw 03

NOTE:

1. This parameter is guaranteed by design but not tested.

2795 tbl 07

+5V

AC TEST CONDITIONS

Input Pulse Levels GND to 3.0V

Input Rise/Fall Times 5ns

DATA

OUT

Input Timing Reference Levels 1.5V

Output Reference Levels 1.5V

255Ω

Output Load See Figures 1 and 2

2795 tbl 08

*Including scope and jig capacitances.

Figure 2. Output Load

CHZ, tCLZ, tOHZ, tOLZ, tWHZ, tOW)

AC ELECTRICAL CHARACTERISTICS

(For t

(VCC = 5V ± 10%, TA = –55°C to +125°C or 0°C to +70°C)

7M1002SxxG 7M1002SxxGB

30 –35 –40 –45

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Unit

Read Cycle

tRC Read Cycle Time 30 — 35 — 40 — 45 — ns

tAA Address Access Time — 30 — 35 — 40 — 45 ns

(2)

tACS

tOE Output Enable Access Time — 17 — 20 — 22 — 25 ns

tOH Output Hold from Address Change 3 — 3 — 3 — 3 — ns

tLZ

tHZ

tPU

tPD

tSOP Sem. Flag Update Pulse (OE or

Write Cycle

tWC Write Cycle Time 30 — 35 — 40 — 45 — ns

tCW

tAW Address Valid to End-of-Write 25 — 30 — 35 — 40 — ns

tAS Address Set-Up Time 0 — 0 — 0 — 0 — ns

tWP Write Pulse Width 25 — 30 — 35 — 35 — ns

tWR Write Recovery Time 0 — 0 — 0 — 0 — ns

Chip Select Access Time — 30 — 35 — 40 — 45 ns

(1)

Output to Low-Z 3 — 3 — 3 — 5 — ns

(1)

Output to High-Z — 15 — 15 — 17 — 20 ns

(1)

Chip Select to Power Up Time 0 — 0 — 0 — 0 — ns

(1)

Chip Deselect to Power Up Time — 50 — 50 — 50 — 50 ns

SEM

) 15 — 15 — 15 — 15 — ns

(2)

Chip Select to End-of-Write 25 — 30 — 35 — 40 — ns

(Continued on next page)

480Ω

5pF*

2795 drw 04

2795 tbl 09

7.02 4

Loading...

Loading...