IDT IDT71016 User Manual

A

,

CMOS Static RAM

1 Meg (64K x 16-Bit)

IDT71016

Features

◆◆

◆

◆◆

64K x 16 advanced high-speed CMOS Static RAM

◆◆

◆

◆◆

Equal access and cycle times

– Commercial and Industrial: 12/15/20ns

◆◆

◆

◆◆

One Chip Select plus one Output Enable pin

◆◆

◆

◆◆

Bidirectional data inputs and outputs directly TTLcompatible

◆◆

◆

◆◆

Low power consumption via chip deselect

◆◆

◆

◆◆

Upper and Lower Byte Enable Pins

◆◆

◆

◆◆

Commercial and industrial product available in 44-pin

Plastic SOJ package and 44-pin TSOP package

Functional Block Diagram

OE

0-A15

Output

Enable

Buffer

Address

Buffers

Row / Column

Decoders

Description

The IDT71016 is a 1,048,576-bit high-speed Static RAM organized

as 64K x 16. It is fabricated using IDT’s high-perfomance, high-reliability

CMOS technology. This state-of-the-art technology, combined with

innovative circuit design techniques, provides a cost-effective solution for

high-speed memory needs.

The IDT71016 has an output enable pin which operates as fast as 7ns,

with address access times as fast as 12ns. All bidirectional inputs and

outputs of the IDT71016 are TTL-compatible and operation is from a single

5V supply. Fully static asynchronous circuitry is used, requiring no clocks

or refresh for operation.

The IDT71016 is packaged in a JEDEC standard 44-pin Plastic SOJ

and 44-pin TSOP Type II.

I/O 15

CS

WE

BHE

BLE

Chip

Enable

Buffer

Write

Enable

Buffer

Byte

Enable

Buffers

64Kx16

Memory

Array

Sense

16

Amps

and

Write

Drivers

8

8

High

Byte

I/O

Buffer

Low

Byte

I/O

Buffer

8

I/O 8

I/O 7

8

I/O 0

3210drw01

JANUARY 2004

©2004 Integrated Device Technology, Inc.

1

DSC-3210/8

IDT71016, CMOS Static RAM

I

I

I

I

I

I

I

I

,

1 Meg (64K x 16-bit) Commercial and Industrial Temperature Ranges

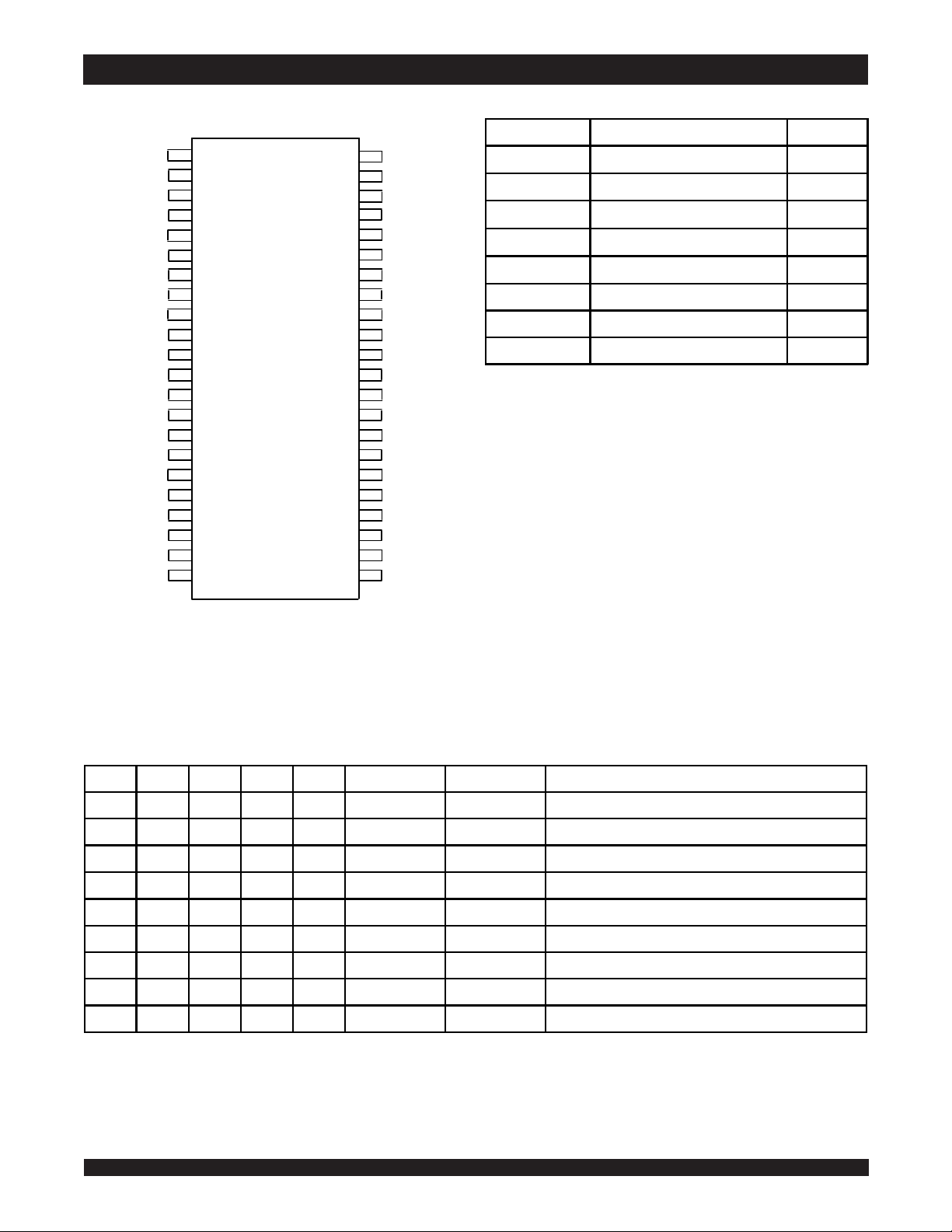

Pin Configurations

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

SO44-1

SO44-2

A4

A3

A2

A1

A0

CS

/O 0

/O 1

/O 2

/O 3

V

CC

V

/O 4

/O 5

/O 6

/O 7

WE

A15

A14

A13

A12

NC

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

A5

A6

A7

OE

BHE

BLE

I/O 15

I/O 14

I/O 13

I/O 12

SS

V

V

CC

I/O 11

I/O 10

I/O 9

I/O 8

NC

A8

A9

A10

A11

NC

Pin Descriptions

A0 - A

15

CS

WE

OE

High Byte Enable Input

Low Byte Enable Input

Data Inp ut/ Outp ut I/O

I/O

BHE

BLE

0

- I/O

V

V

15

CC

SS

Address Inputs Input

Chip Select Input

Write Enab le Input

Outp ut En ab le Inp ut

5.0V Po wer Pwr

Ground Gnd

3 2 10 t b l 01

3210drw 02

SOJ/TSOP

Top View

Truth Table

CS OE WE BLE BHE

H X X X X High-Z High-Z Deselected - Standby

LLHLH DATAOUT High-Z Low Byte Read

L L H H L Hig h-Z DATAO UT Hig h B y te Re ad

L L H L L DATAO UT DATAO UT` Word R ea d

L X L L L DATAIN DATAIN Wo rd Wri te

L X L L H DATAIN High-Z Low Byte Write

L X L H L High-Z DATAIN High Byte Write

L H H X X High-Z High-Z Outputs Disabled

L X X H H High-Z High-Z Outputs Disabled

NOTE:

1. H = VIH, L = VIL, X = Don't care.

(1)

0

- I/O

I/O

7

I/O8 - I/ O

15

Function

3210 tbl 02

6.422

IDT71016, CMOS Static RAM

1 Meg (64K x 16-bit) Commercial and Industrial Temperature Ranges

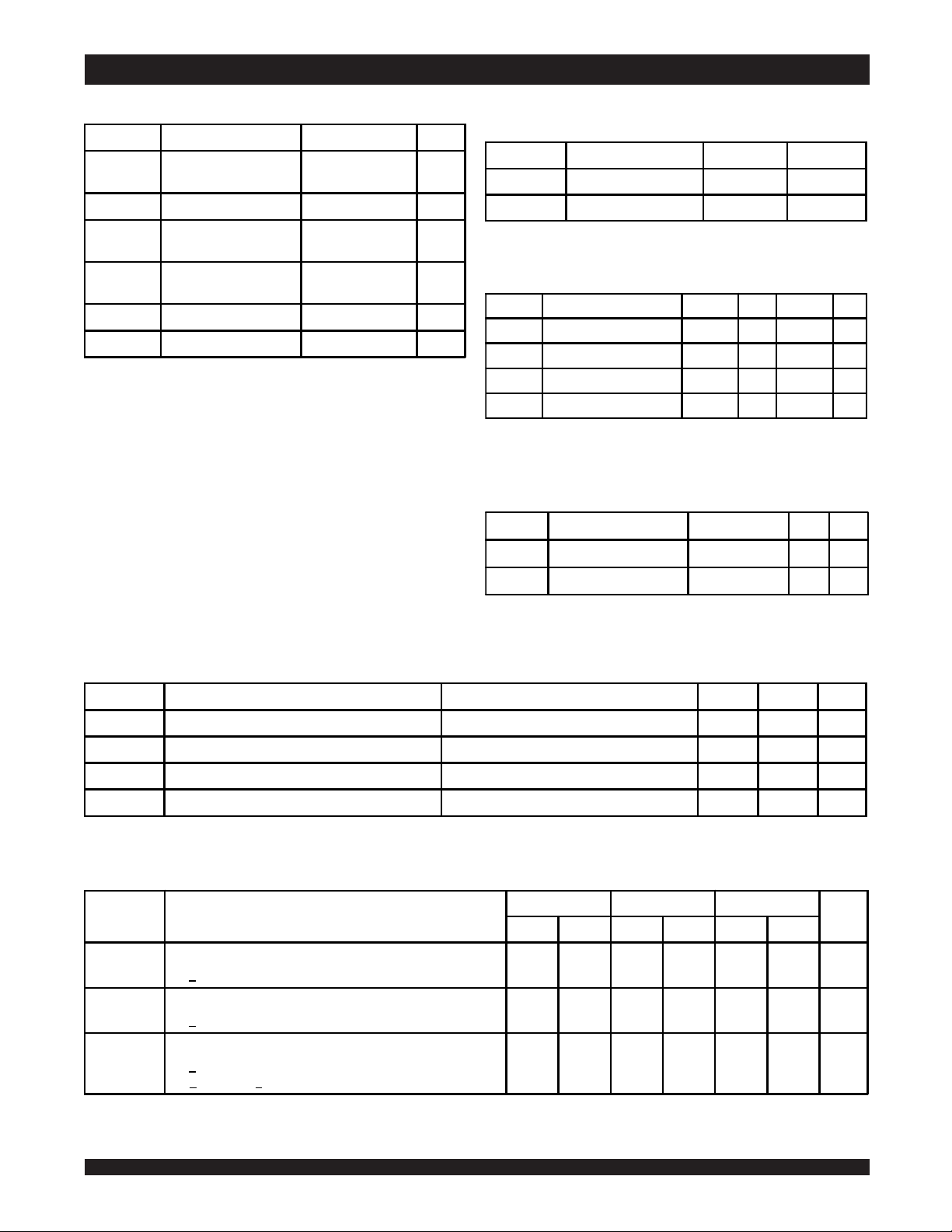

Absolute Maximum Ratings

Symbol Rating Value Unit

(2)

V

TERM

A

T

T

BIAS

STG

T

T

P

I

OUT

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may

cause permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect reliability.

2. V

TERM must not exceed VCC + 0.5V.

Terminal Voltage with

-0.5 to +7.0 V

Respect to GND

Operating Temperature 0 to +70

Temperature

-55 to + 125

Under Bias

Storage

-55 to + 125

Temperature

Pow er D issipation 1. 25 W

DC Output Current 50 m A

(1)

o

C

o

C

o

C

3210 tbl 03

Recommended Operating

Temperature and Supply Voltage

Grade Temperature GND V

Com m ercial 0° C to +70° C 0V 5.0V ± 10%

Indust rial –40°C to +85° C 0V 5.0V ± 10%

CC

3210 tbl 0 4

Recommended DC Operating

Conditions

Symbol Parameter Min. Typ. Max. Unit

CC

Supply Voltage 4.5 5. 0 5.5 V

V

GND Ground 0 0 0 V

IH

Input High Voltage 2.2

V

IL

Input Low Voltage -0.5

V

NOTE:

1. VIL (min.) = –1.5V for pulse width less than tRC/2, once per cycle.

____

V

DD

+0.5 V

(1)

____

0.8 V

3210 tbl 05

Capacitance

(TA = +25° C, f = 1.0MHz, SOJ Package)

Symbol Parameter

(1)

Conditions Max. Unit

C

IN

Input Capacitance VIN = 3dV 6 pF

I/O

I/O Capacitance V

C

OUT

= 3dV 7 pF

NOTE:

1. This parameter is guaranteed by device characterization, but not production

tested.

DC Electrical Characteristics

(VCC = 5.0V ± 10%, Commercial and Industrial Temperature Range)

Symbol Parameter Test Conditions Min. Max. Unit

LI

| Input Leak age Current VCC = Max., VIN = GND to V

|I

LO

| Output Leakage Current VCC = Max., CS = VIH, V

|I

OL

V

OH

V

Output Low Voltage IOL = 8mA, VCC = Min.

Output H igh Voltage IOH = -4mA, VCC = M in. 2.4

DC Electrical Characteristics

(1)

CC

OUT

= GND to V

CC

(VCC = 5.0V ± 10%, VLC = 0.2V, VHC = VCC–0.2V)

71016S12 71016S15 71016S20

Symbol Parameter Com'l. Ind. Com'l. Ind. Com'l. Ind. Unit

I

CC

I

SB

Dy namic O perating Current

VIL, Outputs Open, VCC = Max., f = f

CS <

Standby Power Supply Current (TTL Level)

VIH, Outputs Open, VCC = Max., F = f

CS >

MAX

MAX

(2)

(2)

210 210 180 180 170 170 mA

60 60 50 50 45 45 mA

___

___

___

5µA

5µA

0.4 V

___

3210 tbl 06

V

3210 tbl 07

SB1

I

Standby Pow er Supply C urrent (CM OS Lev el)

VHC, Out puts Open, VCC = Max., f = 0

CS >

VIN < VLC or VIN > V

HC

(2)

10 10 10 10 10 10 mA

NOTES:

1. All values are maximum guaranteed values.

2. fMAX = 1/tRC (all address inputs are cycling at fMAX); f = 0 means no address input lines are changing .

6.42

3

3210 tbl 08

Loading...

Loading...