Integrated Device Technology Inc IDT7015S15G, IDT7015S15J, IDT7015S15PF, IDT7015S17G, IDT7015S17J Datasheet

...

Integrated Device Technology, Inc.

HIGH-SPEED

8K x 9 DUAL-PORT

STATIC RAM

IDT7015S/L

FEATURES:

• True Dual-Ported memory cells which allow simultaneous access of the same memory location

• High-speed access

— Military: 20/25/35ns (max.)

— Commercial: 12/15/17/20/25/35ns (max.)

• Low-power operation

— IDT7015S

Active: 750mW (typ.)

Standby: 5mW (typ.)

— IDT7015L

Active: 750mW (typ.)

Standby: 1mW (typ.)

• IDT7015 easily expands data bus width to 18 bits or

more using the Master/Slave select when cascading

more than one device

•M/S = H for

M/S = L for

BUSY

output flag on Master

BUSY

input on Slave

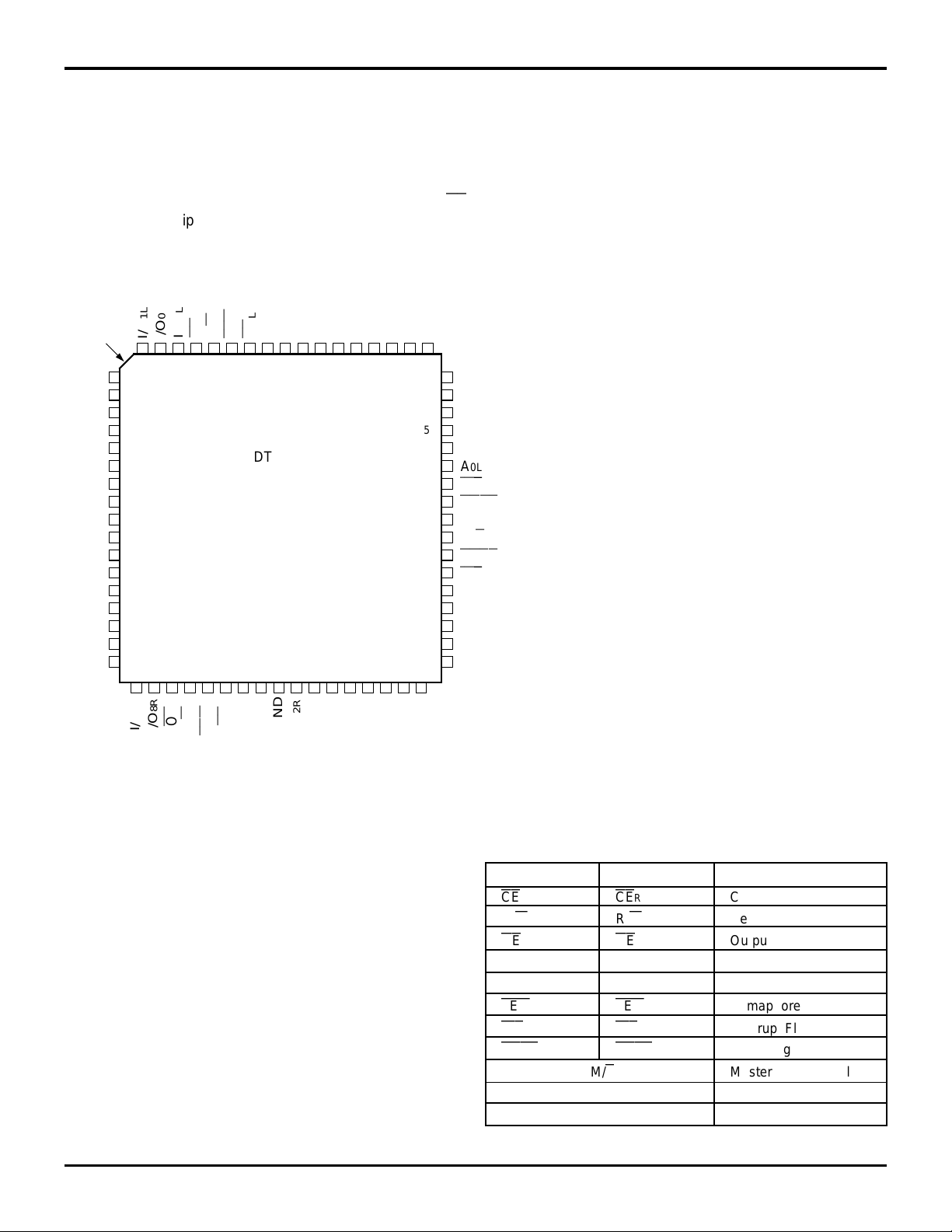

FUNCTIONAL BLOCK DIAGRAM

OE

L

CE

L

R/

W

L

• Interrupt and Busy Flags

• On-chip port arbitration logic

• Full on-chip hardware support of semaphore signaling

between ports

• Fully asynchronous operation from either port

• Devices are capable of withstanding greater than 2001V

electrostatic discharge

• TTL-compatible, single 5V (±10%) power supply

• Available in ceramic 68-pin PGA, 68-pin PLCC, and an

80-pin TQFP

• Industrial temperature range (–40°C to +85°C) is available, tested to military electrical specifications

DESCRIPTION:

The IDT7015 is a high-speed 8K x 9 Dual-Port Static

RAMs. The IDT7015 is designed to be used as stand-alone

Dual-Port RAM or as a combination MASTER/SLAVE DualPort RAM for 18-bit-or-more word systems. Using the IDT

OE

R

CE

R

R/

W

R

I/O0L- I/O

NOTES:

1. In MASTER mode:

In SLAVE mode:

2.

BUSY

outputs and

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

BUSY

SEM

INT

8L

(1,2)

L

A

12L

A

0L

L

(2)

L

BUSY

is an output and is a push-pull driver

BUSY

is input.

INT

outputs are non-tri-stated push-pull drivers.

Address

Decoder

CE

OE

R/

W

L

L

L

13

I/O

Control

MEMORY

ARRAY

ARBITRATION

INTERRUPT

SEMAPHORE

LOGIC

M/

S

I/O

Control

I/O0R-I/O

Address

Decoder

13

CE

R

OE

R

R/

W

R

SEM

INT

2954 drw 01

BUSY

A

12R

A

0R

R

8R

(1,2)

R

R

(2)

MILITARY AND COMMERCIAL TEMPERATURE RANGES OCTOBER 1996

©1996 Integrated Device Technology, Inc. DSC-2954/2

For latest information contact IDT’s web site at www.idt.com or fax-on-demand at 408-492-8391.

6.12 1

IDT7015S/L

HIGH-SPEED 8K x 9 DUAL-PORT STATIC RAM MILITARY AND COMMERCIAL TEMPERATURE RANGES

MASTER/SLAVE Dual-Port RAM approach in 18-bit or wider

memory system applications results in full-speed, error-free

operation without the need for additional discrete logic.

This device provides two independent ports with separate

control, address, and I/O pins that permit independent,

asynchronous access for reads or writes to any location in

memory. An automatic power down feature controlled by

CE

permits the on-chip circuitry of each port to enter a very low

standby power mode.

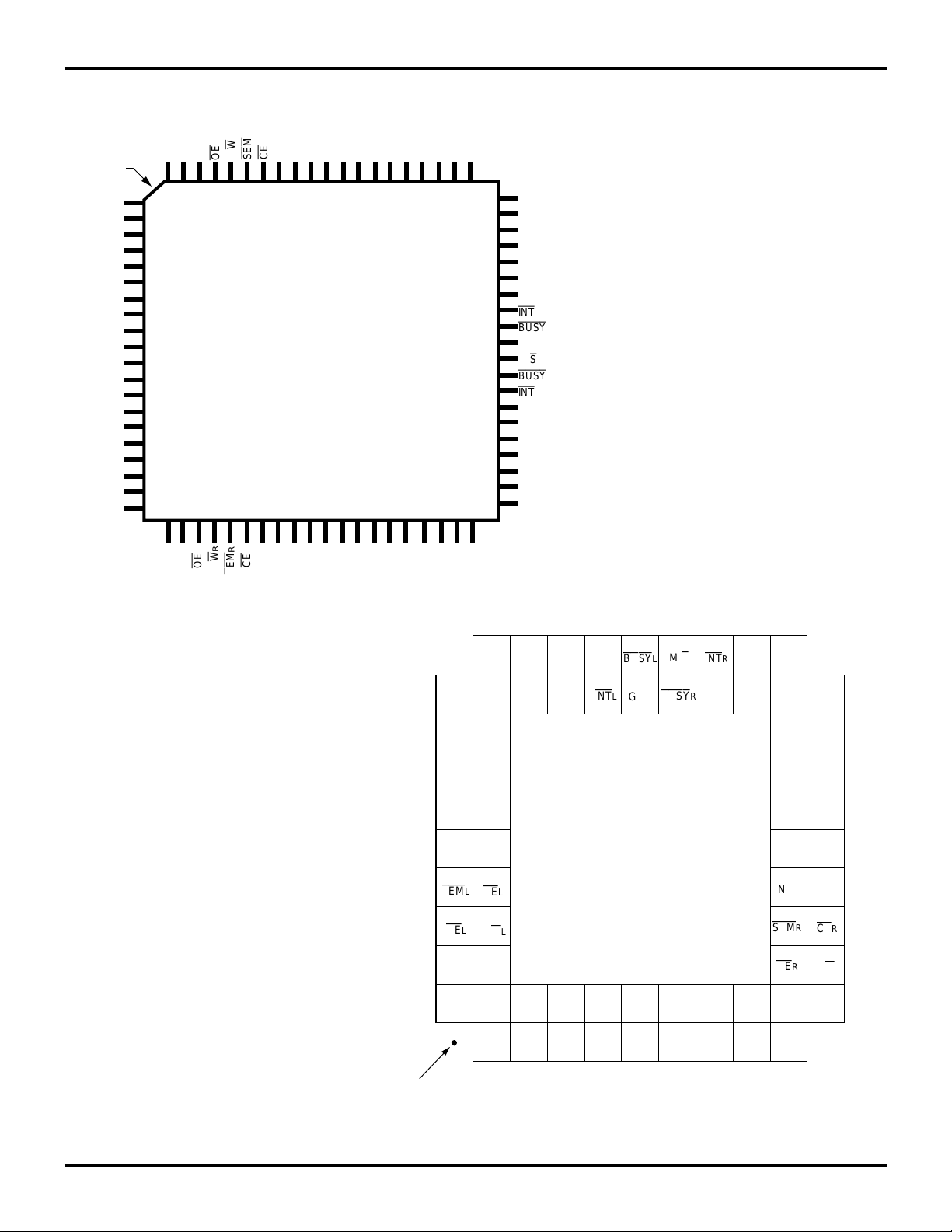

PIN CONFIGURATIONS

L

L

8L

1L

INDEX

I/O

2L

I/O

3L

I/O

4L

I/O

5L

GND

I/O

6L

I/O

7L

V

CC

GND

0R

I/O

I/O

1R

I/O

2R

V

CC

I/O

3R

I/O

4R

I/O

5R

I/O

6R

0L

I/O

I/O

98765432168676665

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27 28 29 30 31 32 33 34 35 36 37 38 39

I/O

OE

W

R/

(1,2)

L

L

CE

SEM

N/C

IDT7015

(8K x 9)

J68-1

PLCC

TOP VIEW

N/C

CC

V

12L

A

(3)

A

A

64 63 62 61

40 41 42 43

A

A

A

A

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

6L

7L

8L

9L

10L

11L

Fabricated using IDT’s CMOS high-performance technol-

ogy, these devices typically operate on only 750mW of power.

The IDT7015 is packaged in a ceramic 68-pin PGA, a 64pin PLCC and an 80-pin TQFP (Thin Quad FlatPack). Military

grade product is manufactured in compliance with the latest

revision of MIL-STD-883, Class B, making it ideally suited to

military temperature applications demanding the highest level

of performance and reliability.

A

5L

4L

A

A

3L

A

2L

A

1L

A

0L

INT

L

BUSY

L

GND

M/

S

R

BUSY

INT

R

A

0R

A

1R

A

2R

A

3R

A

4R

R

R

R

7R

8R

OE

I/O

I/O

NOTES:

CC pins must be connected to power supply.

1. All V

2. All GND pins must be connected to ground supply.

3. This text does not imply orientation of Part-Mark.

W

R/

SEM

R

CE

N/C

N/C

12R

GND

A

11R

A

10R

A

9R

A

8R

A

7R

A

6R

A

5R

A

2954 drw 02

PIN NAMES

CE

R/

W

OE

A

0L – A12L A0R – A12R Address

I/O

SEM

INT

BUSY

Left Port Right Port Names

L

L R/WR Read/Write Enable

L

0L – I/O8L I/O0R – I/O8R Data Input/Output

L

L

L

CE

R Chip Enable

OE

R Output Enable

SEM

R Semaphore Enable

INT

R Interrupt Flag

BUSY

R Busy Flag

M/

S

V

CC Power

Master or Slave Select

GND Ground

2954 tbl 01

6.12 2

IDT7015S/L

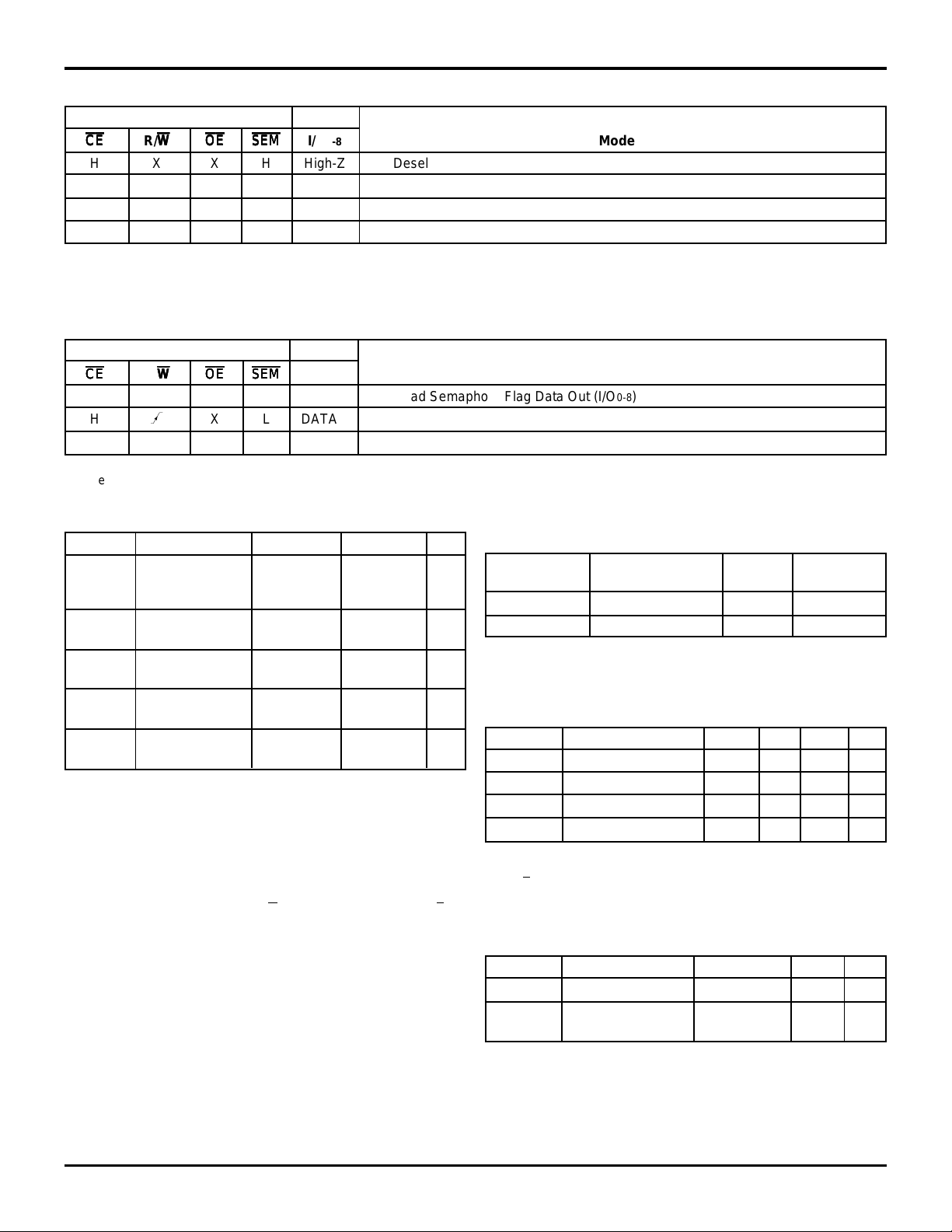

2954 drw 04

51 50 48 46 44 42 40 38 36

53

55

57

59

61

63

65

676866

13579

11 13 15

20

22

24

26

28

30

32

35

ABCDEFGH JK L

47 45 43 41 34

21

23

25

27

29

31

33

246810121416

18 19

17

56

58

60

62

64

11

10

09

08

07

06

05

04

03

02

01

525449 39 37

A

5L

INT

L

N/C

SEM

L

CE

L

V

CC

OE

L

R/

W

L

I/O

0L

I/O

8L

GND GND

I/O

0R

V

CC

I/O

8R

OE

R

R/

W

R

SEM

R

CE

R

GND

BUSY

R

BUSY

L

M/

S

INT

R

N/C

GND

A

1R

N/C

N/C

INDEX

A

4LA2LA0L

A

3R

A

2R

A

4R

A

5R

A

7R

A

6R

A

9R

A

8R

A

11R

A

10R

A

12R

A

0R

A

7L

A

6L

A

3LA1L

A

9L

A

8L

A

11L

A

10L

A

12L

V

CC

I/O2RI/O3RI/O

5R

I/O

6R

I/O

1R

I/O

4R

I/O

7R

I/O

1L

I/O

2L

I/O

4L

I/O

7L

I/O

3L

I/O

5L

I/O

6L

IDT7015

(8K x 9)

G68-1

68-PIN PGA

TOP VIEW

(3)

HIGH-SPEED 8K x 9 DUAL-PORT STATIC RAM MILITARY AND COMMERCIAL TEMPERATURE RANGES

PIN CONFIGURATIONS (CON'T.)

L

L

L

W

CE

SEM

R/

77

NC

75

76

74

CC

V

NC

NC

70

72

73

71

IDT7015

(8K X 9)

PN-80

TQFP

TOP VIEW

31

27

26

25

30

28

29

INDEX

NC

I/O

I/O

I/O

I/O

GND

I/O

I/O

CC

V

NC

GND

I/O

0R

I/O

1R

I/O

2R

V

CC

I/O

3R

I/O

4R

I/O

5R

I/O

6R

NC

L

8L

1L

0L

OE

I/O

I/O

I/O

78

79

80

1

2

2L

3

3L

4

4L

5

5L

6

7

6L

8

7L

9

10

11

12

13

14

15

16

17

18

19

20

22

21

23

24

(1,2)

12L

A

69

32

11L

10L

A

A

68

67

(3)

34

33

7L

9L

A

66

35

6L

8L

A

A

A

65

64

36

37

NC

NC

62

61

63

60

NC

59

5L

A

58

A

4L

57

A

3L

56

A

2L

55

A

1L

54

A

0L

53

INT

BUSY

GND

M/

S

BUSY

INT

A

0R

A

1R

A

2R

A

3R

A

4R

NC

NC

L

L

R

R

52

51

50

49

48

47

46

45

44

43

42

41

40

38

39

R

R

W

R/

R

NC

NC

CE

SEM

NC

GND

12R

A

11R

A

R

8R

7R

OE

I/O

I/O

NOTES:

1. All Vcc must be connected to power supply.

2. All GND must be connected to ground supply.

3. This text does not imply orientation of Part-Mark.

9R

8R

10R

A

A

A

7R

A

5R

6R

NC

A

A

2954 drw 03

NC

6.12 3

IDT7015S/L

HIGH-SPEED 8K x 9 DUAL-PORT STATIC RAM MILITARY AND COMMERCIAL TEMPERATURE RANGES

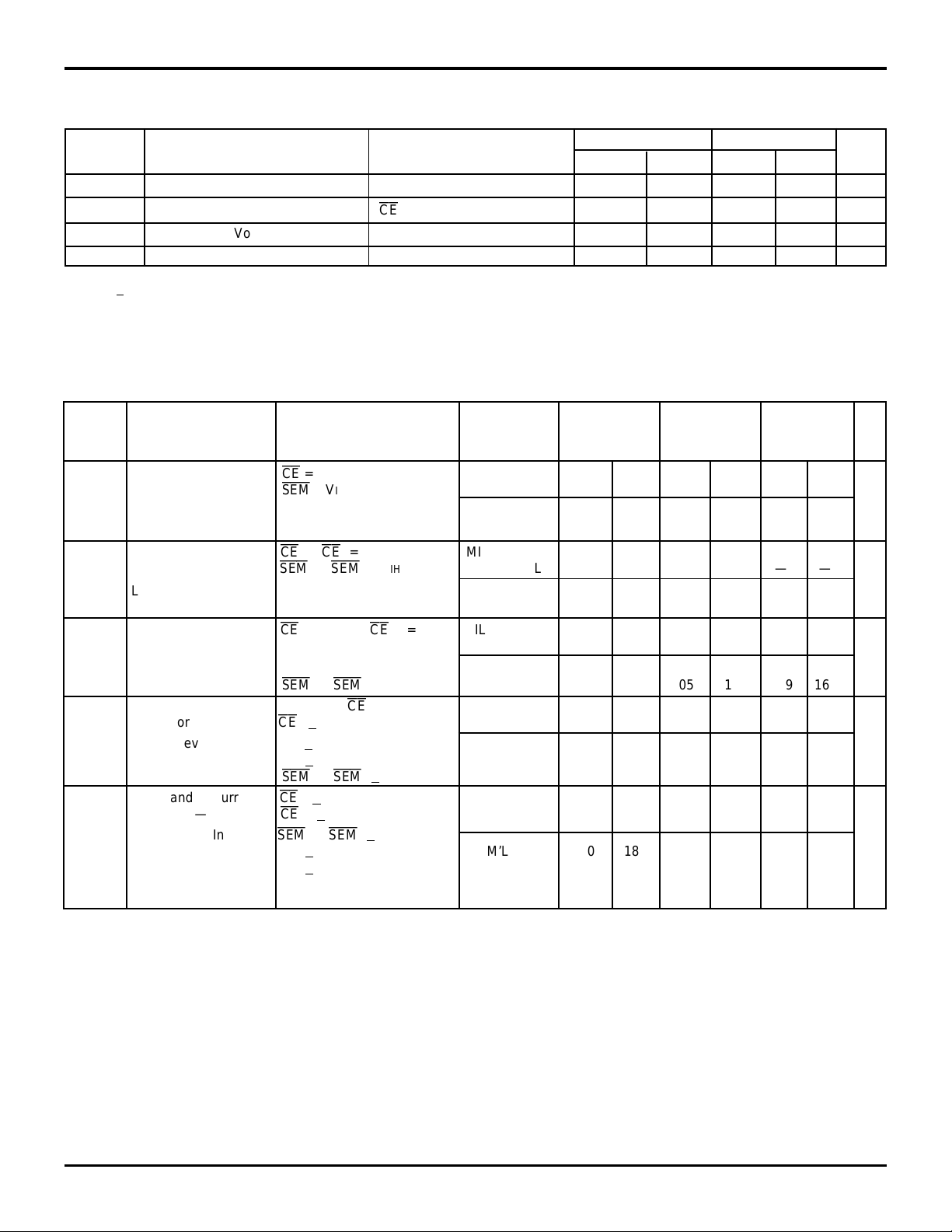

TRUTH TABLE: NON-CONTENTION READ/WRITE CONTROL

Inputs

CECE

CE

CECE

R/

WW

W

WW

H X X H High-Z Deselected: Power-Down

L L X H DATA

L H L H DATA

X X H X High-Z Outputs Disabled

NOTE: 2954 tbl 02

1. Condition: A0L — A12L is not equal to A0R — A12R.

(1)

OEOE

OE

OEOE

SEMSEM

SEM

SEMSEM

Outputs

0-8 Mode

I/O

IN Write to Memory

OUT Read Memory

TRUTH TABLE: SEMAPHORE READ/WRITE CONTROL

(1)

Inputs Outputs

CECE

CE

CECE

H H L L DATA

H

R/

WW

W

WW

u

OEOE

OE

OEOE

SEMSEM

SEM

SEMSEM

I/O

X L DATA

0-8 Mode

OUT Read Semaphore Flag Data Out (I/O0-8)

IN Write I/O0 into Semaphore Flag

L X X L — Not Allowed

NOTE: 2954 tbl 03

1. There are eight semaphore flags written to via I/O0 and read from I/O0-8 . These eight semaphores are addressed by A0 - A2.

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Rating Commercial Military Unit

(2)

V

TERM

Terminal Voltage –0.5 to +7.0 –0.5 to +7.0 V

with Respect

to GND

T

A Operating 0 to +70 –55 to +125 °C

Temperature

BIAS Temperature –55 to +125 –65 to +135 °C

T

RECOMMENDED OPERATING

TEMPERATURE AND SUPPLY VOLTAGE

Ambient

Grade Temperature GND V

Military –55°C to +125°C 0V 5.0V ± 10%

Commercial 0°C to +70°C 0V 5.0V ± 10%

CC

2954 tbl 05

Under Bias

T

STG Storage –55 to +125 –65 to +150 °C

Temperature

OUT DC Output 50 50 mA

I

Current

NOTES: 2954 tbl 04

1. Stresses greater than those listed under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

TERM must not exceed Vcc + 0.5V for more than 25% of the cycle time

2. V

or 10ns maximum, and is limited to

+ 0.5V.

< 20mA for the period of VTERM > Vcc

RECOMMENDED DC OPERATING

CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

CC Supply Voltage 4.5 5.0 5.5 V

V

GND Supply Voltage 0 0 0 V

IH Input High Voltage 2.2 — 6.0

V

V

IL Input Low Voltage –0.5

NOTES: 2954 tbl 06

1. VIL > -1.5V for pulse width less than 10ns.

2. V

TERM must not exceed Vcc + 0.5V.

CAPACITANCE

(1)

(1)

— 0.8 V

(2)

V

(TA = +25°C, f = 1.0MHz) TQFP ONLY

Symbol Parameter Conditions

IN Input Capacitance VIN = 3dV 9 pF

C

OUT Output VOUT = 3dV 10 pF

C

Capacitance

2954 tbl 07

NOTES:

1. This parameter is determined by device characteristics but is not

production tested.

2. 3dV references the interpolated capacitance when the input and

output signals switch from 0V to 3V or from 3V to 0V .

(2)

Max. Unit

6.12 4

IDT7015S/L

HIGH-SPEED 8K x 9 DUAL-PORT STATIC RAM MILITARY AND COMMERCIAL TEMPERATURE RANGES

DC ELECTRICAL CHARACTERISTICS OVER THE

OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE

Symbol Parameter Test Conditions Min. Max. Min. Max. Unit

|I

LI| Input Leakage Current

LO| Output Leakage Current

|I

OL Output Low Voltage IOL = 4mA — 0.4 — 0.4 V

V

OH Output High Voltage IOH = -4mA 2.4 — 2.4 — V

V

NOTE:

1. At Vcc < 2.0V, Input leakages are undefined.

(1)

VCC = 5.5V, VIN = 0V to VCC —10—5µA

CE

= VIH, VOUT = 0V to VCC —10—5µA

(VCC = 5.0V ± 10%)

7015S 7015L

2954 tbl 08

DC ELECTRICAL CHARACTERISTICS OVER THE

OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE

7015X12 7015X15 7015X17

Test Com'l. Only Com'l. Only Com'l. Only

Symbol Parameter Condition Version Typ.

CC Dynamic Operating

I

Current

(Both Ports Active) f = f

I

SB1 Standby Current CER = CEL = VIH MIL. S — — — — — — mA

(Both Ports — TTL

Level Inputs) f = f

SB2 Standby Current CE"A"=VIL and CE"B" = VIH

I

(One Port — TTL Active Port Outputs Open L — — — — — —

Level Inputs) f = f

I

SB3 Full Standby Current Both Ports CEL and MIL. S — — — — — — mA

(Both Ports — All

CMOS Level Inputs) V

I

SB4 Full Standby Current CE"A"< 0.2V and MIL. S — — — — — — mA

(One Port — All

CMOS Level Inputs)

NOTES: 2954 tbl 09

1. "X" in part numbers indicates power rating (S or L).

CC = 5V, TA = +25°C, and are not production tested. ICCDC = 120mA(typ.)

2. V

3. At f = f

4. f = 0 means no address or control lines change.

5. Port "A" may be either left or right port. Port "B" is the opposite of port "A".

MAX, address and I/O'S are cycling at the maximum frequency read cycle of 1/tRC, and using “AC Test Conditions” of input levels of GND to 3V.

CE

= VIL, Outputs Open MIL. S — — — — — — mA

SEM

= V

IH L— —— ———

(3)

MAX

COM’L. S 170 325 170 310 170 310

L 170 275 170 260 170 260

SEM

R =

SEM

L = VIH L— —— ———

(3)

MAX

COM’L. S 25 70 25 60 25 60

L256025 502550

(5)

MIL. S — — — — — — mA

(3)

MAX

SEM

R =

SEM

L = VIH L 105 170 105 160 109 160

CE

R > VCC - 0.2V L — — — — — —

IN > VCC - 0.2V or COM’L. S 1.0 15 1.0 15 1.0 15

V

IN < 0.2V, f = 0

SEM

R =

CE

"B" > VCC - 0.2V

R =

SEM

V

V

Active Port Outputs Open,

f = f

SEM

IN > VCC - 0.2V or COM’L. S 100 180 100 170 100 170 mA

IN < 0.2V L 100 150 100 140 100 140

(3)

MAX

(4)

SEM

L > VCC - 0.2V

L > VCC - 0.2V

(5)

COM’L. S 105 200 105 190 105 190

L 0.2 5 0.2 5 0.2 5

L— —— ———

(1)

(VCC = 5.0V ± 10%)

(2)

Max. Typ.

(2)

Max. Typ.

(2)

Max. Unit

6.12 5

IDT7015S/L

HIGH-SPEED 8K x 9 DUAL-PORT STATIC RAM MILITARY AND COMMERCIAL TEMPERATURE RANGES

DC ELECTRICAL CHARACTERISTICS OVER THE

OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE

Test

Symbol Parameter Condition Version Typ.

CC Dynamic Operating

I

Current

(Both Ports Active) f = f

SB1 Standby Current

I

(Both Ports — TTL

Level Inputs) f = f

I

SB2 Standby Current

(One Port — TTL Active Port Outputs Open L — — 90 180 85 160

Level Inputs) f = f

I

SB3 Full Standby Current Both Ports CEL and MIL. S — — 1.0 30 1.0 30 mA

(Both Ports — All

CMOS Level Inputs) V

I

SB4 Full Standby Current

(One Port — All

CMOS Level Inputs)

NOTES: 2954 tbl 10

1. "X" in part numbers indicates power rating (S or L).

CC = 5V, TA = +25°C, and are not production tested. ICCDC = 120mA(typ.)

2. V

3. At f = f

4. f = 0 means no address or control lines change.

5. Port "A" may be either left or right port. Port "B" is the opposite of port "A".

MAX, address and I/O'S are cycling at the maximum frequency read cycle of 1/ tRC, and using

“AC Test Conditions” of input levels of GND to 3V.

CE

= VIL, Outputs Open MIL. S — — 155 340 150 300 mA

SEM

= V

IH L — — 155 280 150 250

(3)

MAX

COM’L. S 160 290 155 265 150 250

L 160 240 155 220 150 210

CE

L = CER = VIH MIL. S — — 16 80 13 80 mA

SEM

R =

SEM

L = VIH L— — 16651365

(3)

MAX

COM’L. S 20 60 16 60 13 60

L2050 16501350

(5)

(5)

MIL. S — — 90 215 85 190 mA

COM’L. S 95 180 90 170 85 155

L 0.2 5 0.2 5 0.2 5

L — — 85 170 80 150

CE

"A"=VIL and CE"B"=VIH

(3)

MAX

SEM

R =

SEM

L = VIH L 95 150 90 140 85 130

CE

R > VCC - 0.2V L — — 0.2 10 0.2 10

IN > VCC - 0.2V or COM’L. S 1.0 15 1.0 15 1.0 15

V

IN < 0.2V, f = 0

SEM

R =

SEM

CE

"A"< 0.2V and MIL. S — — 85 200 80 175 mA

CE

"B" > VCC - 0.2V

R =

SEM

V

V

SEM

IN > VCC - 0.2V or COM’L. S 90 155 85 145 80 135

IN < 0.2V L 90 130 85 120 80 110

(4)

L > VCC - 0.2V

L > VCC - 0.2V

Active Port Outputs Open,

(3)

f = f

MAX

(1)

(Cont'd) (VCC = 5.0V ± 10%)

7015X20 7015X25 7015X35

(2)

Max. Typ.

(2)

Max. Typ.

(2)

Max. Unit

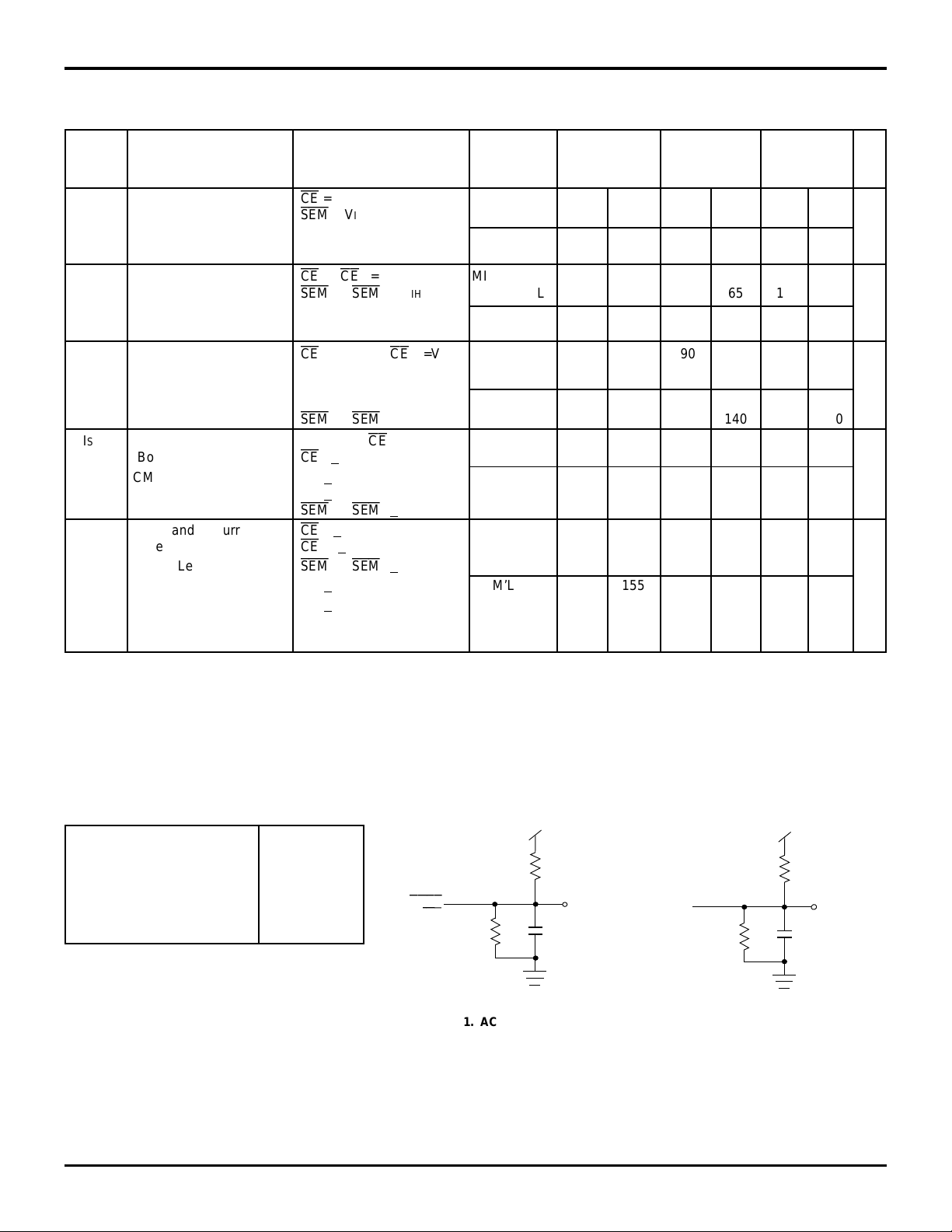

OUTPUT LOADS AND AC TEST

CONDITIONS

Input Pulse Levels GND to 3.0V

(1)

Input Rise/Fall Times

Input Timing Reference Levels 1.5V

Output Reference Levels 1.5V

Output Load Figure 1 and 2

NOTE:

1. 3ns Max. for t

AA=12ns

5ns Max.

5V

DATA

OUT

BUSY

INT

Figure 1. AC Output Test Load

6.12 6

893Ω

30pF347Ω

2954 drw 05

DATA

5V

893Ω

OUT

5pF347Ω

Figure 2. Output Test Load

LZ, tHZ, tWZ, tOW)

(For t

Including scope and jig.

*

2954 drw 06

Loading...

Loading...