ICT PA7540J-15, PA7540JI-15, PA7540JN-15, PA7540JNI-15, PA7540P-15 Datasheet

...

PA7540 PEEL Array™

Programmable Electrically Erasable Logic Array

Commercial/Industrial

Most Powerful 24-pin PLD Available

- 20 I/Os, 2 inputs/clocks, 40 registers/latches

- 40 logic cell output functions

- PLA structure with true product-ter m sharing

- Logic functions and registers can be I/O-buried

Ideal for Combinatorial, Synchronous and

Asynchronous Logic Applications

- Integration of multiple PLDs and random logic

- Buried counters, complex state-machines

- Comparators, decoder s, m ultiplexers and other wid egate functions

High-Speed Commercial and Industrial Versions

- As fast as 10ns/15ns (tpdi/tpdx), 71.4MHz (f

- Industrial grade available for 4.5 to 5.5V V

CC

MAX

and

)

-40 to +85 °C temperatures

General Description

The PA7540 is a m ember of the Pr ogramm able Electr icall y

Erasable Logic (PEEL™) Array family based on ICT’s

CMOS EEPROM technology. PEEL™ Arrays free

designers from the limitations of ordinary PLDs by

providing the arc hitectural flexibilit y and speed needed for

today’s programm able logic designs. T he PA7540 is by far

the most powerful 24-pin PLD available today with 20 I/O

pins, 2 input/global-clocks and 40 registers/latches (20

buried logic cells and 20 I/O registers/latches). Its logic

array implements 84 sum-of-products logic functions. The

PA7540’s logic and I/O cells (LCCs, IOCs) are extremely

flexible offering two out put functions per cell (a total of 40

for all 20 logic c ells). Logic cells ar e configurable as D, T,

and JK registers with independent or global clock s, resets,

CMOS Electrically Erasable Technology

- Reprogrammable in 24-pin DIP, SOIC and

28-pin PLCC packages

- Optional JN package for 22V10 power/ground

compatibility

Flexible Logic Cell

- 2 output functions per logic cell

- D,T and JK registers with special features

- Independent or global clocks, resets, presets,

clock polarity and output enables

- Sum-of-products logic for output enables

Development and Programmer Support

- ICT PLACE Development Software

- Fitters for ABEL, CUPL and other software

- Programming support by popular third-party

programmers

presets, clock polarity, and other features, making the

PA7540 suitable for a variety of combinatorial,

synchronous and asynch ronous logic applicat io ns. W ith pin

compatibility and super-set functionality to most 24-pin

PLDs, (22V10, EP610/630, GAL6002), the PA7540 can

implement designs that exceed the architectures of such

devices. The PA7540 supports speeds as fast as

10ns/15ns (tpdi/tpdx) and 71.46MHz (f

) at moderate

MAX

power consumption 80mA (55mA typical). Packaging

includes 24-pin DIP, SOIC and 28-pin PLCC (see Figure

1). ICT and popular third-party development tool

manufacturers provide development and programming

support for the PA7540.

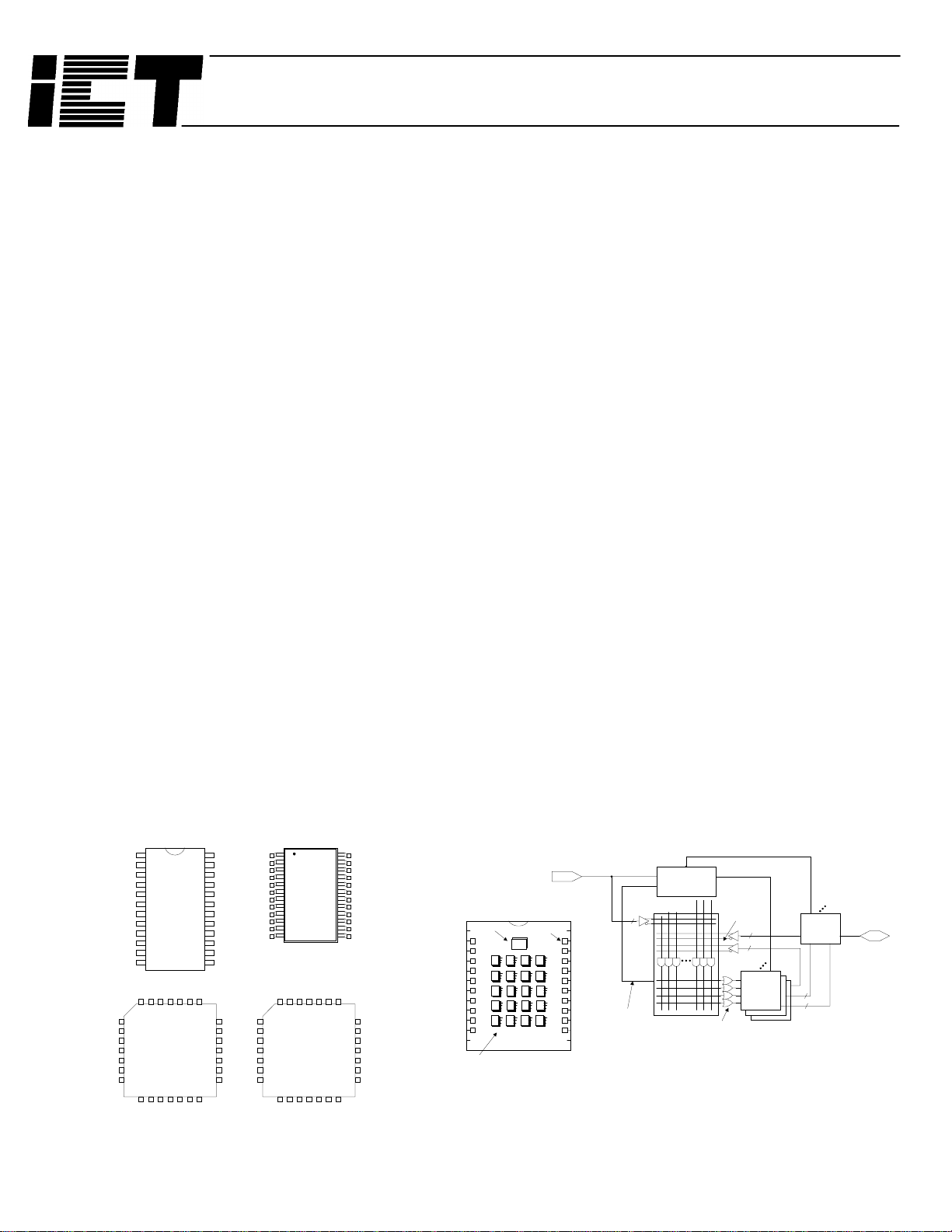

Figure 1. Pin Configuration

I/CLK1

1

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

I/O

8

I/O

9

I/O

10

I/O

11

GND

12

DIP

I/O3I/O

VCC28VCC27I/O26I/O

I/CLK1

4

2

I/O

I/O

I/O

NC

I/O

I/O

I/O

PLCC-J

1

5

6

7

8

9

10

11

12

14

I/O13I/O

GND15GND

VCC

24

I/O

23

I/O

22

I/O

21

I/O

20

I/O

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/CLK2

13

I/O

25

I/O

24

I/O

23

NC

22

I/O

21

I/O

20

I/O

19

16

17

I/O18I/O

I/CLK2

I/CLK1

I/O

I/O

I/O

NC

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

1

2

3

4

5

6

7

8

9

10

11

12

I/O3I/O2I/CLK11NC28VCC27I/O26I/O

4

5

6

7

8

9

10

11

12

I/O13I/O

Figure 2. Block Diagram

PA7540

2 Inp u t/

Global Clock Pins

I/O C e lls

VCC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/CLK 2GND

2

4 sum terms

4 product terms

for Globa l C ells

Global

Ce lls

Logic

Array

84 (42X2)

Arra y In p u ts

true a n d

complement

A

B

C

D

80 sum term s

(four per LCC)

I/O

20

20

Logic

Control

Ce lls

(LCC)

Ce lls

(IOC)

Buried

logic

20

20

20 Logic Control Cells

2 output functions per cell

(40 total output fu n ctions p o ss ible )

20 I/O Pins

Logic functions

to I/O c e lls

08-14-002A

24

VCC

23

I/O

22

I/O

21

I/O

20

I/O

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/O

13

I/CLK2

SOIC

I/O

25

I/O

24

I/O

23

NC

22

I/O

21

I/O

20

I/O

GND

15NC16

19

17

PLCC-JN

I/O18I/O

08-14-001B

I/CLK2

14

I/CLK 1

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Logic Control Cells

Global Cells

1 04-02-051B

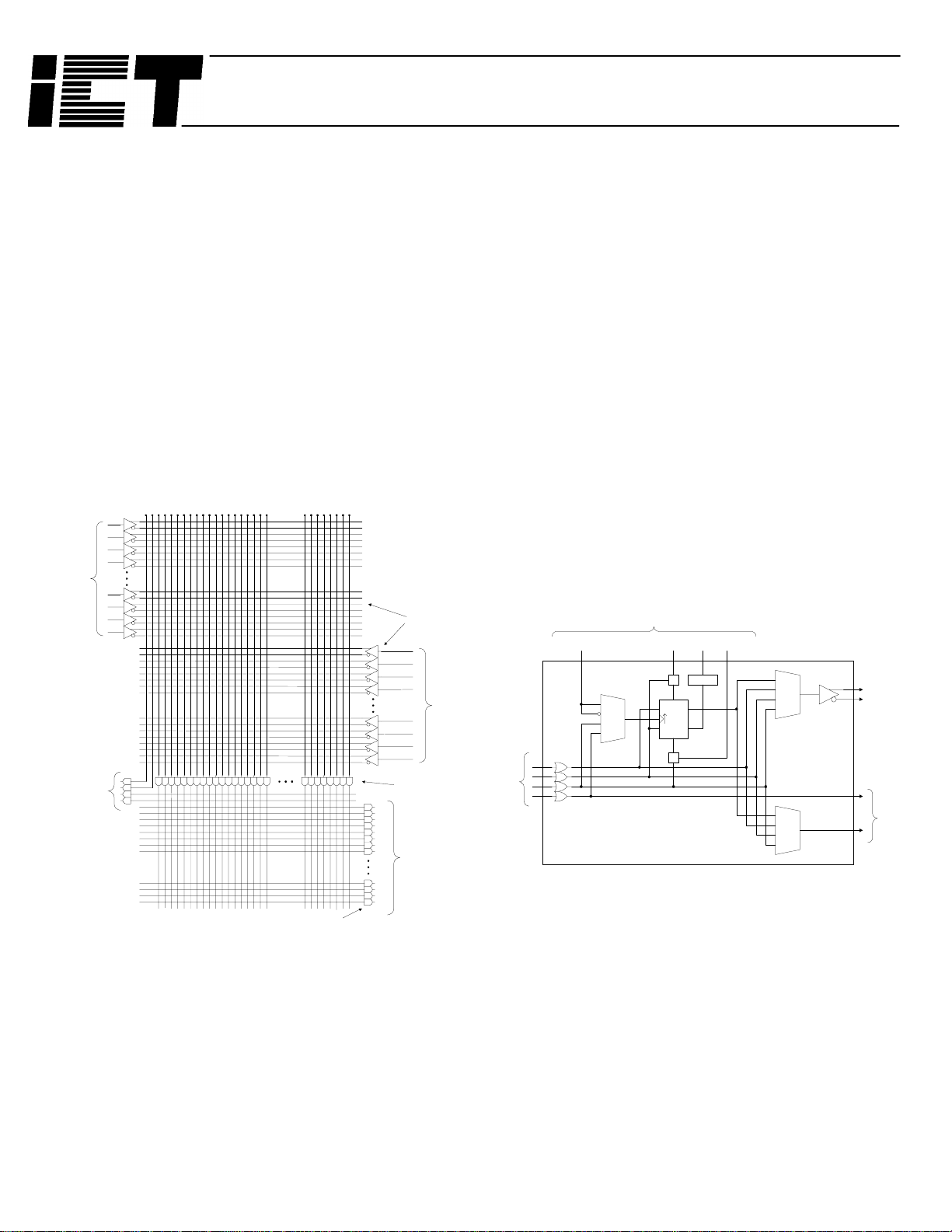

Inside the Logic Array

Commercial/Industrial

The heart of the P EEL™ Array architecture is based on a

logic array structur e s imilar to that of a PLA (programmable

AND, programmable OR). The logic array implements all

logic functions and provi des interconnection and contr ol of

the cells. In the PA7540 PEEL™ Array, 42 inputs are

available into the arra y from the I/O cells and input/gl obalclock pins.

All inputs provide b oth true and c omplem ent signa ls, which

can be programm ed to any product term in the array. T he

PA7540 PEEL™ Arrays contains 84 product terms. All

product terms ( with the ex ception of c ertain ones f ed t o the

global cells) can be progr ammabl y connected to any of the

sum-terms of the logic control cells (four sum-terms per

logic control cell). Product-terms and sum-term s are also

routed to the global cells for control purposes. Figure 3

shows a detailed view of the logic array structure.

From

IO C ells

(IOC) and

I/CLK s

42 Array Inputs

needed and not left unutilized or duplicated. Secondly, the

sum-of-products f unctions provided to the logic cells can be

used for clocks, res ets, presets and output e nables i nstead of

just simple product-term control.

The PEEL™ logic array can also implement logic functions

with many product terms within a single-level delay. For

example a 16-bit c omparator ne eds 32 shared product term s

to implement 16 exclusive-OR functions. The PEEL™ logic

array easily handles this in a single level delay. Other

PLDs/CPLDs either run out of product-terms or require

expanders or additional logic levels that often slow

performance and skew timing.

Logic Control Cell (LCC)

Logic Control Cells (LCC) a re us ed t o a ll oc ate and c on trol th e

logic functions created in the logic array. Each L CC has four

primary inputs and thre e outputs . T he inputs t o each LCC are

complete sum-of - produc t logic f unc tions f rom the array, which

can be used to implem ent combinatoria l and sequential l ogic

functions, and to control LCC registers and I/O cell output

enables.

From G loba l Cell

Preset Reset

System Clock

RegType

From

Logic

Control

Cells

(LCC)

To

Global

Cells

PA7540 Logic Array

84 Sum Terms

84 Product Terms

To

Logic Control

Cells

(LCC)

08-14-003A

Figure 3 PA7540 Logic Array

True Product-Term Sharing

The PEEL™ logic arra y provides several advantages over

common PLD logic arra ys. First, it allows for true pro ductterm sharing, not simply product-term steering, as

commonly found in other CPLDs. Product term sharing

ensures that product-terms are used where they are

On/Off

P

D,T,J

Q

K

REG

R

From

Array

MUX

A

B

C

D

Figure 4. Logic Control Cell Block Diagram

MUX

MUX

To

Array

To

I/O

Cell

08-14-004A

As shown in Figure 4, the LCC is made up of three signal

routing multiplexer s and a versatile reg ister with s ynchronous

or asynchronous D, T , or JK registers (c locked-SR registers,

which are a subset of JK, are also possible). See Figure 5.

EEPROM memory cells are used for programming the

desired configuration. Four sum-of-product logic functions

(SUM terms A, B, C and D) are f ed into each LCC from the

logic array. Each SUM term can be selectively used for

multiple functions as listed below.

2 04-02-051B

Commercial/Industrial

Sum-A = D, T, J or Sum-A

Sum-B = Preset, K or Sum-B

Sum-C = Reset, Clock, Sum-C

Sum-D = Clock, Output Enable

D Register

Q = D after clocked

P

Q

D

T

J

K

Best for storage, simple counters,

shifters and state machines with

R

few hold (loop) conditions.

T Register

Q toggles when T = 1

P

Q

Q holds when T = 0

Best for wide binary counters (saves

R

product terms) and state machines

with many hold (loop) conditions.

JK Register

Q toggles when J/K = 1/1

P

Q

Q holds when J/K = 0/0

Q = 1 when J/K = 1/0

Q = 0 when J/K = 0/1

R

Combines features of both D and T

registers.

08-14-005A

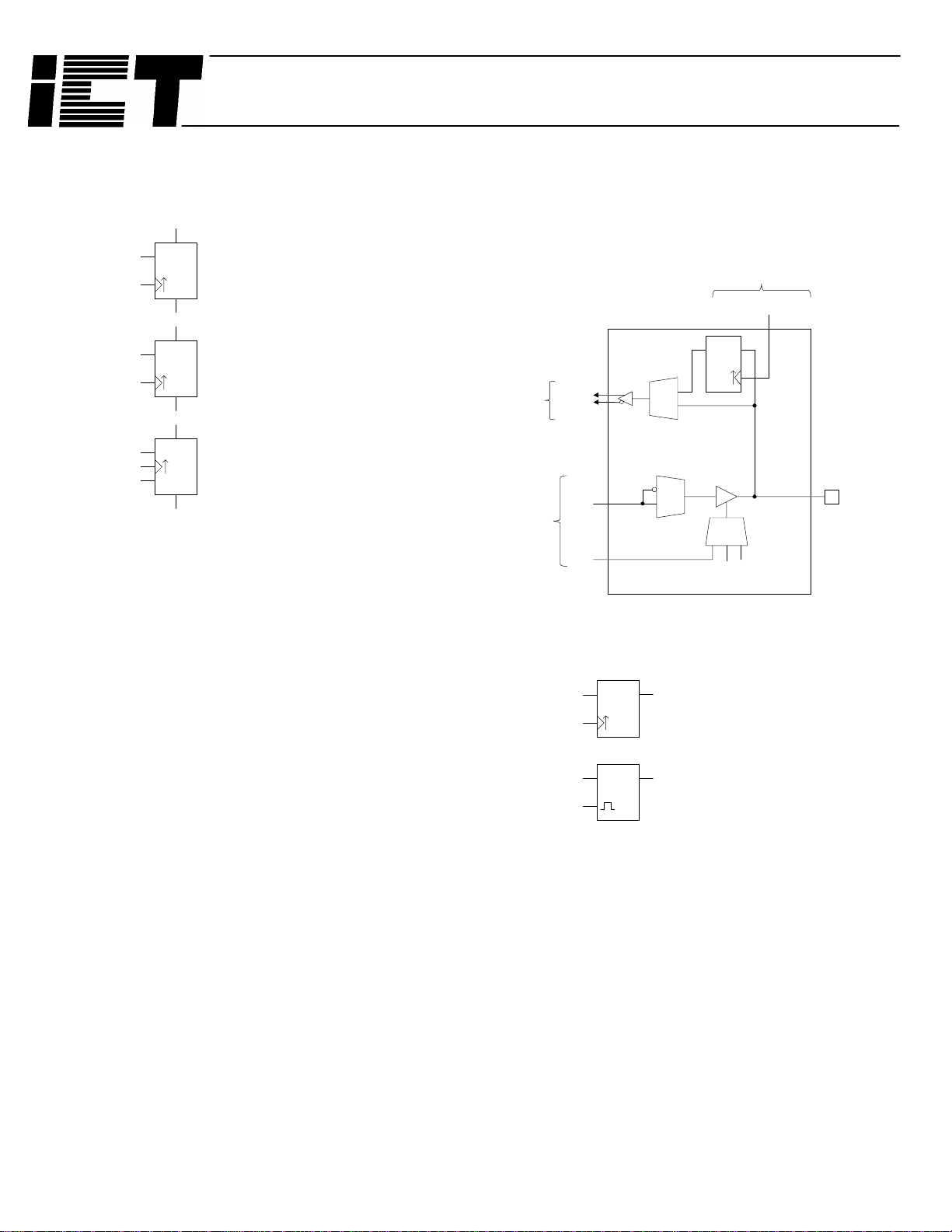

Figure 5. LCC Register Types

SUM-A can serve as the D, T, or J input of the reg is ter or a

combinatorial pat h. SUM-B can s erve as th e K inp ut, or the

preset to the register , or a combinator ial path. SUM-C can

be the clock, the reset to the register, or a combinatorial

path. SUM-D can be the clock to the regis ter or the output

enable for the connected I/O cell. Note that the sums

controlling clocks, resets, presets and output enables are

complete sum-of-pr oduct functions, not just product terms

as with most other PLDs. This also means tha t a ny input or

I/O pin can be used as a clock or other control function.

Several signals f rom the global cell are provided pr imarily

for synchronous (global) register control. The global cell

signals are routed to all LCCs. These signals include a

high-speed clock of positive or negative polarity, global

preset and reset, and a special register-type control that

selectively allo ws dynam ic switching of register type. This

last feature is especially useful for saving product terms

when implementing loa dable counters and state m achines

by dynamicall y switching from D-type register s to load and

T-type registers to count (see Figure 10).

Multiple Outputs Per Logic Cell

An important feature of the logic c ontrol cell is its c apabilit y

to have multiple output functions per cell, each operating

independently. As shown in Figure 4, two of the three

outputs can select the Q output from the register or the

Sum A, B or C com binatorial paths. T hus, one LCC output

can be registered, one output can be combinatorial and the

third, an output enable. The multi-function P EEL ™ Array logic

cells are equivalent to t wo or three macr ocells of other PLDs,

which have only one output per c ell. T hey also all ow re gisters

to be truly buried f rom I/O pins with out limiting t hem to inputonly (see Figure 8 ).

From Global Cell

I/O C e ll Clo ck

REG/

Latch

Q

To

Arra y

From

Logic

Control

Cell

Input

A,B,C

or

Q

D

MUX

MUX

MUX

0

7540 /O Cell (IOC )

1

I/O P in

08-14-006A

Figure 6. I/O Cell Block Diagram

D Q

LQ

IOC Register

Q = D after rising edge of clock

holds until next rising edge

IOC L atc h

Q = L when clock is high

holds value when clock is low

08-14-007A

Figure 7. IOC Register Configurations

I/O Cell (IOC)

All PEEL™ Arrays have I/O cells (IOC) as shown above in

Figure 6. Inputs to the IOCs c an be fed from any of the LCCs

in the array. Each IOC consists of routing and control

multiplexers, an input r egister/transparent l atch, a three-state

buffer and an output p olarity control. The register/ latc h can

be clocked from a var i ety of sources determ ined b y th e global

cell. It can also be b ypassed for a non-registered i nput. The

combination of LCC and IOC allows for multiple buried

registers and logic paths. (See Figure 8).

3 04-02-051B

Loading...

Loading...