ICST MK1412STR, MK1412A, MK1412ATR, MK1412S Datasheet

MK1412

MPEG Audio Clock Synthesizer

Description

The MK1412 is the ideal way to generate clocks

for MPEG audio devices in computers. The device

uses ICS/MicroClock’s proprietary mixture of

analog and digital Phase-Locked Loop (PLL)

technology to synthesize one of eight frequencies

(four on each output) from the 14.31818 MHz

reference. In an 8 pin SOIC, the MK1412 can save

component count, board space, and cost over

crystals and oscillators, and increase reliability by

eliminating three expensive mechanical devices

from the board.

We offer many other clocks for computers and

computer peripherals. Consult us when you need

to remove crystals and oscillators from your board.

Due to a long lead time in the original wafer fab

that makes the MK1412S, we have retooled the

die and now call the part the MK1412A. All

functional parameters are the same as or better

than the original part.

Features

• Packaged in 8 pin SOIC

• Input crystal or clock frequency of 14.31818 MHz

• Provides master MPEG clocks for 32 kHz,

44.1 kHz, 48 kHz and 96 kHz sampling rates

• Output clock frequencies of 256x and 512x of the

audio sampling rates compatible with most DACs

• Low jitter

• Full CMOS output swing with 25mA drive

capability at TTL levels

• 3.3V or 5V±10% supply voltage

• Advanced, low power CMOS process

• The A version is the newest version in a more

advanced manufacturing process

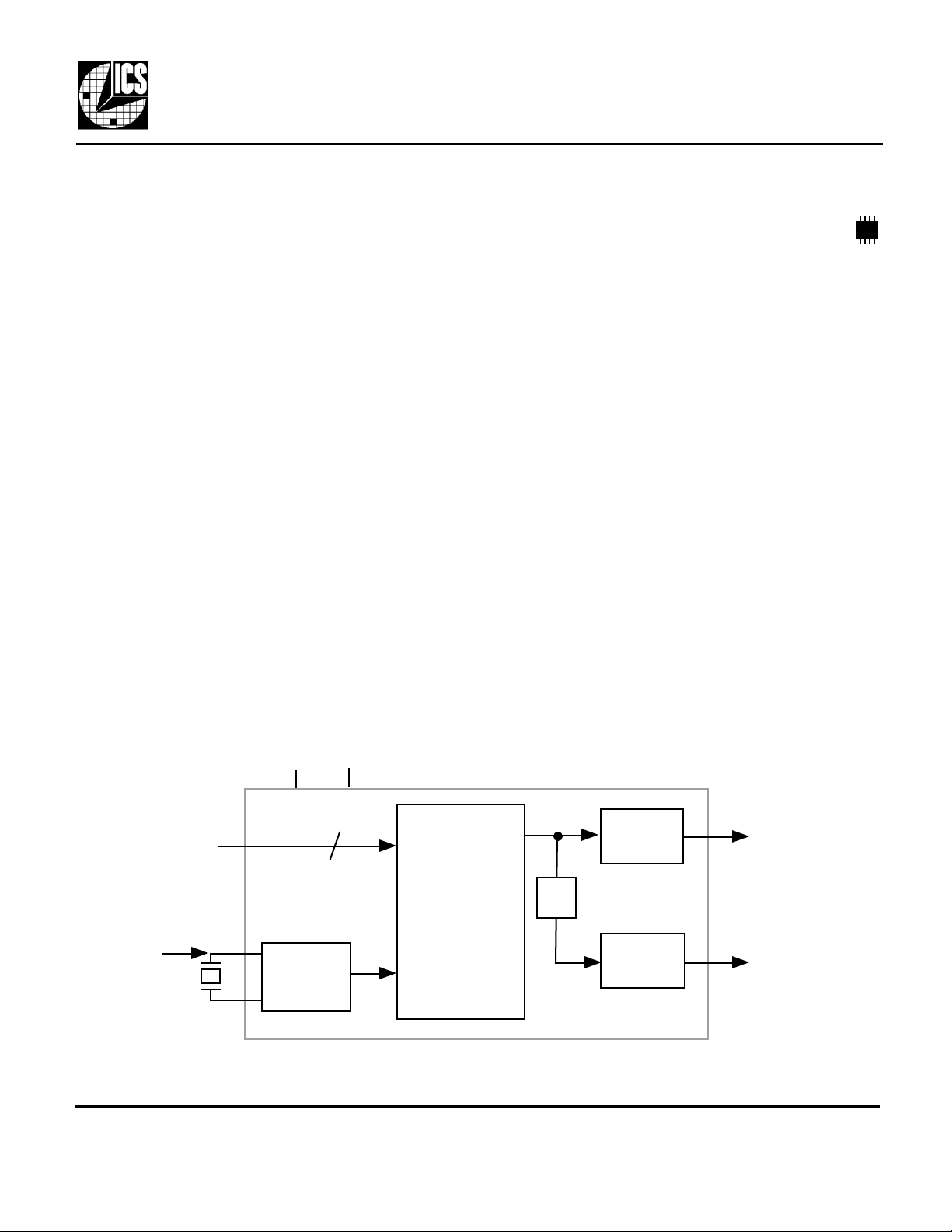

Block Diagram

VDD GND

2

S1, S0

PLL

14.31818 MHz

crystal or clock

X1

Crystal

Oscillator

X2

MDS 1412 B 1 Revision 060200 Printed 11/15/00

Integrated Circuit Systems, Inc.• 525 Race Street• San Jose • CA • 95126• (408)295-9800tel •www.icst.com

Clock Synthesis

and Control

Circuitry

÷ 2

Output

Buffer

Output

Buffer

CLK

CLK/2

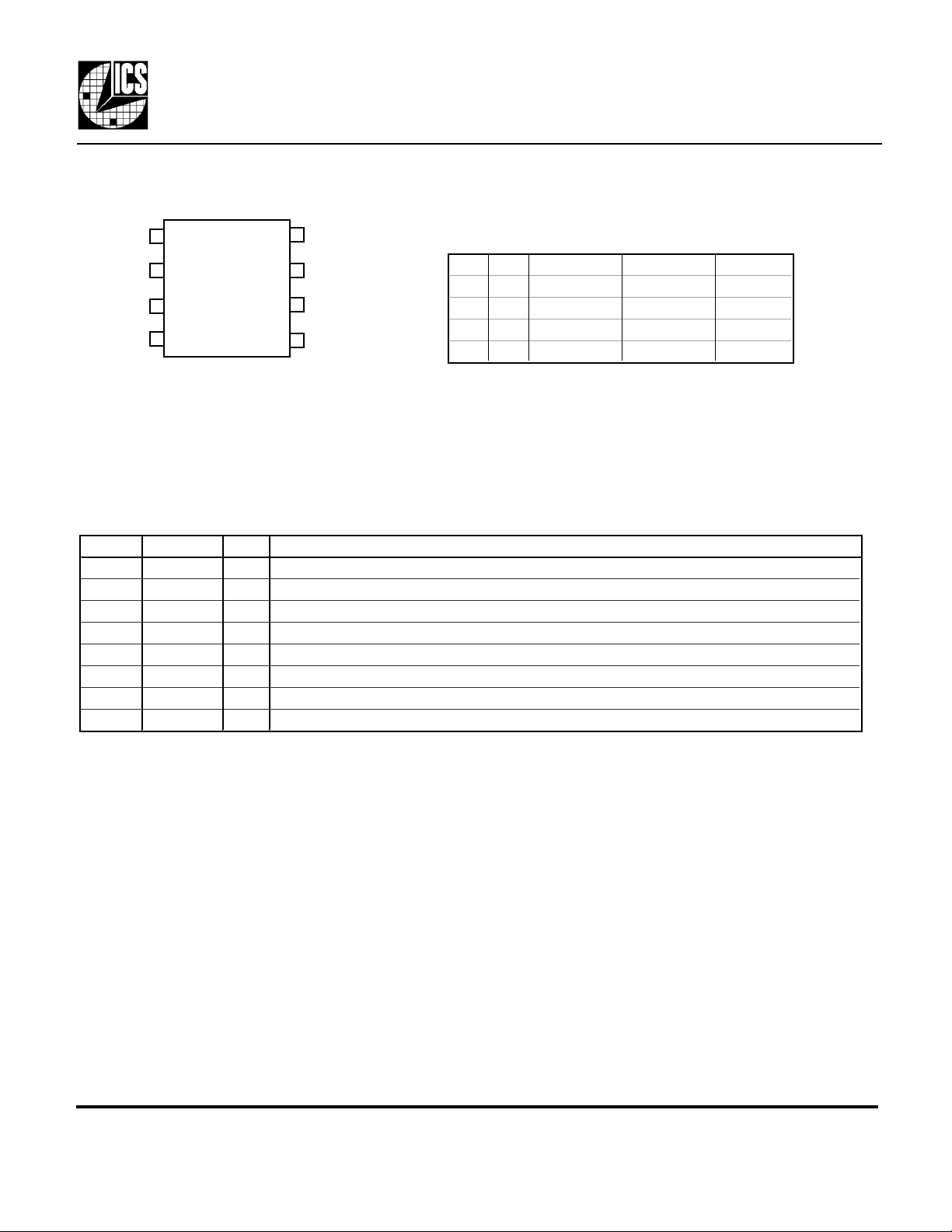

Pin Assignment

MK1412

MPEG Audio Clock Synthesizer

X1

VDD CLK

GND

CLK/2

1 8

2

3

4

7

6

5

X2

S1

S0

Audio Clock Outputs Select Table (MHz)

S1 S0 CLK CLK/2 Accuracy

0 0 16.384 8.192 1 ppm

0 1 22.5792 11.2896 25 ppm

1 0 24.576 12.288 1 ppm

1 1 49.152 24.576 1 ppm

8 pin SOIC

Pin Descriptions

Number Name Type Description

1 X1 I Crystal Connection. Connect to a 14.31818 MHz crystal or clock.

2 VDD P Connect to +3.3V or +5V.

3 GND P Connect to ground.

4 CLK/2 O Audio Clock divide by 2 output as per table above.

5 S0 I Frequency Select 0 Input. Determines CLK and CLK/2 outputs as per table above.

6 S1 I Frequency Select 0 Input. Determines CLK and CLK/2 outputs as per table above.

7 CLK O Audio Clock output as per table above.

8 X2 O Crystal Connection to a 14.31818 MHz crystal, or leave unconnected for clock input.

Key: I = Input, O = output, P = power supply connection

External Components/Crystal Selection

A minimum number of external components are required for proper oscillation. For a crystal input, one

load capacitor can be connected to each of the X1 and X2 pins and ground, and a parallel resonant

14.31818 MHz crystal is recommended. The value (in pF) of each crystal load capacitor should equal

(CL-18)*2, where CL is the crystal’s load (correlation) capacitance in pF. So for crystals with 18 pF load

capacitance (or less), no extra capacitors are needed. The frequency tolerance of the crystal should be

50ppm or better. For a clock input, connect to X1 and leave X2 unconnected. A decoupling capacitor of

0.1µF should be connected between VDD and GND on pins 2 and 3, and 33Ω terminating resistor may

be used on the clock outputs if the trace is longer than 1 inch.

MDS 1412 B 2 Revision 060200 Printed 11/15/00

Integrated Circuit Systems, Inc.• 525 Race Street• San Jose • CA • 95126• (408)295-9800tel •www.icst.com

Loading...

Loading...