Integrated

Circuit

Systems, Inc.

ICS94211

94211 Rev A 03/28/01

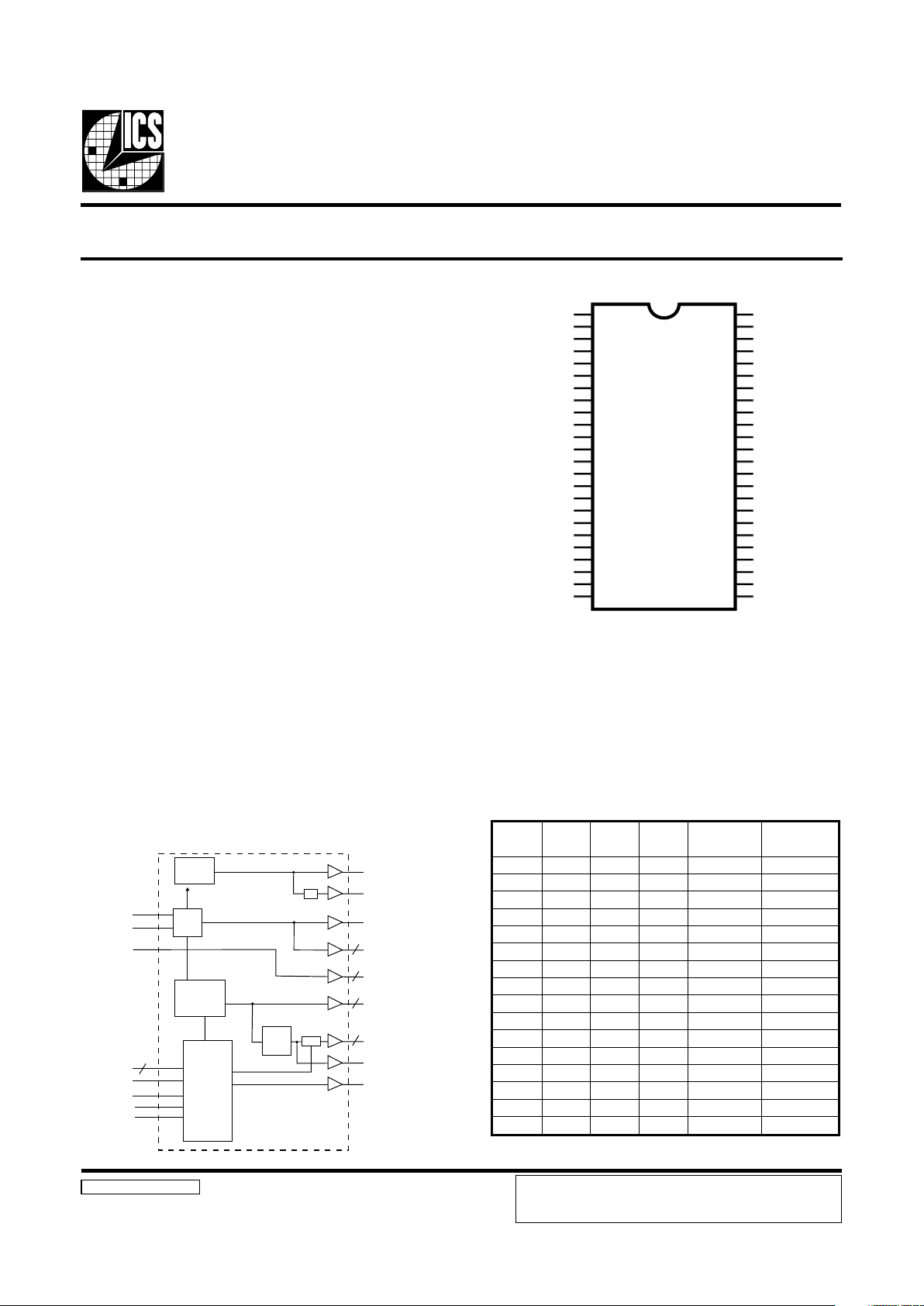

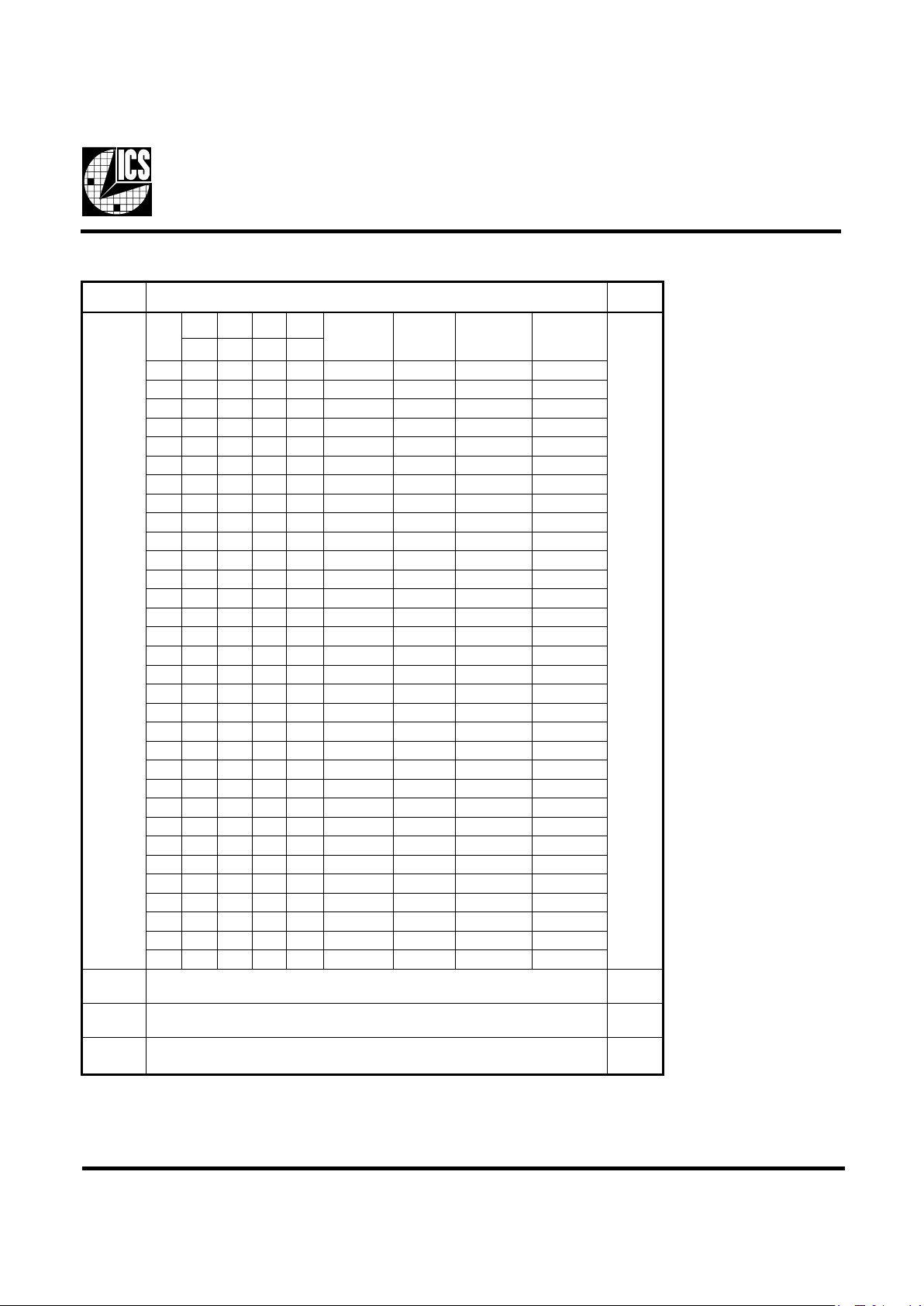

Pin Configuration

Recommended Application:

440BX/VIA Apollo Pro133/ ALI 1631 style chipset.

Output Features:

• 2 - CPUs @2.5V

• 1 - IOAPIC @ 2.5V

• 13 - SDRAM @ 3.3V

• 6 - PCI @3.3V,

• 1 - 48MHz, @3.3V

• 1 - 24MHz @ 3.3V

• 2 - REF @3.3V, 14.318MHz.

Features:

• Programmable ouput frequency.

• Programmable ouput rise/fall time.

• Programmable PCICLK, PCICLK_F,

SDRAM skew.

• Real time system reset output

• Spread spectrum for EMI control typically by 7dB to 8dB,

with programmable spread percentage.

• Watchdog timer technology to reset system

if over-clocking causes malfunction.

• Uses external 14.318MHz crystal.

• FS pins for frequency select

Key Specifications:

• CPU – CPU: <175ps

• SDRAM - SDRAM: <500ps

• PCI – PCI: <500ps

• CPU(early)-PCI: Min=1.0ns, Typ=2.0ns, Max=4.0ns

Programmable System Frequency Generator for PII/III™

Block Diagram

48-Pin 300mil SSOP

VDDREF

*PCI_STOP/REF0

GND

X1

X2

VDDPCI

*MODE/PCICLK_F

**FS3/PCICLK0

GND

PCICLK1

PCICLK2

PCICLK3

PCICLK4

VDDPCI

BUFFER_IN

GND

SDRAM12

SDRAM11

VDDSDR

SDRAM10

SDRAM9

GND

S DATA

SCLK

VDDL

IOAPIC

REF1/FS2*

GND

CPUCLK0

CPUCLK1

VDDLCPU

RESET#

SDRAM0

GND

SDRAM1

SDRAM2

VDDSDR

SDRAM3

SDRAM4

GND

SDRAM5

SDRAM6

VDDSDR

SDRAM7

SDRAM8

VDD48

48MHz/FS0*

24MHz/FS1*

ICS94211

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

* Internal Pull-up Resistor of 120K to VDD

** Internal Pull-down resistor of 120K to GND

Functionality

3SF2SF1SF0SF

UPC

)zHM(

KLCICP

)zHM(

0000 00.0800.04

0001 00.5705.73

0010 13.3856.14

0011 28.6614.33

0100 00.30133.43

0101 10.21143.73

0110 10.8610.43

0111 32.00114.33

1000 00.02100.04

100 1 99.41133.83

10 10 99.90166.63

10 11 00.50100.53

1100 00.04100.53

1101 00.05105.73

1110 00.42100.13

1111 99.23152.33

PCI_STOP#

PLL2

PLL1

Spread

Spectrum

48MHz

24MHz

IOAPIC

CPUCLK (1:0)

RESET#

SDRAM (12:0)

PCICLK (4:0)

PCICLK_F

X1

X2

BUFFER IN

XTAL

OSC

PCI

CLOCK

DIVDER

STOP

S DATA

SCLK

FS(3:0)

MODE

Control

Logic

Config.

Reg.

/2

REF(1:0)

2

2

13

5

4

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS94211

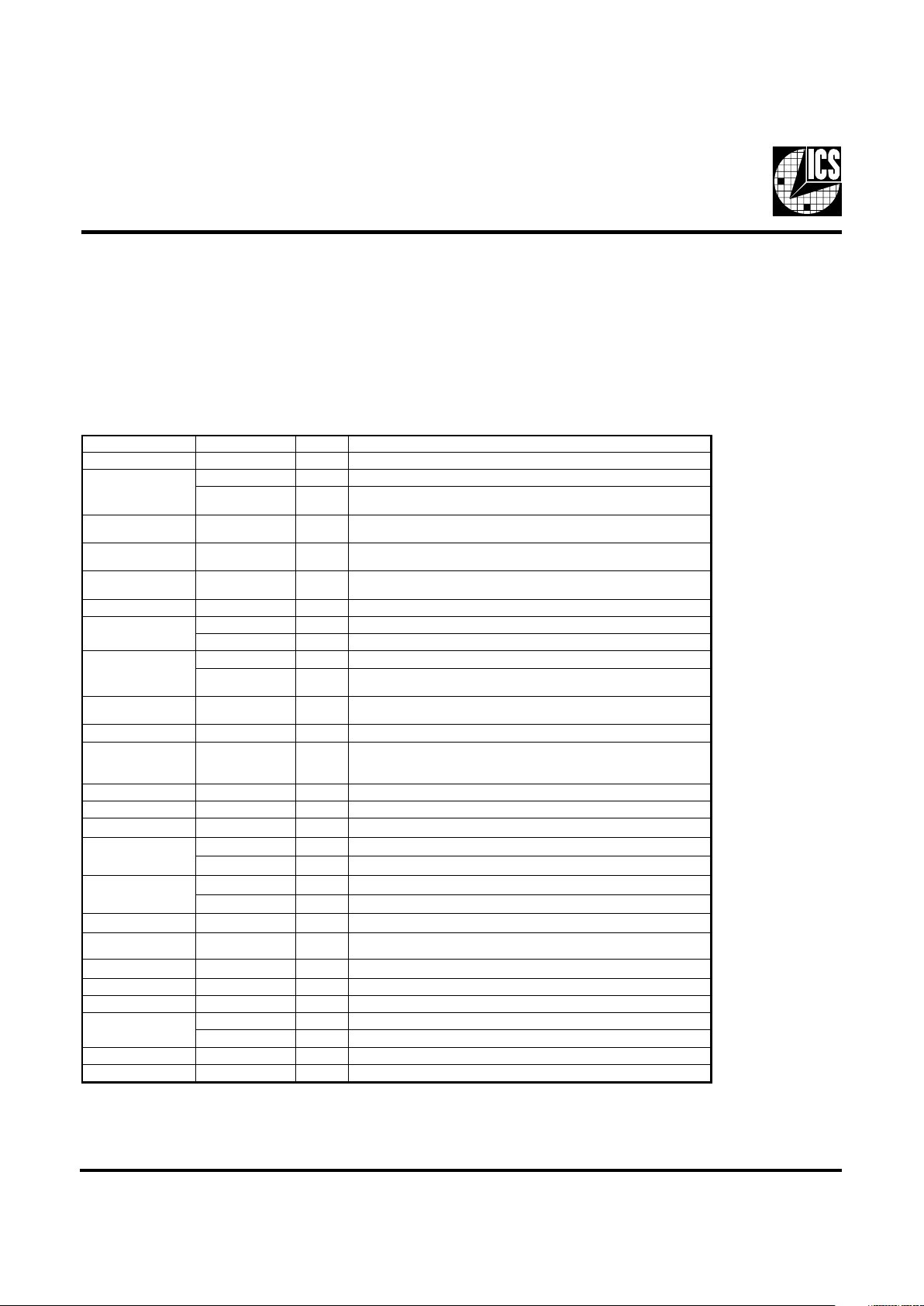

General Description

Pin Configuration

The ICS94211 is a single chip clock solution for desktop designs using the BX/Apollo Pro133/ALI 1631 style chipset. It provides all

necessary clock signals for such a system.

The ICS94211 belongs to ICS new generation of programmable system clock generators. It employs serial programming I

2

C interface

as a vehicle for changing output functions, changing output frequency, configuring output strength, configuring output to output skew,

changing spread spectrum amount, changing group divider ratio and dis/enabling individual clocks. This device also has ICS

propriety 'Watchdog Timer' technology which will reset the frequency to a safe setting if the system become unstable from over

clocking.

Notes:

1: Internal Pull-up Resistor of 120K to 3.3V on indicated inputs

2: Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor

to program logic Hi to VDD or GND for logic low.

REBMUNNIPEMANNIPEPYTNOITPIRCSED

1FERDDVRWPV3.3lanimon,ylppusrewopLATX,feR

2

0FERTUO.kcolcecnereferzhM813.41

#POTS_ICP

1

NI

elibomnI(woltupninehw,level0cigoltaskcolc)4:0(KLCICPstlaH

)0=EDOM,edom

,22,61,9,3

54,93,33

DNGRWPdnuorG

41XNI

kcabdeefdna)Fp63(pacdaollanretnisah,tupnilatsyrC

2Xmorfrotsiser

52XTUO

daollanretnisaH.zHM813.41yllanimon,tuptuolatsyrC

)Fp63(pac

41,6ICPDDVRWPV3.3lanimon,)4:0(KLCICPdnaF_KLCICProfylppuS

7

F_KLCICPTUO .tnemeganamrewoprof#POTS_ICPybdetceffatonkcolcICPgninnureerF

EDOM

2,1

NI .tupnIdehctaL.edoMeliboM=0,edoMpotkseD=1,niptcelesnoitcnuf7niP

8

3SFNIDNGotnwod-lluPlanretnI.tupnIdehctaL.niptcelesycneuqerF

0KLCICPTUO

wekssn84-1htiwskcolcUPCotsuonorehcnyS.stuptuokcolcICP

)ylraeUPC(

01,11,21,31)1:4(KLCICPTUO

wekssn84-1htiwskcolcUPCotsuonorehcnyS.stuptuokcolcICP

)ylraeUPC(

51NIREFFUBNI.stuptuoMARDSrofsreffuBtuonaFottupnI

,92,82,12,02,81,71

,83,73,53,43,23,13

04

)0:21(MARDSTUO

nipNIREFFUBmorfstuptuoreffuBtuonaF,stuptuokcolcMARDS

)tespihcybdellortnoc(

63,03,91RDSDDVRWP.V3.3lanimon,eroCLLPUPCdna)21:0(MARDSrofylppuS

32ATADSO/IIroftupniataD

2

tupnitnarelotV5,tupnilairesC

42KLCSNIIfotupnikcolC

2

tupnitnarelotV5,tupniC

52

zHM42TUOkcolctuptuozHM42

1SF

2,1

NI.tupnIdehctaL.niptcelesycneuqerF

62

zHM84TUOkcolctuptuozHM84

0SF

2,1

NItupnIdehctaL.niptcelesycneuqerF

7284DDVRWP.erocLLPdexifdnasreffubtuptuozHM84&42rofrewoP

14TESERTUO

godhctawroegnahcoitarycneuqerfroflangistesermetsysemitlaeR

.wolevitcasilangissihT.tuoemitremmit

24UPCLDDVRWPlanimonV3.3roV5.2rehtie,skcolcUPCrofylppuS

341KLCUPCTUOwoL=#POTS_UPCfiwoL.2LDDVybderewop,stuptuokcolcUPC

440KLCUPCTUO#POTS_UPCehtybdetceffatoN.kcolcUPCgninnureerF

64

1FERTUO.kcolcecnereferzHM813.41

2SF

2,1

NItupnIdehctaL.niptcelesycneuqerF

74CIPAOITUOCIPAOI.LDDVybderewoPzHM813.41.tuptuokcolc

84LDDVRWPlanimonV3.3ro5.2rehtie,CIPAOIrofylppuS

3

ICS94211

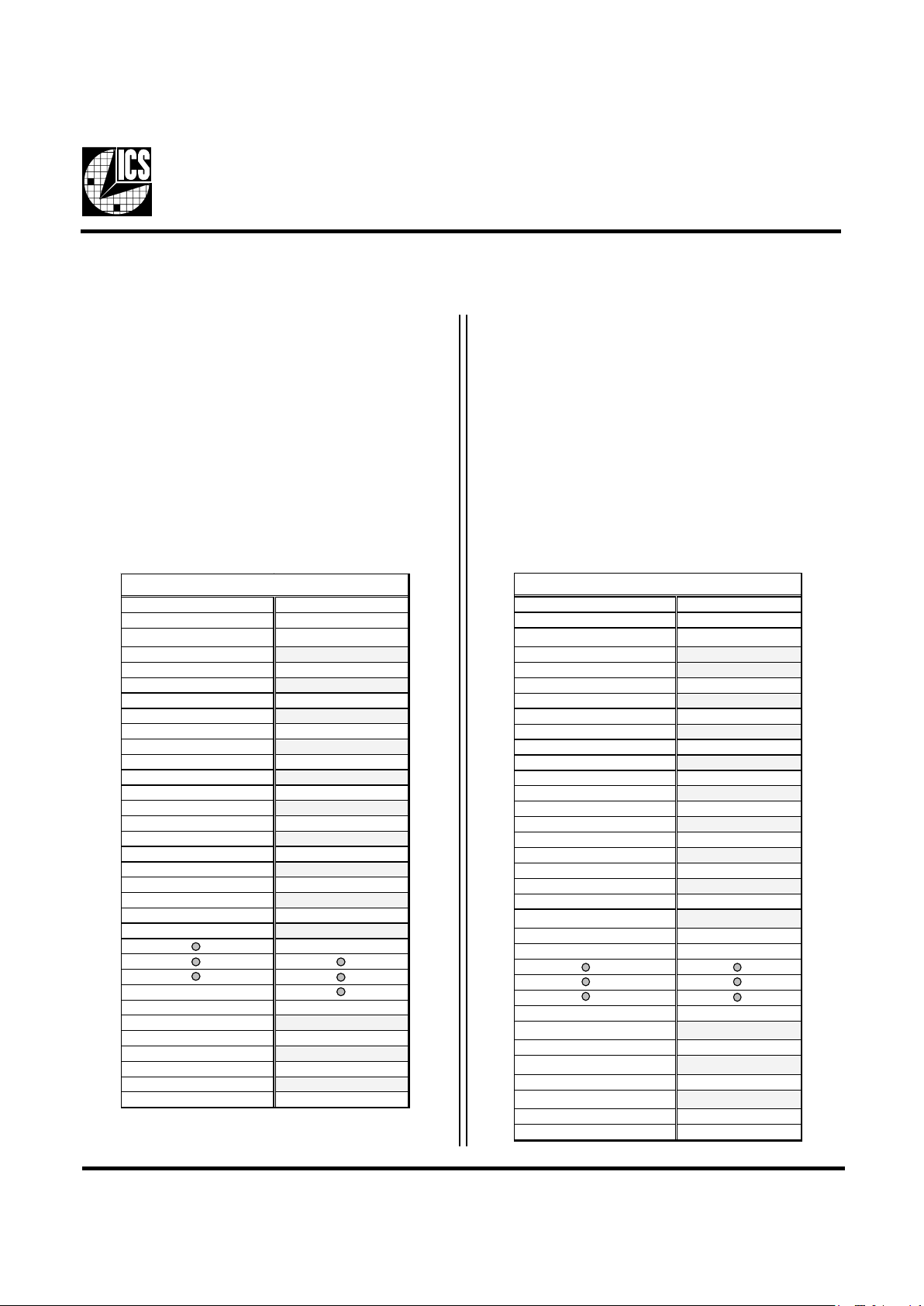

General I2C serial interface information for the ICS94211

How to Write:

• Controller (host) sends a start bit.

• Controller (host) sends the write address D2

(H)

• ICS clock will acknowledge

• Controller (host) sends a dummy command code

• ICS clock will acknowledge

• Controller (host) sends a dummy byte count

• ICS clock will acknowledge

• Controller (host) starts sending Byte 0 through Byte 20

(see Note)

• ICS clock will acknowledge each byte one at a time

• Controller (host) sends a Stop bit

How to Read:

• Controller (host) will send start bit.

• Controller (host) sends the read address D3

(H)

• ICS clock will acknowledge

• ICS clock will send the byte count

• Controller (host) acknowledges

• ICS clock sends Byte 0 through byte 8 (default)

• ICS clock sends Byte 0 through byte X (if X

(H)

was

written to byte 8).

• Controller (host) will need to acknowledge each byte

• Controller (host) will send a stop bit

Controller (Host)

ICS (Slave/Receiver)

Start Bit

Address D2

(H)

ACK

Dummy Com mand Code

ACK

Dummy B yt e Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Byte 6

ACK

Byte 18

ACK

Byte 19

ACK

Byte 20

ACK

Stop Bit

How to Write:

*See notes on the following page.

Controller (Host)

ICS (Slave/Receiver)

Start Bit

Addres s D3

(H)

ACK

Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Byte 6

ACK

If 7

H

has been wri tten t o B6

Byte 7

ACK

If 12

H

has been wri tten t o B6

Byte18

ACK

If 13

H

has been wri tten t o B6

Byte 19

ACK

If 14

H

has been wri tten t o B6

Byte 20

ACK

Stop Bit

How to Read:

4

ICS94211

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for verification.

Readback will support standard SMBUS controller protocol. The number of bytes to readback is defined by writing to

byte 8.

2. When writing to byte 11 - 12, and byte 13 - 14, they must be written as a set. If for example, only byte 14 is written

but not 15, neither byte 14 or 15 will load into the receiver.

3. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

4. The input is operating at 3.3V logic levels.

5. The data byte format is 8 bit bytes.

6. To simplify the clock generator I

2

C interface, the protocol is set to use only Block-Writes from the controller. The bytes

must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte has been

transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those two bytes.

The data is loaded until a Stop sequence is issued.

7. At power-on, all registers are set to a default condition, as shown.

Notes:

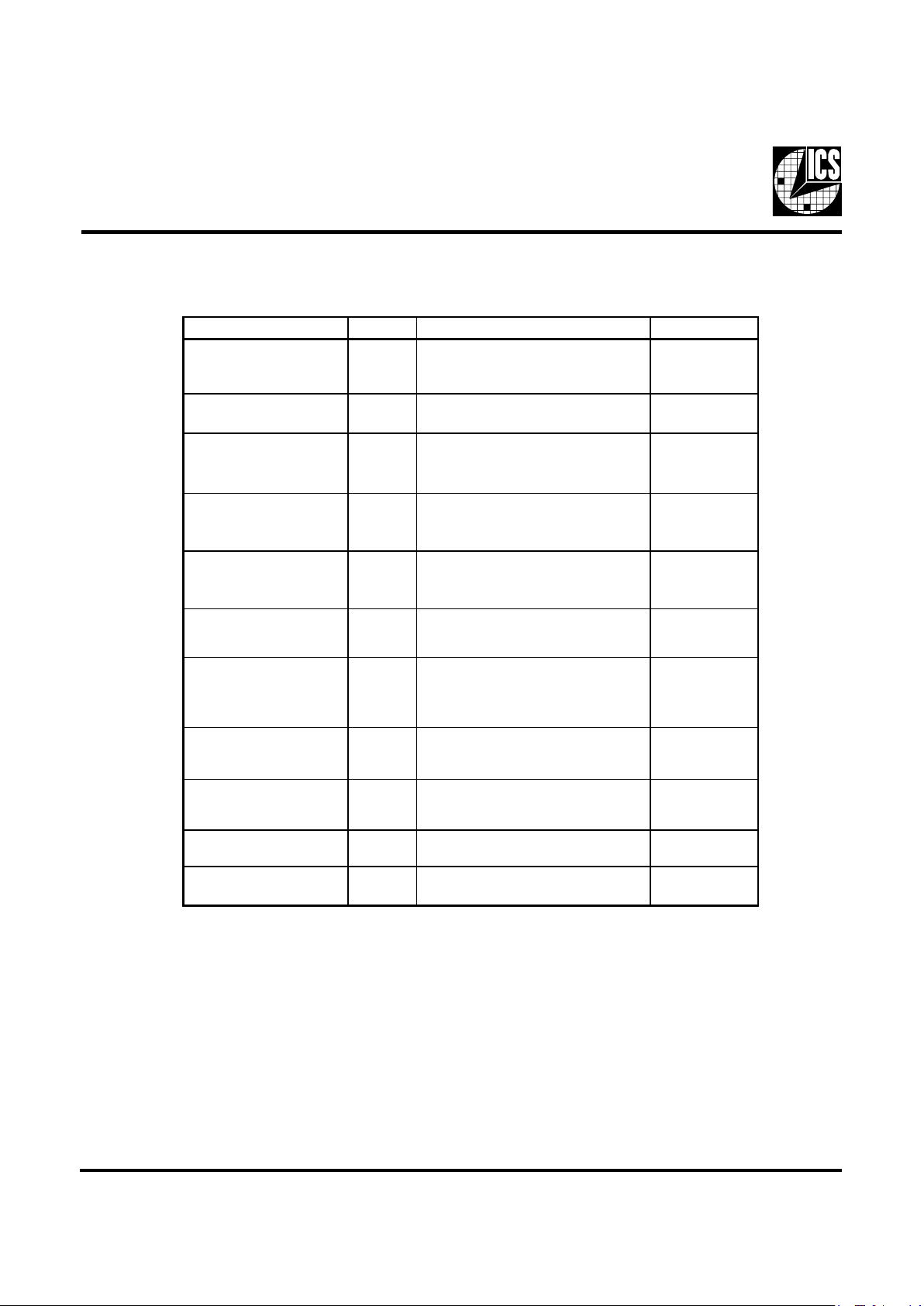

Brief I2C registers description for ICS94211

Programmable System Frequency Generator

Register Name Byte Description PWD Default

Functionality & Frequency

Select Register

0

Output frequency, hardware / I

2

C

frequency select, spread spectrum &

output enable control register.

See individual

byte description

Output Control Registers 1-6

Active / inactive output control

registers/latch inputs read back.

See individual

byte description

Vendor ID & Revision ID

Registers

7

Byte 11 bit[7:4] is ICS vendor id - 1001.

Other bits in this register designate device

revision ID of this part.

See individual

byte description

Byte Count

Read Back Register

8

Writing to this register will configure

byte count and how many byte will be

read back. D o not w rite 00

H

to this byte.

08

H

Watchdog Timer

Count Register

9

Writing to this register will configure the

number of seconds for the watchdog

timer to reset.

10

H

Watchdog Control Registers 10 Bit [6:0]

Watchdog enable, watchdog status and

programmable 'safe' frequency' can be

configured in this register.

000,0000

VCO Control Selection Bit 10 Bit [7]

This bit select whether the output

frequency is control by hardware/byte 0

configurations or byte 11&12

programming.

0

VCO Frequency Control

Registers

11-12

These registers control the dividers ratio

into the phase detector and thus control

the VCO output frequency.

Depended on

hardware/byte 0

configuration

Spread Spectrum Control

Registers

13-14

These registers control the spread

percentage amount.

Depended on

hardware/byte 0

configuration

Group Skews Control

Registers

15-16

Increment or decrement the group skew

amount as compared to the initial skew.

See individual

byte description

Output Rise/Fall Time

Select Registers

17-20

These registers will control the output

rise and fall time.

See individual

byte description

5

ICS94211

Byte 0: Functionality and frequency select register (Default=0)

Notes:

1.

Default at power-up will be for latched logic inputs to define frequency, as displayed by Bit 3.

tiB

noitpircseD

DWP

tiB

)4:7,2(

2tiB

7tiB6tiB5tiB4tiB

FER/OCV

rediviD

OCV

zHM

KLCUPC

zHM

KLCICP

zHM

1etoN

3SF2SF1SF0SF

00000 04/74410.06100.0800.04

00001 24/04400.05100.5705.73

00010 44/21516.66113.3856.14

00011 24/29346.33128.6614.33

00100 13/64400.60200.30133.43

00101 13/58410.42210.21143.73

00110 45/31520.63110.8610.43

00111 73/81554.00232.00114.33

01000 12/25300.04200.02100.04

01001 23/41599.92299.41133.83

01010 33/70589.91299.90166.63

01011 33/48400.01200.50100.53

01100 81/25300.08200.04100.53

01101 12/04400.00300.05105.73

01110 52/33499.74200.42100.13

01111 62/38499.56299.23152.33

10000 12/69300.07200.53157.33

1000 1 91/54399.95299.92105.23

10010 52/04400.25200.62105.13

10011 92/87400.63200.81133.93

10 100 03/68459.13289.51166.83

10 101 73/19410.09100.5976.13

10 110 53/04400.08100.0900.03

10 111 93/36489.96110.5843.82

11000 61/17300.23300.66105.14

11001 02/74410.02310.06100.04

11010 02/33499.90399.45157.83

11011 51/01319.59259.74199.63

11100 32/96479.19289.54105.63

1110 1 81/26359.78289.34199.53

11110 42/67489.38299.14105.53

11111 81/74320.67210.83105.43

3tiB

stupnidehctal,tceleserawdrahybdetcelessiycneuqerF-0

4:7,2tiBybdetcelessiycneuqerF-1

0

1tiB

lamroN-0

daerpSretneC%53.0±elbanemurtcepsdaerpS-1

1

0tiB

gninnuR-0

stuptuollaetatsirT-1

0

Loading...

Loading...