Integrated

Circuit

Systems, Inc.

ICS9248-99

Third party brands and names are the property of their respective owners.

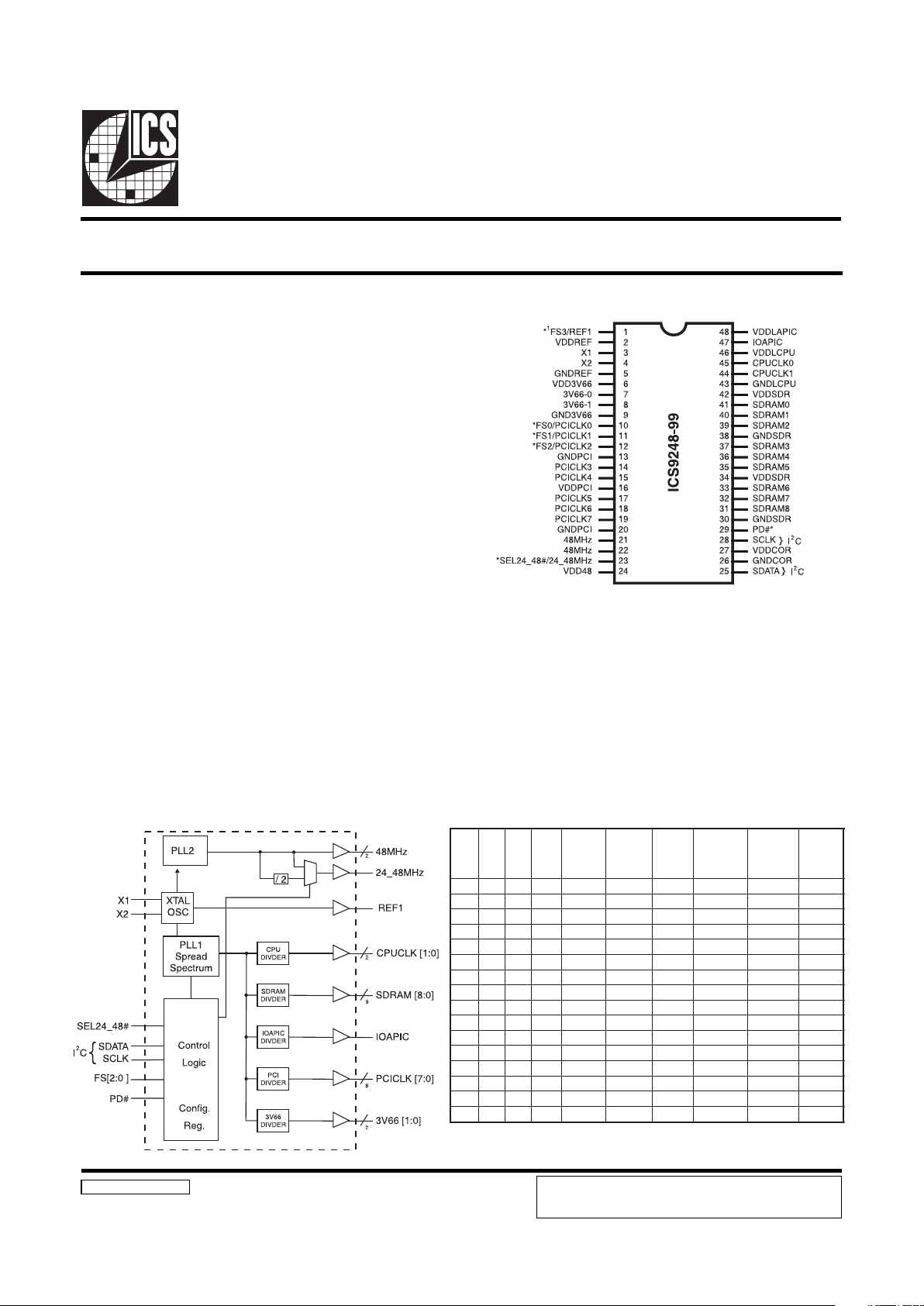

Block Diagram

9248- 99 Rev A 8/27/99

Recommended Application:

810/810E style chipset

Output Features:

• 2- CPUs @2.5V @ 150MHz (up to 200MHz. achievable

through I

2

C)

• 9 - SDRAM @ 3.3V @ 150MHz (up to 200MHz.

achievable through I

2

C)

• 8 - PCICLK @ 3.3V

• 1 - IOAPIC @ 2.5V,

• 2 - 3V66MHz @ 3.3V

• 2- 48MHz, @ 3.3V fixed.

• 1- 24/48MHz, @ 3.3V

• 1- REF @3.3V, 14.318MHz.

Features:

• Up to 200.4MHz frequency support

• Support FS0-FS3 trapping status bit for I

2

C read back.

• Support power management: Power down Mode form I

2

C

programming.

• Spread spectrum for EMI control ( ± 0.25% center).

• FS0, FS1, FS2, FS3 must have a internal 120K pull-Down

to GND.

• Uses external 14.318MHz crystal

Skew Specifications:

• CPU – CPU: <175ps

• SDRAM - SDRAM: < 250ps

• 3V66 – 3V66: <175ps

• PCI – PCI: <500ps

• For group skew specifications, please refer to group

timing relationship table.

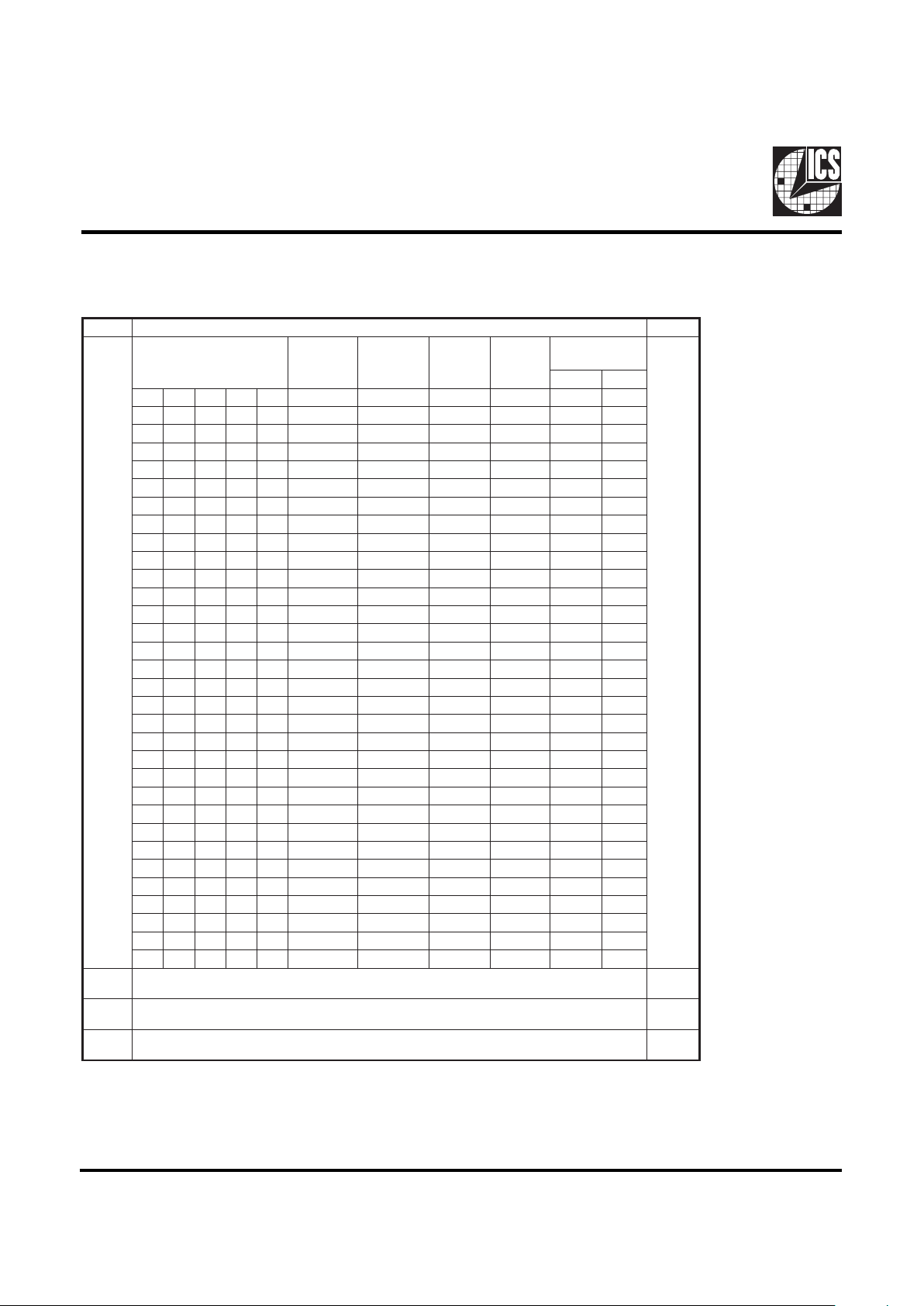

Functionality

3SF2SF1SF0SF

UPC

)zHM(

MARDS

)zHM(

66V3

)zHM(

KLCICP

*66V3(

)2/1

)zHM(

CIPAOI

*ICP(

)2/1

)zHM(

CIPAOI

)ICP(

)zHM(

0000

33.5700.31133.5776.7338.8176.73

0001

00.52100.52133.3876.1438.0276.14

0010

00.92100.92100.6800.3405.1200.34

0011

92.05100.31133.5776.7338.8176.73

0100

00.05100.05100.00100.0500.5200.05

0101

00.21100.21176.4733.7376.8133.73

0110

00.54100.54176.6933.8471.4233.84

0111

46.34100.80100.2700.6300.8100.63

100 0

03.8605.20133.8671.4380.7171.43

100 1

00.50100.50100.0700.5305.7100.53

1010

00.83100.83100.2900.6400.3200.64

1011

00.04100.50100.0700.5305.7100.53

1100

76.6600.00176.6633.3376.6133.33

110 1

00.00100.00176.6633.3376.6133.33

1110

06.33106.33170.9835.4472.2235.44

1111

33.33100.00176.6633.3376.6133.33

Pin Configuration

48-Pin 300mil SSOP

* These inputs have a 120K pull down to GND.

1 These are double strength.

Frequency Generator & Integrated Buffers for Celeron & PII/III™

Preliminary Product Preview

PRODUCT PREVIEW documents contain information on new

products in the sampling or preproduction phase of development.

Characteristic data and other specifications are subject to change

without notice.

2

ICS9248-99

Preliminary Product Preview

Third party brands and names are the property of their respective owners.

General Description

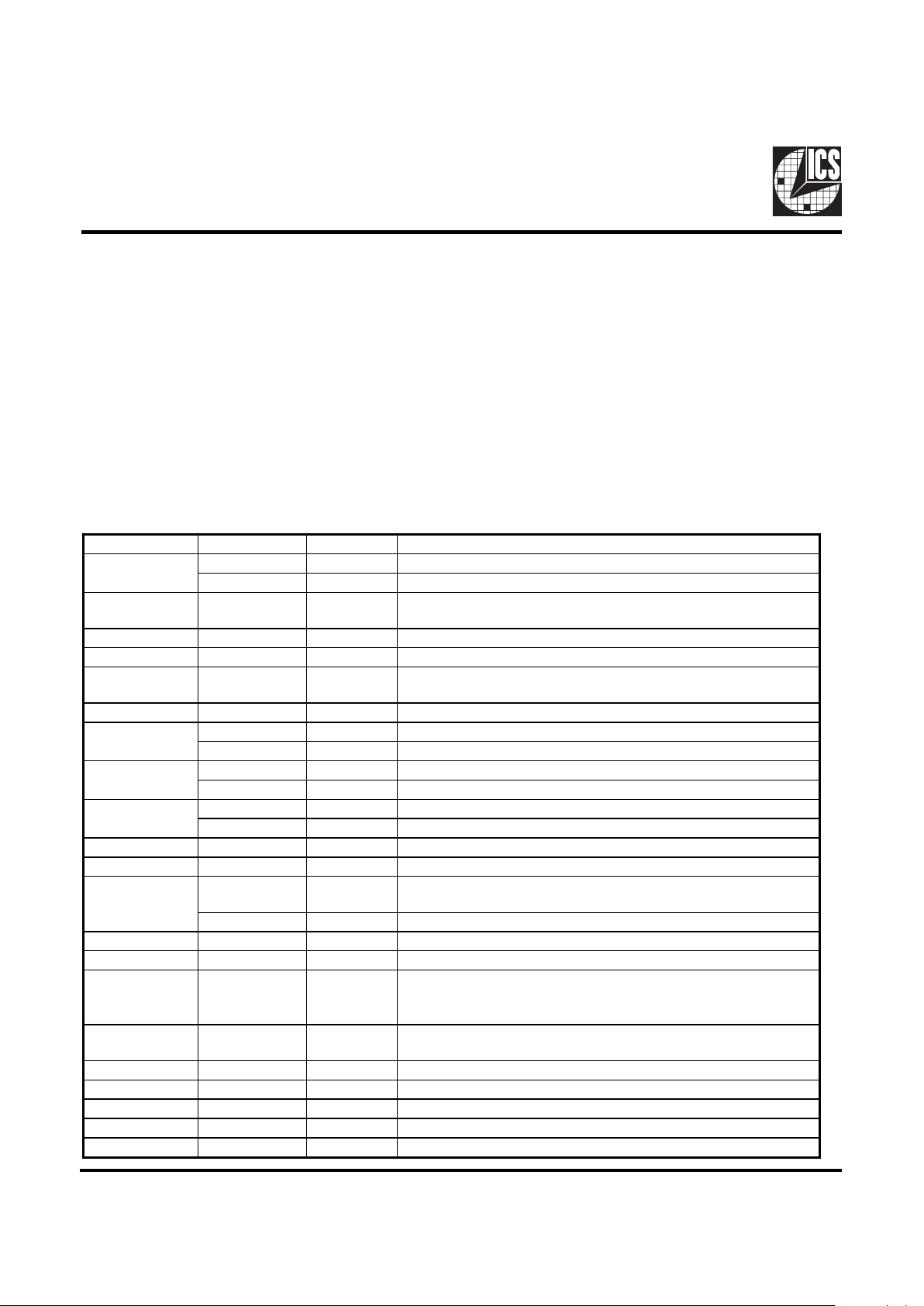

Pin Configuration

The ICS9248-99 is the single chip clock solution for Desktop

designs using 810/810/E style chipset. It provides all necessary

clock signals for such a system.

Spread spectrum may be enabled through I

2

C programming.

Spread spectrum typically reduces system EMI by 8dB to

10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9248-99

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

Serial programming I

2

C interface allows changing functions,

stop clock programming and frequency selection.

Power Groups

GNDREF, VDDREF = REF1, X1, X2

GNDPCI , VDDPCI = PCICLK [7:0]

GNDSDR, VDDSDR = SDRAM [8:0]

GNDCOR, VDDCOR = supply for PLL core

GND3V66 , VDD3V66 = 3V66

VDD48 = 48MHz, 24_48MHz,

VDDLAPIC = IOAPIC

GNDLCPU , VDDLCPU = CPUCLK [1:0]

PIN NUMBER PIN NAME TYPE DESCRIPTION

REF1 OU T 14.31 8 MHz reference clock.

FS3 IN Frequency select pin .

2, 6, 16, 24, 27 , 34,

42

VDD PWR

3.3V Power s upply for SD RAM output b uffers, PCI output buffers,

reference out

p

ut buffers and 48MHz output

3 X1 IN C r yst al input , no minally 14.318MHz.

4 X2 OUT Crystal output, nominally 14.318MHz.

5, 9, 13, 20, 26, 30,

38

GND P WR Ground pin for 3V outputs.

8, 7 3V66 [1:0] OU T 3.3V clock outputs

FS0 IN Frequency select pin .

PCICLK0 OUT PCI clock output.

FS1 IN Frequency select pin .

PCICLK1 OUT PCI clock output.

FS2 IN Frequency select pin .

PCICLK2 OUT PCI clock output.

19, 18, 17, 15, 14 PCICLK [7:3] OUT PCI clock outputs.

21, 22 48MHz OUT 48MHz output clocks

SEL24_48# IN

Select pin for enabling 24MHz or 48MHz

H=24MHz L=48MHz

24_48MHz OUT Clock output for super I/O/US B

25 SDATA IN Data input for I2C serial input, 5V tolerant input

28 SCLK IN Clock input of I2C input, 5V tolerant input

29 PD# IN

Asynchronous active low input pin used to pow er down the device into a low

power state. The internal clocks are disabled and the VC O and the crystal are

sto

pp

ed. The latency of the power down will not b e greater than 3ms.

31, 32, 33, 35, 36,

37, 39, 40, 41

SDRAM [8:0] OUT SD RAM clock outputs

43 GNDLCPU PWR Ground pin for the CPU clocks.

44, 45 CPUCLK [1:0] OUT CPU clock outputs.

46 VDD LCPU PWR Power pin for the CPUCLKs. 2.5V

47 IOAPIC OU T 2.5V clock output.

48 VDDLAPIC PWR Power pin for the IOAPIC. 2.5V

23

1

11

12

10

3

ICS9248-99

Preliminary Product Preview

Third party brands and names are the property of their respective owners.

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for

verification. Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I

2

C interface, the protocol is set to use only "Block-Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I

2

C programming application note.

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

(H)

ICS clock will acknowledge

Controller (host) sends a dummy command code

ICS clock will acknowledge

Controller (host) sends a dummy byte count

ICS clock will acknowledge

Controller (host) starts sending first byte (Byte 0)

through byte 5

ICS clock will acknowledge each byte one at a time.

Controller (host) sends a Stop bit

How to Read:

Controller (host) will send start bit.

Controller (host) sends the read address D3

(H)

ICS clock will acknowledge

ICS clock will send the byte count

Controller (host) acknowledges

ICS clock sends first byte (Byte 0) through byte 5

Controller (host) will need to acknowledge each byte

Controller (host) will send a stop bit

Notes:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

AC

K

Byte Count

ACK

Byte

0

ACK

Byte 1

ACK

Byte

2

ACK

Byte

3

ACK

Byte 4

ACK

Byte

5

ACK

Stop Bit

How to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

AC

K

Dummy Command Code

AC

K

Dummy Byte Count

AC

K

Byte 0

AC

K

Byte 1

ACK

Byte 2

AC

K

Byte 3

AC

K

Byte 4

AC

K

Byte 5

AC

K

Stop Bit

How to Write:

4

ICS9248-99

Preliminary Product Preview

Third party brands and names are the property of their respective owners.

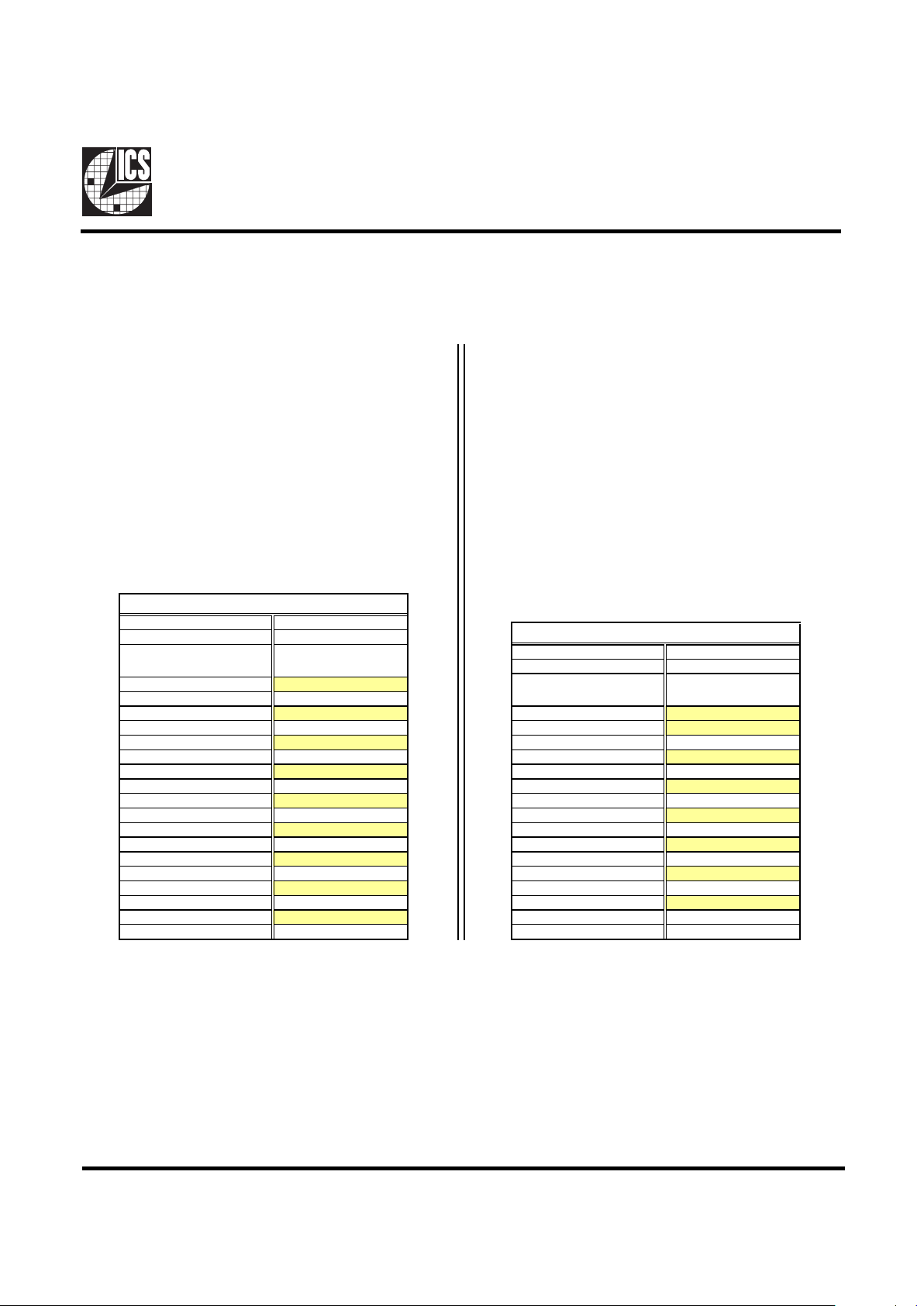

Byte4: Functionality and Frequency Select Register (default = 0)

Serial Configuration Command Bitmap

Note 1: Default at power-up will be for latched logic inputs to define frequency, as displayed by Bit 3.

1) The IOAPIC Frequency change from IOAPIC=PCICLK/2 to IOAPIC=PCICLK is controlled by

IOAPC_Freq control in I2C Byte 3 Bit 1

2) The I2C readback of the power up default indicate the revision ID in bits 2, 7:4

I2C is a trademark of Philips Corporation

tiBnoitpircseDDWP

,2tiB

4:7tiB

)4:7,2(tiB

KLCUPC

)zHM(

MARDS

)zHM(

66V3

)zHM(

KLCICP

zHM(

CIPAOI

)zHM(

11000

1etoN

2/ICP=ICP=

00000 33.5700.31133.5776.7338.8176.73

00001 00.52100.52133.3876.1438.0276.14

00010 00.92100.92100.6800.3405.1200.34

00011 92.05100.31133.5776.7338.8176.73

00100 00.05100.05100.00100.0500.5200.05

00101 00.21100.21176.4733.7376.8133.73

00110 00.54100.54176.6933.8471.4233.84

00111 46.34100.80100.2700.6300.8100.63

01000 03.8605.20133.8671.4380.7171.43

01001 00.50100.50100.0700.5305.7100.53

01010 00.83100.83100.2900.6400.3200.64

01011 00.04100.50100.0700.5305.7100.53

01100 76.6600.00176.6633.3376.6133.33

01101 00.00100.00176.6633.3376.6133.33

01110 06.33106.33170.9835.4472.2235.44

01111 33.33100.00176.6633.3376.6133.33

10000 49.65100.81176.8733.9376.9133.93

10001 00.06100.02100.0800.0400.0200.04

10010 03.64100.01133.3776.6333.8176.63

10011 00.72152.5905.3657.1388.5157.13

10100 00.72100.72176.4833.2471.1233.24

1010 1 00.12100.12176.0833.0471.0233.04

10110 00.71100.71100.8700.9305.9100.93

10111 00.41100.41100.6700.8300.9100.83

11000 00.0800.02100.0800.0400.0200.04

11001 00.8700.71100.8700.9305.9100.93

11010 00.00200.00233.33176.6633.3376.66

11011 00.08100.08100.02100.0600.0300.06

11100 00.66100.66176.01133.5576.7233.55

11101 00.01100.01133.3776.6333.8176.63

11110 00.70100.70133.1776.5338.7176.53

11111 00.0900.0900.0600.0300.5100.03

3tiB

stupnIdehctaL,tceleserawdrahybdetcelessiycneuqerF-0

4:7,2tiBybdetcelessiycneuqerF-1

0

1tiB

lamroN-0

daerpSretneC%52.0±delbanEmurtcepSdaerpS-1

1

0tiB

gninnuR-0

stuptuollaetatsirT-1

0

Loading...

Loading...