Integrated

Circuit

Systems, Inc.

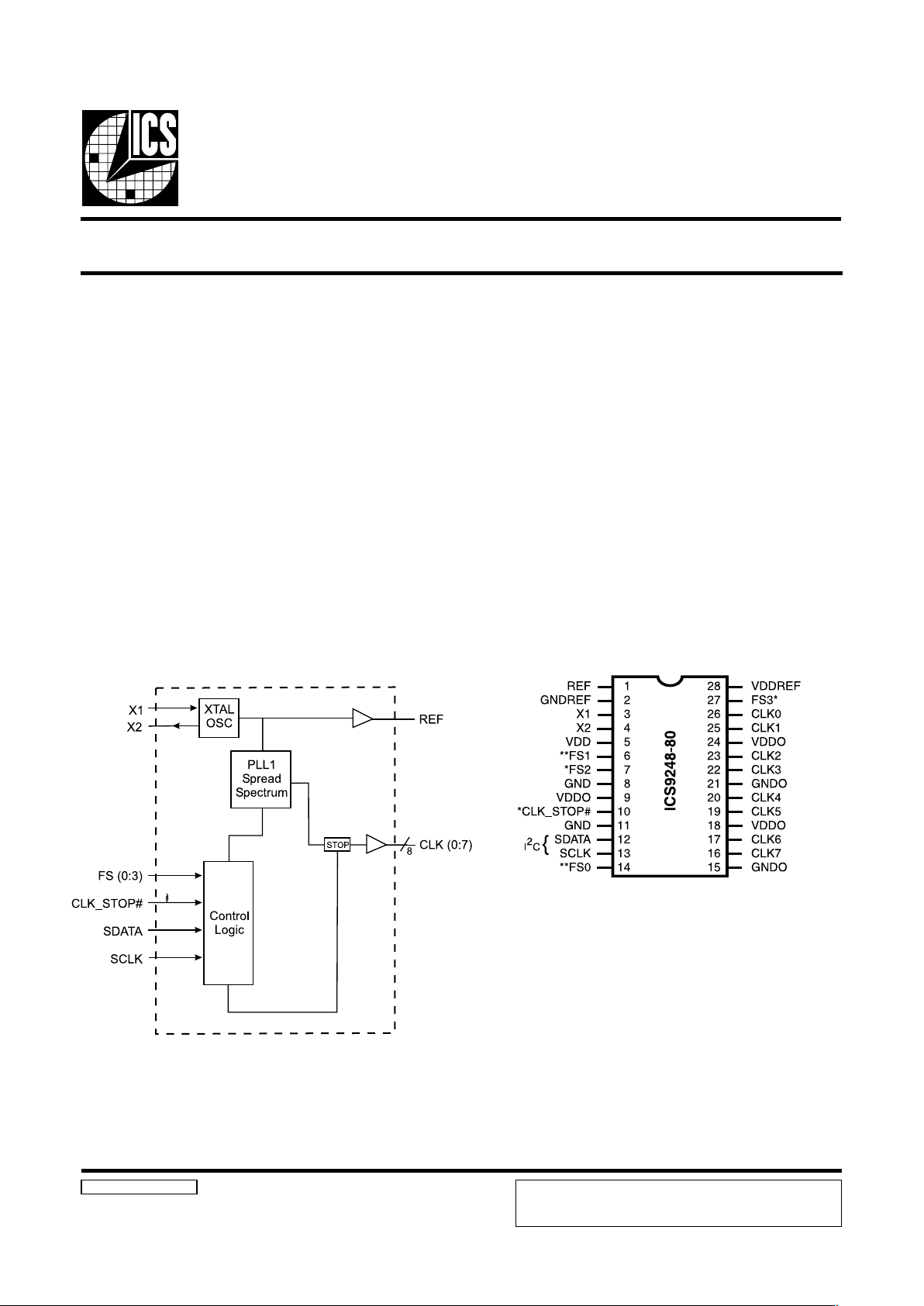

General Description Features

ICS9248-80

Block Diagram

Pentium II is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

General Purpose 133MHz System Clock

9248-80 Rev A 3/21/00

Pin Configuration

Extended temperature range (-20°C to +70°C)

Output features:

- 8 CLK outputs @ 3.3V, up to 133.34MHz.

- 1-REF output @ 3.3V, 14.31818MHz.

Spread Spectrum for EMI control

I

2

C interface to stop clocks, select spread and frequency.

Excellent power managment feature through CLK_STOP#

and individual stop clocks through I2C.

Input is from a 14.31818MHz crystal.

28-Pin 209 mil SSOP

The ICS9248-80 is a general purpose system clock. It

provides 8 output CLKs, 1 REF CLK and excellent power

management features through CLK_STOP#.

Spread spectrum may be enabled through I2C programming.

Spread spectrum typically reduces EMI by 8dB to 10 dB.

This simplifies EMI qualification without resorting to board

design iterations or costly shielding. The ICS9248-80

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

* These inputs have a 120K internal pull-up to 3.3V.

** These inputs have a 120K internal pull-down to GND.

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9248-80

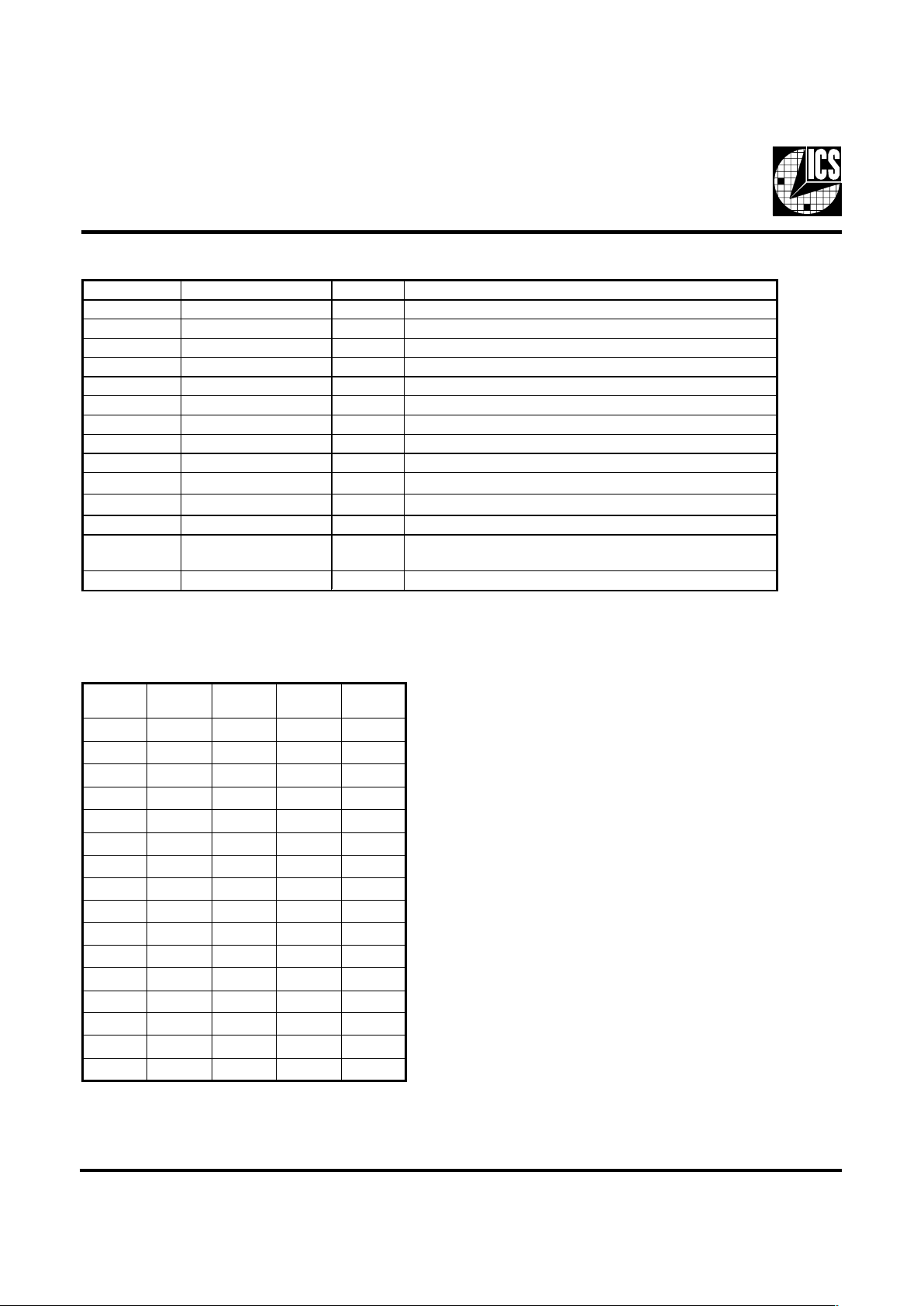

Pin Descriptions

Pin number Pin name Type Description

1 REF OU T 14.318MHz reference clock outputs at 3.3V

2 GNDREF PWR Gnd pin for REF clocks

3 X1 IN XTAL_IN 14 .318 MHz crystal input

4 X2 OUT XTAL_OUT Crystal output

5 VDD PWR

3.3 V power i nput

6, 7, 14, 27 FS (0:3) IN Logic - input for frequency selection

8, 11 GND PWR G round

9, 18, 24 VDDO PWR 3.3V power for CLK outputs

10 CLK_STOP# IN Stops all clock outputs

12 SDATA IN

Data input for I

2

C

serial input.

13 SCLK IN

C

lock input of I

2

C

inp ut

15, 21 GNDO PWR G round for CLK outputs

16, 17, 19, 20 ,

22, 23, 25, 26

CLK (0:7) OU T Clock outputs up to 133.34MHz

28 VDDREF PWR Power pin for REF clocks

3SF2SF1SF0SF

KLC

)zHM(

0000 43.331

0001 10.521

0010 00.021

0011 99.411

0100 99.901

0101 00.501

0110 00.001

0111 00.59

1000 00.09

1001 10.58

1010 00.57

1011 00.07

1100 76.66

1101 00.06

1110 99.45

1111 33.33

Frequency Selection

3

ICS9248-80

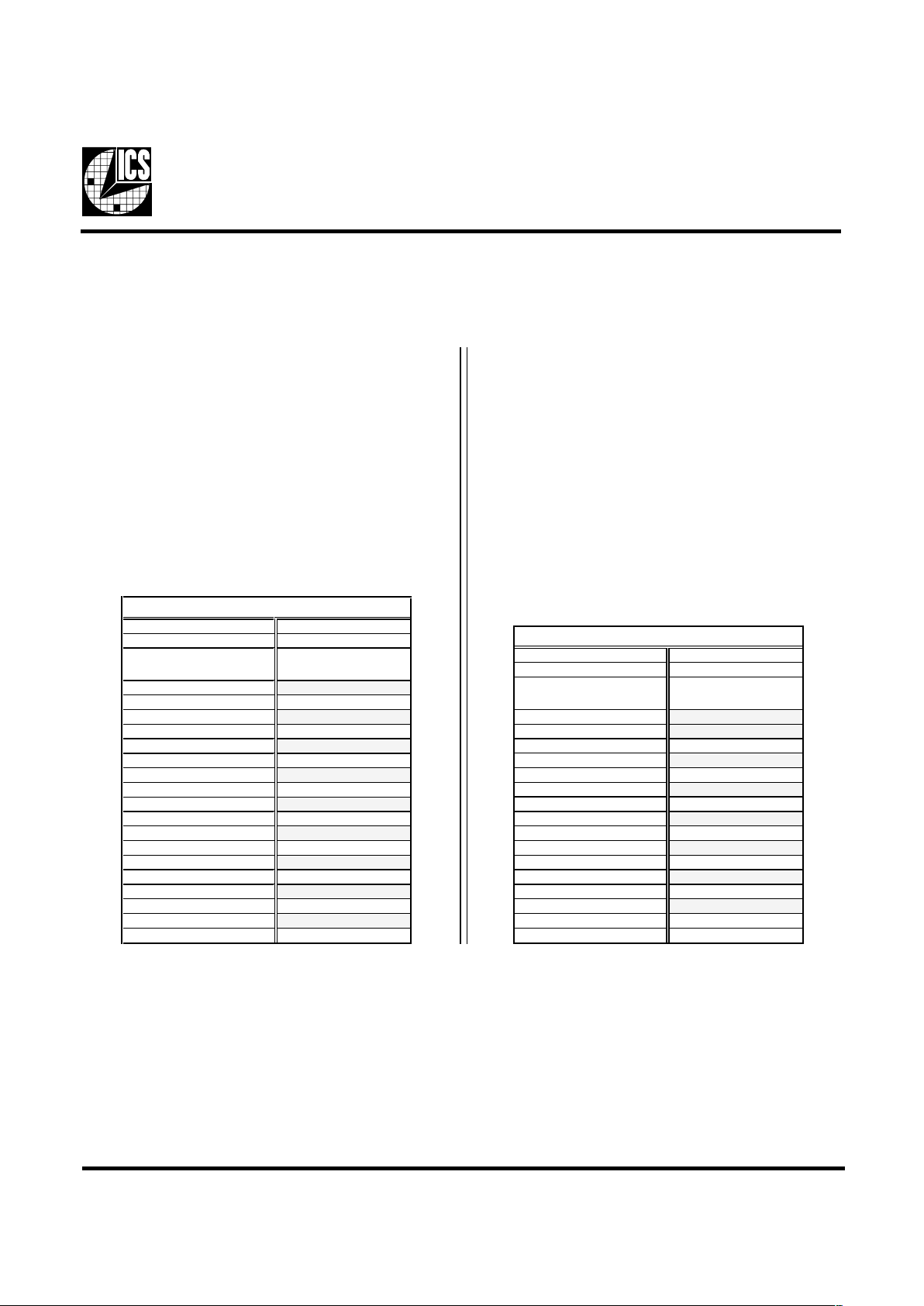

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for verification.

Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I2C interface, the protocol is set to use only "Block-Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I2C programming application note.

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

(H)

ICS clock will acknowledge

Controller (host) sends a dummy command code

ICS clock will acknowledge

Controller (host) sends a dummy byte count

ICS clock will acknowledge

Controller (host) starts sending first byte (Byte 0)

through byte 5

ICS clock will acknowledge each byte one at a time.

Controller (host) sends a Stop bit

How to Read:

Controller (host) will send start bit.

Controller (host) sends the read address D3

(H)

ICS clock will acknowledge

ICS clock will send the byte count

Controller (host) acknowledges

ICS clock sends first byte (Byte 0) through byte 5

Controller (host) will need to acknowledge each byte

Controller (host) will send a stop bit

Notes:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

ACK

Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Stop Bit

H

ow to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

ACK

Dummy Command Code

ACK

Dummy Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Stop Bit

H

ow to Write:

Loading...

Loading...