ICST AV9107C-20CS08, AV9107C-19CS08, ICS9107C-19CS08, ICS9107C-20CS08 Datasheet

Integrated

Circuit

Systems, Inc.

General Description Features

AV9107C-19

AV9107C-20

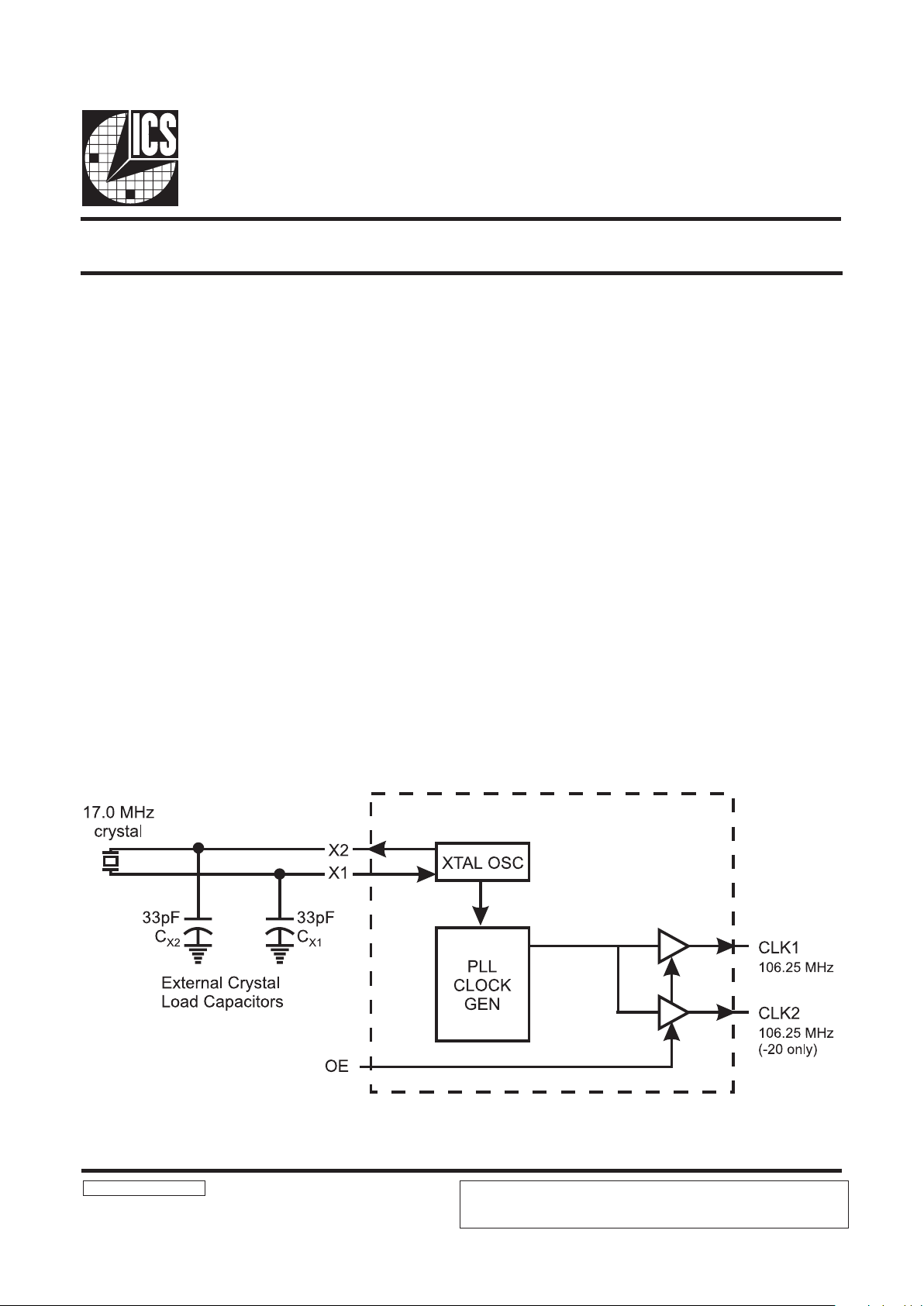

Block Diagram

Frequency Generator for Fibre Channel Systems

Applications

AV 9107-19 20 RevC091897P

The AV9107C-19 and AV9107C-20 are high-speed clock

generators designed to support fibre channel system

requirements. The AV9107C-19 generates a single copy of

the 106.25 MHz from a 17 MHz crystal. The AV9107C-20

provides a second copy of the 106.25 MHz clock with

output skew less than ±100ps.

An exact frequency multiplying ratio ensures better than

±100 ppm frequency accuracy using a standard AT crystal

with external load capacitors (typically 33pF±5% for an

18pF load crystal). Achieving ±100 ppm over four years

requires the crystal to have a ±20 ppm initial accuracy, ±30

ppm tempera-ture and ±5 ppm/year aging coefficients.

Generates one or two 106.25 MHz clocks from a

17 MHz crystal

Less than 60ps one sigma jitter

Less than ±200ps absolute jitter

Output skew less than ±100ps on two channel

version (-20)

Rise/fall times less than 4ns driving 15pF

On-chip loop filter components

3.0V-5.5V supply range

8-pin, 150-mil SOIC package

Specifically designed to support the high-speed

clocking requirements of fibre channel systems

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

2

AV9107C-19

AV9107C-20

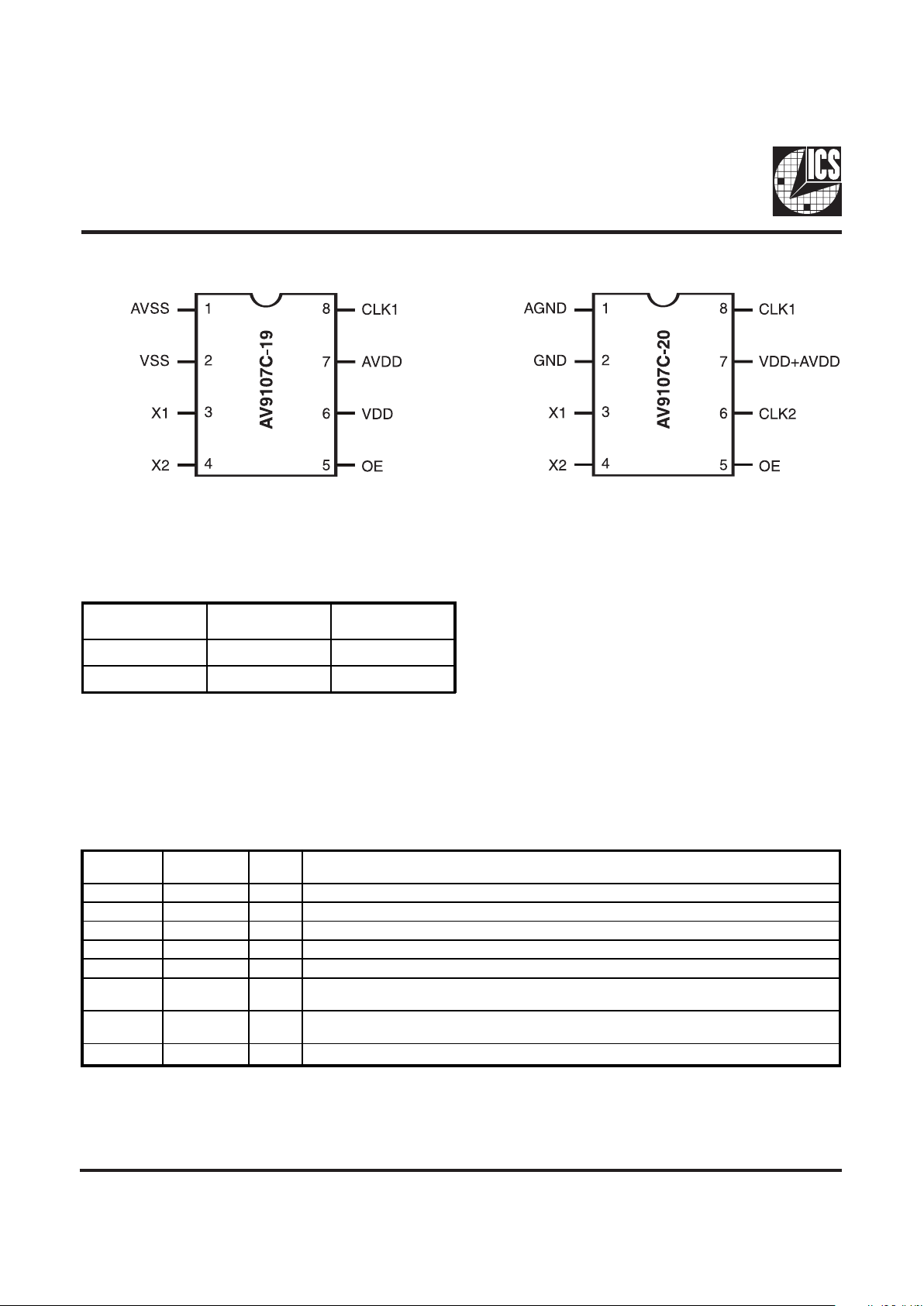

Pin Descriptions

Pin Configurations

8-Pin SOIC

Functionality

PIN

NUMBER

PIN NAME TYPE DESCRIPTION

1 AVSS PWR Analog ground.

2 VSS PRW Digital Ground.

3 X1 IN Crystal or clock input to device; nominally 17.0 MHz. Requires external load capacitors.

4 X2 IN Crystal drive output from device. Requires external load capacitors.

5 OE IN Output enable causes all outputs to tristate when at a logic low level; has a pull-up.

6

VDD

CLK2

PWR

OUT

+3.3 or +5.0 volt supply (-19).

106.25 MHz clock output (-20).

7

AVDD

VDD+AVDD

PWR

PWR

Analog power. (Must equal digital power voltage) (-19).

Digital and analog power, +3.3 or +5.0 volt supply (-20).

8 CLK1 OUT 106.25 M Hz clock output.

8-Pin SOIC

OE

X1, X2

(MHz)

FOUT

(MHz)

1 17.00 106.25

0 X Tristate

Loading...

Loading...