Integrated

Circuit

Systems, Inc.

ICS2002

Wavedec Digital Audio Codec

ICS2002RevF093094

Features

•• Digital audi o 8/16-bit record/p layba c k

•• Fully programmable sample rates including industry

standards:

- 44.1 kH z

- 22.050 kHz

- 11.025 kHz

- 8.00 kH z

- 5.513 kHz

•• DAC output over sam pl ed to simplify exte rna l fi lt e rin g.

•• Fo u r data for mats:

- 16 bit linear

- 8 bit l ine a r

- 8 bit u-law

- 8 bit a-law

•• 16 step analog output level con tro l, -1. 5dB /ste p

•• 8-bi t log sc a le di git a l vol um e con trol

•• Oversampling ADC with input filter.

•• Progra mmable IIR filter s for inp ut anti-a liasing a nd output

reconstructio n.

•• ISA bus interface

•• 8/16-bit DMA and I/O transfe r mo de s

•• Input/o utp ut FIFO buffer

•• Power-down mode

•• 44-pin PL CC pa c ka ge

Block Diagram

Description

The ICS2002 is a mixed-signal integrated circuit providing a

low-cost recording and playbac k solution for multime dia audio

appli cat ions. These ap pli cat io ns inc lude doc um en t annot ati on,

voice mail, interactive games, multimedia sound record/playback, and Windows sound production. The ICS2002 sup-

ports the record and pla yback of 16-bit a udio data, and provides

a 8/16-bit p ar al le l interface to the industry standard PC bus.

Wavedec is a trademark of Integ rated Circuit Systems, Inc.

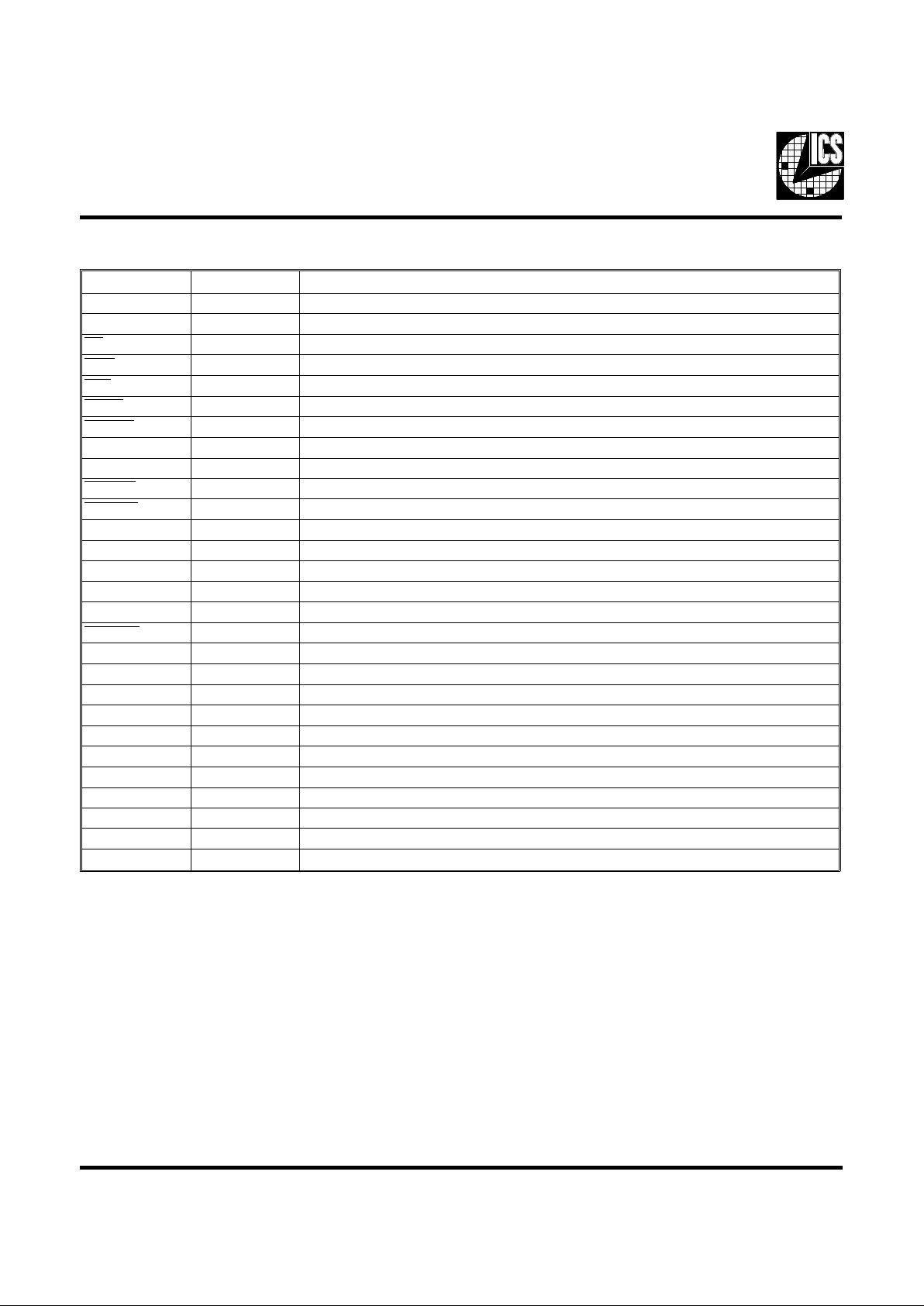

Pin Descriptions

PIN TYPE DESCRIPTION

SD15 - SD0 I/O Data bus

SA1 - SA0 I Address

CS I Chip select (active low)

IOW I Write strobe (active low)

IOR I Read strobe (active low)

SBHE I System High Byte En able (active low)

IOCS16 OC Indicates that the access reg iste r ca n suppor t 16 bit transfe r.

DRQP O DMA Request (play channel)

DRQR O DMA Request (r ecor d chan nel)

DACKP I DMA Ack nowl edge (play c hannel)

DACKR I DMA Acknowl edge (recor d chan nel)

TC I DMA terminal count

IRQ O Interrupt re que st (a c ti ve high , open dra in)

RESET I Reset (active high)

XTLI I Crystal oscill ator

XTLO O Crystal oscillator

PWRDN I Power-down (active low)

AUDIOIN AI Audio buffer input

ADCIN AO Audio buffer output/ input to ADC

DACOUT AO DAC audio output

BUFIN AI Uncommitted audio buffer input

BUFOUT AO Uncommitted audio buffer output

VDD P Digital +5V supply

VDDA P Analog +5V supply

VDDP P Digital +5V supply

VSS P Digital GND

VSSA P Analog GND

VSSP P Digital GND

ICS2002

2

Package Pinout

44-Pin TQFP

44-Pin PLCC

ICS2002

3

Absolute Maximum Ratings

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7.0V

Logic Inputs . . . . . . . . . . . . . . . . . . . -0.5V to V

DD

+ 0.5V

Ambient Operating Temperature. . . . . . . . . . 0°C to 70°C

Storage Temperature . . . . . . . . . . . . . . . . . -65°C to 150 °C

Stresses abo ve tho se l isted unde r Absol ute Ma xi mum Ratings may cause pe rma nent d ama ge to the de vice. This is a stres s ratin g

only and functi ona l oper atio n of the devic e at these or any othe r conditions above those indi cat e d in the ope ra ti ona l sect io ns of

the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product

reliability.

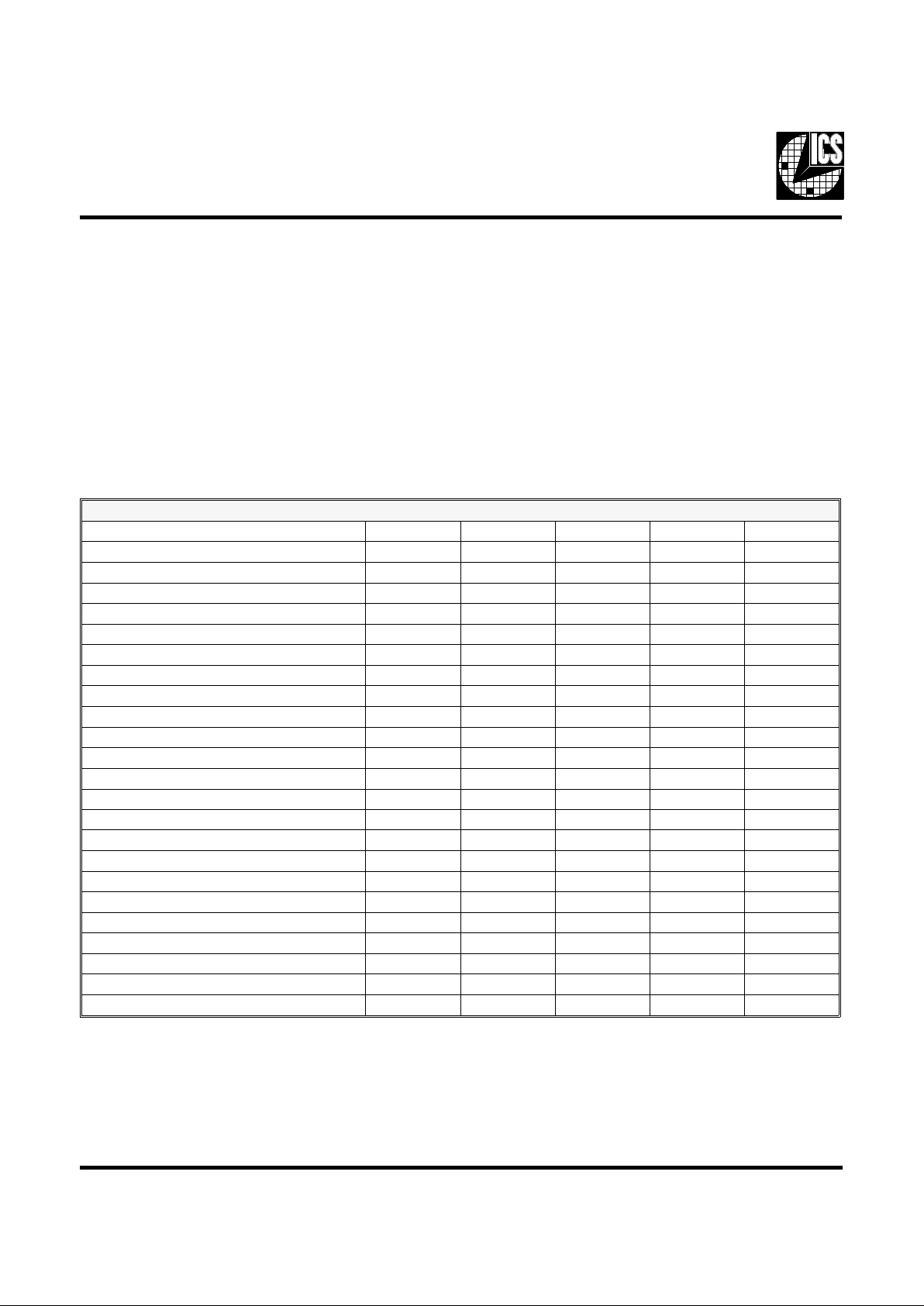

Electrical Characteristics

VDD = 5.0V ± 10%; GND = 0V; TA = 0°C to +70°C

DC/STATIC

P ARAME TER SYMBOL MIN TYP MAX UNITS

Digital Inputs

Input Low Voltage V

IL

-0.3 0.8 V

Input High Voltage V

IH

2.0 VDD + 0.3 V

Input Leakage Curre nt I

LI

1 µA

Input Capacitan ce C

IN

7pF

Digital Outputs

Output Low Voltage (I

OL

= 4.0mA) V

OL

0.4 V

Output High Voltage (I

OH

= 0.4mA) V

OH

2.4 V

Tristate Current I

OZ

10 µA

Output Capacita nce 10 pF

Bi-direc tional Capacitance 10 pF

Analog Inputs

Audio Input Voltage 0.7 V rm s

Audio Input Impedanc e 500k o hm

Buffer Input Impedance 500k ohm

Audio Outputs

Audio Output Voltage 0.7 V rm s

DACOUT, BUFOUT Output Impedance 1k ohm

Digital Supply Current I

CC1

1mA

Analog Supply Current I

DD2

35 mA

Power-Down Mod e 1 mA

Play Only Mode 15 mA

Record Mode 30 mA

ICS2002

4

Electrical Characteristics

VDD = 5.0V ± 10% ; GND =0V; TA = 0° C to +70°C

AC/DYNAMIC

PARAMETER SYMBOL MIN TYP MAX UNITS

Address setup to command t

AS

10 ns

Address hold from command t

AH

10 ns

Command cycle time t

CCY

100 ns

Address valid to /IOCS16 delay t

AID

50 ns

IOCS16 hold from address invalid t

IH

0ns

Data valid to /IOW t

DS

50 ns

/IOR active to valid data t

DAC

60 ns

Data hold after /IOR t

DHR

0ns

Data hold after /IOW t

DHW

10 ns

/DACK setup to /IOR t

DAR

30 ns

/DACK setup to /IOW t

DAW

50 ns

/DACK hold from command t

DAH

50 ns

/CS setup to comma nd t

CS

10 ns

/CS hold from comm a nd t

CH

10 ns

TC setu p to c om m and inacti v e t

TS

25 ns

TC hold from command t

TH

0ns

ICS2002

5

ICS2002

6

ICS2002

7

Digital Audio Playback

To play digital audio files, the chip is programmed for the

desired sa mple rate, dat a type, DMA cha nnel wi dth, an d output

volume .

For DMA mode playback, DRQ generation is programmable

for servicing the FIFO at several levels. This allows optimal

performan ce with a vari e ty of hosts. Whe n TC is rece ived , the

chip wil l opt ion ally ge ne ra te a n in terru pt to t he ho st to ind ic ate

the nee d to servi c e the DMA controll e r.

For I/O Mode playback, data is written to the FIFO until it is

full. This is determined by polling the “DIR” bit of the status

register. Once the FIFO is fu ll, an i nterrupt will be generated

optionally at one of several selectable points: 1/4, 1/2, or 3/4

full. The ho st ca n t hen bu rst a p re dete rmin ed amo unt of da ta t o

the FIFO and wait for the next in terru pt.

Digital Audio Recor ding:

Audio recording operates in a DMA or I/O mode similarly to

audio playba ck with th e audio in put program mable as a line or

microphone level input. Simultaneous record and playback is

supported and permits the recorded file to be synchronized to

an existing file. The new and existing file can then be mixed

digita ll y for hi gh qu al ity re sults.

Data Processing:

To simplif y the e xtern al circu itry associa ted wit h the a nalog

input and output signals of the chip, input and output sample

rates are oversample d. This allows si mple RC filters to b e used.

For playback, the output data is oversampled, interpolated,

filtered and scaled. Since the DSP is fully programmable,

various sampl e rates and filter shapes can be imple mented. The

processed data is then output to the DAC. The DAC output

passes through an analog volume control (4 bits, 1.5dB steps)

befor e be i ng pa s sed t o the analog filte r sta ge.

For recording, t he input da ta is first filtered, removing most of

the freque ncy co ntent ab ove the Nyqu ist fre quenc y . The result ing data stre am is the n undersam pled to the d esired sam ple ra te

and fed in to t he FIFO for tr an sf er to the host .

Power Management:

The

PWRDN input can be prog ramme d to a ct as an i mmedi ate

hardware powe r control, or as an inter rupt source for a softwa re

driven power mana gement routine . The software driven optio n

allows the driver to clean ly shut down to chip, thus preve nting

unwanted noise. When active, the power-down function disables a ll an alog com ponents including the osc illator , a nd cau ses

the chip to enter a low power mode.

Miscellaneous Functions:

The chip has a full com pleme nt of status and cont rol functi ons.

All significant functions are capable of generating interrupts

and/or be in g pol le d.

The DMA can be run in single or demand mode (for bursts of

data in progr ammed sizes).

The FIFO has programmable interrupt and DMA request capacitie s, and also in dicate s when overfl ow or unde rflow condi tions occur.

The processor interface is designed for simple connection to

the ISA bus. For be st noise perfo rmance, isol ating the data lines

from the ISA bus is recommended. In ge ne ral , fee d through of

digital noise is reduced by minimizing the load which the

digita l out put s are dri vi ng.

ICS2002

8

76543210

Clear Play IRQ

Clear Record IRQ

reserved

Power-Down Mode IRQ

FIFO Overflow/Underflow IRQ

Sample Rate IRQ

FIFO Ready

IRQ (same as pin)

Status (Base + 0 read)

76543210

Clear PLAY IRQ

Clear REC IRQ

reserved

Clear PDM IRQ

Clear FOU IRQ

Clear SR IRQ

reserved

reserved

IRQ Reset (Base + 0 write)

This register provides the driver software easy access to the

interrupt source when read. Note that bit 7 indicates the state

of the IRQ pin, and hence will be zero when th e MIE bit is zero

(see “Interrup t Ena ble” regist er ).

A write to the re gister is performed to cle ar interrupts. Writing

a one to a given bit will cause the associated interrupt to be

cleared. To release the clear interrupt bit and allow further

interrupts to occur, a zero must be written back to the bit of

interest (some bits have alternat e methods of cleari ng described

later). This feature ensures that if the interrupt condition still

exists, an edge will be gener ate d on the IRQ pin, th us ensurin g

recognition on platforms that are edge sensitive. This also

allows for a return fr om inter rupt instruc tion t o be execut ed on

the pla tfo rm wh il e the IR Q li ne is ina c ti ve .

Bit 6 is a special case . There is no IR Q associat ed wit h this bit.

It is located here for use in Soun d Source Emul ation Mode , and

represents the BUSY status of a Sound Source. When the

ST ATUS is read and tested with 40h, a zero r esult indic ates that

the play FIFO is full.

76543210

Register Address (RA) (Base + 1)

76543210

Data Low Byte/Word (DLW)

76543210

Data High Byte (DH) (Base + 3)

Note that this register can only be read in STAND ALONE

mode. Hen ce, indir ect acc ess t o t his regist er ha s be e n provi de d

at RA=83h for use in COMP ANI ON mode.

Direct Register Descriptions

The base address is determined externally by an address decoder which selects the chip via the

CS input.

This register is the indirect pointer to direct data transfers to

and from the da ta reg iste rs. It is a read/ write re gister. Note that

this register can only be read if the chi p is in STAND ALONE

mode.

These two addre sses are used t o accomplish all internal register

reading and writing. Most internal registers are 8-bit or less.

These are a cces sed by first wri ting th e appr opria te value to the

DW, then wri ti ng (re a di ng) the data byte to (from) DLW.

I/O Mode FIFO data (RA= 0Bh), Algor ithm RAM, and Coef ficient RAM are always treated as 16-bit entities, and can be

transf erred in t wo w ays:

- a single operation to/ from DLW with

SBHE = 0

- two successive operations, l ow byt e to/f rom DLW

with

SBHE = 1, then high by te to/ from DH.

ICS2002

9

Indirect Register Map

Indirect

Address Register

4E Companion Se le ct Regi ste r (wri te onl y)

80 Chip Control

81 Interrupt Enables

82 reserved

83 Interrupt status

84 Sample Rate Low 8 bits

85 Sample Rate High 4 bits

86 Sample Rate Control/Status

87 reserved

88 Play DMA Co ntrol

89 Play DMA Burst Cou nt

8A Play DMA Mode

8B DMA IO Mode Data Port

8C FIFO Enable/St a tus

8D FIFO IRQ Mode

8E reserved

8F reserved

90 Power Enable/Status

91 Power Mode

92 reserved

93 reserved

94 DSP Control/Status

95 DSP RAM Address Latch

96 Code RAM Data Port (8/16-bit)

97 Data RAM Data Port (8/16-bit)

98 Record DMA Control

99 Record DMA Burst Count

9A Record DMA M o de

9B reserved

Indirect

Address Register

9C Record FIFO Enable/Status

9D Record FIFO IRQ Mode

9E reserved

9F reserved

A0 Digital Mast er Volu me

A1 DAC Deglitcher Contro l

A2 reserved

A3 reserved

A4 ADC Control

A5 Analog Volume/Mute

A6 ADC Timing Control

A7 reserved

ICS2002

10

Indirect Register Definitions

All write able bit s/registers are also readab le. In a ddition, t here

are some read only bits/re gisters, which are not ed where appropriate.

Reserved bits should be written to zero, and read back zeros.

Reserved regist er s should not be writ ten or read.

Except where noted, registers should be accessed as 8 bit

registers via ad dress BASE+2.

General Purpose Registers

IR4E Register Access Mode Select

This register must be written to 01h for any other

indirect (or direct) accesses to occur, except for RA

writes, which always occur based on chip select. This

indirect address allows multiple companion chips to

share resources in a system (such as bus buffers, a ddress

decode s, interr upts, and DM A channels).

This register is cleared only by hardware reset, and in

unaffe c ted by MCR (see be lo w).

IR80 Chip Control

Bits 7:3 - rese rve d

Bit 2 - Sound Source Emulation Mode (SSMODE)

This bit sets t he ch ip to op erate in Sound S o urc e E mu lation mode . In Sound Source E mulation Mode , the two

address pins (SA1, SA0) are mapped to match the PC

parallel port as used by the Sound Sou rc e as follows:

Chip Addre ss Sound Source IC2002

0DataDH

1 Status Statu s

2 Control DL

3 unused RA

To use this mode, the chip must be configured before

the Sound Source compatible application is run (I/O

Mode DMA, DSP loaded and running, SR running,

etc.) . Then, the IC2002 is put in SSMODE and RA

(now at addre ss 3) is writ ten to 8Bh. In the PC, the BIO S

pointer to the parallel port is changed to the base address

of the IC2002 chip, and the application can then be

started.

This bit is reset by MCR. Hence, it must be set after

MCR is set, on a second write to this register .

Bit 1 - Chip STAND ALONE Mode

This bit sets the chip to operate in STAND ALONE

mode. In STAND ALONE mode, the STATUS and RA

registers are accessibl e at BASE+0 and BASE+1. This

mode should be used to speed register access when the

ICS2002 is being used by itself, without other ICS

chips sharing resources ( such as addr ess decodes, interrupts, DMA channels, bus buffers, etc.).

When bi t 1 i s ze r o , the ICS20 02 will operate in COMPANION mode. In this mode, the STATUS register is

mapped only to indirect address 83h. This is done to

avoid conflict with other ICS chips that will provide

STATUS and RA read back at the first two base addresses.

In addition, STAND ALONE mode configures the

DRQP , DRQR, and IRQ pins to oper ate as outputs, with

both one and zero lev els being ac tively driven. When

in COMP ANION mode, t hese pins have a stron g source

for the high state and a weak sink for the low state to

allow wire-a nd conne ct ions to ot he r ICS chip s.

This bit is reset by hardwa re reset only, not by MCR.

Bit 0 - Master Chip Reset (MCR)

0 - Hold chip in reset

1 - Remov e re set

This bit is c leared to zero by a ha rdware rese t. Thus, an y

functions reset by MCR are also reset by the RESET

pin.

ICS2002

11

IR81 Interrupt Enables

Bit 7 - Master Interrupt En able (MIE )

In the zero state, this bit prevents the IRQ pin from

going acti ve (hi gh) re ga rdless of the sta te o f any of t he

individual interrupt sources. It is cleared to zero by

MCR. A zer o in this bi t does not pre ve nt an individual

interrupt source from bei ng activ e in the STATUS register. This allows interrupts to be ma sked while allo w -

ing thei r sta tus to be po ll ed .

Bit 6 - rese r ved

Bit 5 - Sample Rate Interrupt Enable (SRIE )

Bit 4 - FIFO Overflow/Unde rfl ow Int e rrup t

Enable (FOUIE)

Bit 3 - Power-down Mode Change Int e rrup t

Enable (PMCIE)

Bit 2 - rese r ved

Bit 1 - Record FIFO Interrupt Enabl e (RFIE )

Bit 0 - Play FIFO Interrupt Enable (PFIE)

Each of th ese bits in dividually enables, one, or disa bles,

zero, their respective interrupt sources from being ac-

tive in the STATUS register. In addition, there will be

no IRQ generated if MIE is one when an individual

enable bit is zero. The state of this bit does not affect

the source of these inte rrupts in any way, and they may

be polled for activity in the approp riate register for each

interrupt type. These bits are all cleared to zero by

MCR.

IR83 Status

This register is the same as the direct access status register,

except that it can be read in COMPANION mode.

Sample Rate Generato r Regi sters

IR84 Sample Rate Low 8 bits (SRL)

Bits 7:0 - Sam pl e Ra t e Bits 7:0

IR85 Sample Rate High 4 bits (SRH)

Bits 3:0 - Sam pl e Ra t e Bits 11:8

Together, these two registers define the record and

playback sample rate. Based on the crystal frequency

FXtal, and a 12 bit value SR (the concatenation of the

two registers), the sa mple rate will be:

Sample Rate = FXtal * SR / 524288

These registers are not initi alized by any of the res et

mechanisms. Note that the Sample R ate Counter should

always be stopped via SRCS bit 0 when these two

registers are changed.

IR86 Sample Rate Control/Statu s (SRCS)

Bits 7:2 - rese rve d

Bit 1 - Sample Rate Int errupt (SRIRQ) - Read Only

This is set by the hardware whenever the sample rate

counter overflows, indicating that a new sample is

being input or generated. This bit is cleared by any of

the following act ion s:

- Mast e r C hip Rese t

- Sample Rate Run = 0 (SRR bit 0)

- a writ e t o STATUS with bit 5 = 1

- any write to SR C S

Bit 0 - Sample Ra te Run (SR R)

This bit resets the Sam ple Ra te Count er , the SRIRQ bit,

and shuts down the sampling and playback pro-cesses

when written to a zero. When written to a one, the

sample rate generator runs at the programmed rate.

SRR is internally synchronized to the master clock to

provide clean starts and stops of the counter. MCR

clears this bit.

ICS2002

12

Play DMA Control and Status Registers

IR88 Play DMA Contro l (DMACTL )

Bits 7 - re se r v ed

Bit 6 - TC Re set Mask

When set to 1, t his bit masks the ‘DMA Run’ bit res et

upon recei pt of TC, term inal count , signal from th e ISA

bus. When reset to 0, the ‘DMA Run’ bit will be reset

upon receipt of TC.

Bits 5:1 - rese rve d

Bit 0 - DMA R un

This bit enables the DMA hardware to begin transfer-

ring data when set to one. It is cleared by either MCR

or receipt of a TC whe n ‘T C R ese t Ma sk’ is a zero (see

the DMAMODE register for detai ls).

IR89 Play DMA Burst Count (DM ABC)

Bits 7:6 - rese rve d

Bits 5:0 - DMA Burst Count

This value determines the number of DMA transfers

that take pla ce for each DMA r equest issued to the host.

The actual number of transfers will be DMABC+1.

Thus, for single transfe r mode , program this registe r to

zero . The b urst c ounte r is automat icall y pres et to the

burst co unt wh e neve r th e

DACKP input is high. Thus,

there is no need t o reprogram the count value aft er TC,

since the next transfer will use the full programmed

count value. This register has no affect on I/O Mode

data transfers, sinc e its only influence is over the DRQP

output. This register is not initialized by any means

other than a direct write, and hence must be written to

before DMA is enabled.

IR8A Play DMA Mode (DMAMODE)

All bits in this re gist er are c lea re d by MCR.

Bits 7:6 - rese rve d

Bit 5 - T erm ina l Count Int er rupt (TCIRQ) - (re ad on ly)

This bit indicates that a Terminal Count has been received on the last DMA operation. If the PFIE and

PLAYIRQ bits have been programmed to a one, an

interrupt will be generated at the end of the last DMA

operation. This bit is cleared by MCR or a write to

STATUS with bit 0 = one. The reset state is then

removed by e ithe r wri ti ng th e STATUS bit 0 to zero.

Bit 4 - I/O Mode Transfe r (IOXFE R)

When this bit is a one, the DMA hardware (DRQP and

TCIRQ) is disabled. Data transfers take place via IR8Bh,

and are required to be treated as 16-bit transfers. Thus, data

should be written to DL W (with

SBHE = low , 16- bit data)

or to DLW (with

SBHE = high, 8-bit data low byte)

followed by DH (8-bit data, high byte). It is also the

programmers resp onsibility to ensure that DMAMODE

bit 2 (DMA16) is set to a one for all I/O mode transfers.

Bit 3 - Unsigned Data (USIGN)

When set to a one, this bit expects to receive (and will

generate) unsigned data. The native data format is

Signed Binary Twos Complement. This bit will invert

the most significant bit of each data byte (or word,

depending on the state of DATATYPE). Note that this

bit should be zero when the DATATYPE indicates

u-law or A- l aw da ta fo rm at s.

Bit 2 - 16 Bit Data (DMA16)

When set to a one, this bit ca uses the hardware to expect

data to be sent in 16-bit words. When low , the hardware

expects 8-bit bytes. This bit must be set to one when

performing I/O mode transfers, as all I/O transfers are

treat ed as 16 bi t va lu es.

Bit 1:0 - Data T ype (DATATYPE)

These bits direct the hardware how to interpret the

outgoing data. This is independent of the DMA or I/O

data width. It effects how data is signed and how data

is packed to and unpacked from the Play FIFO. The

DATATYPE field selects the format of data for playback.

Value Data Type

00 8-bit linear

01 16-bit linear

10 8-bit µ256 Law

11 8-bit A-L aw

IR8B DMA I/O Mode Data Port (DMADATA) (8/16-bit)

This register address is used to trap I/O mode data to

and from the FIFOs. It is only used in I/O mode. See

the description of the IOXFER bits for more details.

When DMA16 is one, this register MUST be ac c essed

as a sixteen bit value. Note that this can be done from

either an eight or sixtee n bit ISA slot, since the chip used

SBHE to determine the proper byte swapping.

ICS2002

13

FIFO Con trol/ Stat us Regi ste rs

IR8C FIF O Enab le/Statu s (F ES)

Bit 0 - FIFO Enable (FE)

This bit holds the FIFO in a reset state when low, and

enables the FIFO to operate when high. This bit is reset

by MCR. This bit, when low , also resets all FIFO related

conditions (see the following bits) and prevents DMA

start requests from being issued. It does not reset the

FIFO IRQ Mode register.

Bit 1 - FIFO Overflow (read only)

This bit is set when a FIFO shi ft in com mand is g en erated (by either DMA, I/O, or the DSP) with the FIFO

full, an d indic ates a n error condit ion. T his b it will cause

the FOUIRQ bit to go active, generating an IRQ if

enabled. This bit is reset by writing to ST ATUS with bit

4 = 1, and re-e nabled by wr i ti ng t o S TATUS with bit 4

= 0. FE low also rese ts thi s bit .

Bit 2 - FIFO Underflow (read on ly)

This bit is set when a FIFO shift out command is

generated (by either DMA, I/O, or the DSP) with the

FIFO empty, and indicates an error condition. This bit

will cause the FOUIRQ bit to go active, generating an

IRQ if enabled . Thi s bit is re se t by writ ing to STATUS

with bit 4 = 1, and re-enabled by writing to STATUS

with bit 4 = 0. FE low also re sets this bit.

Bit 3 - FIFO 25% Full (read only)

This bit goe s high afte r 4 wo rds (o r 8 byt es) ha ve be e n

loaded into the FIFO, and low aga in when 13 words (or

26 bytes) may be loaded into the FIFO. There is no

interrupt associ a te d wit h this bit direc t ly.

Bit 4 - FIFO 50% Full (read only)

This bit goe s high after 8 wo rds (or 16 bytes) ha ve been

loaded into the FI FO, and l ow ag ain whe n 9 words (or

18 bytes) may be loaded into the FIFO. There is no

interrupt associ a te d wit h this bit direc t ly.

Bit 5 - FIFO 75% Full (read only)

This bit goes high after 12 words (or 24 bytes) have

been loaded into the FIFO, and low again when 5 words

(or 10 bytes) may be loade d into the FIFO. There is no

interrupt associ a te d wit h this bit direc t ly.

Bit 6 - FIFO DIR (read only)

This bit goes high when a single word (or two bytes)

may be written to the FIFO. There is no interrupt

associate d with this bi t dire ctly. Note that this b it rese ts

to a one because when the FIFO is reset it is forced to

be empty, and hence is ready to accept data.

Bit 7 - FIFO DOR (read only)

This bit goes high when a single word (or two bytes)

may be read from the FIFO. There is no interrupt

associated with this bit directly.

IR8D FIFO IRQ Mode

This register must never be written to when the FIFO is enab led.

Invalid interrupts and DMA requests could be generated as a

result.

Bits 7:4 - rese rve d

Bit 3 - FIFO IRQ Enable (FIE)

This bit enables the various FIFO capacity thresholds

to generate interru pts (a s PLAYIRQ) when one. When

zero, this bit prevents FIFO capacity IRQ generation

when operating in DMA mode, which only needs

TCIRQ.

Bits 2:0 - FIFO Ready IRQ Mode Selection

This field defines FIFO utilization for both DMA and

I/O mode data transfers. In I/O mode, it is used to

generate inte rrupts (FRDYIRQ) wh en the FIFO ca pacity reaches a predefined point. For DMA transfers, it

signals the DMA logic to request a transfer at those

same predefined points. By programming the DMA

Burst Count appropr iately , the FIFO m ay be easily kept

near the de sire d ca pacity.

The following table describes the selections available:

Bits

2:0

IRQ/DRQ

Source Notes

000 DIR Ready to take 1 word from HOST

001 EMPTY 75% Ready to take 13 words from

HOST

010 EMPTY 50% Ready to take 9 word s from HOST

011 EMPTY 25% Ready to ta ke 5 words from HOST

100 DOR Ready to provide 1 word to DSP

101 FULL 25% Ready to provide 4 words to DSP

110 FULL 50% Ready to provide 8 words to DSP

11 1 FULL 75% Ready to provide 12 words to DS P

Note that for byte transfers (DMA16=0), the numbers listed

above should be doubled.

This must be programmed before the FIFO is enabled. It may

be changed while the FIFO is enabled, if necessary. This

register is cle ar ed by MCR, but not by FE lo w.

ICS2002

14

IR8E reserved

IR8F Play FIFO Output Data Read Back (8/16 bit)

This registe r is provide d for test use onl y , although it may find

system level use as a diagnost ic too l.

Power Control and Status

IR90 Power Enable/Statu s ( PEST )

Bit 7 - PWRIRQ (read only)

This bit is a one when either edge has occurred on the

PWRDN pin, and the edge enable in the Power Mode

register is set. If bit 3 of the MIE is one, this will also

generate an external interrupt. In any case, this bit is

also visible as STA TUS regi ster bit 3. PWRIRQ is re set

by disabling both edge enable bits or resetting the edge

interrupts (see below).

Bits 6:5 - rese rve d

Bit 4 - ADCPWR Disab le

This bit controls the power state of the ADC analog

circuitry. When 0, ADC analog power is contr olle d by

the SOFTPWR bit the same as the DAC analog powe r

is. When this bit is set to a 1, the ADC analog power is

turned off independent of the stat e of SOFTPW R.

This feature is included for advanced power manage-

ment routines, as chi p power dissipation can be re duced

by almost half by turning ADC power off when not in

use. Note, howe ver , that seve ral milliseco nds of settl ing

time is required afte r power is turned on before the ADC

functions properly.

Bit 3 -

PWRDN Pin Value (read only)

This bit indicates the sta te of the

PWRDN pin.

Bit 2 - F AL L IRQ (re a d only)

This bit is set when the

PWRDN pi n make s a transit ion

from high to low . If PWRMODE bit 2 (FAL LIE) is one,

this will cause PW RIR Q t o go h igh as we ll . Th is bit is

reset by one of the foll owing:

- MCR

- any write to PEST

- a write to ST ATUS with bit 3 set to one . This will hol d

the bit reset until released by a write to STATUS with

bit 3 cle a re d to z ero.

Note that FALLIE does not mask this bit, allowing

polling to be per form e d.

Bit 1 - RISEIRQ (read only )

This bit is set when the

PWRDN pi n make s a transit ion

from low to high. If PWRMODE bit 1 (RISEIE) is one,

this will cause PW RIR Q t o go h igh as we ll . Th is bit is

reset by one of the foll owing:

- MCR

- any write to PEST

- a writ e t o S TATUS with bit 3 set to o n e. This will

hold the bit rese t until release d by a writ e to STA TU S

with bi t 3 c le a re d to zero.

Note that RISEIE does not mask this bit, allowing

polling to be per form e d.

Bit 0 - Soft Power (SOFTPWR)

The function of this bit depends on the status of the

“SWMODE” bit (bit 0 of PWRMODE). When

SWMODE is zero, writes to this bit have no affect.

Reads will ret urn t he state of th e PWR DN* pi n, whic h

is also the state of the on chip PWRON control signal.

When SWMODE is a one , a write of one to this bit turns

on power to the c hip analog circ uitry , while a zero clears

this bit and puts the chip in a low power mode. Reads

will return t he last va lue wri tt en .

IR91 Power Mode (PWRMO DE)

All bits in this re gist er are c lea re d by MCR.

Bits 7:3 - rese rve d

Bit 2 - Fa ll IR Q Enable (FALLIE )

When set to one, this bit allows a falling edge on

PWRDN to cause PW RIRQ to go high. It does not mask

PEST bit 2.

Bit 1 - Rise IRQ Enable (RISEIE)

When set to one, this bit allows a rising edge on

PWRDN to cause PW RIRQ to go high. It does not mask

PEST bit 1.

Bit 0 - Software Mode (SWMODE)

When cleared to zero, this bit causes the chip to operate

in a “hardware driven” mode; that is, the

PWRDN pin

directly controls the chip anal og power (for low powe r

consumption ). In this mod e, a lo w on

PWRDN put s the

chip in low power mode, while a high enables normal

operat ion . W he n se t t o a on e, this bit ca use s t he ch ip to

operate in a “software driven” mode. In this mode,

changes on the

PWRDN pin only generate interrupts.

The hardware low power mode is then controlled (via

software) by SOFTPWR (b it 0 of PEST). This function

allows “clean” software controlled turn on and off of

the analog circuitry power.

ICS2002

15

IR92 reserved

IR93 reserved

IR94 DSP Control/Status (DSPCS)

Bits 7:4 - Index Cou nter Value (Read Onl y)

This value indicates the current contents of the DSP

address Inde x Counter , and is pr ovide d as a code debu g

aid for use in Step Mode . In norm al opera tion it should

be ignored. It is reset to zero when the DSP is not

runn ing, and increme nts by on e at the comp letion of

each “pass” of the DSP engine.

Bit 3 - DSP Se que nc e Com pl et e (Re ad only )

This bit is se t each tim e the DS P c omplete s its seque nce

and restarts. It is reset to zero when the DSPRUN bit is

zero or after a read of thi s reg ister .

Bit 2 - DSP Output Saturation Detect

This bit is set to one whenever the DSP output value

written to any output destination (DATA RAM, DAC,

or Record FIFO) exc eeds a sixtee n b it sign ed range . I n

these cases, the DSP output satura tes to $7FFF or $8000

(for positive or negative values) rather than overflowing. It is reset to zero when the DSPRUN bit is zero or

after a re ad of this register .

Bit 1 - DSP Step Mode

This bit is intended as a DSP code debug aid only.

When set to a one, t his bit halt s the DSP microco de

sequencer at the end of each “pass” of code. This

enables the host to read the DATA RAM contents to

check the resul ts of the pre vious cal culations. Note th at

writes to the Record FIFO and DAC will be captured

by t he DATA RAM “under ” th em to a id wit h deb ug

efforts. For normal operation, this bit MUST be set to

a zero.

Bit 0 - DSP Run

When written to one, this bit starts the DSP engine

running. A zero stops and resets the DSP en gine exe cution. This bi t is rese t by MCR.

Before running the DSP, the Code and Data RAMs must be

loaded. T o do this, perf orm the foll ow i ng:

1) wri te 95h (DSPR A) to the desire d addre s s

2) wri te 96h (Code Ram da ta) or 97h (Data RAM da ta ) t o the

desired 16 -bi t va lu e.

3) repe a t 1 and 2 for all RAM location s of both RAM s.

4) when done, write any data to DSPRA to reset the load logic.

ICS will provide algorithm and constants data supporting filtering func ti ons for va ri ous sam pl e rate s.

Note that when the DSP is running, it is forbidden to read or

write either the Code or Data RAMs (except when halted in

STEP mode, see above ). Also , afte r writing to the Code or Data

RAMs to load them, and before starting the DSP, you must reset

the RAM load hardware by writing to the DSPRA register (the

value wri tte n is ign ore d).

IR95 DSP RAM Address Latch (DSPRA) (writ e onl y)

Bit 7 - Rea d

When one, this b it in dic ates t hat the next DSP RAM

operat ion is a rea d. Zero i ndi ca t es a writ e op er at io n.

Bits 5:0 - DSP RAM Add re ss

These bits are the addre s s for the nex t DSP RAM data

transfer. Note that the Code RAM address can be $00

through $3f, and the Data RAM address can be $00

through $1F.

IR96 Code RAM Data Port (8/16-b it)

Bits B:0 - Code RAM Data

This 8/16 -bi t p ort is d at a to be re a d f rom /wr it te n to t he

DSP Code RAM. T he data i s the low 12 bits of the wo rd.

IR97 Data RAM Data Port (8/16-bit)

Bits F:0 - Data RAM Da ta

This 8/16 -bi t p ort is the data to be rea d fr om/writte n to

the DSP Da t a RAM. The data is a full 16-bit word.

Record DMA Control and Status Registers

IR98 Record DMA Control (DMACTL)

Bits 7 - re se r v ed

Bit 6 - TC Re set Mask

When set to 1, t his bit masks the ‘DMA Run’ bit res et

upon recei pt of TC, term inal count , signal from th e ISA

bus. When reset to 0, the ‘DMA Run’ bit will be reset

upon receipt of TC.

Bits 5:1 - rese rve d

Bit 0 - DMA R un

This bit enables the DMA hardware to begin transfer-

ring data when set to one. It is cleared by either MCR

or receipt of a TC whe n ‘T C R ese t Ma sk’ is a zero (see

the DMAMODE register for detai ls).

ICS2002

16

IR99 Record DMA Burst Count (RDMABC)

Bits 7:6 - rese rve d

Bits 5:0 - Record DMA Burst Count

This value determines the number of DMA transfers

that take pla ce for each DMA r equest issued to the host.

The actual number of transfe rs will be RDMABC + 1.

Thus, for single transfe r mode , program this registe r to

zero . The b urst c ounte r is automat icall y pres et to the

burst c ou nt w he ne ve r the

DACKR input is hig h. Thus,

there is no need t o reprogram the count value aft er TC,

since the next transfer will use the full programmed

count value. This register has no affect on I/O Mode

data tra nsfers, sinc e its only influen ce is ove r the DR QR

output. This register is not initialized by any means

other than a direct write, and hence must be written to

before DMA is enabled.

IR9A Record DMA Mode (RDMAMODE)

All bits in this re gist er are c lea re d by MCR.

Bits 7:6 - rese rve d

Bit 5 - T e rm inal Count Inter rupt (RTCIRQ) (read on ly)

This bit indicates that a Terminal Count has been received on the la st DMA ope rati on. If the RECIE bit has

been programmed to a one, an interrupt will be generated at the end of the last DMA operation. This bit is

cleared by MCR or a write to STATUS with bit 1 = 1.

The reset state is then removed by either writing the

STATUS bi t 0 to 0, or by the next DMA operation.

Hence, there is no need to “remove” this reset as there

is for other IRQ reset operations.

Bit 4 - Record I/O Mode T r an sfer (RIOXFE R)

When thi s bi t is a one , the D MA hardware (D R QR an d

R TCIRQ) is disabled. Da ta transfers take pla ce via RA

$8B (NOT $9B), and a re re quired t o be t reated as 16-bit

transfers. Thus, data should be read from DLW (with

SBHE = 0, 16-bit data) or from DLW (with SBHE = 1,

8-bit data low byte) followed by DH (8-bit data, high

byte). It is also the programmers responsibility to ensure that RDMAMODE b it 1 (RD MA16 ) is set t o a o ne

for all I/O mode transfers.

Bit 3 - Unsigned Data (RUSIGN)

When set to a one, the record FIFO will generate

unsigned da ta. T he na tive data form at is Signe d Binar y

T wos Complement . This bit will invert the most significant bit of ea ch data by te (or wo rd, dep end in g on th e

state of RDATATYPE).

Bit 2 - 16-Bit DMA (RDMA16)

When set to a one, this bit ca uses the hardware to expect

data to be sent in 16-bit words. When low , the hardware

expects 8-bit bytes. This bit must be set to one when

performing I/O mode transfers, as all I/O transfers are

treated as 16-bit entities.

Bits 1:0 - Record Data Type (RDATATYPE)

These bits direct the hardware how to interpret the

incoming data. Note that this is independent of the

DMA or I/O dat a width. It ef fe cts how dat a is “signe d”

and how data is packed to/unpacked from the Record

FIFO.

Value Data Type

00 8-bit linear

01 16-bit linear

10 reserved

11 reserved

IR9B reserved

Record FIFO Control/Status Registers

IR9C Record FIFO Enable/Status (RFES)

Bit 0 - Record FIFO Enable (RFE)

This bit hol ds the record FIFO in a rese t sta te whe n low ,

and enables the FIFO to opera te whe n high. This bit is

reset by M CR. This bit, when low, also resets al l FIFO

related condi tions (se e the follo wing bits) and pr even ts

DMA st ar t requ est s f rom be in g i ssued. I t doe s not re set

the Record FIFO IRQ Mode regist er.

Bit 1 - FIFO Overflow (read only)

This bit is set when a FIFO shi ft in com mand is g en erated (by either DMA, I/O, or the DSP) with the FIFO

full, an d indic ates a n error condit ion. T his b it will cause

the FOUIRQ bit to go active, generating an IRQ if

enabled. This bit is reset by writing to ST ATUS with bit

4 = 1, and re-e nabled by wr i ti ng t o S TATUS with bit 4

= 0. FE low also rese ts thi s bit .

Bit 2 - FIFO Underflow (read on ly)

This bit is set when a FIFO shift out command is

generated (by either DMA, I/O, or the DSP) with the

FIFO empty, and indicates an error condition. This bit

will cause the FOUIRQ bit to go active, generating an

IRQ if enabled . Thi s bit is re se t by writ ing to STATUS

with bit 4 = 1, and re-enabled by writing to STATUS

with bit 4 = 0. FE low also re sets this bit.

ICS2002

17

Bit 3 - FIFO 25% Full (read only)

This bit goe s high afte r 4 wo rds (o r 8 byt es) ha ve be e n

loaded into the FI FO, and l ow ag ain whe n 5 words (or

10 bytes) may be loaded into the FIFO. There is no

interrupt associ a te d wit h this bit direc t ly.

Bit 4 - FIFO 50% Full (read only)

This bit goe s high after 8 wo rds (or 16 bytes) ha ve been

loaded into the FI FO, and l ow ag ain whe n 9 words (or

18 bytes) may be loaded into the FIFO. There is no

interrupt associ a te d wit h this bit direc t ly.

Bit 5 - FIFO 75% Full (read only)

This bit goes high after 12 words (or 24 bytes) have

been loaded into the FIFO, and low again when 13

words (or 26 bytes) may be loaded i nto the FIFO. There

is no interrupt assoc iate d wi th this bi t dire ct ly.

Bit 6 - FIFO DIR (read only)

This bit goes high when a single word (or two bytes)

may be written to the FIFO. There is no interrupt

associate d with this bi t dire ctly. Note that this b it rese ts

to a one because when the FIFO is reset it is forced to

be “empty,” and hence is ready to accept data.

Bit 7 - FIFO DOR (read only)

This bit goes high when a single word (or two bytes)

may be read from the FIFO. There is no interrupt

associated with this bit directly.

IR9D Record FIFO IRQ Mode

Bits 7:4 - rese rve d

Bit 3 - FIFO IRQ Enable (RFIE)

This bit enables the various FIFO capacity thresholds

to generate interrupts (as RECIRQ) when one. When

zero, this bit prevents FIFO capacity IRQ generation

when operating in DMA mode, which only needs

RTCIRQ.

Bits 2:0 - FIFO Ready IRQ Mode Selection

This register defines FIFO utilization for both DMA

and I/O mode data transfers. In I/O mode, it is used to

generate in terru pts (R ECIRQ) wh en the FIFO ca pac ity

reaches a predefined point. For DMA transfers, it signals the DMA logic to request a transfer at those same

predefined points. By programming the Record DMA

Burst Count appropr iately , the FIFO m ay be easily kept

near the de sire d ca pacity.

The following table describes the selections available:

Bits

2:0 Source Notes

000 DIR Ready to take 1 word from DSP

001 EMPTY 75% Read y to take 13 words from DSP

010 EMPTY 50% Ready to take 9 words from DSP

011 EMPTY 25% Ready to take 5 words from DSP

100 DOR Ready to provide 1 word to HOST

101 FUL L 25% Ready to provi de 4 words t o HOST

110 FULL 50% Ready to provi de 8 words to HOST

11 1 FULL 75% Ready to provide 12 words

Note that for byte transfers (RDMA16=0), the numbers listed

above should be doubled.

This must be programmed before the FIFO is enabled. It may

be changed while t he FIFO is enabled if necessary . This regi ster

is cleared by MCR, but not by RFE low.

IR9E reserved

IR9F reserved

Miscellaneous Registers

IRA0 Digit al Master Volume

Bits 7: 0 - Vol um e

This val ue is used to scale a ll value s that ar e output from

the DSP to the DAC. It may be written while the DSP

is running.

The value written is interpreted as to give a log scale

output response of 0.1875dB per step. The value for

nominal (0dB atte nuation) is E0h. A value of FFh gives

5.8125dB of ga in . Note tha t a ny va lu e abov e E0h m a y

result in digital saturation of the internal 16 bit data

value.

ICS2002

18

IRA1 DAC De-glitcher Control

Bits 7:3 - V olume bits 7:3 (read only)

Bit 2 - DAC Enable Bi t (rea d onl y, for test)

Bits 1:0 - DAC De-gl itch Width

Code Notes

00 De-glitcher disabled

01 Minimum de-glitch width

10 Nominal de-glitch width

11 Maximum de-glit ch width

This val ue is de te rm i ne d by th e cl ock rate at wh ic h t he

chip is run. ICS will provide the proper value for an

applica tion. This reg ister is also use d for test purposes.

This registe r is not initialized in any wa y and should be

programmed before muting is removed.

IRA2 reserved

IRA3 reserved

ADC and Analog Contro l Reg ist e rs

IRA4 ADC Control

Bits 7:3 - rese rve d

Bit 2 - ADC Test Mode

This bit is f or fac tory testi ng use o nly, and must alwa ys

be programmed to zero by an application. It is reset to

zero by a z ero in ADCRUN, and hence t akes two writes

of $05 to this regi st e r to ac tivate for safe ty.

Bit 1 - rese r ved

Bit 0 - ADC Run

When written to a one, this bit enables the ADC hard-

ware to run. No te that t he ADC Tim ing C ontrol registe r

should be programmed appropriately first. Also note

that the DSP must be running (and programmed prop-

erly) for the conversion results to be retrieved. The

Samp le Rat e Ge nera to r det erm ines t he r ate at wh ich the

conversion da ta is load ed into the Rec ord FIFO.

This bit is cle a re d to ze ro by M CR .

Note that this bit, when 0, shuts down the successive

approximation logic, the dynamic comparators and

various logic functions. When the ADC is not being

used, disabling it via this bit reduces background noise

in the playback section and power consumption, and

thus is recommended.

IRA5 Anal og Volume/Mute

Bits 7:5 - rese rve d

Bits 4:1 - Analog Volume

These bits set the analog output level, in 1.5dB steps.

All bits one gives 0dB attenuation of the DAC output

signal, an d all bits ze ro gives f ull attenua tion. These bits

are unaffected by any reset mechanism.

Bit 0 - Audio Enabl e

This bit disconnects the audio output of the output

buffer amp and sets the BUFOUT pin to the nominal

bias voltage when cleared to zero. When set to one, it

passes the output of the output buffer amp to the

BUFOUT pin.

The main function of this bit is to prevent sudden DC

offset ch an ge s on t he BUFOUT pin wh en e nteri ng and

leaving powe r -do wn mode. By proper softwa re proc edure, noisel ess tr ansi tions c an be made .

This bit is cle a re d to ze ro by M CR .

IRA6 ADC Timing Control

This registe r is use d to cont rol the ADC inter nal ope ration timing.

Bits 7:4 - Com pa ra tor Ti ming Control

These bit s co ntrol the t ime of c ompa rator in put switch ing. Bits 7:5 are the count, and bit 4 is 0 for half cycle

and 1 full cycle delays.

Bits 3:1 - Cycle Timing Cont rol

These b its co ntr ol t he nu mber o f c locks us ed for each

step of the successive approximation process. For the

full 64 step DSP cycle, the value of these bits should be

7. For a 40 step c y cle, the value should be 4.

Bit 0 - rese r ved

ICS2002

19

W

O

W

T

.029 ± .003

W

O

W

T

.050 ± .002

PIN 1 IDENT.

.070 DIA X .025 DP.

.045 X 45 DEG

CORNER CHAMFER

W

B

W

B

.030 ± .005

.035 ± .005

.029 ± .005

.035

R TYP

7 ± 2 DEG

.020 MIN

.015 REF

.010 MIN

.006 MIN

7 ± 2 DEG

W

C

T

P

T

F

.045 X 45 DEG

CORNER CHAMFER

44-Pin PLCC Package

LEAD COUNT

FRAME

THICKNESS

TF

+/-.003

PKG.

THICKNESS

TP

+/-.004

PKG. WIDTH

TOP

WT

+/-.004

PKG. WIDTH

BOTTOM

WB

+/-.066

OVERALL

PKG. WIDTH

WO

+/-.005

CONTACT

WIDTH

WO

+.010/-.030

44L 0.010 0.152 0.650 0.623 0.690 0.620

Ordering Information

ICS2002V

Example:

ICS XXXX M

Package Type

V=PLCC

Device Type (consists of 3 or 4 digit numbe rs)

Prefix

ICS, AV=Standard Device; GSP=Genlock Device

ICS2002

20

LEAD COUNT 44L

BODY THICKNESS 1.00

FOOTPRINT (BODY+) 2.00

DIMENSIONS TOLERANCE

A MAX. 1.20

A

1

0.05 MIN./0.10 MAX.

A

2

±0.5 1.00

D ±0.25 12.00

D

1

±0.10 10.00

E ±0.25 12.00

E

1

±0.10 10.00

L ±0.15/-0.10 0.60

e BASIC 0.80

b +0.05 0.35

ccc MAX. 0.10

ddd 0.20 MAX.

0 0° - 7°

Ordering Information

ICS2002Y

Example:

ICS XXXX M

Package Type

Y=QFP

Device Type (consists of 3 or 4 digit numbe rs)

Prefix

ICS, AV=Standard Device; GSP=Genlock Device

TQFP Package

ICS2002

21

Loading...

Loading...