ICST AV1660N, AV1660M, ICS1660M Datasheet

Integrated

Circuit

Systems, Inc.

ICS1660

Incoming Call Line Identification (ICLID) Receiver

with R ing D etec tion

Features

•• Ring Dete c tio n

•• Low Battery Detection

•• Internal 5V Regulator - can externally source 25mA

•• FSK Demodulat ion

•• Power-down in Standby Mode

•• Direct Interfac e to Host Micropr oc essor or

Microcomputer

Applications

•• Telephones

•• Facsimile Ma chines

•• Modems

•• Telephon e Interface Equipm e nt

•• Stand-a lon e ICLI D produ ct s

Description

The ICS1660 “ICLID” circuit is a monolithic CMOS VLSI

device that decodes and detects the

Frequency Shift Keying

(FSK) signals used in caller identification telephone service.

The ICS1660, when used in conjunction with some external

components, amplifies, filters and demodulates the FSK

data transmitted from the central office to the telephone

subscriber .

The ICS1660 detects the first power ring signal and demodulates the 1200 baud FSK data transmitted during the silent

interval between the first and second powe r ring. The FSK data

is transmitted from the central office switch to the subscriber

line as part of the CLASS se rvi ce of

Calling Number Delivery

(CND). This data is then demodulated, amplified and filtered

by the ICS1660 and digitally transmitted to the host controller/processor.

The ICS1660 is designed to be powered by any off-the-shelf

9.0 volt battery. Th e on-ch ip 5.0 vol ta ge regula t or powe rs the

host microprocessor and any external circuitry supported by

the ICS1660. This portion of th e circuit ca n be overri dden by

connecti ng the V

IN

pin (18) to the VDD pin (1) for a common

power supply. A low ba t te ry d ete ct ion c ircui t is al so pr ovi de d

on-chip and signals the microprocessor on the FSK/BAT pin

(17) when the PW R pin (16) i nput is pulle d lo w.

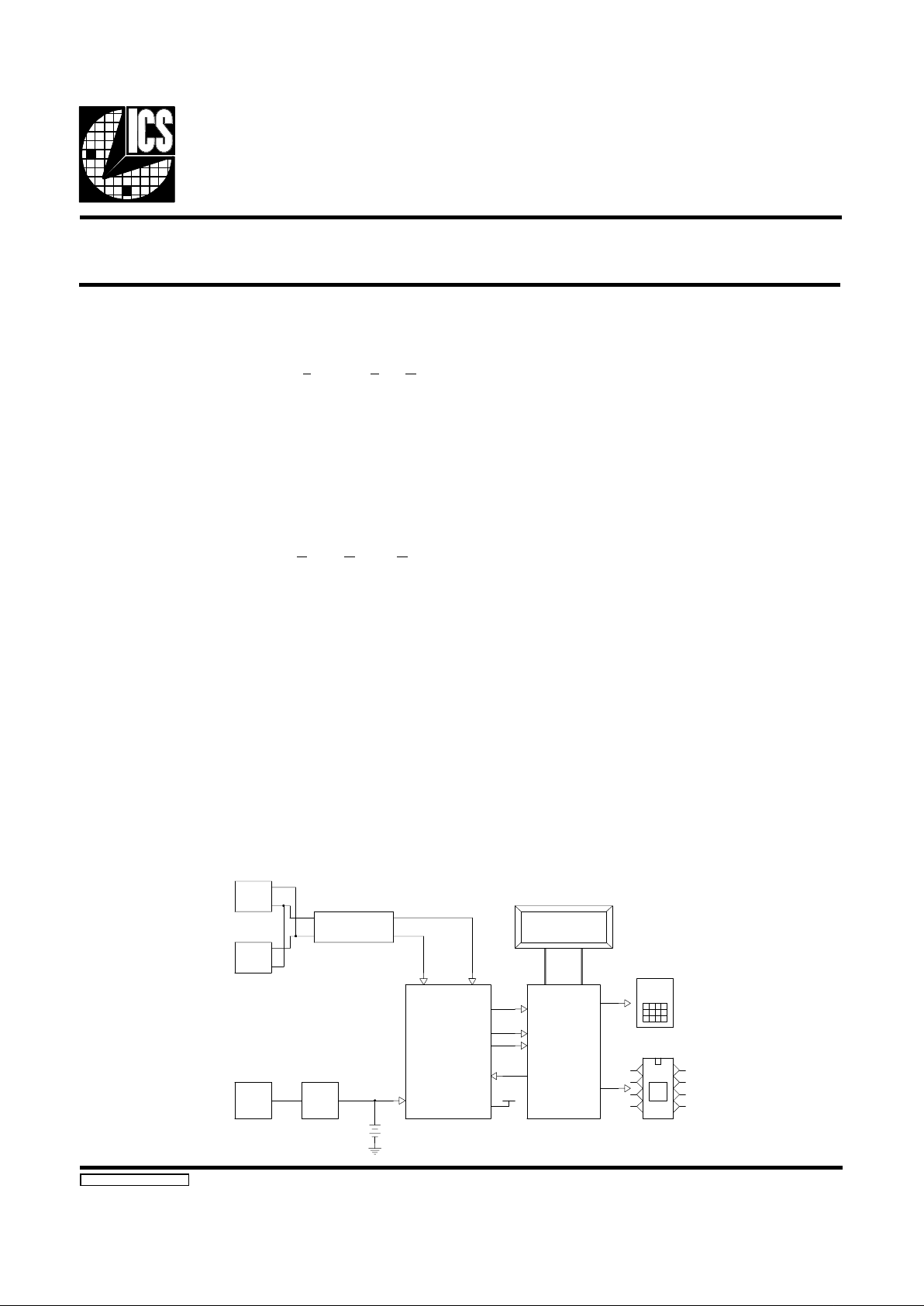

TO LINE

TO PHONE

Surge and

Lightning

Protection

2 x 16 LCD

Display

AC/DC

Adapter

DC

Jack

KEYPAD

External

Memory

(RAM/EPROM)

8

Data

3

Control

ICS1660

Rng Detect

FSK Demodulation

Signal Conditioning

Low Battery Detect

Power-down

Standby

Voltage

Regulation

9VDC

+5VDC

Micro-

Controller

ICLID Block Diagram

ICS1660RevA100694

Block Diagram

.022µF

F1 F2 F3

.033µF

RING

FOUT

.0033µF

.022µF

AMPIN

VCOSET

LFILTER

POSTF

500k.01µF

1000pF

FSKBAT

MUX

PLL

LOW

BATTERY

DETECT

POST

AMP

POWER

CONTROL

REGULATOR

5 VOLT

BUFFER

RING

DETECT

DIFF

AMP

FILTER

PWR

10

µF

VIN

VDD

VSS

BUFFER

0.01

µF

0.01µF

LINE AF

LINE BF

LINE A

LINE B

82k

0.1µF

0.1µF

82k

TIP

RING

15 10 13 2

11

12

6

4

3

17

16

9

18

1

14

8

7

5

ICS1660

2

Function Description

Power Supply

The ICS1660 is desig ned to be power ed by a standard 9.0 volt

battery. The chip contains a voltage regulator that powers

extern al circ uitry and pro vides t he suppl y vol tage fo r all digital

I/O on the circuit. This allows easy interface between the

ICS1660 and othe r standa rd log ic worki ng at 5.0 V. Thi s regu lator has short circuit protection and requires an external filter/compe nsat io n capa c itor with a minimum val ue of 10uf.

In the event that an external regulated 5.0V supply is available,

the V

IN

and VDD pins can be shorte d to permit the entire system

to work from a common supply .

A low battery detection circuit is provided. This circuit is

designed for a typical tri p point of 6.0 V with hysteresi s of about

200mV above the trip point. This signal is low active and is

multiplexed to the FSKBAT output pin when the PWR input is

low.

In an effort to keep powe r dissipati on to a minimum and ext end

batte ry life , most of the an alog c ircui ts are tu rned off when the

circuit is at rest waiting for a ring detect, (PWR pin low).

During this time only the regulator, low battery detect, reference generator, and ring detect circuits are active. When the

PWR pin is high, all circuits are active.

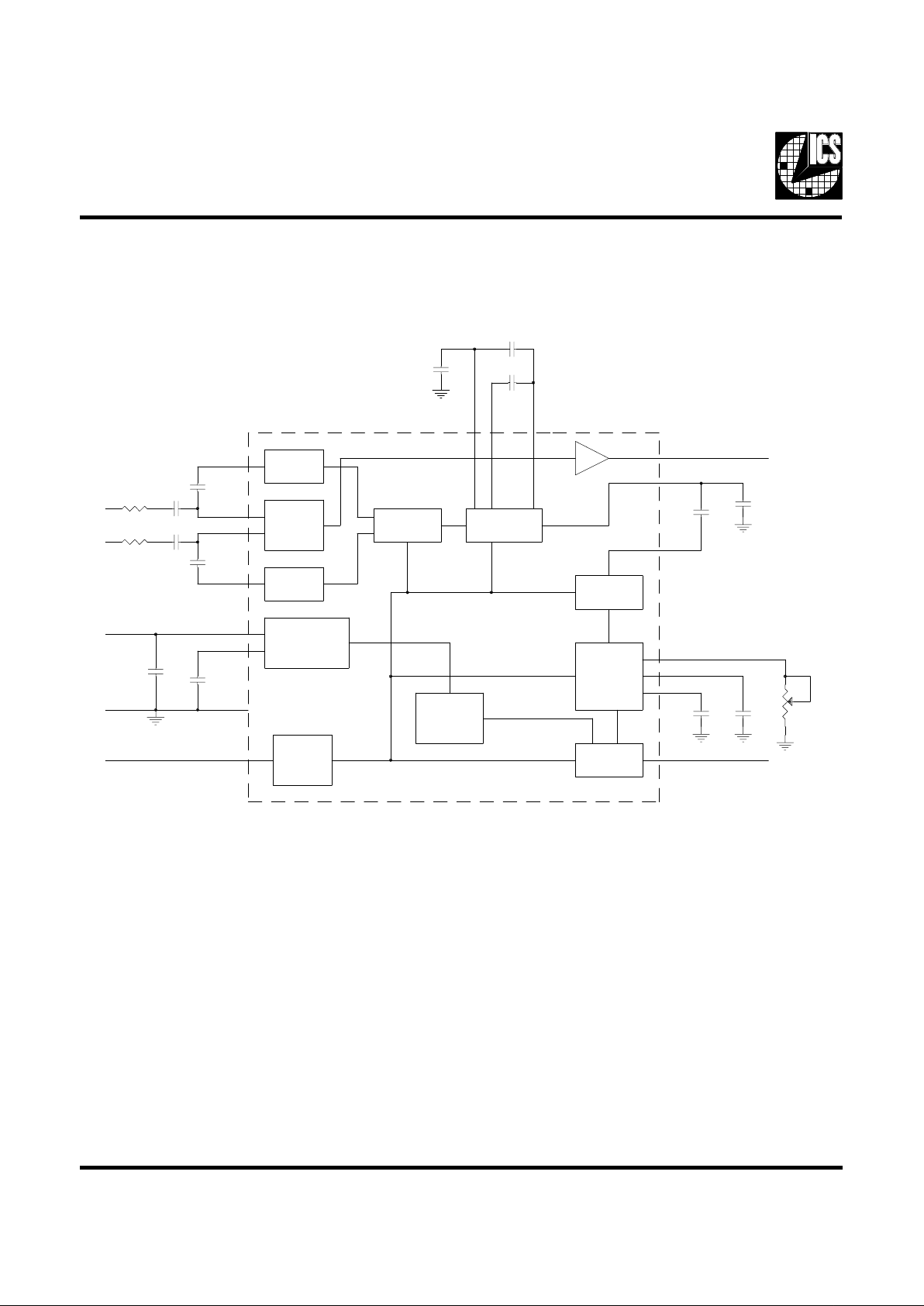

Ring Detect

As shown in the attached block diagram, the LINEA and

LINEB inputs should be connected to the telephone line

through external 82kΩ resistors and 0.1uf capacitors. This

provides DC i sola t ion an d set s up a voltage di vid er wit h i nt er nal resistors t hat will detec t 35.0V RMS typica lly. This vol tage

is applied across the LINEA and LINEB inputs. The design

value of the internal resistors is 8.1KΩ ± 20% with relative

accuracy of 2%. The RING output is high active.

Differential Front End

As shown in the attached block diagram, the LINEA and

LINEB inputs go into a differential amplifier which in turn

drives a filter. All resistors are internal to the chip while

capacitors are connec t ed as shown in the bl ock diagram. After

filtering, the signal is AC coupled into a high gain amplifier

that conv erts the signal t o digital. This di gital si gnal i n turn a cts

as the reference frequency for the phase comparator section of

the phase locked loop.

FSK Demodulation

After the signal from the telephone line has been filtered,

amplifie d a nd co nve rt ed to dig it al, it a cts as an input t o a ph ase

locked l oop. This PLL does FSK demo dulation . The summ ing

amplifier shown in the block diagram provides a signal to the

VCO that should be about 0.5V for MARK frequency

(1200 HZ), and 2.0V for SPACE fre que nc y (2 200 HZ ).

As shown in the block diagram, the LFILTER (loop filter)

output has a post filter att ached to it. This POSTF signa l is sent

to a comparator. The other side of the comparator is set to

approximately 2.5V. This comparator has a small amount

(200mV) of hysteresis and its output is the demodulated FSK

data. The FSK output is high for MARK freq uency and low for

SPACE frequency. FSK data is multiplexed out of the

FSKBAT pin when the PWR input is high.

The VCO frequency is set with one external resistor with a

value in t he range of 3 00K fo r a cent e r fre qu ency of 1700 HZ.

The lock r an ge wil l be 66 0 HZ to 2630 HZ t ypi cal . Th e ce nt e r

frequen cy reproduc i bil it y wil l be ±1 5 %. Th e c e nte r frequency

can be adjusted in the system by connecting AMPIN to VSS,

PWR to VDD, and ad justing the exter nal resist or for 17 00 HZ.

This freque nc y can be observed at the LFILTE R outp ut or the

FSK/BAT output.

ICS1660

3

Loading...

Loading...