Page 1

DUAL BAND TRANSCEIVER

S-15103XZ-C1

June 2014

Page 2

INTRODUCTION CAUTION

This service manual describes the latest technical information for the ID-5100A and ID-5100E

DUAL BAND TRANSCEIVER, at

the time of publication.

MODEL VERSION

TPE 25 W

ID-5100A

ID-5100E

USA

KOR

EXP

EUR

ITR

TX OUTPUT

POWER

50 W

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than the specifi ed voltage. This

will ruin the transceiver.

DO NOT expose the transceiver to rain, snow or liquids.

DO NOT reverse the polarities of the power supply when con-

necting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW) to

the antenna connector. This could damage the transceiver’s

front-end.

To upgrade quality, any electrical or mechanical parts

and internal circuits are subject to change without notice

or obligation.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit Icom part number

2. Component name

3. Equipment model name and unit name

4. Quantity required

<ORDER EXAMPLE>

1110003491 S.IC TA31136FNG ID-5100A MAIN UNIT 5 pieces

8820001210 Screw 2438 screw ID-5100A Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

(ID-5100A)

REPAIR NOTES

1. Make sure that the problem is internal before dis-assembling the transceiver.

2. DO NOT open the transceiver until the transceiver is dis-

connected from its power source.

3. DO NOT force any of the variable components. Turn them

slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An insulated

tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the trans-

ceiver is defective.

6. DO NOT transmit power into a Standard Signal Generator

or a Sweep Generator, otherwise the RF power may damage them.

7. ALWAYS connect a 50 dB to 60 dB attenuator between the

transceiver and a Deviation Meter or Spectrum Analyzer,

when using such test equipment.

8. READ the instructions of the test equipment thoroughly

before connecting it to the transceiver.

Icom, Icom Inc. and the Icom logo are registered trademarks of Icom Incorporated (Japan) in Japan, the United States, the

United Kingdom, Germany, France, Spain, Russia and/or other countries.

Page 3

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASSEMBLY INSTRUCTION

SECTION 4 CIRCUIT DESCRIPITON

4-1 RECEIVER CIRCUITS ...................................................................................... 4-1

4-2 TRANSMITTER CIRCUITS ............................................................................... 4-3

4-3 FREQUENCY SYNTHESIZER CIRCUITS ....................................................... 4-5

4-4 VOLTAGE BLOCK DIAGRAM ........................................................................... 4-6

4-5 PORT ALLOCATIONS ...................................................................................... 4-6

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION ................................................................................................. 5-1

5-2 FREQUENCY ADJUSTMENT .......................................................................... 5-2

5-3 TRANSMIT ADJUSTMENTS ............................................................................ 5-3

5-4 RECEIVE ADJUSTMENTS ............................................................................... 5-5

SECTION 6 PARTS LIST

SECTION 7 MECHANICAL PARTS

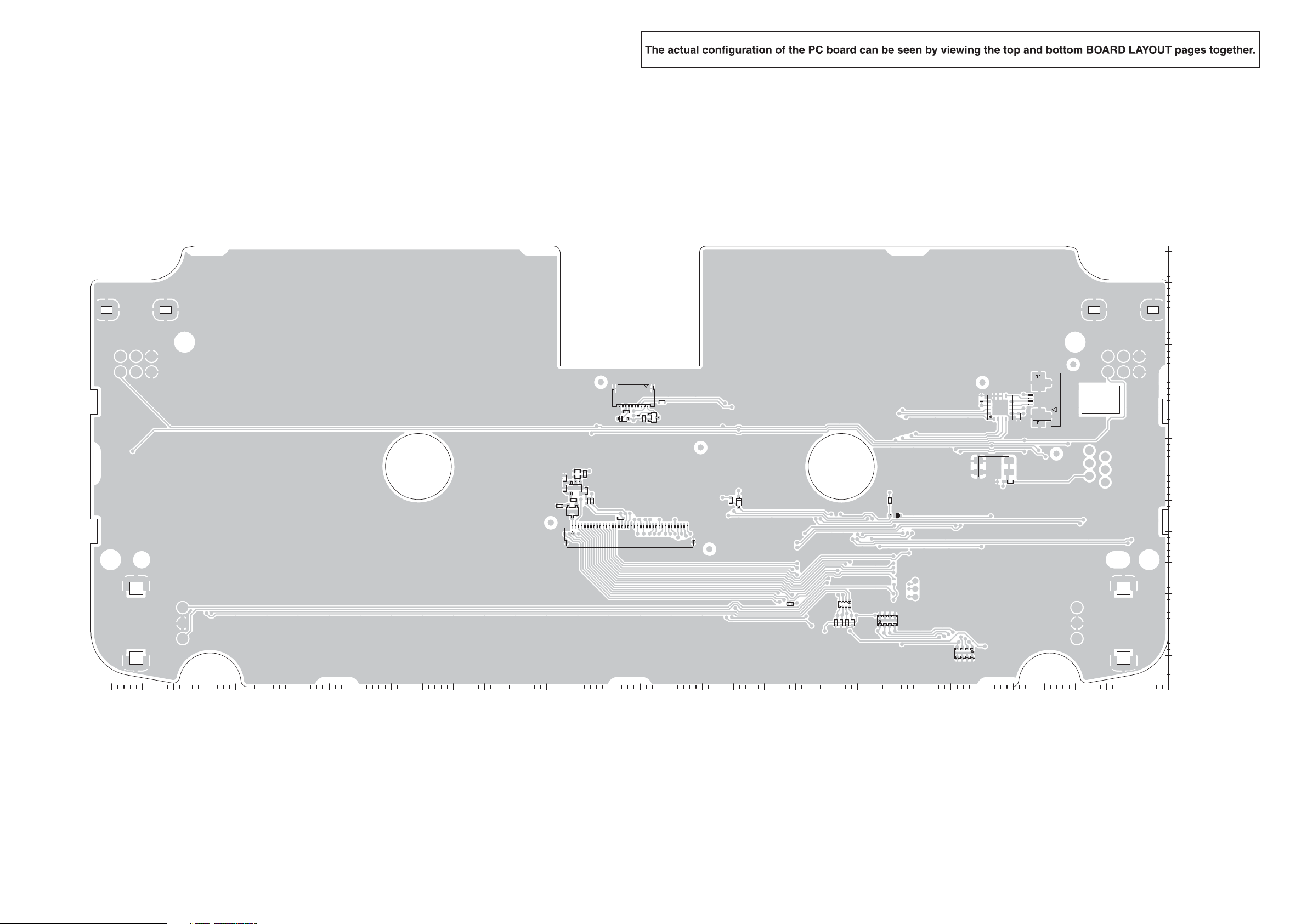

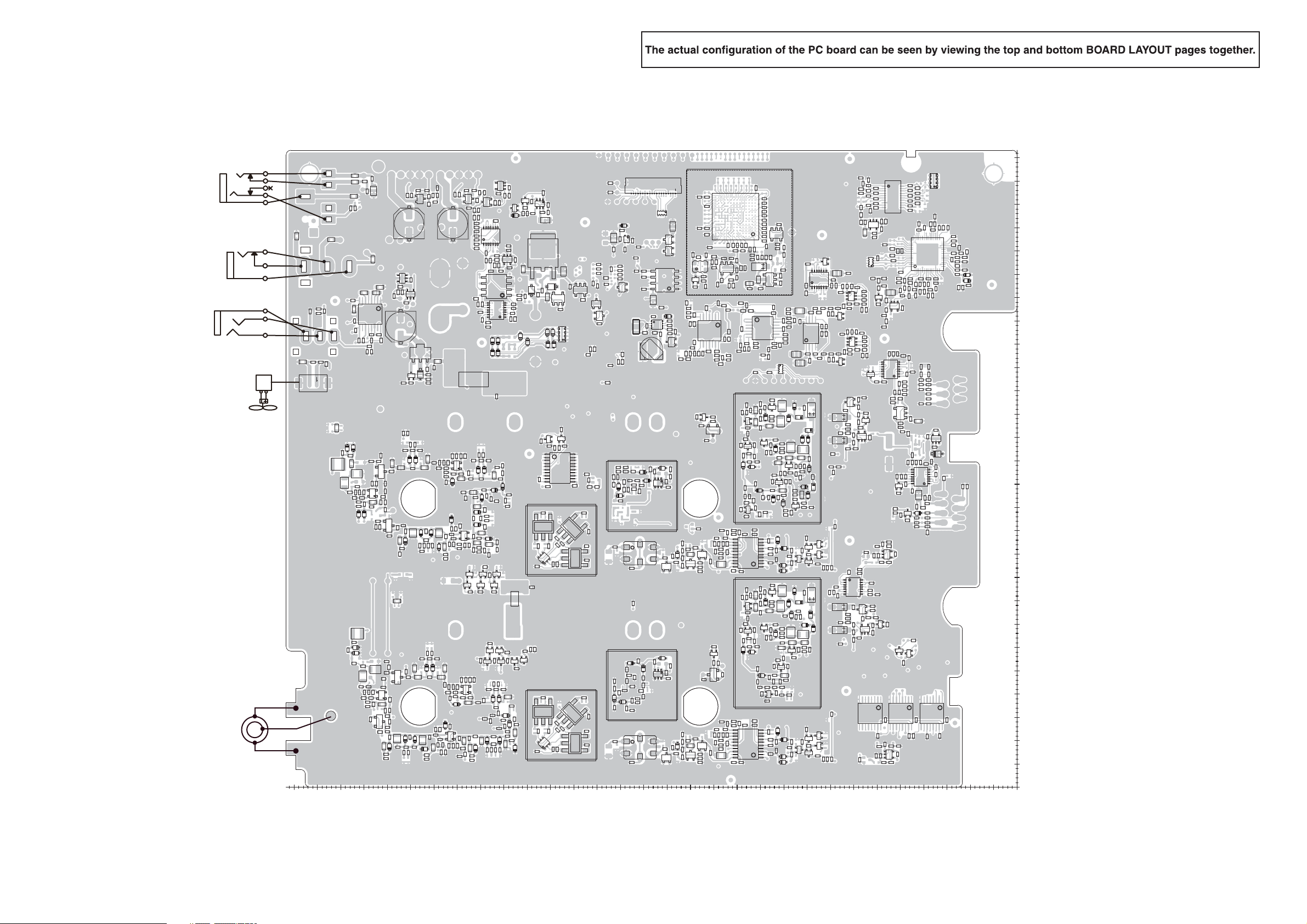

SECTION 8 BOARD LAYOUTS

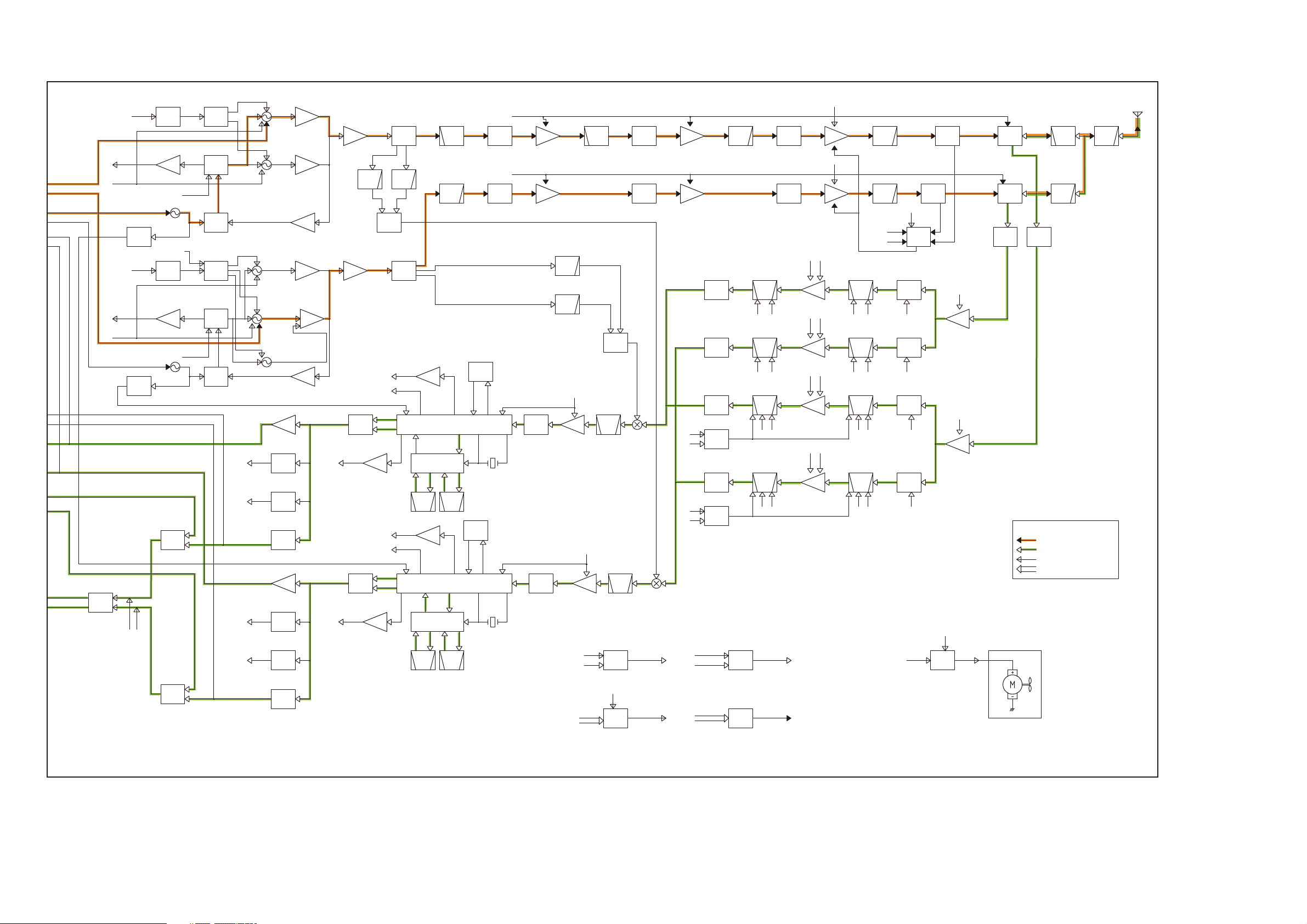

SECTION 9 BLOCK DIAGRAM

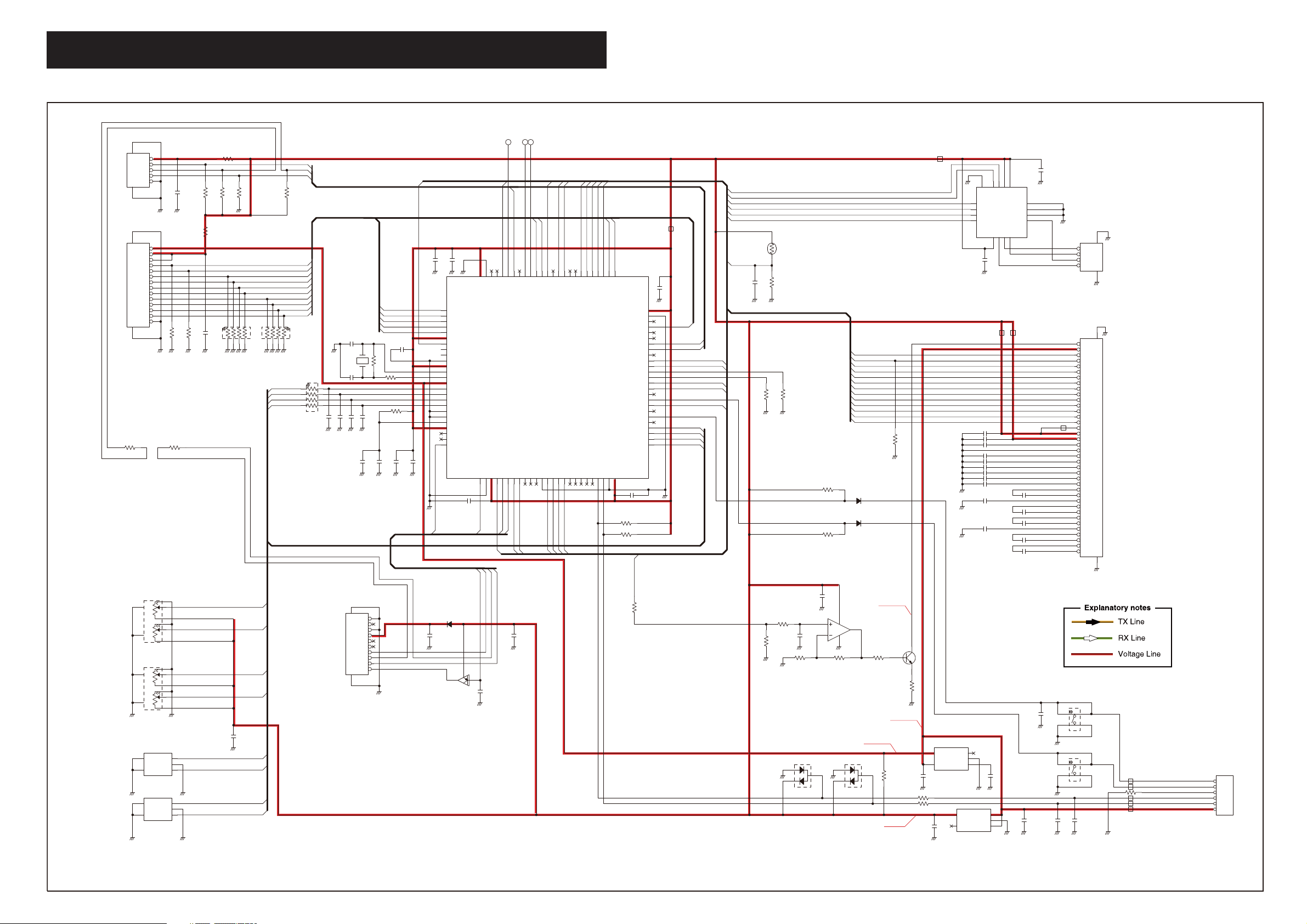

SECTION 10 VOLTAGE DIAGRAM

Page 4

SECTION 1. SPECIFICATIONS

General

■

• Frequency coverage:

EUR

ITR

TPE

USA

KOR

EXP

RX 118–174 MHz*

TX 144–146 MHz, 430–440 MHz

RX 118–136.99166 MHz*

TX 144–146 MHz, 430–434 MHz, 435–438 MHz

RX 144–146 MHz, 430–432 MHz

TX 144–146 MHz, 430–432 MHz

RX 118–174 MHz*

TX 144–148 MHz, 430–450 MHz*

RX 144–146 MHz, 430–440 MHz

TX 144–146 MHz, 430–440 MHz

RX 118–174 MHz*

TX 137–174 MHz*4, 400–470 MHz*

1

, 375–550 MHz*

3

, 144–146 MHz, 430–434 MHz, 435–438 MHz

4

, 375–550 MHz*

4

, 375–550 MHz*

2

5

5

2

2

*1 Guaranteed only 144–146 MHz, *2 Guaranteed only 430–440 MHz,

*4 Guaranteed only 144–148 MHz, *5 Guaranteed only 440–450 MHz

*3 Not guaranteed,

• Mode: F2D/F3E (FM/FM-N), F7W (DV), A3E (AM/AM-N) RX only

• Number of memory channels: 1000 channels

• Number of program scan channels: 25 channels

(2 edge frequencies in each channel)

• Number of call channels: 4 channels (2 channels × 2 bands)

• Antenna connector: SO-239

• Antenna impedance: 50 ø

• Usable temperature range: –10˚C to +60˚C; +14˚F to +140˚F

• Frequency stability: ±2.5 ppm (–10˚C to +60˚C; +14˚F to +140˚F)

•

Digital transmission speed

: 4.8 kbps

• Voice coding speed: 2.4 kbps

• Frequency resolution: 5 kHz, 6.25 kHz, 8.33 kHz, 10 kHz, 12.5 kHz, 15 kHz, 20 kHz, 25 kHz, 30 kHz, 50 kHz

(The 8.33 kHz step is selectable only when the VHF air band is selected.)

• Power supply: 13.8 V DC ±15% (negative ground)

• Current drain:

Transmit

Maximum current drain: 10.5 A (TPE version)

13.0 A (Other versions)

Receive

Standby: 1.2 A

Maximum audio: 1.8 A

• Dimensions (projections not included):

Main unit: 150(W) 40(H) 172.6(D) mm; 5.9(W) 1.6(H) 6.8(D) inch

Controller:

182.2(W) 24.8(H) 81.5(D) mm;

7.2(W) 1.0(H) 3.2(D) inch

• Weight (approximately):

Main unit: 1.3 kg; 2.9 lb

Controller: 260 g; 9.2 oz

1-1

Page 5

Transmitter

■

• Modulation system:

FM/FM-N Variable reactance frequency modulation

DV GMSK reactance frequency modulation

• Maximum Deviation:

FM ±5.0 kHz

FM-N ±2.5 kHz

• Microphone impedance: 600 ø

• Spurious emission: –60 dBc

• Output power: High 25 W, Mid 15 W, Low 5 W (TPE version)

High 50 W, Mid 15 W, Low 5 W (Other versions)

Receiver

■

• Receive system: Double superheterodyne system

• IF frequencies:

Band A 1st IF 38.85 MHz

2nd IF 450 kHz

Band B 1st IF 46.35 MHz

2nd IF 450 kHz

• Sensitivity (except spurious points)

Amateur bands

FM/FM-N (12 dB SINAD)

0.18 µV

DV (BER 1%) 0.28 µV

Except Amateur bands

FM/FM-N (12 dB SINAD)

0.32 µV (137.000 to 159.995 MHz)

0.56 µV (160.000 to 174.000 MHz)

0.56 µV (375.000 to 399.995 MHz)

0.32 µV (400.000 to 499.995 MHz)

0.56 µV (500.000 to 550.000 MHz)

AM (10 dB S/N) 1 µV (118.000 to 136.99166 MHz)

• Squelch sensitivity: 0.13 µV (Threshold)

• Selectivity:

FM 60 dB

FM-N 55 dB

DV 50 dB

• Spurious and image rejection ratio:

60 dB

55 dB (A band UHF)

• AF output power: 2.0 W (at 10% distortion with an 8 ø load)

• AF output impedance: 8 ø

All stated specifi cations are typical and subject to change without notice or obligation.

1-2

Page 6

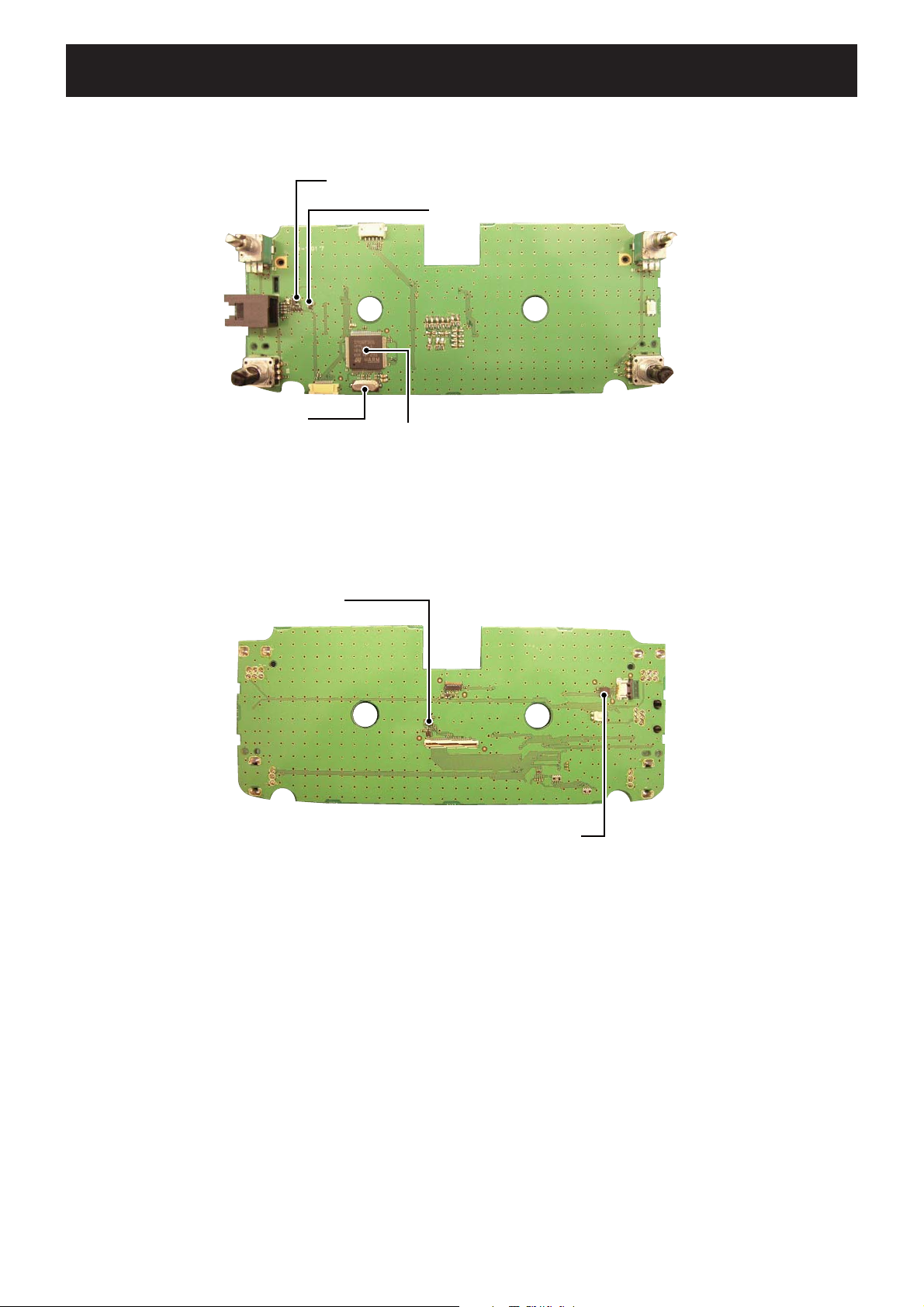

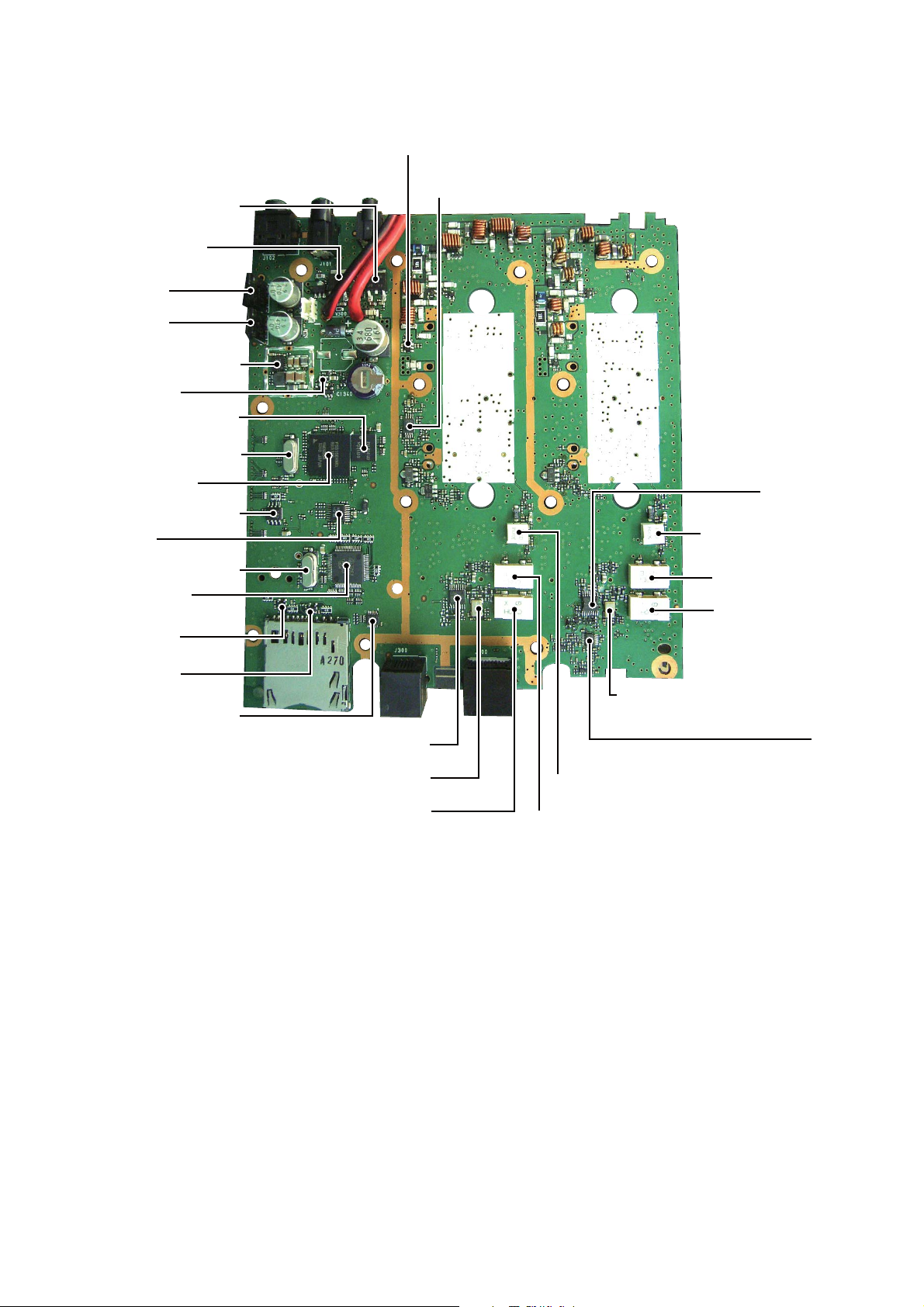

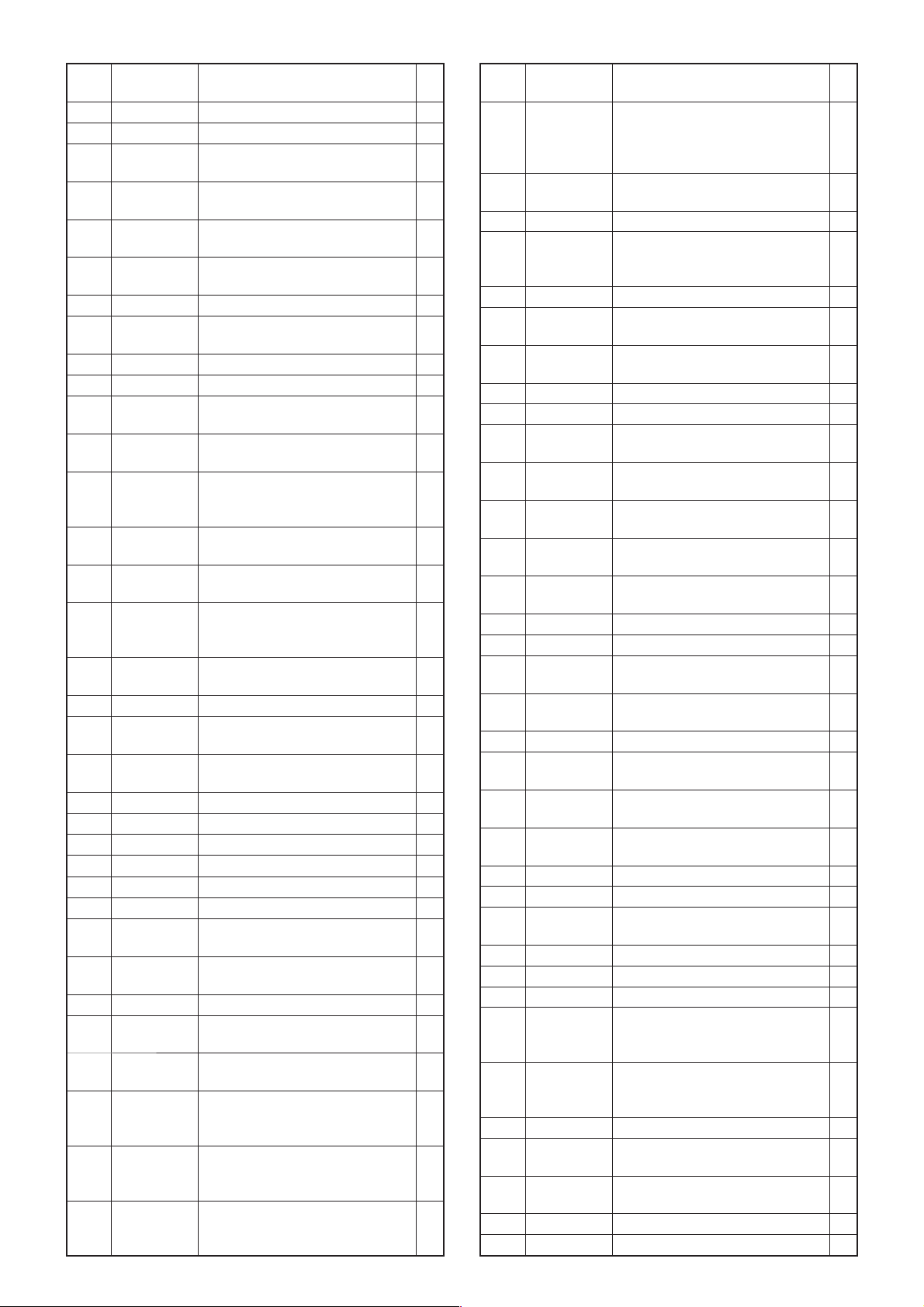

SECTION 2. INSIDE VIEWS

IC7

IC8

Q3

Q6

IC2

IC5

IC6

X1

• CONTROL UNIT

(TOP VIEW)

3.3 V REGULATOR

(IC6)

IC6

IC5

IC2

X1

RESET IC

(IC5)

C80

CPU CLOCK

(X1)

• CONTROL UNIT

(BOTTOM VIEW)

3.3 V REGULATOR

(IC7)

CONTROLLER CPU

(IC2)

Q6

IC7

Q3

TOUCH SCREEN CONTROLLER

(IC8)

IC8

2-1

Page 7

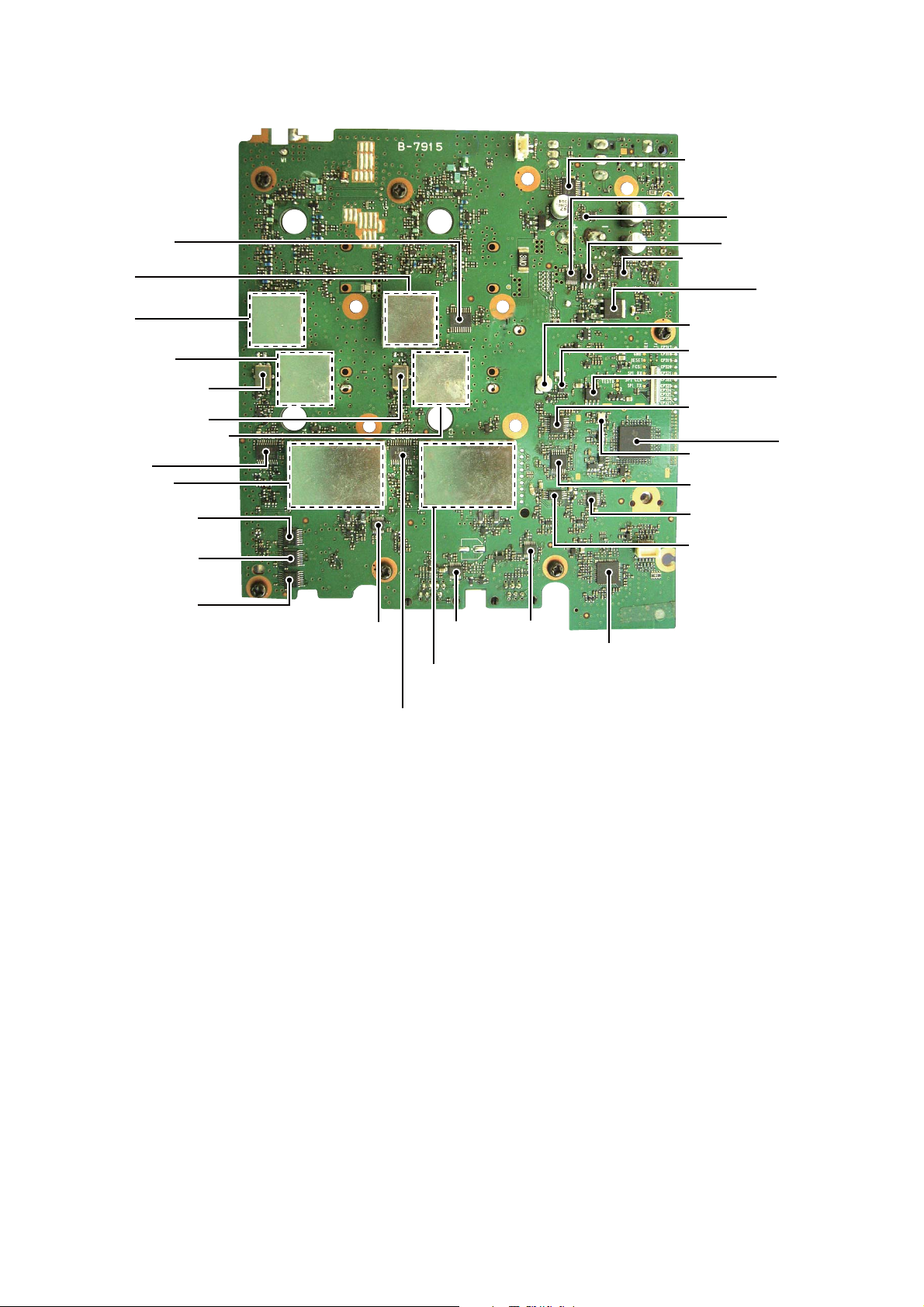

FI104

FI105

IC1

IC3

IC4

IC100

IC101

IC102

IC103

IC104

IC107

IC108

IC109

IC110

IC111

IC112

IC113

IC117

IC120

IC121

IC122

IC123

IC124

IC125

IC202

IC203

IC205

IC207

IC208

IC301

IC302

IC307

IC308

IC312

IC314

IC315

IC316

IC317

IC318

IC319

IC320

IC323

IC324

IC400

IC403

IC404

IC405

IC406

IC407

X301

X400

D/A CONVERTER

(IC1)

1ST MIXER

(Band A)

1ST MIXER

(Band B)

LO AMP & LO SW

(Band B)

1ST IF FILTER (Band B)

(FI104)

1ST IF FILTER (Band A)

(FI105)

LO AMP & LO SW

(Band A)

IF IC (Band B)

(IC120)

VCO

(Band B)

EXPANDER

(IC317)

EXPANDER

(IC316)

EXPANDER

(IC315)

• MAIN UNIT

(TOP VIEW)

IC124

FI104

IC120

IC122

IC208

IC4

IC317

IC316

IC315

IC207

AF SW

(IC205)

IC125

FI105

IC121

IC205

IC123

IF IC (Band A)

(IC121)

IC1

IC203

IC3

IC100

AF SW

(IC100)

VCO

(Band A)

IC202

IC102

IC101

IC104

AF SW

(IC104)

IC318

IC111

X301

IC302

IC407

IC406

IC117

IC112

RS232 LEVEL CONVERTER

(IC318)

AF SW

IC324

IC320

(IC111)

AF SW

IC110

IC323

IC314

IC109

IC107

IC319

IC108

IC312

(IC109)

RTC BACKUP BATTERY

(IC301)

REAL TIME CLOCK (RTC) IC

(IC302)

AF LPF & HPF

(IC407)

DSP CLOCK

(X400)

IC301

X400

IC405

IC403

IC308

IC400

IC404

AF LPF & HPF

IC113

(IC406)

AF SW

(IC113)

IC307

AF BUFFER

(IC117)

IC103

AUDIO SIGNAL PROCESSOR

(IC103)

VOLTAGE DETECTOR

(IC324)

ELECTRIC VOLUME IC

(IC110)

5 V REGULATOR

(IC319)

EEPROM

(IC301)

DSP

(IC400)

2-2

Page 8

8 V REGULATOR

(IC313)

• MAIN UNIT

(BOTTOM VIEW)

CURRENT DETECTOR

(IC310)

APC AMP

(IC2)

8 V REGULATOR

AF POWER AMP

AF POWER AMP

6 V SWITCHING REGULATOR

3.3 V REGULATOR

LINER CODEC

(IC402)

3.3 V REGULATOR

3.3 V REGULATOR

(IC321)

(IC106)

(IC105)

(IC309)

(IC311)

MAIN CPU CLOCK

MAIN CPU

(IC300)

DSP FLASH ROM

SUB CPU CLOCK

SUB CPU

(IC303)

(IC306)

(IC305)

QUAD BUS BUFFER

REFERENCE FREQUENCY OSCILLATOR (Band A)

SRAM

(IC304)

(X300)

(IC401)

(X302)

(IC200)

PLL IC (Band A)

(IC201)

(X200)

2ND IF FILTER (Band A)

(FI102)

PLL IC (Band B)

(IC206)

DISCRIMINATOR (Band A)

(X101)

2ND IF FILTER (Band A)

(FI101)

2ND IF FILTER (Band A)

(FI100)

REFERENCE FREQUENCY

OSCILLATOR (Band B)

(X201)

AF SW

(IC119)

DISCRIMINATOR (Band A)

(X102)

2ND IF FILTER (Band A)

(FI103)

2-3

Page 9

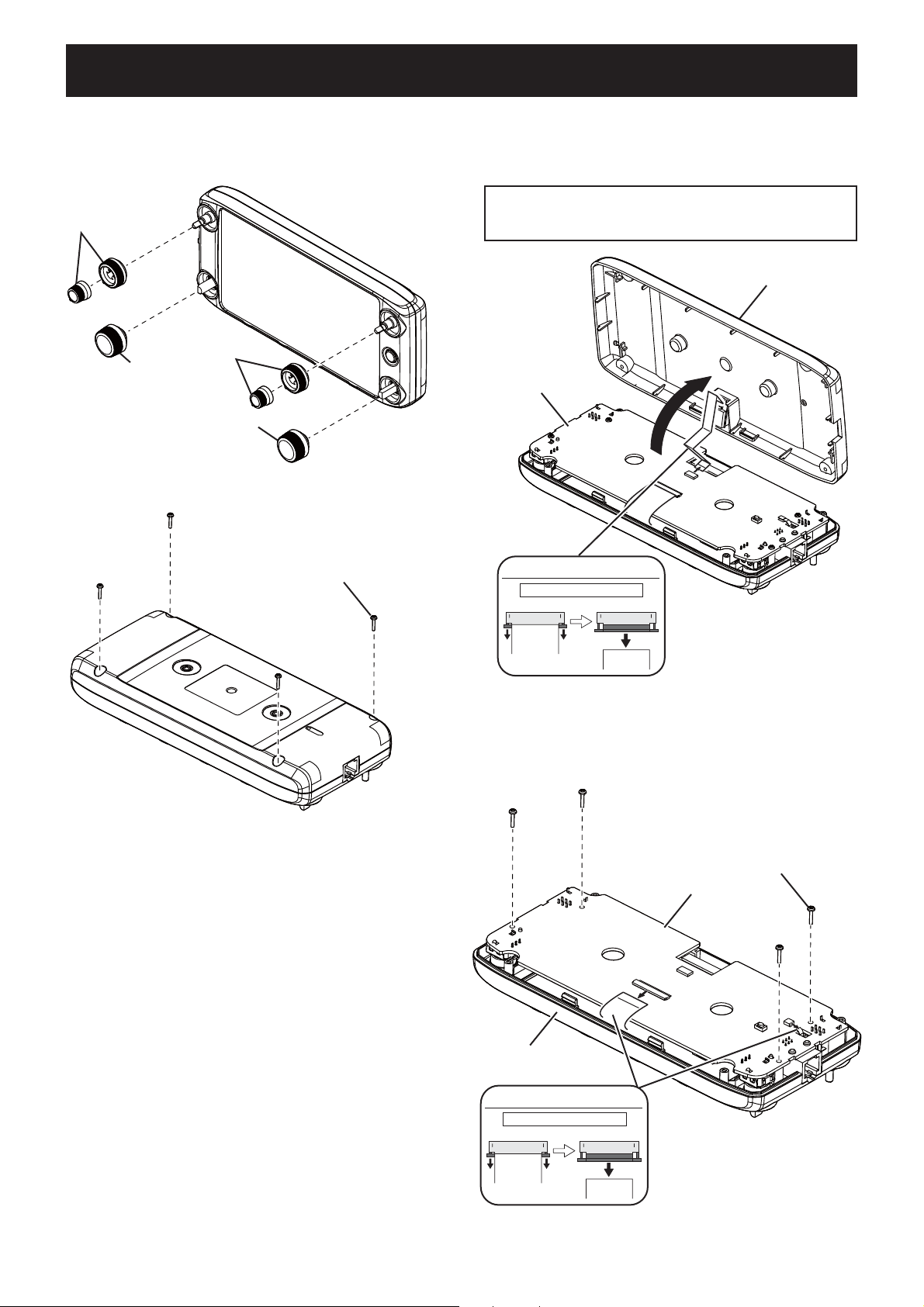

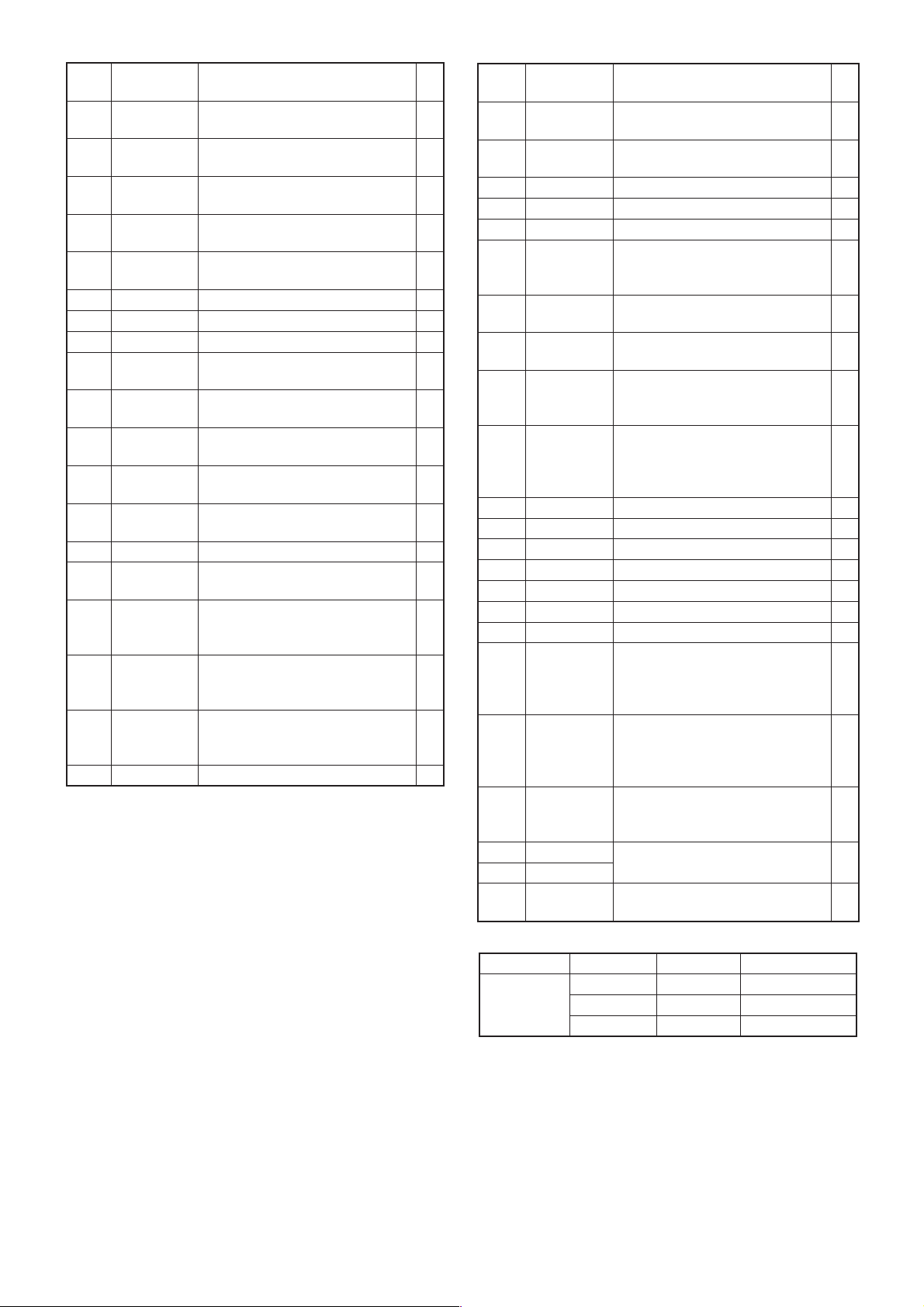

SECTION 3. DISASSEMBLY INSTRUCTION

M

Removing the CONTROL UNIT from the controller.

1) Remove two dials and four knobs from the front

panel.

Knob

3) Take off the rear panel carefully in the direction of

the arrow, and then disconnect the fl at cable.

BE CAREFUL when you disassemble the rear panel from

the CONTROL UNIT. Otherwise the flat cable and the

connector may be cut.

Rear panel

Dial

Knob

Dial

2) Remove four screws from the rear panel.

Four screws

CONTROL UNIT

FLAT CABLE

BE CAREFUL about the locks.

Release the locks

Flat cable

flat cable

Pull straight

Flat cable

4) Disconnect two fl at cables.

5) Remove four screws from the CONTROL UNIT.

6) Remove the CONTROL UNIT from the front panel.

(Continued on the right above.)

FRONT PANEL

BE CAREFUL about the locks.

Release the locks

Flat cable

flat cable

3-1

Four screws

CONTROL UNIT

FLAT CABLE

Pull straight

Flat cable

Page 10

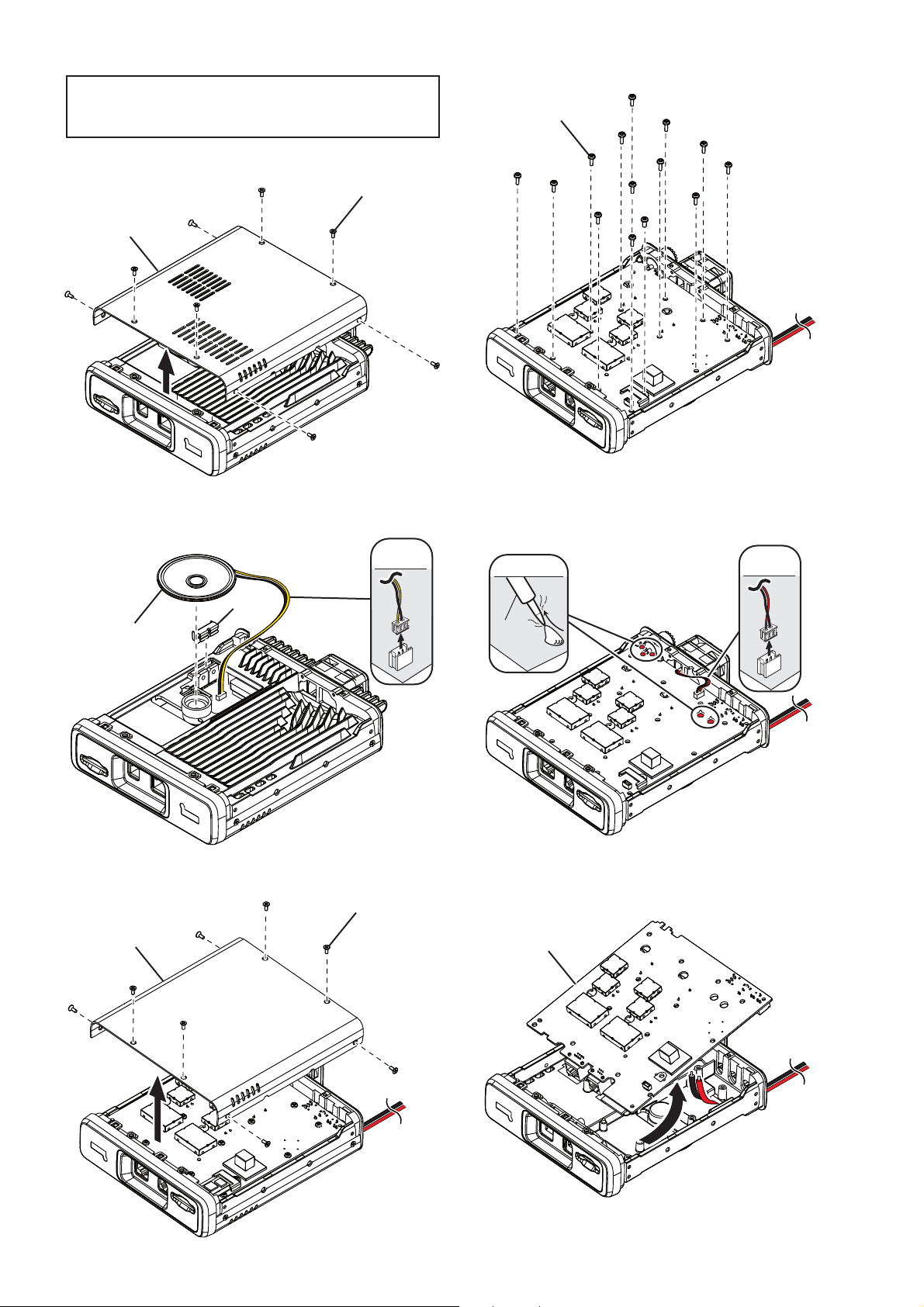

M Removing the MAIN UNIT from the chassis.

Before disassembling:

REMOVE the SD card if inserted. Otherwise the MAIN

UNIT and chassis cannot be separated.

1) Remove eight screws from the top cover.

Eight screws

Bottom cover

4) Remove total of 14 screws from the MAIN UNIT.

14 screws

2) Remove the clip and disconnect the speaker cable.

SPEAKER

CABLE

Clip

Speaker

3) Remove eight screws from the bottom cover.

Eight screws

Bottom cover

5) Disconnect the cooling fan cable, and unsolder fi ve

points (at the antenna connector and the DC cable).

UNSOLDER

Solder

remover

FAN

CABLE

6) Remove the MAIN UNIT from the chassis in the direction of the arrow.

MAIN UNIT

(Continued on the right above.)

3-2

Page 11

SECTION 4. CIRCUIT DESCRIPTION

4-1 RECEIVE CIRCUITS

RF CIRCUITS (MAIN UNIT)

VHF BAND (108–174 MHz)

The RF signal from the antenna is passed through two LPFs

(L90, L94, L96, C409, C418 and L79, L83, L87, C378, C386,

C394), ANT SW (D66, D69, D70 and D77), and then applied

to the RF AMP (Q24).

• Band A

The amplifi ed signal is passed through the ATT (D34), BPF

(D28, D88, L24, L26, L31 L34, C127 and C128), and then

applied to another RF AMP (Q20).

The amplifi ed signal is applied to the 1st IF circuit, through

the BPF (D20, D87, L10, L18, C71 and C74) and RX circuit

SW (D14).

• Band B

The amplifi ed signal is passed through the ATT (D33), BPF

(D27, D85, L23, L25, L32, L33, C125 and C126), and then

applied to another RF AMP (Q19).

The amplifi ed signal is applied to the 1st IF circuit, through

the BPF (D19, D86, L9, L17, C69 and C70) and RX circuit

SW (D13).

UHF BAND (380–479 MHz)

The RF signal from the antenna is passed through the LPF

(L90, L94, L96, C409 and C418) and HPF (L84, L88, C391,

C395 and C402) and ANT SW (D68, D73, D75 and D84), and

then applied to the RF AMP (Q23).

• Band A

The amplifi ed signal is passed through the ATT (D32), BPF

(D24, D26, L21, L28, C113 and C114), and then applied to

the RF AMP (Q18).

The amplifi ed signal is applied to the 1st IF circuit, through

the BPF (D12, D16, L4, L12, C42 and C43) and RX circuit

SW (D8).

• Band B

The amplifi ed signal is passed through the ATT (D31), BPF

(D23, D25, L22, L27, C107, C111, C112 and C121), and then

applied to the RF AMP (Q17).

The amplifi ed signal is applied to the 1st IF circuit, through

the BPF (D11, D15, L3, L11, C36, C40, C41 and C49) and

RX circuit SW (D7).

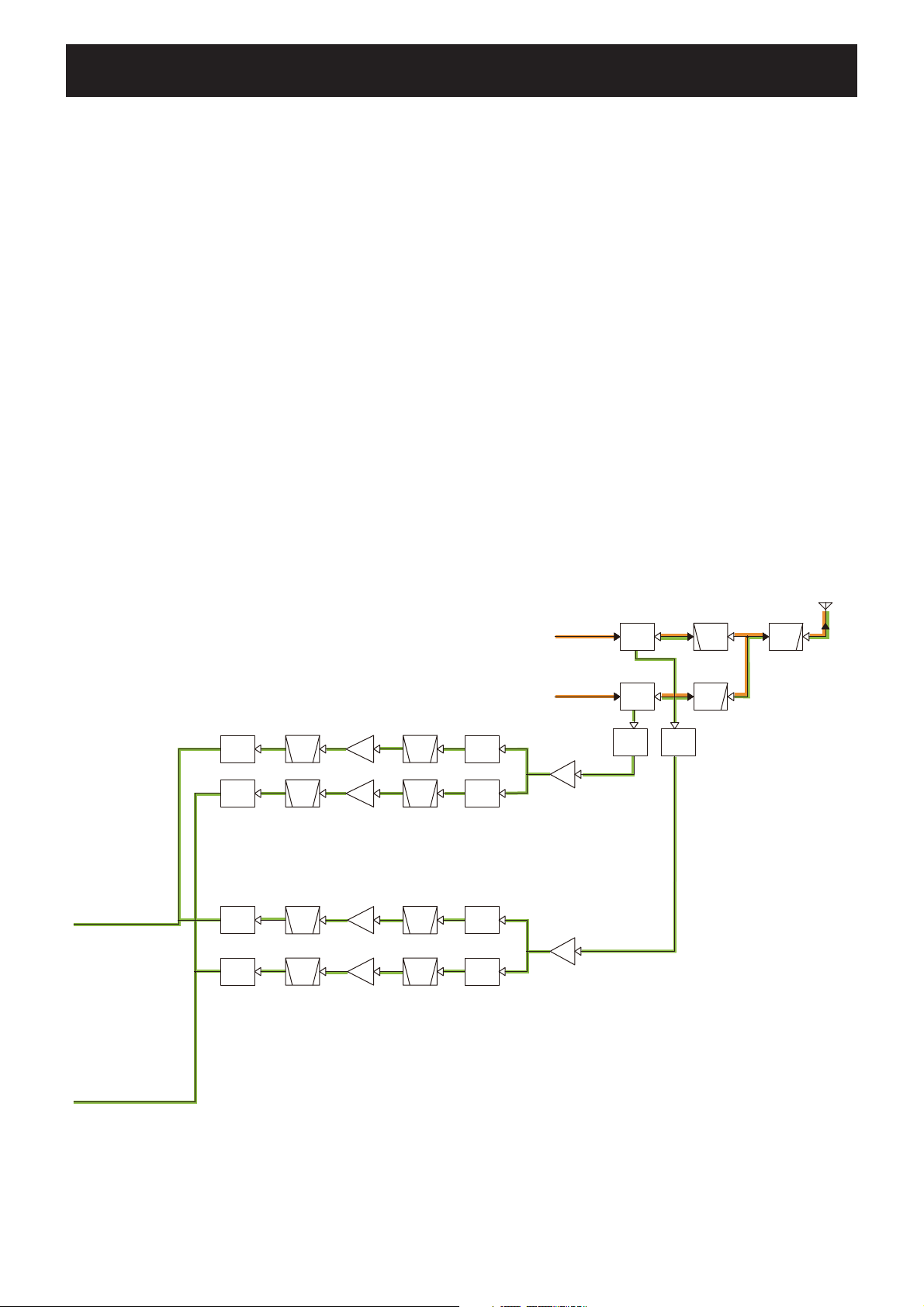

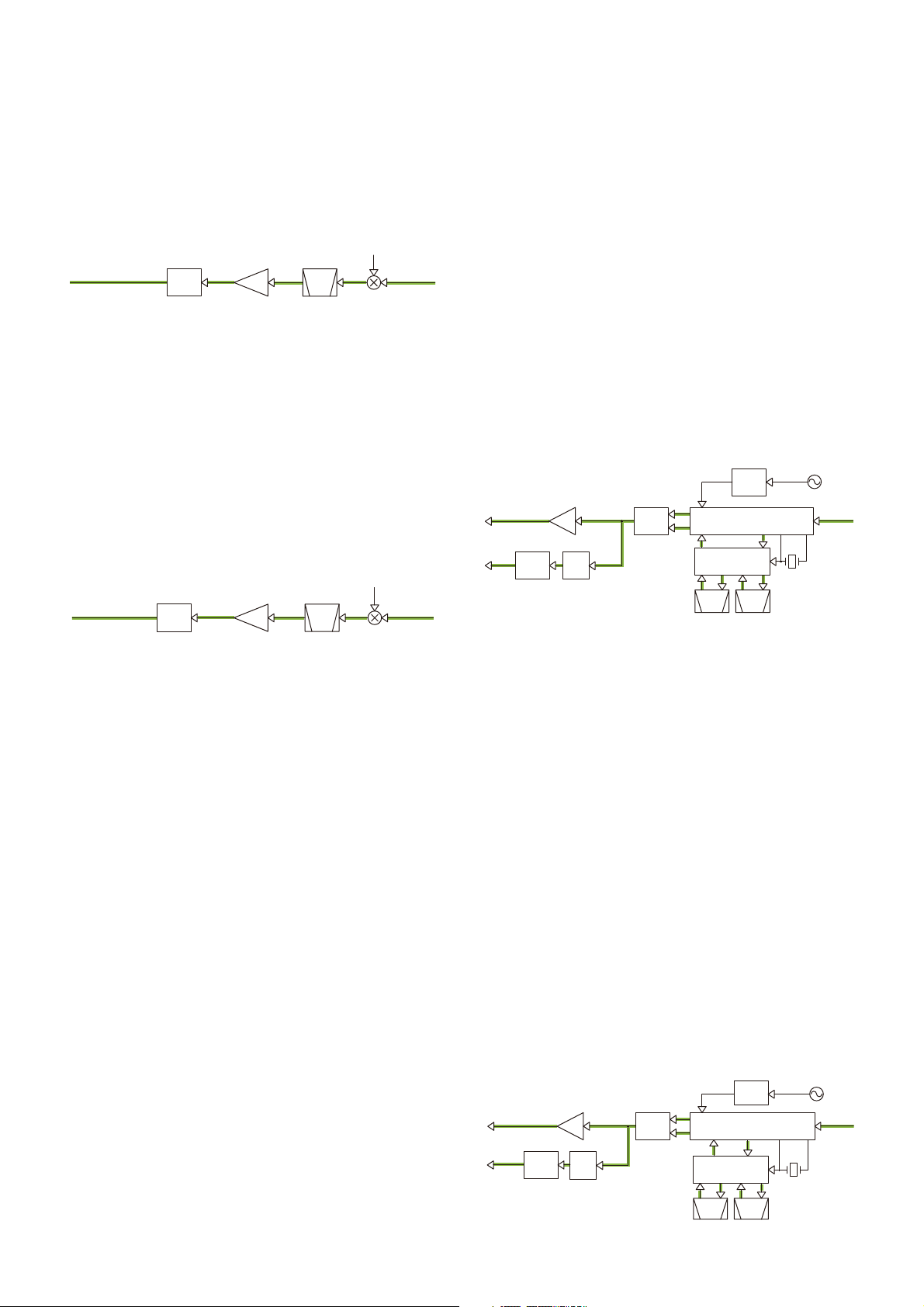

• RF CIRCUITS

1st IF

circuit

D84

D68/D73/D75

LIMITER

118-174MHz

375-550MHz

TX/RX

SW

D66/D69/

D70/D77

TX/RX

SW

400-470MHz

137-174MHz

VHF BAND

D34D28/D88Q20D20/D87D14

RX

SW

RX

SW

D8

RX

SW

D7

RX

SW

BPF

BPF

D10/D12/

D16/D18

BPF

D9/D11/

D15/D17

BPF

RF

AMP

RF

AMP

UHF BAND

Q18

RF

AMP

Q17

RF

AMP

BPF

BPF

D22/D24/

D26/D30

BPF

D21/D23/

D25/D29

BPF

ATT

D33D27/D85Q19D19/D86D13

ATT

D32

ATT

D31

ATT

Band A

Band B

Band A

Band B

Q24

RF

AMP

Q23

RF

AMP

375-550MHz

HPF

118-174MHz

LPF

D79D81

LIMITER

ANTENNA

118-550MHz

LPF

1st IF

circuit

4-1

Page 12

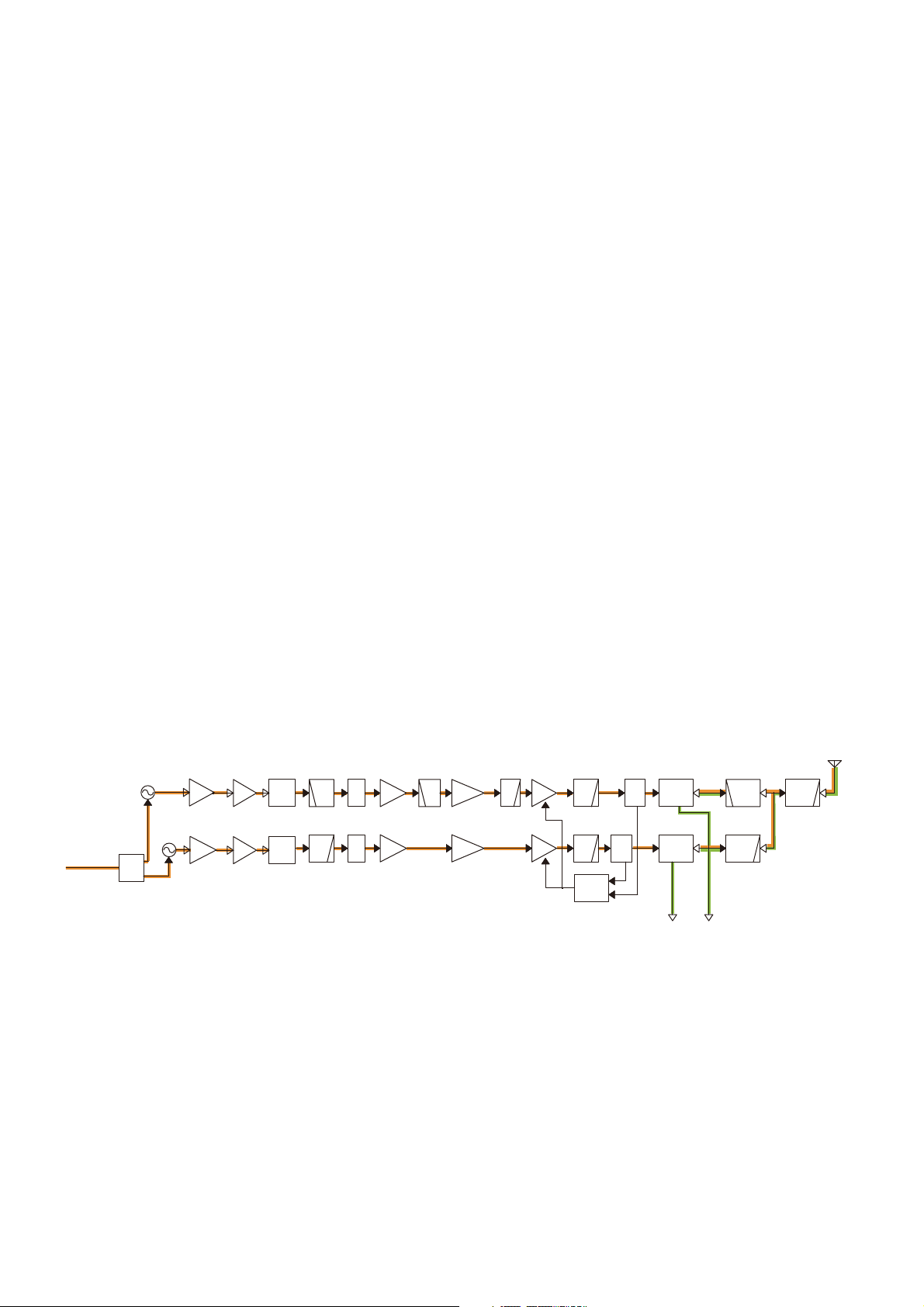

1ST IF CIRCUITS (MAIN UNIT)

• Band A

The RX signal from the RF circuit is applied to the 1st mixer

(IC125) and mixed with the 1st LO signal, resulting in the

38.85 MHz 1st IF signal. The converted signal is passed

through the 1st IF fi lter (FI105), and then applied to the 1st

IF AMP (Q138). The amplifi ed signal is applied to the 2nd IF

circuit, through the limiter (D114).

• 1ST IF CIRCUITS (Band A)

Band A

2nd IF

circuit

D114

LIMITER

IF

AMP

Q138/

D116/D118

FI105

XTAL

BPF

38.85MHz

• Band B

The RX signal from the RF circuit is applied to the 1st mixer

(IC124) and mixed with the 1st LO signal, resulting in the

46.35 MHz 1st IF signal. The converted signal is passed

through the 1st IF fi lter (FI104), and then applied to the 1st

IF AMP (Q137). The amplifi ed signal is applied to the 2nd IF

circuit, through the limiter (D113).

1st LO

LIF

IC125

• 1ST IF CIRCUITS (Band B)

2nd IF

circuit

D113

LIMITER

IF

AMP

Q137/

D115/D117

Band B

FI104

46.35MHz

XTAL

BPF

1st LO

RIF

IC124

2ND IF CIRCUITS (MAIN UNIT)

• Band A

The 1st IF signal from the 1st IF circuit is applied to the IF IC

(IC121, pin 20), which contains the 2nd IF AMP, 2nd mixer,

FM demodulator, and so on.

The 1st IF signal is mixed with the 38.4 MHz 2nd LO signal,

resulting in the 450 kHz 2nd IF signal. The converted signal

is passed through the external 2nd IF fi lter (FM mode: FI103,

FM-N or DV mode: FI102) to remove sideband noise.

While operating in the FM or AM mode, the fi ltered signal is

amplifi ed by the 2nd IF AMP, and then demodulated by the

internal demodulator circuit. The demodulated signal is applied to the RX AF circuit, through the RX mode SW (IC119),

AF fi lter (Q113 and Q140) and AF SW (IC111).

While operating in the DV mode, the fi ltered signal is amplifi ed by the 2nd IF AMP, and then demodulated by the internal demodulator circuit. The demodulated signal is applied

to the digital demodulation circuit, through the RX mode SW

(IC119) and buffer AMP (IC117).

• 2ND IF CIRCUITS (Band A)

Q200

38.4MHz

IF IC

WIDE/NARROW

SELECTOR

CERAMIC

CERAMIC

BPF

FI102 FI103

X3

BPF

12.8MHz

X102

X200

Digital

demodulation

Cricut

IC111 Q113/Q140

RX AF

Cricut

DIGI/AN

AFMUTE

Band A

IC117 IC119 IC121

BUFF

AF

FIL

DV

FM/AM

Q122/Q124/Q142

Q128/D107/D108

D111/D112

DET OUT

SELECT

AM

FM

• Band B

The 1st IF signal from the 1st IF circuit is applied to the IF IC

(IC120, pin 20), which contains the 2nd IF AMP, 2nd mixer,

FM demodulator, and so on.

The 1st IF signal is mixed with the 45.9 MHz 2nd LO signal,

resulting in the 450 kHz 2nd IF signal. The converted signal

is passed through the external 2nd IF fi lter (FM mode: FI101,

FM-N or DV mode: FI100) to remove sideband noise.

While operating in the FM or AM mode, the fi ltered signal is

amplifi ed by the 2nd IF AMP, and then demodulated by the

internal demodulator circuit. The demodulated signal is applied to the RX AF circuit, through the RX mode SW (IC119),

AF fi lter (Q112 and Q139) and AF SW (IC111).

While operating in the DV mode, the fi ltered signal is amplifi ed by the 2nd IF AMP, and then demodulated by the internal demodulator circuit. The demodulated signal is applied

to the digital demodulation circuit, through the RX mode SW

(IC119) and buffer AMP (IC117).

• 2ND IF CIRCUITS (Band B)

Digital

demodulation

Cricut

RX AF

Cricut

DIGI/AN

AFMUTE

IC117 IC120IC119

BUFF

IC111

Q112/Q139

AF

FIL

DV

FM/AM

Q121/Q123/Q141

Q127/D105/D106

D109/D110

Band B

DET OUT

SELECT

AM

FM

CERAMIC

Q220

45.9MHz

X3

IF IC

WIDE/NARROW

SELECTOR

CERAMIC

BPF

BPF

FI100 FI101

15.3MHz

X101

X201

4-2

Page 13

DIGITAL DEMODULATION CIRCUIT (MAIN UNIT)

While operating in the DV mode, the demodulated signal (digital audio signal) is passed through the LPF (Band A: R1195,

R1206, C1461 and C1475/Band B: R1194, R1205, C1460

and C1474) and amplifi ed by the AF AMP (Band A: IC407/

Band B: IC406). The amplifi ed signal is applied to the liner

codec (IC402) to be converted into the digital audio signal.

The digital audio signal is demodulated by the DSP (IC400),

and then applied to the linear codec (IC402) again, to be decoded into an analog audio signal.

The decoded AF signal is applied to the RX AF circuit, through

the HPF (Band A: IC407/Band B: IC406) and LPF (Band A:

IC407/Band B: IC406) and AF SW (IC111).

• DIGITAL DEMODULATION CIRCUIT

IC400

L_DAF

R_DAF

DSP

LINEAR

CODEC

IC402

IC407

AMP LPF

IC406

AMP LPF

L_DDET

R_DDET

4-2 TRANSMIT CIRCUITS

TX AF CIRCUIT (MAIN UNIT)

The AF signal from the microphone (MIC signal) is passed

through the MIC SW (IC100) and ATT (IC100), and then applied to the MIC AMP (IC102).

The amplifi ed signal is applied to the audio processor LSI

(IC103), through the mute SW (IC104).

The audio processor LSI contains 16-bit liner CODEC, MIC

AMP, audio fi lters, D/A converter, and so on.

• When operating in the DV mode

The applied signal is further amplifi ed by the ALC AMP. The

amplifi ed signal is applied to the liner CODEC, to be encoded

into a digital audio signal.

The digital audio signal is processed by the DSP (IC400), and

then passed through the mode SW (IC104) and LPF (IC103),

and then applied to the D/A converter (IC103), to be adjusted

in level.

IC407

HPF

IC406

HPF

IC407

IC406

LPF

LPF

IC111

DIGI/AN

AFMUTE

IC111

DIGI/AN

AFMUTE

L_DAF

R_DAF

RX AF CIRCUIT (MAIN UNIT)

The demodulated AF signal from the AF SW (IC111) is applied to the electric volume (IC110), which separately adjusts

the A and B bands AF signal in level. The level-adjusted AF

signal is passed through the AF line SW (IC109).

When the AF signal is output from the internal speaker

or [SP1] jack:

The AF signal is passed through two speaker mute SWs

(Q105 and Q104), and then amplifi ed by the AF power AMP

(IC105).

The amplifi ed AF signal is output to the internal speaker

(CHASSIS: SP1) or external speaker, through the [SP1] jack

(J101).

When the AF signal is output from the [SP2] jack:

The AF signal is passed through the speaker mute SW

(Q106), and then amplifi ed by the AF power AMP (IC106).

• When operating in the FM/FM-N mode

The applied signal is passed through the HPF (IC103), IDC

(IC103), LPF (IC103), mode SW (IC104) and LPF (IC103),

and then applied to the D/A converter (IC103) to be adjusted

in level.

The level-adjusted signal is applied to the modulation circuit.

• TX AF CIRCUIT

IC307

BTMIC

MIC

BUFF

J100

1

2

3

4

5

6

7

8

IC100 IC100

BTMIC

SW

IC103

DV

ALC

AMP

IC102

MIC

ATT

AMP

Audio Processor LSI

IDC

HPF

DSP

IC400

LPF

IC104

MUTE

SW

IC104

FMFM

MODE

DV

SELECT

D/AA/D

IC103

LPF

IC103

D/A

The amplifi ed AF signal is applied to the [SP2] jack (J102).

• RX AF CIRCUITS

[SP1]

J101

SP1

[SP2]

J102

IC105 Q104 Q105

AF

SP

AMP

MUTE

IC106 Q106

AF

AMP

SP

MUTE

SP

MUTE

IC109 IC110

AFSW

ELEC.

VR

A band AF

B band AF

4-3

Page 14

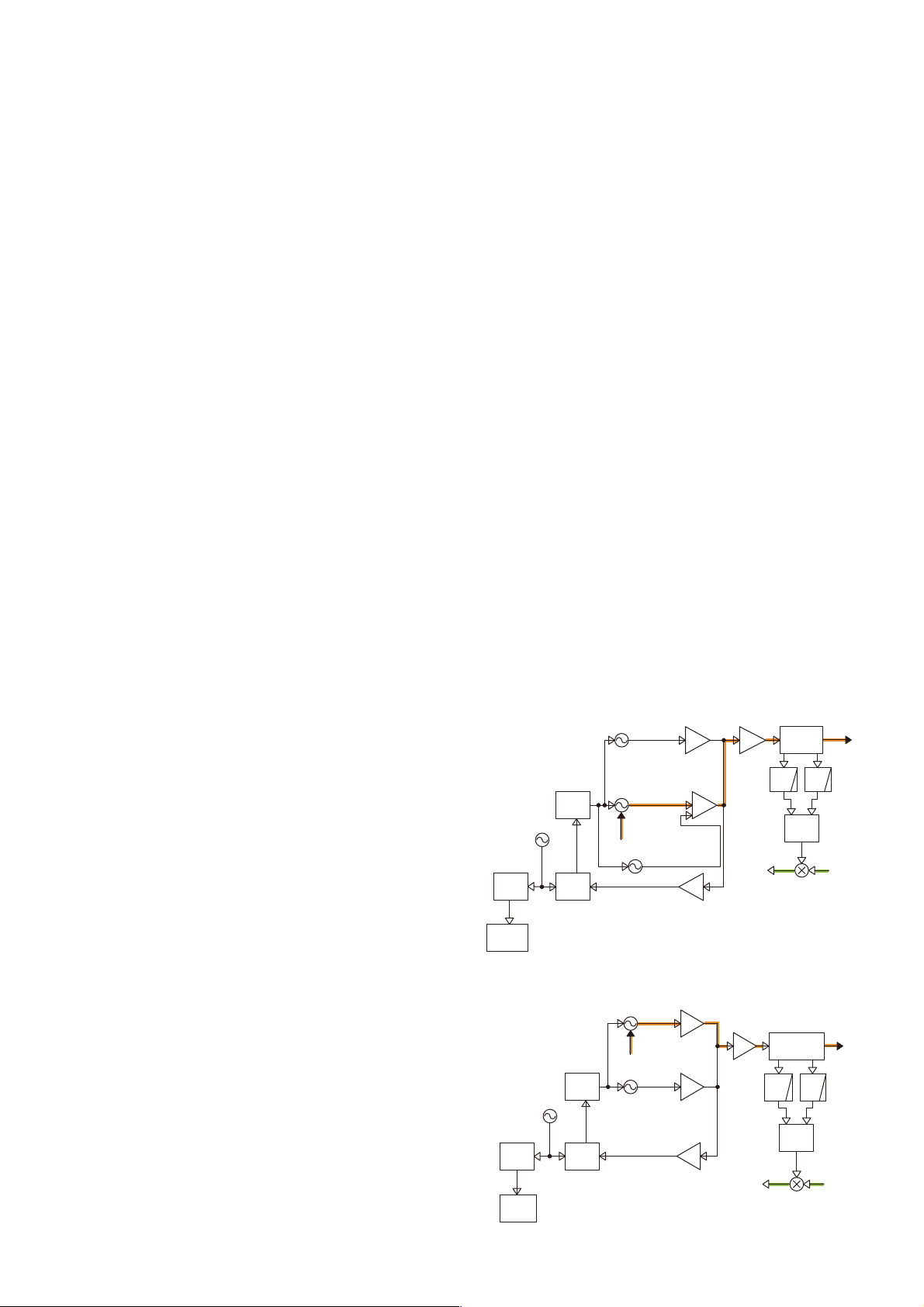

MODULATION CIRCUITS (MAIN UNIT)

The MIC signal from the TX AF circuits is applied to the VCO

as the GMSK (For the DV mode) or Frequency Modulation

(For the FM mode) modulation signal.

VHF BAND

The modulation signal is applied to the VHF VCO (Q211,

D203, D204 and D228).

The modulated VCO output signal is amplifi ed by the buffer

(Q215) and LO AMP (IC203), and then applied to the TX AMP

circuits as the TX signal, through the LO SW (D50).

UHF BAND

The modulation signal is applied to the UHF VCO (Q232,

D223, D224 and D227) as a modulation signal.

TX AMP CIRCUITS (MAIN UNIT)

VHF BAND

The TX signal is passed through the LPF (L50, L51, C215,

C220 and C225) and ATT (R146, R147 and R151), and then

sequentially amplifi ed by the YGR (Q36), drive AMP (Q40)

and power AMP (IC3).

The amplifi ed TX signal is passed through the LPF (L67,

C291 and C297), TX output power detector (D59 and D63),

ANT SW (D66) and two LPFs (L90, L94, L96, C409, C418

and L79, L83, L87, C378, C386, C394), before being applied

to the antenna.

UHF BAND

The TX signal is passed through the HPF (L52 and C232) and

ATT (R155, R156 and R162), and then sequentially amplifi ed

by the YGR (Q38), drive AMP (Q41) and power AMP (IC4).

The modulated VCO output signal is amplifi ed by the buffer

(Q235) and LO AMP (IC208), and then applied to the TX AMP

circuits as the TX signal, through the LO SW (D52).

• TX AMP AND APC CIRCUITS

UHF TX VCO

IC205

VCOMOD

MOD

MUTE

Q232

Q227

Q211

Q207

VHF TX VCO

Q235

BUFF

Q215

BUFF

IC208

LO

AMP

IC203

LO

AMP

D52

TX/RX

SW

D50

TX/RX

SW

HPF

LPF

Q38 Q41 IC4 D62/D67 D68/D73/D75

YGR

ATT

Q36 Q40 IC3 D59/D63

ATT

YGR

The amplifi ed TX signal is passed through the LPF (L69,

C310 and C319), TX output power detector (D62 and D67),

ANT SW (D68 and D84), HPF (L84, L88, C391, C395 and

C402) and LPF (L90, L94, L96, C409, C418), before being

applied to the antenna.

APC CIRCUITS (MAIN UNIT)

At the TX output power detector, the RF signal at the LPFs

(VHF band: L68, C301, C302 and C326/UHF band: L73,

C322, C323 and C350) is rectifi ed by the diodes (VHF band:

D59 and D63, UHF band: D62 and D67), and it is used as the

TX power sensing voltage.

The voltage is applied to the APC AMP (IC2), and the output

voltage controls the bias voltages of the power AMP (VHF

band: IC3, UHF band: IC4) to keep the TX output power constant.

DRIVE

AMP

DRIVE

AMP

UHF band

VHF band

PWR

LPFHPF

AMP

PWR

LPF

AMP

IC2

APC

CTRL

PWR

DET

PWR

DET

D84

TX/RX

SW

D66/D69/

D70/D77

TX/RX

SW

375-550MHz

HPFLPF

118-174MHz

LPF

118-550MHz

ANTENNA

LPF

4-4

VHF RX circuit

UHF RX circuit

Page 15

4-3 FREQUENCY SYNTHESIZER CIRCUIT

(MAIN UNIT)

VCOs

The ID-5100A/E has total of fi ve VCOs: three VCOs for Band

A and another two for Band B.

• Band A

VHF VCO #1

(Used when the Heterodyne function is set to "Normal")

The VHF VCO #1 (Q211, D204, D206 and D228) generates

both 1st LO signal (for receiving a VHF signal on Band A)

and the VHF TX signal. The output of buffer (Q215) is amplifi ed by the LO AMP (IC203), and then used as the VHF TX/

RX LO signal.

While receiving, the LO signal is applied to the 1st IF mixer

(IC125) for receiving a signal on the VHF band, through the

RX LO SW (D212 and D217) and LPF (L314, L316, C986,

C992 and C997).

While transmitting, the LO signal is applied to the TX AMP

circuits, through the LO SW (D50).

VHF VCO #2

(Used when the Heterodyne function is set to "Reverse")

The VHF VCO #2 (Q237, D238 and D239) generates the 1st

LO signal (for receiving a VHF signal on Band A). The output

of buffer (Q215) is amplifi ed by the LO AMP (IC203), and

then applied to the 1st IF mixer (IC125) for receiving a signal

on the VHF band, through the RX LO SW (D212 and D217)

and LPF (L314, L316, C986, C992 and C997).

PLL

•Band A

A portion of VHF and UHF VCOs output signal is amplifi ed by

the buffer (Q213), and then fed back to the PLL IC (IC201).

The PLL IC (IC201) phase-compares the output of reference

frequency oscillator (TCXO: X200) and VCO, and the phase

difference is output as the charge pump current. The current

is passed though the loop fi lter (R715, R717, R719, R722,

C924, C926 to C928 and C930) to be converted into the lock

voltage, which controls the oscillating frequency of VCO.

When the oscillation frequency drifts, its phase changes from

that of the reference frequency, causing a lock voltage change

to compensate for the drift in the VCO oscillating frequency.

• Band B

A portion of VHF and UHF VCOs output signal is amplifi ed by

the buffer (Q234), and then fed back to the PLL IC (IC206).

The PLL IC (IC206) phase-compares the output of reference

frequency oscillator (TCXO: X201) and VCO, and the phase

difference is output as the charge pump current. The current

is passed though the loop fi lter (R797, R799, R802, R805,

C1041, C1043 to C1045 and C1048) to be converted into the

lock voltage, which controls the oscillating frequency of VCO.

When the oscillation frequency drifts, its phase changes from

that of the reference frequency, causing a lock voltage change

to compensate for the drift in the VCO oscillating frequency.

UHF VCO

The UHF VCO (Q205, Q210, D201, D202 and D205) generates the 1st LO signal (for receiving a UHF signal on Band

A). The output of buffer (Q214) is amplifi ed by the LO AMP

(IC203), and then applied to the 1st IF mixer (IC125), through

the RX LO SW (D213 and D216) and LPF (L315, C988 and

C995).

• Band B

VHF VCO

The VHF VCO (Q228, Q233, D225, D226 and D230) generates the 1st LO signal (for receiving a UHF signal on Band

A). The output of buffer (Q236) is amplifi ed by the LO AMP

(IC208), and then applied to the 1st IF mixer (IC124), through

the RX LO SW (D235 and D237) and LPF (L338, L339,

C1103, C1105 and C1106).

UHF VCO

The UHF VCO (Q232, Q227, D223, D224, D227 and D229)

generates both 1st LO signal (for receiving a UHF signal on

Band B) and the UHF TX signal. The output of buffer (Q235)

is amplifi ed by the LO AMP (IC208), and then used as the

UHF TX/RX LO signal.

While receiving, the LO signal is applied to the 1st IF mixer

(IC124) for receiving a signal on the UHF band, through the

RX LO SW (D234 and D236) and LPF (L337, C1102 and

C1104).

While transmitting, the LO signal is applied to the TX AMP

circuits, through the LO SW (D52).

• FREQUENCY SYNTHESIZER CIRCUIT

2nd LO

IC121

2nd LO

IC120

12.8 MHz

Q200

IF IC

IF IC

X3

38.4 MHz

15.3 MHz

Q220

X3

45.9 MHz

X200

X201

IC202/Q202

LOOP

FIL

IC201

PLL

IC

IC207/Q222

LOOP

FIL

IC206

PLL

IC

Q210

D201,D202,D205

RX:361.15-511.15 MHz

Q211

D203,D204,

D206,D228

TX:

137-174 MHz

RX:

156.85-212.85 MHz

RX:79.15-135.15 MHz

Q237

D238,D239

A band

Q232

D223,D224,

D227,D227

TX:400-470 MHz

RX:353.65-516.35 MHz

Q233

D225,D226,D230

RX:164.35-220.35 MHz

B band

Q213

Q235

BUFF

Q236

BUFF

Q234

BUFF

Q214

BUFF

BUFF

L_UHF

Q215

BUFF

L_VHF

R_VHF

R_UHF

IC208

AMP

IC203

AMP

D216

D217

D52/D234/D235

D236

D237

D50

D212/D213

TX/RX

SW

LPFLPF

RX

SW

1st LO

1st mixer

IC125

TX/RX

SW

LPFLPF

RX

SW

1st LO

1st mixer

IC124

4-5

Page 16

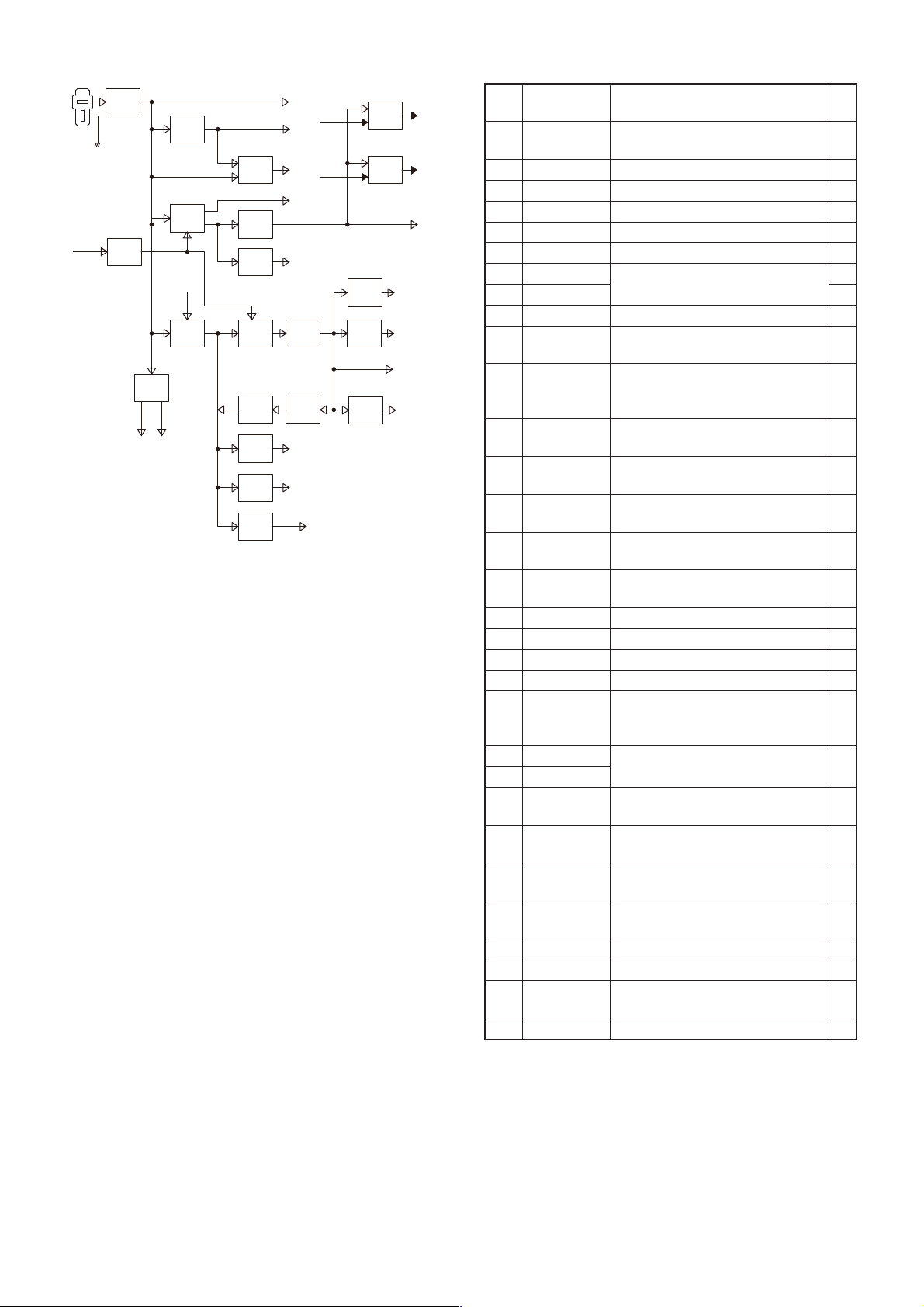

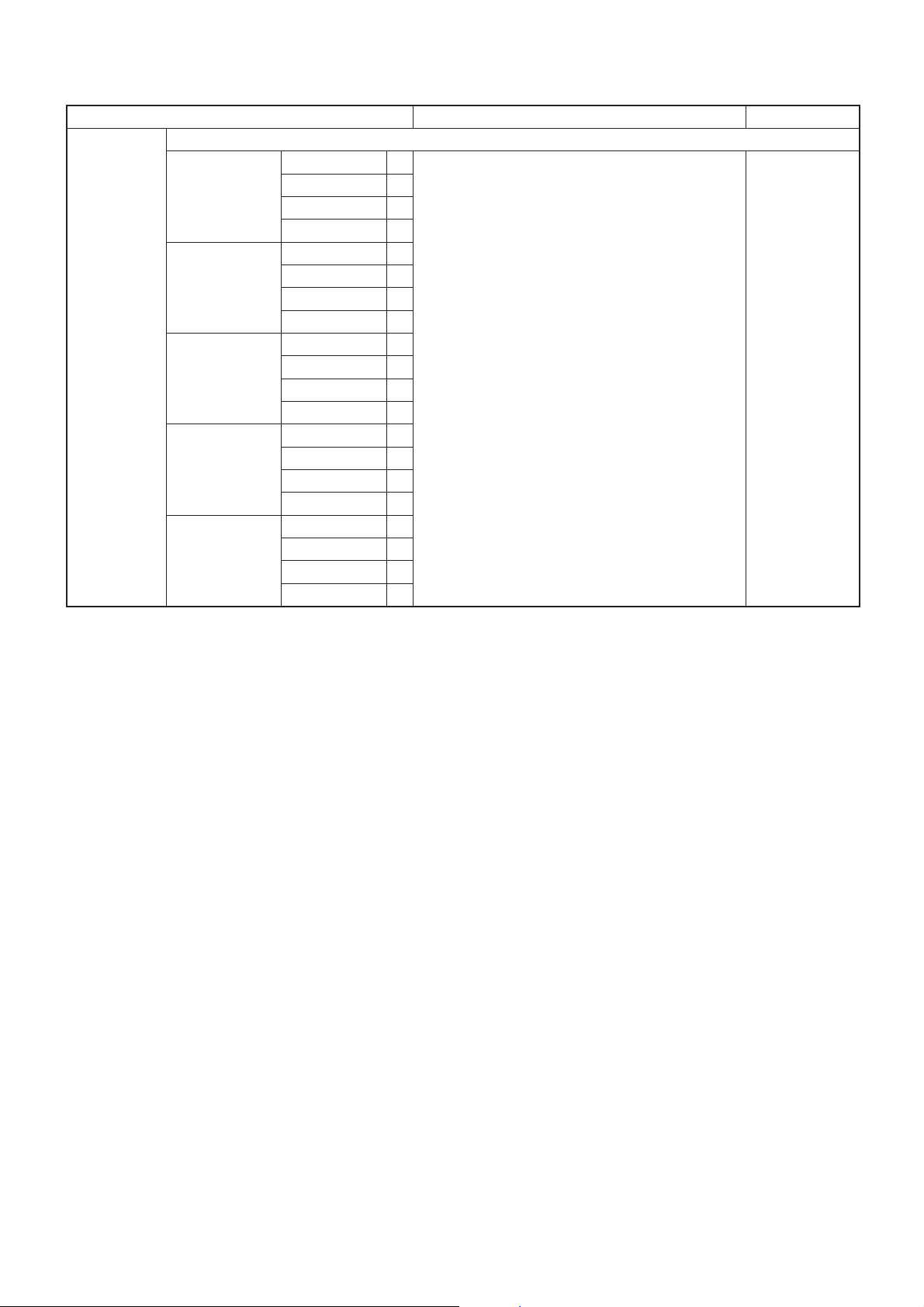

W300

NOISE

FILTER

Q301

PWR

PCON

CTRL

PDV

To CPU

MAIN UNIT

LOW V

DET

Q302/Q306

IC309

IC324

IC320

ALARM

To BT

I SENS

VCC

SW

PSC

SW

REG(6V)

FANHV

IC310

CURRENT

DETECT

IC313

+8

REG

IC321

CTRL8V

IC323 C1340

4.2V

REG

IC311

3.3V

REG

IC306

IC305

REG

SW

BT3V

REG

SD3V

REG

CONT8V

HV

IDET

VCC

IC319Q303

5V

REG

SUPER

CAP

CPU3.3V

BT3.3V

SD3.3V

UTX_C

VTX_C

IC404

1.3V

REG

IC403

3.3V

REG

IC314

3.3V

REG

Q32/Q34

UT8

REG

Q27/Q28

VT8

REG

DSP1.3V

DSP3.3V

5VS

3VS

UT8

VT8

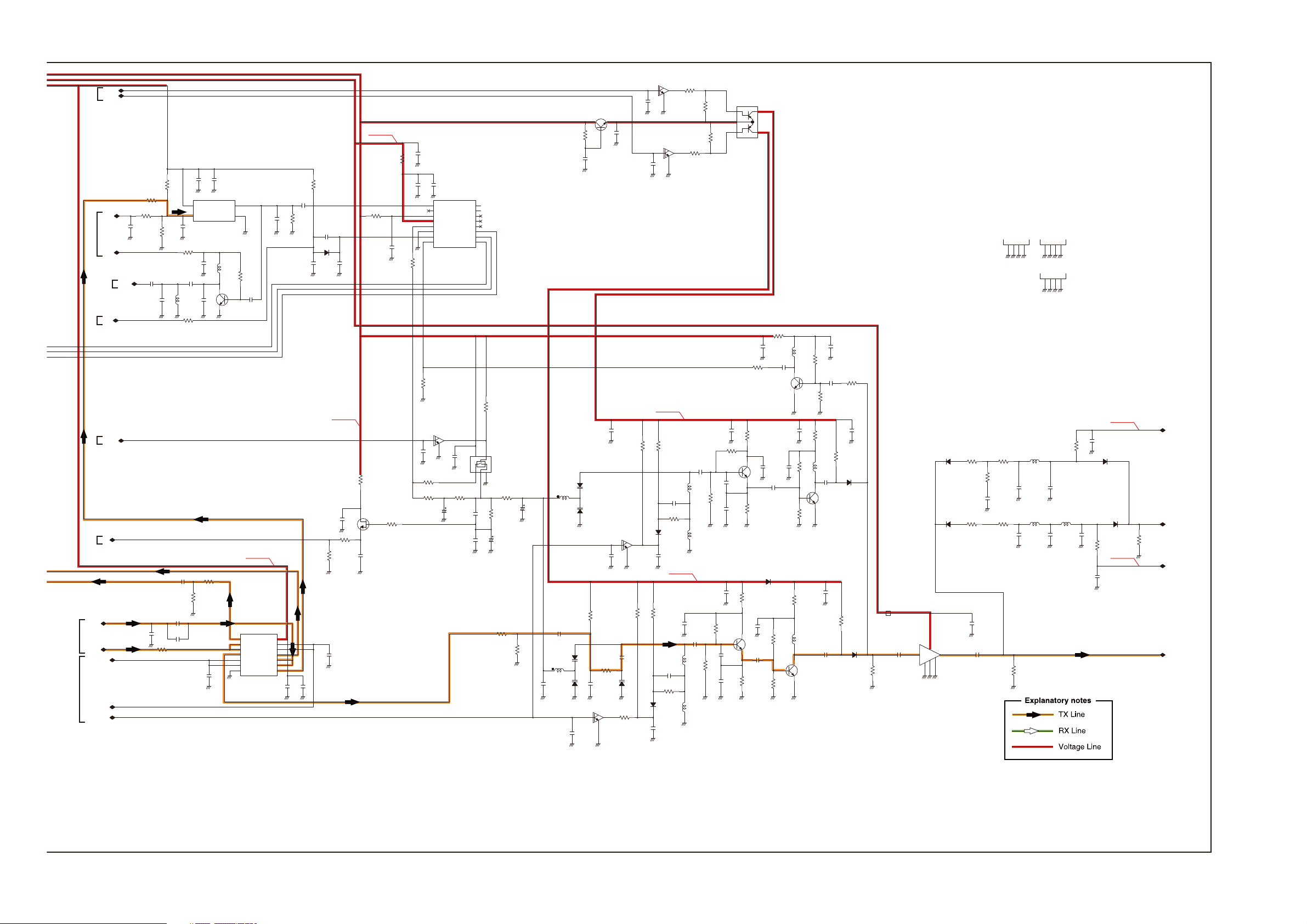

4-5 PORT ALLOCATIONS4-4 VOLTAGE DIAGRAM

• CONTROLLER CPU (CONTROL UNIT: IC2)

Ball

Line Name Description I/O

No.

7 TWDTX

14 RESET Reset signal input. I

15 R_VOLV Band B [VOL] input. I

8V

16 R_SQLV Band B [SQL] input. I

17 L_VOLV Band A [VOL] input. I

18 L_SQLV Band A [SQL] input. I

25 G_TXD

26 G_RXD I

29 DIM_DA LCD backlit brightness control. O

30 G_RES

31 GPSC

32 LCDRST

33 TEMP

38–41LCDD4–

LCDD7

47 FLTXD

48 FLRXD

51 L_DIALB Band A [DIAL] phase-B. I

52 L_DIALA Band A [DIAL] phase-A. I

53 R_DIALB Band B [DIAL] phase-B. I

54 R_DIALA Band B [DIAL] phase-A. I

58 LCDCD

61 LCDD0

62 LCDD1

65 TWCS

66 TWBUSY

78 TWPIRQ

79 TWDCLC

80 TWDRX Touch panel controller serial data. O

81 LCDD2 LCD control data. O

86 LCDWR0

88 LCDCS LCD controller chip select. O

Touch panel controller touch sens-

ing data.

GPS data.

GPS module (EP13) reset.

L= Resets.

O

O

O

GPS module (EP13) power supply

control.

O

L=GPS module is activated.

LCD controller reset.

L= Resets.

O

LCD controller temperature sens-

ing voltage.

LCD control data. I/O

Control signal to the main CPU

(IC300).

O

Control signal from the main CPU

(IC300).

LCD controller data/command se-

lect.

O

H=While sending the control data.

LCD control data. I/O

Touch panel controller chip select.

L=While inputting/outputting data.

O

Touch panel controller status.

H=Busy.

Touch panel controller interrupt.

L=Touching detected.

Touch panel controller serial

clock.

Touch panel controller read/write

control.

O

O

I

I

I

I

4-6

Page 17

• MAIN CPU (MAIN UNIT: IC300)

Ball

Line Name Description I/O

No.

A4 R_LV Lock voltage input. (Band B) I

A6 VIN External power supply voltage. I

A7 L_WXALT

A8 MICUD

A9 AUDI

A11 PSC

A12 DA_STB D/A converter serial strobe. O

B1 DTMF

B4 R_RSSI RSSI voltage. (Band B) I

B7 IDET Transmit current sensing voltage. I

B8 TEMP

B9 AURES

C2 DTCS

C4 R_DTCSIN

C7 L_DTCSIN

C9 DTMUTE

C11 DSP_PD

D1 DA_DATA Serial data to the D/A converter. O

D2 BTRXD

D4 R_WXALT

D5 R_LV Lock voltage. (Band B) I

D6 VOX VOX sensing voltage. I

D7 L_RSSI RSSI voltage. (Band A) I

D8 AUSTB Audio IC serial strobe. O

D11 DA_CK Serial clock to the D/A converter. O

E4 BTTXD Serial data to the Bluetooth

G1 RESET

G3 BT_RES

G4 MIC_PTT PTT input from the microphone. I

H14 SCSCK

H15 SCRXD

J4 RTC_IRQ

J12 BWD

J13 BTPLAY

WX alert signal (1050 Hz). (Band

A)

The [UP]/[DOWN] key input from

the microphone.

Response signal from the audio

IC.

5VS power supply line control.

L= While in the power save mode.

DTMF tone, European tone and

beep sound signals.

Transceiver temperature sensing

voltage.

Audio IC reset.

L=Reset.

TSQL/DTCS tone fi lter switching

control.

H= While the DTCS tone is used.

TSQL/DTCS tone signal. (Band

B)

TSQL/DTCS tone signal. (Band

A)

Tone signal (BEEP/DTMF/

ETONE) modulation mute.

L=Mute.

DSP power down control.

H= Power down.

Serial data from the Bluetooth

unit.

Weather alert signal (1050 Hz)

detect. (Band B)

®

unit. O

CPU reset signal.

L=Reset.

®

Bluetooth

unit reset signal.

H=Reset.

Serial clock to the sub CPU

(IC303).

Serial data from the sub CPU

(IC303).

Interrupt detection from the real

time clock IC.

L= Alerm detected.

The [RWD] key input from the Blu-

®

etooth

unit.

L=When pushed.

The [PLAY] key input from the Blu-

®

etooth

unit.

L=When pushed.

Ball

Line Name Description I/O

No.

®

Bluetooth

J15 BT_SW

I

I

K1 L_SQL

trol.

H= The Bluetooth

vated.

Noise level detection. (Band A)

H= Noise signal is detected.

unit power supply con-

®

unit is acti-

O

I

K3 IOSTB Expander serial strobe. O

I

K14 FWD

O

The [FWD] key input from the Blu-

®

etooth

unit.

L=When pushed.

I

K15 IOEN Expander chip enable. O

O

M1 98_DATA

M2 TX_DATA

Control serial data from the microphone.

Control serial data to the CPU on

the CONTROL UNIT.

I

O

M5 DSP_STB DSP serial strobe. O

I

O

O

I

I

O

M7 ECK EEPROM serial clock. O

M8 L_UNLK

M9 VOL_DATA

M12 TX232

N1 RX_DATA

N2 SD_SENC

PLL unlock detection. (Band A)

L=Unlocked.

Serial data to the audio volume

IC.

UART data (RS-232C).

(4800/9600/38400 bps)

Control serial data from the CPU

on the CONTROL UNIT.

SD card insert detection.

L=Inserted.

N3 SD_TXD Serial data to the SD card. O

I

O

O

I

I

N4 DSP_SI DSP serial data. I

O

®

I

I

N5 CLIN

N6 RTC_SDA

N7 ESIO EEPROM serial data. I/O

N9 VOL_CK

N12 DATA

N13 SCTXD

CI-V/CLONE UART data.

(300–38400 bps)

Serial data to/from the real time

clock IC.

Serial clock to the audio volume

IC.

Common serial clock to the D/A

converter and expander.

Serial data to the sub CPU

(IC303).

I

I/O

O

O

O

P1 SD_CS Chip select to the SD card. O

P2 SD_SCK Serial clock to the SD card. O

I

R8 R_UNLK

PLL unlock detection. (Band B)

L=Unlocked.

I

K4 DSP_REQ DSP "REQEST" signal. I

O

P4 DSP_CK DSP serial clock. O

P5 PDV Power supply voltage drop detect. I

[PTT] input from the Bluetooth

O

P6 H_PTT

unit.

®

I

L=Pushed.

I

P7 SD_SW

I

P10 SCACK "ACK" signal from the sub CPU. I

P12 BTUNIT

I

P13 RX232

I

R1 SD_RXD Serial data from the SD card. I

SD card driver power supply control.

H=SD card driver is activated.

Bluetooth

®

unit mount detect.

L=Mounted.

RS-232C UART data.

(4800/9600 bps)

O

I

I

R2 DSP_SO DSP serial data. O

4-7

Page 18

• MAIN CPU (MAIN UNIT: IC300) (continued)

Ball

Line Name Description I/O

No.

R4 CLOUT

R5

DSP_RESET

R6 RTC_SCL

R7 PCON

R9 SD_PTC

R10 SCRES Sub CPU reset. O

R11 SCTRG "TRG" signal to the sub CPU. O

R12 SCTXS "TXS" signal to the sub CPU. O

R13 CK

R14 MICSEL

59 L_AFMUTE

56 MICMUTE

27 DCSFT

17 R_PLLSTB PLL serial strobe. (Band B) O

63 R_AFMUTE

55 PLAY

22 VTX_C

23 UTX_C

20 L_PLLSTB PLL serial strobe. (Band A) O

CI-V/CLONE UART data.

(300–38400 bps)

DSP reset control.

L=Reset.

Serial clock to the real time clock

IC.

Main power supply line control.

H= Power ON.

SD card write protect control.

H=Write protect.

Common serial clock to the D/A

converter and expander.

External microphone connection

detect.

AF output mute. (A band)

H=Mute.

MIC mute switch control.

H= Mute.

DSP clock shift control.

L=+600 Hz shifted.

RX AF mute control. (Band B)

L= Mute.

Modulation signal line switching

control.

H= Recorded audio is transmitted.

VHF band transmit circuit power

control.

H= While transmitting.

UHF band transmit circuit power

control.

H= While transmitting.

• SUB CPU (MAIN UNIT: IC303)

Ball

Line Name Description I/O

No.

O

O

O

O

O

O

I

O

O

O

O

O

O

O

1 L_REFC

2 R_REFC

7 SCRES Sub CPU reset. I

18 PLLCK PLL serial clock. O

19 PLLDATA PLL serial data. O

31 AF_SW

24 L_RMUTE

25 R_RMUTE

26 DTCS_SEL

34

MAIN_DASEL

36 MIC1 Microphone gain control. O

48 SCSCK Sub CPU clock. I

49 SCTXD Sub CPU data to the main CPU. I

50 SCRXD Main CPU data. O

51 MIC2 Microphone gain control. O

52 SCTRG "TRG" signal from the main CPU. I

53 SCTXS "TXS" signal from the main CPU. I

57 VRX_RPT

58 URX_RPT

60 CLSFT3

61 CLSFT2*

62 CLSFT1*

64 SCACK

Reference frequency control.

(Band A)

Reference frequency control.

(Band B)

AF output control.

H= AF signal is output from the ex-

ternal speaker.

AF mute control. (Band A)

L=Mute.

AF mute control. (Band B)

L=Mute.

Tone signal (CTCSS/DTCS) fi lter

switching control.

H=While sending DTCS signal.

Operating mode (FM/DV) switching control.

H= While operating in the DV

mode.

Demodulated signal polarity

switching control.

H= While operating on the VHF

band.

Demodulated signal polarity

switching control.

H= While operating on the UHF

band.

Sub CPU clock frequency shift

control.

H=Shifted.

Main CPU clock frequency shift

control.

Sub CPU "ACK" signal to the main

CPU.

O

O

O

O

O

O

O

O

O

O

O

O

*: Clock frequency shifting range.

Line name CLSFT1 CLSFT2 Shifting range

H H –1.2 kHz

Line state

4-8

H L ±0 kHz

L L +1.2 kHz

Page 19

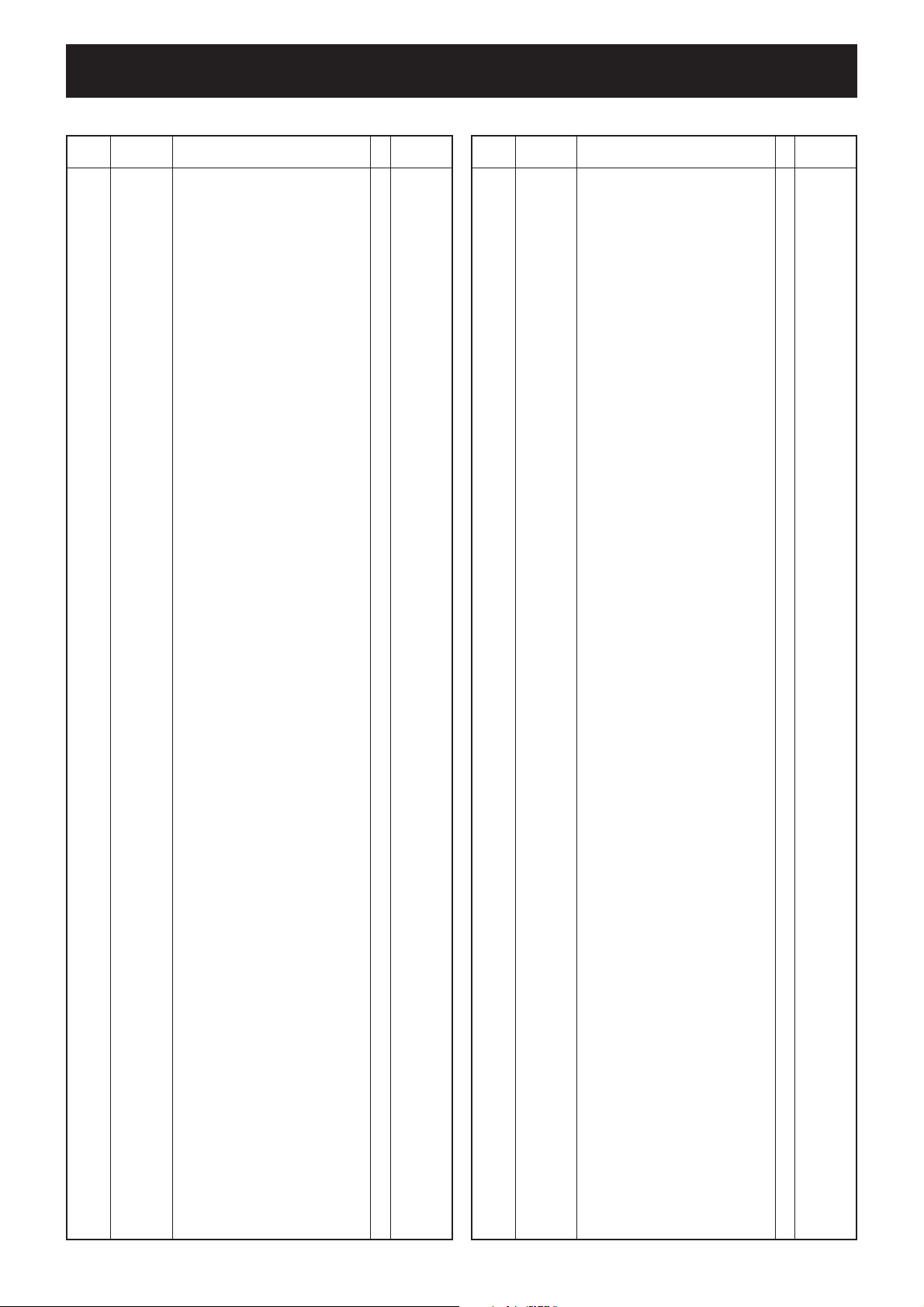

SECTION 5. ADJUSTMENT PROCEDURE

5-1 PREPARATION

M REQUIRED TEST EQUIPMENT

EQUIPMENT GRADE AND RANGE EQUIPMENT GRADE AND RANGE

Modifi ed 8-pin modular jack

(See the illustration shown below.)

Frequency range: 300–3000 Hz

Output level: 1–500 mV

Frequency range: 0.1–600 MHz

Output level: –20 to +90 dBµ

(–127 to –17 dBm)

Impedance: 50

Capacity: More than 100 W

Power attenuation: 50 dB

Capacity: More than 100 W

DC power supply

RF power meter

(terminated type)

Frequency counter

Modulation

Analyzer

Output voltage: 13.8 V DC

Current capacity: More than 20 A

Measuring range: 1–100 W

Frequency range: 100–600 MHz

Impedance: 50

SWR: Less than 1.2 : 1

Frequency range: 0.1–600 MHz

Frequency accuracy: ±1 ppm or better

Sensitivity: 100 mV or better

Frequency range: 30–600 MHz

Measuring range: DC to ±10 kHz

JIG cable

Audio generator

Standard signal

generator (SSG)

AC millivoltmeter Measuring range: 10 mV to 10 V

Terminator

Attenuator

CAUTION!:

SAVE the originally programmed contents

adjustment. When all adjustments are completed, these contents in the transceiver may be cleared.

JIG CABLE

M

JIG cable

To the MICROPHONE CONNECTOR

M CONNECTION

Standard signal generator

–20 to 90 dBµ

(–127 dBm to –17 dBm)

FM

deviation meter

Attenuator

40 dB

(Memory channel contents, set mode settings, and so on.),

8-pin modular jack

ytre

i

u

q

w

e

r

t

y

u

i

8V

MICU/D

EXTMIC

PTT

MICE

MIC

GND

MICIN

q

w

to the antenna connector

AUDIO GENERATOR

(300–3000 Hz/1–500 mV)

+−

y (MIC)

t (MICE)

22 kΩ

w (MICU/D)

u (GND)

[PTT]

r (PTT)

u (GND)

DO NOT transmit while

an SSG is connected to

the antenna connector.

before starting

AC MILLIVOLT METER

(10 mV to 10 V)

+−

RF power meter

0.1–100 W/50 Ω

Frequency

counter

ID-5100A/E (Rear view)

5-1

Page 20

ENTERING THE ADJUSTMENT MODE

M

1) Connect the JIG cable to the MICROPHONE CONNECTOR (see the illustration on page 5-1).

2) Turn Band A [SQL] maximum clockwise.

3) Set Band B [SQL] to the center position.

4) Touch and hold [QUICK], and turn ON the power.

• Enters to the adjustment mode.

2) Turn Band A [SQL] maximum clockwise.

D

N

A

B

N

I

A

M

4) Touch and hold [QUICK], then push [ ] turn ON the power.

KEY ASSIGNMENTS IN THE ADJUSTMENT MODE

M

3) Set Band B [SQL] to the center position.

Adjustment frequency.

Adjustment value.

Adjustment item name.

D

N

A

B

N

I

A

M

[ENT]

• Stores the set value.

(For the manual adjustments)

• Adjusts the value for the item.

(For the automatic adjustments)

Band A [DIAL]

Turn Clockwise : Selects the next adjustment item.

Turn Counterclockwise : Selects the previous adjustment item.

Band B [DIAL]

Adjusts the value for the item.

(For the manual adjustments)

5-2 FREQUENCY ADJUSTMENT

1) Select the adjustment item by rotating Band A [DIAL].

2) Set or modify the adjustment value as specifi ed by rotating Band B [DIAL].

3) Touch [ENT] to store the value.

ADJUSTMENT ITEM ADJUSTMENT CONDITIONS OPERATION VALUE

REFERENCE

FREQUENCY

(Band A)

(Band B) 2

[REF] 1 • Connect an RF power meter to the antenna

connector.

• Loosely couple a Frequency Counter to the

antenna connector.

• Transmitting

Rotate Band B [DIAL] to adjust

the transmit frequency, and then

touch [ENT] during transmit.

Displayed

frequency

(±200 Hz)

5-2

Page 21

5-3 TRANSMIT ADJUSTMENTS

M TRANSMIT OUTPUT POWER ADJUSTMENTS

1) Select the adjustment item by rotating Band A [DIAL].

2) Set or modify the adjustment value as specifi ed, by rotating Band B [DIAL].

3) Touch [ENT] to store the value.

ADJUSTMENT ITEM

144 MHz BAND

TRANSMIT OUTPUT POWER

(HIGH POWER)

(MID POWER) (Band Low)

(LOW POWER) (Band Low)

430 MHz BAND

TRANSMIT OUTPUT POWER

(HIGH POWER)

(MID POWER) (Band Low)

(LOW POWER) (Band Low)

(Band Low)

[PHL]

(Band High)

[PHH]

[PML]

(Band High)

[PMH]

[PLL]

(Band High)

[PLH]

(Band Low)

[PHL]

(Band High)

[PHH]

[PML]

(Band High)

[PMH]

[PLL]

(Band High)

[PLH]

ADJUSTMENT

CONDITIONS

1• Connect an RF power

meter to the antenna

connector.

2

• Transmitting

3 15 W

4

55 W

6

1• Connect an RF power

meter to the antenna

connector.

2

• Transmitting

3 15 W

4

55 W

6

Rotate Band B [DIAL] to ad-

just the transmit output power,

and then touch [ENT] during

transmit.

Rotate Band B [DIAL] to ad-

just the transmit output power,

and then touch [ENT] during

transmit.

OPERATION VALUE

50 W

(Except

[TPE])

22 W

([TPE])

50 W

(Except

[TPE])

22 W

([TPE])

5-3

Page 22

M DEVIATION ADJUSTMENTS

1) Select the adjustment item by rotating Band A [DIAL].

2) Set or modify the adjustment value as specifi ed, by rotating Band B [DIAL].

3) Touch [ENT] to store the value.

ADJUSTMENT ITEM

144 MHz Band

FM DEVIATION

(Band A)

430 MHz Band

FM DEVIATION

(Band B)

144 MHz Band

FM MODULATION

BALANCE

(Band A)

430 MHz Band

FM MODULATION

BALANCE

(Band B)

(Band Low) (FM)

[FMS]

(FM-N)

[FMS]

(Band Center)

(Band High) (FM)

(Band Low) (FM)

(Band Center)

(Band High) (FM)

(Band Low) (FM)

(Band Center)

(Band High) (FM)

(Band Low) (FM)

(Band Center)

(Band High) (FM)

(FM)

[FMS]

(FM-N)

[FMS]

[FMS]

(FM-N)

[FMS]

[FMS]

(FM-N)

[FMS]

(FM)

[FMS]

(FM-N)

[FMS]

[FMS]

(FM-N)

[FMS]

[FMB]

(FM-N)

[FMB]

(FM)

[FMB]

(FM-N)

[FMB]

[FMB]

(FM-N)

[FMB]

[FMB]

(FM-N)

[FMB]

(FM)

[FMB]

(FM-N)

[FMB]

[FMB]

(FM-N)

[FMB]

ADJUSTMENT

CONDITIONS

1• Connect a modulation

analyzer with an oscilloscope to the antenna

2 ±2.1 kHz

connector, through an

attenuator, and set it as:

3 ±4.2 kHz

HPF: OFF

LPF: 20 kHz

4 ±2.1 kHz

De-emphasis: OFF

Detector: (P–P)/2

• Connect an audio gen-

5 ±4.2 kHz

erator to the [MIC] jack,

and set it as:

6 ±2.1 kHz

Frequency: 1 kHz

Level:

80 mV rms (For [USA])

1 ±4.2 kHz

20 mV rms (Except [USA])

• Transmitting

2 ±2.1 kHz

3 ±4.2 kHz

4 ±2.1 kHz

5 ±4.2 kHz

6 ±2.1 kHz

1• Connect a modulation

analyzer with an oscilloscope to the antenna

2 ±2.1 kHz

connector, through an

attenuator, and set as:

3 ±4.2 kHz

HPF: OFF

LPF: 20 kHz

4 ±2.1 kHz

De-emphasis: OFF

Detector: (P–P)/2

• No audio applied.

5 ±4.2 kHz

• Transmitting

6 ±2.1 kHz

1 ±4.2 kHz

2 ±2.1 kHz

3 ±4.2 kHz

4 ±2.1 kHz

5 ±4.2 kHz

6 ±2.1 kHz

Rotate Band B [DIAL] to adjust the deviation, and then

touch [ENT] during transmit.

Rotate Band B [DIAL] to adjust the deviation, and then

touch [ENT] during transmit.

OPERATION VALUE

±4.2 kHz

±4.2 kHz

5-4

Page 23

M DEVIATION ADJUSTMENT (continued)

1) Select the adjustment item by rotating Band A [DIAL].

2) Set or modify the adjustment value as specifi ed, by rotating Band B [DIAL].

3) Touch [ENT] to store the value.

ADJUSTMENT ITEM

144 MHz Band

DV DEVIATION

144 MHz Band

DV MODULATION BALANCE

430 MHz Band

DV DEVIATION

430 MHz Band

DV MODULATION BALANCE

144 MHz Band

CTCSS DEVIATION

430 MHz Band

CTCSS DEVIATION

144 MHz Band

DTCS DEVIATION

430 MHz Band

DTCS DEVIATION

(Band Low)

[MDS]

(Band Center)

[MDS]

(Band High)

[MDS]

(Band Low)

[MDB]

(Band Center)

[MDB]

(Band High)

[MDB]

(Band Low)

[MDS]

(Band Center)

[MDS]

(Band High)

[MDS]

(Band Low)

[MDB]

(Band Center)

[MDB]

(Band High)

[MDB]

(FM)

[MCT]

(FM-N)

[MCT]

(FM)

[MCT]

(FM-N)

[MCT]

(FM)

[MDT]

(FM-N)

[MDT]

(FM)

[MDT]

(FM-N)

[MDT]

1• Connect a modulation

2

3

1 Minimum

2

3

1 ±1.05 kHz

2

3

1 Minimum

2

3

1• Connect a modulation

2 (Set the

1 ±0.75 kHz

2 (Set the

1 ±0.75 kHz

2 (Set the

1 ±0.75 kHz

2 (Set the

ADJUSTMENT

CONDITIONS

analyzer with an oscilloscope to the antenna

connector, through an

attenuator, and set it as:

HPF: OFF

LPF: 20 kHz

De-emphasis: OFF

Detector: (P–P)/2

• No audio applied.

• Transmitting

analyzer with an oscilloscope to the antenna

connector, through an

attenuator, and set it as:

HPF: OFF

LPF: 20 kHz

De-emphasis: OFF

Detector: (P–P)/2

• No audio applied.

• Transmitting

Rotate Band B [DIAL] to adjust the deviation, and then

touch [ENT] during transmit.

Rotate Band B [DIAL] to adjust the deviation, and then

touch [ENT] during transmit.

OPERATION VALUE

±1.05 kHz

deviation

deviation

±0.75 kHz

same value

as the FM

mode.)

same value

as the FM

mode.)

same value

as the FM

mode.)

same value

as the FM

mode.)

5-5

Page 24

5-4 RECEIVE ADJUSTMENTS

M RECEIVE SENSITIVITY ADJUSTMENT

1) Select the adjustment item by rotating Band A [DIAL].

2) Set or modify the adjustment value as specifi ed, by rotating Band B [DIAL].

3) Touch [ENT] to store the value.

ADJUSTMENT ITEM ADJUSTMENT CONDITIONS OPERATION VALUE

SENSITIVITY • Connect a Standard Signal Generator to the antenna connector.

118.020 MHz (Band A)

[LT1]

(Band B)

[LT1]

146.020 MHz (Band A)

[MT1]

(Band B)

[MT1]

173.980 MHz (Band A)

[HT1]

(Band B)

[HT1]

375.020 MHz (Band A)

[LT4]

(Band B)

[LT4]

420.020 MHz (Band A)

[MT4]

(Band B)

[MT4]

449.980 MHz (Band A)

[HT4]

(Band B)

[HT4]

450.020 MHz (Band A)

[LT5]

(Band B)

[LT5]

500.020 MHz (Band A)

[MT5]

(Band B)

[MT5]

549.980 MHz (Band A)

[HT5]

(Band B)

[HT5]

1 Set the SSG as:

Frequency: (Displayed)

Modulation: None

2

Level: 0 dBµ (–107 dBm)

3 Set the SSG as:

Frequency: (Displayed)

Modulation: None

4

Level: 0 dBµ (–107 dBm)

5 Set the SSG as:

Frequency: (Displayed)

Modulation: None

6

Level: 0 dBµ (–107 dBm)

7 Set the SSG as:

Frequency: (Displayed)

Modulation: None

8

Level: 0 dBµ (–107 dBm)

9 Set the SSG as:

Frequency: (Displayed)

Modulation: None

10

Level: 0 dBµ (–107 dBm)

11 Set the SSG as:

Frequency: (Displayed)

Modulation: None

12

Level: 0 dBµ (–107 dBm)

13 Set the SSG as:

Frequency: (Displayed)

Modulation: None

14

Level: 0 dBµ (–107 dBm)

15 Set the SSG as:

Frequency: (Displayed)

Modulation: None

16

Level: 0 dBµ (–107 dBm)

17 Set the SSG as:

Frequency: (Displayed)

Modulation: None

18

Level: 0 dBµ (–107 dBm)

Touch [ENT].

(Automatic

adjustment)

5-6

Page 25

M S-METER ADJUSTMENT

1) Select the adjustment item by rotating Band A [DIAL].

2) Confi gure the SSG setting as specifi ed.

3) Touch [ENT] to automatically adjust and store the value.

ADJUSTMENT ITEM

S-METER

127.020 MHz

145.020 MHz Band A (FM) [S12] 7 Set the SSG as:

387.020 MHz Band A (FM) [S13] 13 Set the SSG as:

435.020 MHz*

445.020 MHz**

500.020 MHz Band A (FM) [S15] 25 Set the SSG as:

• Connect a Standard Signal Generator to the antenna connector.

Band A (AM) [S11] 1 Set the SSG as:

Band B (AM) [S11] 2

Band A (AM) [S31] 3 Set the SSG as:

Band B (AM) [S31] 4

Band A (AM) [SF1] 5 Set the SSG as:

Band B (AM) [SF1] 6

Band B (FM) [S12] 8

Band A (FM) [S32] 9 Set the SSG as:

Band B (FM) [S32] 10

Band A (FM) [SF2] 11 Set the SSG as:

Band B (FM) [SF2] 12

Band B (FM) [S13] 14

Band A (FM) [S33] 15 Set the SSG as:

Band B (FM) [S33] 16

Band A (FM) [SF3] 17 Set the SSG as:

Band B (FM) [SF3] 18

Band A (FM) [S14] 19 Set the SSG as:

Band B (FM) [S14] 20

Band A (FM) [S34] 21 Set the SSG as:

Band B (FM) [S34] 22

Band A (FM) [SF4] 23 Set the SSG as:

Band B (FM) [SF4] 24

Band B (FM) [S15] 26

Band A (FM) [S35] 27 Set the SSG as:

Band B (FM) [S35] 28

Band A (FM) [SF5] 29 Set the SSG as:

Band B (FM) [SF5] 30

Frequency: (Displayed)

Modulation: None

Level:

Level: 0 dBµ (–107 dBm)

Level:

Frequency: (Displayed)

Modulation: None

Level:

Level: 0 dBµ (–107 dBm)

Level:

Frequency: (Displayed)

Modulation: None

Level:

Level: 0 dBµ (–107 dBm)

Level:

Frequency: (Displayed)

Modulation: None

Level:

Level: 0 dBµ (–107 dBm)

Level:

Frequency: (Displayed)

Modulation: None

Level:

Level: 0 dBµ (–107 dBm)

Level:

ADJUSTMENT

CONDITIONS

–6 dBµ (–113 dBm)

+10 dBµ (–97 dBm)

–6 dBµ (–113 dBm)

+10 dBµ (–97 dBm)

–6 dBµ (–113 dBm)

+10 dBµ (–97 dBm)

–6 dBµ (–113 dBm)

+10 dBµ (–97 dBm)

–6 dBµ (–113 dBm)

+10 dBµ (–97 dBm)

OPERATION VALUE

Touch [ENT].

(Automatic

adjustment)

5-7

Page 26

M SQUELCH ADJUSTMENT

1) Select the adjustment item by rotating Band A [DIAL].

2) Touch [ENT] to automatically adjust and store the value.

ADJUSTMENT ITEM OPERATION VALUE

SQUELCH • Connect a Terminator (50 ) to the antenna connector, to block any RF signal.

127.020 MHz (AM) [SQ1] 1

(AM) [SQ1] 2

(AM-N) [SQ1] 3

(AM-N) [SQ1] 4

145.020 MHz (FM) [SQ2] 7

(FM) [SQ2] 8

(FM-N) [SQ2] 9

(FM-N) [SQ2] 10

387.020 MHz (FM) [SQ3] 13

(FM) [SQ3] 14

(FM-N) [SQ3] 15

(FM-N) [SQ3] 16

435.020 MHz (FM) [SQ4] 19

(FM) [SQ4] 20

(FM-N) [SQ4] 21

(FM-N) [SQ4] 22

500.020 MHz (FM) [SQ5] 25

(FM) [R SQ5] 26

(FM-N) [L SQ5] 27

(FM-N) [R SQ5] 28

Touch [ENT].

(Automatic

adjustment)

5-8

Page 27

SECTION 6. PARTS LIST

[CONTROL UNIT]

REF PARTS

NO. NO.

IC2 1140016220 S.IC STM32F101VFT6 <TOMEN> B 84.3/89.3

IC6 1180003480 S.REG NJU7772F33-TE1-#ZZZB T 21.1/39.1

IC7 1110006490 S.IC LMV321IDCKR B 95.4/32.0

IC8 1130017190 S.IC UC6528XBNQ4GRC <GOS> B 27.1/45.0

Q3 1530002851 S.TRA 2SC4116-BL(TE85RF) B 95.9/28.2

Q6 1590004040 S.TRA LDTA123YET1G <SLVJ> B 82.9/43.4

D1 1750001820 S.DIO LRB706F-40T1G <SLVJ> T 23.2/35.9

D2 1750001820 S.DIO LRB706F-40T1G <SLVJ> T 20.7/35.9

D3 1750001810 S.DIO L1SS400T1G <SLVJ> B 87.7/43.2

D4 1750001810 S.DIO L1SS400T1G <SLVJ> B 69.2/29.7

D5 1750001810 S.DIO L1SS400T1G <SLVJ> B 44.1/27.6

X1 6050013180 S.XTA CR-910(HC-49US/9.8304 MHz)

<JJE> T 50.5/4.3

R1 7210003660 VAR R09461GO-FF17S5.0-B504

<EVT>

R2 7210003660 VAR R09461GO-FF17S5.0-B504

<EVT>

R3 7510001770 S.THE NTCG10 4LH 473JT T 92.8/29.9

R4 7030007350 S.RES ERJ2GEJ 393 X (39K) T 93.7/28.3

R5 7030005240 S.RES ERJ2GEJ 473 X (47K) T 60.9/22.3

R6 7030005240 S.RES ERJ2GEJ 473 X (47K) T 60.9/23.2

R7 7030005240 S.RES ERJ2GEJ 473 X (47K) T 61.3/15.5

R11 7030005530 S.RES ERJ2GEJ 100 X (10) T 29.6/7.3

R14 7030005530 S.RES ERJ2GEJ 100 X (10) T 57.0/61.4

R16 7410000720 S.ARR EXB-V8V 473JV (47K) B 32.8/5.5

R18 7410001130 S.ARR EXB28V102JX B 52.2/13.3

R19 7030005160 S.RES ERJ2GEJ 105 X (1M) T 50.7/7.4

R20 7030010040 S.RES ERJ2GEJ-JPW T 51.2/8.3

R21 7030005530 S.RES ERJ2GEJ 100 X (10) T 56.0/7.8

R27 7030005050 S.RES ERJ2GEJ 103 X (10K) T 28.0/35.0

R33 7030005240 S.RES ERJ2GEJ 473 X (47K) B 93.9/34.3

R34 7030005050 S.RES ERJ2GEJ 103 X (10K) B 97.2/33.6

R36 7030005040 S.RES ERJ2GEJ 472 X (4.7K) B 97.2/32.0

R37 7030005050 S.RES ERJ2GEJ 103 X (10K) B 95.7/30.1

R39 7030005530 S.RES ERJ2GEJ 100 X (10) B 98.0/29.1

R44 7030005090 S.RES ERJ2GEJ 104 X (100K) T 50.0/28.2

R47 7030010040 S.RES ERJ2GEJ-JPW B 60.9/13.4

R50 7030010040 S.RES ERJ2GEJ-JPW T 53.7/61.2

R51 7030010040 S.RES ERJ2GEJ-JPW B 81.5/45.8

R52 7030005120 S.RES ERJ2GEJ 102 X (1K) T 18.7/36.1

R53 7030005120 S.RES ERJ2GEJ 102 X (1K) T 18.7/37.0

R56 7030005240 S.RES ERJ2GEJ 473 X (47K) T 51.0/28.2

R58 7410000720 S.ARR EXB-V8V 473JV (47K) B 45.3/10.7

R59 7030005240 S.RES ERJ2GEJ 473 X (47K) T 31.6/8.5

R63 7030005240 S.RES ERJ2GEJ 473 X (47K) T 30.5/9.9

R67 7030005240 S.RES ERJ2GEJ 473 X (47K) T 55.8/62.6

R68 7030005090 S.RES ERJ2GEJ 104 X (100K) T 55.8/61.7

R69 7030005240 S.RES ERJ2GEJ 473 X (47K) T 52.1/62.6

R70 7030005090 S.RES ERJ2GEJ 104 X (100K) T 55.8/60.8

R71 7030005240 S.RES ERJ2GEJ 473 X (47K) B 95.1/34.7

R72 7030005240 S.RES ERJ2GEJ 473 X (47K) B 70.5/30.0

R73 7030005240 S.RES ERJ2GEJ 473 X (47K) B 44.9/30.0

R74 7030003860 S.RES ERJ3GE JPW V T 16.2/34.6

C1 4030016790 S.CER C1005 JB 1E 103K-T T 72.1/41.2

C2 4030016930 S.CER C1005 JB 1A 104K-T T 57.5/62.6

C3 4030016930 S.CER C1005 JB 1A 104K-T T 92.8/28.3

C4 4030017460 S.CER C1005 JB 1H 102K-T T 167.7/39.8

C10 4030016790 S.CER C1005 JB 1E 103K-T T 30.5/8.5

C15 4030016790 S.CER C1005 JB 1E 103K-T B 84.4/43.2

C16 4030017780 S.CER C1005 JB 1H 472K-T B 50.9/10.4

C17 4030017780 S.CER C1005 JB 1H 472K-T B 51.8/10.4

C18 4030017650 S.CER C1005 CH 1H 270J-T T 49.1/7.4

C19 4030017650 S.CER C1005 CH 1H 270J-T T 52.3/7.4

C20 4030017780 S.CER C1005 JB 1H 472K-T B 52.7/10.4

C21 4030017780 S.CER C1005 JB 1H 472K-T B 53.6/10.4

C22 4030019560 S.CER GRM21BB31C106KE15L T 58.2/6.5

C23 4030016790 S.CER C1005 JB 1E 103K-T T 54.8/7.4

C24 4030017460 S.CER C1005 JB 1H 102K-T B 87.3/44.3

C25 4030019560 S.CER GRM21BB31C106KE15L T 58.2/8.3

C27 4030016930 S.CER C1005 JB 1A 104K-T T 49.3/8.3

C28 4030016790 S.CER C1005 JB 1E 103K-T T 54.8/8.3

C29 4030016930 S.CER C1005 JB 1A 104K-T T 42.6/10.6

C32 4030019560 S.CER GRM21BB31C106KE15L T 45.4/29.2

C34 4030016930 S.CER C1005 JB 1A 104K-T T 60.5/12.9

C36 4030017460 S.CER C1005 JB 1H 102K-T B 85.3/43.2

C37 4030016930 S.CER C1005 JB 1A 104K-T T 60.5/24.5

C38 4030016930 S.CER C1005 JB 1A 104K-T T 44.5/27.8

C39 4030017460 S.CER C1005 JB 1H 102K-T T 29.4/38.5

C40 4030020000 S.CER C1005 JB 1A 105K-T T 21.8/41.3

C41 4030017040 S.CER C1005 JB 1A 333K-T T 26.7/39.3

C42 4030019560 S.CER GRM21BB31C106KE15L T 18.4/39.1

C45 4030020000 S.CER C1005 JB 1A 105K-T B 95.1/33.8

C46 4030017440 S.CER C1005 CH 1H 221J-T T 18.9/34.9

C57 4030016790 S.CER C1005 JB 1E 103K-T B 93.7/31.5

C58 4030017440 S.CER C1005 CH 1H 221J-T T 18.0/34.9

C71 4030016930 S.CER C1005 JB 1A 104K-T B 30.1/46.4

C72 4030016930 S.CER C1005 JB 1A 104K-T B 24.2/43.5

C73 4030021580 S.CER GRM188B31E225KA12D T 77.2/21.4

DESCRIPTION

Eqv.= This component is equivalent to the REF No. component listed above, and

may be substituted on parts orders and repairs.

M.

H/V

LOCATION

[CONTROL UNIT]

REF PARTS

NO. NO.

C74 4030021580 S.CER GRM188B31E225KA12D T 77.8/25.8

C75 4030021580 S.CER GRM188B31E225KA12D T 76.2/29.3

C76 4030021580 S.CER GRM188B31E225KA12D T 80.4/21.4

C77 4030021580 S.CER GRM188B31E225KA12D T 82.5/21.4

C78 4030021580 S.CER GRM188B31E225KA12D T 83.1/25.8

C79 4030021580 S.CER GRM188B31E225KA12D T 88.0/20.5

C80 4030021580 S.CER GRM188B31E225KA12D T 84.6/29.3

C81 4030021580 S.CER GRM188B31E225KA12D T 88.0/22.6

C82 4030021580 S.CER GRM188B31E225KA12D T 88.0/24.7

C83 4030021580 S.CER GRM188B31E225KA12D T 82.5/29.3

C84 4030021580 S.CER GRM188B31E225KA12D T 80.4/29.3

C85 4030021580 S.CER GRM188B31E225KA12D T 78.3/29.3

C86 4030021580 S.CER GRM188B31E225KA12D T 86.7/30.1

C87 4030021580 S.CER GRM188B31E225KA12D T 88.8/30.1

C88 4030021580 S.CER GRM188B31E225KA12D T 88.0/26.8

J1 6510027710 S.CON S5B-ZR-SM4A-TF(LF)(SN) T 54.0/67.9

J2 6510028740 S.CON 14FLH-SM1-TB(LF)(SN) T 32.8/2.8

J3 6510028880 S.CON 04-6238-010-410-800 B 86.1/46.9

J5 6510030110 S.CON IMSA-9681S-38Y901 B 86.7/24.2

J6 6450002260 CON 6606A-B11G ROHS <KTC>

J7 6510030080 S.CON IMSA-9632S-04Y800 B 20.0/46.2

DS1 5030003870 LCD JIC-MSGF013343-01 <RYOYO>

S4 2250000880 ENC EC12E2420801

S5 2250000880 ENC EC12E2420801

S6 2260002740 S.SWI LS8J2M-T T 168.6/35.5

S7 2260002740 S.SWI LS8J2M-T B 28.2/35.5

W1 8910000210 FFC FFC-1026 (P0.5N10L80) <TJM>

EP1 6910024590 E.O WT5039-E <SKD>

EP2 6910018460 S.BEA MMZ1005Y102C-T T 44.1/30.8

EP3 6910018460 S.BEA MMZ1005Y102C-T T 15.7/32.6

EP5 6910012350 S.BEA MMZ1608Y 102BT T 16.2/35.8

EP6 6910012350 S.BEA MMZ1608Y 102BT T 16.2/37.0

EP7 6910012350 S.BEA MMZ1608Y 102BT T 16.2/38.2

EP8 6910018460 S.BEA MMZ1005Y102C-T B 25.5/33.0

EP9 6910018460 S.BEA MMZ1005Y102C-T B 93.7/29.9

EP10 6910018460 S.BEA MMZ1005Y102C-T B 92.8/29.9

EP11 6910018460 S.BEA MMZ1005Y102C-T B 88.2/27.2

EP12 6910018460 S.BEA MMZ1005Y102C-T T 22.3/42.8

EP13 6910024430 E.O GPS-123B-077

DESCRIPTION

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

6-1

M.

S.=Surface mount

H/V

LOCATION

Page 28

[MAIN UNIT]

REF PARTS

NO. NO.

IC2 1110003800 S.IC NJM2904V-TE1-#FMZB T 50.8/18.0

IC3 1150002423 IC RA60H1317M1A-222

IC4 1150002400 IC RA60H4047M1-121

IC100 1130015760 S.IC TC74VHC4066AFK(EK) T 66.6/20.7

IC101 1110006490 S.IC LMV321IDCKR T 74.8/17.4

IC102 1130017510 S.IC NJM2741F-TE1-#ZZZB T 80.3/25.0

IC103 1110007920 S.IC SC-1445-E2 T 114.3/19.3

IC104 1130015760 S.IC TC74VHC4066AFK(EK) T 89.7/27.1

IC105 1110003091 IC LA4425A-E

IC106 1110003091 IC LA4425A-E

IC107 1110006490 S.IC LMV321IDCKR T 113.2/109.3

IC108 1130013010 S.IC SN74AHC1G08DCK3 T 129.0/110.8

IC109 1130015760 S.IC TC74VHC4066AFK(EK) T 118.2/112.9

IC110 1110007200 S.IC M61545AFP#DF0R T 107.4/111.7

IC111 1130015760 S.IC TC74VHC4066AFK(EK) T 102.4/111.6

IC112 1130007021 S.IC TC7S66FU(TE85LF) T 103.2/26.3

IC113 1130015760 S.IC TC74VHC4066AFK(EK) T 109.0/42.5

IC117 1110006740 S.IC LMV358IPWR T 97.4/44.2

IC119 1130015760 S.IC TC74VHC4066AFK(EK) B 28.5/23.9

IC120 1110007300 S.IC NJM2552V-TE1-#ZZZB T 9.3/57.7

IC121 1110007300 S.IC NJM2552V-TE1-#ZZZB T 50.3/57.7

IC122 1110006490 S.IC LMV321IDCKR T 7.1/27.5

IC123 1110006490 S.IC LMV321IDCKR T 50.0/27.9

IC124 1190003780 S.IC SMA5101-TL-H T 9.5/101.5

IC125 1190003780 S.IC SMA5101-TL-H T 49.1/101.5

IC200 1130013640 S.IC TC74VHCT125AFK(EK) B 95.4/29.1

IC201 1140005991 S.IC MB15A02PFV1-G-BND-ERE1 B 69.2/36.7

IC202 1130007021 S.IC TC7S66FU(TE85LF) T 75.3/33.3

IC203 1110008530 S.IC BGA2869115 <RYO> T 65.3/77.0

IC205 1130015760 S.IC TC74VHC4066AFK(EK) T 43.0/35.2

IC206 1140005991 S.IC MB15A02PFV1-G-BND-ERE1 B 28.5/35.0

IC207 1130007021 S.IC TC7S66FU(TE85LF) T 33.9/32.7

IC208 1110008530 S.IC BGA2869115 <RYO> T 24.3/77.0

IC300 1140017162 S.IC R5F56106WNBG(DX-3484A-2) B 109.2/80.1

IC301 1140016690 S.IC M24M02-DRMN6TP-HF T 108.8/75.5

IC302 1130015740 S.IC S-35390A-I8T1G T 99.2/77.2

IC303 1140015231 S.IC R4F20102NFA U1(EMPTY) B 103.2/45.2

IC304 1130017182 S.IC RMLV0416EGBG-4S2 B 98.4/82.3

IC305 1180003980 S.REG XC6221A332MR-G B 114.6/32.0

IC306 1180003980 S.REG XC6221A332MR-G B 124.4/33.0

IC307 1110006490 S.IC LMV321IDCKR T 120.7/30.8

IC308 1110007820 S.IC S-80929CNPF-G8ZTFG T 117.6/83.8

IC309 6910022360 S.DC TPS62110RSAR B 126.6/108.8

IC310 1190002500 S.IC ZXCT1022E5TA B 84.6/113.7

IC311 1180003980 S.REG XC6221A332MR-G B 110.0/99.8

IC312 1130014260 S.IC SN74LVC2GU04DCKR T 125.2/102.3

IC313 1180004410 S.REG NJM2835DL1-08-TE1-#ZZZB B 94.9/132.9

IC314 1180003980 S.REG XC6221A332MR-G T 106.7/93.7

IC315 1130011760 S.IC CD4094BPWR T 15.9/18.3

IC316 1130011760 S.IC CD4094BPWR T 15.9/24.9

IC317 1130011760 S.IC CD4094BPWR T 15.9/31.5

IC318 1120003020 S.IC MAX3221IPWR T 101.5/138.7

IC319 1180003470 S.REG NJM2835DL1-05-TE1-#ZZZB T 113.1/101.7

IC320 1110007620 S.IC NJU7704F3-42A-TE1-#ZZZB T 105.8/130.1

IC321 1180004410 S.REG NJM2835DL1-08-TE1-#ZZZB B 107.4/132.9

IC323 1180003920 S.REG XC6222D421MR-G T 104.8/98.4

IC324 1110007620 S.IC NJU7704F3-42A-TE1-#ZZZB T 109.2/131.8

IC400 1140016370 S.IC TMS320C5517AZCHA20 T 122.4/60.4

IC401 1130015620 S.IC EN25Q40-100GIP <MSK> B 127.0/61.5

IC402 1110007770 S.IC PCM3008T/2K B 106.6/62.1

IC403 1180003980 S.REG XC6221A332MR-G T 108.9/53.1

IC404 1180004480 S.REG XC6221A142MR-G T 118.6/51.6

IC405 1110008210 S.IC OPA356AIDBVR T 111.3/62.3

IC406 1110006470 S.IC LMV324IPWR T 98.5/54.6

IC407 1110006470 S.IC LMV324IPWR T 97.9/66.0

Q1 1590004070 S.TRA LDTC144EET1G <SLVJ> T 29.3/111.0

Q2 1590004070 S.TRA LDTC144EET1G <SLVJ> T 43.4/117.9

Q5 1590004070 S.TRA LDTC144EET1G <SLVJ> T 29.3/113.1

Q6 1590004070 S.TRA LDTC144EET1G <SLVJ> T 43.4/112.1

Q8 1590005220 S.TRA LDTA114YET1G <SLVJ> T 27.0/107.8

Q9 1590005220 S.TRA LDTA114YET1G <SLVJ> T 45.7/114.5

Q10 1590005220 S.TRA LDTA114YET1G <SLVJ> T 27.0/110.7

Q11 1590005220 S.TRA LDTA114YET1G <SLVJ> T 45.7/117.4

Q14 1590005220 S.TRA LDTA114YET1G <SLVJ> T 27.0/113.6

Q15 1590005220 S.TRA LDTA114YET1G <SLVJ> T 45.7/111.6

Q17 1580000731 S.FET 3SK293(TE85LF) T 11.0/121.5

Q18 1580000731 S.FET 3SK293(TE85LF) T 54.0/118.6

Q19 1580000731 S.FET 3SK293(TE85LF) T 21.0/118.2

Q20 1580000731 S.FET 3SK293(TE85LF) T 69.0/120.2

Q21 1530003990 S.TRA 2SC4738-BL(TE85LF) T 74.8/97.7

Q22 1530003990 S.TRA 2SC4738-BL(TE85LF) T 74.7/100.5

Q23 1580000731 S.FET 3SK293(TE85LF) T 19.7/136.3

Q24 1580000731 S.FET 3SK293(TE85LF) T 63.1/138.2

Q27 1590004070 S.TRA LDTC144EET1G <SLVJ> T 79.4/67.2

Q28 1510000581 S.TRA 2SA1362-GR(TE85RF) T 76.5/65.2

Q29 1530003990 S.TRA 2SC4738-BL(TE85LF) T 88.3/129.9

Q30 1520000910 S.TRA 2SB1132L-R-AB3-R <SLVJ> T 93.1/128.0

Q31 1590004070 S.TRA LDTC144EET1G <SLVJ> T 27.3/105.8

Q32 1590004070 S.TRA LDTC144EET1G <SLVJ> T 28.6/65.0

Q33 1590004070 S.TRA LDTC144EET1G <SLVJ> T 43.4/115.0

Q34 1510000581 S.TRA 2SA1362-GR(TE85RF) T 24.2/65.2

Q36 1530004100 S.TRA MT3S20P(TE12LF) B 78.0/69.1

Q38 1530003321 S.TRA 2SC5108-Y(TE85RF) B 31.8/69.5

Q40 1530004100 S.TRA MT3S20P(TE12LF) B 84.0/74.2

Q41 1530004100 S.TRA MT3S20P(TE12LF) B 40.5/74.2

Q46 1590004050 S.TRA LDTA144EET1G <SLVJ> B 80.2/88.9

Q48 1590004050 S.TRA LDTA144EET1G <SLVJ> B 80.6/85.4

Q100 1590004070 S.TRA LDTC144EET1G <SLVJ> T 64.7/25.4

Q102 1530003990 S.TRA 2SC4738-BL(TE85LF) T 58.8/23.5

Q103 1590004070 S.TRA LDTC144EET1G <SLVJ> T 105.1/29.7

Q104 1530003091 S.TRA 2SC4213-B(TE85RF) T 126.2/117.6

Q105 1530003091 S.TRA 2SC4213-B(TE85RF) T 125.5/113.8

Q106 1530003091 S.TRA 2SC4213-B(TE85RF) T 126.2/128.0

DESCRIPTION

Eqv.= This component is equivalent to the REF No. component listed above, and

may be substituted on parts orders and repairs.

M.

H/V

LOCATION

[MAIN UNIT]

REF PARTS

NO. NO.

Q108 1590004070 S.TRA LDTC144EET1G <SLVJ> T 88.5/31.4

Q110 1590004070 S.TRA LDTC144EET1G <SLVJ> T 112.8/41.2

Q112 1590004590 S.TRA DMC506010R T 105.4/35.6

Q113 1590004590 S.TRA DMC506010R T 95.6/35.4

Q117 1590004070 S.TRA LDTC144EET1G <SLVJ> T 11.1/42.6

Q118 1590004070 S.TRA LDTC144EET1G <SLVJ> T 52.1/42.6

Q119 1590005220 S.TRA LDTA114YET1G <SLVJ> T 10.5/44.7

Q120 1590005220 S.TRA LDTA114YET1G <SLVJ> T 51.5/44.7

Q121 1590004070 S.TRA LDTC144EET1G <SLVJ> T 8.9/42.6

Q122 1590004070 S.TRA LDTC144EET1G <SLVJ> T 49.9/42.6

Q123 1590004050 S.TRA LDTA144EET1G <SLVJ> T 7.4/44.7

Q124 1590004050 S.TRA LDTA144EET1G <SLVJ> T 48.4/44.7

Q125 1590004390 S.TRA DMG504010R B 30.9/14.4

Q126 1590004390 S.TRA DMG504010R B 37.1/21.4

Q127 1590004070 S.TRA LDTC144EET1G <SLVJ> B 6.9/51.1

Q128 1590004070 S.TRA LDTC144EET1G <SLVJ> B 47.9/51.1

Q129 1590005220 S.TRA LDTA114YET1G <SLVJ> T 28.8/23.2

Q130 1590005220 S.TRA LDTA114YET1G <SLVJ> T 29.3/25.3

Q131 1590004070 S.TRA LDTC144EET1G <SLVJ> B 6.9/64.5

Q132 1590004070 S.TRA LDTC144EET1G <SLVJ> B 47.8/64.5

Q133 1530003990 S.TRA 2SC4738-BL(TE85LF) B 7.9/66.6

Q134 1530003990 S.TRA 2SC4738-BL(TE85LF) B 48.9/66.6

Q137 1530002601 S.TRA 2SC4215-O(TE85RF) T 6.9/70.0

Q138 1530002601 S.TRA 2SC4215-O(TE85RF) T 48.0/70.0

Q139 1590004090 S.TRA LDTC114YET1G <SLVJ> T 101.1/38.0

Q140 1590004090 S.TRA LDTC114YET1G <SLVJ> T 91.3/37.9

Q141 1590004070 S.TRA LDTC144EET1G <SLVJ> T 8.0/46.8

Q142 1590004070 S.TRA LDTC144EET1G <SLVJ> T 49.0/46.8

Q200 1530003990 S.TRA 2SC4738-BL(TE85LF) B 62.1/38.4

Q201 1560000541 S.FET 2SK880-Y(T5RICOMF) T 82.6/35.9

Q202 1590004070 S.TRA LDTC144EET1G <SLVJ> T 78.7/32.5

Q205 1590004070 S.TRA LDTC144EET1G <SLVJ> T 81.5/52.6

Q206 1530003990 S.TRA 2SC4738-BL(TE85LF) B 66.0/43.1

Q207 1590004070 S.TRA LDTC144EET1G <SLVJ> T 73.8/54.3

Q208 1590004070 S.TRA LDTC144EET1G <SLVJ> B 61.0/44.9

Q209 1590004070 S.TRA LDTC144EET1G <SLVJ> B 61.0/46.9

Q210 1530003582 S.TRA 2SC5231A-8-TL-E T 78.5/57.8

Q211 1530003582 S.TRA 2SC5231A-8-TL-E T 69.0/49.0

Q212 1590004580 S.TRA DMA501010R B 65.3/45.9

Q213 1530003321 S.TRA 2SC5108-Y(TE85RF) T 59.5/57.7

Q214 1530003321 S.TRA 2SC5108-Y(TE85RF) T 73.1/57.8

Q215 1530003321 S.TRA 2SC5108-Y(TE85RF) T 65.4/51.0

Q220 1530003990 S.TRA 2SC4738-BL(TE85LF) B 21.4/38.4

Q221 1560000541 S.FET 2SK880-Y(T5RICOMF) T 38.2/33.3

Q222 1590004070 S.TRA LDTC144EET1G <SLVJ> T 35.0/29.4

Q226 1530003990 S.TRA 2SC4738-BL(TE85LF) B 26.3/43.5

Q227 1590004070 S.TRA LDTC144EET1G <SLVJ> T 41.8/52.5

Q228 1590004070 S.TRA LDTC144EET1G <SLVJ> T 34.2/54.3

Q229 1590004070 S.TRA LDTC144EET1G <SLVJ> B 22.2/44.9

Q230 1590004070 S.TRA LDTC144EET1G <SLVJ> B 22.2/46.9

Q231 1590004580 S.TRA DMA501010R B 26.5/45.9

Q232 1530003582 S.TRA 2SC5231A-8-TL-E T 38.9/57.8

Q233 1530003582 S.TRA 2SC5231A-8-TL-E T 29.3/48.3

Q234 1530003321 S.TRA 2SC5108-Y(TE85RF) T 20.0/53.2

Q235 1530003321 S.TRA 2SC5108-Y(TE85RF) T 33.5/57.8

Q236 1530003321 S.TRA 2SC5108-Y(TE85RF) T 25.7/50.6

Q237 1530003582 S.TRA 2SC5231A-8-TL-E T 60.3/47.5

Q240 1590005220 S.TRA LDTA114YET1G <SLVJ> B 67.8/45.3

Q241 1590004070 S.TRA LDTC144EET1G <SLVJ> B 67.8/47.6

Q301 1590004090 S.TRA LDTC114YET1G <SLVJ> B 101.9/136.1