Page 1

VHF TRANSCEIVERS

S-14319XZ-C1

Feb. 2007

Page 2

INTRODUCTION CAUTION

This service manual describes the latest service information

for the IC-F5061/F5062/F5063 VHF TRANSCEIVERS at the

time of publication.

MODEL VERSION CHANNEL SPACING TX POWER

IC-F5061 USA-01 15.0/30.0 kHz 50 W

IC-F5062 EXP-01 12.5/25.0 kHz

IC-F5063 EUR-01 12.5/20/25.0 kHz

To upgrade quality, any electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

25 W

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 15 V. This will ruin the

transceiver.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when

connecting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW)

to the antenna connector. This could damage the transceiver’

s front end.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit Icom parts numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1110003491 S.IC TA31136FNG IC-F5061 MAIN UNIT 5 pieces

8820001210 Screw 2438 screw IC-F5062 Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

REPAIR NOTES

1. Make sure a problem is internal before disassembling

the transceiver.

2. DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn

them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An

insulated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the

transceiver is defective.

6. DO NOT transmit power into a signal generator or a

sweep generator.

7. ALWAYS connect a 50 dB to 60 dB attenuator between

the transceiver and a deviation meter or spectrum

analyzer when using such test equipment.

8. READ the instructions of test equipment thoroughly

before connecting equipment to the transceiver.

Icom, Icom Inc. and

Kingdom, Germany, France, Spain, Russia and/or other countries.

logo are registered trademarks of Icom Incorporated (Japan) in the United States, the United

Page 3

CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASSEMBLY INSTRUCTIONS

SECTION 4 OPTIONAL UNITS INSTALLATIONS

SECTION 5 CIRCUIT DESCRIPITON

5-1 RECEIVER CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5-2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5-3

5-4 POWER SUPPLY CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5-5 PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

SECTION 6 ADJUSTMENT PROCEDURES

6-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6-2 FREQUENCY ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6-3 TRANSMIT ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6-4 RECEIVE ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

FREQUENCY SYNTHESIZER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

SECTION 7 PARTS LIST

SECTION 8 MECHANICAL PARTS AND DISASSEMBLY

SECTION 9 BOARD LAYOUTS

SECTION 10 BLOCK DIAGRAM

SECTION 11 VOLTAGE DIAGRAM

SECTION 12 HM-152

Page 4

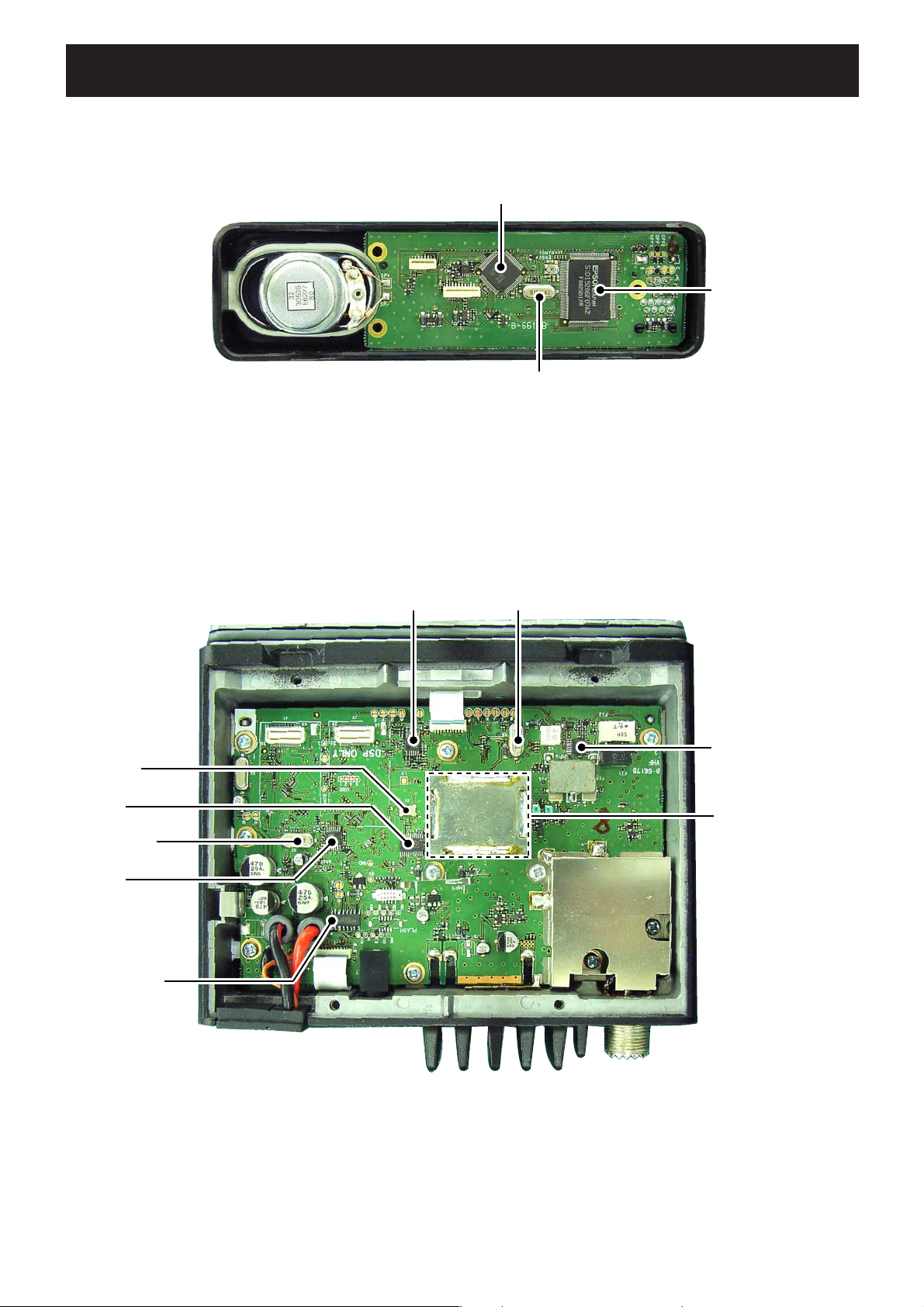

SECTION 1 SPECIFICATIONS

[USA] [EXP] [EUR]

• Frequency coverage 136–174 MHz

• Type of emission Wide 16K0F3E (25.0 kHz)

Middle – 14K0F3E (20.0 kHz)

11K0F3E (12.5 kHz)

Narrow

• Number of programable channels max. 512 channels (128 zones)

• Antenna impedance

• Operating temperature range −30˚ to +60˚; −22˚F to +140˚F –25˚C to +55˚C

• Power supply requirement

GENERAL

(negative ground)

• Current drain

(approx.)

• Dimensions (projections not included)

Stand-by 300 mA

RX

Max.audio 1200 mA

TX

at 25 W 7 A

at 50 W 14 A

8K10F1E/D (12.5 kHz)

4K00F1E/D(6.25 kHz)

50 Ω (nominal)

13.6 V DC (nominal) 13.2 V DC (nominal)

160 (W) × 45 (H) × 150 (D) mm

; 2 3/32 (W) × 4 23/32 (H) × 1 9/32 (D) in

8K50F3E (12.5 kHz)

4K00F1E/D (6.25 kHz)

• Weight (with BP-231, approx.)

• Transmit output power 50 W 25 W

• Modulation Variable reactance frequency modulation

• Max. permissible deviation Wide ±5.0 kHz

Middle – ±4.0 kHz

Narrow ±2.5 kHz

• Frequency error ±1.0 ppm ±1.5 kHz

• Spurious emission

• Adjacent channel power Wide More than 70 dB

TRANSMITTER

• Audio harmonic distortion 3% typ. (with 1 kHz AF 40% deviation)

• FM hum and noise

(without CCITT filter)

• Limiting charact of modulation 70–100% of max. deviation

• Microphone impedance 600

• Receive system Double-conversion superheterodyne

• Intermediate frequencies 1st IF; 46.35 MHz, 2nd IF; 450 kHz

• Sensitivity

• Squelch sensitivity (at threshold) 0.25 µV typ.

• Adjacent channel

selectivity

RECEIVER

• Spurious response More than 85 dB (90 dB typ.)

• Intermodulation More than 75 dB (77 dB typ.) More than 65 dB (70 dB typ.)

• Hum and noise

(without CCITT filter)

• Audio output power 4 W typ. at 10% distortion with a 4 Ω load

• Audio output impedance 4

Measurements made in accordance with EIA-152-C/204D, TIA-603 ([USA],

All stated specifications are subject to change without notice or obligation.

Middle – More than 70 dB

Narrow More than 60 dB

Wide More than 40 dB (45 dB typ.) –

Narrow More than 34 dB (40 dB typ.) –

0.25 µV typ. at 12 dB SINAD

Wide More than 80 dB (85 dB typ.)

Middle − More than 78 dB (83 dB typ.)

Narrow More than 70 dB (75 dB typ.)

Wide More than 45 dB (50 dB typ.) –

Narrow More than 40 dB (45 dB typ.) –

75 dB typ.

[EXP]) or

1310 g; 2 Ib 14 oz

0.25 µW (≤1 GHz),

1.0 µW (>1 GHz)

Ω

−4 dBµV (EMF) typ.

at 20 dB SINAD

Ω

EN 300 086 ([EUR]).

1 - 1

Page 5

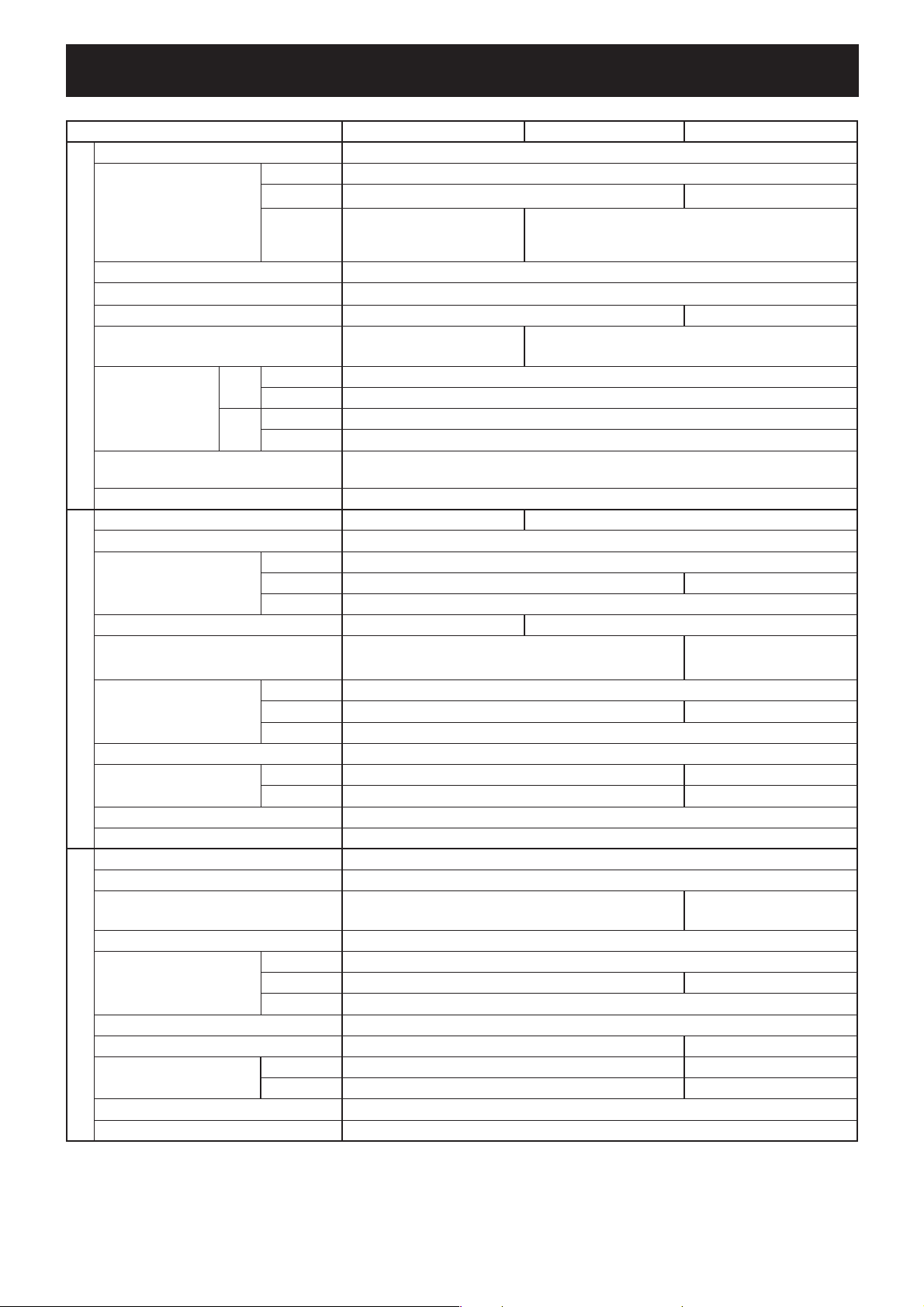

SECTION 2 INSIDE VIEWS

• FRONT UNIT

FRONT CPU

(IC503: HD64F3687)

FRONT CPU CLOCK

(X501: CR-764)

LCD DRIVER

(IC501: S1D15206F)

• MAIN UNIT

REF OSC

(X1: CR-826)

PLL IC

(IC4: LMX2352TM)

CPU CLOCK

(X5: CR-764)

AF LPF

(IC7: NJM12902V)

LEVEL CONV.

(IC19: DS14C232TM)

AF SWITCH/AMP

(IC1: NJM12902V)

BBIC CLOCK

(X2: CR-765)

IF IC

(IC170: TA31136FNG)

VCO

2 - 1

Page 6

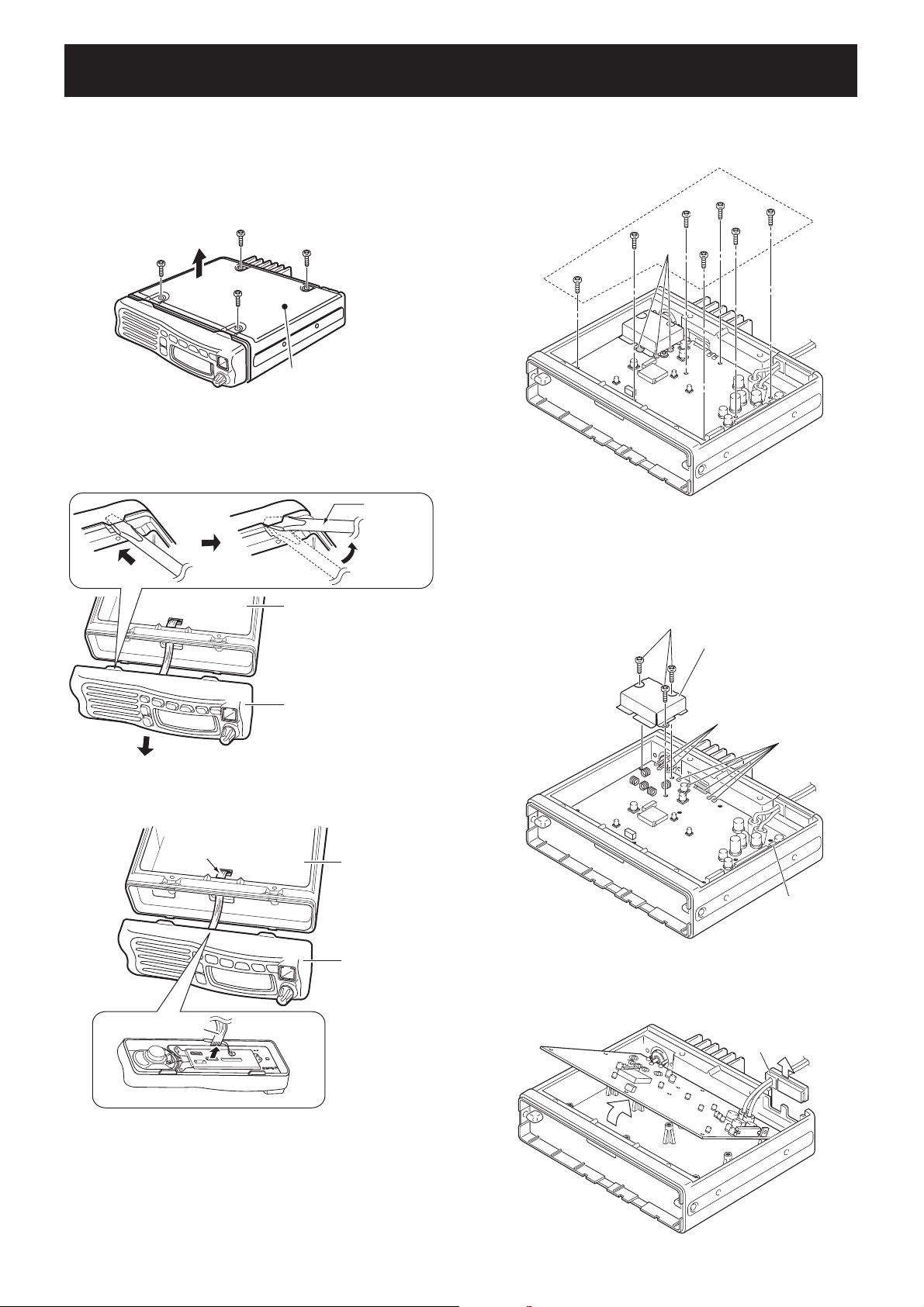

SECTION 3 DISASSEMBLY INSTRUCTION

1. Removing the front panel

q Turn the transceiver’s power OFF, then disconnect the DC

power cable

w Unscrew the 4 bottom screws, then remove the bottom

cover from the transceiver in the direction of the arrow.

Bottom cover

e Remove the front panel from the main body using a

standard cabinet screw driver as shown below.

Standard

screw driver

Main body

2. Removing the MAIN UNIT

q Unscrew 7 screws A, and unsolder 3 points B.

A

B

w Unscrew 3 screws C and remove the shield cover.

e Unsolder 3 points D (at the antenna connector) and

5 points E (at the PA module).

r Remove the clip.

C

Shield cover

Front panel

r Disconnect the flat cable from the front panel.

Flat cable

Flat cable

Front panel

Main body

Front panel

D

E

Clip

t Remove the bush, and remove the MAIN UNIT in the

direction of the arrow.

Bush

3 - 1

Page 7

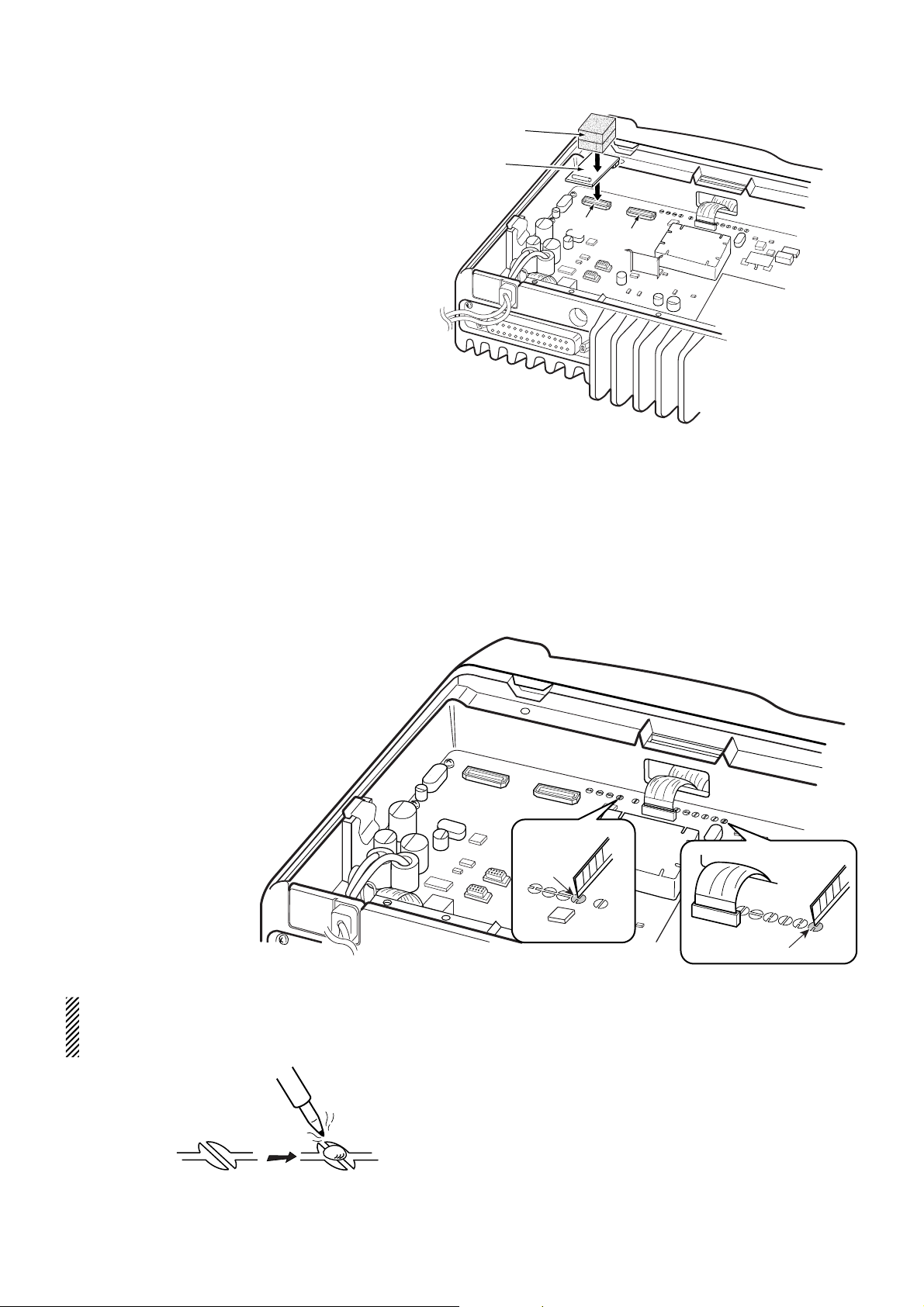

SECTION 4 OPTIONAL UNITS INSTALLATION

BEFORE INSTALLING OPTIONAL UNITS

P

A sponge with an adhesive strip has been added to optional units (UT-96R,

UT-108R, UT-109R, UT-110R, UT-119R, UT-119H, UT-124, UT-124R).

Remove the bottom protective papar, and attach the sponge to the specifi ed

position on the optional units as below.

• UT-96R • UT-108R/UT-124/UT-124R

Supplied sponge

• UT-109R/UT-110R • UT-119R

Supplied sponge

Supplied sponge

Supplied sponge

4 - 1

Page 8

Optional UT-96R or UT-119H installation

P

Install the optional UT-96R or UT-119H unit as follows:

Turn the power OFF, then disconnect the DC power cable.

q

Unscrew the 4 cover screws, then remove the bottom cover.

w

Install the UT-96R to J1 and the UT-119H to J2 as shown

e

in the diagram below.

Remove the protective paper from the supplied sponge,

r

then attach it on the installed unit.

Replace the bottom cover and screws, then re-connect

t

the DC power cable.

Sponge

UT-96R

J1

J2

*This illustration describes the UT-96R installation.

Front panel

Optional UT-109R or UT-110R installation

P

Turn the power OFF, then disconne ct the DC power cable.

q

Unscrew the 4 cover screws, then remove the bottom cover.

w

Cut the pattern on the PCB at the A (MIC) and B (AF OUT)

e

as shown below.

Install the scrambler unit to J1 as described in the instal-

r

lation of optional UT-96R installation as above.

Remove the protective paper from the supplied sponge,

t

then attach it on the installed unit.

Replace the bottom cover and screws.

y

Front panel

A

B

NOTE: When uninstalling the unit

Be sure to re-solder the disconnected points as below

when you remove the unit. Otherwise no TX modulation or

AF output is available.

Re-solder

4 - 2

Page 9

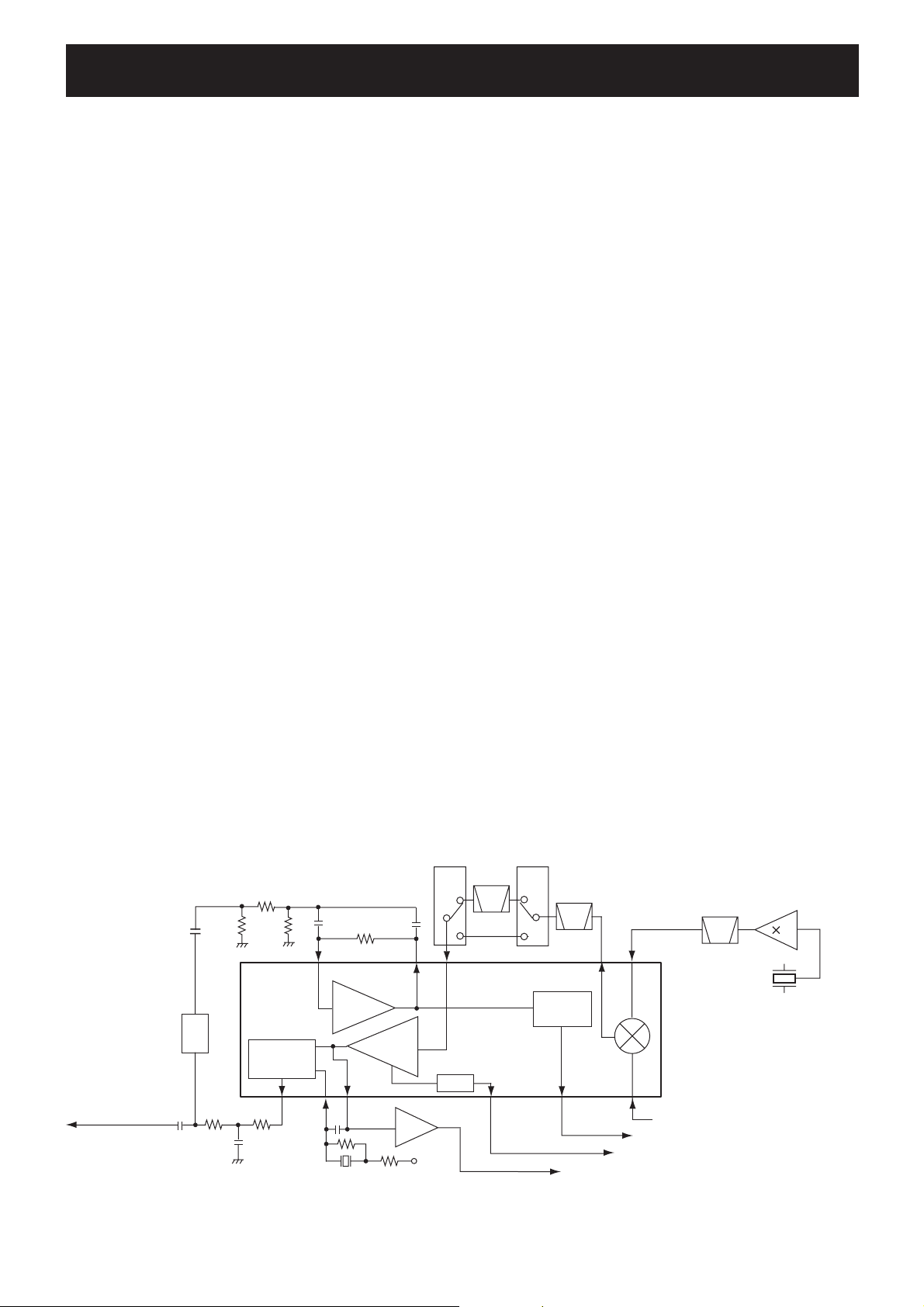

SECTION 5 CIRCUIT DESCRIPTION

5-1 RECEIVER CIRCUITS

RF CIRCUITS

The antenna switching circuit toggles between the receive

(RX) line and transmit (TX) line. RF amplifi er

received signals within the frequency coverage.

Received signals from the antenna are passed through Low

Pass filter (LPF; L40, C369, C370), TX power detector (D47,

D49, D51) and another LPF (L38, L39, C343, C345, C356,

C357), then applied to the antenna switching circuit (D38/

D39, L37, C337, C346).

The received signals are passed through the antenna

switching circuit as an LPF (L37, C337, C346), LPF (L35,

C322, C322, C323, C336) and two-staged tuned Bandpass

Filter (BPF; D34, L32, C299, C300 and D31, L31, C278,

C279), then applied to the RF amplifier (Q31).

The amplified signals are passed through another twostaged tuned BPF (D27, L28, C260−C263, C242 and D26,

L26, C219, C220, C240) and applied to the 1st mixer (IC10;

pins 4, 5, L18, L19, L24).

1ST IF CIRCUITS

The amplified received signals from the RF circuit are

converted into the 1st IF signal, fi ltered and amplifi ed at the

1st IF circuits.

The received signals from the RF circuits are mixed with

1st Local Oscillator (LO) signal from the RX VCOs, to be

converted into the 1st IF signal. The converted 1st IF signal

is amplified by 1st IF amplifier (Q50). The amplified 1st IF

signal is passed through the 1st IF filter (FI3 for analog

mode, FI4 for digital mode) via filter switches (Q20, D21,

D66, D67 on input side; D6, D68, D69 on output side) to

suppress unwanted signals. The filtered 1st IF signal is

amplified by another 1st IF amplifier (Q12), then applied to

the 2nd IF circuits.

2ND IF CIRCUITS

The 1st IF signal is converted into the 2nd IF signal,

amplified and demodulated in the IF IC.

amplifi es the

The 1st IF signal from the 1st IF amplifier (Q12) is applied

to the IF IC (IC5, pin 16). The applied signal is converted

into the 2nd IF signal by being mixed with the 2nd LO signal

from X1 via tripler (Q3, L3, L2, C32−C35).

The converted 2nd IF signal is output from pin 3, and

passed through the 2nd IF filter (FI1). The filtered 2nd IF

signal is passed through (bypassed) another 2nd IF filter

(FI2) via filter switches (D1 on input side; D2 on output

side). The filtered signal is then applied to the IF IC (IC5, pin

5), and amplified by 2nd IF amplifier. The amplified signal is

FM-demodulated by quadrature detector (IC5, pins 10, 11;

X3).

The demodulated AF signals are output from pin 9, then

applied to the AF circuits.

AF CIRCUITS

The demodulated AF signals from the IF IC are amplified

and fi ltered at AF circuits.

This transceiver employs the base band IC for audio signal

processing for both transmit and receive. The base band

IC is an audio processor and composed of pre-amplifier,

compressor, expander, scrambler, etc. in its package.

The demodulated AF signals from IF IC (IC5, pin 9) are

passed through Digital/Analog switch (IC8, pins 2, 15), and

applied to the base band IC (IC2, pin 23).

The applied AF signals are amplified at the amplifier section

and level adjusted at the volume controller section, then

suppressed unwanted 3 kHz and higher audio signals at

LPF. The filtered AF signals are applied (bypassed) the TX/

RX HPF, scrambler, de-emphasis sections in sequence.

The TX/RX HPF filters out 250 Hz and lower audio signals,

and the de-emphasis circuit obtains –6 dB/oct of audio

characteristics. The expander expands the compressed

audio signals and also noise reduction function is provided.

The AF signals are then level adjusted at the volume

controller section and amplified at the amplifier section, then

output from pin 20 (IC2).

• 2nd IF AND DEMODULATOR CIRCUITS

2

D/A converter

Demodulated signals

to the AF circuits

(IC6)

1

Quadrature

detector

9

8

Filter

amp.

1110

X3

Limiter

amp.

Buffer

D2

N/W

SW

735

Q13

+5V

RSSI

5 - 1

FI2

D1

N/W

SW

FI1

Noise

detector

Mixer

45.9 MHz

2

BPF

IF IC (IC5)

1312

“D_IF” signal to the optional digital unit via J2

16

1st IF signal from the IF amplifier (Q12)

“NOIS” signal to the CPU (IC14: pin 113)

“RSSI” signal to the CPU (IC14: pin 71)

Q3

3

X1

15.3 MHz

Page 10

The processed AF signals from the base band IC (IC2) are

passed through the AF mute switch (IC8, pins 3, 4) and D/A

converter (IC6, pins 15, 16) for level adjustment. The level

adjusted AF signals are amplified by AF amplifier (IC22).

The amplified AF signals are then;

- Output from D-sub 25 pin connector (CONNECT UNIT;

J602).

or

- Buffer-amplified by Q49, then applied to connected micro phone via FRONT UNIT.

or

- Applied to the AF power amplifier (IC21, pin 1) to obtain AF

output power level, then applied to the internal/external

speaker via external speaker jack (J7).

5-2 TRANSMITTER CIRCUITS

MICROPHONE AMPLIFIER CIRCUITS

The AF signals from the microphone (MIC signals) are

filtered and level-adjusted at the microphone amplifier

circuits.

AF signals from the connected microphone (MIC signals)

are passed through (bypassed) the ALC (Automatic Level

Control) amplifier (FRONT UNIT; IC505, pins 3, 5) via AF

switch (FRONT UNIT; IC507, pins 1, 6/7), then applied to

the microphone amplifier (FRONT UNIT; IC508, pin 3). The

amplified MIC signals are output from pin 4, and applied to

the MAIN UNIT.

The MIC signals from the FRONT UNIT are passed through

the Int./Ext. MIC switch (IC23, pins 1, 6), and applied to the

base band IC (IC2, pin 3) and processed.

SQUELCH CIRCUITS

<NOISE SQUELCH>

The squelch mutes the AF output signals when no RF signals

are received. By detecting noise components (30 kHz and

higher signals) in the demodulated AF signals, the squelch

circuit toggles the AF power amplifi er ON and OFF.

A portion of the demodulated AF signals from the IF IC

(IC5, pin 9) are applied to the D/A converter (IC6, pin 1)

for level adjustment (squelch threshold adjustment). The

level-adjusted AF signals are output from pin 2 and passed

through the noise filter (IC5, pins 7, 8, R121−R124, C216

−C218). The filtered noise signals are amplified the noise

components only.

The amplifi ed noise components are converted into the pulsetype signal at the noise detector section, and output from pin

13 as the “NOIS” signal. The “NOIS” signal is applied to the

CPU (IC14, pin 113), Then the CPU outputs signal “AFON2”

signal from pin 15 to the AF power amplifier controller (Q51,

Q52, D65), according to the “NOIS” signal level. The AF power

amplifi er controller toggles AF power amplifi er (IC21) ON and

OFF according to the “AFON” signal.

<TONE SQUELCH>

The tone squelch circuit detects tone signals and opens the

squelch only when receiving a signal containing a matched

sub audible tone. When the tone squelch is in use, and a

signal with a mismatched or no sub audible tone is received,

the tone squelch circuit mutes the AF signals even when the

noise squelch is open.

• CTCSS/DTCS

A portion of the demodulated AF signals are passed through

the active LPF (Q4, R45, R46, R47, R63, R64, C45, C46,

C47, C71) to filters CTCSS/DTCS signal. The filtered signal

is applied to the CPU (IC14, pin 64). The CPU compares the

applied signal and the set CTCSS/DTCS, then outputs control signal as same as “NOISE SQUELCH.”

• 2/5 TONE AND DTMF

2/5 tone signals in the demodulated AF signals are passed

through the LPF in the base band IC (IC2) and output from

pin 21, then applied to the CPU (IC14, pin 63) via tone

amplifer (IC1, pins 8, 9), and decoded.

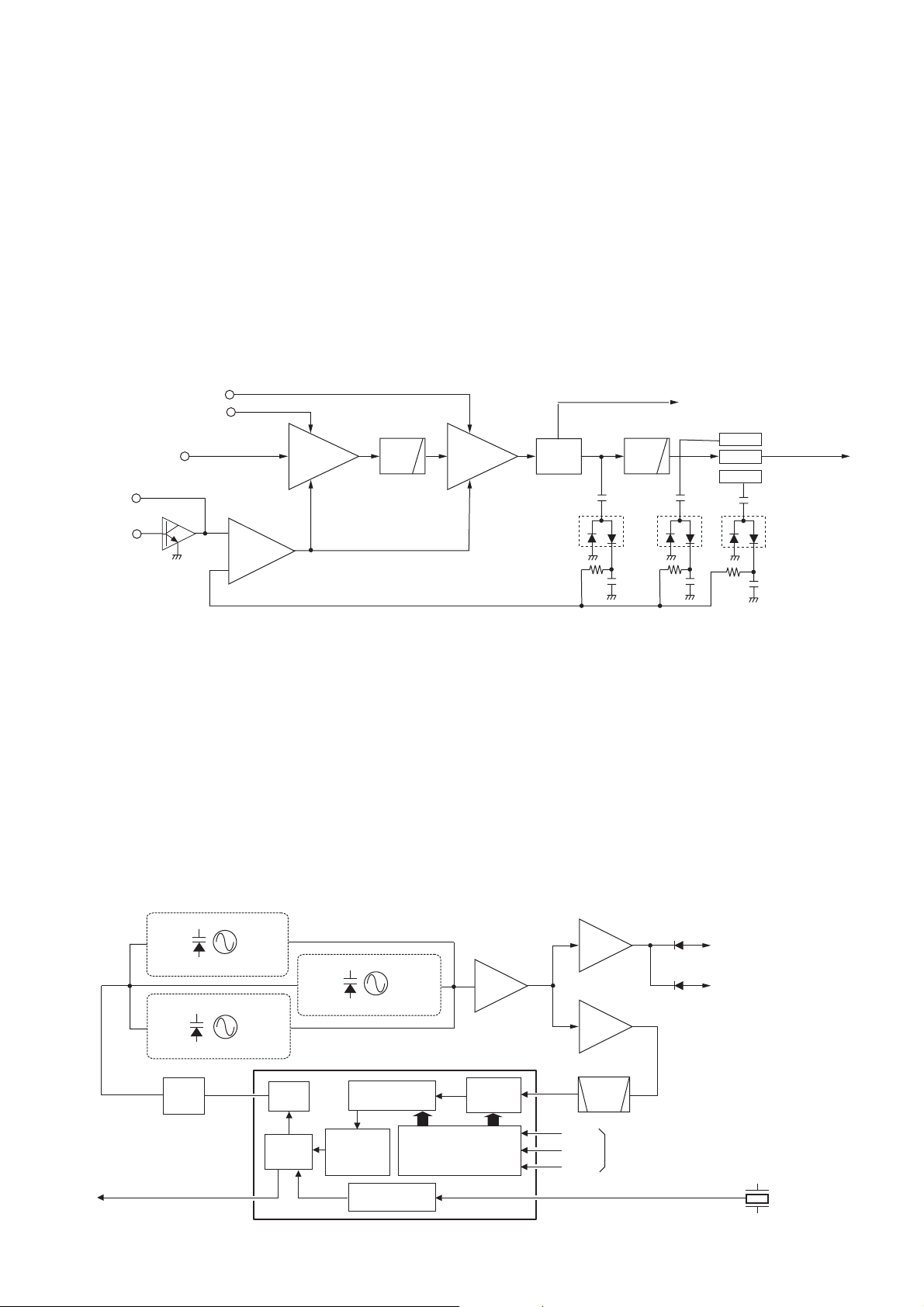

• BASE BAND IC BLOCK DIAGRAM

The applied MIC signals are amplifi ed at the amplifi er (TXA1),

and level adjusted at the volume controller (VR1). The level

adjusted MIC signals are applied (bypassed) the compressor

section, pre-emphasis section, TX/RX HPF, de-scrambler, limiter,

splatter, in sequence, then applied to another volume controller.

The compressor compresses the MIC signals to provide high S/N

ratio for receive side, and the pre-emphasis obtains +6 dB/oct

audio characteristics. The TX/RX HPF filters out 250 Hz and

lower audio signals, the limiter limits its level and the splatter

filters out 3 kHz and higher audio signals. The filtered MIC

signals are level adjusted at another volume controller (VR2),

and then output from pin 7 via smoothing fi lter (SMF).

The MIC signals from the base band IC are passed through

the digital/analog switch (IC8, pins 12, 14), FM/PM switch

(IC3, pins 13, 14), and applied to the AF mixer (IC1, pin

13) where the MIC signals and tone signals are mixed with.

The mixed MIC signals are passed through D/A converter

(IC6, pins 3, 4) for level adjustment. The level adjusted MIC

signals are then applied to the VCO as modulation signals.

MODULATION CIRCUITS

The modulation circuits modulates the VCO oscillating signal

using the modulation signals.

The MIC signals from the microphone amplifier circuits are

applied to the D20 of TX VCO (Q19, D14, D17, D18, D20)

as the modulation signals, and modulate the VCO oscillating

signal by changing the reactance of D20.

The FM-modulated VCO output is amplified by bufferamplifiers (Q22, Q29), then applied to the power amplifiers

via D24 as the TX signal.

SIGNALING ENCODE

5/2-TONE, DTMF and CTCSS/DTCS signals are output

from the CPU (IC14) and passed through the LPF (IC7)

and level converter (IC6), then applied to the AF mixer

(IC1, pin 13) and mixed with MIC signals. The mixed tone

signals are passed through the D/A converter (IC6, pins 3,

4) for level adjustment. The level adjusted tone signals are

applied to the both of TX VCO (Q19, D14, D17, D18, D20)

and reference frequency oscillator (X1, pin 1) via the level

adjuster (IC1, pins 1, 3).

BASE BAND IC (IC2)

Com-

pressor

RX

LPF

Pre-

emphasis

TX/RX

HPF

Scrambler/

De-scrambler

Limiter Splatter VR2

De-

emphasis

Expander

VR4

SMF

RXA2

7 MOD

18

19

20

SIGNAL

TXA1

RXA1

VR1

(HPF)

VR3

(HPF)

3TXIN

23RXIN

21SDEC

5 - 2

Page 11

TX POWER AMPLIFIERS

The transmit signal from the TX VCO is amplified to the

transmit output level by the transmit amplifi ers.

The TX VCO output signal from buffer amplifier (Q29) is

applied to the YGR amplifier (Q30) via the TX/RX switch

(D24). The amplified TX signal is passed through the LPF

(L29, L30, C269−C271, C290), and applied to the RF power

module (IC15, pin 1) and power-amplified to obtain 50 W/25

W (max.) of TX output power.

The power-amplified TX signal is passed through the LPF as

a harmonic filter (L33, C305−C308), the antenna switching

circuit (D38, D39) and LPF (L38, L39, C343, C345, C356,

C357).

The TX signal is also gone through the power detector (D47,

D49, D51) and LPF (L40, C369, C370) before being applied

to the antenna connector.

• APC CIRCUIT

APC CIRCUIT

The APC (Automatic Power Control) circuit prevents the

transition of the transmit output power level which is caused

by load mismatching or heat effect, etc. At the power

detector, a portion of the transmit signal is rectified to

produce DC voltage which is in proportion of the transmit

power level.

The rectified voltage is applied to the inverted input terminal

of the operational amplifier (IC17, pin 3). The TX power

setting voltage “T2” from the D/A converter (IC12, pin 2) is

applied to the non-inverted input terminal as the reference.

The operational amplifier compares the rectified voltage and

reference voltage “T2,” and the difference of the voltage is

output from the operational amplifier pin 4, and the output

voltage controls the bias of YGR (Q30) amplifier and power

module (IC15) for stable transmit output power.

HV

T8V

Q30

IC17

YGR

amp.

LPF

Transmit signal

from TX/RX switch (D24)

“T2”

Q53

“TMUT”

+

OP.

amp.

–

5-3 FREQUENCY SYNTHESIZER CIRCUITS

VCO

VCO is a oscillator whose oscillating frequency is controlled

by adding voltage (lock voltage).

• RX VCO1 (Q18, D10, D13)

RX VCO1 generates the 1st LO signal for receiving 155−174

MHz signals.

• RX VCO2 (Q17, D8, D9)

RX VCO2 generates the 1st LO signal for receiving 136−155

MHz signals.

to the 1st mixer (IC10)

IC15

Powe r

amp.

ANT

SW

D47

LPF

D49

to the antenna

D51

Each output signals are amplified by the buffer amplifiers

(Q22, Q29), and applied to the 1st mixer (IC10, pins 4, 5) via

TX/RX switch (D25 is ON, D24 is OFF) and LPF (L22, L23,

C215, C216, C236, C237), to be mixed with the received

signals to produce the 46.35 MHz 1st IF signal.

• TX VCO (Q19, D14, D17, D18, D20)

The output signal is applied to the transmit amplifi ers via the

buffer amplifi ers (Q22, Q29) and TX/RX switch (D24 is ON,

D25 is OFF).

A portion of the buffer-amplified VCO output signals from the

buffer amplifier (Q22) are applied to the PLL IC (IC4, pin 6)

via doubler (Q25) and BPF (Q5, D4, D5, L4, R77, C84−C90).

• PLL CIRCUITS

RX VCO1 (155–174 MHz)

Q18, D10, D13

RX VCO2 (136–155 MHz)

Q17, D8, D9

Loop

filter

PLL unlock signal

to the CPU (IC14, pin 73)

11

4

TX VCO

Q19, D14, D17, D18, D20

Charge

pump

Phase

detector

Programmable

Divide

ratio

adjustment

divider

Reference

divider

Buffer

Q22

PLL IC (IC4)

Prescaler

Shift register

5 - 3

Buffer

Q29

×3

Q25

6

14

15

16

10

BPF

SCK

SSO

PLL control signals from the CPU (IC14)

PLST

15.3 MHz

reference frequency signal

D14

to transmitter circuit

D15

to 1st mixer circuit

X1

15.3 MHz

Page 12

PLL IC

The PLL circuit provides stable oscillation of the transmit

frequency and receive 1st LO frequency. The PLL output

frequency is controlled by the divided ratio (N-data) from the

CPU.

The phase difference is output from pin 4 as a pulse type

signal after being passed through the internal charge pump.

The output signal is converted into the DC voltage (lock

voltage) by passing through the loop filter (Q8, Q9). The lock

voltage is applied to the variable capacitors (D10 and D13

of RX VCO1, D8 and D9 of RX VCO2, D14 and D17 of TX

The applied signals are divided at the prescaler and

VCO), and locked to keep the VCO frequency constant.

programmable counter according to the control signals

(“SSO,” “PLST” and "SCK”) from the CPU. The divided signal

is phase-compared with the reference frequency signal from

the reference frequency oscillator (X1, pin 3), at the phase

If the oscillated signal drifts, its phase changes from that of

the reference frequency, causing a lock voltage change to

compensate for the drift in the VCO oscillating frequency.

detector.

5-4 POWER SUPPLY CIRCUITS (MAIN UNIT)

Voltage from the attached battery pack is routed to whole of the circuit in the transceiver via switches and regulators.

• POWER SUPPLY CIRCUITS

CPU (IC14),

EEPROM (IC16),

etc.

RF power amplifier (IC15)

AF power amplifier (IC21)

etc.

etc.

Transmitter circuits

Common circuits

Receiver circuits

PLL IC (IC4)

Attached optional units,

D/A converters,

etc.

R8V

+5V

Q38, Q39

R8V

regurator

+5V

regurator

Q35, Q36

HV

T8V

+8V

T8V

regurator

Q34, Q37, D37

+8V

regurator

IC20

“RXC”

CPU5

VCC

47

IC18

CPU5

regurator

Q47, Q48

Power switch

“PWON”

“TXC”

4146

(IC14)

CPU

HV

Control signal

Power Supply

Voltage line

5 - 4

Page 13

5-5 PORT ALLOCATIONS

• CPU (MAIN UNIT; IC14)

Pin

Port

No.

Name

1 DSDA Outputs serial data to the D/A converter (IC20, pin 6).

2 DAST Outputs strobe signal to the D/A converter (IC4, pin 6).

3 SIDE3

4−7 CBI0−3 Input ports for [ROTARY SELECTOR] (S701).

10 SSO

11 SCK

13 PLST

15 DASW

17 TMUT

18 NWC2

19 NWC1

20 DDSD

21 DDAC

26 T5C

27 R5C

28 S5C

29 PTTSW

30 SIDE2

32 RMUT Outputs mute signal to the AF mute switch (D42).

37 NOIS

38 POSW

39 DDST

40 MTCK

41 PWON

43 SENC

44 BEEP Outputs beep sound to the AF circuits (IC4, pin 13).

45 SDEC Input port for decoded 2/5 tone and DTMF signals.

46 CDEC Input port for decoded CTCSS/DTCS signal.

47 ISENS

48 BATV Input port for remaining battery power.

49 LVIN Input port for VCO lock voltage.

50 RSSI

55 EMER Input port for [Emer] switch (S702).

Input port for [Side3] key (S4).

"Low"=When the key is pushed.

Outputs serial data to the PLL IC (IC1, pin 15), D/A

converter (IC4, pin 8).

Outputs serial crock signal to the PLL IC (IC1, pin

14), D/A converter (IC4, pin 8).

Outputs PLL strobe signal to the PLL IC (RF UNIT;

IC1, pin 16).

Outputs mode (Digital/Analog) switching signal to

the D/A converter (IC14, pins 10, 11).

Outputs transmit mute signal to the transmit mute

switch (RF UNIT; Q606).

Outputs Narrow/Wide mode switching signal to the

bandwidth switches (Q26, D32, D33).

Outputs Narrow/Wide mode switching signal to the

bandwidth switches (Q27, Q41, Q42, D34, D35).

Outputs serial data to the DTMF decode IC (IC10,

pin 9).

Outputs serial clock signal to the DTMF decode IC

(IC10, pin 11).

Outputs T5V line control signal to the T5V regulator

(Q15).

"Low"= While transmitting.

Output R5V line control signal to the R5V regulator

(Q16).

"Low"= While receiving.

Output S5V line control signal to the S5V regulator

(Q14).

"Low"=While power save mode.

Input port for [PTT] switch (S3).

"Low"=When the switch is pushed.

Input port for [Side2] key (S5).

"Low"=When the key is pushed.

Input port for the noise level from the IF IC (IC3, pin

13).

Input port for power switch (R702) from power

controller (D36).

Outputs strobe signal to the DTMF decode IC (MAIN

UNIT; IC10, pin 14).

Outputs serial clock signal to the base band IC

(MAIN UNIT; IC5, pin 9).

Outputs VCC line control signal to the power switch

(Q30, Q31).

"Low"=While the power is ON.

Outputs single tone encode signal to the LPF (IC17,

pin 10).

Input port for power amplifier current detect signal

from the current detector (RF UNIT; Q604, Q605).

Input port for RSSI signal from the IF IC (IC3, pin

12).

Description

Pin

Port

No.

Name

70 CSFT

71 DUSE

73 UNLK

74 RLED

75 TLED

78 FSDA

79 FSCL

81 CIRQ

88 SIDE1

CENC0−

89−

91

92 EMPH

93 MTDT Outputs serial data to the base band IC (IC5, pin 10).

96 MSCK

97 PMFM

98 ESDA Outputs serial data to the EEPROM (IC19, pin 5).

99 ESCL

100 RESL Input port for reset signal from the reset IC (IC8, pin 1).

Outputs CPU clock frequency shift signal to the CPU

clock oscillator (X2, D38).

Outputs CTCSS/DTCS select signal to the CTCSS/

DTCS switch (Q34).

Input port for PLL unlock detect signal from the PLL

IC (IC1, pin 11).

Outputs RX indicator (DS701) control signal to the

LED driver (Q701).

Outputs TX indicator (DS701) control signal to the

LED driver (Q701).

Outputs serial data to the expand IC (FRONT UNIT;

IC505, pin 3).

Outputs serial clock signal to the expand IC (FRONT

UNIT; IC505, pin 3).

Input port for external connection detect signal from

J1 and J2.

Input port for [Side1] key (S6).

"Low"=When the key is pushed.

Output CTCSS/DTCS signals to the LPF (IC17, pin 3).

2

Outputs emphasis characteristic change signal to

the D/A converter (IC13, pins 9, 10).

Outputs serial clock signal to the base band IC

(MAIN UNIT; IC5, pin 13).

Outputs modulation mode switching signal to the

PM/FM switch (IC13, pin 11) .

Outputs serial clock signal to the EEPROM (IC19,

pin 6).

Description

• D/A CONVERTER (MAIN UNIT; IC6)

Pin

Port

No.

Name

1T1

2T2

3 TXLVA

4 RXLVA

Outputs BPF tuning voltage to the tunable BPF (

D24, L31, L32, C120−C122, C125−C127

• While receiving

Outputs BPF tuning voltage to the tunable BPF

(

D28, D29, L33, L34, C140−C144, C147).

• While transmitting

Outputs TX power setting voltage to the APC

amplifi er (RF UNIT; IC601).

Outputs oscillation frequency adjust voltage to the

TX VCO (

Outputs oscillation frequency adjust voltage to the

RX VCO1/2 (

Q3, D10−D12).

Description

D23,

).

Q1, D1−D4/Q2, D5−D8).

5 - 5

Page 14

SECTION 6 ADJUSTMENT PROCEDURES

6-1 PREPARATION

When adjusting IC-F5060 series transceiver, CS-F5060

,

er), RS-232C cable

JIG cable (modifi ed OPC-1122/U

CLONING SOFTWARE,

CLONING CABLE

; see the page 6-2) and the following test equipments are required.

CS-F5060 ADJ

EQUIPMENT GRADE AND RANGE EQUIPMENT GRADE AND RANGE

DC power supply

Output voltage

Current capacity

modulation analyzer

Frequency counter

RF power meter

▄

SYSTEM REQUIREMENTS

• Microsoft

®

Windows® 98/98SE/Me/2000/XP • RS-232C serial port (D-sub 9 pin)

Frequency range

Measuring range

Frequency range

Frequency accuracy

Sensitivity

Measuring range

Frequency range

Impedance

SWR

: 13.6 V DC [USA]

13.2 V DC [EUR], [EXP]

: More than 1.5 A

: DC–300 MHz

: 0 to ±10 kHz

: 0.1–300 MHz

: ±1 ppm or better

: 100 mV or better

: 0.1–60 W [USA]

0.1–30 W [EUR], [EXP]

: 100–300 MHz

: 50

Ω

: Better than 1.2 : 1

Attenuator

External speaker

Standard signal

generator (SSG)

Oscilloscope

Digital voltmeter

(for the ADJUSTMENT SOFTWARE)

ADJUSTMENT SOFTWARE

Power attenuation

Capacity

Input impedance

Capacity

Frequency range

Output level

Frequency rang

Measuring range

Input impedance

Measuring range

: 50 or 60 dB

: 60 W [USA]

30 W [EUR], [EXP]

: 4

: 5 W or more

: 0.1–300 MHz

: 0.1 µV to 32 mV

(–127 to –17 dBm)

: DC–20 MHz

: 0.01–20 V

: 50 k

: 0.1–10V

(Rev. 1.0 or lat-

Ω

Ω

▄

ADJUSTMENT SOFTWARE INSTALLATION

Quit all applications when Windows is running.

q

Insert the CD into the appropriate CD drive.

w

Double-click the “Setup.exe” contained in the ‘CS-F5060

e

ADJ’ folder in the CD drive.

The “Welcome to the InstallShield Wizard for CS-F5060

r

ADJ” will appear. Click [Next>].

The “Choose Destination Location” will appear. Then click

t

[Next>] to install the software to the destination folder. (e.g.

C:\Program Files\Icom\CS-F5060 ADJ)

After the installation is completed, the “InstallShield Wiz-

y

▄

STARTING SOFTWARE ADJUSTMENT

Connect the transceiver and PC with RS-232C cable and

q

JIG CABLE

Turn the transceiver power ON.

w

Boot up Windows, and click the program group ‘CS-F5060

e

.

ADJ’ in the ‘Programs’ folder of the [Start] menu, then

CS-F5060 ADJ’s window appears.

Click ‘Connect’ on the CS-F5060 ADJ’s window, then the

r

window shows transceiver’s condition and adjustment

items as below.

Set or modify adjustment data as specifi ed.

t

ard Complete” will appear. Then click [Finish].

Eject the CD.

u

Program group ‘CS-F5060 ADJ’ appears in the ‘Programs’

i

folder of the start menu, and ‘CS-F5060 ADJ’ icon appears on the desk top screen.

▄

BEFORE STARTING SOFTWARE ADJUSTMENT

Clone the adjustment frequencies and settings into the transceiver, and set the confi guration using the CS-F5060

WARE

before starting the software adjustment. Otherwise, the software adjustment can not be started.

Microsoft and Windows are registered trademarks of Micro-

soft Corporation in the U.S.A. and other countries.

CLONING SOFT-

CAUTION!: BACK UP the originally programmed memory data in the transceiver before programming the adjustment frequencies.

When program the adjustment frequencies into the transceiver, the transceiver’s memory data will be overwritten and

lose original memory data at the same time.

• ADJUSTMENT FREQUENCY LIST

CH FREQUENCY SETTING CH FREQUENCY SETTING

1 154.900 MHz

2 174.000 MHz

3 136.000 MHz

4 155.000 MHz

5 136.000 MHz

6 136.000 MHz

7 155.000 MHz

8 155.000 MHz

9 136.000 MHz

*; [EUR] only

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• DTCS

• TX power

• Mode

• TX power

• Mode

: Low1

: Narrow

: Low1

: Wide

: Low1

: Wide

: Low1

: Wide

: High

: Narrow

: Low2

: Wide

: Low1

: Middle

: 007

: Low1

: Narrow

: Low1

: Narrow

10 174.000 MHz

11* 155.000 MHz

12* 136.000 MHz

13* 174.000 MHz

14 155.000 MHz

15 136.000 MHz

16 174.000 MHz

17 136.000 MHz

18 136.000 MHz

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• Mode

• TX power

• CTCSS

• TX power

• Mode

• DTMF

: Low1

: Narrow

: Low1

: Middle

: High

: Middle

: Low2

: Middle

: Low1

: Digital

: Low1

: Digital

: Low1

: Digital

: Low1

: 151.4 Hz

: Low1

: Wide

: P3

6 - 1

Page 15

• CONNECTION

CAUTION:

DO NOT transmit while

SSG is connected to

the antenna connector.

to an RS-232C port

RS-232C cable

(straight)

AC millivoltmeter

Audio generator

Standard signal generator

–127 to –17 dBm

(0.1 V to 32 mV)

Modulation analyzer

Attenuator

50 dB or 60 dB

OPC-1122U (USB type)

JIG CABLE

PC

JIG CABLE

RF power meter (50 Ω)

1–60 W [USA]

1–30 W [EUR], [EXP]

Frequency

counter

to the antenna connector

to the

[MICROPHONE CONNECTOR]

DC power supply

13.6 (13.2) V / 20 A [USA]

13.2 (13.2) V / 20 A [EUR], [EXP]

SINAD meter

SP (4 Ω)

to EXT. SP jack

to DC cable

IC-F5061

IC-F5062

IC-F5063

• JIG CABLE

(USB type Cloning cable)

Add a jumper wire here

OPC-1122

(RS-232C type Cloning cable)

OPC-1122U

PTTE

PTT

MIC

MICE

Electrolytic

capacitor

47 µF

PTT switch

+

Audio generator

300 Hz to 3 kHz

AC

millivoltmeter

Add a jumper wire here

GND

MIC

GND

PTT

6 - 2

+

PTT switch

Electrolytic

capacitor

47 µF

Audio generator

300 Hz to 3 kHz

AC

millivoltmeter

Page 16

• ADJUSTMENT SOFTWARE WINDOW

Transmit output power

(*)

Modulation balance

(*)

(*)

FM deviation

(*)

CTCSS/DTCS deviation

Squelch level

Reference frequency

RX sensitivity (Auto.)

RX sensitivity (Manu.)

(*)

PLL lock Voltage

(Adjustment)

PLL lock Voltage

(Preset)

S-meter

FM deviation

(Narrow)

FM deviation

(Middle)

*; DO NOT put the cursor on these items

FM deviation

(Wide)

Digital deviation

Digital mode preset

2/5tone, DTMF

and push the [ENTER] key. Otherwise,

some adjustment items will not be ad justed properly.

NOTE: The above screen is an example only. Each transceiver has its own specific values for each setting.

6 - 3

Page 17

6-2 FREQUENCY ADJUSTMENT

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT ADJUSTMENT CONDITION UNIT OPERATION VALUE

PLL LOCK

VOLTAGE

(adjustment)

[RX LVA1]

[RX LVA2] 3 • Channel

[TX LVA] 4 • Channel

PLL LOCK

VOLTAGE

(verify)

REFERENCE

FREQUENCY

[REF]

1 Set the preset value of [LV (RX1)], [LV (RX2)] and [LV (TX)] to “204 [4.00V]” on the adjustment software.

2 • Channel

• Receiving

• Receiving

• Transmitting

CONVENIENT:

1: Set the Lock voltage preset ([LV RX1], [LV RX2], [LV TX]) to “204 (4.00 V).”

2: Put the cursor on [RX LVA1], [RX LVA2] and [TX LVA], then push the [ENTER] key on the connected PC’s keyboard.

1 • Channel

• Receiving

2 • Channel

• Receiving

3 • Channel

• Transmitting

1 • Channel : CH 2 Top

• Connect an RF power meter to the

antenna connector.

• Transmitting

The “

: CH 1 PC

: CH 2

: CH 2

PLL LOCK VOLTAGE”

: CH 3 PC

: CH 4

: CH 3

Click [Reload (F5)] button, then

screen

screen

panel

check the “LVIN” item on the

CS-F5060 ADJ’s screen as below.

can be adjusted automatically.

Click [Reload (F5)] button, then

check the “LVIN” item on the

CS-F5060 ADJ’s screen.

Loosely couple a frequency

counter to the antenna connector.

4.00 V

0.8–1.6 V

(Verify)

174.000000 MHz

PLL LOCK VOLTAGE

will be appeared here

NOTE: The above screen is an example only.

Each item’s voltage will appear when pushing [Update] button.

6 - 4

Page 18

6-3 TRANSMIT ADJUSTMENT

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT ADJUSTMENT CONDITION UNIT OPERATION VALUE

OUTPUT

POWER

[Power (Hi)]

[Power (L2)] 2 • Channel : CH 6

[Power (L1)] 3 • Channel : CH 3

MODULATION

BALANCE

[BAL (Narrow)]

FM

DEVIATION

(NARROW)

[MOD N C]

[MOD N L] 2

[MOD N H] 3

(WIDE)

[MOD W C]

[MOD W L] 5

[MOD W H] 6

(MIDDLE)*

[MOD W C]

[MOD M L] 8

[MOD M H] 9

DIGITAL

DAVIATION

[MOD D C]

[MOD D L] 3

[MOD D H] 4

CTCSS/DTCS

DEVIATION

[CTCS/DTCS]

2TONE,

5TONE,

DTMF

[S.Tone]

*; [EUR] only.

1 • Channel : CH 5

• Transmitting

Rear

panel

Connect an RF power meter to

the antenna connector.

• Transmitting

• Transmitting

1 Set the preset value of [MOD N] to “100” on the adjustment software.

2 • Channel : CH 7

• No audio signals applied to the JIG cable.

• Set a modulation analyzer as;

HPF : OFF

Rear

panel

Connect the modulation analyzer with an oscilloscope to the

antenna connector through an

attenuator.

LPF : 20 kHz

De-emphasis : OFF

Detector : (P–P)/2

• Push [P0] while transmitting.

• Connect an audio generator to the JIG

1

cable and set as;

Frequency : 1.0 kHz

Rear

panel

Connect the modulation ana-

lyzer to the antenna connector

through an attenuator.

Level : 40 mV rms

• Set the modulation analyzer to the same

condition as “MODULATION BALANCE.”

• Transmitting

• Channel : CH 8

• Transmitting

• Channel : CH 9

• Transmitting

• Channel : CH 10

• Transmitting

• Channel : CH 4

4

• Transmitting

• Channel : CH 3

• Transmitting

• Channel : CH 2

• Transmitting

• Channel : CH 11

7

• Transmitting

• Channel : CH 12

• Transmitting

• Channel : CH 13

• Transmitting

Set the preset value of [Digital Mode] to “7” on the adjustment software.

1

• Attach the UT-119 to J2.

2

(Refer to page 4-2 for the installation)

• Channel : CH 14

Rear

panel

Connect the modulation ana-

lyzer to the antenna connector

through an attenuator.

• Transmitting

• Channel : CH 15

• Transmitting

• Channel : CH 16

• Transmitting

• Channel : CH 17

1

• No audio signals applied to the JIG cable.

• Set the modulation analyzer to the same

Rear

panel

Connect a modulation analyzer to

the antenna connector through

an attenuator.

condition as “MODULATION BALANCE.”

• Transmitting

• Channel : CH 18

1

• Transmitting

Rear

panel

Connect a modulation analyzer to

the antenna connector through

an attenuator.

50 W [USA]

[EUR], [EXP]

25 W

25 W [USA]

[EUR], [EXP]

10 W

5.0 W [USA]

[EUR], [EXP]

2.5 W

Set to square wave

form

±2.05 to ±2.15 kHz

±4.05 to ±4.15 kHz

±3.15 to ±3.25 kHz

±1.41 to ±1.45 kHz

±0.68 to ±0.72 kHz

1.50 kHz

±

6 - 5

Page 19

6-4 RECEIVE ADJUSTMENT

Select an adjustment item using [↑] / [↓] keys, then set to the specifi ed value using [←] / [→] keys on the connected PC’s keyboard.

ADJUSTMENT ADJUSTMENT CONDITION UNIT LOCATION VALUE

RECEIVE

SENSITIVITY

[BPF (T1) C]

[BPF (T2) C]

NOTE:

adjusted properly.

1

CONVENIENT:

The “RECEIVE SENSITIVITY” can be adjusted automatically.

1: Put the cursor on “[BPF C ALL]” and push [ENTER] key.

2: The connected PC tunes BPF’s to peak levels automaticaly.

S-METER

(S3 level)

[RSSI]

(S1 level)

SQUELCH

[SQL]

†;

The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

1

2

1 • Channel : CH 3

“RECEIVE SENSITIVITY” must be adjusted before “S-METER.” Otherwise, “S-METER” will not be

• Channel : CH 3

• Connect the SSG to the antenna connector and set as;

Frequency : 136.000 MHz

Level : +20 dBµ

†

(–87 dBm)

SP jack Connect the SINAD meter

with an 4 Ω load to the SP

jack.

Minimum distortion

level

Modulation : 1 kHz

Deviation : ±3.5 kHz

• Receiving

• Channel : CH 3

• Connect the SSG to the antenna connec-

Push the [ENTER] key on the connected PC’s keyboard to set

“S3” level.

tor and set as;

Frequency : 136.000 MHz

Level : +23 dBµ

†

(–84 dBm)

Modulation : 1 kHz

Deviation : ±3.5 kHz

• Receiving

• Set the SSG as;

Level : –7 dBµ

†

(–114 dBm)

Push the [ENTER] key again to set “S1” level.

• Receiving

• Close the squelch by adjusting the value of

[SQL] item on the CS-F5060 ADJ’s screen.

• Connect the SSG to the antenna connec-

tor and set as;

Frequency : 136.000 MHz

Level : –14 dBµ

†

(–121 dBm)

External

speaker

Connect an 4 Ω speaker to

the SP jack.

Close the squelch by

increase the value of

[SQL].

Set the [SQL] to the

value that the audio

signals just appear.

Modulation : 1 kHz

Deviation : ±3.5 kHz

• Receiving

6 - 6

Page 20

SECTION 7 PARTS LIST

[FRONT UNIT]

REF ORDER

NO. NO.

IC501 1130009121 S.IC S1D15206F00A200 B 33.1/19.5

IC502 1110005771 S.IC S-80942CNMC-G9CT2G B 61.4/9.7

IC503 1140010771 S.IC HD64F3687FPV B 62.1/25.2

IC504 1130007111 S.IC TC7W04FU (TE12L,F) B 73.9/26.3

IC505 1110005310 S.IC AN6123MS B 10/8.4

IC506 1110005350 S.IC NJM2870F05-TE1 B 84.9/9.9

IC507 1130006221 S.IC TC4W53FU (TE12L,F) B 6.5/19

IC508 1130008561 S.IC TC75S51F (TE85L,F) B 74/11.3

Q501 1590001050 S.TR DTC114TUA T106 B 15.1/32.9

Q502 1590001050 S.TR DTC114TUA T106 B 18/32.9

Q503 1590001330 S.TR DTA114EUA T106 B 77/24.7

Q504 1530002851 S.TR 2SC4116-BL (TE85R,F) B 91.5/22.4

Q505 1590001050 S.TR DTC114TUA T106 B 92.5/18.8

Q506 1590000680 S.TR DTC114EUA T106 B 77/27.4

Q507 1590001050 S.TR DTC114TUA T106 B 51.4/30.2

D501 1750000370 S.DIO DA221 TL T 3.5/27.1

D502 1750000370 S.DIO DA221 TL T 3.5/25

D503 1750000370 S.DIO DA221 TL T 3.5/22.9

D504 1790001260 S.DIO MA2S077-(TX) B 50.9/23.1

D505 1790001250 S.DIO MA2S111-(TX) B 3.3/23.3

D506 1790001250 S.DIO MA2S111-(TX) B 82.1/21.7

D507 1790001250 S.DIO MA2S111-(TX) B 79.7/25.8

D508 1790000950 S.ZEN MA8056-M (TX) T 4.8/19.7

D509 1790000950 S.ZEN MA8056-M (TX) T 8.6/19.7

D510 1790000950 S.ZEN MA8056-M (TX) T 10.4/19.7

X501 6050011720 S.XTL CR-764 (19.6608 MHz) B 49.6/18.9

L501 6200003640 S.COL MLF1608E 100K-T B 12/19.1

R501 7030003810 S.RES ERJ3GEYJ 125 V (1.2 M) B 46/28.8

R502 7030003810 S.RES ERJ3GEYJ 125 V (1.2 M) B 46.6/23.8

R503 7310005130 S.TRI RH03ADCS5X (470 k) B 45.5/26.3

R504 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 8/29.3

R505 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 10/29.3

R506 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 12/29.3

R507 7030005010 S.RES ERJ2GEJ 681 X (680) T 14.3/37.2

R508 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 14.3/36.3

R509 7510001730 S.TMR ERTJOEP 473J B 59.9/17.1

R510 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 61.1/17.1

R511 7030005530 S.RES ERJ2GEJ 100 X (10) B 57.1/19.4

R512 7030008010 S.RES ERJ2GEJ 123 X (12 k) B 52/22.7

R513 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 63.8/10.2

R514 7030005160 S.RES ERJ2GEJ 105 X (1 M) B 56.1/20.7

R515 7030008010 S.RES ERJ2GEJ 123 X (12 k) B 52.3/23.9

R516 7030008010 S.RES ERJ2GEJ 123 X (12 k) B 49.5/23.9

R517 7410001140 S.ARY EXB28V104JX B 66.5/10.8

R518 7410001140 S.ARY EXB28V104JX B 67.5/19.2

R519 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 51.5/26.9

R520 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 71.6/26.8

R522 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 3.3/17.2

R523 7030004980 S.RES ERJ2GEJ 101 X (100) B 13.2/10.9

R524 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 71.6/28.4

R525 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 80.2/27

R526 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 79/24.4

R528 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 71.7/24.1

R529 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 82.1/19.6

R530 7030005160 S.RES ERJ2GEJ 105 X (1 M) B 5.4/10

R531 7030009280 S.RES ERJ2GEJ 391 X B 92/20.6

R532 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 91.4/24.2

R533 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 91.4/25.2

R534 7030009140 S.RES ERJ2GEJ 272 X (2.7 k) B 90.6/20.2

R535 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 82.4/31.4

R536 7030005220 S.RES ERJ2GEJ 223 X (22 k) B 77.8/22.9

R537 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 7.2/19.2

R538 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 6.2/19.2

R539 7030010040 S.RES ERJ2GEJ-JPW B 76/15.9

R540 7030009290 S.RES ERJ2GEJ 562 X (5.6 k) B 4.3/10.9

R541 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 3.3/16.6

R542 7030009160 S.RES ERJ2GEJ 181 X (180) B 89.8/24.2

R543 7030009160 S.RES ERJ2GEJ 181 X (180) B 89.8/25.2

R545 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 11.8/19.2

R546 7210003050 VAR EVU-F2KFK3 B14 (10KB)

R547 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 11.8/17.2

R548 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 6.8/17.2

R549 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 9.3/17.2

R550 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 10.9/19.4

R551 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 11/5.8

R552 7030009280 S.RES ERJ2GEJ 391 X B 10.1/5.8

R553 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 75.2/8.7

R554 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) B 71.4/12.4

R555 7030005220 S.RES ERJ2GEJ 223 X (22 k) B 71.4/11.5

R556 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 73.2/8.7

R557 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 71.8/10.2

R558 7030005060 S.RES ERJ2GEJ 333 X (33 k) B 74/13.5

R559 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 11/20.8

R560 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 6.2/20.8

C501 4030016930 S.CER ECJ0EB1A104K B 41.8/30.2

C502 4030016930 S.CER ECJ0EB1A104K B 40.9/30.2

DESCRIPTION

M.

H/V

LOCATION

[FRONT UNIT]

REF ORDER

NO. NO.

C503 4030016930 S.CER ECJ0EB1A104K B 42.7/30.2

C504 4030016930 S.CER ECJ0EB1A104K B 43.6/30.2

C505 4030016930 S.CER ECJ0EB1A104K B 44.5/30.2

C506 4030017490 S.CER C1608 JB 1A 105K-T B 44.7/23.2

C507 4030017460 S.CER ECJ0EB1E102K B 46.1/22.7

C508 4030017490 S.CER C1608 JB 1A 105K-T B 43.4/23.2

C509 4030017730 S.CER ECJ0EB1E471K B 13.1/33.3

C510 4030017730 S.CER ECJ0EB1E471K B 18.6/30.5

C511 4030016790 S.CER ECJ0EB1C103K B 58.3/17.1

C512 4030016930 S.CER ECJ0EB1A104K B 62/17.1

C513 4030017030 S.CER ECJ0EB1A273K B 59.1/10.2

C514 4030016930 S.CER ECJ0EB1A104K B 58.3/18.3

C515 4030017630 S.CER ECJ0EC1H120J B 57.1/17.8

C516 4030017580 S.CER ECJ0EC1H060C B 48.9/22.7

C517 4030016790 S.CER ECJ0EB1C103K B 52.9/22.7

C518 4030017640 S.CER ECJ0EC1H150J B 49.8/22.7

C519 4030016930 S.CER ECJ0EB1A104K B 53.8/22.7

C520 4030017420 S.CER ECJ0EC1H470J T 12.5/36.3

C521 4030017460 S.CER ECJ0EB1E102K B 78.8/27.5

C522 4550006480 S.TAN TEESVA 1C 475M8R B 87.7/9.8

C523 4550006250 S.TAN TEESVA 1A 106M8R B 12.8/7.6

C524 4550006250 S.TAN TEESVA 1A 106M8R B 7.2/7.6

C525 4030017330 S.CER ECJ0EF1C104Z B 85.7/7.7

C526 4030016790 S.CER ECJ0EB1C103K B 84.1/7.7

C527 4030017420 S.CER ECJ0EC1H470J T 5.9/17.2

C528 4030017460 S.CER ECJ0EB1E102K T 8.4/17.2

C529 4550006250 S.TAN TEESVA 1A 106M8R B 82.1/9.8

C530 4030016930 S.CER ECJ0EB1A104K B 84.1/12.1

C531 4030017460 S.CER ECJ0EB1E102K B 79/22.5

C533 4030017460 S.CER ECJ0EB1E102K B 80/22.5

C534 4030017420 S.CER ECJ0EC1H470J B 76.2/22.9

C535 4030016930 S.CER ECJ0EB1A104K B 5.4/9.1

C536 4030016930 S.CER ECJ0EB1A104K B 3.3/18.2

C537 4030017460 S.CER ECJ0EB1E102K B 14/25

C538 4030017330 S.CER ECJ0EF1C104Z B 6/10.9

C539 4030017420 S.CER ECJ0EC1H470J T 10.9/17.2

C540 4030017460 S.CER ECJ0EB1E102K B 10.9/17.8

C541 4030017420 S.CER ECJ0EC1H470J B 8.5/10.9

C543 4030017420 S.CER ECJ0EC1H470J B 77.6/16.7

C544 4030017420 S.CER ECJ0EC1H470J B 79.8/16.7

C545 4030017420 S.CER ECJ0EC1H470J B 77.6/15.8

C546 4030017420 S.CER ECJ0EC1H470J B 74/15.3

C547 4030017460 S.CER ECJ0EB1E102K B 74/16.2

C548 4030017490 S.CER C1608 JB 1A 105K-T B 9.7/19.3

C549 4030016930 S.CER ECJ0EB1A104K B 3.7/21.2

C550 4030018900 S.CER ECJ0EB0J474K B 70.1/11.9

C551 4030016930 S.CER ECJ0EB1A104K B 70.9/10.2

C552 4030017460 S.CER ECJ0EB1E102K B 75.2/6.9

C553 4030017460 S.CER ECJ0EB1E102K B 71.4/13.3

C554 4030016790 S.CER ECJ0EB1C103K B 74.2/8.7

C555 4030017460 S.CER ECJ0EB1E102K B 74/14.4

C556 4550006480 S.TAN TEESVA 1C 475M8R B 76.9/10.2

J501 6510022021 S.CNR 14FLT-SM2-TB (LF) (SN) B 88/28.5

J502 6510023091 S.CNR 20FLT-SM2-TB (LF) (SN) B 75.5/19.5

J503 6450002210 CNR 3017-8821 <KIN>

DS501 5030003020 LCD L6-0226TVM-3

DS502 5040002670 S.LED CL-165HR/YG T 18.2/35.9

DS503 5040002310 S.LED SML-311YTT86 T 32.8/6.5

DS504 5040002310 S.LED SML-311YTT86 T 46.1/6.3

DS505 5040002310 S.LED SML-311YTT86 T 59.8/6.3

DS506 5040002310 S.LED SML-311YTT86 T 92.3/24.5

DS507 5040002310 S.LED SML-311YTT86 T 73.1/6.5

DS508 5040002310 S.LED SML-311YTT86 T 31.7/26

DS509 5040002310 S.LED SML-311YTT86 T 40.2/26

DS510 5040002310 S.LED SML-311YTT86 T 48.7/26

DS511 5040002310 S.LED SML-311YTT86 T 74.2/26

DS512 5040002310 S.LED SML-311YTT86 T 65.7/26

DS513 5040002310 S.LED SML-311YTT86 T 57.2/26

SP501 2510001400 SP

W501 8900012711 CBL OPC-1297A (P0.5,N20,L62) <TJM>

W502 7120000470 JMP ERDS2T0

W503 7120000470 JMP ERDS2T0

EP502 8930072220 LCT SRCN-2979-SP-N-W

DESCRIPTION

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

7 - 1

M.

S.=Surface mount

H/V

LOCATION

Page 21

[MAIN UNIT]

REF ORDER

NO. NO.

IC1 1110005340 S.IC NJM12902V-TE1 T 82.3/12.9

IC2 1110006221 S.IC AK2346P-E2/P B 44.7/11.7

IC3 1140013200 S.IC CD4053BPWR B 58.7/9.3

IC4 1130010100 S.IC LMX2352TMX/NOPB T 82.9/46

IC5 1110003491 S.IC TA31136FNG (D,EL) T 28/13.9

IC6 1190001350 S.IC M62364FP 600D B 84.9/12.9

IC7 1110005340 S.IC NJM12902V-TE1 T 108.5/43.7

IC8 1140013200 S.IC CD4053BPWR B 58.7/16.1

IC9 1130012960 S.IC BU8872FS-E2 B 133.1/21.3

IC10 1190002051 S.IC SPM5001-TL-E B 33.8/36.9

IC12 1190001340 S.IC M62334FP 600C B 9.1/25.7

IC13 1110005771 S.IC S-80942CNMC-G9CT2G B 126/44.8

IC14 1140013520 S.IC HD64F2506FC26DV B 111.8/35.7

IC15 1150002042 IC RA30H1317M-121

[EXP-01], [EUR-01]

1150002073 IC RA60H1317M-125 [USA-01]

IC16 1140012950 S.IC 24LC512T-I/SM B 133.3/29

IC17 1110002751 S.IC TA75S01F (TE85R,F) T 54.1/70.4

IC18 1180000970 S.IC AN78L05M-(E1) B 113/65.3

IC19 1120002510 S.IC DS14C232TM T 104.7/70.5

IC20 1180001251 S.IC TA7808F (TE16L,Q) B 121.5/65.8

IC21 1110003091 IC LA4425A-E

IC22 1110002751 S.IC TA75S01F (TE85R,F) B 135.5/54.4

IC23 1130006221 S.IC TC4W53FU (TE12L,F) B 106.9/9.6

Q1 1590003230 S.TR UNR9113J-(TX) B 15.2/6

Q3 1530002851 S.TR 2SC4116-BL (TE85R,F) B 36.4/15.5

Q4 1590001650 S.TR XP4601 (TX) B 92.8/12.4

Q5 1590003290 S.TR UNR9213J-(TX) B 76.7/50

Q6 1530002851 S.TR 2SC4116-BL (TE85R,F) T 63.2/55.1

Q7 1560000541 S.FET 2SK880-Y (T5RICOM,F) B 81.2/27.1

Q8 1530002851 S.TR 2SC4116-BL (TE85R,F) B 79.2/31.8

Q9 1530002851 S.TR 2SC4116-BL (TE85R,F) B 81.7/31.8

Q10 1560001360 S.FET 2SK3019 TL B 57/31.6

Q12 1530002601 S.TR 2SC4215-O (TE85R,F) T 26.9/20

Q13 1530002851 S.TR 2SC4116-BL (TE85R,F) B 31.8/9.9

Q16 1590003290 S.TR UNR9213J-(TX) T 113.2/47.6

Q17 1530002920 S.TR 2SC4226-T1 R25 T 50.9/47.6

Q18 1530002920 S.TR 2SC4226-T1 R25 T 61.6/42.6

Q19 1530002920 S.TR 2SC4226-T1 R25 T 72.1/43

Q20 1590003230 S.TR UNR9113J-(TX) B 33.9/25.2

Q22 1530003311 S.TR 2SC5107-O (TE85R,F) T 58.1/46.3

Q23 1590001400 S.TR XP1214 (TX) B 55.7/40.9

Q24 1590003290 S.TR UNR9213J-(TX) B 55.8/38.2

Q25 1530003311 S.TR 2SC5107-O (TE85R,F) B 65.9/49.5

Q26 1590001400 S.TR XP1214 (TX) B 67.2/43.1

Q27 1590003230 S.TR UNR9113J-(TX) T 124.7/52

Q28 1590003290 S.TR UNR9213J-(TX) B 123.4/46.3

Q29 1530003311 S.TR 2SC5107-O (TE85R,F) B 53.5/51.2

Q30 1530000372 S.TR 2SC3356-T1B R (R24) B 65.5/66

Q31 1580000731 S.FET 3SK293 (TE85L,F) B 10.2/38.6

Q32 1560000841 S.FET 2SK1829 (TE85R,F) T 11/42.5

Q33 1530002851 S.TR 2SC4116-BL (TE85R,F)

[USA-01] only T 47.5/69.4

Q34 1590003290 S.TR UNR9213J-(TX) T 83/67.4

Q35 1520000460 S.TR 2SB1132 T100 R T 100.1/57.9

Q36 1590001190 S.TR XP6501-(TX) .AB T 104.3/55.8

Q37 1540000550 S.TR 2SD1664 T100Q T 75.5/63.6

Q38 1510000920 S.TR 2SA1577 T106 Q T 39.3/21.3

Q39 1590003290 S.TR UNR9213J-(TX) T 42.6/21.3

Q40 1590003290 S.TR UNR9213J-(TX) T 104.1/51.9

Q41 1590001451 S.FET 2SJ144-GR (TE85R,F) B 110.3/83.3

Q42 1590003290 S.TR UNR9213J-(TX) B 132.1/45

Q43 1590000990 S.TR DTC363EK T146 B 135.7/49

Q44 1590003290 S.TR UNR9213J-(TX) T 108.5/21.6

Q45 1590003290 S.TR UNR9213J-(TX) B 133.3/58.9

Q46 1590003290 S.TR UNR9213J-(TX) T 117.9/84.4

Q47 1550000100 S.FET 2SJ377 (TE16L1,NQ) B 131.3/71.5

Q48 1590003290 S.TR UNR9213J-(TX) B 124.9/77.7

Q49 1530002851 S.TR 2SC4116-BL (TE85R,F) B 139.3/37.2

Q50 1530002601 S.TR 2SC4215-O (TE85R,F) T 40.6/39.2

Q51 1590003321 S.FET TPC6103 (TE85L,F) B 133.6/63.4

Q52 1590003290 S.TR UNR9213J-(TX) B 128.2/61.1

Q53 1590000430 S.TR DTC144EUA T106 B 52.3/67.4

Q54 1590000430 S.TR DTC144EUA T106 T 25.5/6.3

Q55 1560001360 S.FET 2SK3019 TL T 75.5/20.9

Q57 1590003230 S.TR UNR9113J-(TX) T 112/14.4

D1 1750001070 S.DIO DAN235ETL T 10.4/15.7

D2 1750001070 S.DIO DAN235ETL T 22.6/8.9

D3 1790001250 S.DIO MA2S111-(TX) T 61.3/55

D4 1790001260 S.DIO MA2S077-(TX) B 72.9/49.8

D5 1790001260 S.DIO MA2S077-(TX) B 71.1/51.3

D6 1750001070 S.DIO DAN235ETL T 30.6/20.8

D7 1160000140 S.DIO DAP222 TL T 58.9/14

D8 1720000791 S.VCP HVC321B1TRF-E T 49.5/32.4

D9 1720000791 S.VCP HVC321B1TRF-E T 52.7/32.4

D10 1720000791 S.VCP HVC321B1TRF-E T 60.5/30

D11 1720000641 S.VCP 1SV284 (TPH3,F) T 52.7/33.6

D12 1720000641 S.VCP 1SV284 (TPH3,F) T 52.7/34.8

D13 1720000791 S.VCP HVC321B1TRF-E T 63.8/28.6

D14 1720000791 S.VCP HVC321B1TRF-E T 73.6/30.4

D15 1720000641 S.VCP 1SV284 (TPH3,F) T 63.8/31.3

D16 1720000641 S.VCP 1SV284 (TPH3,F) T 63.8/30

D17 1720000791 S.VCP HVC321B1TRF-E T 72.1/27.9

D18 1750000721 S.VCP HVC375BTRF-E T 69.8/33.3

D19 1160000140 S.DIO DAP222 TL B 120.5/17.8

D20 1720000471 S.VCP 1SV239 (TPH3,F) T 69.4/34.9

D21 1750001070 S.DIO DAN235ETL T 36.3/38.3

D22 1750000520 S.DIO DAN222TL T 124.7/54.5

D23 1790001260 S.DIO MA2S077-(TX) T 125.6/39.2

D24 1790001260 S.DIO MA2S077-(TX) B 50.7/53.2

DESCRIPTION

M.

H/V

LOCATION

[MAIN UNIT]

REF ORDER

NO. NO.

D25 1790001260 S.DIO MA2S077-(TX) B 49.3/50.8

D26 1750000711 S.VCP HVC350BTRF-E B 17.7/36

D27 1750000711 S.VCP HVC350BTRF-E B 16.2/36

D28 1750000370 S.DIO DA221 TL T 10/37.5

D29 1790001250 S.DIO MA2S111-(TX) T 12/39.5

D30 1750000721 S.VCP HVC375BTRF-E B 8.6/44.7

D31 1790001250 S.DIO MA2S111-(TX) T 8.5/43.7

D32 1750001080 S.DIO RB886G T2R T 64.1/76.5

D33 1750001080 S.DIO RB886G T2R T 65.8/75.8

D34 1750000721 S.VCP HVC375BTRF-E B 8.6/47.4

D35 1790001260 S.DIO MA2S077-(TX) B 17.9/48.1

D36 1790001240 S.DIO MA2S728-(TX) B 16.5/48.1

D37 1750000370 S.DIO DA221 TL T 75.5/67.6

D38 1750000511 S.DIO UX9401F-STD/TR

[EXP-01], [EUR-01] only T 30/66

D39 1710001061 DIO L407CDB [USA-01] only

D42 1750001360 S.DIO L709CER (9401) T 34.6/58.7

D45 1750000520 S.DIO DAN222TL T 91.8/57.5

D46 1750000520 S.DIO DAN222TL T 89.6/57.5

D47 1790001211 S.DIO 1SS375-TL-E B 29.2/63.8

D48 1750000520 S.DIO DAN222TL B 93/61.5

D49 1790001211 S.DIO 1SS375-TL-E B 6/52.8

D50 1750000370 S.DIO DA221 TL B 97.2/65.8

D51 1790001211 S.DIO 1SS375-TL-E B 3.9/79.7

D52 1750000520 S.DIO DAN222TL B 132.5/41

D53 1790001250 S.DIO MA2S111-(TX) B 133.3/47.3

D55 1750000370 S.DIO DA221 TL B 108.8/57.4

D56 1750000370 S.DIO DA221 TL T 108.8/60.6

D57 1750000370 S.DIO DA221 TL B 95.1/65.8

D58 1750000520 S.DIO DAN222TL T 94/57.5

D59 1750000520 S.DIO DAN222TL B 104/80.4

D62 1790000700 DIO DSA3A1

D63 1750000520 S.DIO DAN222TL B 110.3/80.9

D65 1750000520 S.DIO DAN222TL B 129.7/58.9

D66 1790001621 S.DIO 1SV308 (TPL3,F) T 33.9/38.8

D67 1790001621 S.DIO 1SV308 (TPL3,F) T 33.9/37.5

D68 1790001621 S.DIO 1SV308 (TPL3,F) T 29.9/23.2

D69 1790001621 S.DIO 1SV308 (TPL3,F) T 31.2/23.2

D70 1750000351 S.DIO 1SV252 (TE85L,F) T 73.6/75.5

D71 1730002410 S.ZEN MA8200-H (TX) T 118.3/86.3

FI1 2020001410 CER CFWLB450KGFA-B0

FI2 2020002180 S.CER CFWKA450KHFA-R0 T 15.4/9.3

FI3 2030000500 S.MLH FL-401 (46.35 MHz) T 24.7/28.4

FI4 2030000150 S.MLH FL-335 (46.350 MHz) T 35.6/28.4

FI5 2040001440 S.LC NFE31PT152Z1E9L B 94.5/77

FI6 2040001440 S.LC NFE31PT152Z1E9L B 94.5/73.7

FI7 2040001440 S.LC NFE31PT152Z1E9L [USA-01] only B 94.5/70.3

X1 6050012380 S.XTL CR-826 (15.3 MHz) T 84.2/34.7

X2 6050011730 S.XTL CR-765 (3.6864 MHz) T 48.3/11.6

X3 6070000191 S.DCR CDBKB450KCAY24-R0 T 37.1/10.3

X4 6050012320 S.XTL CR-818 (4.194304 MHz) T 139.1/21.9

X5 6050011720 S.XTL CR-764 (19.6608 MHz) T 120.5/44.3

L1 6200004660 S.COL MLF1608A 1R8K-T T 82.7/54.3

L2 6200003540 S.COL MLF1608D R22K-T B 34.4/14.7

L3 6200004480 S.COL MLF1608D R82K-T B 29.7/16.2

L4 6200007911 S.COL ELJRF 18NJFB B 75.9/48.3

L5 6200007170 S.COL MLF1608A 3R3K-T T 49.5/31

L6 6200007170 S.COL MLF1608A 3R3K-T T 52.7/31

L7 6200007170 S.COL MLF1608A 3R3K-T T 60.5/28.6

L8 6200007170 S.COL MLF1608A 3R3K-T T 74/27.5

L9 6200007170 S.COL MLF1608A 3R3K-T T 69.8/32

L10 6200009910 S.COL C6342A-88NG-A T 51.2/39.2

L11 6200003640 S.COL MLF1608E 100K-T T 48.3/33.6

L12 6200009910 S.COL C6342A-88NG-A T 61.6/35.5

L13 6200007170 S.COL MLF1608A 3R3K-T T 63.8/27.2

L14 6200003640 S.COL MLF1608E 100K-T T 60/31.4

L15 6200012450 S.COL 0.25-1.9-8TL 73N T 73.3/35.9

L16 6200008090 S.COL LQW2BHN68NJ03L T 69.5/28

L17 6200003640 S.COL MLF1608E 100K-T T 73.7/32.6

L18 6130003000 S.COL #617DB-1714=P3 B 39/36.2

L19 6130003000 S.COL #617DB-1714=P3 B 34.5/42.6

L20 6200009181 S.COL ELJRE R10JFA T 57.3/48.3

L21 6200007911 S.COL ELJRF 18NJFB B 66.3/51.2

L22 6200005721 S.COL ELJRE 33NGFA B 40.6/48.1

L23 6200005721 S.COL ELJRE 33NGFA B 45.5/48.1

L24 6130003000 S.COL #617DB-1714=P3 B 27/36.2

L25 6200009151 S.COL ELJRE 82NJFA B 54.2/53.4

L26 6200007750 S.COL LQW2BHN56NJ03L B 20.3/36.7

L27 6200009181 S.COL ELJRE R10JFA B 66.5/69.4

L28 6200007750 S.COL LQW2BHN56NJ03L B 12.5/36.7

L29 6200009171 S.COL ELJRE 47NJFA B 70.5/70.8

L30 6200009171 S.COL ELJRE 47NJFA T 72.6/72.7

L31 6200008090 S.COL LQW2BHN68NJ03L B 8.3/42

L32 6200008090 S.COL LQW2BHN68NJ03L B 8.4/50

L33 6200010050 S.COL AS080547-47N T 33.3/73.9

L34 6200007750 S.COL LQW2BHN56NJ03L B 13.2/51.7

L35 6200006991 S.COL ELJRE 56NGFA B 20.1/50.7

L36 6200010420 S.COL FHW1210HC 1R0JGT B 39.2/66

L37 6200010050 S.COL AS080547-47N T 30/58.5

L38 6200010050 S.COL AS080547-47N T 21.6/58

L39 6200010050 S.COL AS080547-47N T 12.5/57.5

L40 6200010050 S.COL AS080547-47N T 10.5/81

L41 6200002861 S.COL NLV25T-4R7J T 122.3/54.4

L42 6200005011 S.COL NLV25T-100J T 40.7/42.1

L43 6200010680 S.COL C2520C-R22G-A (0.22U) T 42.1/34.9

L44 6200010740 S.COL C2520C-R27G-A T 37.8/35.3

L45 6200003960 S.COL MLF1608A 1R0K-T T 71.3/72.7

L46 6200005661 S.COL ELJRE 10NGFA T 78.3/42.3

DESCRIPTION

M.=Mounted side (T: Mounted on the Top side, B: Mounted on the Bottom side)

7 - 2

M.

S.=Surface mount

H/V

LOCATION

Page 22

[MAIN UNIT]

REF ORDER

NO. NO.

R1 7030005060 S.RES ERJ2GEJ 333 X (33 k) B 38.1/5.8

R2 7510001730 S.TMR ERTJOEP 473J T 90.4/35.6

R3 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 79/11.9

R4 7030005700 S.RES ERJ2GEJ 274 X (270 k) B 88.5/18.9

R5 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 90.4/34

R6 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 84/19.4

R7 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 84/17.5

R8 7410001130 S.ARY EXB28V102JX T 86.1/52.4

R9 7030007570 S.RES ERJ2GEJ 122 X (1.2 k) B 34.3/11.6

R10 7030007060 S.RES ERJ2GEJ 684X (680 k) B 35.8/13.7

R11 7030010040 S.RES ERJ2GEJ-JPW T 8.5/9.2

R12 7030004970 S.RES ERJ2GEJ 470 X (47) T 31/17.2

R13 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 8.8/15.9

R14 7030005210 S.RES ERJ2GEJ 822 X (8.2 k) T 7.5/7.4

R15 7030005070 S.RES ERJ2GEJ 683 X (68 k) B 93.3/14.4

R17 7030007570 S.RES ERJ2GEJ 122 X (1.2 k) B 93.3/15.3

R18 7030008300 S.RES ERJ2GEJ 184 X (180 k) B 79/11.8

R19 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 89.3/9

R20 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 85.6/8.3

R21 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 86.6/8.3

R22 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 38.1/7.5

R23 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 38.1/9.2

R24 7030005060 S.RES ERJ2GEJ 333 X (33 k) B 37.2/10.5

R25 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 100.9/51.4

R26 7030005000 S.RES ERJ2GEJ 471 X (470) B 87.5/5.3

R27 7030004980 S.RES ERJ2GEJ 101 X (100) T 53.9/5.6

R28 7030010040 S.RES ERJ2GEJ-JPW T 59.4/5.6

R29 7030005000 S.RES ERJ2GEJ 471 X (470) T 116.4/14.5

R30 7030005170 S.RES ERJ2GEJ 474 X (470 k) B 37.2/9.2

R31 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 36.3/9.2

R32 7030005720 S.RES ERJ2GEJ 563 X (56 k) B 37.2/7.5

R33 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 80.7/8.4

R34 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 80.7/7.2

R35 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 77.6/9.5

R36 7030005030 S.RES ERJ2GEJ 152 X (1.5 k) B 27/14.7

R37 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 15.2/8.6

R38 7030005210 S.RES ERJ2GEJ 822 X (8.2 k) T 22.9/6.2

R39 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 24/9.1

R40 7030005170 S.RES ERJ2GEJ 474 X (470 k) T 25.9/10.6

R41 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 27.6/6.2

R42 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 94.8/11.7

R43 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 94.8/10

R44 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 90.7/11.9

R45 7030005220 S.RES ERJ2GEJ 223 X (22 k) B 92.8/10

R46 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 92.1/14.1

R47 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 92.1/13.1

R48 7030005060 S.RES ERJ2GEJ 333 X (33 k) B 50.9/8.6

R49 7030005160 S.RES ERJ2GEJ 105 X (1 M) B 49.7/13.7

R50 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 49.7/11

R51 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 52.4/7

R52 7030007340 S.RES ERJ2GEJ 153 X (15 k) T 59.1/12.5

R53 7030005000 S.RES ERJ2GEJ 471 X (470) T 86.2/37.7

R54 7030010040 S.RES ERJ2GEJ-JPW B 78.7/36.4

R55 7030005290 S.RES ERJ2GEJ 682 X (6.8 k) T 81.8/25.3

R56 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 77.7/48.4

R57 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 28.3/14.3

R58 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 27.6/9

R59 7030005170 S.RES ERJ2GEJ 474 X (470 k) T 27.6/8.1

R60 7030005000 S.RES ERJ2GEJ 471 X (470) T 30.9/10.2

R61 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 28.8/8.5

R62 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 32.2/11.9

R63 7030005220 S.RES ERJ2GEJ 223 X (22 k) B 92.8/8.3

R64 7030005220 S.RES ERJ2GEJ 223 X (22 k) B 92.8/6.5

R65 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 50.9/9.5

R66 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 86.6/11.8

R67 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 53.4/7

R68 7030010040 S.RES ERJ2GEJ-JPW B 53.7/17.9

R69 7030010040 S.RES ERJ2GEJ-JPW T 85.6/13.6

R71 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 57.7/6.3

R72 7030007290 S.RES ERJ2GEJ 222 X (2.2 k) T 64.9/55.6

R73 7030005000 S.RES ERJ2GEJ 471 X (470) B 83.2/26.9

R74 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 81.8/25.3

R75 7030009140 S.RES ERJ2GEJ 272 X (2.7 k) B 79.2/34

R76 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 80.3/29.1

R77 7030005580 S.RES ERJ2GEJ 560 X (56) T 78.2/47.2

R78 7030005070 S.RES ERJ2GEJ 683 X (68 k) B 81.5/34

R79 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 74.8/50

R80 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 70/50.9

R81 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 55.5/31.4

R82 7030005110 S.RES ERJ2GEJ 224 X (220 k) B 66.3/33.3

R83 7030008400 S.RES ERJ2GEJ 182 X (1.8 k) T 32.6/10.2

R84 7030007280 S.RES ERJ2GEJ 331 X (330) T 24.6/20.3

R85 7030005110 S.RES ERJ2GEJ 224 X (220 k) T 24.6/21.2

R86 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) B 30/10.5

R87 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) T 32.2/20.6

R88 7030005120 S.RES ERJ2GEJ 102 X (1 k) B 91.7/6.5

R90 7030005000 S.RES ERJ2GEJ 471 X (470) B 89.4/18.9

R91 7030005700 S.RES ERJ2GEJ 274 X (270 k) T 85.6/11.8

R92 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 87.3/13.4

R93 7030005310 S.RES ERJ2GEJ 124 X (120 k) T 83.9/8.2

R94 7030005080 S.RES ERJ2GEJ 823 X (82 k) T 108/34.7

R95 7030005720 S.RES ERJ2GEJ 563 X (56 k) T 108/33.8

R96 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 63.7/15.5

R97 7030005060 S.RES ERJ2GEJ 333 X (33 k) B 53.3/16.6

R98 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) B 62.1/19.4

R99 7030007350 S.RES ERJ2GEJ 393 X (39 k) B 60.2/19.4

R100 7030005030 S.RES ERJ2GEJ 152 X (1.5 k) B 77.9/34.4

R101 7030008280 S.RES ERJ2GEJ 271 X (270) B 79.2/29.1

R102 7030005530 S.RES ERJ2GEJ 100 X (10) T 23/20.3

R103 7030005600 S.RES ERJ2GEJ 273 X (27 k) B 29.9/23.8

R104 7030007280 S.RES ERJ2GEJ 331 X (330) T 26.9/22.6

R105 7030005600 S.RES ERJ2GEJ 273 X (27 k) B 30.9/23.8

R106 7030007270 S.RES ERJ2GEJ 151 X (150) T 34.3/22.5

R107 7030007340 S.RES ERJ2GEJ 153 X (15 k) B 129.7/52.3

DESCRIPTION

M.

H/V

LOCATION

[MAIN UNIT]

REF ORDER

NO. NO.

R108 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 82.3/18.9

R109 7030005700 S.RES ERJ2GEJ 274 X (270 k) B 81.3/18.9

R110 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 78.4/20.2

R111 7030005050 S.RES ERJ2GEJ 103 X (10 k) T 95.9/28.3

R112 7030005700 S.RES ERJ2GEJ 274 X (270 k) T 80.8/20.1

R113 7030005240 S.RES ERJ2GEJ 473 X (47 k) B 57.9/19.4

R114 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 53.7/13.3

R115 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 114.4/18.4

R116 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 85.3/7.3

R118 7030006610 S.RES ERJ2GEJ 394 X (390 k) T 89.5/11.7

R120 7030009280 S.RES ERJ2GEJ 391 X T 30.3/34.3

R122 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 32.3/35.2

R123 7030005600 S.RES ERJ2GEJ 273 X (27 k) T 33.5/35.2

R125 7030004970 S.RES ERJ2GEJ 470 X (47) T 35/34

R127 7030005050 S.RES ERJ2GEJ 103 X (10 k) B 79.1/18.3

R128 7030008290 S.RES ERJ2GEJ 183 X (18 k) T 112.1/45.1

R129 7030005040 S.RES ERJ2GEJ 472 X (4.7 k) T 112.1/44.1

R130 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 104.9/43.2

R131 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 104.9/44.1

R132 7030004980 S.RES ERJ2GEJ 101 X (100) T 114.4/17.5

R134 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 128.9/26.3

R135 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 128.9/25.3

R136 7030005160 S.RES ERJ2GEJ 105 X (1 M) T 128.9/24.2

R139 7410001140 S.ARY EXB28V104JX T 130.6/20.6

R140 7030011000 S.RES RR0510P-392-D (3.9 k) T 48.1/47.2

R141 7030008340 S.RES RR0510P-182-D (1.8 k) T 50.8/45.4

R142 7030010040 S.RES ERJ2GEJ-JPW T 49/47.2

R143 7030011000 S.RES RR0510P-392-D (3.9 k) T 58.7/42.2

R144 7030008340 S.RES RR0510P-182-D (1.8 k) T 61.7/40.4

R145 7030010040 S.RES ERJ2GEJ-JPW T 59.6/42.2

R146 7030011000 S.RES RR0510P-392-D (3.9 k) T 71.8/45.8

R147 7030008340 S.RES RR0510P-182-D (1.8 k) T 70/41.9

R148 7030010040 S.RES ERJ2GEJ-JPW T 71.8/44.9

R149 7030005310 S.RES ERJ2GEJ 124 X (120 k) T 69.1/36.3

R150 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 89.8/15.5

R151 7030005060 S.RES ERJ2GEJ 333 X (33 k) T 91/16.1

R152 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 88.9/16.4

R153 7030007300 S.RES ERJ2GEJ 332 X (3.3 k) T 39.9/32.2

R154 7030004970 S.RES ERJ2GEJ 470 X (47) T 42.9/40.1

R155 7030005120 S.RES ERJ2GEJ 102 X (1 k) T 41.7/32.4

R156 7030004970 S.RES ERJ2GEJ 470 X (47) T 42.5/41.3

R157 7030005090 S.RES ERJ2GEJ 104 X (100 k) B 33.7/23.6

R158 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 112.1/42.3

R159 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 112.1/40.5

R160 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 113.8/38.7

R161 7030005070 S.RES ERJ2GEJ 683 X (68 k) T 104.9/46.8

R162 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 128.2/14.4

R163 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 128.7/16.3

R164 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 129.4/14.4

R165 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 128.7/17.8

R166 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 128.7/18.7

R167 7030005230 S.RES ERJ2GEJ 334 X (330 k) T 129.8/16.2

R168 7030006581 S.RES ERA3YED 122V (1.2 k) T 53.6/47.5

R169 7030007230 S.RES ERA3YED 102V (1 k) T 63.8/42.6

R170 7030010390 S.RES ERA3YED 821V (820) T 74.1/43.2

R171 7030005090 S.RES ERJ2GEJ 104 X (100 k) T 56.3/46.7

R172 7030008280 S.RES ERJ2GEJ 271 X (270) B 36.4/46.4

R173 7030007270 S.RES ERJ2GEJ 151 X (150) B 39/31.2

R174 7030004980 S.RES ERJ2GEJ 101 X (100) B 34.6/38.7

R175 7030004980 S.RES ERJ2GEJ 101 X (100) B 33/38.7

R176 7030005590 S.RES ERJ2GEJ 680 X (68) B 31.3/37.4

R177 7030005590 S.RES ERJ2GEJ 680 X (68) B 31.3/34.9

R178 7030005240 S.RES ERJ2GEJ 473 X (47 k) T 113.8/37.8