Page 1

SERVICE

MANUAL

UHF FM TRANSCEIVERS

Page 2

6-9-16, Kamihigashi, Hirano-ku, Osaka 547-0002, Japan

Phone : 06 6793 5302

Fax : 06 6793 0013

Communication Equipment

Himmelgeister Str. 100, D-40225 Düsseldorf, Germany

Phone: 0211 346047 Fax : 0211 333639

URL : http://www.icomeurope.com

Unit 9, Sea St., Herne Bay, Kent, CT6 8LD, U.K.

Phone: 01227 741741 Fax : 01227 741742

URL : http://www.icomuk.co.uk

Zac de la Plaine, Rue Brindejonc des Moulinais

BP 5804, 31505 Toulouse Cedex, France

Phone: 561 36 03 03 Fax : 561 36 03 00

URL : http://www.icom-france.com

Crta. de Gracia a Manresa Km. 14,750

08190 Sant Cugat del Valles Barcelona, SPAIN

Phone: (93) 590 26 70 Fax : (93) 589 04 46

URL : http://www.icomspain.com

<

Corporate Headquarters

>

2380 116th Avenue N.E., Bellevue, WA 98004, U.S.A.

Phone: (425) 454-8155 Fax : (425) 454-1509

URL : http://www.icomamerica.com

<

Customer Service

>

Phone: (425) 454-7619

A.C.N. 006 092 575

290-294 Albert Street, Brunswick, Victoria, 3056, Australia

Phone: 03 9387 0666 Fax : 03 9387 0022

URL : http://www.icom.net.au

6F No. 68, Sec. 1 Cheng-Teh Road, Taipei, Taiwan, R.O.C.

Phone: (02) 2559 1899 Fax : (02) 2559 1874

3071 #5 Road, Unit 9, Richmond, B.C., V6X 2T4, Canada

Phone: (604) 273-7400 Fax : (604) 273-1900

URL : http://www.icomcanada.com

INTRODUCTION

DANGER

ORDERING PARTS

REPAIR NOTES

This service manual describes the latest service information

for the

IC-F4GT and IC-F4GS

at the time of publication.

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 16 V. Such a connection

could cause a fire hazard and/or electric shock.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when con-

necting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100mW)

to the antenna connector. This could damage the transceiver’s front end.

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1130007610 S.IC µPD3140GS IC-F4GT MAIN UNIT 1 pieces

8810009510 Screw BT M2 x 4 NI-ZU IC-F4GS Chassis 10 pieces

Addresses are provided on the inside back cover for your

convenience.

1. Make sure a problem is internal before disassembling the transceiver.

2. DO NOT open the transceiver until the transceiver is disconnected from its power source.

3. DO NOT force any of the variable components. Turn them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An insulated turning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the transceiver is defective.

6. DO NOT transmit power into a signal generator or a sweep generator.

7. ALWAYS connect a 40 dB to 50 dB attenuator between the transceiver and a deviation meter or spectrum analyzer when

using such test equipment.

8. READ the instructions of test equipment thoroughly before connecting equipment to the transceiver.

To upgrade quality, all electrical or mechanical parts and

internal circuits are subject to change without notice or obligation.

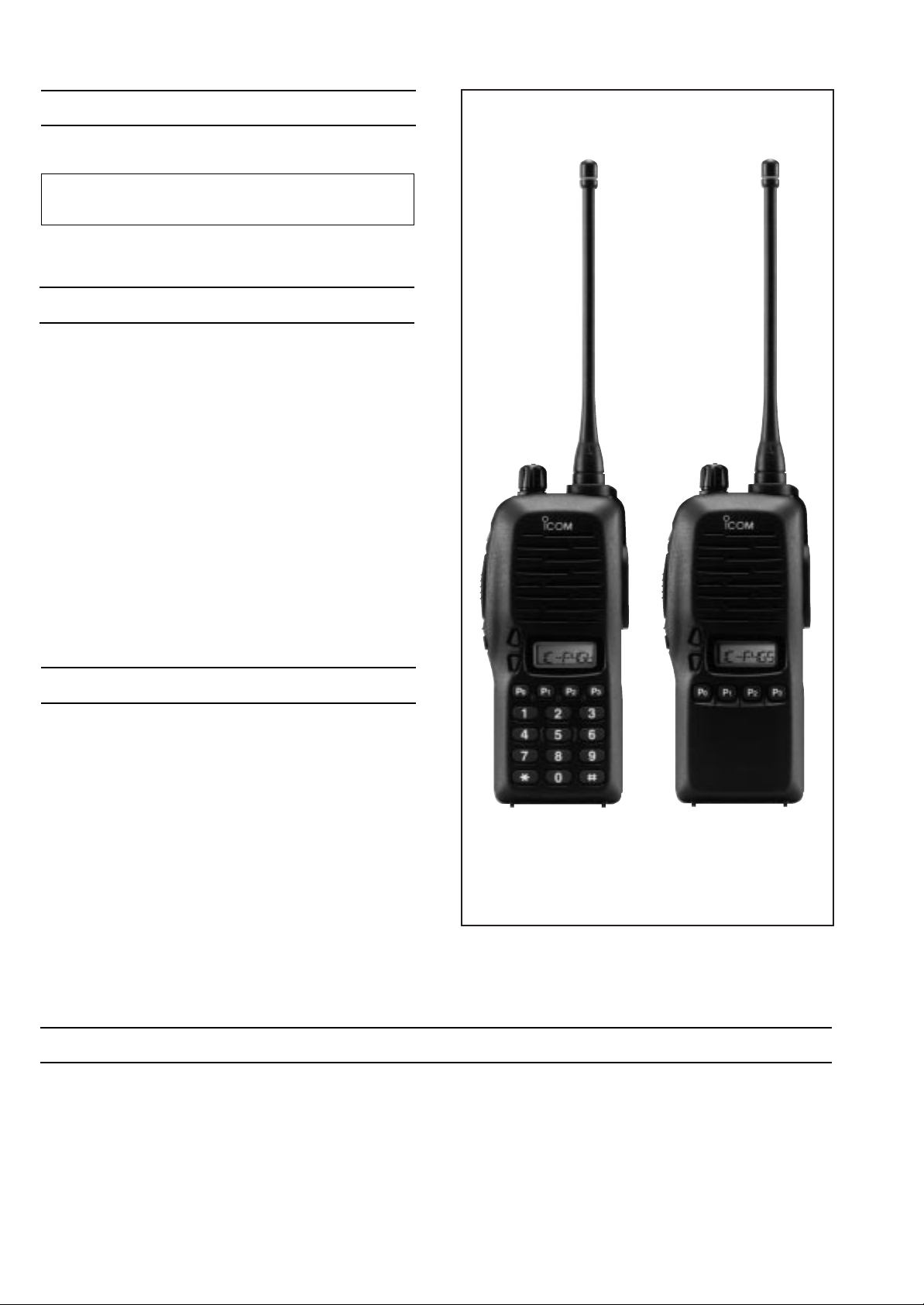

IC-F4GT IC-F4GS

Page 3

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 DISASSEMBLY AND OPTION INSTRUCTIONS

3-1 DISASSEMBLY INSTRUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3-2 OPTIONAL UNIT INSTALLATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

SECTION 4 CIRCUIT DESCRIPTION

4-1 RECEIVER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4-2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4-3 PLL CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

4-4 POWER SUPPLY CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4-5 CPU PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5-2 PLL ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5-3 SOFTWARE ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5

SECTION 6 PARTS LIST

SECTION 7 MECHANICAL PARTS AND DISASSEMBLY

SECTION 8 SEMI-CONDUCTOR INFORMATION

SECTION 9 BOARD LAYOUTS

SECTION 10 BC-137 OPTIONAL DESKTOP CHARGER INFORMATION

10-1 PARTS LIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10-2 DISASSEMBLY INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10-3 VOLTAGE DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

10-4 BOARD LAYOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

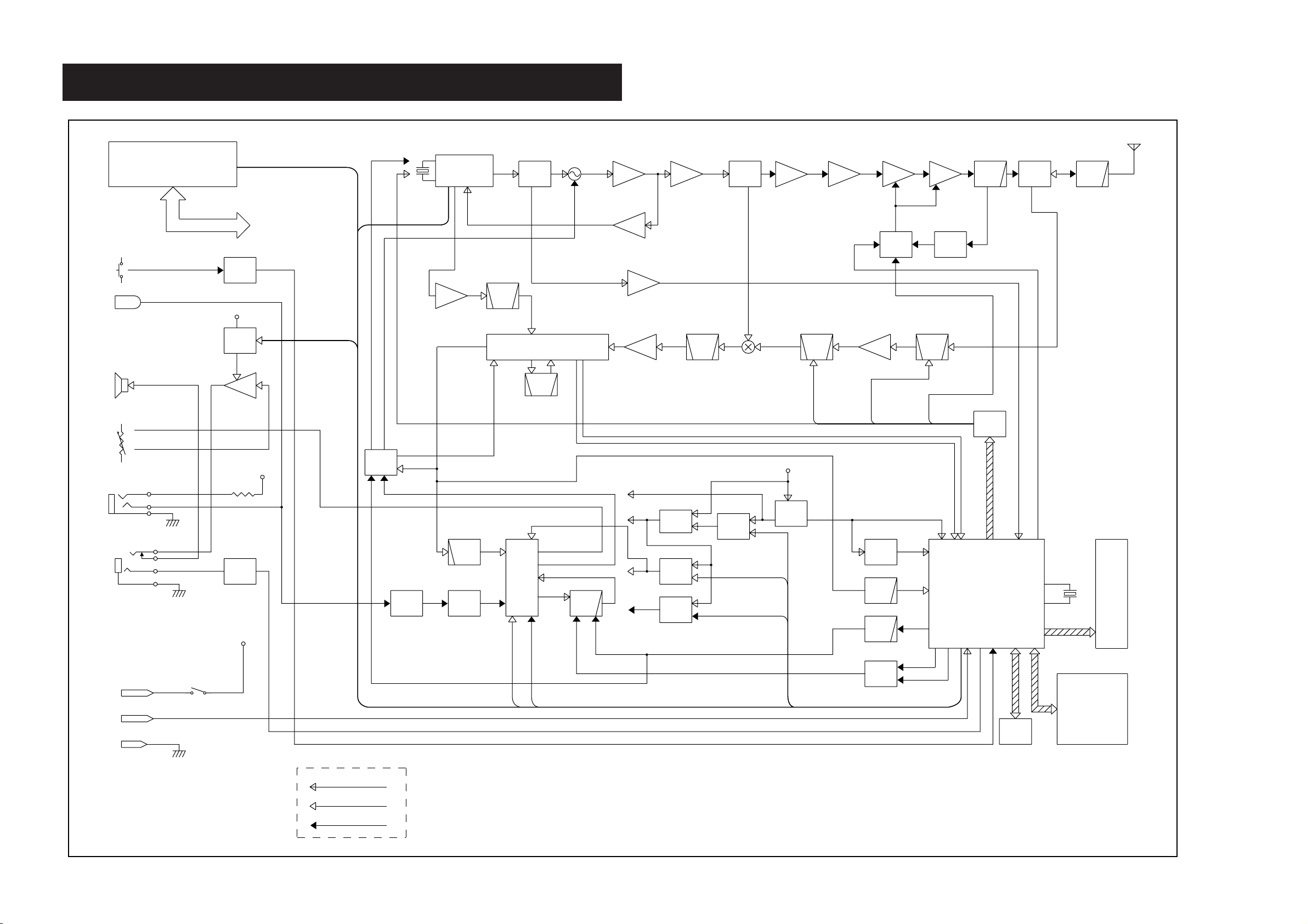

SECTION 11 BLOCK DIAGRAM

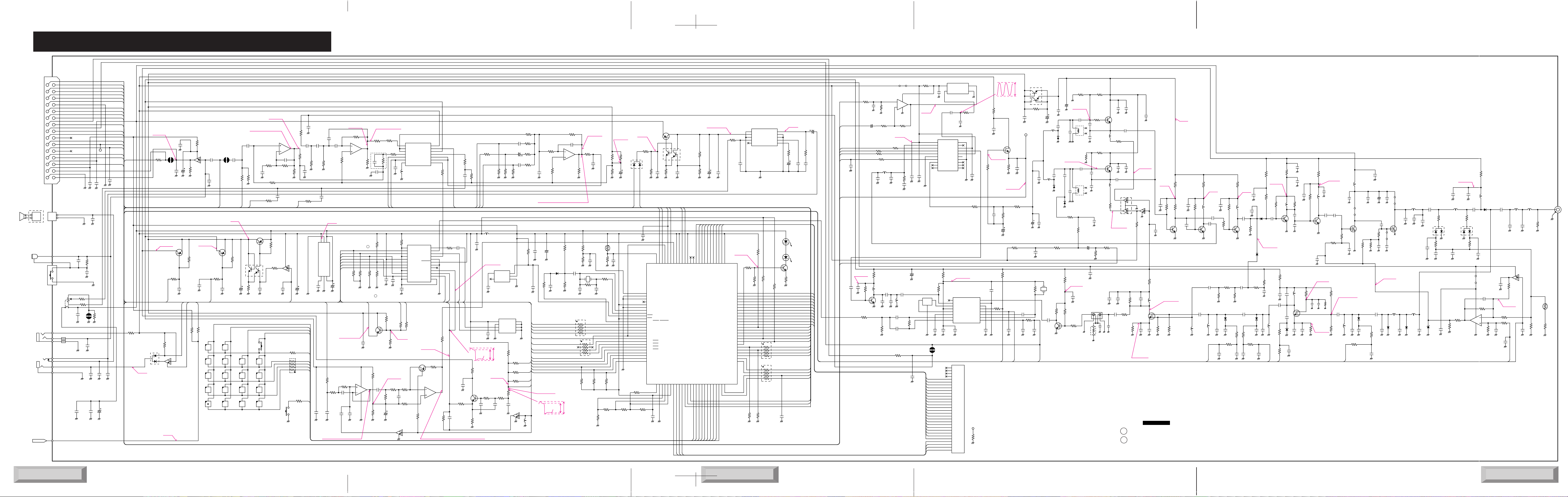

SECTION 12 VOLTAGE DIAGRAM

Page 4

1 - 1

SECTION 1 SPECIFICATIONS

‘‘

GENERAL

• Frequency coverage : 440.000–470.000 MHz

• Type of emission : 8K50F3E

• Number of channels : 32 ch (16 channels × 2 banks: 2-BANK version), 16 ch (16 channel version)

• Power supply requirement : 7.2 V DC (negative ground; supplied battery pack)

• Current drain (approx.) : Transmit at High (4.0 W) 1.55 A

at Low (1.0 W) 800 mA

Receive rated audio 250 mA

stand-by 70 mA

• Frequency stability : ±0.00025 %

• Usable temperature range : –30˚C to +60˚C; –22˚F to +140˚F

• Dimensions (projections not included) : 54(W) × 132(H) × 35(D) mm; 2

5

⁄32(W) × 5 3⁄16(H) × 1 3⁄8(D) in.

• Weight (with ant., BP-209) : 355 g; 12.5 oz.

‘‘

TRANSMITTER

• RF output power (at 7.2 V DC) : 4 W / 1 W (High / Low)

(with supplied battery pack)

• Modulation system : Variable reactance frequency modulation

• Maximum frequency deviation : ±2.5 kHz

• Spurious emissions : 73 dBc (typical)

• Adjacent channel power : 60 dB (typical)

• Transmitter audio distortion : Less than 3% at 1 kHz, 40% deviation

• Limitting charact of modulator : 70–100% of max. deviation

• Ext. microphone connector : 3-conductor 2.5(d) mm (

1

⁄10”)/2.2 kΩ

‘‘

RECEIVER

• Receive system : Double conversion superheterodyne system

• Intermediate frequencies : 1st 46.35 MHz

2nd 450 kHz

• Sensitivity : 0.3 µV at 12 dB SINAD (typical)

• Squelch sensitivity : 0.3 µV at threshold (typical)

• Adjacent channel selectivity : 65 dB (typical)

• Spurious response rejection : 70 dB (typical)

• Intermodulation rejection ratio : 70 dB (typical)

• Hum and noise : 40 dB (typical)

• Audio output power (at 7.2 V DC) : 500 mW typical at 5% distortion with an 8 Ω load

• Ext. speaker connector : 3-conductor 3.5(d) mm (

1

⁄8”)/8 Ω

Specifications are measured in accordance with EIA/TIA-603.

All stated specifications are subject to change without notice or obligation.

Page 5

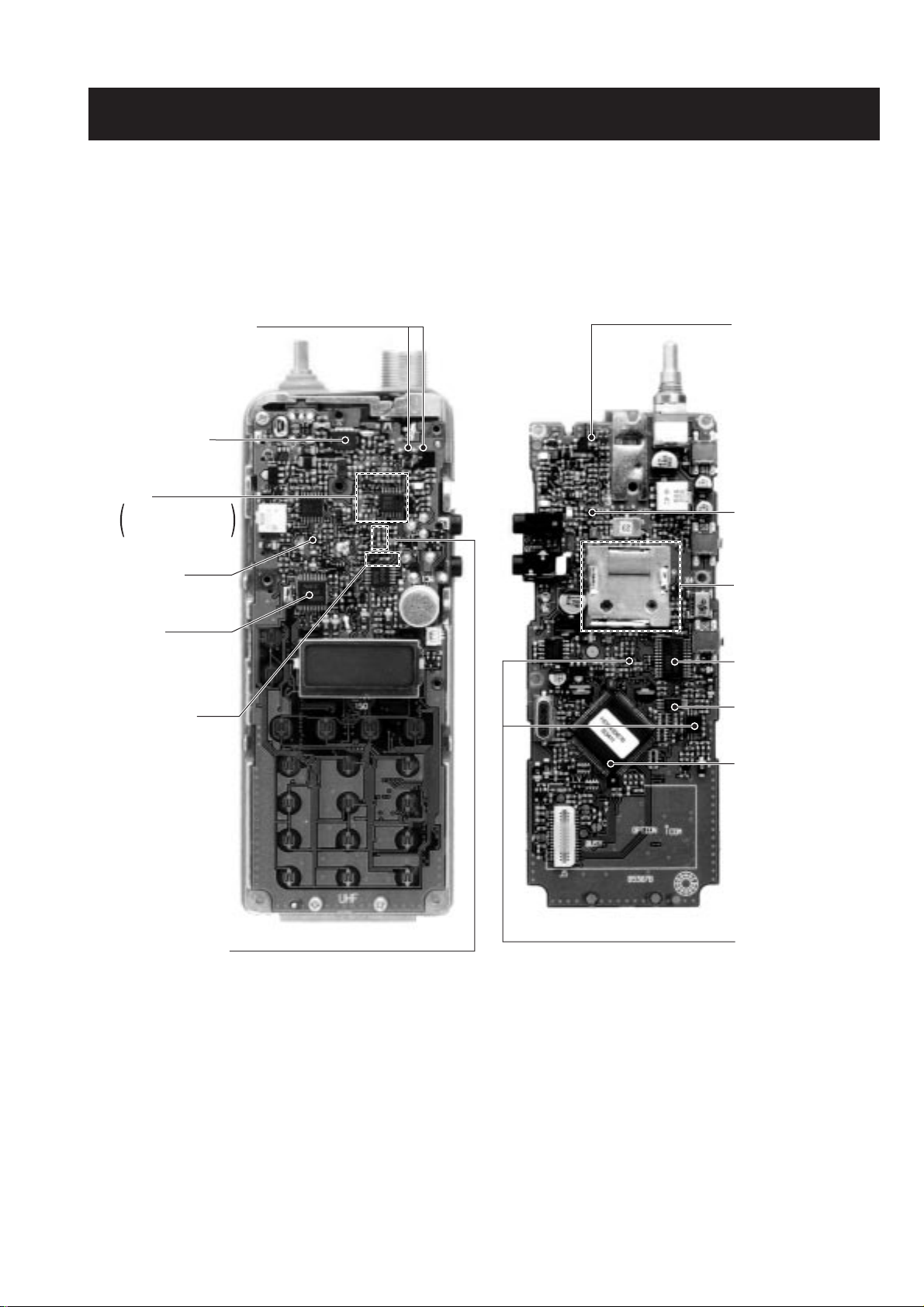

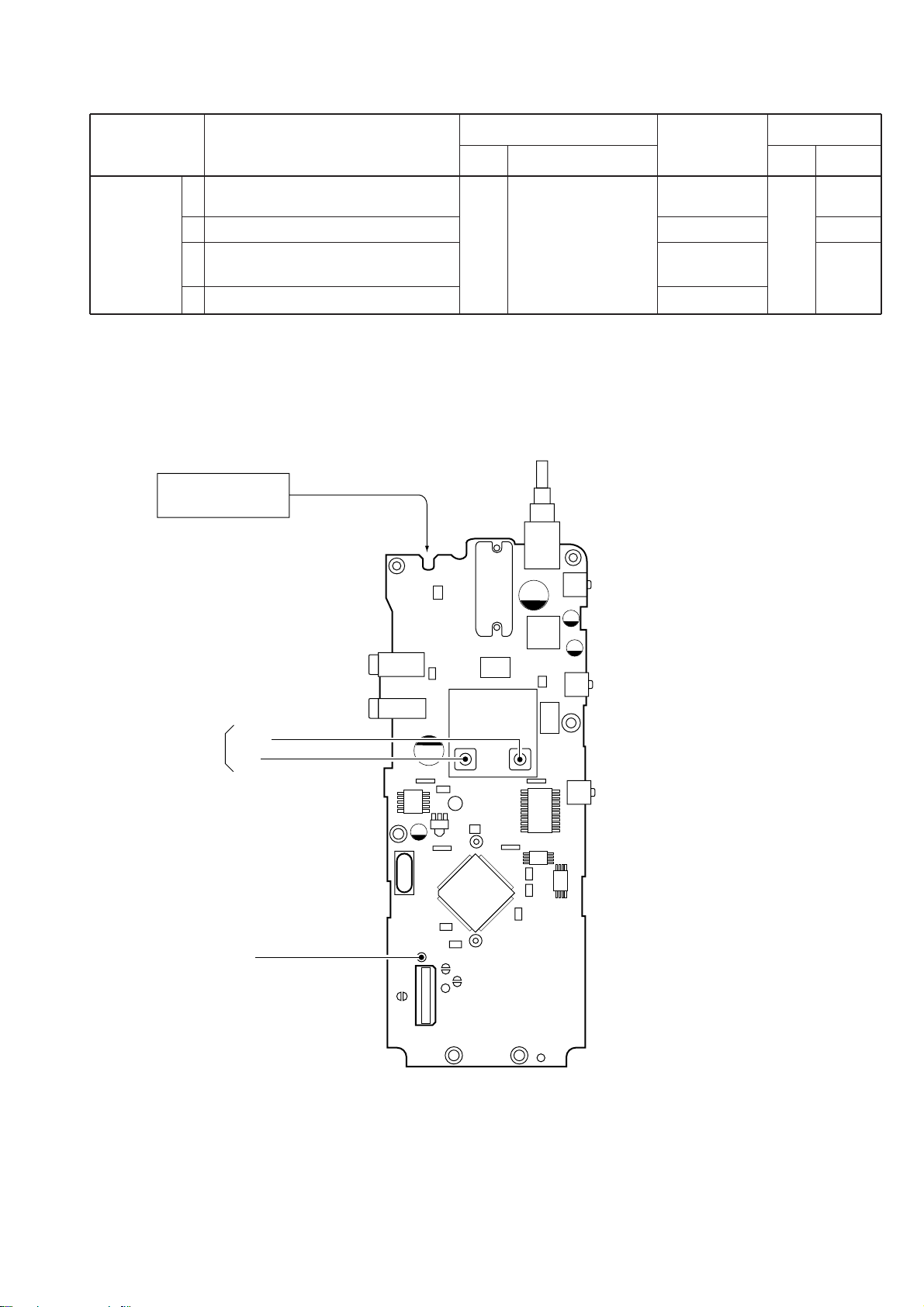

2 - 1

SECTION 2 INSIDE VIEWS

• MAIN UNIT

Antenna switcing circuit

(D1: 1SV307)

1st mixer

(Q13: 3SK239A)

VCO circuit

D/A converter

(IC10: M62363FP-650C)

EEPROM

(IC7: HN58X2432TI)

CPU

(IC8: HD6433876B34H)

Low pass filter circuit

Antenna switcing circuit

(D2, D8: MA77)

Power amplifier

(Q1: 2SK2974)

IF amplifier

(Q14: 2SC4215 O)

PLL IC

(IC1: µPD3140GS)

TX/RX switch

(D3, D4: MA77)

Mic amplifier circuit

APC

IC3A: NJM3403AV

Q37: DTA144EU

TOP VIEW

BOTTOM VIEW

Page 6

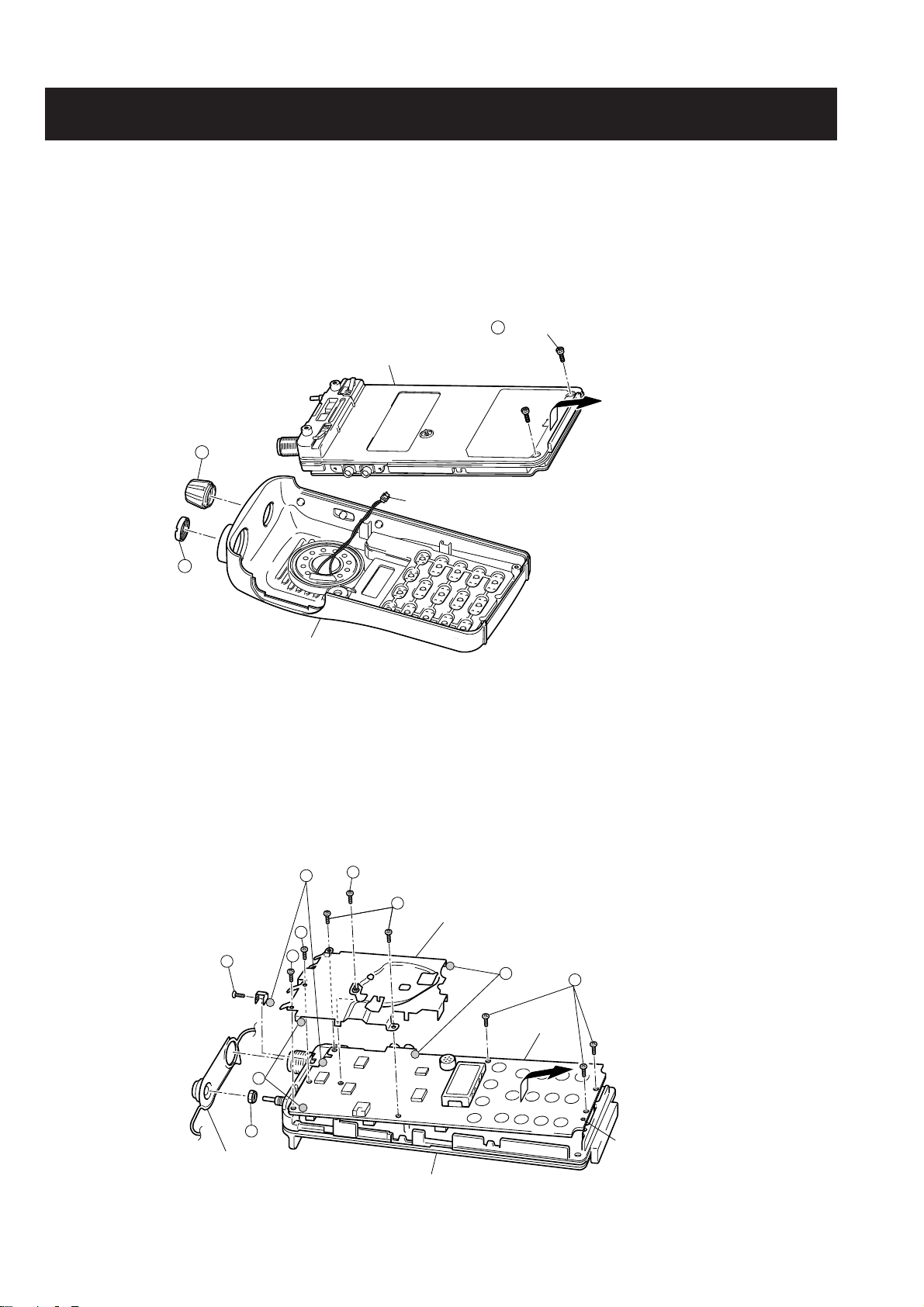

3 - 1

SECTION 3 DISASSEMBLY AND OPTION INSTRUCTIONS

3-1 DISASSEMBLY INSTRUCTION

• REMOVING THE CHASSIS PANEL

1 Unscrew 1 nut A, and remove 1 knob B.

2 Unscrew 2 screws C.

3 Take off the chassis in the direction of the arrow.

4 Unplug J6 to separate front panel and chassis.

• REMOVING THE MAIN UNIT

1 Remove the searing rubber.

2 Unsolder 3 points D, and unscrew 1 nut E.

3 Unscrew 3 screws F and 6 screws G (silver, 2 mm) to separate the chassis and the MAIN unit.

4 Take off the MAIN unit in the direction of the arrow.

(nickel, 2 mm) x 2

Front panel

Chassis

J6 (Speaker connector)

B

C

A

D

F

F

G

G

G

D

(silver, 2 mm) x 6

E

Shield cover

Guide holes

MAIN unit

Sealing rubber

Chassis

D

F

Page 7

3 - 2

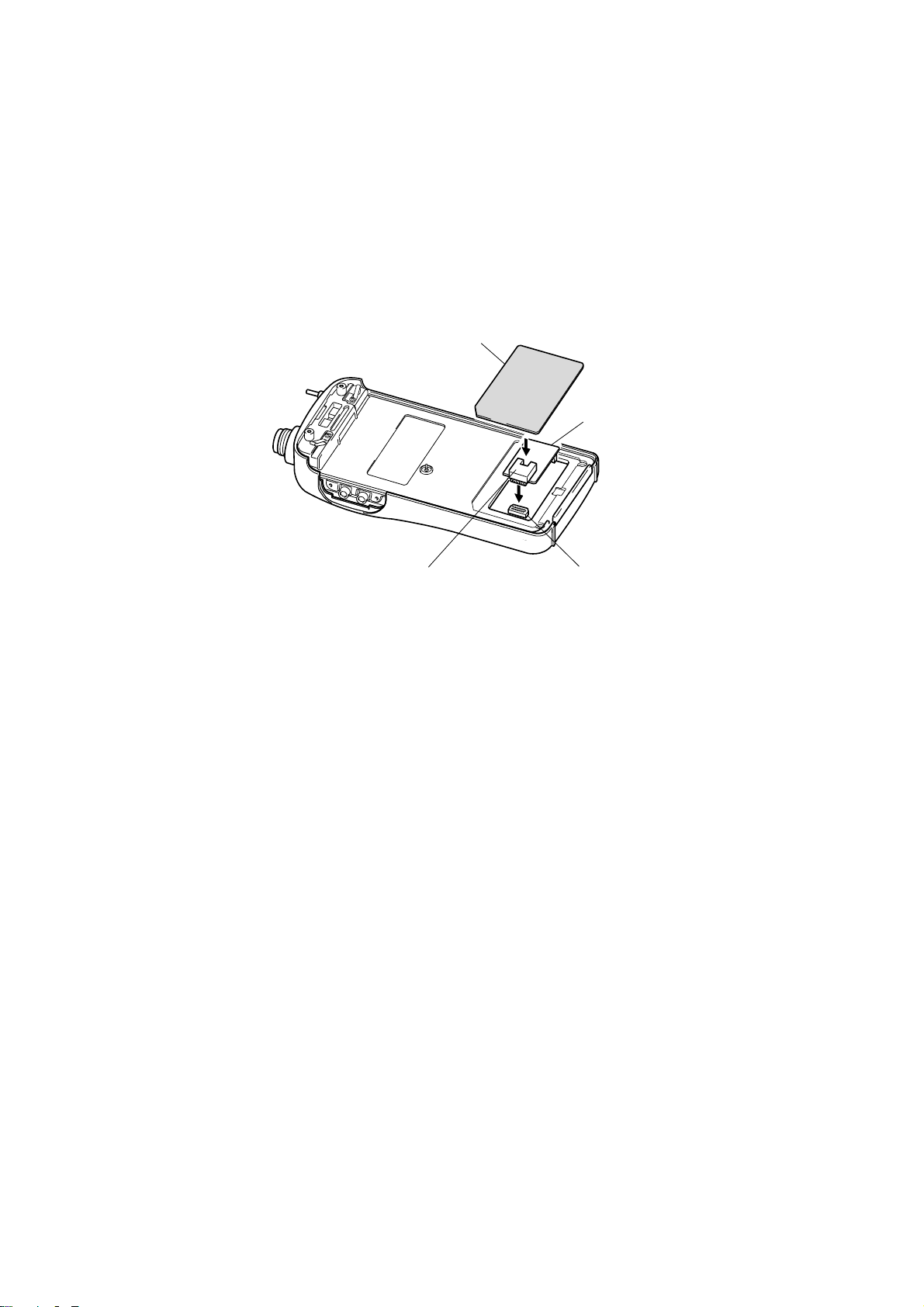

3-2 OPTIONAL UNIT INSTALLATIONS

1 Remove the option cover.

2 Remove the bottom protective paper of spoge.

3 Connect one of UT-96, UT-105, UT-108, UT-109, UT-110, UT-111, and UT-113 optional units to J5.

4 Replace the option cover to the chassis-hole.

SPONGE

Parts name : 1556 sponge

Order No. : 8930013545

Option cover

Optional unit

J5

Page 8

4 - 1

SECTION 4 CIRCUIT DESCRIPTION

4-1 RECEIVER CIRCUITS

4-1-1 ANTENNA SWITCHING CIRCUIT

The antenna switching circuit functions as a low-pass filter

while receiving. However, its impedance becomes very high

while D2 and D8 are turned ON. Thus transmit signals are

blocked from entering the receiver circuits. The antenna

switching circuit employs a λ⁄4 type diode switching system.

Received signals are passed through the low-pass filter (L1,

L2, C3, C8, C666). The filtered signals are applied to the λ⁄4

type antenna switching circuit (D2, D8).

The passed signals are then applied to the RF amplifier circuit.

4-1-2 RF CIRCUIT

The RF circuit amplifies signals within the range of frequency coverage and filters out-of-band signals.

The signals from the antenna switching circuit are amplified

at the RF amplifier (Q12) after passing through the tunable

bandpass filter (L17, D10, C85, C86). The amplified signals

are applied to the 1st mixer circuit (Q13) after out-of-band

signals are suppressed at the 3 stages tunable bandpass filter (D401, L18, C89, C406, D11, L402, C91, C92, C94, D12,

L19, C97, C98).

Varactor diodes are employed at the bandpass filters that

track the filters and are controlled by the CPU (IC8) via the

expander IC (IC10) using T1–T4 signals. These diodes tune

the centre frequency of an RF passband for wide bandwidth

receiving and good image response rejection.

4-1-3 1ST MIXER AND 1ST IF CIRCUITS

The 1st mixer circuit converts the received signal into a fixed

frequency of the 1st IF signal with a PLL output frequency.

By changing the PLL frequency, only the desired frequency

will pass through a crystal filter at the next stage of the 1st

mixer.

The signals from the RF circuit are mixed at the 1st mixer

(Q13) with a 1st LO signal coming from the VCO circuit to

produce a 46.35 MHz 1st IF signal.

The 1st IF signal is applied to a pair of crystal filters (FI1) to

suppress out-of-band signals. The filtered 1st IF signal is

applied to the IF amplifier (Q14), then applied to the 2nd

mixer circuit (IC2, pin 16).

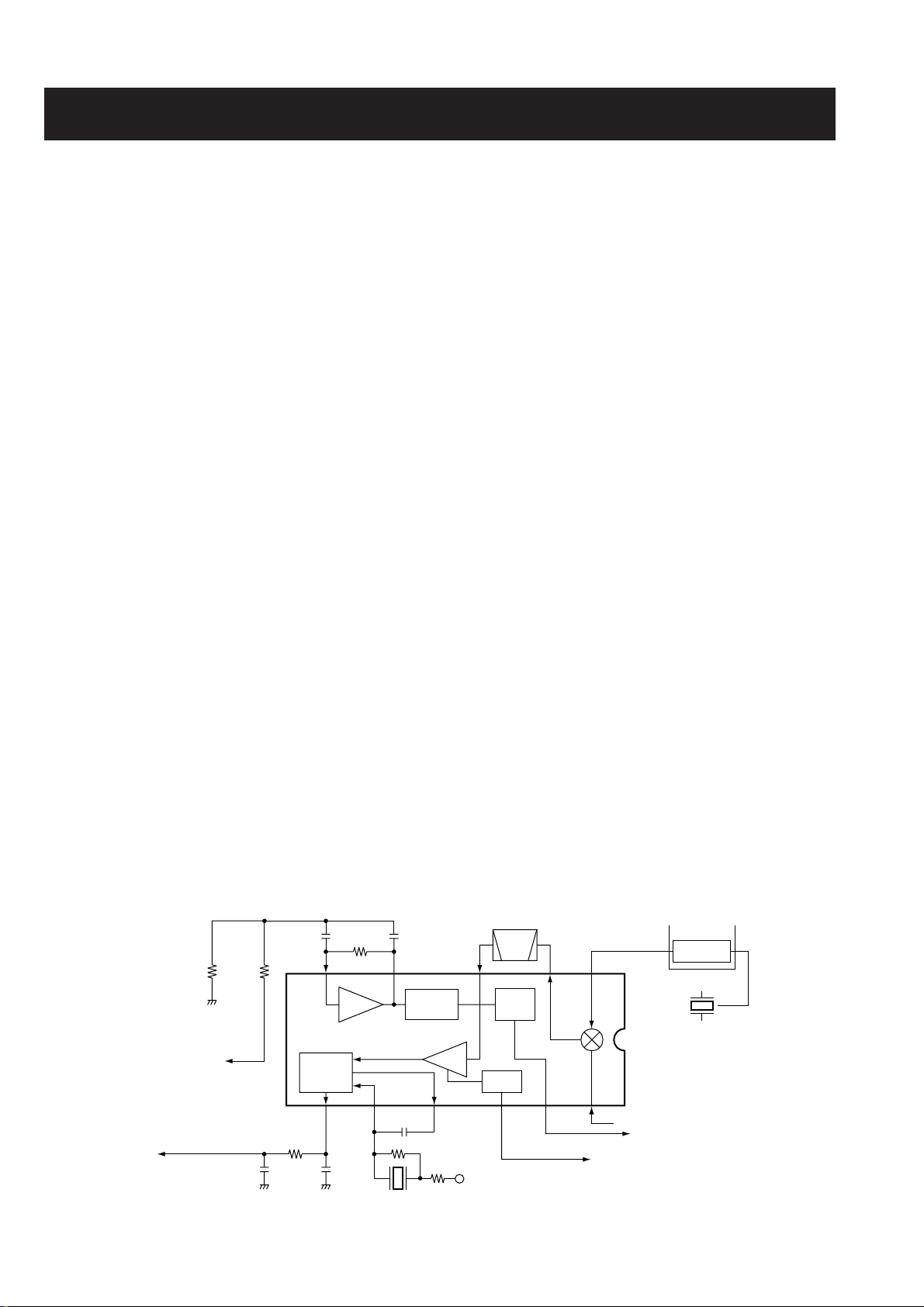

4-1-4 2ND IF AND DEMODULATOR CIRCUITS

The 2nd mixer circuit converts the 1st IF signal into a 2nd IF

signal. Adouble conversion superheterodyne system (which

converts receive signals twice) improves the image rejection

ratio and obtains stable receiver gain.

The 1st IF signal from the IF amplifier is applied to the 2nd

mixer section of the FM IF IC (IC2, pin 16), and is mixed with

the 2nd LO signal to be converted into a 450 kHz 2nd IF signal.

The FM IF IC contains the 2nd mixer, limiter amplifier, quadrature detector and active filter circuits. A 2nd LO signal

(45.9 MHz) is produced at the PLL circuit by tripling it’s reference frequency.

The 2nd IF signal from the 2nd mixer (IC2, pin 3) passes

through a ceramic filter (FI2) to remove unwanted heterodyned frequencies. It is then amplified at the limiter amplifier (IC2, pin 5) and applied to the quadrature detector (IC2,

pins 10, 11) to demodulate the 2nd IF signal into AF signals.

• 2ND IF AND DEMODULATOR CIRCUITS

Mixer

16

Limiter

amp.

2nd IF filter

450 kHz

PLL IC

IC1

X4

15.3 MHz

IC2 TA31136F

12

1st IF from the IF amplifier (Q14)

"SD" signal to the CPU pin 98

11109

87 5 3

AF signal "DET"

R5

X3

R86

C122

C121

R88R87

R83

"SQLIN" signal to the

D/A convertor (IC10, pin 23)

R82

C112 C113

C116

2

17 16

Active

filter

FI2

Noise

detector

FM

detector

13

"NOIS" signal to the CPU pin 19

RSSI

Noise

comp.

×3

R84

Page 9

4 - 2

4-1-5 AF CIRCUIT

AF signals from the FM IF IC (IC2, pin 9) are applied to the

mute switch (IC4, pin 1) via the AF filter circuit (IC3b, pins 6,

7). The output signals from pin 11 are applied to the AF

power amplifier (IC5, pin 4) after being passed through the

[VOL] control (R143).

The applied AF signals are amplified at the AF power amplifier circuit (IC5, pin 4) to obtain the specified audio level. The

amplified AF signals, output from pin 10, are applied to the

internal speaker (SP1) as the “SP” signal via the [SP] jack

when no plug is connected to the jack.

4-1-6 SQUELCH CIRCUIT

Asquelch circuit cuts out AF signals when no RF signals are

received. By detecting noise components in the AF signals,

the squelch switches the AF mute switch.

Aportion of the AF signals from the FM IF IC (IC2, pin 9) are

applied to the active filter section (IC2, pin 8) where noise

components are amplified and detected with an internal

noise detector.

The active filter section amplifies noise components. The filtered signals are rectified at the noise detector section and

converted into “NOIS” (pulse type) signals at the noise comparator section. The “NOIS” signal is applied to the CPU

(IC8, pin 19).

The CPU detects the receiving signal strength from the

number of the pulses, and outputs an “RMUT” signal from

pin 49. This signal controls the mute switch (IC4, pin 13) to

cut the AF signal line.

4-2 TRANSMITTER CIRCUITS

4-2-1 MICROPHONE AMPLIFIER CIRCUIT

The microphone amplifier circuit amplifies audio signals with

+6 dB/octave pre-emphasis characteristics from the microphone to a level needed for the modulation circuit.

The AF signals from the microphone are applied to the

microphone amplifier circuit (IC3c, pin 10). The amplified AF

signals are passed through the low-pass filter circuit (IC3d,

pins 13, 14) via the mute switch (IC4, pins 4, 3). The filtered

AF signals are applied to the modulator circuit after being

passed through the mute switch (IC4, pins 9, 8).

4-2-2 MODULATION CIRCUIT

The modulation circuit modulates the VCO oscillating signal

(RF signal) using the microphone audio signal.

The audio signals change the reactance of a diode (D404)

to modulate an oscillated signal at the VCO circuit (Q7, Q8).

The oscillated signal is amplified at the buffer-amplifiers (Q4,

Q6), then applied to the T/R switching circuit (D3, D4).

4-2-3 DRIVE/POWER AMPLIFIER CIRCUITS

The signal from the VCO circuit passes through the T/R

switching circuit (D3) and is amplified at the buffer (Q403,

Q3), pre-drive (Q2) and power amplifier (Q1) to obtain 4 W

of RF power (at 7.2 V DC). The amplified signal passes

through the antenna switching circuit (D1), and low-pass filter and is then applied to the antenna connector.

The bias current of the pre-drive (Q2) and the power amplifier (Q1) is controlled by the APC circuit.

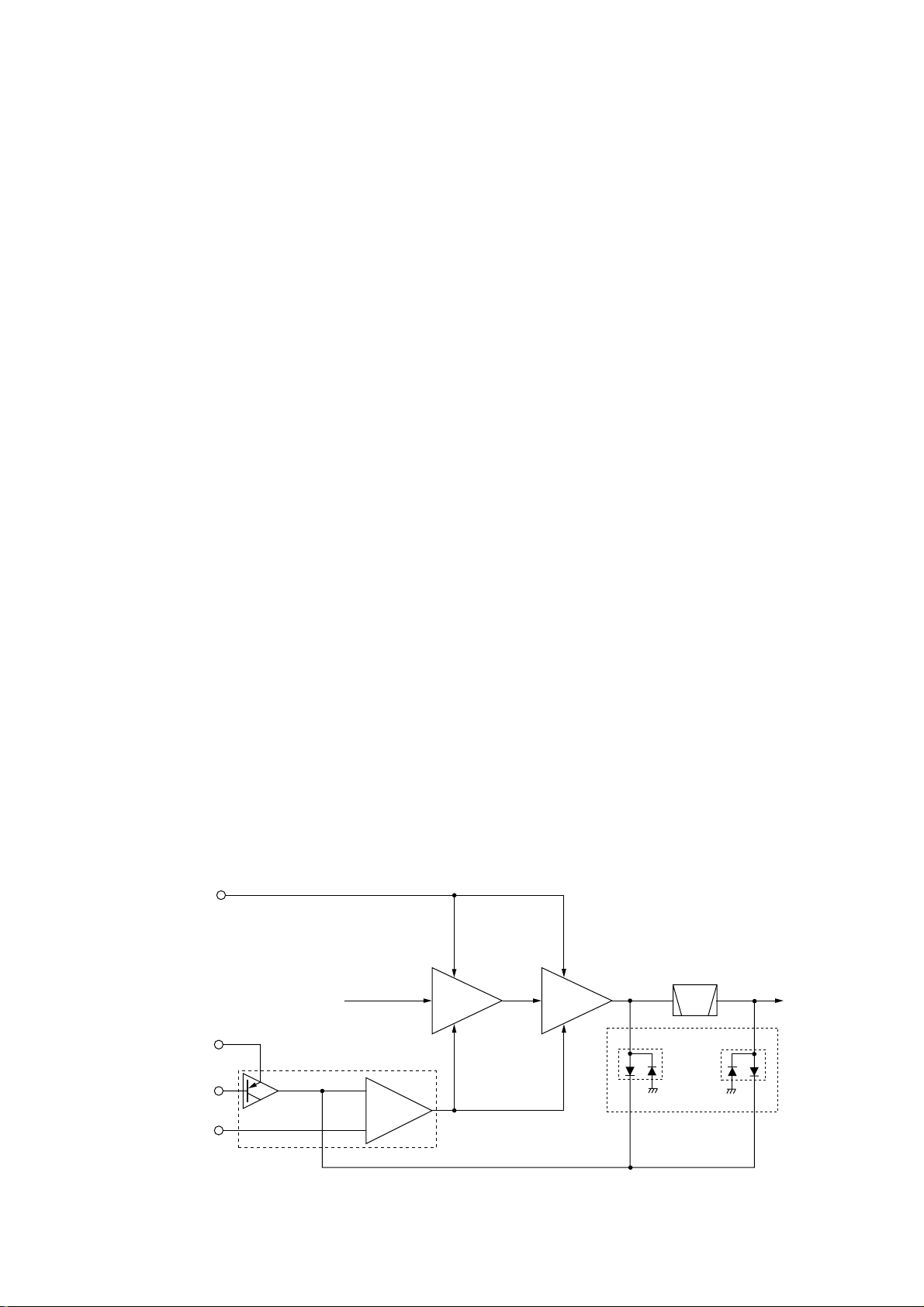

4-2-5 APC CIRCUIT

The APC circuit (IC3a, Q37) protects the drive and the

power amplifiers from excessive current drive, and selects

HIGH or LOW output power.

The signal output from the power detector circuit (D32, D33)

is applied to the differential amplifier (IC3a, pin 2), and the

“T4” signal from the expander (IC10, pin 11), controlled by

the CPU (IC8), is applied to the other input for reference.

• APC CIRCUIT

Q1

Power

amp.

Q2

Driver

amp.

IC3a

+

–

VCC

RF signal

from PLL

to antenna

T4

TXC

Q37

S5

APC control circuit

Power detector

circuit (D32, D33)

D33 D32

L4

LPF

Page 10

4 - 3

When the driving current is increased, input voltage of the

differential amplifier (pin 2) will be increased. In such cases,

the differential amplifier output voltage (pin 1) is decreased

to reduce the driving current.

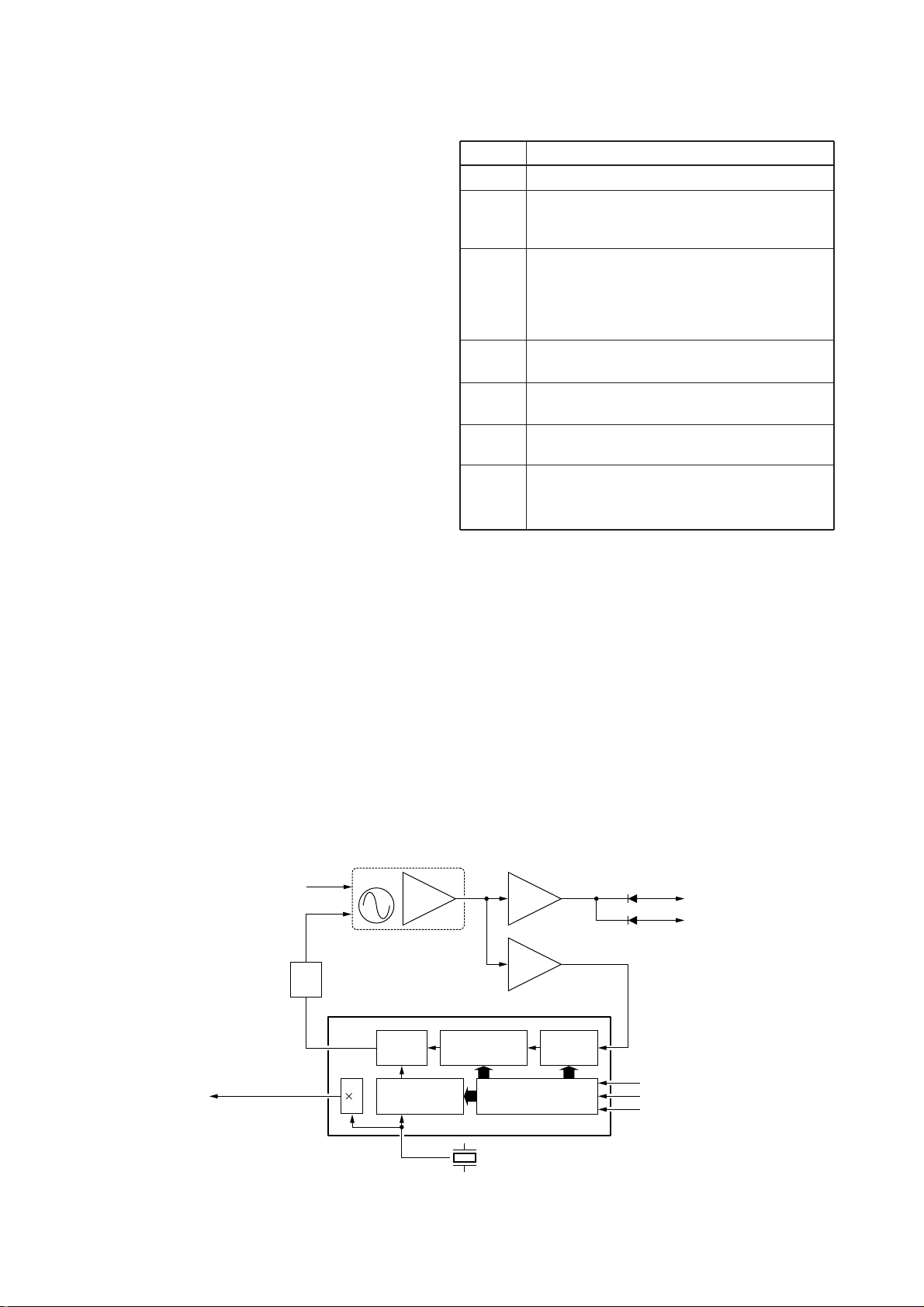

4-3 PLL CIRCUIT

A PLL circuit provides stable oscillation of the transmit frequency and receive 1st LO frequency. The PLL output compares the phase of the divided VCO frequency to the reference frequency. The PLL output frequency is controlled by

the divided ratio (N-data) of a programmable divider.

The PLL circuit contains the VCO circuit (Q7, Q8). The oscillated signal is amplified at the buffer-amplifiers (Q6, Q5) and

then applied to the PLL IC (IC1, pin 2).

The PLL IC contains a prescaler, programmable counter,

programmable divider and phase detector, etc. The entered

signal is divided at the prescaler and programmable counter

section by the N-data ratio from the CPU. The divided signal

is detected on phase at the phase detector using the reference frequency.

If the oscillated signal drifts, its phase changes from that of

the reference frequency, causing a lock voltage change to

compensate for the drift in the oscillated frequency.

A portion of the VCO signal is amplified at the buffer-amplifier (Q4), and is then applied to the receive 1st mixer (Q13)

or transmit buffer-amplifier circuit (Q403) via the T/R switching diode (D3, D4).

4-4 POWER SUPPLY CIRCUITS

VOLTAGE LINE

• PLL CIRCUIT

Shift register

3

Prescaler

Phase

detector

Loop

filter

Programmable

counter

Programmable

divider

X4

15.3 MHz

45.9 MHz signal

to the FM IF IC

"DEV" signal from the

D/A convertor (IC10, pin 22)

when transmitting

16

Q7, Q8

VCO circuit

Buffer

Q6

Buffer

Q4

Buffer

Q5

3

4

5

PLST

SCK

SO

to transmitter circuit

to 1st mixer circuit

D4

D3

17

8

2

LINE

HV

VCC

CPU5

T5

R5

S5

OPT

DESCRIPTION

The voltage from the attached battery pack.

The same voltage as the HV line (battery volt-

age) which is controlled by the power swtich

([VOL] control).

Common 5 V converted from the VCC line by the

reference regulator circuit (IC6). The output voltage is applied to the CPU (IC8), the 5 V regulator circuit (Q18, Q19), reset circuit (IC11) and

etc.

5 V for transmitter circuits regulated by the T5

regulator circuit (Q22).

5 V for receiver circuits regulated by the R5 regulator circuit (Q21).

Common 5 V converted from the VCC line by the

S5 regulator circuit (Q18, Q19).

The same voltage as the CPU5 line for the

optional HM-46L, HM-75A or HS-51 through a

resistor (R132).

Page 11

4 - 4

4-5 PORT ALLOCATIONS

4-5-1 CPU (IC8)

Pin

number

1

9

11

12

15

16

17

18

19

21

36–38

44–47

49

50

51

52

53

54

55

56

57

58

59

Port

name

VIN

RESET

CSIFT

SCK

DAST

CLIN

CLOUT

PLST

NOIS

BUSY

OPV3–

OPV1

KR3–

KR0

RMUT

MMUT

DUSE

S5C

R5C

T5C

TXC

AFON

LIGT

ESCK

ESDA

Description

Input port for battely voltage detection.

Input port for RESET signal.

Outputs reference oscillator for the

CPU control signal.

Outputs clock signal to the PLL IC

(IC1), EEPROM (IC7), etc.

• Outputs strobe signals to the

expander IC (IC10, pin 6).

• Input port for the initial version signal.

Input port for the cloning signal.

Outputs the cloning signal.

Outputs strobe signals to the PLL IC

(IC1, pin 3).

Input port for noise signals (pulse

type).

Outputs BUSY detection.

Low: The channel is busy.

Input ports for the optional unit detection signal from J5.

Output ports for key matrix.

Low: When the key is pushed.

• Outputs RX mute control signal.

• Input port for the RX mute signal

from optional units.

• Output TX mute control signal.

• Input port for the TX mute signal

from optional units.

Outputs low-pass filter cut-off frequency control signal when DTCS is activated.

Outputs S5 regulator control signal.

Low: While power is ON.

Outputs R5 regulator control signal.

Low: While receiving.

Outputs T5 regulator control signal.

Low: While transmitting.

Outputs APC circuit control signal.

High: While transmitting.

Outputs control signal for the regulator

circuit of AF power amplifier.

High: When squelch is open, etc.

Outputs LCD backlight control signal.

High: Lights ON.

Outputs EEPROM (IC7, pin 6) clock

signal.

I/O port for data signals from/to EEPROM (IC7, pin 5)

Pin

number

63

90

91

94

95

96

97

98

99

100

Port

name

UNLK

MTONE

DTMF

CTCIN

PTT

BDET

REM0

SD

LVIN

TEMP

Description

Input port for unlock signal.

High:PLL is unlocked.

Output port for:

Beep audio while receiving.

2/5-tone signals while transmitting.

Outputs DTMF tone signal while transmitting.

CTCSS/DTCS signals input port for

decording.

Input port for the [PTT] switch.

High:While [PTT] switch is pushed.

Input port for the battery’s type detection.

Input port for the remote-control signal

from external MIC (HM-75).

Input port for the RSSI detection.

Input port for the PLL lock voltage.

Input port for the transceiver’s internal

temperature detection.

4-5-2 OUTPUT EXPANDER IC (IC10)

Pin

number

2, 3,

10, 11

6

7

Port

name

T1–T4

DAST

SCK

Description

Output tunable bandpass filter control

signals.

Input port for strobe signal from the

CPU (IC8, pin 15).

Input port for clock signal from the

CPU (IC8, pin 12).

CPU (IC8)–continued

Page 12

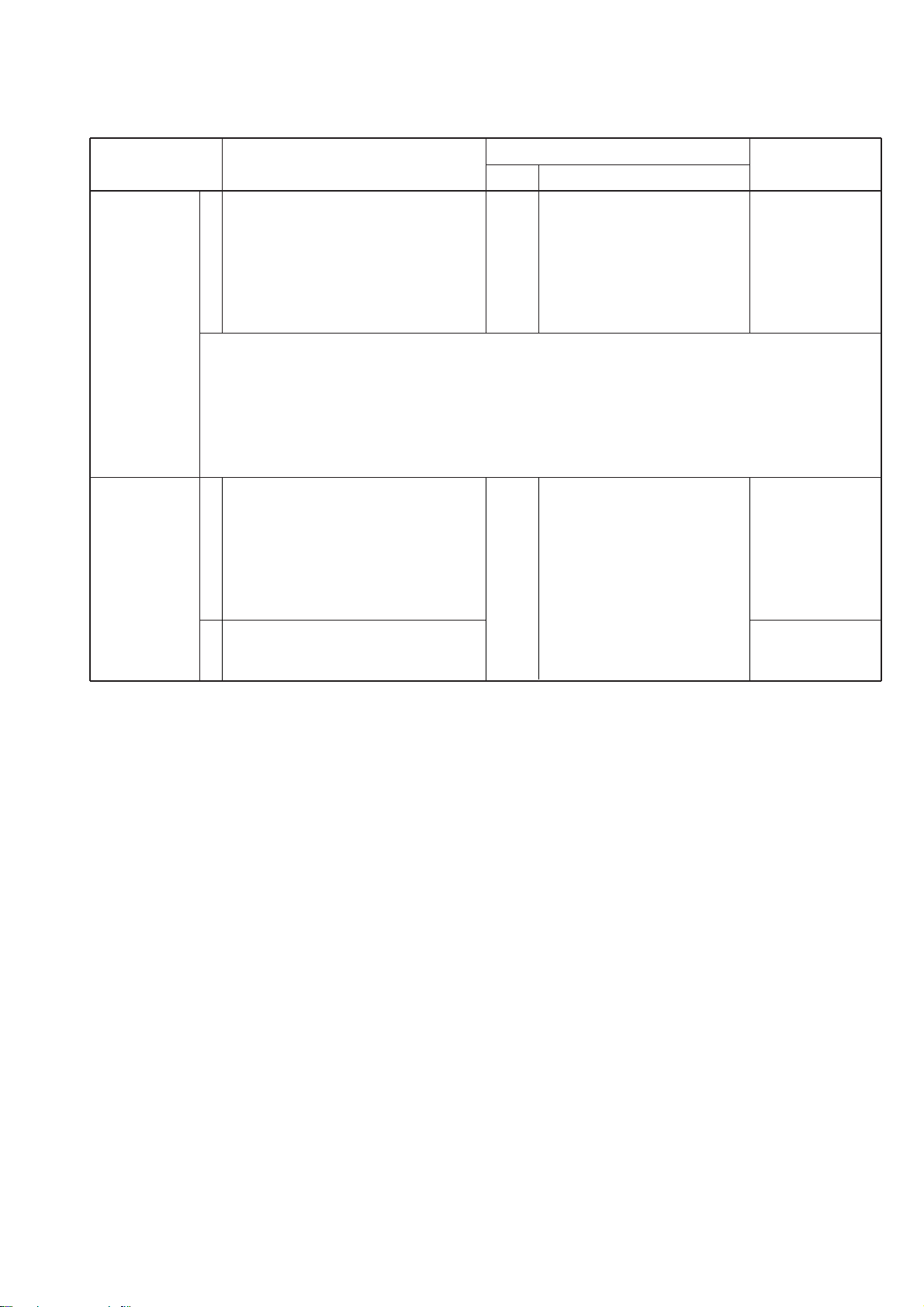

5-1 PREPARATION

When you adjust the contents on page 5-5 or 5-6, SOFTWARE ADJUSTMENT, the optional CS-F3G ADJ ADJUSTMENTSOFTWARE

(Rev. 2.0 or later), OPC-478 CLONING CABLE and a JIG CABLE (see illustration at page 5-2) are required.

■ REQUIRED TEST EQUIPMENT

5 - 1

SECTION 5 ADJUSTMENT PROCEDURES

EQUIPMENT

DC power supply

RF power meter

(terminated type)

Frequency counter

FM deviation meter

Digital multimeter

GRADE AND RANGE

Output voltage : 7.2 V DC

Current capacity : 5 Aor more

Measuring range : 1–10 W

Frequency range : 300–600 MHz

Impedance : 50 Ω

SWR : Less than 1.2 : 1

Frequency range : 0.1–600 MHz

Frequency accuracy : ±1 ppm or better

Sensitivity : 100 mV or better

Frequency range : DC–600 MHz

Measuring range : 0 to ±5 kHz

Input impedance : 10 MΩ/V DC or better

EQUIPMENT

Audio generator

Attenuator

Standard signal

generator (SSG)

DC voltmeter

Oscilloscope

AC millivoltmeter

GRADE AND RANGE

Frequency range : 300–3000 Hz

Output level : 1–500 mV

Power attenuation : 40 or 50 dB

Capacity : 10 W or more

Frequency range : 120–600 MHz

Output level : 0.1 µV–32 mV

(–127 to –17 dBm)

Input impedance : 50 kΩ/V DC or better

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Measuring range : 10 mV–10 V

■ SYSTEM REQUIREMENTS

• IBM PC compatible computer with an RS -232C serial port

(38400 bps or faster)

• Microsoft Windows 95 or Windows 98

• Intel i486DX processor or faster (Pentium 100 MHz or

faster recommended)

• At least 16 MB RAM and 10 MB of hard disk space

• 640×480 pixel display (800×600 pixel display recommended)

■ ADJUSTMENT SOFTWARE INSTALLATION

NOTE: Before using the program, make a backup copy of

the original disk. After making a backup copy, keep the original disk in a safe place.

q Boot up Windows.

- Quit all applications when Windows is running.

w Insert the backup disk1 into the appropriate floppy drive.

e Select ‘Run’ from the [Start] menu.

r Type the setup program name using the full path name,

then push the [Enter] key. (A:\ setup)

t Follow the prompts.

y Program group ‘CS-F3G ADJ’ appears in the ‘Programs’

folder of the [Start] menu.

■ STARTING SOFTWARE ADJUSTMENT

q Connect IC-F4GT/GS and PC with the optional OPC-478

and the JIG cable.

w Boot up Windows, and turn the transceiver power ON.

e Click the program group ‘CS-F3G ADJ’ in the ‘Programs’

folder of the [Start] menu, then CS-F3G ADJ’s window is

appeared.

r Click the TCXO tag.

t Click ‘Connect’ on the CS-F3G’s window, then appears

IC-F4GT/GS’s up-to-date condition.

y Set or modify adjustment data as desired.

IBM is a registered trademark of International Bussiness

Machines Corporation in the U.S.A. and other countries.

Microsoft and Windows are registered trademarks of

Microsoft Corporation in the U.S.A. and other countries.

Screen shots produced with permission from Microsoft

Corporation. All other products or brands are registered

trademarks or trademarks of their respective holders.

Page 13

5 - 2

• JIG CABLE

+

( CLONE)

–

( GND)

+

( SP)

–

( SPE)

3-conductor 3.5(d) mm plug

OPC-478

JIG cable

to IC-F4GT/GS [SP] jack

CS-F3G ADJ Rev.1.0

File

COM 1: OPEN

Option

Connect

Reload (F5) Disp para TCXO

[A / D]

VIN : : : 189 BDh 7 . 41V

TEMPS : : : 186 BAh 30 . 35'C

LVIN : : : 98 62h 1 . 92V

CH No. : 38 (RX Freq = 160.500, TX Freq = <– ) RF Power : High

Power (LO) : 50 [ # # # # – – – – – – – – – – – – – ]

BPF ALL : [ Enter] to Start

BPF T2 : 104 [ # # # # # # # # # # # # # # # – – ] [ Enter ] to Sweep

DTCS BAL : 140 [ # # # # # # # # # # # – – – – – – ]

MOD : 117 [ # # # # # # # # # – – – – – – – – ]

BPF T1 : – 70 [ # # # # # – – – – – – – – – – – – ] [ Enter ] to Sweep

BPF T3 : 112 [ # # # # # # # # # # # # # # # # – ] [ Enter ] to Sweep

BPF T4 : 88 [ # # # # # # # # # # – – – – – – – ] [ Enter ] to Sweep

TXF : [ Enter] to Start

SQL : 120 [ # # # # # # # # # – – – – – – – – ]

Power (Hi) : 150 [ # # # # # # # # # # # # – – – – – ]

SD : : : 0 00h 0 . 00V

BDET : : : 255 FFh 5 . 00V

REMOT : : : 14 0Eh 0 . 27V

BPF T1 : : : 114 72h 2 . 24V

BPF T3 : : : 101 65h 1 . 98V

T4/POW : : : 99 63h 1 . 94V

REF : : : 102 66h 2 . 00V

DTCS BL: : : 140 8Ch 54 . 90%

Dev : : : 103 67h 2 . 02V

SQL Lev: : : 120 78h 47 . 06%

BPF T2 : : : 96 60h 1 . 88V

[D / A]

: Transceiver's connection state

: Reload adjustment data

: TCXO tag (must check for F4G adjustment)

: Connected DC voltage

: PLL lock voltage

: Operating channel select

: RF output power

: DTCS wave form

NOTE:

• ADJUSTMENT SOFTWARE'S SCREEN DISPLAY EXAMPLE

1

2 3

14

4

5

6

7

8

9

10

11

12

13

15

7

8

1

2

3

4

5

6

14

15

9

10

11

12

13

: FM deviation

: Squelch level

: Receive sensitivity (automatically)

: Receive sensitivity (manually)

: Reference frequency

: Receive sensitivity measurement

: Adjustment items

The above values for settings are example only.

Each transceiver has its own specific values for each setting.

Page 14

5 - 3

to an RS-232C port

Personal

computer

to [MIC]

to [SP]

JIG cable

DB9 female plug

(incl. level converter circuit)

• CONNECTION

to the antenna connector

RF power meter

0.1–10 W/50 Ω

Frequency

counter

Attenuator

40 dB or 50 dB

FM

deviation meter

Standard signal generator

0.1 µV to 32 mV

(–127 dBm to –17 dBm)

CAUTION:

DO NOT transmit while

SSG is connected to the

antenna connector.

SINAD meter

Speaker (8 Ω)

Audio generator

OPC-478

DC POWER

SUPPLY

• DC POWER CABLE CONNECTIONS

SOFTWARE ADJUSTMENT PLL ADJUSTMENT

–

Top view

Soldering

DC cable here

+

–

+

DC POWER

SUPPLY

Page 15

5 - 4

L11

L405

PLL lock voltage

adjustment

LV

PLL lock voltage

check point

• MAIN unit

Bottom view

RF power meter

5-2 PLL ADJUSTMENT

PLL LOCK

VOLTAGE

1

2

3

4

• Operating frequency: 440.000 MHz

• Receiving

• Transmitting

• Operating frequency: 470.000 MHz

• Receiving

• Transmitting

MAIN Connect a digital multi

meter to check point

LV.

1.3 V

1.3 V

3.0–4.5 V

3.0–4.5 V

MAIN L11

L405

Verify

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

Page 16

5 - 5

1

1

2

1

1

• Operating frequency: 440.000 MHz

• High/Low switch : Low

• Connect the RF power meter or 50 Ω

dummy load to the antenna connector.

• Transmitting

• Operating frequency: 470.000 MHz

• High/Low switch : Low

• Transmitting

• High/Low switch : High

• Transmitting

• Operating frequency: 440.000 MHz

• High/Low switch : Low

• Connect the audio generator to the

[MIC] jack and set as:

1.0 kHz/150 mVrms

• Set the FM deviation meter as:

HPF : OFF

LPF : 20 kHz

De-emphasis : OFF

Detector : (P–P)/2

• Transmitting

• Operating frequency: 470.000 MHz

• High/Low switch : Low

• No audio applied to the [MIC] jack.

• DTCS code : 007

• Transmitting

REFERENCE

FREQUENCY

[TXF]

OUTPUT

POWER

[POWER(LO)]

[POWER(HI)]

FM

DEVIATION

[MOD]

DTCS WAVE

FORM

[DTCS BAL]

Top

panel

Top

panel

Top

panel

Top

panel

Loosely couple a frequnecy

counter to the antenna connector.

Connect an RF power meter to

the antenna connector.

Connect an FM deviation meter

to the antenna connector

through the attenuator.

Connect an FM deviation meter

with an oscilloscope to the

antenna connector through an

attenuator.

440.0000 MHz

1.0 W

4.0 W

±2.0 kHz

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

UNIT

LOCATION

5-3 SOFTWARE ADJUSTMENT

Select an operation using [↑] / [↓] keys, then set specified value using [←] / [→] keys on the connected computer keyboard.

Set to flat wave

form

Page 17

5 - 6

Minimum distortion

level

12 dB SINAD

At the point where

the audio signals

just appears.

1 • Operating frequency : 440.000 MHz

• Connect a standard signal generator to

the antenna connector and set as:

Frequency : 440.000 MHz

Level :

10 µV* (–87 dBm

)

Modulation : 1 kHz

Deviation : ±1.75 kHz

• Receiving

• Operating frequency: 440.000 MHz

• Connect a standard signal generator to

the antenna connector and set as:

Frequency : 440.000 MHz

Level :

0.2 µV* (–121 dBm)

Modulation : 1 kHz

Deviation :

±1.75 kHz

• Receiving

• Receiving

RX

SENSITIVITY

[BPF T1] –

[BPF T4]

SQUELCH

LEVEL

[SQL]

Top

panel

Top

panel

Connect a SINAD meter with an

8 Ω load to the [SP] jack.

Connect a SINAD meter with an

8 Ω load to the [SP] jack.

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

UNIT

LOCATION

*The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

SOFTWARE ADJUSTMENT – continued

Select an operation using [↑] / [↓] keys, then set specified value using [←] / [→] keys on the connected computer keyboard.

CONVENIENT: The BPF T1–BPF T4 can be adjusted automatically.

q-1: Set the cursol to “BPF ALL” on the adjustment program and then push [ENTER]

key.

q-2: The connected PC tunes BPF T1–BPF T4 to peak levels.

or

w-1: Set the cursol to one of BPF T1, T2, T3, or T4 as desired.

w-2: Push [ENTER] key to start tuning.

w-3: Repeat w-1 and w-2 to perform additional BPF tuning.

1

2

Page 18

6 - 1

S.=Surface mount

IC1 1130007610 S.IC µ PD3140GS-E1 (DS8)

IC2 1110003490 S.IC TA31136FN (D,EL)

IC3 1110005140 S.IC NJM3403AV-TE1

IC4 1130008090 S.IC BU4066BCFV-E1

IC5 1110001810 S.IC TA7368F (TP1)

IC6 1180001740 S.IC TK11250BMCL

IC7 1130009680 S.IC HN58X2432TI

IC8 1140008880 S.IC HD6433876B34H

IC10 1190000350 S.IC M62363FP-650C

IC11 1130009110 S.IC S-80942ANMP-DD6-T2

IC12 1110003800 S.IC NJM2904V-TE1

IC13 1110002750 S.IC TA75S01F (TE85R)

Q1 1560001050 S.FET 2SK2974

Q2 1560001020 S.FET 2SK2973 (MTS101P)

Q3 1530002620 S.TRANSISTOR 2SC3585 R44-T2B

Q4 1530003310 S.TRANSISTOR 2SC5107-O (TE85R)

Q5 1530003310 S.TRANSISTOR 2SC5107-O (TE85R)

Q6 1530003310 S.TRANSISTOR 2SC5107-O (TE85R)

Q7 1530003230 S.TRANSISTOR 2SC5085-Y (TE85R)

Q8 1530003230 S.TRANSISTOR 2SC5085-Y (TE85R)

Q10 1530002690 S.TRANSISTOR 2SC4116-GR (TE85R)

Q11 1590001190 S.TRANSISTOR XP6501-(TX) .AB

Q12 1580000720 S.FET 3SK239AXRTL

Q13 1580000720 S.FET 3SK239AXRTL

Q14 1530002600 S.TRANSISTOR 2SC4215-O (TE85R)

Q15 1520000460 S.TRANSISTOR 2SB1132 T100 R

Q16 1590001190 S.TRANSISTOR XP6501-(TX) .AB

Q17 1590002530 S.TRANSISTOR UN911H (TX)

Q18 1520000460 S.TRANSISTOR 2SB1132 T100 R

Q19 1590001190 S.TRANSISTOR XP6501-(TX) .AB

Q20 1590000720 S.TRANSISTOR DTA144EUAT106

Q21 1510000920 S.TRANSISTOR 2SA1577 T107 Q

Q22 1510000920 S.TRANSISTOR 2SA1577 T107 Q

Q25 1530002690 S.TRANSISTOR 2SC4116-GR (TE85R)

Q31 1590000660 S.TRANSISTOR DTC144TU T107

Q33 1590000430 S.TRANSISTOR DTC144EUA T106

Q34 1560000540 S.FET 2SK880-Y (TE85R)

Q35 1530002690 S.TRANSISTOR 2SC4116-GR (TE85R)

Q36 1530002690 S.TRANSISTOR 2SC4116-GR (TE85R)

Q37 1590000720 S.TRANSISTOR DTA144EUAT106

Q38 1590001940 S.TRANSISTOR DTC144EE TL

Q401 1590001400 S.TRANSISTOR XP1214 (TX)

Q402 1590000430 S.TRANSISTOR DTC144EUA T106

Q403 1530003310 S.TRANSISTOR 2SC5107-O (TE85R)

Q404 1550000010 S.FET 2SJ364-Q (TX)

D1 1750000580 S.DIODE 1SV307 (TPH3)

D2 1790000620 S.DIODE MA77 (TX)

D3 1790000620 S.DIODE MA77 (TX)

D4 1790000620 S.DIODE MA77 (TX)

D5 1720000370 S.VARICAP HVU350TRF

D7 1720000660 S.VARICAP 1SV288 (TPH2)

D8 1790000620 S.DIODE MA77 (TX)

D10 1720000370 S.VARICAP HVU350TRF

D11 1720000370 S.VARICAP HVU350TRF

D12 1720000370 S.VARICAP HVU350TRF

D14 1790000620 S.DIODE MA77 (TX)

D26 1160000070 S.DIODE DAN202K T146

D27 1790001670 S.DIODE RB706F-40T106

D29 1730002260 S.ZENER MA8030-H (TX)

D32 1790001670 S.DIODE RB706F-40T106

D33 1790001670 S.DIODE RB706F-40T106

*D34 1790000620 S.DIODE MA77 (TX)

D401 1720000370 S.VARICAP HVU350TRF

D403 1720000370 S.VARICAP HVU350TRF

D404 1720000520 S.VARICAP 1T365-01-T8A

FI1 2010002450 S.XTAL FL-313 (46.35 MHz)

FI2 2020001080 S.CERAMIC SFPC450G-TC01

X2 6050010870 S.XTAL CR-663 (9.200 MHz)

X3 6070000210

S.DISCRIMINATOR

CDBCA450CX24

X4 6050010930 S.XTAL CR-662 (15.3 MHz)

L1 6200008240 S.COIL 0.30-0.9-5TL 14N

L2 6200008240 S.COIL 0.30-0.9-5TL 14N

L4 6200008240 S.COIL 0.30-0.9-5TL 14N

L6 6200007690 S.COIL LQN21A 18NJ04

L7 6200005670 S.COIL ELJRE 12NG-F

L8 6200005710 S.COIL ELJRE 27NG-F

L9 6200005710 S.COIL ELJRE 27NG-F

L11 6200004110 S.COIL MC152-E558ANA-100050

L12 6200003550 S.COIL MLF1608A 4R7K-T

L13 6200003960 S.COIL MLF1608A 1R0K-T

L14 6200005680 S.COIL ELJRE 15NG-F

L15 6200008240 S.COIL 0.30-0.9-5TL 14N

L17 6200008440 S.COIL LQN21A 8N2D04

L18 6200008440 S.COIL LQN21A 8N2D04

L19 6200008440 S.COIL LQN21A 8N2D04

L20 6200002850 S.COIL NL 252018T-R82J

L21 6200005720 S.COIL ELJRE 33NG-F

L22 6200008240 S.COIL 0.30-0.9-5TL 14N

L24 6200009250 S.COIL LQW1608A R22G00

L25 6200004480 S.COIL MLF1608D R82K-T

L26 6200003590 S.COIL EXCCL3225U1

L31 6200008520 S.COIL 0.30-0.7-3TR 4.9N

L33 6200009210 S.COIL NL 252018T-390J

L402 6200008440 S.COIL LQN21A 8N2D04

L404 6200004660 S.COIL MLF1608A 1R8K-T

L405 6200004110 S.COIL MC152-E558ANA-100050

L406 6200004660 S.COIL MLF1608A 1R8K-T

L407 6200003550 S.COIL MLF1608A 4R7K-T

L411 6200005700 S.COIL ELJRE 22NG-F

L441 6200003960 S.COIL MLF1608A 1R0K-T

L442 6200004720 S.COIL MLF1608D R10K-T

R1 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ)

R2 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R3 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R7 7030004980 S.RESISTOR ERJ2GEJ 101 X (100 Ω)

R9 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R12 7030005040 S.RESISTOR ERJ2GEJ 472 X (4.7 kΩ)

R13 7030005530 S.RESISTOR ERJ2GEJ 100 X (10 Ω)

R14 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R15 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R17 7030005040 S.RESISTOR ERJ2GEJ 472 X (4.7 kΩ)

R18 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R19 7030004980 S.RESISTOR ERJ2GEJ 101 X (100 Ω)

R20 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R21 7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω)

R22 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R23 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R30 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R32 7030003540 S.RESISTOR ERJ3GEYJ 682 V (6.8 kΩ)

R33 7030008410 S.RESISTOR ERJ2GEJ 392 X (3.9 kΩ)

R34 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R41 7030004970 S.RESISTOR ERJ2GEJ 470 X (47 Ω)

R44 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R48 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R49 7030003630 S.RESISTOR ERJ3GEYJ 393 V (39 kΩ)

R50 7030003750 S.RESISTOR ERJ3GEYJ 394 V (390 kΩ)

R51 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ)

R52 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R53 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R54 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R55 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R59 7030003340 S.RESISTOR ERJ3GEYJ 151 V (150 Ω)

R61 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R62 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R63 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R64 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R65 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R66 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R67 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

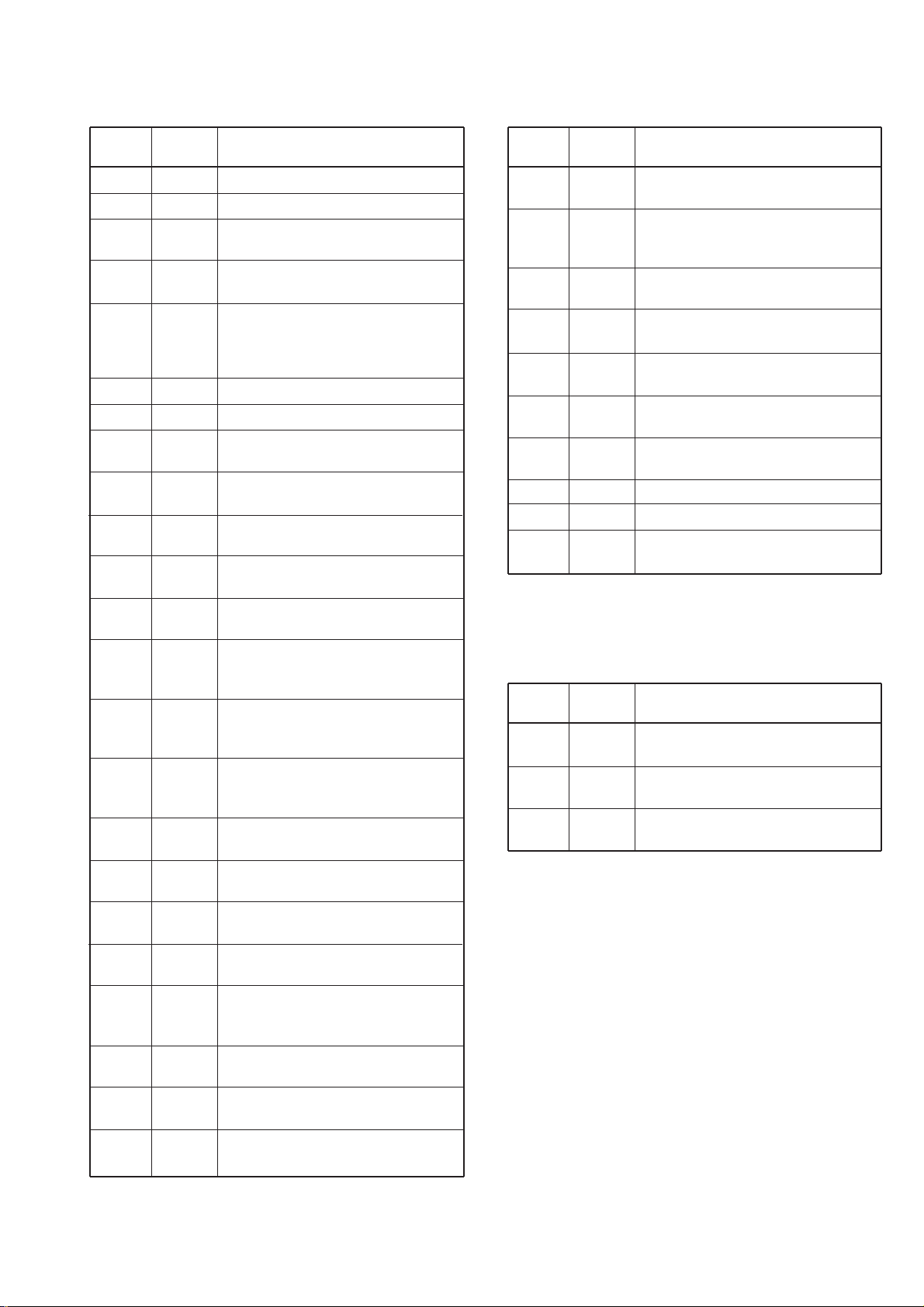

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

SECTION 6 PARTS LIST

Page 19

6 - 2

S.=Surface mount

R68 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R69 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R70 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R72 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R75 7030003350 S.RESISTOR ERJ3GEYJ 181 V (180 Ω)

R77 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R79 7030003350 S.RESISTOR ERJ3GEYJ 181 V (180 Ω)

R80 7030005310 S.RESISTOR ERJ2GEJ 124 X (120 kΩ)

R81 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R82 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ)

R83 7030003380 S.RESISTOR ERJ3GEYJ 331 V (330 Ω)

R84 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R85 7030003460 S.RESISTOR ERJ3GEYJ 152 V (1.5 kΩ)

R86 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R87 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R88 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R89 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

R90 7030003780 S.RESISTOR ERJ3GEYJ 684 V (680 kΩ)

R93 7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ)

R94 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R95 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R96 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R97 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R98 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

R99 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R100 7030008060 S.RESISTOR RR0816P-222-D (2.2 kΩ)

R101 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R102 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω)

R103 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R104 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R105 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R107 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R108 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

R109 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R112 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R113 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R114 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R115 7030005310 S.RESISTOR ERJ2GEJ 124 X (120 kΩ)

R116 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R117 7030003460 S.RESISTOR ERJ3GEYJ 152 V (1.5 kΩ)

R120 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R121 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R122 7030003490 S.RESISTOR ERJ3GEYJ 272 V (2.7 kΩ)

R123 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R125 7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ)

R126 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R127 7030003260 S.RESISTOR ERJ3GEYJ 330 V (33 Ω)

R128 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω)

R130 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R131 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R132 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R133 7030004040 S.RESISTOR ERJ3GEYJ 4R7 V (4.7 Ω)

R134 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R135 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R136 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R137 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R139 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R140 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R141 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R142 7030004980 S.RESISTOR ERJ2GEJ 101 X (100 Ω)

R143 7210003060 VARIABLE TP76N00N-15F-10KA-2251

R144 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R145 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R146 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R147 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R148 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R150 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R152 7030005170 S.RESISTOR ERJ2GEJ 474 X (470 kΩ)

R153 7030005170 S.RESISTOR ERJ2GEJ 474 X (470 kΩ)

R154 7030005170 S.RESISTOR ERJ2GEJ 474 X (470 kΩ)

R155 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R159 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R160 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R161 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R162 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R163 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R164 7030005310 S.RESISTOR ERJ2GEJ 124 X (120 kΩ)

[F4GT] only

R165 7030005310 S.RESISTOR ERJ2GEJ 124 X (120 kΩ)

[F4GS] only

R168 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R169 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R170 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R171 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R174 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R176 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ)

R177 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R178 7030005340 S.RESISTOR RR0816P-332-D (3.3 kΩ)

R181 7030005870 S.RESISTOR RR0816R-104-D (100 kΩ)

R182 7510001280 S.THERMISTOR NTCCM20124AG473J-T

R184 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R185 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R186 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R190 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R191 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R192 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R193 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R194 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R195 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R196 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R197 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R198 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R199 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R200 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R202 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R203 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R204 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R205 7030003460 S.RESISTOR ERJ3GEYJ 152 V (1.5 kΩ)

R207 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R208 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R209 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R210 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R211 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ)

R212 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R213 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R215 7030005870 S.RESISTOR RR0816R-104-D (100 kΩ)

R216 7030005870 S.RESISTOR RR0816R-104-D (100 kΩ)

R218 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ)

R219 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ)

R220 7030003740 S.RESISTOR ERJ3GEYJ 334 V (330 kΩ)

R221 7030003750 S.RESISTOR ERJ3GEYJ 394 V (390 kΩ)

R223 7030005310 S.RESISTOR ERJ2GEJ 124 X (120 kΩ)

R224 7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ)

R225 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R226 7410000950 S.ARRAY EXB-V8V 102JV

R227 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R228 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R229 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

R230 7030003650 S.RESISTOR ERJ3GEYJ 563 V (56 kΩ)

R231 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R232 7410000950 S.ARRAY EXB-V8V 102JV

R234 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R235 7030003780 S.RESISTOR ERJ3GEYJ 684 V (680 kΩ)

R236 7410000950 S.ARRAY EXB-V8V 102JV

R237 7410000950 S.ARRAY EXB-V8V 102JV

R238 7410000950 S.ARRAY EXB-V8V 102JV

R239 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R240 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R241 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R242 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R243 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R244 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R245 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R246 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R251 7030003740 S.RESISTOR ERJ3GEYJ 334 V (330 kΩ)

R252 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R253 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R257 7030004050 S.RESISTOR ERJ3GEYJ 1R0 V (1 Ω)

R258 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R260 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R261 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R262 7030004050 S.RESISTOR ERJ3GEYJ 1R0 V (1 Ω)

R401 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R402 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R404 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R405 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R410 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R411 7030003490 S.RESISTOR ERJ3GEYJ 272 V (2.7 kΩ)

R413 7030004040 S.RESISTOR ERJ3GEYJ 4R7 V (4.7 Ω)

R414 7030003390 S.RESISTOR ERJ3GEYJ 391 V (390 Ω)

R416 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R417 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R420 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R421 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

Page 20

6 - 3

S.=Surface mount

R422 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R445 7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω)

R446 7030003650 S.RESISTOR ERJ3GEYJ 563 V (56 kΩ)

R447 7030005000 S.RESISTOR ERJ2GEJ 471 X (470 Ω)

R448 7030003210 S.RESISTOR ERJ3GEYJ 120 V (12 Ω)

R449 7030005000 S.RESISTOR ERJ2GEJ 471 X (470 Ω)

R457 7030004980 S.RESISTOR ERJ2GEJ 101 X (100 Ω)

R458 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R464 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R465 7030003260 S.RESISTOR ERJ3GEYJ 330 V (33 Ω)

R469 7030003490 S.RESISTOR ERJ3GEYJ 272 V (2.7 kΩ)

R473 7030004970 S.RESISTOR ERJ2GEJ 470 X (47 Ω)

R500 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R501 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R502 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R503 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R504 7030003380 S.RESISTOR ERJ3GEYJ 331 V (330 Ω)

R505 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R506 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R507 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R508 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R509 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R510 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R511 7030007350 S.RESISTOR ERJ2GEJ 393 X (39 kΩ)

R512 7030003490 S.RESISTOR ERJ3GEYJ 272 V (2.7 kΩ)

R515 7030005310 S.RESISTOR ERJ2GEJ 124 X (120 kΩ)

R516 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R517 7030005070 S.RESISTOR ERJ2GEJ 683 X (68 kΩ)

R518 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R519 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R520 7030007280 S.RESISTOR ERJ2GEJ 331 X (330 Ω)

R521 7030007280 S.RESISTOR ERJ2GEJ 331 X (330 Ω)

R522 7030003200 S.RESISTOR ERJ3GEYJ 100 V (10 Ω)

R523 7030008410 S.RESISTOR ERJ2GEJ 392 X (3.9 kΩ)

R524 7510001300 S.THERMISTOR NTCCM1608 4LH 223KC

R525 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R526 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R527 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R528 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R529 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R530 7030004980 S.RESISTOR ERJ2GEJ 101 X (100 Ω)

R531 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R532 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R533 7030003840 S.RESISTOR ERJ3GEYJ 225 V (2.2 MΩ)

C3 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C8 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C9 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C10 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C11 4030011770 S.CERAMIC C1608 CH 1H 060B-T-A

C12 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C13 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C14 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C15 4030014340 S.CERAMIC ECUE1H390JCQ

C17 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C18 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C19 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C21 4550006540 S.TANTALUM ECST1CY475R

C22 4030007020 S.CERAMIC C1608 CH 1H 120J-T-A

C24 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C25 4030009910 S.CERAMIC C1608 CH 1H 040B-T-A

C26 4030013850 S.CERAMIC ECUE1E102KBQ

C27 4030009920 S.CERAMIC C1608 CH 1H 050B-T-A

C28 4030007020 S.CERAMIC C1608 CH 1H 120J-T-A

C29 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C30 4030007020 S.CERAMIC C1608 CH 1H 120J-T-A

C31 4030009920 S.CERAMIC C1608 CH 1H 050B-T-A

C32 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C33 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C42 4030013850 S.CERAMIC ECUE1E102KBQ

C47 4550006360 S.TANTALUM ECST1VY104R

C48 4550006450 S.TANTALUM ECST1EY105R

C50 4550006200 S.TANTALUM ECST0JY106R

C51 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C52 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C53 4030007030 S.CERAMIC C1608 CH 1H 150J-T-A

C54 4030013850 S.CERAMIC ECUE1E102KBQ

C55 4030016790 S.CERAMIC ECJ0EB1C103K

C56 4030016790 S.CERAMIC ECJ0EB1C103K

C60 4030013850 S.CERAMIC ECUE1E102KBQ

C61 4030011770 S.CERAMIC C1608 CH 1H 060B-T-A

C62 4030011770 S.CERAMIC C1608 CH 1H 060B-T-A

C63 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C65 4030009910 S.CERAMIC C1608 CH 1H 040B-T-A

C66 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C67 4030009530 S.CERAMIC C1608 CH 1H 030B-T-A

C71 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C72 4550006320 S.TANTALUM ECST0JY475R

C73 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C75 4030016930 S.CERAMIC ECJ0EB1A104K

C76 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C78 4030009910 S.CERAMIC C1608 CH 1H 040B-T-A

C79 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T-A

C84 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C85 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C86 4030009920 S.CERAMIC C1608 CH 1H 050B-T-A

C87 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C88 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C89 4030009500 S.CERAMIC C1608 CH 1H 0R5B-T-A

C90 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C91 4030006970 S.CERAMIC C1608 CH 1H 060D-T-A

C92 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C93 4030014180 S.CERAMIC ECUE1H470JCQ

C94 4030009500 S.CERAMIC C1608 CH 1H 0R5B-T-A

C95 4030014180 S.CERAMIC ECUE1H470JCQ

C96 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C97 4030006970 S.CERAMIC C1608 CH 1H 060D-T-A

C98 4030007050 S.CERAMIC C1608 CH 1H 220J-T-A

C99 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C100 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C104 4030013850 S.CERAMIC ECUE1E102KBQ

C105 4030014180 S.CERAMIC ECUE1H470JCQ

C106 4030007030 S.CERAMIC C1608 CH 1H 150J-T-A

C107 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C108 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C109 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C110 4030009990 S.CERAMIC C1608 CH 1H 200J-T-A

C111 4030013850 S.CERAMIC ECUE1E102KBQ

C112 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C113 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C114 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C115 4030007130 S.CERAMIC C1608 CH 1H 101J-T-A

C116 4030014200 S.CERAMIC ECUE1H101JCQ

C117 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C118 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C119 4030008680 S.CERAMIC C2012 JF 1C 105Z-T-A

C120 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C121 4030007170 S.CERAMIC C1608 CH 1H 221J-T-A

C122 4030007170 S.CERAMIC C1608 CH 1H 221J-T-A

C123 4030013850 S.CERAMIC ECUE1E102KBQ

C124 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C125 4030006870 S.CERAMIC C1608 JB 1H 222K-T-A

C126 4030008470 S.CERAMIC C1608 JB 1H 272K-T-A

C128 4030008680 S.CERAMIC C2012 JF 1C 105Z-T-A

C129 4550006680 S.TANTALUM ECST0JY156R

C132 4030008770 S.CERAMIC C1608 JB 1H 562K-T-A

C133 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C134 4030007160 S.CERAMIC C1608 CH 1H 181J-T-A

C135 4030007160 S.CERAMIC C1608 CH 1H 181J-T-A

C136 4030008770 S.CERAMIC C1608 JB 1H 562K-T-A

C137 4030008900 S.CERAMIC C1608 JB 1C 333K-T-A

C139 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C140 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C144 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C145 4510004630

S.ELECTROLYTIC

ECEV1CA100SR

C146 4030011810 S.CERAMIC C1608 JB 1A 224K-T-N

C147 4030008630 S.CERAMIC C1608 JF 1C 104Z-T-A

C148 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C149 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C150 4550006200 S.TANTALUM ECST0JY106R

C151 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C152 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C153 4510006940

S.ELECTROLYTIC

EEVFC0J101P

C154 4550006200 S.TANTALUM ECST0JY106R

C155 4510004630

S.ELECTROLYTIC

ECEV1CA100SR

C156 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C158 4550006620 S.TANTALUM ECST0JY226R

C159 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C160 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C161 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C162 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C163 4030013850 S.CERAMIC ECUE1E102KBQ

C164 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

Page 21

6 - 4

S.=Surface mount

C165 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C167 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C168 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C169 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C173 4510004640

S.ELECTROLYTIC

ECEV1CA470SP

C174 4510005430

S.ELECTROLYTIC

ECEV0JA220SR

C179 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C193 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C194 4030007020 S.CERAMIC C1608 CH 1H 120J-T-A

C195 4030007080 S.CERAMIC C1608 CH 1H 390J-T-A

C196 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C197 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C198 4550006170 S.TANTALUM ECST1AY225R

C199 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C200 4030008900 S.CERAMIC C1608 JB 1C 333K-T-A

C201 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C202 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C204 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C205 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C209 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C211 4550006320 S.TANTALUM ECST0JY475R

C212 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C213 4550006170 S.TANTALUM ECST1AY225R

C214 4030008900 S.CERAMIC C1608 JB 1C 333K-T-A

C215 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C216 4030016930 S.CERAMIC ECJ0EB1A104K

C217 4030016930 S.CERAMIC ECJ0EB1A104K

C218 4030013850 S.CERAMIC ECUE1E102KBQ

C219 4030009630 S.CERAMIC C1608 JB 1H 822K-T-A

C221 4030008910 S.CERAMIC C1608 JB 1C 393K-T-A

C222 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C223 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C224 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C225 4030009880 S.CERAMIC C1608 JB 1H 682K-T-A

C227 4030011600 S.CERAMIC C1608 JB 1C 104KT-N

C228 4030009490 S.CERAMIC C1608 JB 1H 821K-T-A

C229 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C230 4030008880 S.CERAMIC C1608 JB 1C 223K-T-A

C231 4030008630 S.CERAMIC C1608 JF 1C 104Z-T-A

C232 4030008630 S.CERAMIC C1608 JF 1C 104Z-T-A

C233 4030013850 S.CERAMIC ECUE1E102KBQ

C234 4030013850 S.CERAMIC ECUE1E102KBQ

C236 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C243 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C244 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C245 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C248 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C249 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C250 4030006900 S.CERAMIC C1608 JB 1E 103K-T-A

C251 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C252 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C282 4030013850 S.CERAMIC ECUE1E102KBQ

C283 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C285 4030009650 S.CERAMIC C1608 CH 1H 240J-T-A

C288 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C289 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C291 4030016930 S.CERAMIC ECJ0EB1A104K

C403 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C404 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C405 4030011770 S.CERAMIC C1608 CH 1H 060B-T-A

C406 4030006990 S.CERAMIC C1608 CH 1H 080D-T-A

C407 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C410 4030007020 S.CERAMIC C1608 CH 1H 120J-T-A

C411 4030011770 S.CERAMIC C1608 CH 1H 060B-T-A

C412 4030011770 S.CERAMIC C1608 CH 1H 060B-T-A

C413 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C414 4030009920 S.CERAMIC C1608 CH 1H 050B-T-A

C416 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C417 4030009570 S.CERAMIC C1608 CH 1H 0R3B-T-A

C418 4030014290 S.CERAMIC ECUE1H090CCQ

C419 4030009570 S.CERAMIC C1608 CH 1H 0R3B-T-A

C421 4030009990 S.CERAMIC C1608 CH 1H 200J-T-A

C422 4030006980 S.CERAMIC C1608 CH 1H 070D-T-A

C423 4030011770 S.CERAMIC C1608 CH 1H 060B-T-A

C424 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C426 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C427 4030009500 S.CERAMIC C1608 CH 1H 0R5B-T-A

C443 4030016950 S.CERAMIC ECJ0EB1A473K

C450 4030009920 S.CERAMIC C1608 CH 1H 050B-T-A

C452 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C455 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C467 4030007000 S.CERAMIC C1608 CH 1H 090D-T-A

C471 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C472 4030014180 S.CERAMIC ECUE1H470JCQ

C473 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C475 4030014000 S.CERAMIC ECUE1H1R5BCQ

C486 4030009920 S.CERAMIC C1608 CH 1H 050B-T-A

C491 4550006450 S.TANTALUM ECST1EY105R

C492 4030007010 S.CERAMIC C1608 CH 1H 100D-T-A

C495 4030016930 S.CERAMIC ECJ0EB1A104K

C496 4030006880 S.CERAMIC C1608 JB 1H 472K-T-A

C501 4550006200 S.TANTALUM ECST0JY106R

C550 4550006620 S.TANTALUM ECST0JY226R

C551 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C552 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C553 4030014180 S.CERAMIC ECUE1H470JCQ

C554 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C555 4030009920 S.CERAMIC C1608 CH 1H 050B-T-A

C556 4030014180 S.CERAMIC ECUE1H470JCQ

C557 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C558 4030014180 S.CERAMIC ECUE1H470JCQ

C559 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C560 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C561 4030014180 S.CERAMIC ECUE1H470JCQ

C562 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C563 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C564 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C565 4030014180 S.CERAMIC ECUE1H470JCQ

C566 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C567 4030007090 S.CERAMIC C1608 CH 1H 470J-T-A

C571 4030014180 S.CERAMIC ECUE1H470JCQ

C572 4030014180 S.CERAMIC ECUE1H470JCQ

C573 4030014180 S.CERAMIC ECUE1H470JCQ

C574 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C659 4030006860 S.CERAMIC C1608 JB 1H 102K-T-A

C662 4030016930 S.CERAMIC ECJ0EB1A104K

C663 4030008920 S.CERAMIC C1608 JB 1C 473K-T-A

C664 4030013850 S.CERAMIC ECUE1E102KBQ

C665 4030014180 S.CERAMIC ECUE1H470JCQ

C666 4030009910 S.CERAMIC C1608 CH 1H 040B-T-A

C669 4030014180 S.CERAMIC ECUE1H470JCQ

C670 4030006850 S.CERAMIC C1608 JB 1H 471K-T-A

C671 4030013850 S.CERAMIC ECUE1E102KBQ

C672 4030014180 S.CERAMIC ECUE1H470JCQ

C673 4030014180 S.CERAMIC ECUE1H470JCQ

C674 4030014180 S.CERAMIC ECUE1H470JCQ

C675 4030014220 S.CERAMIC ECUE1E471KBQ

J2 6450001680 CONNECTOR HSJ1122-010010

J3 6450001690 CONNECTOR HSJ1456-01-220

J5 6510018430 S.CONNECTOR AXN330C038P

J6 6510021900 S.CONNECTOR BM02B-ASRS-TF

DS1 5030001800 LCD LM-7045B

DS2 5010000160 S.LED LNJ310M6URA

DS3 5010000160 S.LED LNJ310M6URA

MC1 7700002160 MICROPHON KUC3523-040245

S1 2230000900 S.SWITCH JPM1990-2013R

S2 2230000900 S.SWITCH JPM1990-2013R

S3 2230000900 S.SWITCH JPM1990-2013R

SP1 2510001060 SPEAKER K036NA500-47

W1 8900009640 CABLE OPC-963

W5 7030009970 S.JUMPER MJ-0.1

W10 7030003860 S.JUMPER ERJ3GE JPW V

W11 7030003860 S.JUMPER ERJ3GE JPW V

W12 7030003860 S.JUMPER ERJ3GE JPW V

W15 7030010040 S.JUMPER ERJ2GE-JPW

EP1 0910052732 PCB B 5387B

EP2 8930051310 LCD CONTACT SRCN-2251-SP-N-W

EP10 6910013370 S.BEAD BLM11B221SB

EP11 6910013370 S.BEAD BLM11B221SB

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

Page 22

SECTION 7 MECHANICAL PARTS AND DISASSEMBLY

7 - 1

REF. NO. ODER NO. DESCRIPTION QTY.

MP1 8210016750 2251-T front panel [F4GT] 1

8210016740 2251-S front panel [F4GS] 1

MP2 8930050890 2251 terminal holder 1

MP3 8010017990 2251 chassis 1

MP4 8210016570 2251 rear panel 1

MP5 8930050870 2251 release button 1

MP7 8310047580 2251 window plate 1

MP8 8930051350 2251 jack rubber 1

MP9 8210016550 2251 jack panel 1

MP10 8610010780 Knob N-276 1

MP12 8930050820 2251 main seal 1

MP13 8930050790 2251 10key [F4GT] 1

8930050590 2251 6key [F4GS] 1

MP14 8930050840 2251 minus terminal 1

MP15 8930050850 2251 plus terminal 1

MP18 8930050880 2251 spring holder 1

MP20 8930042350 1922 mic sheet 1

MP21 8930051300 2251 mic sponge 1

MP22 8930051290 2251 opt sheet 1

MP23 8930001340 1903 hex nut 1

MP24 8930050900 2251 window sheet 1

MP25 8930036751 Spring 1

MP26 8950005260 Ant connector-102 1

MP27 8830001250 Ant connector-101 1

MP31 8810009510 Screw BT M2 x 4 NI-ZU 8

MP32 8810009560 Screw BT M2 x 6 ZK 7

MP33 8810000100 Screw M2 x 4 ZK 4

MP36 8930051330 2251 contact rubber 1

MP37 8930050800 2251 jack cap 1

MP38 8950005240 2251 contact spring 1

MP39 8860001210 2251 ANT rug

MP41 8510013020 2252 shield plate 1

MP42 8930007100 Aluminum sheet 1

[CHASSIS PARTS]

REF. NO . ODER NO . DESCRIPTION QTY.

DS1 5030001800 LM-7045B 1

SP1 2510001060 Speaker K036NA500-47 1

EP2 8930051310 LCD contact SRCN-2251-SP-N-W 1

MP1 8510011111 1922 VCO case-1 1

MP3 8930050810 2251 LCD holder 1

MP4 8210016580 2251 reflector 1

MP5 8410002230 2078 PA heatsink 1

MP6 8510011180 1923 VCO cover 1

MP8 8930052270 Shield sponge (d) 1

[MAIN UNIT]

Screw abbreviations A, B0, BT: Self-tapping

PH: Pan head

FH: Flat head

BiH: Bind head

SUS: Stainless

NI: Nickel

ZK: Black

REF. NO . ODER NO . DESCRIPTION QTY.

EP1 3310002290 Antenna FA-SC57U 1

MP1 8930042040 1922 Belt clip 1

MP2 8930051290 2251 OPT sheet 1

[ACCESSORIES]

EP1

EP2

MP1 MP2

Page 23

7 - 2

UNIT abbreviation (C): CHASSIS PARTS, (M): MAIN UNIT

MP4 (M)

MAIN unit

IC-F4GS parts

MP7 (C)

MP1 (C)

MP1 (C)

MP20 (C)

MP37 (C)

MP21 (C)

MP3 (M)

DS1 (M)

EP2 (M)

MP1 (M)

MP6 (M)

MP18 (C)

MP8 (M)

MP22 (C)

MP32 (C)

MP5 (M)

MP23 (C)

MP12 (C)

MP3 (C)

MP32 (C)

MP13 (C)

MP13 (C)

MP27 (C)

MP10 (C)

MP26 (C)

MP4 (C)

MP25 (C)

MP32 (C)

MP5 (C)

MP14 (C)

MP36 (C)

MP38 (C)

MP31 (C)

MP31 (C)

MP2 (C)

MP15 (C)

MP33 (C)

MP33 (C)

MP39 (C)

SP1 (M)

MP31 (C)

MP32 (C)

MP31 (C)

MP31 (C)

MP31 (C)

MP41 (C)

MP8 (C)

MP9 (C)

MP33 (C)

MP42 (C)

MP32 (C)

MP24 (C)

Page 24

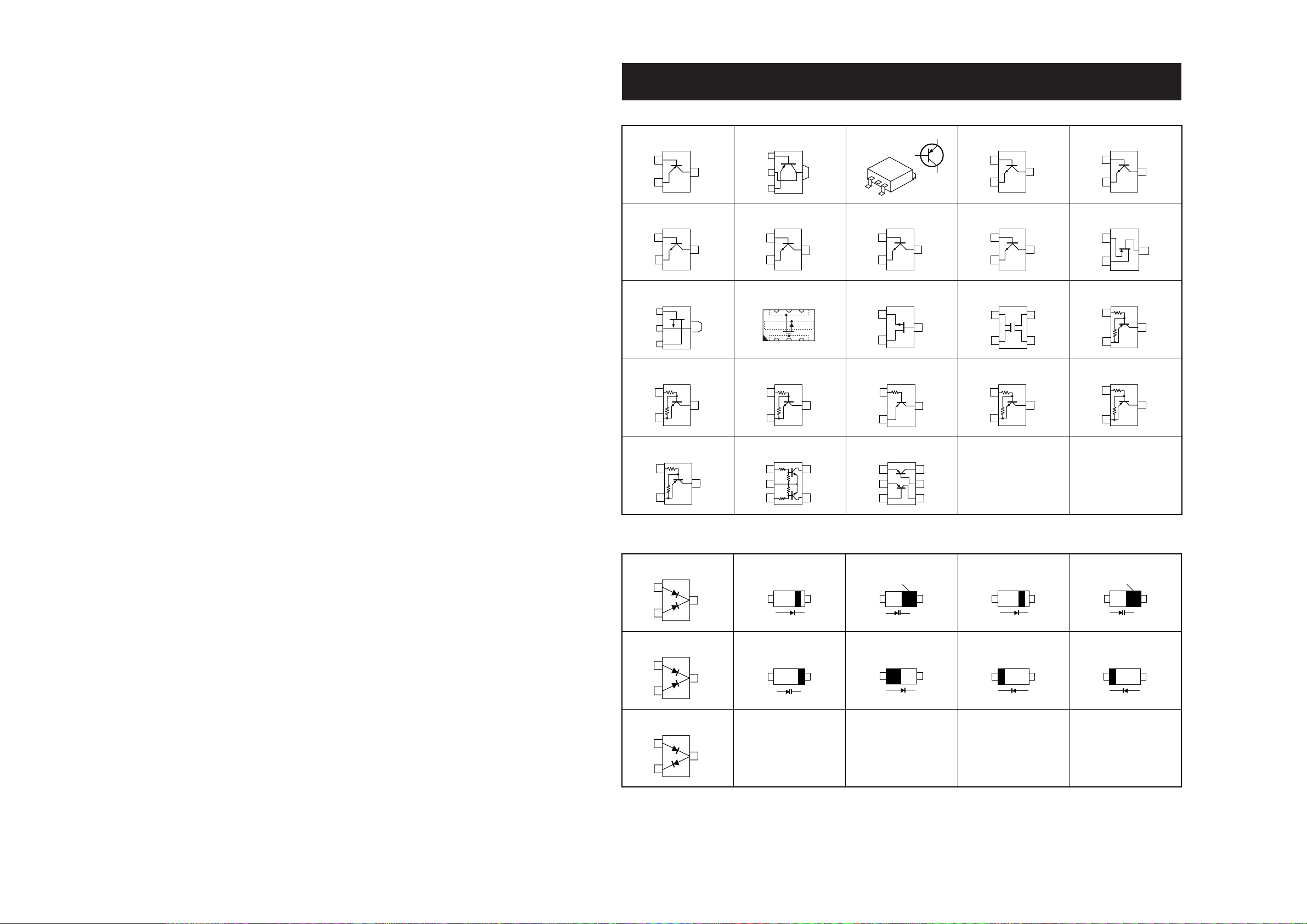

SECTION 8 SEMI-CONDUCTOR INFORMATION

8 - 1

2SC5085 Y

(Symbol: MCY)

2SC5107 O

(Symbol: MFO)

2SJ364 Q

(Symbol: 4MQ)

2SK2974

(Symbol: K2974)

2SC4116 GR

(Symbol: LG)

2SA1577 Q

(Symbol: HQ)

2SB1132 R

(Symbol: BARB)

2SB1201 S

(Symbol: B1201)

2SC2712 GR

(Symbol: LG)

2SC3585 R44

(Symbol: R44)

3SK239 A

(Symbol: XR)

2SK880 Y

(Symbol: XY)

2SC4215 O

(Symbol: QO)

2SK2973

(Symbol: K1)

DTC144 TU

(Symbol: 06)

DTC144 EU

(Symbol: 26)

XP1214

(Symbol: 9H)

DTC144 EE

(Symbol: 26)

XP6501 AB

(Symbol: 5N)

DTA144 EU

(Symbol: 16)

RN1409

(Symbol: XJ)

RN2402

(Symbol: YB)

•

TRANSISTOR AND FET’S

B

E

C

B

E

C

B

E

C

G

S

D

S

D

G

(top view)

S

D

S

G2

G1

B

E

C

B

E

C

E1

E2

B2

C1

B1

C2

B

E

C

B

E

C

UN911 H

(Symbol: 6P)

B

E

C

B

C

E

B

B

E

E

C

C

B

E

C

B

E

C

B

E

C

S

D

G

S

D

G

B

E

C

B

E

C

B

E

C

E1

B1

B2

C1

C2

•

DIODES

MA77

(Symbol: 4B)

HVU350

(Symbol: 4)

1SS184

(Symbol: B3)

1SS355

(Symbol: A)

DAN202K

(Symbol: N)

1SV288

(Symbol: TJ)

1SV307

(Symbol: TX)

1T365

(Symbol: pink line)

MA8030 H

(Symbol: 3^0)

MA8056 M

(Symbol: 5-6)

RB706F-40

(Symbol: 3J)

A

pink

C

A

C

C

A1

A2

C

A1

A2

A

C

A

C

A

pink

C

Page 25

SECTION 9 BOARD LAYOUTS

9 - 1

9-1 MAIN UNIT

• TOP VIEW

DS1

C291

R186

C443

C573

C561

C556

R116

C665

R530

R457

R502

C558

R507

C217

R518

C675

R142

C282

R244

C664

R527

C572

C495

R528

L441

C137

R30

Q25

R97

D4

R44

Q34

R14

Q401

Q403

R32

IC1

IC2

X3

C63

R89

R83

R90

C496

C112

C113

C159

C122

C289

C551

C405

R258

C156

C283

C121

R133

R257

R125

R155R205

C148

R169

R215

R170

L404

R414

C473

R79

C25

C19

L31

C9

Q37

R1

W12

R84

R93

R52

C73

R64

D11

D12

D27

R66

R61

C96

C92

R63

R252

R251

R210

R163

R62

C84

C90

L18

L22

R86

R85

Q19

L26

C21

Q1

C14

W5

C12

IC6

Q20

C117

C659

R445

R253

C452

C135

R177

R108

R33

C55

C54

R15

R9

R7

C26

R17

C75

C15

R65

C234

R223

J5 J6

R185

C233

C672

C42

R81

R80

C56

R12

C93

C95

W15

R13

R34

R41

C60

R511

C673

R109

R509

R503

R523

R421

R521

R520

C674

C472

R508

R115

C111

R529

C218

R526

R473

C116

R184

C571

R422

L406

C115

C492

C179

R176

C124

C552

R522

R401

R174

C574

R524

C252

R161

C467

R458

C285

C120

C160

R135

R88

W11

C118

R134

R420

C471

R446

C134

R105

R114

R117

C133

C136

L411

C214

R113

R204

R505

R107

C212

R168 C560

R512

L407

L12

R98

R67

R112

D3

C128

DS3

C51

L13

Q10

R82

R87

C18

C17

C11

R2

D32

C52

R54

D2

C78

D8

C13

C119

C667

Q18

Q402

Q14

Q3

Q2

L7

C22

C24

R53

C89

Q31

C48

C47

DS2

C491

Q11

+

+

C50

IC4

IC3

MC1

+

+

C213

+

+

+

+

+

+

C501

+

+

++

+

+

Page 26

9 - 2

• BOTTOM VIEW

C666

R162

C100

R448

C168

C165

EP10

C555

C106

C450

C110

C114

R261

R469

R464

R417

C417

C413

C414

R413

C419

R416

C411

C228

R203

C227

R224

R207

R122

R218

R219

R216

R101

R147

R146

C550

C154

C197

R131

C563

J5

1

R243

C663

C132

C230

C567

C194

C195

R515

C152

C149 R126

R220

R120

R127

C151

D404

D403

C416

C670

R506

R449

C104

C105

C669

R447

C557

C406

R404

C243

R159

C76

C3

D1

L1

C79

R55

R68

C153

C99

R70

L21

L20

Q13

R75

Q22

Q21

C158

L25

R20

R49

R51

Q33

R236

R238

R237

R191

R230

C249

R197

R211

C200

R532

R212

C201

C225

C202

R196

R195

R194

R193

C199

C564

C245

R245

R246

R22

C211

C198

IC7IC10

IC5

IC8

C145

X2

C28

R19

C418

C475

C123

R519

R48

R165

R154

C565

R164

R153

R152

R525

R531

R227

R517

C216

R202

C671

C29

C27

C486

D5

D26

L33

Q38

C66

C53

C65

FI2

X4

C174

C155

C173

L19

C98

D29

L24

C10

MP5

J2

J3

C8

R96

C125

C86

C85

C288

C204

C403

C404

R402

D401

C407

C251

R160

R100

R178

C455

C169

R144

R104

R262

R109

C162

R141

R139

C161

R260

C108

C107

C426

C410

R410

C424

C423

C566

C219

Q16

C140

R140

C662

C248

C232

R215

C231

C193

R103

D14

C196

C209